# **DRAGSTER Evaluation Board**

Revision History:

| Version | Date     | Modifications    | Author         |

|---------|----------|------------------|----------------|

| 4.0     | 19/05/15 | Updated document | Fátima Gouveia |

|         |          |                  |                |

|         |          |                  |                |

|         |          |                  |                |

|         |          |                  |                |

| DATE: | 19/05/15 | Version 4.0 | PAGE: | 2/37 |

|-------|----------|-------------|-------|------|

|-------|----------|-------------|-------|------|

### **Table of Contents**

| 1 General Concept                                   | 6  |

|-----------------------------------------------------|----|

| 1.1 Architecture Diagram                            | 7  |

| 1.2 Power Connection                                | 8  |

| 1.3 Board Reset                                     | 8  |

| 2 Evaluation Board components and connectors pinout | 9  |

| 2.1 Debug points in the Parallel TTL Connectors     |    |

| 3 Dragster Sensors                                  |    |

| 3.1 Assembling DR_4K_7um on the Evaluation board    |    |

| 3.2 Assembling DR_8K_7um on the Evaluation board    |    |

| 3.3 DR_8K_7um                                       |    |

| 3.4 Assembling DR_8K_3.5um on the Eval board        | 15 |

| 3.5 Assembling DR_16K_3.5um on the Eval board       |    |

| 3.6 DR_16K_3.5um                                    |    |

| 4 Camera-Link Data Interface                        |    |

| 4.1 TAP Assignment DR_16K_3.5um                     |    |

| 4.2 TAP Assignment DR_8K_7um                        |    |

| 5 Serial configuration interface                    |    |

| 5.1 Serial Port Configuration                       |    |

| 5.2 Communication data structure                    |    |

| 5.3 Command Structure                               |    |

| 5.3.1 Setting the Line Period                       |    |

| 5.3.2 Integration Time                              |    |

| 5.3.3 Registers content                             |    |

| 5.3.4 Reset to Evaluation Board and Sensor          |    |

| 6 Trigger Modes                                     |    |

| 6.1 Internal Trigger Mode                           |    |

| 6.2 External Trigger Mode                           |    |

| 7 Load pulse                                        |    |

| 8 ISAC – RS232 Communication Tool                   |    |

| 8.1 Software Installation                           |    |

| 8.2 Configuration of the communication port         |    |

| 8.3 Choose the sensor version under test            |    |

| 8.4 Register Configuration                          |    |

| 8.4.1 Enabling on chip offset subtraction           |    |

|                                                     |    |

| DATE: | 19/05/15 | Version 4.0 | PAGE: | 3/37 |

|-------|----------|-------------|-------|------|

|       |          |             |       |      |

| 8.4.2 Relation between ADC gain and ADC end of range |    |

|------------------------------------------------------|----|

| 8.4.3 Using analogue gain                            | 34 |

| 8.5 Frame Rate                                       |    |

| 8.6 Configure the ini file                           |    |

| 8.7 Debug Console                                    | 35 |

| 8.8 Known issues                                     |    |

| 9 SPARTAN 3AN JTAG Programming                       |    |

### **Index of Tables**

| Table 1: TTL Connectors Debug Signals                   | 10 |

|---------------------------------------------------------|----|

| Table 2: Data structure for uController                 | 21 |

| Table 3: Command Structure                              | 22 |

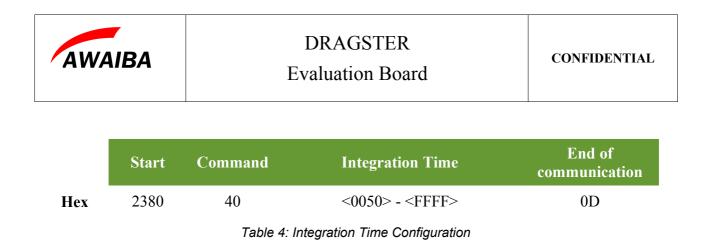

| Table 4: Integration Time Configuration                 | 24 |

| Table 5: SPI selection                                  | 24 |

| Table 6: SPI Command Structure                          | 25 |

| Table 7: Reset to Evaluation Board and Sensor           | 25 |

| Table 8: Dragster Registers Labels and Addresses        | 32 |

| Table 9: Relation between ADC gain and ADC end of range | 33 |

| Table 10: Frame per second description                  | 34 |

| Table 11: Companding Mode, registers configuration      | 35 |

| Table 12: Companding Mode, registers configuration      | 35 |

### **Index of Figures**

| Figure 1: Block Diagram                                   | 7  |

|-----------------------------------------------------------|----|

| Figure 2: Evaluation Board Power connection               | 8  |

| Figure 3: TTL Connectors Debug Signals Identification     | 10 |

| Figure 4: Assembling DR_4K_7um on the Evaluation board    | 11 |

| Figure 5: Assembling DR_8K_7um on the Evaluation Board    | 12 |

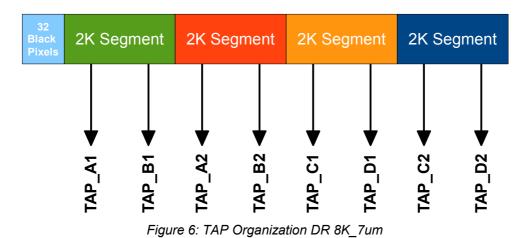

| Figure 6: TAP Organization DR 8K_7um                      | 13 |

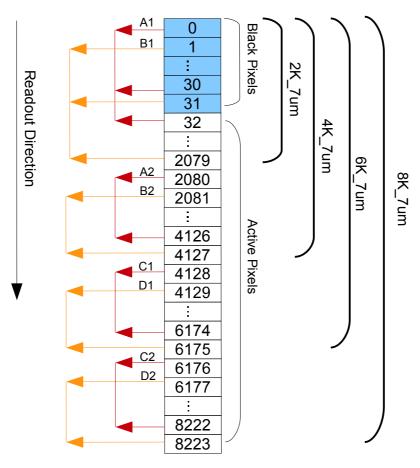

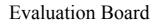

| Figure 7: TAP Organization according to pixel numbers     | 14 |

| Figure 8: Assembling DR_8K_3.5um on the Evaluation board  | 15 |

| Figure 9: Assembling DR_16K_3.5um on the Evaluation Board | 16 |

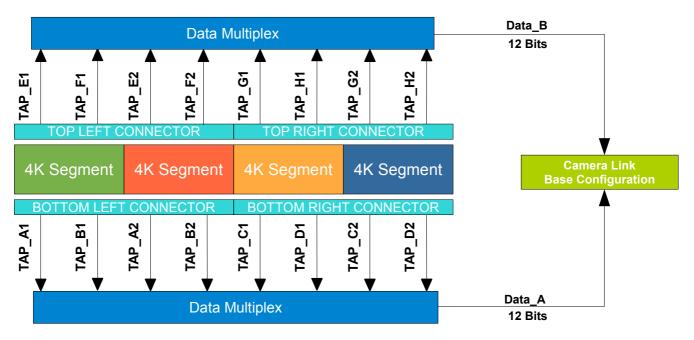

| Figure 10: TAP organization DR_16K_3.5um                  | 17 |

| Figure 11: TAP Organization according to pixel numbers    | 18 |

| DATE: 19/05/15 Version 4.0 PAGE: | 4/37 |

|----------------------------------|------|

|----------------------------------|------|

### **Evaluation Board**

| Figure 12: Camera Link Taps                               | 19 |

|-----------------------------------------------------------|----|

| Figure 13: Camera Link Taps                               | 20 |

| Figure 14: Trigger Modes description                      | 26 |

| Figure 15: Jumper on S16 and S17 to remove the Load Pulse | 27 |

| Figure 16: ISAC software                                  | 29 |

| Figure 17: ISAC - Serial Port Configuration               | 30 |

| Figure 18: ISAC - Registers Configuration                 | 31 |

| Figure 19: SPARTAN JTAG Chain                             | 36 |

| DATE: 19/05/15 | Version 4.0 | PAGE: | 5/37 |

|----------------|-------------|-------|------|

|----------------|-------------|-------|------|

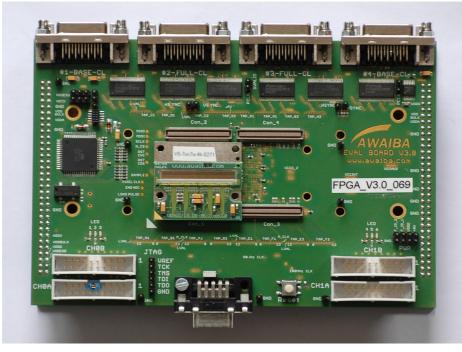

### **1** General Concept

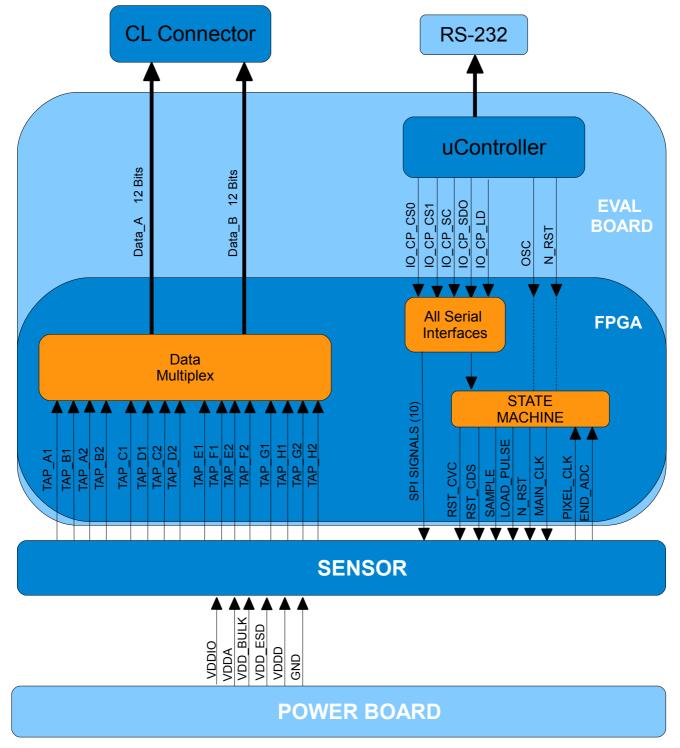

The evaluation system features a highly configurable hardware which enables an easy setup of Awaiba's Dragster line scan family for a quick sensor evaluation.

Image data is transferred to a frame grabber over high speed camera link. Any grabber that supports at least a camera link base configuration can directly acquire data from any Dragster version. The system controls sensor operation using an FPGA to define the state machine timings, it acquires data synchronously and multiplexes that data to Camera-Link Full interfaces.

Over an RS232 serial interface the user can have access to the state machine configuration and all sensor registers. It is possible to read back those sensor registers. Please refer to the serial communication section for further details of the serial communication protocol.

For debugging process, some digital IO sensor control signals sensor are routed as CMOS TTL signals to the parallel connectors.

The Evaluation board features two clock possibilities, one at 100MHz and another at 80MHz. In the current implementation the 80MHz oscillator is used to generate a sensor global clock of 20MHz, which is used for the FPGA state machine, while the Camera-Link interfaces will run at 40Mhz. All timing information in the reminder of this document are with respect to the 20MHz clock.

The evaluation of DRAGSTER sensors uses a stack of three boards:

- Sensor Head Board Contains the DRAGSTER sensor and connects to the FPGA board

- AWAIBA Evaluation Board versatile and easy to program, this board includes a SPARTAN 3AN FPGA, a micro controller for RS232 communication and 2 Camera Link full interfaces. It is the main board where the Sensor Head Board is connected.

- Evaluation Board Power Supply Under the main board there is a power supply board to create a group of filtered voltages to apply to the sensor, micro controller and RS232 sensor operation and camera-link

By default we have an FPGA code that reads out all sensors over 1 Camera Link, base connector, capable of operating the sensor with maximal line rate however discarding lines if the data rate coming from the sensor exceeds the data rate that can be transmitted over one base Camera Link connection. Alternatively we have specific FPGA codes that can support the sensors with full data transmission using up to 4 Camera Link base or 2 Camera Link medium configurations.

|  | DATE: 19/05/15 | Version 4.0 | PAGE: | 6/37 |

|--|----------------|-------------|-------|------|

|--|----------------|-------------|-------|------|

### 1.1 Architecture Diagram

Resume of the interface connections between the different components of the Evaluation Board.

Figure 1: Block Diagram

| DATE: 19/05/15 | Version 4.0 | PAGE: | 7/37 |

|----------------|-------------|-------|------|

|----------------|-------------|-------|------|

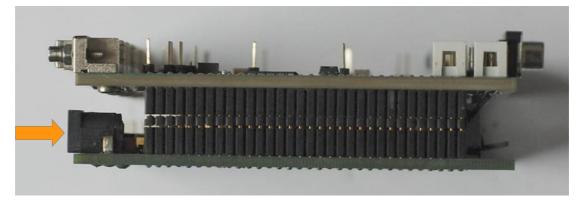

#### **1.2 Power Connection**

The system main input voltage is 12V DC (Figure 2). A green LED in the power board will turn on when the power is connected. It has also a 1A soldered fuse for user safety and board protection. After any wrong manipulation check its connectivity and if the LED does not start please replace the fuse by another with same specification.

All voltages are generated in this board.

Figure 2: Evaluation Board Power connection

### 1.3 Board Reset

It's a good practise to perform a full system reset before starting evaluating the sensor. In the AWAIBA Evaluation Board there are two possibilities to make this reset: by pressing the Reset button or by sending the reset command. Both have the same effect of restarting the state machine's operation. After this the sensor is loaded with the default values defined in the datasheet, which may obviously need to be reconfigured to match the current setup.

*Note:* Always perform a reset to the system after power up to guarantee a defined power up status!

If the board does not start operation after power up, if the sensor was wrong configured or if data is not consistent, please press the board reset button and reconfigure the sensor.

| _ |               |               | 1     |      |

|---|---------------|---------------|-------|------|

|   | DATE: 19/05/1 | 5 Version 4.0 | PAGE: | 8/37 |

|   |               |               |       |      |

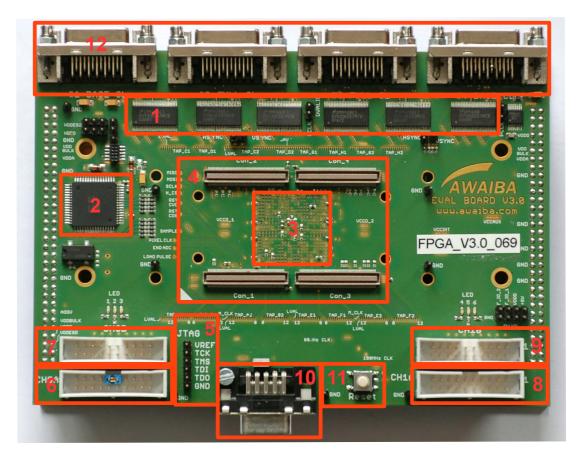

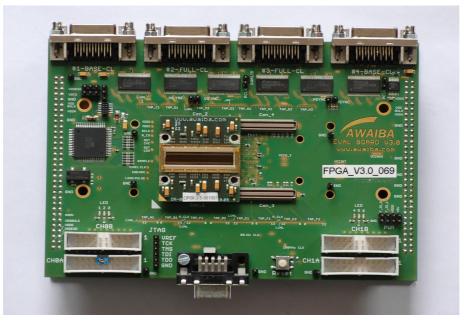

# 2 Evaluation Board components and connectors pinout

| Legend:                           |                                    |

|-----------------------------------|------------------------------------|

| 1. Camera Link Drivers            | 7. Parallel TTL Connector Ch0B     |

| 2. ATMega 128 Controller          | 8. Parallel TTL Connector Ch1A     |

| 3. Spartan 3AN FPGA (bottom side) | 9. Parallel TTL Connector Ch1B     |

| 4. Sensor Connectors Base         | 10. Serial Communication Connector |

| 5. JTAG Connector                 | 11. Board Reset Button             |

| 6. Parallel TTL Connector Ch0A    | 12. Camera-Link Connector          |

| DATE: | 19/05/15 | Version 4.0 | PAGE: | 9/37 |

|-------|----------|-------------|-------|------|

|-------|----------|-------------|-------|------|

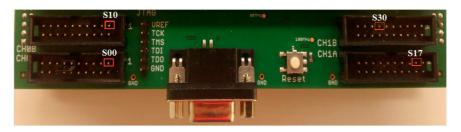

### 2.1 Debug points in the Parallel TTL Connectors

| TTL Connector | S-Connectors<br>Channel | Signal Name                       |

|---------------|-------------------------|-----------------------------------|

|               | S00                     | 80MHz clock                       |

|               | S01                     | 100MHz clock                      |

|               | S02                     | Sensor clock                      |

| CH0A          | S03                     | Camera Link drivers clock         |

| CHUA          | S04                     | VCC                               |

|               | S05                     | Trigger selector jumper           |

|               | S06                     | Internal trigger signal           |

|               | S07                     | External trigger signal (input)   |

| CH0B          | S10                     | Sensor SCLK                       |

|               | S16                     | Test Mode Jumper (Load Pulse Off) |

|               | S17                     | VDD                               |

|               | S18                     | END ADC AB1                       |

| CH1A          | S19                     | LVAL AB1                          |

| CHIA          | S20                     | Sensor Load Pulse                 |

|               | S21                     | Sensor Sample                     |

|               | S22                     | Sensor RST CVC                    |

| -             | S23                     | Sensor RST CDS                    |

| CH1B          | S30                     | Pixel CLK AB1                     |

Table 1: TTL Connectors Debug Signals

Figure 3: TTL Connectors Debug Signals Identification

| DATE:         19/05/15         Version 4.0         PAGE: | 10/37 |

|----------------------------------------------------------|-------|

|----------------------------------------------------------|-------|

### **3 Dragster Sensors**

### 3.1 Assembling DR\_4K\_7um on the Evaluation board

The DR\_4K\_7um Sensor is assembled in connector 1 of the Evaluation Board, with the triangle marks aligned (Figure 4).

Figure 4: Assembling DR\_4K\_7um on the Evaluation board

| DATE: 19/05/15 | Version 4.0 | PAGE: | 11/37 |

|----------------|-------------|-------|-------|

|----------------|-------------|-------|-------|

### 3.2 Assembling DR\_8K\_7um on the Evaluation board

The DR\_8K\_7um sensor is assembled in the BOTTOM SIDE connectors (Connector 1 and Connector 3) of the Evaluation Board, with the triangle marks aligned (Figure 5).

Figure 5: Assembling DR\_8K\_7um on the Evaluation Board

| DATE: | 19/05/15 | Version 4.0 | PAGE: | 12/37 |

|-------|----------|-------------|-------|-------|

|-------|----------|-------------|-------|-------|

### 3.3 DR\_8K\_7um

Dragster 8K\_7um sensor is made out of segments with 2K pixels and 7um pitch. Each 2K segment has 2 taps outputs of 12 bits width. At sensor's beginning (readout direction) there are 32 extra black pixels that are read out and make part of the first 2K segment (taps A1, B1).

DATE: 19/05/15 Version 4.0 PAGE: 13/37

### **Evaluation Board**

Figure 7: TAP Organization according to pixel numbers

| DATE: 19/05/15 | Version 4.0 | PAGE: | 14/37 |

|----------------|-------------|-------|-------|

|----------------|-------------|-------|-------|

#### 3.4 Assembling DR\_8K\_3.5um on the Eval board

The DR\_8K\_3.5um sensor is assembled in connectors Connector 1 and Connector 2 of the Evaluation Board, with the triangle marks aligned (Figure 8).

Figure 8: Assembling DR\_8K\_3.5um on the Evaluation board

| DATE: 19/ | /05/15 | Version 4.0 | PAGE: | 15/37 |

|-----------|--------|-------------|-------|-------|

|-----------|--------|-------------|-------|-------|

### 3.5 Assembling DR\_16K\_3.5um on the Eval board

The DR\_16K\_3.5um sensor is assembled in the 4 connectors of the Evaluation Board. The sensor orientation is such that the triangle marker on the sensor head board aligns with the white triangle on the Evaluation board (Figure 9).

Figure 9: Assembling DR\_16K\_3.5um on the Evaluation Board

| DATE: | 19/05/15 | Version 4.0 | PAGE: | 16/37 |

|-------|----------|-------------|-------|-------|

|-------|----------|-------------|-------|-------|

| AWAIBA | DRAGSTER<br>Evaluation Board | CONFIDENTIAL |

|--------|------------------------------|--------------|

|--------|------------------------------|--------------|

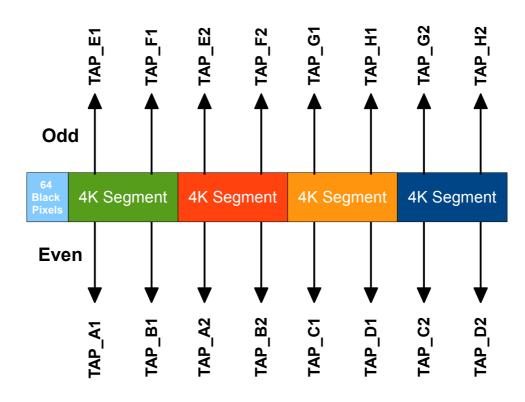

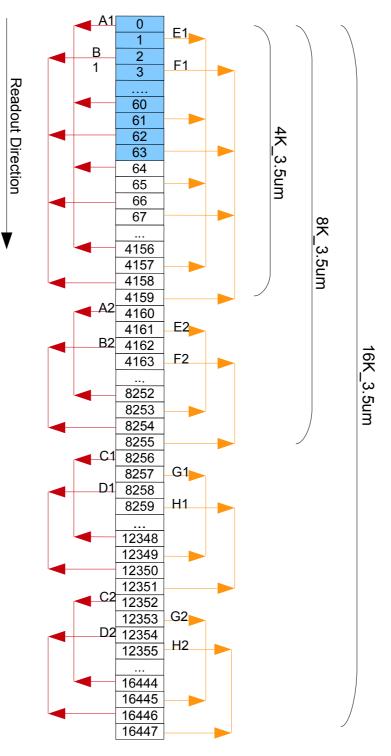

### 3.6 DR\_16K\_3.5um

Dragster 16K sensor is organized in segments of 4K pixels, described like this due to the 4 taps with 12 bit each. At the sensor's beginning (readout direction) there are 64 black extra pixels placed that are read out and make part of the first 4K segment (taps A1, B1, E1 and F1).

Figure 10: TAP organization DR\_16K\_3.5um

The Dragster 16K sensor has in total 16 TAPS of 12bits.

| DATE: 19/05/15 | Version 4.0 | PAGE: | 17/37 |

|----------------|-------------|-------|-------|

|----------------|-------------|-------|-------|

Figure 11: TAP Organization according to pixel numbers

| DATE: 19/05/15 | Version 4.0 | PAGE: | 18/37 |

|----------------|-------------|-------|-------|

|----------------|-------------|-------|-------|

### 4 Camera-Link Data Interface

### 4.1 TAP Assignment DR\_16K\_3.5um

The FPGA board can receive up to 16TAPS of 12 Bits each so that it reads out all DR\_16K\_3.5um sensor. The data received in the FPGA are multiplexed and sent to one Camera Link Connector through Data\_A and Data\_B.

Figure 12: Camera Link Taps

The explanation above is valid for DR\_16K\_3.5um sensors. Because the FPGA implementation is compatible with all sensor variations, that means that in case other sensors are tested, like DR\_4K or DR\_8K, not all the TAPs will contain valid data.

The Camera-Link driver chips can be enabled or disabled via the serial interface. Please refer to the Serial communication interface section for this details.

| DATE: 19/05/15 Version 4.0 | PAGE: 19/3' | 7 |

|----------------------------|-------------|---|

|----------------------------|-------------|---|

*Note: Make sure the Camera-Link drivers are enabled when trying to capture image data!*

### 4.2 TAP Assignment DR\_8K\_7um

Figure 13: Camera Link Taps

| DATE: | 19/05/15 | Version 4.0 | PAGE: | 20/37 |

|-------|----------|-------------|-------|-------|

|-------|----------|-------------|-------|-------|

**Evaluation Board**

### **5** Serial configuration interface

State machine's basic parameters, like line and integration time, together with all sensor's registers are accessible via a RS232 interface.

The serial communication uses a standard serial communication port on the PC side and a D-SUB 13 connector on board's side. (Serial communication over Camera-Link is not implemented).

### 5.1 Serial Port Configuration

- Baud Rate: 19200

- Databits: 8

- Stopbits: 1

- Parity: none

- Flow control: none

#### 5.2 Communication data structure

| HEX Format   | Function                                                               |

|--------------|------------------------------------------------------------------------|

| 23           | Start of transmission                                                  |

| 80           | Address of Evaluation Board                                            |

| 40 / 41 / 44 | Command                                                                |

| DATA         | MSBs Data for line/integration times or Register address of the sensor |

| ADDRESS      | LSBs Data for line/integration times or Data to send to the register   |

| 0D           | End of transmission                                                    |

Table 2: Data structure for uController

| DATE: | 19/05/15 | Version 4.0 | PAGE: | 21/37 |

|-------|----------|-------------|-------|-------|

|-------|----------|-------------|-------|-------|

### 5.3 Command Structure

| Command in HEX | Data                                        | Valid Data Range | Description                           |

|----------------|---------------------------------------------|------------------|---------------------------------------|

| 0x30           | None                                        | none             | Enable 4k-side Camera Link Chips      |

| 0x31           | None                                        | none             | Disable 4k-side Camera Link Chips     |

| 0x32           | None                                        | none             | Enable 8k-side Camera Link Chips      |

| 0x33           | None                                        | none             | Disable 8k-side Camera Link Chips     |

| 0x40           | <hi_byte><br/><lo_byte></lo_byte></hi_byte> | 0x00000xFFFF     | Set Integration time                  |

| 0x41           | <hi_byte><br/><lo_byte></lo_byte></hi_byte> | 0x00000xFFFF     | Set Line time                         |

| 0x44           | <hi_byte><br/><lo_byte></lo_byte></hi_byte> | 0x00000x0FFF     | Write to AB1 segment SPI channels     |

| 0x44           | <hi_byte><br/><lo_byte></lo_byte></hi_byte> | 0x10000x1FFF     | Write to CD1 segment SPI channels     |

| 0x44           | <hi_byte><br/><lo_byte></lo_byte></hi_byte> | 0x20000x2FFF     | Write to AB2 segment SPI channels     |

| 0x44           | <hi_byte><br/><lo_byte></lo_byte></hi_byte> | 0x30000x3FFF     | Write to CD2 segment SPI channels     |

| 0x44           | <hi_byte><br/><lo_byte></lo_byte></hi_byte> | 0x40000x4FFF     | Write to EF1 segment SPI channels     |

| 0x44           | <hi_byte><br/><lo_byte></lo_byte></hi_byte> | 0x50000x5FFF     | Write to GH1 segment SPI channels     |

| 0x44           | <hi_byte><br/><lo_byte></lo_byte></hi_byte> | 0x60000x6FFF     | Write to EF2 segment SPI channels     |

| 0x44           | <hi_byte><br/><lo_byte></lo_byte></hi_byte> | 0x70000x7FFF     | Write to GH2 segment SPI channels     |

| 0x44           | <hi_byte><br/><lo_byte></lo_byte></hi_byte> | 0x80000x8FFF     | Write to all bottom side SPI channels |

| 0x44           | <hi_byte><br/><lo_byte></lo_byte></hi_byte> | 0x90000x9FFF     | Write to all top side SPI channels    |

| 0x44           | <hi_byte><br/><lo_byte></lo_byte></hi_byte> | 0xA0000xAFFF     | Write to all SPI channels             |

| 0x44           | None                                        | 0xBXXX           | Send a reset                          |

Table 3: Command Structure

Please note that the Camera-Link interface is made of a chip set with internal PLL's. In order to reset the PLL's for the case they might have booted in illegal state, use the commands 31 and 30.

| DATE: | 19/05/15 | Version 4.0 | PAGE: | 22/37 |

|-------|----------|-------------|-------|-------|

|-------|----------|-------------|-------|-------|

*Note: Make sure the Camera-Link drivers are enabled when trying to capture image data!*

#### 5.3.1 Setting the Line Period

To set the line time, use command 0x41 and a 16bit value. The line time is adjusted in multiples of 50ns (20MHz main clock). It is user responsibility to keep the line time above the minimum value permitted with the applied sensor register setting. The line time must in any case be longer than the maximum of:

- ADC time (controlled by sensor register 0x09) + 1us

- Integration Time (controlled by command 0x40) + 1us

but never larger than 3276us.

**Note:** Setting the line period shorter than the integration time or the time required for ADC conversion shorter than data readout time will set the state machine in an undefined state with unpredictable output, and require a global reset to restore proper operation!

#### 5.3.2 Integration Time

The integration time is controlled by command 0x40 and it's value is also multiple of 50ns, like the line period.

The minimum allowed integration time for the evaluation board is 3us or 0x0078h. (the sensor itself permits 2us minimal integration time). The maximum programmable integration time is 0xFFFF which corresponds to 3276us. It is the users responsibility to assure that the integration time is set shorter than the line period, otherwise the state machine will fall in an illegal state.

| DATE: 19/05/15 |  | PAGE: 23/37 |  |

|----------------|--|-------------|--|

|----------------|--|-------------|--|

#### 5.3.3 Registers content

The Dragster Sensors features a separate SPI for each segment (2K). The SPI "segments" can be selected according to the following table.

| 1 <sup>st</sup> 4 bits Data | Selected SPI                  |

|-----------------------------|-------------------------------|

| 0                           | AB1 segment SPIs              |

| 1                           | CD1 segment SPIs              |

| 2                           | AB2 segment SPIs              |

| 3                           | CD2 segment SPIs              |

| 4                           | EF1 segment SPIs              |

| 5                           | GH1 segment SPIs              |

| 6                           | EF2 segment SPIs              |

| 7                           | GH2 segment SPIs              |

| 8                           | All BOTTOM SIDE segments SPIs |

| 9                           | All TOP SIDE segments SPIs    |

| А                           | Write to all SPIs             |

Table 5: SPI selection

*Note:* Normally the best results should be obtained by writing identical content to all SPI registers. Writing conflicting operation modes or settings to the respective segments may stop the sensor or Evaluation Board from functioning or lead to severely distorted image data!

The sensor SPI is controlled with the command "D" and the bit structure is:

| DATE: 19/05/15 | Version 4.0 | PAGE: | 24/37 |

|----------------|-------------|-------|-------|

|----------------|-------------|-------|-------|

| AI  | WAIB  | A       | E           | DRAGSTER<br>valuation Board    |                       | CONFIDENTIAL         |

|-----|-------|---------|-------------|--------------------------------|-----------------------|----------------------|

|     | Start | Command | Data<br>MSB | 4bit Register<br>Address (0-F) | 8bit Register<br>data | End of communication |

| Hex | 2380  | 44      | 8           | <0-F>                          | <00>- <ff></ff>       | 0D                   |

Table 6: SPI Command Structure

Sensor registers must be written in first place and the new settings will only take effect after setting the "update request bit" in the control register (address 0x01)

Please refer to the Dragster Datasheet Section 9 for more detailed description of the sensor registers.

#### 5.3.4 Reset to Evaluation Board and Sensor

To send a reset to the Evaluation Board and sensor a command must be sent via RS232.

|     | Start | Command | Data<br>MSB | 4bit Register<br>Address (0-F) | 8bit Register<br>data | End of communication |

|-----|-------|---------|-------------|--------------------------------|-----------------------|----------------------|

| Hex | 2380  | 44      | В           | 0xX                            | 0xXX                  | 0D                   |

Table 7: Reset to Evaluation Board and Sensor

Note: The 12 less significant data bits are "don't care" bits!

| DATE: 19/05/15 Version 4.0 | PAGE: 25/37 |

|----------------------------|-------------|

|----------------------------|-------------|

# 6 Trigger Modes

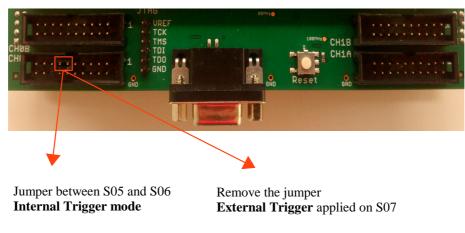

The state machine implemented for timing control allows internal or external trigger modes and to switch between these modes is used a jumper.

Figure 14: Trigger Modes description

The S07 Channel is used to input the trigger signal and the pin right under can be used to connect GND.

### 6.1 Internal Trigger Mode

For internal trigger mode a jumper must be placed between S05 and S06, pulling the S06 to HIGH state. The internal trigger is generated according to the line time.

### 6.2 External Trigger Mode

For external trigger operation the jumper for internal trigger mode must be removed and the external trigger signal must be supplied in the S07 pin in the Parallel TTL Connector Ch0A. To restore to internal mode the jumper must be placed like described in the previous point.

**Note:** The implemented state machine will discard a trigger event that occurs while the sensor is still in a readout/integration mode. The trigger event will be discarded if it is sent before the line period counter reached it's end state. The user can use the internal signals of the state machine available on the Parallel TTL Connectors to define the correct trigger moment!

| DAT | E: 19/05/15 | Version 4.0 | PAGE: | 26/37 |  |

|-----|-------------|-------------|-------|-------|--|

|-----|-------------|-------------|-------|-------|--|

# 7 Load pulse

When the Auto Generation bit, from register 0x02, is set to "0" the sensor sends the output data without the need of sending the external Load Pulse.

The Load Pulse generation is turned off on the FPGA, when the Test Mode Jumper is connected as in figure 15.

Figure 15: Jumper on S16 and S17 to remove the Load Pulse.

| DATE: 19/05/15 | Version 4.0 | PAGE: | 27/37 |

|----------------|-------------|-------|-------|

|----------------|-------------|-------|-------|

DRAGSTER Evaluation Board

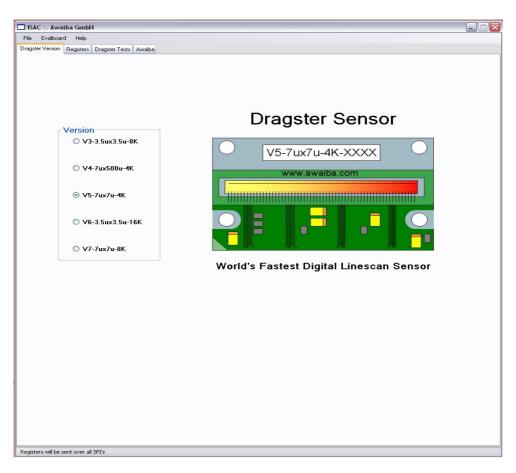

### 8 ISAC – RS232 Communication Tool

#### 8.1 Software Installation

The ISAC tool can be used to communicate with Dragster line-scan sensors and its a simple software that allows the user to send commands to sensor registers using a RS232 communication port. With this software the user can configure all the sensor operation modes in order to achieve the best configuration settings for the set up and take advantage over it's great performance.

To run the installation package please launch the executable sent with the Evaluation system, follow the instructions and one ISAC icon will appear in the desktop. This software is distributed only under the operating system Windows.

The following sequence of steps are mandatory before sending a command to the sensor:

- Configure the serial port under "EvalBoard" → "Configure" → "Serial Port" choose the right port of your system from the drop menu (figure 17)

- Choose the sensor under test in the "Dragster Version" tab (figure 16)

- Send registers in the "Registers" tab (figure 18)

- As extra options, it's possible to check the Ini file considered by the software ("File" → "IniFile..."), to activate and de-activate both camera link interfaces ("Evalboard" → "CL drivers") and to double check the software version ("Help" → "About...")

| DATE: 19/05/15 | Version 4.0 | PAGE: | 28/37 |

|----------------|-------------|-------|-------|

|----------------|-------------|-------|-------|

Figure 16: ISAC software

#### 8.2 Configuration of the communication port

Before start communicating with the sensor, it's necessary to set the communication port parameters.

Click on "Evalboard"  $\rightarrow$  "Configure"  $\rightarrow$  "Serial Port..." menu and set the COM port number where the sensor is connected to.

| DATE: 19/05/15 | Version 4.0 | PAGE: | 29/37 |

|----------------|-------------|-------|-------|

|----------------|-------------|-------|-------|

|  | AWAIBA | DRAGSTER<br>Evaluation Board | CONFIDENTIAL |

|--|--------|------------------------------|--------------|

|--|--------|------------------------------|--------------|

| 🖳 Eval Serial COM port  | <u>×</u> |  |  |  |  |  |

|-------------------------|----------|--|--|--|--|--|

| Port Settings           |          |  |  |  |  |  |

| Serial Port: COM1 💌     |          |  |  |  |  |  |

| Baud Rate: 19200 💌      |          |  |  |  |  |  |

| Data Bits: 8 💌          |          |  |  |  |  |  |

| Stop Bits: 1            |          |  |  |  |  |  |

| Parity: None 🗸          |          |  |  |  |  |  |

| Connect Cancel          |          |  |  |  |  |  |

| Com ports: 1 COM found. |          |  |  |  |  |  |

Figure 17: ISAC - Serial Port Configuration

All other parameters (baud rate, data bits, stop bits and parity) are well selected by default so just press "Connect".

#### 8.3 Choose the sensor version under test

The sensor version is chosen in ISAC's first tab. It is important to choose the right version because of SPI compatibilities since they have different address assignments.

#### 8.4 Register Configuration

In the **Registers** tab all 10 Dragster register values are accessible together with the state machine timings.

**Note:** Edit the respective register content but take in account that some modes are not compatible and can lead to sensor wrong function. Please refer to the respective sections of Dragster sensor datasheet and Evaluation board documentation for description of the register content and functionality of the bit switches in the control registers!

| DATE: 19/05/1 | Version 4.0 | PAGE: 30/ | 37 |

|---------------|-------------|-----------|----|

|---------------|-------------|-----------|----|

### **Evaluation Board**

| 🗆 DragsterComm 📃 🗆 🔯                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                      |                       |        |                         |                                                 |                    |          |        |     |     |                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------|--------|-------------------------|-------------------------------------------------|--------------------|----------|--------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| File Evalboard Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                      |                       |        |                         |                                                 |                    |          |        |     |     |                                                                                                                                                                          |

| Dragster Version Registers Dragster Tests Av                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | vaiba                                                                                                |                       |        |                         |                                                 |                    |          |        |     |     |                                                                                                                                                                          |

| Evaluation Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                      |                       |        |                         |                                                 |                    |          |        |     |     |                                                                                                                                                                          |

| Line Period (us): 500 Send = 0x4E20 Sensor Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                      |                       |        |                         |                                                 |                    |          |        |     |     |                                                                                                                                                                          |

| Integration time (us): 410 Send = 0x4038                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                      |                       |        |                         |                                                 |                    |          |        |     |     |                                                                                                                                                                          |

| Dragster                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                      |                       |        |                         |                                                 |                    |          |        |     |     |                                                                                                                                                                          |

| Control 1         1         0           Bit 7 - Vthr_whiteclamp:         ○         ○           Bit 6 - Companding:         ○         ○           Bit 5 - 12 bit seturation:         ○         S           Bit 4 - Subtract offset:         ○         S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Control 2<br>Bit 7 - Not used<br>Bit 6 - Not used<br>Bit 5 - Analog gain x4:<br>Bit 4 - White clamp: |                       |        | Bit 7<br>Bit 6<br>Bit 5 | rol 3<br>- Not u<br>- Not u<br>- Band<br>- Band | sed<br>gap sw      |          |        |     |     | ADC<br>Inverted ADC gain: 28 m Send Reg 0x03= 0x10<br>Inverted black level: 48 m Send Reg 0x04= 0x00<br>Threshold 1 [D.N.]: 64 m Send Reg 0x06= 0x02                     |

| Bit 3 - Dithering:         Image: Constraint of the second se | Bit 3 - Anti blooming:<br>Bit 2 - Write offset:<br>Bit 1 - Control Vref:<br>Bit 0 - Autogen readout  |                       |        | Bit 2<br>Bit 1          | -Band<br>-Offsel<br>-Re-lin<br>-PCLK            | t SRAM<br>earisati | :<br>on: |        |     |     | Threshold 2 [D.N.]:         128         Send         Reg 0x/07 =         0x/04           Threshold 3 [D.N.]:         512          Send         Reg 0x/07 =         0x/04 |

| Reg 0x01 = 0xA1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Reg 0                                                                                                | 0x02 = 0x10           |        |                         |                                                 | F                  | leg 0x05 | = 0x12 |     |     | End of range [D.N.]: 4090 Send Reg 0x03 = 0x7F                                                                                                                           |

| Choose the SPI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Sensor                                                                                               | r registers current s | tatus: |                         |                                                 |                    |          |        |     |     | Test multiplexer [Hex]: 15 Send Reg 0x0A = 0x0F                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                                                                                                    |                       | AB1    | AB2                     | CD1                                             | CD2                | EF1      | EF2    | GH1 | GH2 |                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Cont                                                                                                 | trol 1                | ххх    | xxx                     | ххх                                             | ххх                | ххх      | ххх    | ххх | ххх |                                                                                                                                                                          |

| V5-7ux7u-4K-XXXX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Cont                                                                                                 | trol 2                | XXX    | XXX                     | xxx                                             | ххх                | xxx      | xxx    | xxx | ххх |                                                                                                                                                                          |

| www.awajba.com                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Cont                                                                                                 | trol 3                | xxx    | XXX                     | xxx                                             | xxx                | xxx      | xxx    | xxx | xxx |                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                      | ADC gain              | xxx    | xxx                     | xxx                                             | xxx                | xxx      | xxx    | xxx | xxx |                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Inv.                                                                                                 | ADC black I           | xxx    | XXX                     | xxx                                             | XXX                | xxx      | ххх    | xxx | ххх | Send All                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ADC                                                                                                  | Threshold 1           | xxx    | xxx                     | xxx                                             | xxx                | xxx      | xxx    | xxx | xxx |                                                                                                                                                                          |