# AS5410 3D-Hall Absolute Linear Position Sensor

### **General Description**

The chip can measure magnetic field components in two different orientation directions and converts the magnetic field information into absolute position information. The AS5410 supports absolute linear position measurement applications.

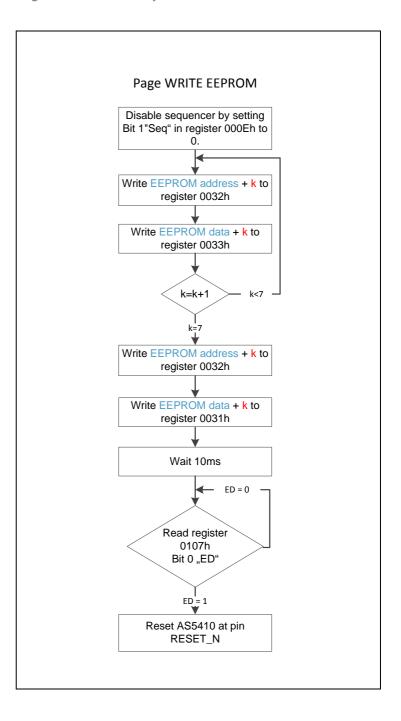

Only a simple 2-pole magnet is required as the magnetic field source.

Using two 3D-Hall cells allows both absolute as well as differential 3D magnetic field measurement.

The differential measurement makes the AS5410 ideal for use in rough industrial position sensing applications that include not only dust, dirt or moisture but also unwanted magnetic stray fields.

All the signal conditioning, including compensation of temperature effects, linearization of the output is included in the IC.

The absolute position information of the magnet is directly accessible over a SPI interface and PWM output. A cycle redundancy check (CRC) allows verification of the received data.

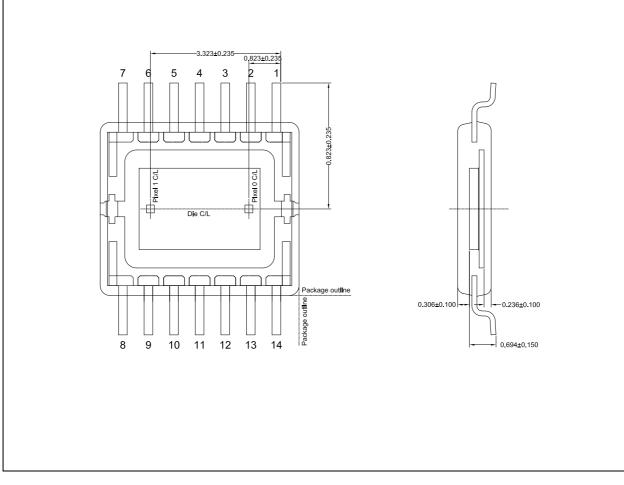

The AS5410 is available in a 14-pin TSSOP package and is qualified for an ambient temperature range from -40°C to  $105^{\circ}$ C.

It operates at a supply voltage of  $3.3V \pm 10\%$ .

Ordering Information and Content Guide appear at end of datasheet.

### Key Benefits & Features

The benefits and features of AS5410, 3D-Hall Absolute Linear Position Sensor are listed below:

Figure 1: Added Value of Using AS5410

| Benefits                                         | Features                                                                                                     |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| High flexibility in magnet selection             | Wide magnetic input range                                                                                    |

| Suppression against magnetic stray fields        | Dual 3D sensor pixel principle                                                                               |

| Flexibility in choice of interface               | SPI and PWM output                                                                                           |

| Contactless position sensing                     | Absolute linear position sensing                                                                             |

| Flexible mechanical arrangement of<br>magnet     | Flexible configuration registers                                                                             |

| External calculations of raw data                | Bx and Bz raw data assessment possible                                                                       |

| High linearity after teaching                    | 33 linearization points to achieve high precision                                                            |

| Ideal for applications in harsh     environments | <ul> <li>Integrated diagnostic functions</li> <li>Temperature range from -40°C to 105°C (ambient)</li> </ul> |

### **Applications**

AS5410 is ideal for:

- Plunger position

- Pedal position

- Pneumatic and hydraulic cylinder position

- Automation with linear position stages through cascading of several AS5410 devices.

Figure 2: AS5410 Linear Position Sensing of the Magnet

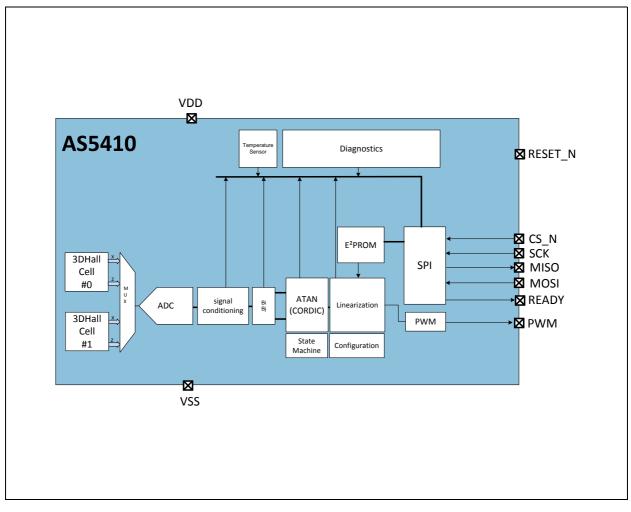

## **Block Diagram**

The functional blocks of this device are shown below.

# amu

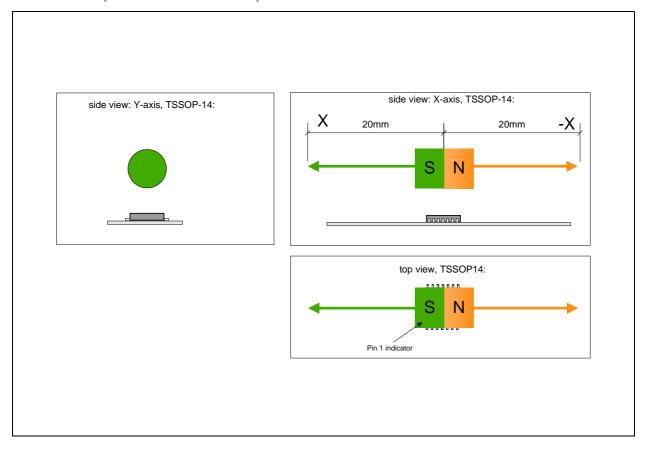

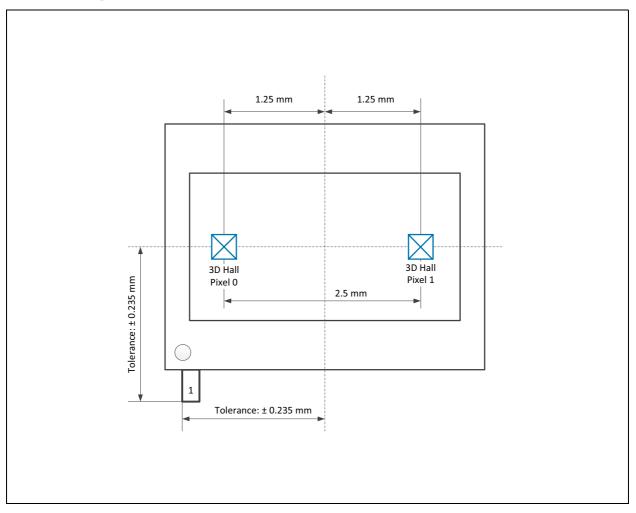

| 3D Hall cells:       | The AS5410 contains two 3D Hall cells, spaced 2.5mm apart.                                                                                                                                                                |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MUX:                 | The multiplexer selects two magnetic field components Bx and Bz as the inputs for the CORDIC. The selected inputs can either be absolute sensor signals or differential sensor signals.                                   |

| ADC:                 | The Sigma-Delta ADC samples the Hall sensors signals selected by the MUX. The sampling of the sensors is done sequentially.                                                                                               |

| Signal conditioning: | This block includes offset and temperature compensation as well as amplitude matching.                                                                                                                                    |

| Bi/Bj values:        | This block represents the registers containing the input sensor signals of the CORDIC inputs.                                                                                                                             |

| ATAN:                | Coordinate to Rotation Digital Computer: This block converts rectangular coordinates (sine and cosine signals from the Hall sensors) into polar coordinates (angle/distance and magnitude).                               |

| Linearization:       | A 33-point linearization of the CORDIC output data is available to accommodate a variety of different magnet sizes and applications.                                                                                      |

| Temperature sensor:  | An on-chip temperature sensor is available. It can be read over the SPI interface.<br>This sensor is also used for signal conditioning.                                                                                   |

| PWM interface:       | The linearized measurement data is available over a single pin in the form of a pulse width modulated (PWM) signal.                                                                                                       |

| SPI interface:       | A bi-directional SPI interface allows communication with the chip, including reading measurement data, E <sup>2</sup> PROM contents or writing configuration data.                                                        |

| E <sup>2</sup> PROM: | The on-chip E <sup>2</sup> PROM contains the configuration data of the chip.                                                                                                                                              |

| State machine:       | The state machine (sequencer) controls the automatic sequencing of measurements. Once it is configured for a certain measurement, the state machine executes all necessary steps to perform a complete measurement cycle. |

| Configuration:       | The configuration is pre-defined in the AS5410. Mode selection.                                                                                                                                                           |

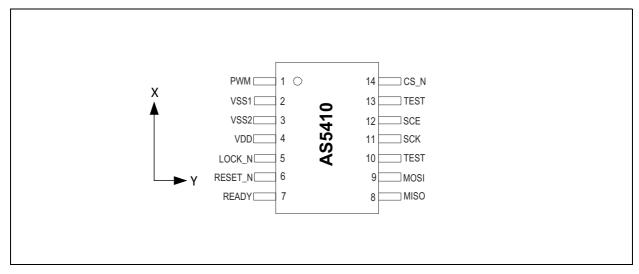

## **Pin Assignment**

### Pin Diagram

Figure 4: AS5410 Pin Configuration, TSSOP-14 Package (Top View)

#### Note(s) and/or Footnote(s):

1. X indicates the axis of lateral position measurement; z axis is perpendicular to the package surface

### **Pin Description**

Figure 5: Pin Description

| Pin<br>TSSOP | Symbol  | Туре   | Description                                                                                                                  |

|--------------|---------|--------|------------------------------------------------------------------------------------------------------------------------------|

| 1            | PWM     | DO     | PWM output. The linearized output data is available on this pin.                                                             |

| 2            | VSS2    | S      | Ground (0V) <sup>(1)</sup>                                                                                                   |

| 3            | VSS1    | S      | Ground (0V) <sup>(1)</sup>                                                                                                   |

| 4            | VDD     | S      | Positive supply voltage (3.0V to 3.6V)                                                                                       |

| 5            | LOCK_N  | DI_ST  | Test pin, must be connected to VSS in normal operation                                                                       |

| 6            | RESET_N | DIO_ST | Reset input (active low) to be connected with open drain driver. In case of output application leave open                    |

| 7            | READY   | DO     | Measurement ready signal is set high when a measurement cycle is completed and the results in the output registers are valid |

| 8            | MISO    | DO_T   | Master in / Slave out (SPI interface data output)                                                                            |

| 9            | MOSI    | DI_ST  | Master out / Slave in (SPI interface data input)                                                                             |

| 10           | TEST    | DIO    | Must be connected to VSS.                                                                                                    |

# amu

| Pin<br>TSSOP | Symbol | Туре  | Description                                            |

|--------------|--------|-------|--------------------------------------------------------|

| 11           | SCK    | DI_ST | SPI interface clock input (max. 1 MHz)                 |

| 12           | SCE    | DI_ST | Test pin, must be connected to VSS in normal operation |

| 13           | TEST   | DI_ST | Test pin, must be connected to VSS in normal operation |

| 14           | CS_N   | DI_ST | Chip select (active low)                               |

#### Note(s) and/or Footnote(s):

1. Both VSS1 and VSS2 must be connected.

2. CS\_N is active low and activates data transmission. If only a single device is used, CS\_N may remain low for several commands, for example while reading the output registers.

Abbreviations for Pin Types in Figure 5:

| DO  | : Digital output         |

|-----|--------------------------|

| DIO | : Digital input & output |

- DI\_ST : Digital Schmitt-Trigger input

- DO\_T : Digital output /tri-state

- S : Supply pin

- DIO\_ST : Digital Schmitt-Trigger input & output

## **Electrical Characteristics**

## **Absolute Maximum Ratings**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in Operating Conditions is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Figure 6: Absolute Maximum Ratings

| Parameter                             | Min  | Мах      | Unit   | Comments                                               |

|---------------------------------------|------|----------|--------|--------------------------------------------------------|

| DC supply voltage at pin VDD          |      | 5        | V      |                                                        |

| Input pin voltage                     | -0.3 | VDD +0.3 | V      |                                                        |

| Input current<br>(latchup immunity)   | -100 | 100      | mA     | Norm: JEDEC 78                                         |

| Electrostatic discharge               |      | ±2       | kV     | Norm: MIL 883 E method 3015                            |

| Storage temperature                   | -55  | 150      | °C     | Min – 67°F; Max 257°F                                  |

| Body temperature                      |      | 260      | °C     | IPC/JEDEC J-Std-020 Lead finish<br>100% Sn "matte tin" |

| Relative humidity<br>(non-condensing) | 5    | 85       | %      |                                                        |

| Moisture sensitivity level (MSL)      |      | 3        |        | Represents a maximum floor time of 168h                |

| EEPROM read/write cycles              |      | 100      | cycles |                                                        |

## **Operating Conditions**

Operating conditions: operating temperature = -40°C to 105°C, VDD = 3.0-3.6V unless otherwise noted.

Figure 7: Electrical Characteristics

| Symbol           | Parameter                     | Min | Тур | Max | Unit | Note                                  |

|------------------|-------------------------------|-----|-----|-----|------|---------------------------------------|

| VDD              | Positive supply voltage       | 3.0 | 3.3 | 3.6 | V    |                                       |

| lsupp            | Supply current                |     | 15  |     | mA   | Active operation,<br>continuous mode  |

| T <sub>AMB</sub> | Operating ambient temperature | -40 |     | 105 | °C   | -40°F to 221°F                        |

| twu              |                               |     | 2   |     | ms   | From cold start                       |

| twlp             | Wake up time                  |     |     | 200 | μs   | From standby; see<br>Single Loop Mode |

## System Performance Specifications

Operating conditions: magnet placement as specified in Figure 2, operating temperature =  $-40^{\circ}$ C to  $105^{\circ}$ C, VDD = 3.0V to 3.6V, unless otherwise noted.

Figure 8: System Parameters

| Symbol             | Parameter                                    | Min               | Тур | Мах                  | Unit | Note |

|--------------------|----------------------------------------------|-------------------|-----|----------------------|------|------|

| B <sub>IR_x</sub>  | Magnetic Range X                             | ±5 <sup>(1)</sup> |     | ±60                  | mT   |      |

| B <sub>IR_z</sub>  | Magnetic Range Z                             | ±5 <sup>(1)</sup> |     | ±50                  | mT   |      |

| S <sub>var_x</sub> | Sensitivity Variation absolute X             |                   |     | ±1.85 <sup>(2)</sup> | %    |      |

| S <sub>var_z</sub> | Sensitivity Variation absolute Z             |                   |     | ±1.05 <sup>(2)</sup> | %    |      |

| dSx/dSz            | Sensitivity Ratio Drift X/Z                  |                   |     | ±1.00 <sup>(3)</sup> | %    |      |

| T <sub>S0</sub>    | Sampling rate configuration 0 <sup>(4)</sup> |                   | 1   | 1.08                 | ms   |      |

| T <sub>S1</sub>    | Sampling rate configuration 1 <sup>(4)</sup> |                   | 2   | 2.15                 | ms   |      |

#### Note(s) and/or Footnote(s):

1. Minimum condition is valid if both input components are above 5mT.

2. Maximum value of 1 sigma (static variation). Sensitivity variation absolute from part to part. Better performance can be reached with linearization step at end of line.

3. Over temperature. Value in % (1 sigma).

4. Configurable in register 000Bh.

# DC Characteristics for Digital Inputs and Outputs

### CMOS Schmitt-Trigger Inputs: LOCK\_N, RESET\_N, CLK, MOSI, SCK, CS\_N

Operating conditions: operating temperature =  $-40^{\circ}$ C to  $105^{\circ}$ C, VDD = 3.0V to 3.6V unless otherwise noted.

Figure 9: CMOS Schmitt-Trigger Inputs

| Symbol          | Parameter                    | Min  | Max  | Unit | Note                        |

|-----------------|------------------------------|------|------|------|-----------------------------|

| VIH             | VIH High level input voltage |      | 1.87 | V    | VDD = 3.0V                  |

| VIII            | vin high level liput voltage | 2.07 | 2.23 | v    | VDD = 3.6V                  |

|                 | VIL Low level input voltage  | 1.12 | 1.27 | V    | VDD = 3.0V                  |

| VIL             |                              | 1.42 | 1.52 | v    | VDD = 3.6V                  |

| l <sub>in</sub> | Input current                |      | 10   | mA   | for Vin >VDD <sup>(1)</sup> |

#### Note(s) and/or Footnote(s):

1. Input pin voltages higher than VDD (e.g. 5V TTL levels) must be limited by a series resistor to ensure that the maximum input current (lin) is not exceeded.

#### CMOS Outputs: READY, MISO, PWM

Operating conditions: operating temperature =  $-40^{\circ}$ C to  $105^{\circ}$ C, VDD = 3.0V to 3.6V unless otherwise noted.

Figure 10: CMOS Outputs: READY, MISO, PWM

| Symbol          | Parameter              | Min | Max | Unit | Note |

|-----------------|------------------------|-----|-----|------|------|

| VO <sub>H</sub> | Output high level      | 2.5 | VDD | V    |      |

| IO <sub>H</sub> | Output current, source |     | 8   | mA   |      |

| VOL             | Output low level       | 0   | 0.4 | V    |      |

| IOL             | Output current, sink   |     | 8   | mA   |      |

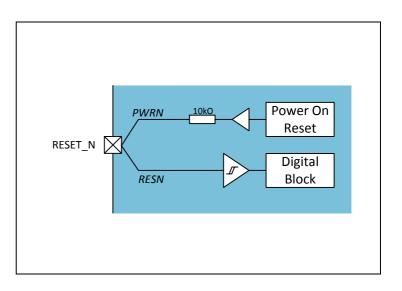

### Power On Reset

Operating conditions: operating temperature = -40°C to 105°C

| Figure | 11:      |

|--------|----------|

| Power  | On Reset |

| Symbol           | Parameter                          | Min  | Тур  | Мах  | Unit | Note |

|------------------|------------------------------------|------|------|------|------|------|

| V <sub>ON</sub>  | Reset threshold; VDD level rising  | 1.4  | 2.38 | 2.97 | V    |      |

| V <sub>OFF</sub> | Reset threshold; VDD level falling | 1.18 | 2.2  | 2.79 | V    |      |

| Tpwrmin          | Minimum reset pulse duration       | 1.8  |      | 7.1  | μs   |      |

#### RESET\_N

The RESET\_N pin can work as an output to monitor the internal power on reset signal (see Figure 12).

The RESET\_N can also work as an input and trigger an internal reset. While power on cycle is not finished, communication is not allowed until the READY pin is high.

Figure 12: Power On Reset

### **On-Chip Temperature Measurement**

The AS5410 provides a linear on-chip temperature sensor which is use for automatic compensation of sensitivity and offset drifts for the Hall-In-One sensors.

The measured chip temperature is available in a register (0110h) and can be used for monitoring purposes.

Operating conditions: operating temperature = -40°C to 105°C

Figure 13: Temperature Sensor

| Symbol              | Parameter                 | Min | Тур | Max | Unit  | Note |

|---------------------|---------------------------|-----|-----|-----|-------|------|

| D <sub>temp</sub>   | Temperature signal at 25° |     | 0   |     | LSB   |      |

| Res <sub>temp</sub> | Resolution                | 185 | 200 | 210 | LSB/K |      |

## **Detailed Description**

#### Power Modes

The AS5410 can be configured for two power modes:

- Continuous mode

- Single loop mode

#### **Continuous Mode**

In this mode, the AS5410 is always active. The chip continuously updates the output registers. The completion of a new measurement is signalled with pin READY.

#### Single Loop Mode

The AS5410 features an automatic power down mode. After completion of a measurement, the chip automatically suspends to standby. The SPI interface remains active. The control of this mode is possible over register 000Eh (see Register Description). A high on the Ready output indicates that a measurement is completed. The AS5410 suspends to stand-by state after the Ready output has been set.

## Serial Interface (SPI)

The SPI interface provides data transfer between AS5410 and the external microcontroller.

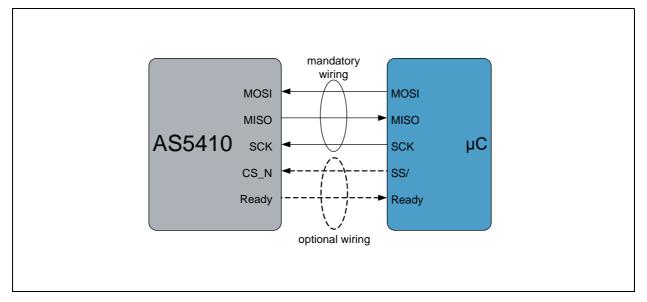

The minimum number of connections between microcontroller and AS5410 is three:

- 1. MOSI: Master Out Slave In; data transfer from microcontroller to AS5410 (Write)

- 2. MISO: Master In Slave Out; data transfer from AS5410 to microcontroller (Read)

- 3. SCK: Serial clock; Data is written and read with the rising edge of SCK

Optionally, two further connections may be used:

CS\_N: Chip select; this connection is mandatory when multiple AS5410 devices are connected in parallel. In electrically "noisy" environment it is recommended to use the CS\_N connection in order to maintain safe data transfer.

For a single unit, this connection is optional as the data transmission is synchronized automatically by the number of SCK cycles. In this case it is recommended to verify the synchronization by CRC, Data readback or repeated reading and cross-checking of subsequent measurements.

2. Ready: this output indicates when data is ready, it is cleared by reading data from address 0100h or 0122h.

# amu

#### Figure 14: Hardware Connection Between AS5410 and Microcontroller

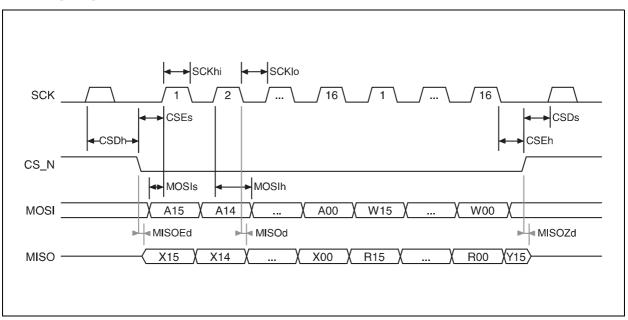

#### Figure 15: SPI Timing Diagram

The data bits sent to the chip via MOSI and the data bits received from the chip via MISO are defined as follows (see also Figure 15):

| A15 A00      | : 16-bit register address                                      |

|--------------|----------------------------------------------------------------|

| W15 W00      | : 16-bit write data (in write mode)                            |

| X15 X00, Y15 | : 16-bit read data or previous command<br>(depending on mode)  |

| R15 R0       | : 16-bit read data in read mode or previous data in write mode |

# amu

Figure 16: SPI Timing

| Symbol              | Parameter                             | Min | Тур | Max | Unit | Note |

|---------------------|---------------------------------------|-----|-----|-----|------|------|

| f <sub>sck</sub>    | SCK frequency                         |     |     | 1   | MHz  |      |

| t <sub>SCKhi</sub>  | SCK pulse width HI                    | 15  |     |     | ns   |      |

| t <sub>SCKlo</sub>  | SCK pulse width LO                    | 15  |     |     | ns   |      |

| t <sub>CSEs</sub>   | CS_N enable setup time before SCK     | 10  |     |     | ns   |      |

| t <sub>CSEh</sub>   | CS_N enable hold time after SCK       | 10  |     |     | ns   |      |

| t <sub>CSDs</sub>   | CS_N disable setup time before<br>SCK | 10  |     |     | ns   |      |

| t <sub>CSDh</sub>   | CS_N disable hold time after SCK      | 10  |     |     | ns   |      |

| t <sub>MOSIs</sub>  | MOSI setup time before SCK            | 10  |     |     | ns   |      |

| t <sub>MOSIh</sub>  | MOSI hold time after SCK              | 10  |     |     | ns   |      |

| t <sub>MISOd</sub>  | MISO delay after SCK                  |     |     | 10  | ns   |      |

| t <sub>MISOEd</sub> | MISO enable delay after CS_N          |     |     | 10  | ns   |      |

| t <sub>MISOZd</sub> | MISO high Z delay after CS_N          |     |     | 10  | ns   |      |

| t <sub>Or</sub>     | Output edge rise time                 |     |     | 3   | ns   |      |

| t <sub>Of</sub>     | Output edge fall time                 |     |     | 3   | ns   |      |

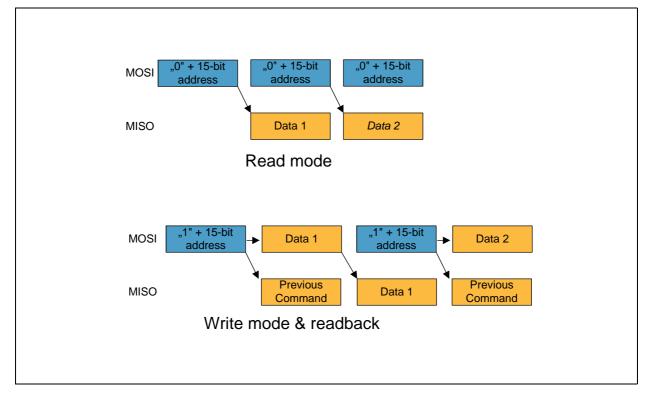

# Data Transfer Between AS5410 and Microcontroller

Data is transferred to the AS5410 via the MOSI pin (Master Out – Slave In) with the rising edge of SCK. Data is read from the AS5410 from the MISO pin (Master In – Slave Out) with the rising edge of SCK.

The data format consists of data streams with 32 bit in length. The first 16 bits define a 16-bit address and the subsequent 16 bits contain read or write data.

The MSB of the address word A<15> defines the direction of data transfer:

A<15> = 0 READ; data transfer from AS5410 to microcontroller; read measurement data

A<15> = 1 WRITE; data transfer from microcontroller to AS5410; write configuration data

#### Figure 17: Data Transfer Between AS5410 and Microcontroller

### Read Mode

For reading a register, the 16-bit Read address (with A<15>=0) is sent to the MOSI pin. After 16 SCK cycles, data of the specified address is read from the MISO pin (see Figure 17). At the same time, the new address may be clocked into the MOSI pin.

# amu

#### **Continuous Measurement**

It is possible to continuously read data from the AS5410 even if a new measurement is not yet finished. In this case, the last measurement data will be read. As soon as a new measurement is completed, it will be available at the SPI interface.

#### Write Mode and Readback

For additional safety and detection of communication errors, the actual contents of a register may be read at the same time as new data is written to this register.

In case of a Write command, the 16-bit Write address (with A<15>=1) is sent to the MOSI pin. After 16 SCK cycles, data following the address bits is written to the specified address via MOSI in (see Figure 17) At the same time, the present data of that register may be read from the MISO pin. Following the 16-bit of data (Data 1 in Figure 17), a new address may be written to the AS5410. While the new address is written, the address from the previous command is available at the MISO output.

#### Checksum

To avoid reading errors, the IC calculates a Checksum at every read cycle from the register content. The Checksum value is built by an XOR operation of the previous Checksum value and the read register content. The CRC is calculated every time a register is read.

By choosing how often the Checksum is read and rechecked by the master it is possible to adjust the communication speed and safety level.

The Checksum value is stored in register 0108h (see Register Description).

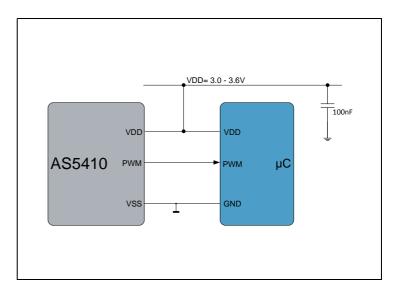

### **PWM Data Transmission**

In addition to the SPI interface, the AS5410 offers a PWM output that provides data transmission of the linearized output data over a single wire. The base frequency of the PWM is the system clock frequency, so one PWM digit always corresponds to approx. 125ns. The PWM resolution is set by 3 bits (PWMPreScale) which shift the 16 bit wide angle value by 0 to 7 digits.

The duty cycle of the PWM signal lies between 0% to 100%. In case of an error, the duty cycle is 0%.

If register 0122h value increases the duty cycle decreases. If register 0122h value decreases the duty cycle increases.

| Register                  | Access | Bit    | Function           | Default | Note                                                               |

|---------------------------|--------|--------|--------------------|---------|--------------------------------------------------------------------|

|                           |        | D15-10 | PWMLimitHi <5:0>   | 0       | PWM Limit High,<br>Limits the PWM duty cycle to a<br>maximum value |

| 000Dh:<br>PWM<br>settings | R/W    | D9-4   | PWMLimitLo <5:0>   | 0       | PWM Limit Low,<br>Limits the PWM duty cycle to a<br>minimum value  |

| settings                  |        | D3     | PWMEn              | 0       | PWM Enable,<br>Enables the PWM output                              |

|                           |        | D2-0   | PWMPreScale < 2:0> | 0       | PWM PreScale,<br>Sets PWM frequency and resolution                 |

Figure 19: Single Pin Data Transmission Connection Diagram

#### Figure 18: Register 000Dh

# amu

#### Figure 20: PWM Duty Cycle Information

| PWM Duty Cycle<br>[%] | Register 122h<br>(Linear Angle) [LSB] |

|-----------------------|---------------------------------------|

| 0                     | 32767                                 |

| 50                    | 0                                     |

| 100                   | -32768                                |

Between 0% to 100% the duty cycle is linear to the Linear Angle.

**PWM Enable:** Must be set high to enable the PWM mode.

**PWMPreScale0 to PWMPreScale3:** The PWM resolution is set by those 3 Bits.

#### Figure 21: PWM Resolution

| PWMPreScale0 to<br>PWMPreScale3 | Resolution<br>(bit) | PWM (kHz) |

|---------------------------------|---------------------|-----------|

| 000                             | 16                  | 0.122     |

| 001                             | 15                  | 0.244     |

| 010                             | 14                  | 0.488     |

| 011                             | 13                  | 0.977     |

| 100                             | 12                  | 1.953     |

| 101                             | 11                  | 3.906     |

| 110                             | 10                  | 7.813     |

| 111                             | 9                   | 15.63     |

#### PWMLimitHi5 to PWMLimitHi0: Limits the PWM duty cycle.

Figure 22: PWM Upper Clamping Limits

| Duty Cycle  | PWMLimitHi0 to PWMLimitHi5 |

|-------------|----------------------------|

| Minimum 50% | 000000                     |

| Minimum 0%  | 111111                     |

Between 0% to 50% the duty cycle limit is linear to the binary values selected by PWMLimitHi5 to PWMLimitHi0.

The limits are clamping limits (by selecting limits the resolution decreases).

PWMLimitLo5 to PWMLimitLo0: Limits the PWM duty cycle.

Figure 23: PWM Lower Clamping Limits

| Duty Cycle   | PWMLimitLo0 to PWMLimitLo5 |

|--------------|----------------------------|

| Maximum 50%  | 111111                     |

| Maximum 100% | 000000                     |

Between 50% to 100% the duty cycle limit is linear to the binary values selected by PWMLimitLo5 to PWMLimitLo0. The limits are clamping limits (by selecting limits the resolution decreases).

Figure 24: PWM Setting Example

| Clamping Range | 0% – 100% PWM<br>Duty Cycle | 10% – 90% PWM<br>Duty Cycle | 50% – 50% PWM<br>Duty Cycle |

|----------------|-----------------------------|-----------------------------|-----------------------------|

| PWMLimitHi5    | 1                           | 1                           | 0                           |

| PWMLimitHi4    | 1                           | 1                           | 0                           |

| PWMLimitHi3    | 1                           | 0                           | 0                           |

| PWMLimitHi2    | 1                           | 0                           | 0                           |

| PWMLimitHi1    | 1                           | 1                           | 0                           |

| PWMLimitHi0    | 1                           | 0                           | 0                           |

| PWMLimitLo5    | 0                           | 0                           | 1                           |

| PWMLimitLo4    | 0                           | 0                           | 1                           |

| PWMLimitLo3    | 0                           | 1                           | 1                           |

| PWMLimitLo2    | 0                           | 1                           | 1                           |

| PWMLimitLo1    | 0                           | 0                           | 1                           |

| PWMLimitLo0    | 0                           | 1                           | 1                           |

## **Register Description**

The following registers can be addressed by the user via the SPI interface. Each register is 16-bit wide.

Registers not listed in the table below must not be modified from their factory programmed setting.

**Note(s):** "r" are reserved bits, they must not be modified (unless otherwise noted)

## **Register 000Bh**

This register controls the sequencer

Figure 25: Register 000Bh

| Register                       | Access | Bit          | Function          | Default | Note                                                                                                                                                                                                                                                                               |

|--------------------------------|--------|--------------|-------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                |        | D15<br>(MSB) | r                 | 0       |                                                                                                                                                                                                                                                                                    |

|                                |        | D14          | r                 | 0       |                                                                                                                                                                                                                                                                                    |

|                                |        | D13          | r                 | 0       |                                                                                                                                                                                                                                                                                    |

|                                |        | D12          | r                 | 0       |                                                                                                                                                                                                                                                                                    |

| 000Bh:<br>Sequencer<br>control |        | D11          | MgRangExt         | 0       | "Magnet Range Extension"<br>Enable the algorithm for an extended<br>position range.<br>1 = Magnet Range Extension enabled<br>0 = Magnet Range Extension disabled                                                                                                                   |

|                                | R/W    | D10          | CoordSel          | 0       | "Coordinate System Selection"<br>1 = The sign of the Lin Ang<br>(Register 0122h) gets changed if MagDir<br>(Register 000Bh) = 1<br>0 = Lin Ang (Register 0122h) gets not<br>changed                                                                                                |

|                                |        | D9           | r                 | 0       |                                                                                                                                                                                                                                                                                    |

|                                |        | D8           | r                 | 0       |                                                                                                                                                                                                                                                                                    |

|                                |        | D7           | Table<br>Select 0 | 0       | These bits allow the selection of 4<br>different operating modes, stored in 4                                                                                                                                                                                                      |

|                                |        | D6           | Table<br>Select 1 | 0       | individual sequencer tables                                                                                                                                                                                                                                                        |

|                                |        | D5           | MagDir            | 0       | This bit allows to switch the magnet<br>direction<br>MagDir = 0: North pole must point in +x<br>direction (pin 7 to pin1) Default/powerup<br>mode.<br>MagDir = 1: North pole must point in -x<br>direction (pin1 to pin7). Preferred<br>orientation to permit use of CoordSel bit. |

# amu

| Register                       | Access | Bit         | Function | Default | Note                                                                                                                                                                                                                                            |

|--------------------------------|--------|-------------|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                |        | D4          | DiffMd   | 0       | Differential mode:<br>0 = Absolute measurement of Hall cells,<br>1 = Differential measurement of Hall cells                                                                                                                                     |

|                                |        | D3          | r        | 0       |                                                                                                                                                                                                                                                 |

| 0000                           |        | D2          | r        | 0       |                                                                                                                                                                                                                                                 |

| 000Bh:<br>Sequencer<br>control | R/W    | D1          | RdyHZ    | 0       | READY Tri-State:<br>0: The READY pin is always active. It must<br>NOT be connected in parallel<br>1: The READY output may be connected in<br>parallel. It is normally in high Z and only<br>active (high) if the IC is selected. <sup>(1)</sup> |

|                                |        | D0<br>(LSB) | r        | 0       |                                                                                                                                                                                                                                                 |

#### Note(s) and/or Footnote(s):

1. A 10k pull down resistor is mandatory at the common READY signal line if RdyHz = 1.

Figure 26: Possible Table Selection

|                           | Table 0                                                                                                                             | Table 1                                                                                                                             | Table 2                                                                                                        | Table 3                                                                                                        |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|

|                           | Differential Mode                                                                                                                   |                                                                                                                                     | Absolute Pixel1                                                                                                |                                                                                                                |  |

|                           | 1kHz Sample Rate                                                                                                                    | 0.5kHz Sample Rate                                                                                                                  | 1kHz Sample Rate                                                                                               | 0.5kHz Sample Rate                                                                                             |  |

| CORDIC<br>Input<br>Values | Pixelcell0, Bz0 = 0x112h<br>-Pixelcell1, Bz1 = 0x111h<br>Pixelcell0, Bx0 = 0x114h<br>-Pixelcell1, Bx1 = 0x113h                      | Pixelcell0, Bz0 = 0x112h<br>-Pixelcell1, Bz1 = 0x111h<br>Pixelcell0, Bx0 = 0x114h<br>-Pixelcell1, Bx1 = 0x113h                      | Pixelcell1, Bz1 = 0x111h<br>Pixelcell1, Bx1 = 0x113h                                                           | Pixelcell1, Bz1 = 0x111h<br>Pixelcell1, Bx1 = 0x113h                                                           |  |

| Register B<br>Settings    | Table Select 1<br>Table Select 0 = 00<br>(mandatory)<br>DiffMd = 1 (mandatory)<br>MgRangExt = 0 or 1<br>depending on<br>application | Table Select 1<br>Table Select 0 = 01<br>(mandatory)<br>DiffMd = 1 (mandatory)<br>MgRangExt = 0 or 1<br>depending on<br>application | Table Select 1<br>Table Select 0 = 10<br>(mandatory)<br>DiffMd = 0 (mandatory)<br>MgRangExt = 0<br>(mandatory) | Table Select 1<br>Table Select 0 = 11<br>(mandatory)<br>DiffMd = 0 (mandatory)<br>MgRangExt = 0<br>(mandatory) |  |

## Register 000Dh

Figure 27: Register 000Dh

| Register | Access                                  | Bit       | Function                                                                               | Default                      | Note                                                                                                                   |

|----------|-----------------------------------------|-----------|----------------------------------------------------------------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------|

|          | h: R/W D7 PWMLimitLo 3 1 PWM Limit Low, | D15 (MSB) | PWMLimitHi 5                                                                           | 1                            | PWM Limit High,<br>Limits the PWM duty cycle to a<br>maximum value<br>PWM Limit Low,<br>Limits the PWM duty cycle to a |

|          |                                         |           |                                                                                        |                              |                                                                                                                        |

|          |                                         |           |                                                                                        |                              |                                                                                                                        |

|          |                                         | D12       | PWMLimitHi 2     0     maximum value       PWMLimitHi 1     1       PWMLimitHi 0     1 |                              |                                                                                                                        |

|          |                                         | D11       | PWMLimitHi 1                                                                           | 1                            |                                                                                                                        |

|          |                                         | D10       | PWMLimitHi 0                                                                           | 1                            | -                                                                                                                      |

|          |                                         | D9        | PWMLimitLo 5                                                                           | 0                            |                                                                                                                        |

|          | 000Dh: R/W                              | D8        | PWMLimitLo 4                                                                           | 0                            |                                                                                                                        |

| 000Dh:   |                                         | D7        | PWMLimitLo 3                                                                           | 1                            |                                                                                                                        |

|          |                                         | D6        | PWMLimitLo 2                                                                           | Limits the PWM duty cycle to |                                                                                                                        |

|          |                                         | D5        | PWMLimitLo 1                                                                           | 0                            |                                                                                                                        |

|          |                                         | D4        | PWMLimitLo 0                                                                           | 1                            |                                                                                                                        |

|          |                                         | D3        | PWMEn                                                                                  | 0                            |                                                                                                                        |

|          |                                         | D2        | PWM PreScale 2                                                                         | 0                            |                                                                                                                        |

|          |                                         | D1        | PWM PreScale 1                                                                         | 1                            |                                                                                                                        |

|          |                                         | D0 (LSB)  | PWM PreScale 0                                                                         | 1                            |                                                                                                                        |

## Register 000Eh

This register holds the sequencer control bits.

Figure 28: Register 000Eh

| Register                       | Access | Bit               | Function | Default | Note                                                                                                                         |

|--------------------------------|--------|-------------------|----------|---------|------------------------------------------------------------------------------------------------------------------------------|

|                                |        | D15 (MSB)<br>– D2 | r        | 0       |                                                                                                                              |

| 000Eh:<br>Sequencer<br>control | R/W    | D1                | Seq      | 1       | <ul> <li>1 = Sequencer enabled</li> <li>(to be set to activate the state machine)</li> <li>0 = Sequencer disabled</li> </ul> |

|                                |        | D0 (LSB)          | SL       | 0       | 1 = Single loop mode enabled<br>0 = Single loop mode disabled                                                                |

## **Register 000Fh**

This register holds the threshold and hysteresis of the CORDIC magnitude value (see Register 0120h), at which the "Magnet Lost" flag in register 0107h is set/cleared.

| Figure 29:     |  |

|----------------|--|

| Register 000Fh |  |

| Register | Access                                                                                                                                                                                                 | Bit                                                                                                                                     | Function                     | Default                                                                                                                                                                                                                                         | Note                                                              |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

|          | AccessBitFunctionDefaultNoteD15 (MSB)r0D14r0D13r0ReservedD12r0D11r0H2Hyst0H1Hyst0H0Hyst1V7MgnLostLmt0V5MgnLostLmt0V4MgnLostLmt0V2MgnLostLmt0V1MgnLostLmt0V2MgnLostLmt0V1MgnLostLmt1V0 (LSB)MgnLostLmt1 | D15 (MSB)                                                                                                                               | r                            | 0                                                                                                                                                                                                                                               | Reserved Hysteresis for "magnet lost" Magnet lost threshold value |

|          |                                                                                                                                                                                                        |                                                                                                                                         |                              |                                                                                                                                                                                                                                                 |                                                                   |

|          |                                                                                                                                                                                                        | D15 (MSB)r0D14r0D14r0D13r0D12r0D11r0H2Hyst0H1Hyst0H0Hyst1V7MgnLostLmt0V5MgnLostLmt0V4MgnLostLmt0V2MgnLostLmt0V1MgnLostLmt0V1MgnLostLmt1 | Reserved                     |                                                                                                                                                                                                                                                 |                                                                   |

|          |                                                                                                                                                                                                        | D12                                                                                                                                     | r                            | 0       0         0       Reserved         0       0         0       0         0       Hysteresis for "magnet lost"         1       0         0       0         0       Magnet lost threshold value         0       Magnet lost threshold value |                                                                   |

|          |                                                                                                                                                                                                        | D11                                                                                                                                     | r                            | 0                                                                                                                                                                                                                                               |                                                                   |

|          |                                                                                                                                                                                                        | H2                                                                                                                                      | Hyst                         | 0                                                                                                                                                                                                                                               |                                                                   |

|          |                                                                                                                                                                                                        |                                                                                                                                         | Hysteresis for "magnet lost" |                                                                                                                                                                                                                                                 |                                                                   |

| 000Fh:   | D/M/                                                                                                                                                                                                   | H0                                                                                                                                      | Hyst                         | 1                                                                                                                                                                                                                                               |                                                                   |

| 000FN.   | Π/ Ψ                                                                                                                                                                                                   | V7                                                                                                                                      | MgnLostLmt                   | 0                                                                                                                                                                                                                                               |                                                                   |

|          |                                                                                                                                                                                                        |                                                                                                                                         |                              |                                                                                                                                                                                                                                                 |                                                                   |

|          |                                                                                                                                                                                                        | V5                                                                                                                                      | MgnLostLmt                   | 0                                                                                                                                                                                                                                               |                                                                   |

|          |                                                                                                                                                                                                        | V4 MgnLostLmt 0 Magnet lost threshold                                                                                                   | Magnet lost threshold value  |                                                                                                                                                                                                                                                 |                                                                   |

|          |                                                                                                                                                                                                        | V3                                                                                                                                      | MgnLostLmt                   | 0                                                                                                                                                                                                                                               | compared to register 0121h                                        |

|          |                                                                                                                                                                                                        | V2                                                                                                                                      | MgnLostLmt                   | 0                                                                                                                                                                                                                                               |                                                                   |

|          |                                                                                                                                                                                                        | V1                                                                                                                                      | MgnLostLmt                   | 1                                                                                                                                                                                                                                               |                                                                   |

|          |                                                                                                                                                                                                        | V0 (LSB)                                                                                                                                | MgnLostLmt                   | 1                                                                                                                                                                                                                                               |                                                                   |

#### Note(s) and/or Footnote(s):

1. V7 to V0: The minimum allowed Magnitude of CORDIC can be selected. The binary number, represented by V7 to V0 must be multiplied with 64 to calculate the minimum allowed Magnitude of CORDIC.

#### Figure 30: Example: Select V0 and V1.

|   | Binary |    |    |    |    |    |    | Decimal |         |

|---|--------|----|----|----|----|----|----|---------|---------|

| ١ | V7     | V6 | V5 | V4 | V3 | V2 | V1 | V0      | Decimar |

|   | 0      | 0  | 0  | 0  | 0  | 0  | 1  | 1       | 3       |

The corresponding dual number to 00000011 is 3 this number multiplied with 64 is the minimum allowed magnitude of CORDIC.

64 \* 3 = 192 = Threshold limit

If the magnitude of CORDIC turns under 192 the MagLost bit in register 0107h will turn form 0 to 1.

**H2...H0:** The hysteresis around the minimum allowed magnitude of CORDIC can be selected.

The hysteresis *Hystd* is calculated by the formula

- *Hyst* : Hysteresis value in Register 000Fh

- *Hystd* : Decimal hysteresis value around the minimum allowed magnitude of CORDIC

- **MgnLostLmt** : The threshold limit as calculated in the example above.

(EQ1) Hystd = MgnLostLmt

$$\times \frac{1}{2^{Hyst}}$$

Figure 31: Example: Select H0

|    | Binary | Decimal |         |

|----|--------|---------|---------|

| H2 | H1     | H0      | Decimar |

| 0  | 0      | 1       | 1       |

(EQ2) Hystd = MgnLostLmt

$$\times \frac{1}{2^{Hyst}} = 192 \times \frac{1}{2^1} = 96$$

Now the MagLost bit in register 0107h will turn form 0 to 1 at a magnitude of CORDIC value lower than 192. After the MagLost bit is 0 it turns back to 1 at a value higher than 288, because 192 + 96 = 288.

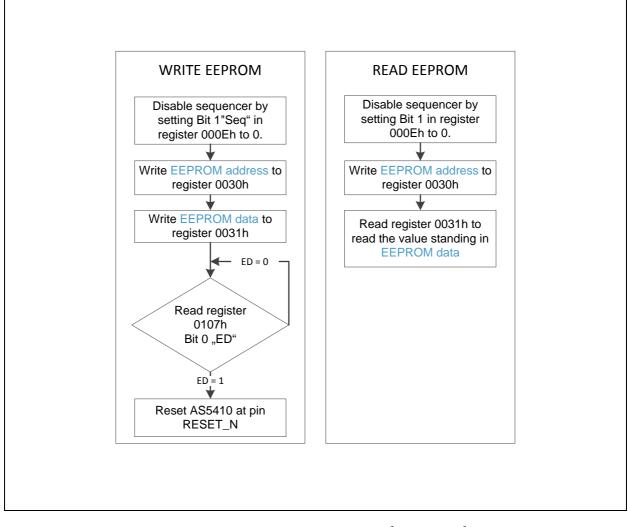

# Register 0030h

E<sup>2</sup>PROM address

Figure 32: Register 0030h

| Register                      | Access | Bit       | Function | Note                                                                                                         |

|-------------------------------|--------|-----------|----------|--------------------------------------------------------------------------------------------------------------|

|                               |        | D15 (MSB) | A15      |                                                                                                              |

|                               |        | D14       | A14      |                                                                                                              |

|                               |        | D13       | A13      |                                                                                                              |

|                               |        | D12       | A12      |                                                                                                              |

|                               |        | D11       | A11      |                                                                                                              |

|                               |        | D10       | A10      |                                                                                                              |

|                               |        | D9        | A9       | To read/write E <sup>2</sup> PROM contents,<br>the selected E <sup>2</sup> PROM address must be specified in |

| 0030h:<br>E <sup>2</sup> PROM | R/W    | D8        | A8       | this register.<br>The corresponding data is available in register 0031h.                                     |

| address                       | 10 00  | D7        | A7       | For write operations, status bit ED in register 0107h which indicates the completion of a write operation    |

|                               |        | D6        | A6       | must be verified before starting a new write cycle.<br>Writing 16 bits of data requires ~10ms                |

|                               |        | D5        | A5       |                                                                                                              |

|                               |        | D4        | A4       |                                                                                                              |

|                               |        | D3        | A3       |                                                                                                              |

|                               |        | D2        | A2       |                                                                                                              |

|                               |        | D1        | A1       |                                                                                                              |

|                               |        | D0 (LSB)  | A0       |                                                                                                              |

#### Note(s) and/or Footnote(s):

1. 1LSB=4mT.

# Register 0031h

E<sup>2</sup>PROM data

Figure 33: Register 0031h

| Register                      | Access | Bit       | Function | Note                                                        |

|-------------------------------|--------|-----------|----------|-------------------------------------------------------------|

|                               |        | D15 (MSB) | D15      |                                                             |

|                               |        | D14       | D14      |                                                             |

|                               |        | D13       | D13      |                                                             |

|                               |        | D12       | D12      |                                                             |

|                               |        | D11       | D11      |                                                             |

|                               |        | D10       | D10      |                                                             |

|                               |        | D9        | D9       |                                                             |

| 0031h:<br>E <sup>2</sup> PROM | R/W    | D8        | D8       | This register holds the E <sup>2</sup> PROM contents of the |

| data                          |        | D7        | D7       | address selected in register 0030h                          |

|                               |        | D6        | D6       |                                                             |

|                               |        | D5        | D5       |                                                             |

|                               |        | D4        | D4       |                                                             |

|                               |        | D3        | D3       |                                                             |

|                               |        | D2        | D2       |                                                             |

|                               |        | D1        | D1       |                                                             |

|                               |        | D0 (LSB)  | D0       |                                                             |

# Register 0032h

### Figure 34: Register 0032h

| Register                       | Access | Bit       | Function                                                        | Note                                                     |

|--------------------------------|--------|-----------|-----------------------------------------------------------------|----------------------------------------------------------|

|                                |        | D15 (MSB) | A15                                                             |                                                          |

|                                |        | D14       | A14                                                             |                                                          |

|                                |        | D13       | A13                                                             |                                                          |

|                                |        | D12       | A12                                                             |                                                          |

|                                |        | D11       | A11                                                             |                                                          |

|                                | D10    | A10       |                                                                 |                                                          |

|                                |        | D9        | A9                                                              |                                                          |

| 0032h:<br>Page WRITE           | D /\\/ | D8        | A8                                                              | To page write E <sup>2</sup> PROM contents, the selected |

| E <sup>2</sup> PROM<br>address | D7     | A7        | E <sup>2</sup> PROM address must be specified in this register. |                                                          |

|                                |        | D6        | A6                                                              |                                                          |

|                                |        | D5        | A5                                                              |                                                          |

|                                |        | D4        | A4                                                              |                                                          |

|                                |        | D3        | A3                                                              |                                                          |

|                                |        | D2        | A2                                                              |                                                          |

|                                |        | D1        | A1                                                              |                                                          |

|                                |        | D0 (LSB)  | A0                                                              |                                                          |

## Register 0033h

Figure 35: Register 0033h

| Register                 | Access                                     | Bit                   | Function                            | Note                                                                     |

|--------------------------|--------------------------------------------|-----------------------|-------------------------------------|--------------------------------------------------------------------------|

|                          |                                            | D15 (MSB)             | D15                                 |                                                                          |

|                          |                                            | D14                   | D14                                 |                                                                          |

|                          |                                            | D13                   | D13                                 |                                                                          |

|                          |                                            | D12                   | D12                                 |                                                                          |

|                          |                                            | D11                   | D11                                 |                                                                          |

|                          |                                            | D10                   | D10                                 |                                                                          |

|                          |                                            | D9                    | D9                                  |                                                                          |

| 0033h:                   | D/\\/                                      | D8                    | D8                                  | To page write E <sup>2</sup> PROM contents, the E <sup>2</sup> PROM data |

| E <sup>2</sup> PROM data | Page WRITE R/W<br>E <sup>2</sup> PROM data | D7 D7 must k<br>D6 D6 | must be specified in this register. |                                                                          |

|                          |                                            |                       |                                     |                                                                          |

|                          |                                            | D5                    | D5                                  |                                                                          |

|                          |                                            | D4                    | D4                                  |                                                                          |

|                          |                                            | D3                    | D3                                  |                                                                          |

|                          |                                            | D2                    | D2                                  |                                                                          |

|                          |                                            | D1                    | D1                                  |                                                                          |

|                          |                                            | D0 (LSB)              | D0                                  |                                                                          |

## Register 0107h

Status register; this register holds various status flags

Figure 36: Register 0107h

| Register             | Access | Bit       | Function                               | Note                                                                                                                                                                                                                                                  |

|----------------------|--------|-----------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      |        | D15 (MSB) | RDY                                    | Indicates completion of a new measurement;<br>same function as the "Ready" output pin.<br>0 = calculation is in progress or chip not ready<br>1 = measurement completed, new measurement<br>data is stored in register 0110h-0114h and<br>0120h-0122h |

|                      |        | D14       | MagLost                                | 1 = Magnetic field values are too low for position<br>measurement; the threshold level can be selected at<br>Register 000Fh Bit D7 to D0                                                                                                              |

|                      |        | D13       | CorrOvfl                               | Ambiguous angle correction overflow                                                                                                                                                                                                                   |

|                      |        | D12       | NormOvfl                               | Normalizing scale overflow                                                                                                                                                                                                                            |