# Si8935/36/37 Data Sheet

## Delta-Sigma Modulator for Voltage Measurement

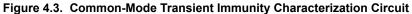

The Si8935/36/37 is a galvanically isolated delta-sigma modulator optimized for voltage sensing. Its 2.5 V input range is ideal for isolated voltage sensing applications. The Si8935/36/37 provides excellent linearity with low offset and gain drift to ensure that accuracy is maintained over the entire operating temperature range. Exceptionally high common-mode transient immunity means that the Si8935/36/37 delivers accurate measurements even in the presence of high-power switching as is found in motor drive systems and inverters.

The output of the Si8935/36/37 comes from a second-order, delta-sigma modulator. The modulator can be clocked either from an onboard oscillator (Si8936/37) or from an external clock (Si8935). The output is typically digitally filtered by a MCU or FPGA in the system.

The Si8935/36/37 isolated delta-sigma modulator utilizes Skyworks' proprietary isolation technology. It supports up to 5.0 kVrms withstand voltage per UL1577. This technology enables higher performance, reduced variation with temperature and age, tighter part-to-part matching, and longer lifetimes compared to other isolation technologies.

#### Applications:

- · Industrial, HEV and renewable energy inverters

- AC, Brushless, and DC motor controls and drives

- · Variable speed motor control in consumer white goods

- · Isolated switch mode and UPS power supplies

- · General industrial data acquisition and sensor interface

- · Automotive onboard chargers, battery management systems, and charging stations

#### Safety Approvals (Pending):

- UL 1577 recognized

- Up to 5000 Vrms for 1 minute

- CSA approval

- IEC 60950-1, 62368-1 (reinforced insulation)

- · VDE certification conformity

- · VDE0884 Part 11 (basic/reinforced insulation)

- · CQC certification approval

- GB4943.1-2011

#### KEY FEATURES

- 0 to 2.5 V nominal input voltage

- Modulator clock options

External clock up to 25 MHz (Si8935)

- 10 MHz internal clock (Si8936)

- 20 MHz internal clock (Si8937)

- Typical input offset: ±0.4 mV

- Typical gain error: ±0.05%

- Excellent drift specifications

- $\pm 0.5 \,\mu\text{V/°C}$  typical offset drift

- 9 ppm/°C typical gain drift

- Typical nonlinearity: 0.003%

- Typical SNR: 86 dB

- High common-mode transient immunity: 75 kV/µs

- Auomotive-grade OPNs

AIAG-compliant PPAP documentation support

- IMDS and CAMDS listing support

- · Compact packages

- · 8-pin wide body stretched SOIC

1

- 8-pin narrow body SOIC

- –40 to 125 °C

## 1. Ordering Guide

| Ordering          | Automotive OPN <sup>4</sup> | Ordering Options     |               |                        |  |

|-------------------|-----------------------------|----------------------|---------------|------------------------|--|

| Part Number (OPN) | Automotive OPN <sup>+</sup> | Isolation Rating Clo |               | Package Type           |  |

| Si8935D-IS4       | Si8935D-AS4                 | 5.0 kVrms            | Input         | WB Stretched<br>SOIC-8 |  |

| Si8935B-IS        | Si8935B-AS                  | 2.5 kVrms            | Input         | NB SOIC-8              |  |

| Si8936D-IS4       | Si8936D-AS4                 | 5.0 kVrms            | 10 MHz Output | WB Stretched<br>SOIC-8 |  |

| Si8936B-IS        | Si8936B-AS                  | 2.5 kVrms            | 10 MHz Output | NB SOIC-8              |  |

| Si8937D-IS4       | Si8937D-AS4                 | 5.0 kVrms            | 20 MHz Output | WB Stretched<br>SOIC-8 |  |

| Si8937B-IS        | Si8937B-AS                  | 2.5 kVrms            | 20 MHz Output | NB SOIC-8              |  |

## Table 1.1. Si8935-36-37 Ordering Guide<sup>1, 2, 3</sup>

#### Note:

1. All packages are RoHS-compliant.

2. "Si" and "SI" are used interchangeably.

3. AEC-Q100 pending qualification.

4. Automotive-Grade devices ("-A" suffix) are identical in construction materials, topside marking, and electrical parameters to their Industrial-Grade ("-I" suffix) version counterparts. Automotive-Grade products are produced utilizing full automotive process flows and additional statistical process controls throughout the manufacturing flow. The Automotive-Grade part number is included on shipping labels.

## **Table of Contents**

| 1. | Ordering Guide                                      |

|----|-----------------------------------------------------|

| 2. | System Overview                                     |

|    | 2.1 Fail-Safe and Low-Power Modes                   |

|    | 2.2 Modulator                                       |

| 3. | Voltage Sense Application                           |

| 4. | Electrical Specifications                           |

|    | 4.1 Regulatory Information                          |

|    | 4.2 Typical Operating Characteristics               |

| 5. | Pin Descriptions                                    |

| 6. | Packaging                                           |

|    | 6.1 Package Outline: 8-Pin Wide Body Stretched SOIC |

|    | 6.2 Package Outline: 8-Pin Narrow Body SOIC         |

|    | 6.3 Land Pattern: 8-Pin Wide Body Stretched SOIC    |

|    | 6.4 Land Pattern: 8-Pin Narrow Body SOIC            |

|    | 6.5 Top Marking: 8-Pin Wide Body Stretched SOIC     |

|    | 6.6 Top Marking: 8-Pin Narrow Body SOIC             |

| 7. | Revision History                                    |

## 2. System Overview

The input to the Si8935/36/37 is designed for 0 to 2.5 V nominal input.

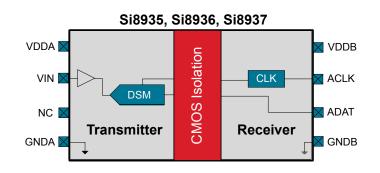

The analog input stage of the Si8935/36/37 is a single-ended amplifier feeding the input of a second-order, delta-sigma ( $\Delta\Sigma$ ) modulator that digitizes the input signal into a 1-bit output stream. The isolated data output ADAT pin of the converter provides a stream of digital ones and zeros that is synchronous to the ACLK pin. The Si8936/37 clock is generated internally while the Si8935 clock is provided externally. The time average of this serial bit-stream output is proportional to the analog input voltage.

Figure 2.1. Si8935/36/37 Functional Block Diagram

#### 2.1 Fail-Safe and Low-Power Modes

The Si8935/36/37 implements a fail-safe output when the high-side supply voltage VDDA goes away. The fail-safe output is steady state logic 0 on ADAT for the externally clocked Si8935. The fail-safe output is a steady state logic 1 on ADAT for the internally clocked Si8936/37. The clock output ACLK of the Si8946/47 will stop after 256 cycles with a steady state logic 1. When the supply comes back, the clock will be turned back on and normal DSM data stream will be output in approximately 200 µs. To differentiate from the fail-safe output, a maximum nominal input signal will generate a single one every 128 bits at ADAT.

In addition to the fail-safe output, when a loss of VDDA supply occurs the part will automatically move into a lower power mode that reduces IDDB current to approximately 1 mA. Similarly, a loss of VDDB supply will reduce IDDA current to approximately 1 mA. When the supply voltage is returned, normal operation begins in approximately 250 µs.

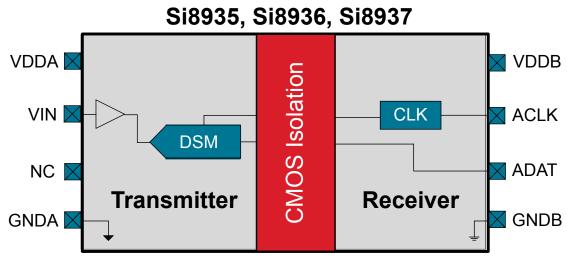

#### 2.2 Modulator

The output of the Si8935/36/37 comes from a second-order, delta-sigma modulator like that shown in the figure below. The modulator provides 1-bit datastream whose average represents the input analog voltage. 0 V across the inputs is represented at the output by a pulse train that has 50% ones density. Specified linear full-scale at the input (e.g., +2.25 V) produces an output datastream that has 92.87% ones density.

Figure 2.2. Typical 2nd Order Delta-Sigma Modulator Block Diagram

| Table 2.1. Modulator Output | Table | 2.1. | Modulator | Output |

|-----------------------------|-------|------|-----------|--------|

|-----------------------------|-------|------|-----------|--------|

| Single-Ended Input | Bitstream % Ones |

|--------------------|------------------|

| 2.25 V             | 92.87%           |

| 1.125 V            | 71.44%           |

| 0 V                | 50%              |

## 3. Voltage Sense Application

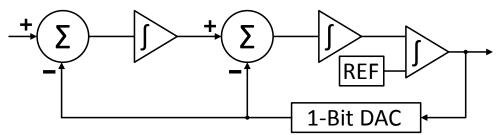

A typical isolated voltage sensing application circuit is shown below. In this example, a high voltage is divided down to produce a voltage (VIN) within the optimum input signal range of the Si8935/36/37. Numerous alternative inputs configurations are possible with the flexibility of a high impedance input isolator. The Si8935/36/37 senses the single-ended input voltage where it is oversampled and converted into a 1-bit bitstream, then transmitted across the isolation barrier to be processed by the system controller/FPGA. If the voltage sensed is > 2.5 V, a simple voltage divider consisting of R1 and R2 can be used to scale down any voltage to fit the input range of the Si8935/36/37. R2 < 10 k $\Omega$  is recommended for best performance.

Figure 3.1. Voltage Sense Application

The Si8935/36/37 has intrinsic low-pass filtering at approximately 800 kHz. For applications where input filtering is required, a passive RC low-pass filter can be placed at the input pin. Consider the source resistance of the signal measured (or the parallel combination of R1 and R2 if using a voltage divider) as it should be included in the filter calculation. Capacitor C1 should be sized to make a band limiting filter at the desired frequency.

C4, the local bypass capacitor for the B-side of Si8935/36/37, should be placed closed to VDDB supply pin with its return close to GNDB. The output signal typically goes directly to a digital filter for additional processing. The digital filter may be implemented by a dedicated FPGA in the system or may be a peripheral in the main system controller. The Si8935 expects an external clock to provide the clock signal for the modulator. That external clock can be provided by the same device that implements the digital filtering or another device that syncs both the modulator and the digital filter. The Si8936/37 generates an internal clock to the digital filter.

## 4. Electrical Specifications

#### Table 4.1. Electrical Specifications

$T_A = -40$  to +125 °C, SINC3 filter with 256 oversampling ratio and 20 MHz clock; typical specs at 25 °C and VDDA = VDDB = 5V unless specified otherwise

| Parameter                                   | Symbol           | Test Condition                       | Min    | Тур   | Мах   | Units  |

|---------------------------------------------|------------------|--------------------------------------|--------|-------|-------|--------|

| Input Side Supply<br>Voltage                | VDDA             |                                      | 3.0    |       | 5.5   | V      |

| Input Supply Current                        | IDDA             | VDDA = 3.3 V                         | 5.6    | 7     | 8.7   | mA     |

| Output Side Supply<br>Voltage               | VDDB             |                                      | 3.0    |       | 5.5   | V      |

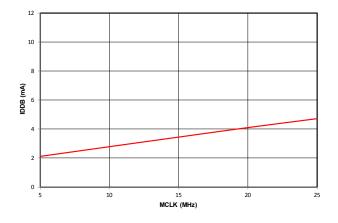

| Output Supply<br>Current (Si8935)           | IDDB             | VDDB = 3.3 V                         | 1      | 1.8   | 2.7   | mA     |

| Output Supply<br>Current (Si8936)           | IDDB             | VDDB = 3.3 V                         | 2.8    | 4.4   | 7.2   | mA     |

| Output Supply<br>Current (Si8937)           | IDDB             | VDDB = 3.3 V                         | 4.1    | 6.1   | 11    | mA     |

| Amplifier Input                             |                  | 1                                    |        |       | 1     |        |

| Specified Linear In-<br>put Range           | VIN              |                                      | 0.25   |       | 2.25  | V      |

| Maximum Input<br>Voltage Before<br>Clipping | VIN              |                                      |        | 2.5   |       | v      |

| Input Referred<br>Offset                    | VOS              | T <sub>A</sub> = 25 °C, VIN = 0.25 V | -3     | ±0.4  | 3     | mV     |

| Input Offset Drift                          | VOS <sub>T</sub> |                                      | -40    | ±0.5  | 25    | µV/°C  |

| Input Impedance                             | RIN              |                                      |        | 500   |       | ΜΩ     |

| Dynamic Characteri                          | stics            |                                      |        |       |       |        |

| Gain                                        |                  |                                      |        | 1     |       |        |

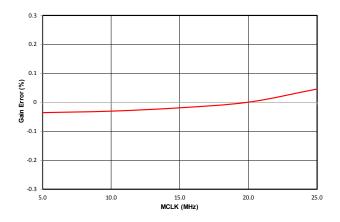

| Gain Error                                  |                  | T <sub>A</sub> = 25 °C               | -0.15  | ±0.05 | 0.15  | %      |

| Gain Error Drift                            |                  |                                      | -7     | 9     | 20    | ppm/°C |

| Nonlinearity                                |                  | T <sub>A</sub> = 25 °C               | -0.016 | 0.003 | 0.016 | %      |

| Nonlinearity Drift                          |                  |                                      | -1     |       | 1     | ppm/°C |

|                                             |                  | F <sub>IN</sub> = 5 kHz              |        |       |       |        |

| Signal-to-Noise<br>Ratio                    | SNR              | BW = 40 kHz (Si8935/37)              | 73     | 86    |       | dB     |

|                                             |                  | BW = 20 kHz (Si8936)                 |        |       |       |        |

|                                             |                  | F <sub>IN</sub> = 5 kHz              |        |       |       |        |

| Total Harmonic<br>Distortion                | THD              | BW = 40 kHz (Si8935/37)              |        | -83   | -60   | dB     |

|                                             |                  | BW = 20 kHz (Si8936)                 |        |       |       |        |

| Common-Mode<br>Transient<br>Immunity        | CMTI             | VIN = GNDA,<br>VCM = 1500 V          | 50     | 75    |       | kV/µs  |

7

| Parameter                              | Symbol            | Test Condition                    | Min            | Тур  | Мах            | Units |

|----------------------------------------|-------------------|-----------------------------------|----------------|------|----------------|-------|

|                                        |                   | VDDA at DC                        |                | -100 |                | dB    |

| Power-Supply Re-                       | PSRR              | VDDA at 100 mV and 10 kHz ripple  |                | -100 |                | dB    |

| jection Ratio                          |                   | VDDB at DC                        |                | -100 |                | dB    |

|                                        |                   | VDDB at 100 mV and 10 kHz ripple  |                | -100 |                | dB    |

| Digital                                |                   | · · · · · ·                       |                |      |                |       |

| Logic high input<br>threshold (Si8935) | VIH               |                                   | 85% of<br>VDDB |      |                | V     |

| Logic low input<br>threshold (Si8935)  | VIL               |                                   |                |      | 15% of<br>VDDB | V     |

| Input hysteresis                       | VIHYST            |                                   |                | 120  |                | mV    |

| Output load capacitance                | C <sub>LOAD</sub> |                                   |                | 15   |                | pF    |

| External Clock (Si893                  | 35)               |                                   |                |      | 1              |       |

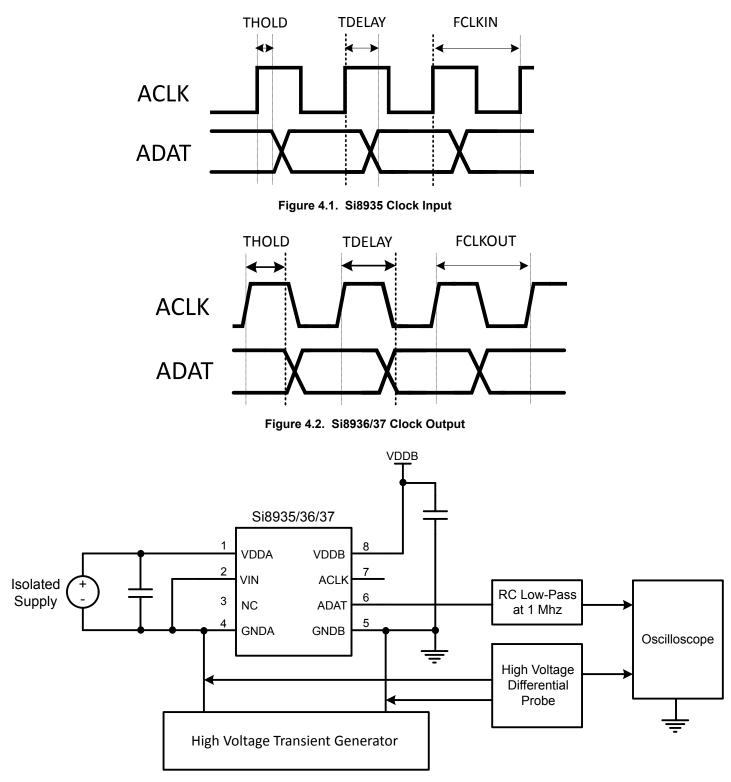

| Clock Frequency                        | FCLKIN            |                                   | 5              |      | 25             | MHz   |

| Duty Cycle                             | FDUTY             |                                   | 45             | 50   | 55             | %     |

| Delay to Data Valid                    | TDELAY            |                                   |                |      | 23             | ns    |

| Data Hold Time                         | THOLD             |                                   | 6              |      |                | ns    |

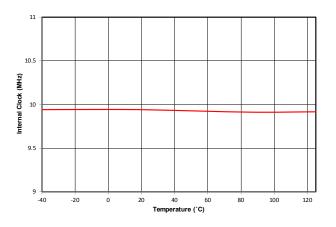

| Internal Clock (Si893                  | 6)                |                                   |                |      |                |       |

|                                        | FOLKOUT           | T <sub>A</sub> = 25 °C            | 9.9            | 10   | 10.1           | MHz   |

| Clock Frequency                        | FCLKOUT           | T <sub>A</sub> = -40 °C to 125 °C | 9.8            | 10   | 10.2           | MHz   |

| Duty Cycle                             | FDUTY             |                                   | 45             | 50   | 55             | %     |

| Delay to Data Valid                    | TDELAY            |                                   |                |      | 60             | ns    |

| Data Hold Time                         | THOLD             |                                   | 40             |      |                | ns    |

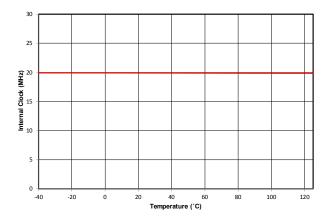

| nternal Clock (Si893                   | 7)                |                                   |                |      |                |       |

| Clock Frequency                        | FOLKOUT           | T <sub>A</sub> = 25 °C            | 19.8           | 20   | 20.2           | MHz   |

|                                        | FCLKOUT           | T <sub>A</sub> = -40 °C to 125 °C | 19.6           | 20   | 20.4           | MHz   |

| Duty Cycle                             | FDUTY             |                                   | 45             | 50   | 55             | %     |

| Delay to Data Valid                    | TDELAY            |                                   |                |      | 30             | ns    |

| Data Hold Time                         | THOLD             |                                   | 20             |      |                | ns    |

| Parameter                                      | Symbol         | Test Condition                   | Characteristic | Unit |

|------------------------------------------------|----------------|----------------------------------|----------------|------|

| Safety Temperature                             | T <sub>S</sub> |                                  | 150            | °C   |

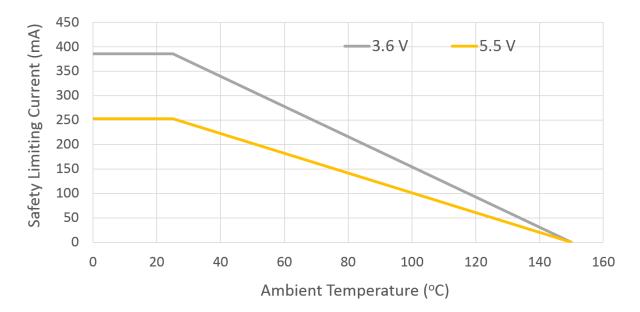

|                                                |                | $\theta_{JA} = 90 \text{ °C/W}$  |                |      |

|                                                |                | VDD = 5.5 V                      | 050            |      |

|                                                |                | T <sub>J</sub> = 150 °C          | 253            | mA   |

|                                                |                | T <sub>A</sub> = 25 °C           |                |      |

| Safety Input Current (WB Stretched SOIC-8)     | I <sub>S</sub> | $\theta_{JA} = 90 \ ^{\circ}C/W$ |                |      |

|                                                |                | VDD = 3.6 V                      |                |      |

|                                                |                | T <sub>J</sub> = 150 °C          | 386            | mA   |

|                                                |                | T <sub>A</sub> = 25 °C           |                |      |

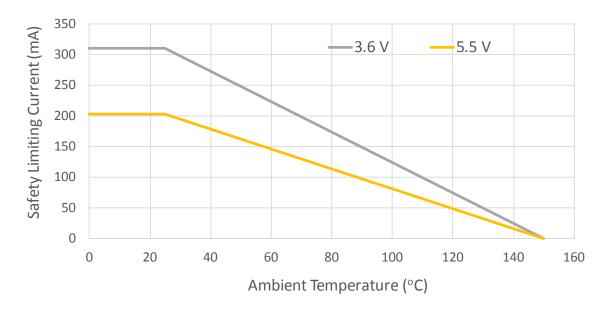

| Safety Input Current (NB SOIC-8)               |                | θ <sub>JA</sub> = 112 °C/W       |                |      |

|                                                |                | VDD = 5.5 V                      | 203            |      |

|                                                |                | T <sub>J</sub> = 150 °C          |                | mA   |

|                                                |                | T <sub>A</sub> = 25 °C           |                |      |

|                                                | I <sub>S</sub> | θ <sub>JA</sub> = 112 °C/W       |                | mA   |

|                                                |                | VDD = 3.6 V                      | 310            |      |

|                                                |                | T <sub>J</sub> = 150 °C          |                |      |

|                                                |                | T <sub>A</sub> = 25 °C           |                |      |

|                                                |                | $\theta_{JA} = 90 \ ^{\circ}C/W$ |                |      |

| Safety Input Power (WB Stretched SOIC-8)       | PS             | T <sub>J</sub> = 150 °C          | 1389           | mW   |

|                                                |                | T <sub>A</sub> = 25 °C           |                |      |

|                                                |                | θ <sub>JA</sub> = 112 °C/W       |                |      |

| Safety Input Power (NB SOIC-8)                 | P <sub>S</sub> | T <sub>J</sub> = 150 °C          | 1116           | mW   |

|                                                |                | T <sub>A</sub> = 25 °C           |                |      |

| Device Power Dissipation (WB Stretched SOIC-8) | PD             |                                  | 1.39           | W    |

| Device Power Dissipation (NB SOIC-8)           | PD             |                                  | 1.12           | W    |

| Note:                                          |                |                                  |                | 1    |

## Table 4.2. IEC Safety Limiting Values<sup>1</sup>

1. Maximum value allowed in the event of a failure. Refer to the thermal derating curves below.

#### Table 4.3. Thermal Characteristics

| Parameter                             | Symbol        | WB Stretched<br>SOIC-8 | NB SOIC-8 | Unit |

|---------------------------------------|---------------|------------------------|-----------|------|

| IC Junction-to-Air Thermal Resistance | $\theta_{JA}$ | 90                     | 112       | °C/W |

Figure 4.4. WB Stretched SOIC-8 Thermal Derating Curve for Safety Limiting Current

Figure 4.5. NB SOIC-8 Thermal Derating Curve for Safety Limiting Current

|                                                               | J                | -    |            |                  |

|---------------------------------------------------------------|------------------|------|------------|------------------|

| Parameter                                                     | Symbol           | Min  | Мах        | Unit             |

| Storage Temperature                                           | T <sub>STG</sub> | -65  | 150        | °C               |

| Ambient Temperature Under Bias                                | T <sub>A</sub>   | -40  | 125        | °C               |

| Junction Temperature                                          | TJ               | _    | 150        | °C               |

| Supply Voltage                                                | VDDA, VDDB       | -0.5 | 6.0        | V                |

| Input Voltage respect to GNDA                                 | VIN              | -0.5 | VDDA + 0.5 | V                |

| Output Sink or Source Current                                 | I <sub>O</sub>   | _    | 5          | mA               |

| Total Power Dissipation                                       | PT               | _    | 212        | mW               |

| Lead Solder Termperature (10 s)                               |                  | _    | 260        | °C               |

| Human Body Model ESD Rating                                   |                  | 6000 | _          | V                |

| Capacitive Discharge Model ESD Rating                         |                  | 2000 | _          | V                |

| Maximum Isolation (WB Stretched SOIC-8 Input to Output) (1 s) |                  |      | 6500       | V <sub>RMS</sub> |

| Maximum Isolation (NB SOIC-8 package Input to Output) (1 s)   |                  |      | 4500       | V <sub>RMS</sub> |

#### Table 4.4. Absolute Maximum Ratings<sup>1</sup>

#### Note:

1. Permanent device damage may occur if the absolute maximum ratings are exceeded. Functional operation should be restricted to conditions as specified in the operational sections of the data sheet.

#### 4.1 Regulatory Information

#### Table 4.5. Regulatory Information (Pending)<sup>1, 2</sup>

#### CSA

The Si8935/36/37 is certified under CSA. For more details, see Master Contract File 232873.

60950-1, 62368-1: Up to 600 V<sub>RMS</sub> reinforced insulation working voltage; up to 1000 V<sub>RMS</sub> basic insulation working voltage.

#### VDE

The Si8935/36/37 is certified according to VDE 0884-11. For more details, see File 5006301-4880-0001.

VDE 0884-11: Up to 1414 V<sub>peak</sub> for reinforced insulation working voltage.

#### UL

The Si8935/36/37 is certified under UL1577 component recognition program. For more details, see File E257455.

Rated up to 5000  $V_{\text{RMS}}$  isolation voltage for basic protection.

#### CQC

The Si8935/36/37 is certified under GB4943.1-2011.

Rated up to 600 V<sub>RMS</sub> reinforced insulation working voltage; up to 1000 V<sub>RMS</sub> basic insulation working voltage.

#### Note:

1. Regulatory Certifications apply to 5 kV<sub>RMS</sub> rated devices which are production tested to 6.0 kV<sub>RMS</sub> for 1 sec.

2. Regulatory Certifications apply to 2.5 kV<sub>RMS</sub> rated devices which are production tested to 3.0 kV<sub>RMS</sub> for 1 sec.

#### Table 4.6. Insulation and Safety-Related Specifications

|                                              |                 |                | Va                     |                  |      |

|----------------------------------------------|-----------------|----------------|------------------------|------------------|------|

| Parameter                                    | Symbol          | Test Condition | WB Stretched<br>SOIC-8 | NB<br>SOIC-8     | Unit |

| Nominal External Air Gap (Clearance)         | CLR             |                | 9.0 <sup>1</sup>       | 4.9              | mm   |

| Nominal External Tracking<br>(Creepage)      | CPG             |                | 9.0 <sup>1</sup>       | 4.01             | mm   |

| Minimum Internal Gap<br>(Internal Clearance) | DTI             |                | 36                     | 36               | μm   |

| Tracking Resistance                          | PTI or CTI      | IEC60112       | 600                    | 600              | V    |

| Erosion Depth                                | ED              |                | 0.04                   | 0.04             | mm   |

| Resistance (Input-Output) <sup>2</sup>       | R <sub>IO</sub> |                | 10 <sup>12</sup>       | 10 <sup>12</sup> | Ω    |

| Capacitance (Input-Output) <sup>2</sup>      | C <sub>IO</sub> | f = 1 MHz      | 1                      | 1                | pF   |

#### Note:

1. The values in this table correspond to the nominal creepage and clearance values. VDE certifies the clearance and creepage limits as x.x mm minimum for the WB Stretched SOIC-8 package. UL does not impose a clearance and creepage minimum for component-level certifications. CSA certifies the clearance and creepage limits as 8 mm minimum for the WB Stretched SOIC-8 package.

2. To determine resistance and capacitance, the Si8935/36/37 is converted into a two-terminal device. Pins 1–4 are shorted together to form the first terminal, and pins 5–8 are shorted together to form the second terminal. The parameters are then measured between these two terminals.

#### Table 4.7. IEC 60664-1 Ratings

|                                |                                             | Specification          |           |  |

|--------------------------------|---------------------------------------------|------------------------|-----------|--|

| Parameter                      | Test Conditions                             | WB Stretched<br>SOIC-8 | NB SOIC-8 |  |

| Basic Isolation Group          | Material Group                              | I                      | I         |  |

|                                | Rated Mains Voltages ≤ 150 V <sub>RMS</sub> | I-IV                   | I-IV      |  |

| Installation<br>Classification | Rated Mains Voltages ≤ 300 V <sub>RMS</sub> | I-IV                   | I-IV      |  |

| Classification                 | Rated Mains Voltages ≤ 600 V <sub>RMS</sub> | I-IV                   | 1-111     |  |

#### Table 4.8. VDE 0884-11 Insulation Characteristics<sup>1</sup>

|                                                                      |                   |                                                                                                                                           | Charac                      |                             |        |

|----------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------|--------|

| Parameter                                                            | Symbol            | Symbol Test Condition                                                                                                                     |                             | NB SOIC-8                   | Unit   |

| Maximum Working Insula-<br>tion Voltage                              | V <sub>IORM</sub> |                                                                                                                                           | 1414                        | 560                         | V peak |

| Input to Output Test Volt-<br>age                                    | V <sub>PR</sub>   | Method b1<br>(V <sub>IORM</sub> x 1.875 = V <sub>PR</sub> , 100%<br>Production Test, t <sub>m</sub> = 1 sec,<br>Partial Discharge < 5 pC) | 2650                        | 1050                        | V peak |

| Transient Overvoltage                                                | V <sub>IOTM</sub> | t = 60 sec                                                                                                                                | 8000                        | 4000                        | V peak |

| Surge Voltage                                                        | V <sub>IOSM</sub> | Tested per IEC 60065 with surge<br>voltage using rise/decay time of<br>1.2 μs/50 μs                                                       | 6250<br>(Tested with 10 kV) | 6250<br>(Tested with 10 kV) | V peak |

| Pollution Degree<br>(DIN VDE 0110, Table 1)                          |                   |                                                                                                                                           | 2                           | 2                           |        |

| Insulation Resistance at<br>T <sub>S</sub> , V <sub>IO</sub> = 500 V | $R_S$             |                                                                                                                                           | >10 <sup>9</sup>            | >10 <sup>9</sup>            | Ω      |

Note:

1. This isolator is suitable for reinforced electrical isolation only within the safety limit data. Maintenance of the safety data is ensured by protective circuits. The Si8935/36/37 provides a climate classification of 40/125/21.

#### 4.2 Typical Operating Characteristics

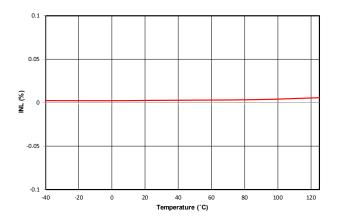

Figure 4.6. Si8935 Nonlinearity (%) vs. Temperature (°C)

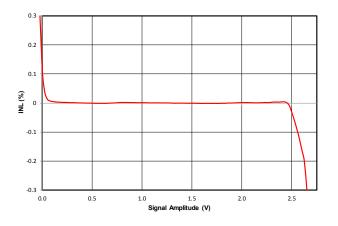

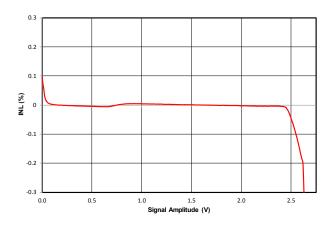

Figure 4.8. Si8935 Nonlinearity (%) vs. Input Signal Amplitude (mV)

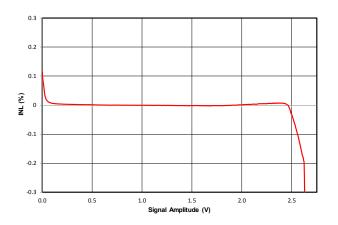

Figure 4.10. Si8937 Nonlinearity (%) vs. Input Signal Amplitude (mV)

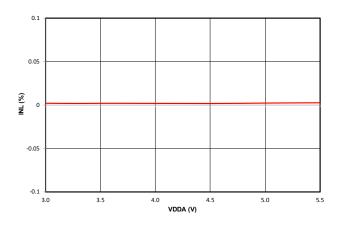

Figure 4.7. Si8935 Nonlinearity (%) vs. VDDA Supply (V)

Figure 4.9. Si8936 Nonlinearity (%) vs. Input Signal Amplitude (mV)

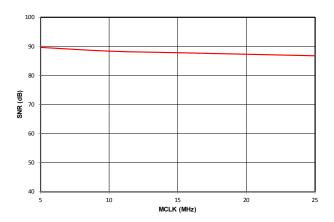

Figure 4.11. Si8935 Signal-to-Noise Ratio (dB) vs. MCLK (MHz)

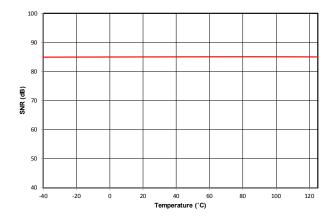

Figure 4.12. Si8935 Signal-to-Noise Ratio (dB) vs. Temperature (°C)

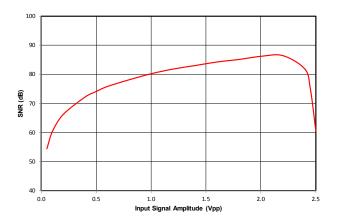

Figure 4.14. Si8935 Signal-to-Noise Ratio (dB) vs. Input Signal Amplitude (mV)

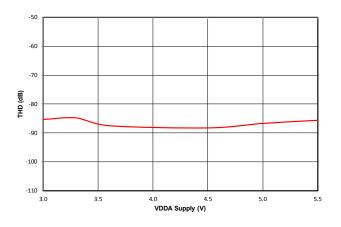

Figure 4.16. Si8935 Total Harmonic Distortion (dB) vs. VDDA Supply (V)

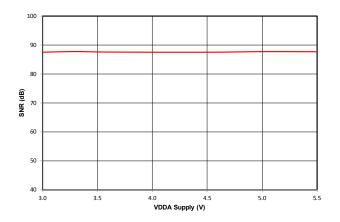

Figure 4.13. Si8935 Signal-to-Noise Ratio (dB) vs. VDDA Supply (V)

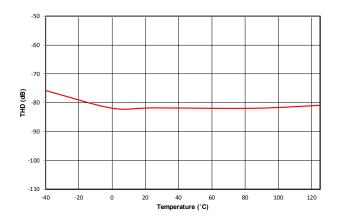

Figure 4.15. Si8935 Total Harmonic Distortion (dB) vs. Temperature (°C)

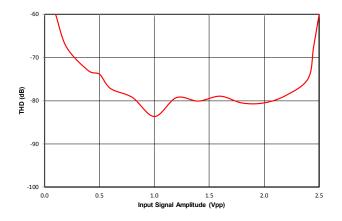

Figure 4.17. Si8935 Total Harmonic Distortion vs. Input Signal Amplitude (mV)

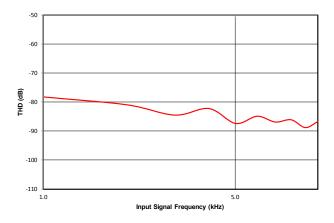

Figure 4.18. Si8935 Total Harmonic Distortion vs. Input Signal Frequency (kHz)

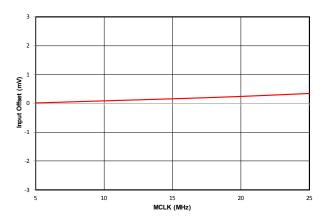

Figure 4.20. Si8935 Input Offset (mV) vs. MCLK (MHz)

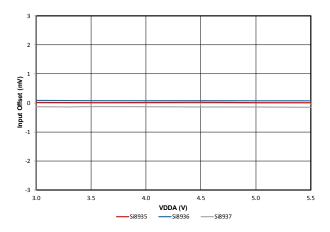

Figure 4.22. Input Offset (mV) vs. VDDA Supply (V)

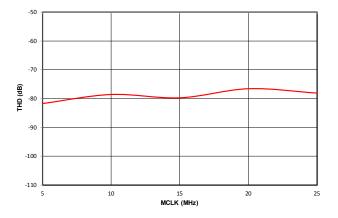

Figure 4.19. Si8935 Total Harmonic Distortion vs. MCLK (MHz)

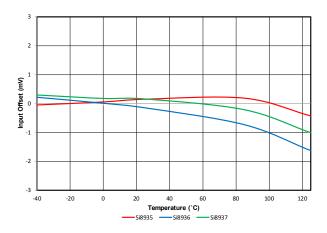

Figure 4.21. Input Offset (mV) vs. Temperature (°C)

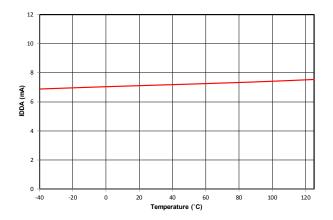

Figure 4.23. Si8935/36/37 IDDA (mA) vs. Temperature (C)

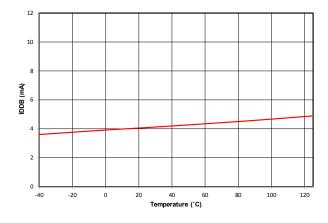

Figure 4.24. Si8935 IDDB (mA) vs. Temperature (C)

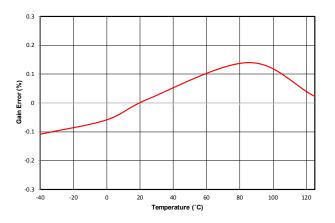

Figure 4.26. Si8935 Gain Error (%) vs. Temperature (C)

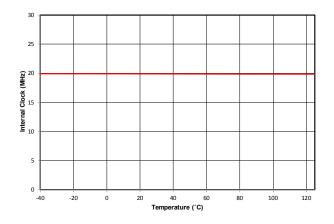

Figure 4.28. Si8936 Internal Clock Frequency (MHz) vs. Temperature (C)

Figure 4.25. Si8935 IDDB (mA) vs. MCLK (MHz)

Figure 4.27. Si8935 Gain Error (%) vs. MCLK (MHz)

Figure 4.29. Si8937 Internal Clock Frequency (MHz) vs. Temperature (C)

Figure 4.30. Si8935 Power Supply Rejection Ratio (dB) vs. Input Signal Frequency (kHz)

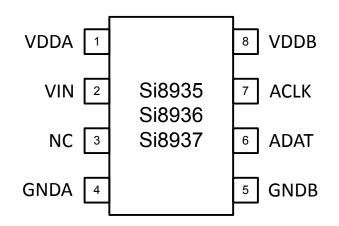

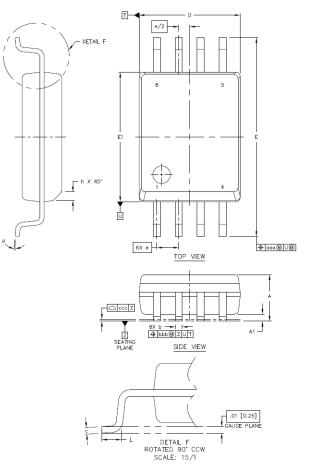

## 5. Pin Descriptions

| Name            | Pin # | Description                                                        |

|-----------------|-------|--------------------------------------------------------------------|

| VDDA            | 1     | Input side power supply                                            |

| VIN             | 2     | Voltage input                                                      |

| NC <sup>1</sup> | 3     | No Connect                                                         |

| GNDA            | 4     | Input side ground                                                  |

| GNDB            | 5     | Output side ground                                                 |

| ADAT            | 6     | Delta-sigma modulator data output                                  |

| ACLK            | 7     | Delta-sigma modulator clock (input on Si8935, output on Si8936/37) |

| VDDB            | 8     | Output side power supply                                           |

| Noto            |       |                                                                    |

#### Note:

1. No Connect. These pins are not internally connected. To maximize CMTI performance, these pins should be connected to the ground plane.

## 6. Packaging

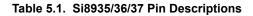

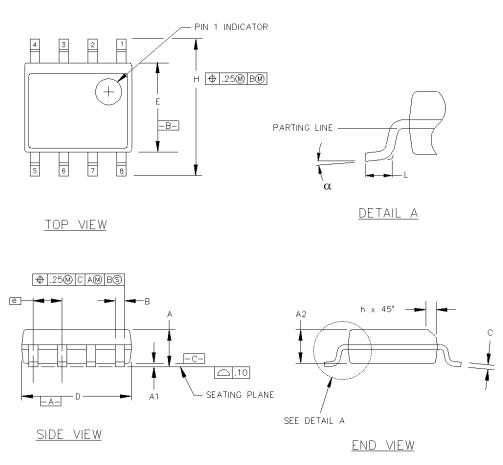

#### 6.1 Package Outline: 8-Pin Wide Body Stretched SOIC

The figure below illustrates the package details for the Si8935/36/37 in a 8-Pin Wide Body Stretched SOIC package. The table lists the values for the dimensions shown in the illustration.

Figure 6.1. 8-Pin Wide Body Stretched SOIC Package

| Table 6.1. 8-Pin Wide Body Stretche | d SOIC Package Diagram Dimensions |

|-------------------------------------|-----------------------------------|

|-------------------------------------|-----------------------------------|

| <u>Qumb al</u> | Millimeters |       |

|----------------|-------------|-------|

| Symbol         | Min         | Мах   |

| A              | 2.49        | 2.79  |

| A1             | 0.36        | 0.46  |

| b              | 0.30        | 0.51  |

| с              | 0.20        | 0.33  |

| D              | 5.74        | 5.94  |

| E              | 11.25       | 11.76 |

| E1             | 7.39        | 7.59  |

| e              | 1.27        | BSC   |

| L              | 0.51        | 1.02  |

| h              | 0.25        | 0.76  |

#### Si8935/36/37 Data Sheet • Packaging

| Symbol | Millimeters |      |  |

|--------|-------------|------|--|

|        | Min         | Мах  |  |

| θ      | 0°          | 8°   |  |

| ааа    | _           | 0.25 |  |

| bbb    | —           | 0.25 |  |

| CCC    |             | 0.10 |  |

| Noto:  |             |      |  |

#### Note:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. Recommended reflow profile per JEDEC J-STD-020C specification for small body, lead-free components.

#### 6.2 Package Outline: 8-Pin Narrow Body SOIC

The figure below illustrates the package details for the Si8935/36/37 in an 8-Pin Narrow Body SOIC package. The table lists the values for the dimensions shown in the illustration.

Figure 6.2. 8-Pin Narrow Body SOIC Package

#### Table 6.2. 8-Pin Narrow Body SOIC Package Diagram Dimensions

| Dimension | Min      | Мах      |

|-----------|----------|----------|

| A         | 1.35     | 1.75     |

| A1        | 0.10     | 0.25     |

| A2        | 1.40 REF | 1.55 REF |

| В         | 0.33     | 0.51     |

| С         | 0.19     | 0.25     |

| D         | 4.80     | 5.00     |

| E         | 3.80     | 4.00     |

| e         | 1.27     | BSC      |

| Н         | 5.80     | 6.20     |

| h         | 0.25     | 0.50     |

| L         | 0.40     | 1.27     |

| α         | 0°       | 8°       |

| Dimension                                                                                                   | Min | Мах |

|-------------------------------------------------------------------------------------------------------------|-----|-----|

| Note:                                                                                                       |     |     |

| 1. All dimensions shown are in millimeters (mm) unless otherwise noted.                                     |     |     |

| 2. Dimensioning and Tolerancing per ANSI Y14.5M-1982.                                                       |     |     |

| 3. This drawing conforms to JEDEC Outline MS-012.                                                           |     |     |

| 4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020B specification for Small Body Components. |     |     |

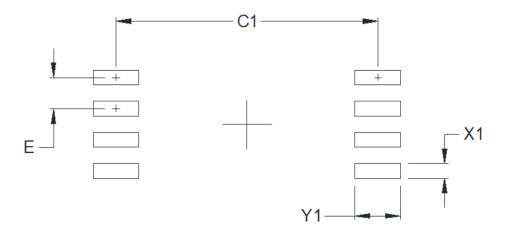

#### 6.3 Land Pattern: 8-Pin Wide Body Stretched SOIC

The figure below illustrates the recommended land pattern details for the Si8935/36/37 in a 8-Pin Wide Body Stretched SOIC package. The table lists the values for the dimensions shown in the illustration.

Figure 6.3. 8-Pin Wide Body Stretched SOIC Land Pattern

#### Table 6.3. 8-Pin Wide Body Stretched SOIC Land Pattern Dimensions<sup>1</sup>

| Dimension | (mm)  |

|-----------|-------|

| C1        | 10.60 |

| E         | 1.27  |

| X1        | 0.60  |

| Y1        | 1.85  |

### Note:

#### General

- 1. All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05 mm.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

#### Solder Mask Design

1. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 µm minimum, all the way around the pad.

#### Stencil Design

- 1. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125 mm (5 mils).

- 3. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pins.

#### Card Assembly

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

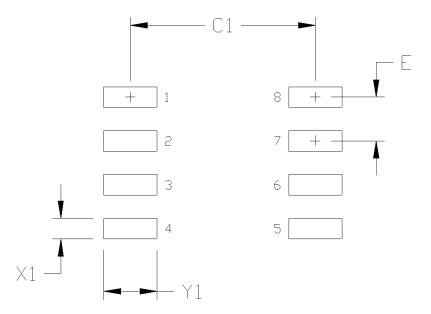

#### 6.4 Land Pattern: 8-Pin Narrow Body SOIC

The figure below illustrates the recommended land pattern details for the Si8935/36/37 in an 8-Pin Narrow Body SOIC package. The table lists the values for the dimensions shown in the illustration.

Figure 6.4. 8-Pin Narrow Body SOIC Land Pattern

| Table 6.4. | 8-Pin Narrow Body | SOIC Land Pattern | Dimensions |

|------------|-------------------|-------------------|------------|

|------------|-------------------|-------------------|------------|

| Symbol | mm   |

|--------|------|

| C1     | 5.40 |

| E      | 1.27 |

| X1     | 0.60 |

| Y1     | 1.55 |

|        |      |

#### Note:

1. This Land Pattern Design is based on IPC-7351 pattern SOIC127P600X173-8N for Density Level B (Median Land Protrusion). 2. All feature sizes shown are at Maximum Material Condition (MMC) and a card fabrication tolerance of 0.05 mm is assumed.

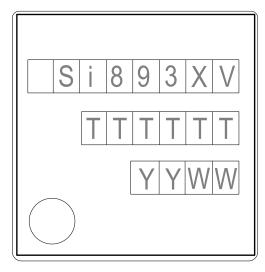

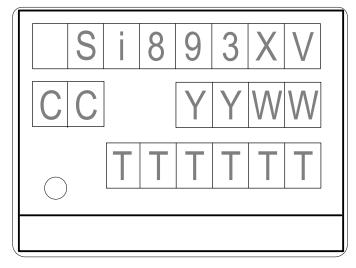

#### 6.5 Top Marking: 8-Pin Wide Body Stretched SOIC

The figure below illustrates the top markings for the Si8935/36/37 in an 8-Pin Wide Body Stretched SOIC package. The table explains the top marks shown in the illustration.

Figure 6.5. Si893x Wide Body Stretched 8-Pin SOIC Top Marking

| Line 1 Marking: | Customer Part Number                                                       | Si893X<br>X = Base part number<br>• 5 = External clock<br>• 6 = Internal 10 MHz clock<br>• 7 = Internal 20 MHz clock<br>V = Insulation rating:<br>• D = 5.0 kVrms |

|-----------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Line 2 Marking: | TTTTTT = Mfg Code                                                          | Manufacturing Code from the Assembly Purchase Order form.                                                                                                         |

| Line 3 Marking: | YY = Year<br>WW = Work Week<br>Circle = 43 mils Diameter<br>Left-Justified | Assigned by the Assembly House. Corresponds to the year and work week of the mold date.                                                                           |

#### 6.6 Top Marking: 8-Pin Narrow Body SOIC

The figure below illustrates the top markings for the Si8935/36/37 in an 8-Pin Narrow Body SOIC package. The table explains the top marks shown in the illustration.

Figure 6.6. 8-Pin Narrow Body SOIC Top Marking

### Table 6.6. 8-Pin Narrow Body SOIC Top Marking Explanation

| Line 1 Marking: | Customer Part Number                                                             | Si893X<br>X = Base part number<br>• 5 = External clock<br>• 6 = Internal 10 MHz clock<br>• 7 = Internal 20 MHz clock<br>V = Insulation rating:<br>• B = 2.5 kVrms |

|-----------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Line 2 Marking: | CC = Country of Origin ISO Code Abbrevi-<br>ation<br>YY = Year<br>WW = Work Week | Assigned by the Assembly House. Corresponds to the year and work week of the mold date.                                                                           |

| Line 3 Marking: | TTTTTT = Mfg Code<br>Circle = 19.7 mils Diameter<br>Left-Justified               | Manufacturing Code from the Assembly Purchase Order form.                                                                                                         |

## 7. Revision History

#### **Revision 0.7**

April, 2021

- Updated Applications and Key Features on front page.

- Added Automotive OPNs to 1. Ordering Guide.

- Updated Table 4.6 Insulation and Safety-Related Specifications on page 13.

- Updated 4. Electrical Specifications after full characterization.

- · Updated narrow body top marking.

- · Numerous clarifications throughout.

### **Revision 0.1**

March, 2019

• Initial release.

Support & Resources www.skyworksinc.com/support

#### Copyright © 2021 Skyworks Solutions, Inc. All Rights Reserved.

Information in this document is provided in connection with Skyworks Solutions, Inc. ("Skyworks") products or services. These materials, including the information contained herein, are provided by Skyworks as a service to its customers and may be used for informational purposes only by the customer. Skyworks assumes no responsibility for errors or omissions in these materials or the information contained herein. Skyworks may change its documentation, products, services, specifications or product descriptions at any time, without notice. Skyworks makes no commitment to update the materials or information and shall have no responsibility whatsoever for conflicts, incompatibilities, or other difficulties arising from any future changes.

No license, whether express, implied, by estoppel or otherwise, is granted to any intellectual property rights by this document. Skyworks assumes no liability for any materials, products or information provided hereunder, including the sale, distribution, reproduction or use of Skyworks products, information or materials, except as may be provided in Skyworks' Terms and Conditions of Sale.

THE MATERIALS, PRODUCTS AND INFORMATION ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, WHETHER EXPRESS, IMPLIED, STATUTORY, OR OTHERWISE, INCLUDING FITNESS FOR A PARTICULAR PURPOSE OR USE, MERCHANTABILITY, PERFORMANCE, QUALITY OR NON-INFRINGEMENT OF ANY INTELLECTUAL PROPERTY RIGHT; ALL SUCH WARRANTIES ARE HEREBY EXPRESSLY DISCLAIMED. SKYWORKS DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. SKYWORKS SHALL NOT BE LIABLE FOR ANY DAMAGES, INCLUDING BUT NOT LIMITED TO ANY SPECIAL, INDIRECT, INCIDENTAL, STATUTORY, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS THAT MAY RESULT FROM THE USE OF THE MATERIALS OR INFORMATION, WHETHER OR NOT THE RECIPIENT OF MATERIALS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

Skyworks products are not intended for use in medical, lifesaving or life-sustaining applications, or other equipment in which the failure of the Skyworks products could lead to personal injury, death, physical or environmental damage. Skyworks customers using or selling Skyworks products for use in such applications do so at their own risk and agree to fully indemnify Skyworks for any damages resulting from such improper use or sale.

Customers are responsible for their products and applications using Skyworks products, which may deviate from published specifications as a result of design defects, errors, or operation of products outside of published parameters or design specifications. Customers should include design and operating safeguards to minimize these and other risks. Skyworks assumes no liability for applications assistance, customer product design, or damage to any equipment resulting from the use of Skyworks products outside of Skyworks' published specifications or parameters.

Skyworks, the Skyworks symbol, Sky5<sup>®</sup>, SkyOne<sup>®</sup>, SkyBlue<sup>™</sup>, Skyworks Green<sup>™</sup>, Clockbuilder<sup>®</sup>, DSPLL<sup>®</sup>, ISOmodem<sup>®</sup>, ProSLIC<sup>®</sup>, and SiPHY<sup>®</sup> are trademarks or registered trademarks of Skyworks Solutions, Inc. or its subsidiaries in the United States and other countries. Third-party brands and names are for identification purposes only and are the property of their respective owners. Additional information, including relevant terms and conditions, posted at www.skyworksinc.com, are incorporated by reference.

## **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Skyworks:

<u>SI8937D-IS4</u> <u>SI8937D-IS4R</u> <u>SI8935D-IS4R</u> <u>SI8936D-IS4</u> <u>SI8936D-IS4R</u> <u>SI8935D-IS4</u> <u>SI8935B-IS8</u> <u>SI8935B-IS8</u> <u>SI8936B-IS8</u> <u>SI8936B-IS8</u> <u>SI8937B-IS8</u> <u>SI8937B-IS8</u>