# Si3229x: ProSLIC<sup>®</sup> Single-Chip Dual FXS Solution

The Si3229x Dual ProSLIC® devices, in a single package, implement two complete foreign exchange station (FXS) telephony interfaces. The Si3229x devices operate from a 3.3 V supply and have standard PCM/SPI or 3-wire ISI digital interfaces. A pair of built-in dc-dc converter controllers can be used to automatically generate the optimal battery voltage required for each line-state, optimizing efficiency and minimizing heat generation. The Si3229x devices are designed to operate with capacitive ultra-boost tracking battery supply for lower power, cost, and footprint vs. other tracking or shared battery supplies in the industry. Self-testing and metallic loop testing (MLT) is facilitated by the built-in DSP, monitor ADC, and test load. The devices are available with wideband audio for better than PSTN voice quality, DTMF detection, and Smart Ringing. Smart Ringing reduces the peak current with 2-channel ringing for lower-cost ac-dc adapters. The Si3229x devices are available in an 8 x 8 mm 68-pin QFN package.

#### Applications:

- · VoIP gateways and routers

- xDSL IADs

- Optical Network Terminals/Units (ONT/U)

- Analog Terminal Adapters (ATA)

- · Cable eMTA

- · Wireless Fixed Terminals (WFT)

- Wireless Local Loop (WLL)

- WiMAX CPE

- Private Branch Exchange (PBX)

- VoIP MDU gateways

# KEY FEATURES

- Two complete FXS channels in a single 8x8 mm package

- · Performs all BORSCHT functions

- · Ultra-low power consumption

- Patented low-power ringing

- · Patented Smart Ringing option

- Reduces peak current with 2-channel ringing (Si32295/7)

- · Adaptive ringing

- · Simplified configuration and diagnostics

- · Supported by SimpleVoice API

- · Audio diagnostics with loopback

- · Integrated test load

- · Wideband voice support

- · On-hook transmission

- · Loop or ground start operation

- · Smooth polarity reversal

- · Programmable interrupts

- · Software-programmable parameters:

- Ringing frequency, amplitude, cadence, and waveshape

- · Two-wire ac impedance

- · Transhybrid balance

- DC current loop feed (10-45 mA)

- Loop closure and ring trip thresholds

- · Ground key detect threshold

- Flexible integrated tracking DC-DC controller supporting patented low-cost capacitive ultra-boost configuration

- DTMF Generation

- DTMF Detection (Si32291/3/5/7)

- 3-wire Integrated Serial Interface (ISI) or PCM interface

- A-Law/µ-Law companding, linear PCM

- · Pulse metering

- · 3.3 V operation

- · Pb-free/RoHS-compliant packaging

# 1. Ordering Guide

Table 1.1. Si3229x Ordering Guide

| P/N <sup>1</sup> | Description                                                                                | Package Type       | Max V <sub>BAT</sub> | Temperature  |

|------------------|--------------------------------------------------------------------------------------------|--------------------|----------------------|--------------|

| Si32290-A-FM     | Wideband Dual FXS, ISI interface                                                           | QFN68 <sup>2</sup> | –140 V               | 0 to 70 °C   |

| Si32290-A-GM     | Wideband Dual FXS, ISI interface                                                           | QFN68 <sup>2</sup> | –140 V               | –40 to 85 °C |

| Si32291-A-FM     | Wideband Dual FXS, ISI interface, DTMF detection                                           | QFN68 <sup>2</sup> | –140 V               | 0 to 70 °C   |

| Si32291-A-GM     | Wideband Dual FXS, ISI interface, DTMF detection                                           | QFN68 <sup>2</sup> | –140 V               | –40 to 85 °C |

| Si32292-A-FM     | Wideband Dual FXS,<br>PCM interface, daisy-<br>chain mode                                  | QFN68 <sup>2</sup> | –140 V               | 0 to 70 °C   |

| Si32292-A-GM     | Wideband Dual FXS,<br>PCM interface, daisy-<br>chain mode                                  | QFN68 <sup>2</sup> | –140 V               | –40 to 85 °C |

| Si32293-A-FM     | Wideband Dual FXS,<br>PCM interface, DTMF<br>detection, daisy-chain<br>mode                | QFN68 <sup>2</sup> | –140 V               | 0 to 70 °C   |

| Si32293-A-GM     | Wideband Dual FXS,<br>PCM interface, DTMF<br>detection, daisy-chain<br>mode                | QFN68 <sup>2</sup> | –140 V               | –40 to 85 °C |

| Si32295-A-FM     | Wideband Dual FXS, ISI interface, DTMF detection, Smart Ringing                            | QFN68 <sup>2</sup> | –140 V               | 0 to 70 °C   |

| Si32295-A-GM     | Wideband Dual FXS, ISI interface, DTMF detection, Smart Ringing                            | QFN68 <sup>2</sup> | –140 V               | –40 to 85 °C |

| Si32297-A-FM     | Wideband Dual FXS,<br>PCM interface, DTMF<br>detection, daisy-chain<br>mode, Smart Ringing | QFN68 <sup>2</sup> | –140 V               | 0 to 70 °C   |

| Si32297-A-GM     | Wideband Dual FXS,<br>PCM interface, DTMF<br>detection, daisy-chain<br>mode, Smart Ringing | QFN68 <sup>2</sup> | –140 V               | –40 to 85 °C |

| Si32290-A-ZM1    | Wideband Dual FXS, ISI interface, customer-specific                                        | QFN68 <sup>2</sup> | –140 V               | 0 to 70 °C   |

| Si32291-A-ZM1    | Wideband Dual FXS, ISI interface, DTMF detection, customer-specific                        | QFN68 <sup>2</sup> | –140 V               | 0 to 70 °C   |

| P/N <sup>1</sup> | Description                                                                                                      | Package Type       | Max V <sub>BAT</sub> | Temperature |

|------------------|------------------------------------------------------------------------------------------------------------------|--------------------|----------------------|-------------|

| Si32292-A-ZM1    | Wideband Dual FXS,<br>PCM interface, daisy-<br>chain mode, customer-<br>specific                                 | QFN68 <sup>2</sup> | –140 V               | 0 to 70 °C  |

| Si32293-A-ZM1    | Wideband Dual FXS,<br>PCM interface, DTMF<br>detection, daisy-chain<br>mode, customer-specific                   | QFN68 <sup>2</sup> | –140 V               | 0 to 70 °C  |

| Si32295-A-ZM1    | Wideband Dual FXS, ISI interface, DTMF detection, Smart Ringing, customer-specific                               | QFN68 <sup>2</sup> | –140 V               | 0 to 70 °C  |

| Si32297-A-ZM1    | Wideband Dual FXS,<br>PCM interface, DTMF<br>detection, daisy-chain<br>mode, Smart Ringing,<br>customer-specific | QFN68 <sup>2</sup> | –140 V               | 0 to 70 °C  |

| Si32290-A-ZM2    | Wideband Dual FXS, ISI interface, customer-specific                                                              | QFN68 <sup>2</sup> | –140 V               | 0 to 70 °C  |

| Si32291-A-ZM2    | Wideband Dual FXS, ISI interface, DTMF detection, customer-specific                                              | QFN68 <sup>2</sup> | –140 V               | 0 to 70 °C  |

| Si32292-A-ZM2    | Wideband Dual FXS,<br>PCM interface, daisy-<br>chain mode, customer-<br>specific                                 | QFN68 <sup>2</sup> | –140 V               | 0 to 70 °C  |

| Si32293-A-ZM2    | Wideband Dual FXS,<br>PCM interface, DTMF<br>detection, daisy-chain<br>mode, customer-specific                   | QFN68 <sup>2</sup> | –140 V               | 0 to 70 °C  |

| Si32295-A-ZM2    | Wideband Dual FXS, ISI interface, DTMF detection, Smart Ringing, customer-specific                               | QFN68 <sup>2</sup> | –140 V               | 0 to 70 °C  |

| Si32297-A-ZM2    | Wideband Dual FXS,<br>PCM interface, DTMF<br>detection, daisy-chain<br>mode, Smart Ringing,<br>customer-specific | QFN68 <sup>2</sup> | –140 V               | 0 to 70 °C  |

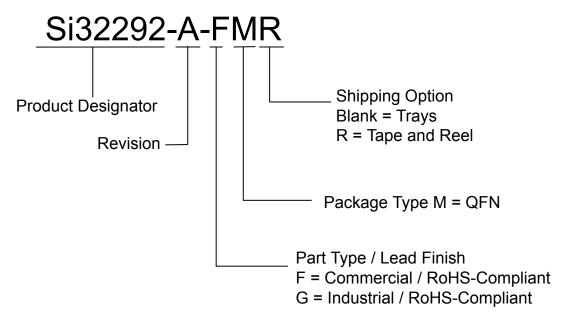

- 1. Adding the suffix "R" to the part number (e.g., Si32292-C-FMR) denotes tape and reel.

- 2. QFN Quad-Flat No-leads

Table 1.2. Evaluation Kit Ordering Guide

| Part Number        | Description                                                                       | V <sub>BAT</sub> Max |

|--------------------|-----------------------------------------------------------------------------------|----------------------|

| Si32293AUB20SL0KIT | 2 FXS evb with lowest-cost capacitive ultra boost dc-dc converter for Si32290/1/5 | –140 V               |

| Si32297AUB20SL0KIT | 2 FXS evb with lowest-cost capacitive ultra boost dc-dc converter for Si32292/3/7 | –140 V               |

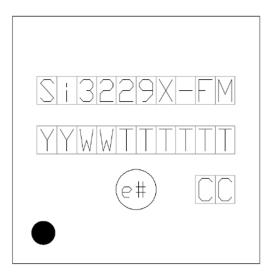

#### 1.1 Product Identification

The product identification number is a finished goods part number or is specified by a finished goods part number, such as a special customer part number.

Figure 1.1. Example Product Identification Number

# **Table of Contents**

| 1. | Ordering Guide                                 | . 2 |

|----|------------------------------------------------|-----|

|    | 1.1 Product Identification                     | . 4 |

| 2. | Functional Description                         | . 6 |

| 3. | Electrical Specifications                      | . 7 |

| 4. | FXS Features                                   | 20  |

|    | 4.1 DC Feed Characteristics                    | .20 |

|    | 4.2 Linefeed Operating States                  | .20 |

|    | 4.3 Line Voltage and Current Monitoring        | .20 |

|    | 4.4 Power Monitoring and Power Fault Detection | .20 |

|    | 4.5 Thermal Overload                           | .20 |

|    | 4.6 Loop Closure/Ring Trip Detection           | .21 |

|    | 4.7 Ground Key Detection                       | .21 |

|    | 4.8 Ringing Generation                         | .22 |

|    | 4.9 Polarity Reversal                          | .22 |

|    | 4.10 Two-Wire Impedance Synthesis              | .22 |

|    | 4.11 Transhybrid Balance Filter                | .22 |

|    | 4.12 Tone Generators                           | .22 |

|    | 4.13 DTMF Detection (Si32291/3/5/7 Only)       | .22 |

|    | 4.14 Pulse Metering                            | .23 |

|    | 4.15 DC-DC Controller                          | .23 |

|    | 4.16 Wideband Audio                            | .23 |

|    | 4.17 Test Facilities                           | .24 |

| 5. | System Interfaces                              | 25  |

|    | 5.1 SPI Control Interface                      | .25 |

|    | 5.2 PCM Interface and Companding               | .25 |

|    | 5.3 Integrated Serial Interface                | .25 |

| 6. | Pin Descriptions                               | 26  |

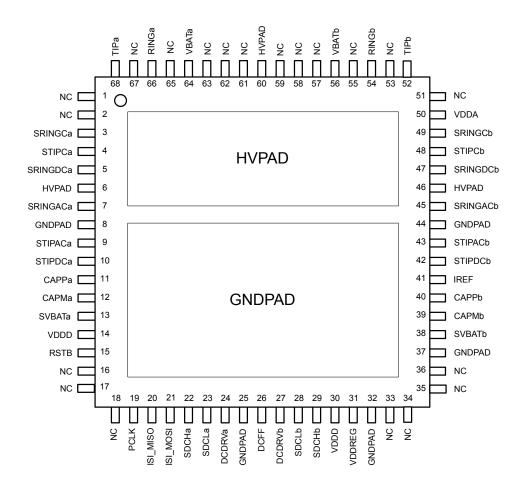

|    | 6.1 Si32290/1/5 ISI 8x8 mm Pinout              |     |

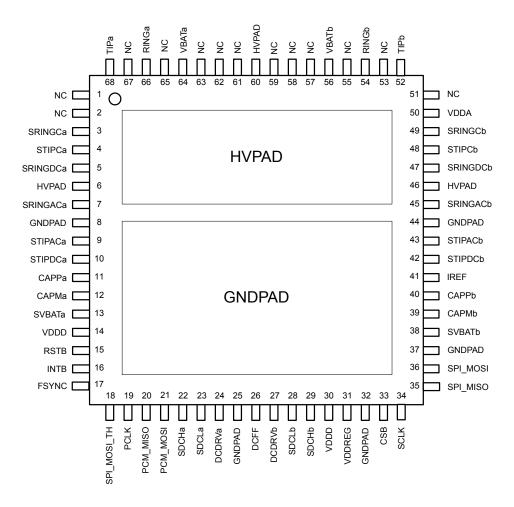

|    | 6.2 Si32292/3/7 PCM 8x8 mm Pinout              |     |

| 7  | Packaging                                      |     |

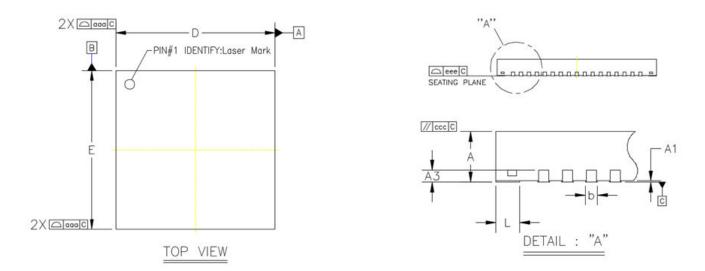

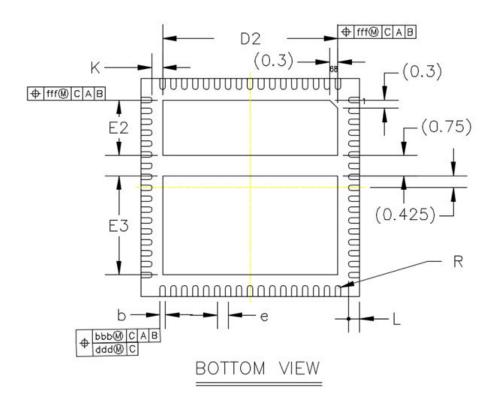

| •  | 7.1 Package Outline: 68-Pin QFN                |     |

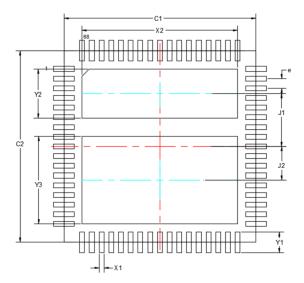

|    | 7.2 Land Pattern: 68-Pin QFN                   |     |

|    | 7.3 Top Marking: 68-Pin QFN                    |     |

| 0  |                                                |     |

| o. | Revision History                               | 42  |

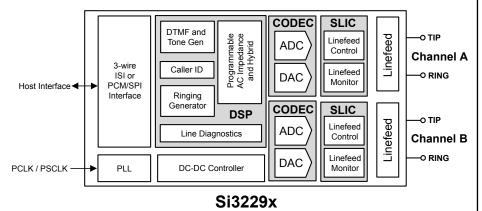

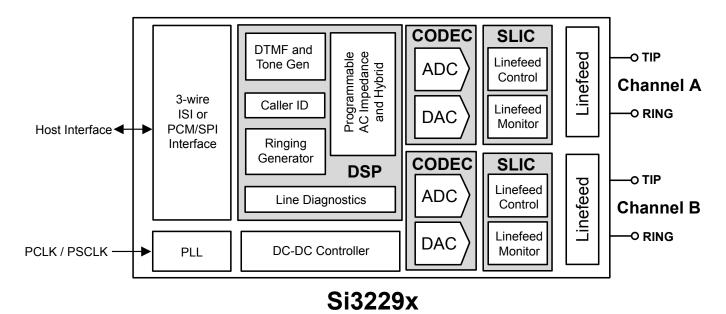

#### 2. Functional Description

Figure 2.1. Functional Block Diagram

The Si3229x dual ProSLIC devices provide all SLIC, codec, DTMF detection, and signal generation functions needed for two complete analog telephone interfaces. They perform all battery, over-voltage, ringing, supervision, codec, hybrid, and test (BORSCHT) functions, and also support extensive metallic loop and self-test capabilities.

The Si3229x supports wideband audio (150Hz-6.8kHz) compliant with PKT-SP-HDV-104-120823, and is configurable to support the full ITU-T-G.722-201209 bandwidth (50Hz-7kHz). The wideband mode provides an expanded audio band with a 16 kHz sample rate for enhanced audio guality while the standard voice-band mode provides standard telephony audio bandwidth.

The Si3229x series supports either a standard PCM/SPI digital interface, or a 3-wire ISI digital interface.

The Si3229x devices incorporate two programmable dc-dc converter controllers that operate in battery tracking mode. The dc-dc converter controllers react to line conditions to provide the optimal battery voltage required for each line-state. Si3229x ICs support a Vbat voltage rating of –140 V. The Si3229x devices are available with DTMF detection and Smart Ringing. Smart Ringing provides reduced peak current 2-channel ringing for lower-cost ac-dc adapters. See 1. Ordering Guide.

Programmable on-hook voltage, programmable offhook loop current, reverse polarity operation, loop or ground start operation, and on-hook transmission are supported. Loop current and voltage are continuously monitored by an integrated monitoring ADC. The Si3229x dual ProSLIC devices support ringing with or without a programmable dc offset, and can operate in low power ringing and adaptive ringing modes. The available offset, frequency, waveshape, and cadence options are designed to ring the widest variety of terminal devices and to reduce external controller requirements.

A complete audio transmit and receive path is integrated, including ac impedance and hybrid gain. These features are software-programmable, allowing a single hardware design to meet global requirements.

# 3. Electrical Specifications

**Table 3.1. Recommended Operating Conditions**

| Parameter                                      | Symbol                                 | Test Condition | Min <sup>1</sup> | Тур | Max <sup>1</sup>      | Unit |

|------------------------------------------------|----------------------------------------|----------------|------------------|-----|-----------------------|------|

| Ambient Temperature                            | т.                                     | F-grade        | 0                | 25  | 70                    | °C   |

| Ambient Temperature                            | T <sub>A</sub> G-grade -40 25 85       |                | °C               |     |                       |      |

| Silicon Junction Temperature, High Voltage Die | T <sub>JHV</sub>                       | Continuous     | _                | _   | Internally<br>Limited | °C   |

| Silicon Junction Temperature, Low Voltage Die  | $T_JLV$                                | Continuous     | _                | _   | 125                   | °C   |

| Supply Voltages                                | V <sub>DDA</sub> ,<br>V <sub>DDD</sub> |                | 3.13             | 3.3 | 3.47                  | V    |

| Battery Voltage <sup>2</sup>                   | V <sub>BAT</sub>                       |                | -140             | _   | -15                   | V    |

- 1. All minimum and maximum specifications apply across the recommended operating conditions. Typical values apply at nominal supply voltages and an operating temperature of 25 °C unless otherwise stated.

- 2. Minimum and maximum battery voltage limits are dependent upon loop conditions and dc-dc converter configuration.

**Table 3.2. Power Supply Characteristics**

| Parameter                 | Symbol            | Test Condition                           | Min | Тур   | Max | Unit |

|---------------------------|-------------------|------------------------------------------|-----|-------|-----|------|

| Supply Currents:<br>Reset | I <sub>DD</sub>   | $V_T$ and $V_R$ = Hi-Z , RSTB = 0        | _   | 3.61  | _   | mA   |

| Reset                     | I <sub>VBAT</sub> |                                          | _   | 0.00  | _   | mA   |

| Supply Currents:          | I <sub>DD</sub>   | V <sub>T</sub> and V <sub>R</sub> = Hi-Z |     | 21.75 | _   | mA   |

| High Impedance,           | I <sub>VBAT</sub> |                                          | _   | 0.6   | _   | mA   |

| Open                      |                   |                                          |     |       |     |      |

| Supply Currents:          | I <sub>DD</sub>   | V <sub>TR</sub> = –48 V,                 | _   | 10.28 | _   | mA   |

| Forward/Reverse,          | I <sub>VBAT</sub> | Automatic Power Save Mode Enabled        | _   | 0.4   | _   | mA   |

| On-hook                   |                   |                                          |     |       |     |      |

| Supply Currents:          | I <sub>DD</sub>   | V <sub>TR</sub> = -48 V,                 | _   | 34.40 | _   | mA   |

| Forward/Reverse,          | I <sub>VBAT</sub> | Automatic Power Save Mode Disabled       | _   | 2.2   | _   | mA   |

| On-hook                   |                   |                                          |     |       |     |      |

| Supply Currents:          | I <sub>DD</sub>   | $V_T$ or $V_R = -48 \text{ V}$           | _   | 10.27 | _   | mA   |

| Tip/Ring Open,            | I <sub>VBAT</sub> | $V_R$ or $V_T$ = Hi-Z,                   | _   | 0.4   | _   | mA   |

| On-hook                   |                   | Automatic Power Save Mode Enabled        |     |       |     |      |

| Supply Currents:          | I <sub>DD</sub>   | $V_T$ or $V_R = -48 \text{ V}$           | _   | 33.60 | _   | mA   |

| Tip/Ring Open,            | I <sub>VBAT</sub> | $V_R$ or $V_T$ = Hi-Z,                   | _   | 1.5   | _   | mA   |

| On-hook                   |                   | Automatic Power Save Mode Disabled       |     |       |     |      |

| Parameter               | Symbol            | Test Condition                           | Min | Тур               | Max | Unit |

|-------------------------|-------------------|------------------------------------------|-----|-------------------|-----|------|

| Supply Currents:        | I <sub>DD</sub>   | V <sub>TR</sub> =48 V                    | _   | 51.22             | _   | mA   |

| Forward/Reverse OHT,    | I <sub>VBAT</sub> |                                          | _   | 3                 | _   | mA   |

| On-hook                 |                   |                                          |     |                   |     |      |

| Supply Currents:        | I <sub>DD</sub>   | $I_{LOOP}$ = 20 mA, $R_{LOAD}$ = 200 $Ω$ | _   | 51.71             | _   | mA   |

| Forward/Reverse Active, | I <sub>VBAT</sub> |                                          | _   | 2.2 +             | _   | mA   |

| Off-hook                |                   |                                          |     | I <sub>LOOP</sub> |     |      |

| Supply Currents:        | I <sub>DD</sub>   | $V_{TR}$ = 55 $V_{RMS}$ + 0 $V_{DC}$ ,   | _   | 37.07             | _   | mA   |

| Ringing                 | I <sub>VBAT</sub> | low power ringing, sinusoidal, f = 20 Hz | _   | 33.32             | _   | mA   |

|                         |                   | R <sub>LOAD</sub> = 5 REN = 1400 Ω       |     |                   |     |      |

- 1. All specifications are for a single channel of Si3229x with a low-cost capacitive boost dc-dc converter at 25 °C.  $V_{DDA} = V_{DDD} = 3.3 \text{ V}$ ;  $V_{DC} = 12 \text{ V}$ .

- $2.\,I_{DD}=I_{DDA}+I_{DDD}.$

Table 3.3. AC Characteristics

| Parameter                                                        | Test Condition                                       | Min                                                                                                                   | Тур | Max | Unit |  |

|------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----|-----|------|--|

| TX/RX Performance                                                |                                                      |                                                                                                                       |     |     |      |  |

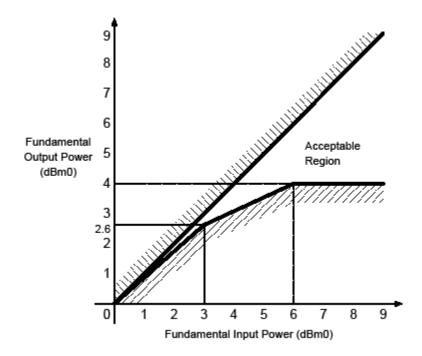

| Overload Compression                                             | 2-Wire - PCM                                         | See Figure 3.6 Overload Compression Performance on page 16.                                                           | _   | _   | _    |  |

| Single Frequency Distortion                                      | 200 Hz to 3.4 kHz (u-law/A-law)                      | _                                                                                                                     | _   | -40 | dBm0 |  |

| (0 dBm0 input)                                                   | 200 Hz to 3.4 kHz (16-bit linear)                    | _                                                                                                                     | _   | -63 | dBm0 |  |

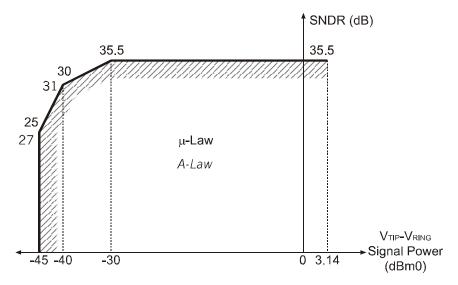

| Signal-to-(Noise + Distortion) Ratio <sup>1</sup>                | 200 Hz to 3.4 kHz transmit or receive path           | See Figure<br>3.5 Transmit<br>and Receive<br>Path SNDR<br>on page 16.                                                 | _   | _   | _    |  |

| Audio Tone Generator Signal-to-<br>Distortion Ratio <sup>1</sup> | 0 dBm0, Active off-hook, and OHT, any Z <sub>T</sub> | 46                                                                                                                    | _   | _   | dB   |  |

| Intermodulation Distortion                                       |                                                      | _                                                                                                                     | _   | -41 | dB   |  |

| Gain Accuracy <sup>1</sup>                                       | 2-Wire to PCM or PCM to 2-Wire                       | _                                                                                                                     | _   | _   | _    |  |

|                                                                  | 1014 Hz, any gain setting                            | _                                                                                                                     | _   | _   | _    |  |

|                                                                  |                                                      | -0.2                                                                                                                  | _   | 0.2 | dB   |  |

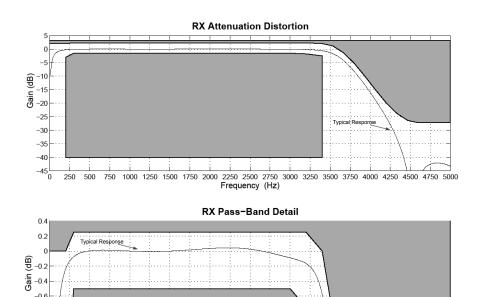

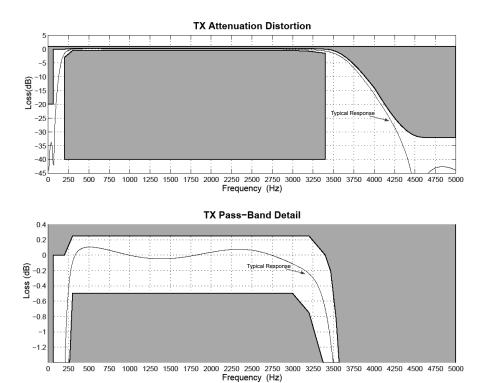

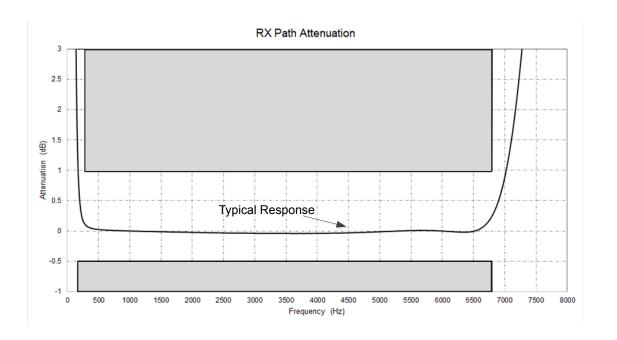

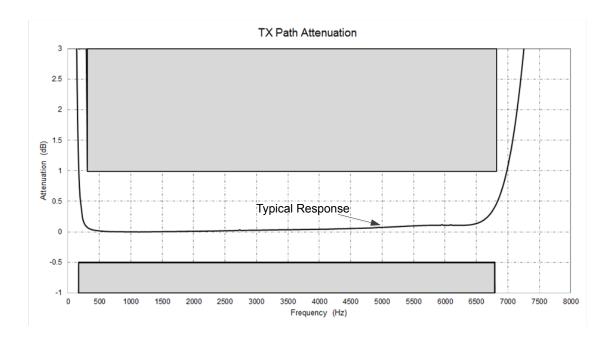

| Attenuation Distortion vs. Freq.                                 | 0 dBm 0 <sup>5</sup>                                 | See Figure 3.7 Receive Path Frequency Response on page 17 and Figure 3.8 Transmit Path Frequency Response on page 17. |     |     |      |  |

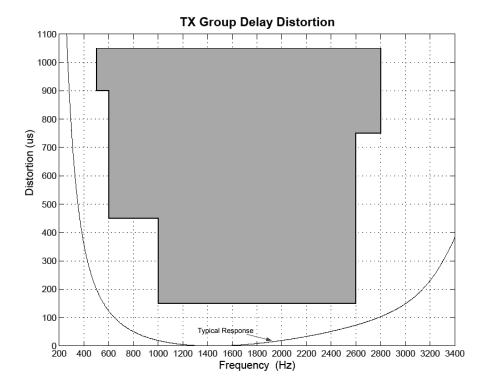

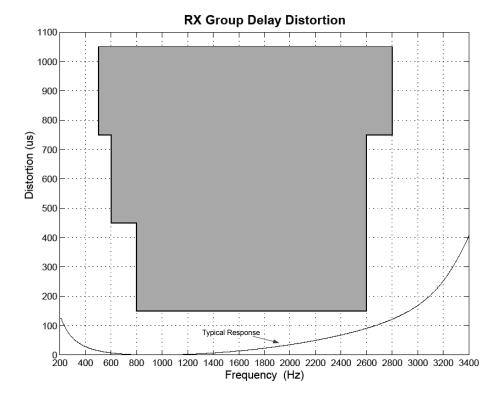

| Group Delay vs. Frequency                                        |                                                      | See Figure 3.9 Transmit Group Delay Distortion on page 18 and Figure 3.10 Receive Group Delay Distortion on page 18.  |     |     |      |  |

| Parameter                                             | Test Condition                             | Min | Тур | Max  | Unit  |

|-------------------------------------------------------|--------------------------------------------|-----|-----|------|-------|

| Gain Tracking <sup>2</sup>                            | 1014 Hz sine wave, reference level -10 dBm | _   | _   | _    | _     |

|                                                       | Signal level:                              |     |     |      |       |

|                                                       | 3 dB to -37 dB                             | _   | _   | 0.25 | dB    |

|                                                       | –37 dB to -50 dB                           | _   | _   | 0.5  | dB    |

|                                                       | –50 dB to -60 dB                           | _   | _   | 1.0  | dB    |

| Round-Trip Group Delay                                | 1014 Hz, Within same time-slot             | _   | 450 | 500  | μs    |

| 2-Wire Return Loss <sup>3</sup>                       | 200 Hz to 3.4 kHz                          | 26  | 30  | _    | dB    |

| Transhybrid Balance <sup>3</sup>                      | 300 Hz to 3.4 kHz                          | 26  | 30  | _    | dB    |

| Noise Performance                                     |                                            |     | l   | I    | l     |

| Idle Channel Noise <sup>4</sup>                       | C-Message weighted                         | _   | 8   | 14   | dBrnC |

|                                                       | Psophometric weighted                      | _   | -82 | -76  | dBmP  |

| PSRR from V <sub>DDD</sub> , V <sub>DDA @ 3.3 V</sub> | RX and TX, 200 Hz to 3.4 kHz               | _   | 55  | _    | dB    |

| Longitudinal Performance                              |                                            |     | l   | I    | l     |

| Longitudinal to Metallic/PCM Bal-                     | 200 Hz to 1 kHz                            | _   | 60  | _    | dB    |

| ance (forward or reverse)                             | 1 kHz to 3.4 kHz                           | _   | 58  | _    | dB    |

| Longitudinal Impedance                                | 200 Hz to 3.4 kHz at TIP or RING           | _   | 50  | _    | Ω     |

| Longitudinal Current Capability                       | Active off-hook 60 Hz<br>Reg 73 = 0x0B     | _   | 25  | _    | mA    |

- 1. Analog signal measured as  $V_{\text{TIP}}$   $V_{\text{RING}}$ . Assumes ideal line impedance matching.

- 2. The quantization errors inherent in the  $\mu$ /A-law companding process can generate slightly worse gain tracking performance in the signal range of 3 to -37 dB for signal frequencies that are integer divisors of the 8 kHz PCM sampling rate.

- $3. V_{DDD}, V_{DDA} = 3.3 V, V_{BAT} = -52 V,$  no fuse resistors;  $R_L = 600 \Omega, Z_S = 600 \Omega$  synthesized using RS register coefficients.

- 4. The level of any unwanted tones within the bandwidth of 0 to 4 kHz does not exceed -55 dBm.

- 5.0 dBm0 is equal to 0 dBm into 600  $\Omega.\,$

**Table 3.4. Linefeed Characteristics**

| Parameter                                               | Symbol            | Test Condition                                                               | Min | Тур | Max | Unit |

|---------------------------------------------------------|-------------------|------------------------------------------------------------------------------|-----|-----|-----|------|

| DC Feed Current                                         |                   | Differential                                                                 | _   | _   | 45  | mA   |

|                                                         |                   | Common Mode                                                                  | _   | _   | 30  | mA   |

|                                                         |                   | Differential + Common Mode                                                   | _   | _   | 45  | mA   |

| DC Loop Current Accuracy                                |                   | I <sub>LIM</sub> = 18 mA                                                     | _   | _   | 10  | %    |

| DC Open Circuit Voltage Accuracy                        |                   | Active Mode; V <sub>OC</sub> = 48 V,<br>V <sub>TIP</sub> – V <sub>RING</sub> | _   | _   | 4   | V    |

| DC Differential Output Resistance                       | R <sub>DO</sub>   | I <sub>LOOP</sub> < I <sub>LIM</sub>                                         | 160 | _   | 640 | Ω    |

| DC On-Hook Voltage Accuracy-<br>Ground Start (TIP Open) | V <sub>OHTO</sub> | $I_{RING} < I_{LIM}$ ; $V_{RING}$ wrt ground,<br>$V_{RING} = -51 \text{ V}$  | _   | _   | 4   | V    |

| Parameter                                       | Symbol               | Test Condition                                                                                | Min | Тур  | Max | Unit            |

|-------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------|-----|------|-----|-----------------|

| DC Output Resistance-Ground<br>Start (TIP Open) | R <sub>ROTO</sub>    | I <sub>RING</sub> <i<sub>LIM;<br/>RING to ground</i<sub>                                      | 160 | _    | 640 | Ω               |

| DC Output Resistance-Ground<br>Start (TIP Open) | R <sub>TOTO</sub>    | TIP to ground                                                                                 | 400 | _    | _   | kΩ              |

| Loop Closure Detect Threshold Accuracy          |                      | I <sub>THR</sub> = 13 mA                                                                      | _   | _    | 10  | %               |

| Ground Key Detect Threshold Accuracy            |                      | I <sub>THR</sub> = 13 mA                                                                      | _   | _    | 10  | %               |

| Ring Trip Threshold Accuracy                    |                      | AC detection, V <sub>RING</sub> = 70 Vpk,<br>no offset,<br>I <sub>TH</sub> = 80 mA            | _   | _    | 4   | mA              |

|                                                 |                      | DC detection, 20 V dc offset, I <sub>TH</sub> = 13 mA                                         | _   | _    | 1   | mA              |

|                                                 |                      | DC Detection, 48 V DC offset, $R_{loop}$ = 1500 $\Omega$                                      | _   | _    | 3   | mA              |

| Ringing Amplitude                               | V <sub>RINGING</sub> | Open circuit, V <sub>BAT</sub> = -140 V                                                       | _   | -138 | _   | V <sub>PK</sub> |

| Sinusoidal Ringing Total Harmonic Distortion    | R <sub>THD</sub>     | 50 V <sub>RMS</sub> , 0 V <sub>OFFSET</sub> , 0–5 REN                                         | _   | 1    | _   | %               |

| Ringing Frequency Accuracy                      |                      | f = 16 Hz to 60 Hz                                                                            | _   | _    | 1   | %               |

| Ringing Cadence Accuracy                        |                      | Accuracy of ON/OFF times                                                                      | _   | _    | 50  | ms              |

| Loop Voltage Sense Accuracy                     |                      | V <sub>TIP</sub> - V <sub>RING</sub> = 48 V                                                   | _   | 2    | 4   | %               |

| Loop Current Sense Accuracy                     |                      | I <sub>LOOP</sub> = 18 mA                                                                     | _   | 7    | 10  | %               |

| Power Alarm Threshold Accuracy                  |                      | Power Threshold = 1.0 W<br>$V_{BAT}$ = -56 V, $I_{VDD}$ = 40 mA,<br>$R_{LOAD}$ = 600 $\Omega$ | _   | 15   | _   | %               |

Table 3.5. Digital I/O Characteristics

| Parameter                                      | Symbol          | Test Condition                                                     | Min                   | Тур | Max | Unit |

|------------------------------------------------|-----------------|--------------------------------------------------------------------|-----------------------|-----|-----|------|

| High Level Input Voltage                       | V <sub>IH</sub> | SCLK, CSB, SPI_MOSI, PCLK, FSYNC, PCM_MOSI, RSTB                   | 2.0                   | _   | _   | V    |

| Low Level Input Voltage                        | V <sub>IL</sub> | SCLK, CSB, SPI_MOSI, PCLK, FSYNC, PCM_MOSI, RSTB                   | _                     |     | 0.8 | V    |

| High Level Output Voltage                      | V <sub>OH</sub> | SPI_MISO, SPI_MOSI_THRU,<br>PMC_MISO, INTB: I <sub>O</sub> = -4 mA | V <sub>DDD</sub> -0.6 | _   | _   | V    |

| Low Level Output Voltage                       | V <sub>OL</sub> | SPI_MISO, SPI_MOSI_THRU,<br>PMC_MISO, INTB: I <sub>O</sub> = 4 mA  | _                     | _   | 0.4 | V    |

| SPI_MOSI_THRU and RSTB Internal Pullup Current |                 |                                                                    | 33                    | 42  | 80  | μА   |

| Input Leakage Current                          | ΙL              |                                                                    | _                     | _   | 10  | μΑ   |

Table 3.6. Charge Pump Characteristics

| Parameter                          | Symbol | Test Condition | Min                         | Тур | Max                  | Unit |

|------------------------------------|--------|----------------|-----------------------------|-----|----------------------|------|

| Output Voltage (DCDRVa/b, DCFFa/b) | VCP    |                | 2 x V <sub>DDD</sub> –<br>1 | _   | 2 x V <sub>DDD</sub> | V    |

| Output Current                     | ICP    |                | _                           | _   | 3 <sup>1</sup>       | mA   |

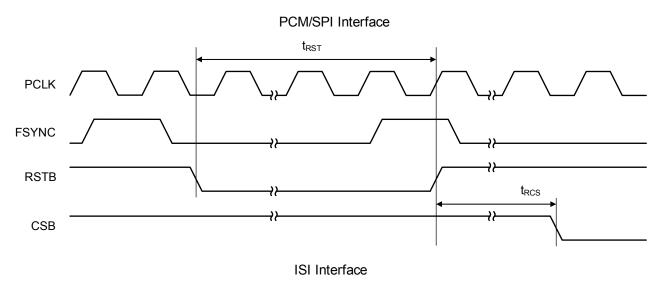

Table 3.7. Switching Characteristics General Inputs

| Parameter                                                                                                    | Symbol           | Min | Тур | Max | Unit |

|--------------------------------------------------------------------------------------------------------------|------------------|-----|-----|-----|------|

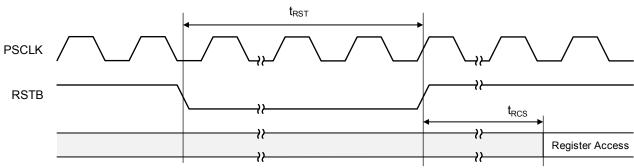

| RSTB Pulse Width (PCM/SPI or ISI Interface)                                                                  | t <sub>RST</sub> | 200 | _   | _   | μs   |

| RSTB High to First SPI Transfer<br>Start (PCM/SPI Interface) or First<br>Register/RAM Access (ISI Interface) | t <sub>RCS</sub> | 5   |     | _   | ms   |

#### Note:

1. All timing is referenced to the 50% level of the waveform. Input test levels are  $V_{IH} = V_{DD} - 0.4 \text{ V}$ ,  $V_{IL} = 0.4 \text{ V}$ . Rise and Fall times are referenced to the 20% and 80% levels of the waveform.

Figure 3.1. Reset Timing Diagram

<sup>1.</sup> Peak drive current capability is >60 mA.

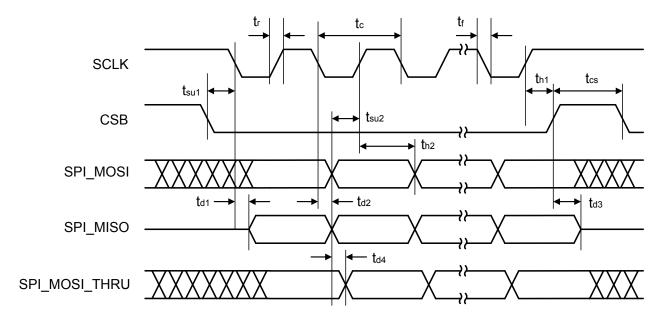

Table 3.8. Switching Characteristics SPI

| Parameter                                    | Symbol           | Min | Тур | Max | Unit |

|----------------------------------------------|------------------|-----|-----|-----|------|

| Cycle Time SCLK                              | t <sub>c</sub>   | 83  | _   | _   | ns   |

| Rise Time, SCLK                              | t <sub>r</sub>   | _   | _   | 25  | ns   |

| Fall Time, SCLK                              | t <sub>f</sub>   | _   | _   | 25  | ns   |

| Delay Time, SCLK Fall to SPI_MISO Active     | t <sub>d1</sub>  | _   | _   | 20  | ns   |

| Delay Time, SCLK Fall to SPI_MISO Transition | t <sub>d2</sub>  | _   | _   | 20  | ns   |

| Delay Time, CSB Rise to SPI_MISO Tristate    | t <sub>d3</sub>  | _   | _   | 20  | ns   |

| Setup Time, CSB Fall to SCLK Fall            | t <sub>su1</sub> | 25  | _   | _   | ns   |

| Hold Time, CSB Rise to SCLK Rise             | t <sub>h1</sub>  | 20  | _   | _   | ns   |

| Setup Time, SPI_MOSI Transition to SCLK Rise | t <sub>su2</sub> | 25  | _   | _   | ns   |

| Hold Time, SCLK Rise to SPI_MOSI Transition  | t <sub>h2</sub>  | 20  | _   | _   | ns   |

| Delay Time between Chip Selects              | t <sub>cs</sub>  | 220 | _   | _   | ns   |

| SPI_MOSI to SPI_MOSI_THRU Propagation Delay  | t <sub>d4</sub>  | _   | 4   | 10  | ns   |

- 1. All timing is referenced to the 50% level of the waveform. Input test levels are  $V_{IH}$  =  $V_{DDD}$  -0.4 V,  $V_{IL}$  = 0.4 V.

- 2. Characteristics for outputs specified with CL = 20 pF.

Figure 3.2. SPI Timing Diagram

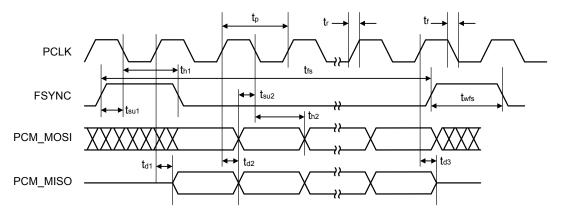

Table 3.9. Switching Characteristics PCM Highway Interface

| Parameter                                               | Symbol              | Min <sup>2</sup> | Typ <sup>2</sup> | Max <sup>2</sup>   | Unit              |

|---------------------------------------------------------|---------------------|------------------|------------------|--------------------|-------------------|

| PCLK Period                                             | tp                  | 122              | _                | 1953               | ns                |

| PCLK Jitter Tolerance                                   | t <sub>jitter</sub> | _                | _                | 8                  | ns <sub>RMS</sub> |

| Valid PCLK Inputs <sup>3</sup>                          |                     | _                | 512              | _                  | kHz               |

|                                                         |                     |                  | 768              |                    | kHz               |

|                                                         |                     |                  | 1.024            |                    | MHz               |

|                                                         |                     |                  | 1.536            |                    | MHz               |

|                                                         |                     |                  | 1.544            |                    | MHz               |

|                                                         |                     |                  | 2.048            |                    | MHz               |

|                                                         |                     |                  | 4.096            |                    | MHz               |

|                                                         |                     |                  | 8.192            |                    | MHz               |

| FSYNC Period <sup>4</sup>                               | $t_fs$              | _                | 125              | _                  | μs                |

| PCLK Duty Cycle Tolerance                               | t <sub>dty</sub>    | 40               | 50               | 60                 | %                 |

| FSYNC Jitter Tolerance <sup>5</sup>                     | t <sub>jitter</sub> | _                | _                | ±120               | ns                |

| Rise Time, PCLK                                         | t <sub>r</sub>      | _                | _                | 25                 | ns                |

| Fall Time, PCLK                                         | t <sub>f</sub>      | _                | _                | 25                 | ns                |

| Delay Time, PCLK Rise to PCM_MISO Active                | t <sub>d1</sub>     | _                | _                | 20                 | ns                |

| Delay Time, PCLK Rise to PCM_MISO Transition            | t <sub>d2</sub>     | _                | _                | 20                 | ns                |

| Delay Time, PCLK Rise to PCM_MISO Tristate <sup>6</sup> | t <sub>d3</sub>     | _                | _                | 20                 | ns                |

| Setup Time, FSYNC Rise to PCLK Fall                     | t <sub>su1</sub>    | 25               | _                | _                  | ns                |

| Hold Time, PCLK Fall to FSYNC Fall                      | t <sub>h1</sub>     | 20               | _                | _                  | ns                |

| Setup Time, PCM_MOSI Transition to PCLK Fall            | t <sub>su2</sub>    | 25               | _                | _                  | ns                |

| Hold Time, PCLK Fall to PCM_MOSI Transition             | t <sub>h2</sub>     | 20               | _                | _                  | ns                |

| FSYNC Pulse Width                                       | t <sub>wfs</sub>    | t <sub>p</sub>   | _                | t <sub>p</sub> x 8 | μs                |

- 1. Characteristics for outputs specified with CL = 20 pF.

- 2. All timing is referenced to the 50% level of the waveform. Input test levels are  $V_{IH} = V_{DDD} 0.4 \text{ V}$ ,  $V_{IL} = 0.4 \text{ V}$ .

- 3. A constant PCLK and FSYNC are required.

- 4. FSYNC source is assumed to be 8 kHz under all operating conditions.

- 5. FSYNC Jitter Tolerance relative to PCLK.

- 6. Specification applies to PCLK fall to DTX tristate when that mode is selected.

Figure 3.3. PCM Highway Interface Timing Diagram

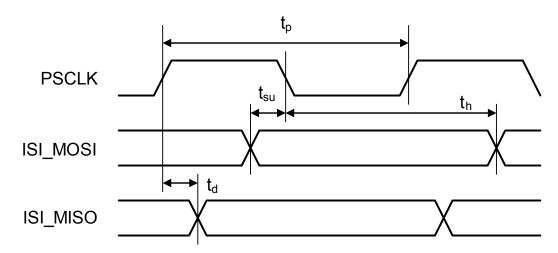

Table 3.10. Switching Characteristics ISI

| Parameter                                     | Symbol          | Min | Тур   | Max | Unit |

|-----------------------------------------------|-----------------|-----|-------|-----|------|

| Setup Time, ISI_MOSI Transition to PSCLK Fall | t <sub>su</sub> | 7.5 | _     | _   | ns   |

| Hold Time, PSCLK Fall to ISI_MOSI Transition  | t <sub>h</sub>  | 5   | _     | _   | ns   |

| Delay Time, PSCLK Rise to ISI_MISO Transition | t <sub>d</sub>  | _   | _     | 16  | ns   |

| PSCLK Period                                  | t <sub>p</sub>  | _   | 40.69 | _   | ns   |

| PSCLK Duty Cycle                              |                 | 40  | 50    | 60  | %    |

1. Timing should be guaranteed by ISI-enabled host SoC.

Figure 3.4. ISI Timing Diagram

**Table 3.11. Thermal Conditions**

| Parameter                                                     | Symbol           | Test Condition | Value      | Unit |

|---------------------------------------------------------------|------------------|----------------|------------|------|

| Storage Temperature Range                                     | T <sub>STG</sub> |                | -55 to 150 | °C   |

| Thermal Resistance, Typical <sup>1</sup>                      | $\theta_{JA}$    |                | 27.0       | °C/W |

| QFN-68                                                        | $\theta_{JB}$    |                | 4.2        | °C/W |

|                                                               | $\theta_{JC}$    |                | 11.3       | °C/W |

| Maximum Junction Temperature, (High Voltage Die) <sup>3</sup> | T <sub>JHV</sub> | Continuous     | 145        | °C   |

| Maximum Junction Temperature                                  | T <sub>JLV</sub> | Continuous     | 125        | °C   |

| (Low Voltage Die) <sup>2</sup>                                |                  |                |            |      |

- 1. The thermal resistance of an exposed pad package is assured when the recommended printed circuit board layout guidelines are followed correctly. The specified performance requires that the exposed pad be soldered to an exposed copper surface of at least equal size and that multiple vias are added to enable heat transfer between the top-side copper surface and a large internal/bottom copper plane. Thermal resistance values are based on JEDEC thermal test standard JESD1.

- 2. Operation of the Si3229x above 125 °C junction temperature may degrade device reliability.

- 3. Si3229x linefeed is equipped with on-chip thermal limiting circuitry that shuts down the circuit when the junction temperature exceeds the thermal shutdown threshold. The thermal shutdown threshold is normally set to 145 °C; when in the ringing state the thermal shutdown is set to 200 °C.

Table 3.12. Absolute Maximum Ratings

| Parameter              | Symbol                               | Value                 | Unit |

|------------------------|--------------------------------------|-----------------------|------|

| Supply Voltage         | $V_{DDA,}V_{DDD}$                    | -0.5 to 4.0           | V    |

| Digital Input Voltage  | V <sub>IND</sub>                     | -0.5 to 4.0           | V    |

| Battery Supply Voltage | V <sub>BAT</sub>                     | +0.4 to -142          | V    |

| Tip or Ring Voltage    | V <sub>TIP</sub> , V <sub>RING</sub> | V <sub>BAT</sub> -0.4 | V    |

| TIP, RING Current      | I <sub>TIP</sub> , I <sub>RING</sub> | ±100                  | mA   |

#### Note:

1. Permanent device damage may occur or the reliability of the device may be affected if the device is operated at or above the absolute maximum ratings.

Figure 3.5. Transmit and Receive Path SNDR

Figure 3.6. Overload Compression Performance

-0.8

Figure 3.7. Receive Path Frequency Response

750 1000 1250 1500 1750 2000 2250 2500 2750 3000 3250 3500 3750 4000 4250 4500 4750 5000 Frequency (Hz)

Figure 3.8. Transmit Path Frequency Response

Figure 3.9. Transmit Group Delay Distortion

Figure 3.10. Receive Group Delay Distortion

Figure 3.11. Wideband Audio RX Path

Figure 3.12. Wideband Audio TX Path

#### 4. FXS Features

#### 4.1 DC Feed Characteristics

ProSLIC internal linefeed circuitry provides completely programmable dc feed characteristics.

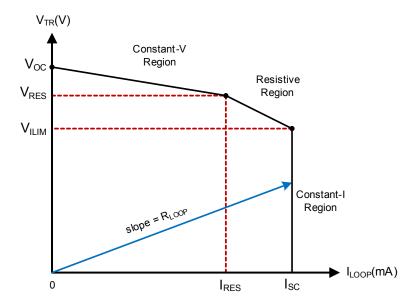

When in the active state, the ProSLIC operates in one of three dc linefeed operating regions: a constant-voltage region, a constant-current region, or a resistive region, as shown in the figure below. The constant-voltage region has a low resistance, typically 160  $\Omega$ . The constant-current region approximates infinite resistance.

Figure 4.1. Dual ProSLIC DC Feed Characteristics

#### 4.2 Linefeed Operating States

The linefeed interface includes eight different register-programmable operating states as listed in Table 4.1 Linefeed Operating States on page 21. The open state is the default condition in the absence of any preloaded register settings. The device may also automatically enter the open state in the event of a linefeed fault condition.

#### 4.3 Line Voltage and Current Monitoring

The ProSLIC continuously monitors the TIP, RING, and battery voltages and currents via an on-chip Monitor ADC and stores the resulting values in individual RAM locations. Additionally, VTIP, VRING, loop current, and longitudinal current values are calculated based on the differential and common mode voltage measurements. The ADC updates all registers at a rate of 2 kHz or greater.

#### 4.4 Power Monitoring and Power Fault Detection

The Si3229x line monitoring functions are used to continuously protect against excessive power conditions.

If the Si3229x detects an overpower condition, it automatically sets that line to the open state and generates a "power alarm" interrupt.

The interrupt can be masked, but masking the automatic transition to open is not recommended.

#### 4.5 Thermal Overload

If the die temperature exceeds the maximum junction temperature threshold (TJmax) of 145 or 200 °C, depending on the operating state, the device has the ability to shut itself down to a low-power state without user intervention. A thermal alarm interrupt is generated to notify host that the device has been switched to open state.

**Table 4.1. Linefeed Operating States**

| Linefeed State                   | Description                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Open                             | Output is high-impedance, and audio is not transmitted. This is the default state after powerup or following a hardware reset. This state can also be used in the presence of line fault conditions and to generate open switch intervals (OSIs). This state is used in line diagnostics mode as a high impedance state during linefeed testing. A power fault condition may also force the device into the open state. |

| Forward Active<br>Reverse Active | Linefeed circuitry is active, and audio is active when off hook. In Forward Active state, the TIP lead is more positive than the RING lead; in Reverse Active state, the RING lead is more positive than the TIP lead.                                                                                                                                                                                                  |

| Forward OHT<br>Reverse OHT       | Provides data transmission during an on-hook loop condition (e.g., transmitting caller ID data between ringing bursts). Linefeed circuitry and audio are active. In Forward OHT state, the TIP lead is more positive than the RING lead; in Reverse OHT state, the RING lead is more positive than the TIP lead.                                                                                                        |

| TIP Open                         | Provides an active linefeed on the RING lead and sets the TIP lead to high impedance (>400 k $\Omega$ ) for ground start operation in forward polarity. Loop closure and ground key detect circuitry are active.                                                                                                                                                                                                        |

| RING Open                        | Provides an active linefeed on the TIP lead and sets the RING lead to high impedance (>400 k $\Omega$ ) for ground start operation in reverse polarity. Loop closure and ground key detect circuitry are active.                                                                                                                                                                                                        |

| Ringing                          | Drives programmable ringing signal onto TIP and RING leads with or without dc offset.                                                                                                                                                                                                                                                                                                                                   |

#### 4.6 Loop Closure/Ring Trip Detection

The Si3229x provides a completely programmable loop closure detection mechanism. The loop closure detection scheme provides two thresholds to allow hysteresis, and also includes a programmable debounce filter to eliminate false detection. A loop closure detect status bit provides continuous status, and a maskable interrupt bit is also provided.

# 4.7 Ground Key Detection

The Si3229x provides a ground key detect mechanism using a programmable architecture similar to the loop closure scheme. The ground key detect scheme provides two thresholds to allow hysteresis and also includes a programmable debounce filter to eliminate false detection. A ground key detect status bit provides continuous status, and a maskable interrupt bit is also provided.

#### 4.8 Ringing Generation

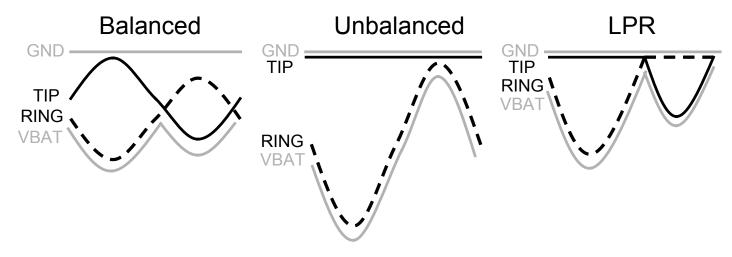

The Si3229x supports the patented Low-Power Ringing (LPR) method exclusively, which when used with a tracking battery scheme, maximizes the ringing power transferred to the load and reduces overall power consumption. The figure below illustrates the fundamental differences between LPR and the traditional balanced or unbalanced ringing. Ringing is fully programmable including frequency, amplitude, dc offset, wave shape, and crest factor. The Si3229x also supports automatic ring cadencing and ringtrip detection (ac and dc). Smart ringing is available on the Si32295 and the Si32297 to reduce the cost of ac-dc power adapters. Smart ringing reduces the peak current required by ringing the two channels out-of-phase with each other. Devices with smart ringing do not support fast ring-start.

Figure 4.2. Low Power Ringing

#### 4.9 Polarity Reversal

The Si3229x supports polarity reversal for message waiting and various other signaling modes. The ramp rate can be programmed for a smooth or abrupt transition to accommodate different application requirements.

#### 4.10 Two-Wire Impedance Synthesis

The ac two-wire impedance synthesis is generated on-chip using a DSP-based scheme to optimally match the output impedance of the Si3229x to the reference impedance. Most real or complex two-wire impedances can be generated with appropriate register coefficients.

#### 4.11 Transhybrid Balance Filter

The trans-hybrid balance function is implemented on-chip using a DSP-based scheme to effectively cancel the reflected receive path signal from the transmit path.

#### 4.12 Tone Generators

The Si3229x includes two digital tone generators that allow a wide variety of single- or dual-tone frequency and amplitude combinations. Each tone generator has its own set of registers that hold the desired frequency, amplitude, and cadence to allow the generation of DTMF and call progress tones for different requirements. The tones can be directed to either receive or transmit paths.

#### 4.13 DTMF Detection (Si32291/3/5/7 Only)

The Dual ProSLIC performs DTMF detection. An interrupt can be enabled to report a DTMF detection.

#### 4.14 Pulse Metering

The pulse metering system for the Si3229x is designed to inject a 12 or 16 kHz billing tone into the audio path with maximum amplitude of 0.85 VRMS at TIP and RING into a 200  $\Omega$  ac load impedance. The tone is generated in the DSP via a table lookup that guarantees spectral purity by not allowing drift. The tone will ramp up until it reaches a host-programmed threshold, at which point it will maintain that level until instructed to ramp down, thus creating a trapezoidal envelope.

The amplitude is controlled by an automatic gain control circuit (AGC). While the tone is ramping up, the AGC takes the feedback audio and applies it to a band pass filter, which is programmed for the 12 or 16 kHz frequency of interest. When the peak is detected, the ramp is stopped.

#### 4.15 DC-DC Controller

The Si3229x integrates two dc-dc controllers that can be used to control external dc-dc converters to generate high voltage supplies to the SLIC channels.

The integrated line feeds are designed to work with a single tracking high voltage input, one for each channel.

The Vbat voltage for each channel is optimized to minimize power consumption by closely tracking the SLIC state, even tracking the ringing waveforms.

Both of the dc-dc controller outputs DCDRVa/b are driven by an internal charge pump which allows them to connect directly to the gate of the MOSFET switch of a dc-dc converter. This connection eliminates the need for external MOSFET pre-drive circuitry, even when VTH is greater than VDD. The Si3229x can use a capacitive ultra boost tracking battery supply for lower power, cost, and footprint compared to other tracking or shared battery supplies in the industry. See Table 3.6 Charge Pump Characteristics on page 11.

#### 4.16 Wideband Audio

The Si3229x supports wideband audio (150Hz—6.8 kHz) compliant with PKT-SP-HDV-104-120823, and is configurable to support the full ITU-T-G.722-201209 bandwidth (50Hz–7 kHz).

#### 4.17 Test Facilities

The Si3229x supports a rich set of metallic loop tests to diagnose external faults, as well as a set of inward self-tests to support diagnostics of the Si3229x-based voice port. Implementation of metallic loop tests requires the ProSLIC<sup>TM</sup> MLT API, while the inward self-tests are included in the standard SimpleVoice API.

**Table 4.2. Supported Tests**

| Test                 | Description                                                                                                                                                   |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Metallic Loop Tests  |                                                                                                                                                               |

| Voltages             | Measures ac and dc voltages from T-R, T-G, and R-G.                                                                                                           |

| Receiver Off-hook    | Discriminates between resistive fault and off-hook terminating device.                                                                                        |

| REN                  | Measures Ringer Equivalence Number (REN).                                                                                                                     |

| REN Capacitance      | Measures T-R capacitance of on-hook load.                                                                                                                     |

| Capacitance          | Measures 3-Terminal Capacitance.                                                                                                                              |

| Resistance           | Measures resistance from T-R, T-G, or R-G.                                                                                                                    |

| Inward Self-Tests    |                                                                                                                                                               |

| PCM Loopback         | Configures Si3229x for 8- or 16-bit PCM loopback.                                                                                                             |

| DC Feed              | Verify dc Feed I/V and loop closure using integrated test load.                                                                                               |

| Ringing and Ringtrip | Verify ringing voltage (ac and dc). Optional ringtrip check to support system level signaling verification.                                                   |

| Battery              | Verify VBAT.                                                                                                                                                  |

| Audio Gain           | Measure gain of RX (host to line) and TX (line to host) paths without using an external load, test equipment, or requiring the host to provide audio samples. |

In addition to these specific test suites, the user is free to use the general test facilities listed in the following table:

Table 4.3. General Test Facilities

| Test                     | Description                                                                                                 |

|--------------------------|-------------------------------------------------------------------------------------------------------------|

| Monitor ADC              | Provides TIP/RING voltages (inside and outside overcurrent protection), TIP/RING currents and VBAT voltage. |

| Audio Diagnostic Filters | Three cascaded second-order Biquad filters with peak hold and averaging capabilities.                       |

| Loopback Modes           | Digital and analog loopback modes to isolate portions of the audio path.                                    |

| Tone Generators          | The dual-tone generators may be used as general-purpose test signal generators.                             |

# 5. System Interfaces

#### 5.1 SPI Control Interface

The controller interface to the Si32292/3/7 is a 4-wire interface modeled after microcontroller and serial peripheral devices. The interface consists of a clock (SCLK), chip select (CSB), serial data input (SPI\_MOSI), and serial data output (SPI\_MISO). In addition, the ProSLIC devices feature a serial data through output (SPI\_MOSI\_THRU) to support operation of up to 32 channels using a single chip select line. The device operates with both 8-bit and 16-bit SPI controllers.

#### 5.2 PCM Interface and Companding

The Si32292/3/7 contains a flexible, programmable interface for the transmission and reception of digital PCM samples. PCM data transfer is controlled by the PCM clock (PCLK) and frame sync (FSYNC) inputs as well as the PCM Mode Select, PCM Transmit Start, and PCM Receive Start settings.

The interface can be configured to support from 8 to 128 8-bit time slots in each 125 µs frame, corresponding to a PCM clock (PCLK) frequency range of 512 kHz to 8.192 MHz. 1.544 MHz is also supported.

The Si3229x supports both  $\mu$ -255 Law ( $\mu$ -Law) and A-law companding formats in addition to 16-bit linear data mode with no companding.

#### 5.3 Integrated Serial Interface

The Si32290/1/5 devices' integrated serial interface (ISI) is a three-wire proprietary interface which serializes SPI and PCM communications and interrupts, reducing the SoC interface from nine wires to three (PSCLK, ISI\_MISO, ISI\_MOSI). SPI communications and PCM data transfers are embedded in the serial data. The host side of the ISI is integrated onto selected SoCs from several vendors.

ISI is a point to point interface; therefore, it is not possible to daisy-chain more than one ISI ProSLIC device. Both μ-255 Law (μ-Law) and A-law companding formats are supported in addition to 16-bit linear data mode with no companding.

# 6. Pin Descriptions

#### 6.1 Si32290/1/5 ISI 8x8 mm Pinout

| Pin # | Pin Name | Description                                                                                                                   |

|-------|----------|-------------------------------------------------------------------------------------------------------------------------------|

| 1     | NC       | No Connect                                                                                                                    |

|       |          | This pin should be left unconnected.                                                                                          |

| 2     | NC       | No Connect                                                                                                                    |

|       |          | This pin should be left unconnected.                                                                                          |

| 3     | SRINGCa  | RING Coarse Sense Input—Channel A                                                                                             |

|       |          | RING Channel A voltage sensing outside protection circuit.                                                                    |

| 4     | STIPCa   | TIP Coarse Sense Input—Channel A                                                                                              |

|       |          | TIP Channel A voltage sensing outside protection circuit.                                                                     |

| 5     | SRINGDCa | RING DC Sense—Channel A                                                                                                       |

|       |          | Analog dc input used to sense voltage on Channel A RING lead.                                                                 |

| 6     | HVPAD    | Exposed paddle.                                                                                                               |

|       |          | Connect to electrically-isolated low thermal impedance inner layer and/or backside thermal plane using multiple thermal vias. |

| 7     | SRINGACa | RING AC Sense—Channel A                                                                                                       |

|       |          | Analog ac input used to detect voltage on Channel A RING lead.                                                                |

| 8     | GNDPAD   | Exposed paddle.                                                                                                               |

|       |          | Connect to ground.                                                                                                            |

| 9     | STIPACa  | TIP AC Sense—Channel A                                                                                                        |

|       |          | Analog ac input used to detect voltage on Channel A TIP lead.                                                                 |

| 10    | STIPDCa  | TIP DC Sense—Channel A                                                                                                        |

|       |          | Analog dc input used to sense voltage on Channel A TIP lead.                                                                  |

| 11    | CAPPa    | SLIC Stabilization Capacitor—Channel A                                                                                        |

|       |          | Capacitor used in dc feed low-pass filter on channel A.                                                                       |

| 12    | CAPMa    | SLIC Stabilization Capacitor—Channel A                                                                                        |

|       |          | Capacitor used in dc feed low-pass filter on channel A.                                                                       |

| 13    | SVBATa   | VBAT Sense—Channel A                                                                                                          |

|       |          | Input used to sense voltage on Channel A dc-dc converter output voltage lead.                                                 |

| 14    | VDDD     | IC Voltage Supply.                                                                                                            |

|       |          | 3.3 V digital supply for internal digital circuitry.                                                                          |

| 15    | RSTB     | Reset Input                                                                                                                   |

|       |          | Active low input. Hardware reset used to place all control registers in the default state.                                    |

| 16    | NC       | No Connect                                                                                                                    |

|       |          | This pin should be left unconnected.                                                                                          |

| Pin # | Pin Name | Description                                                                            |

|-------|----------|----------------------------------------------------------------------------------------|

| 17    | NC       | No Connect                                                                             |

|       |          | This pin should be left unconnected.                                                   |

| 18    | NC       | No Connect                                                                             |

|       |          | This pin should be left unconnected.                                                   |

| 19    | PSCLK    | ISI Bus Clock Input                                                                    |

|       |          | Clock input for ISI bus timing.                                                        |

| 20    | ISI_MISO | ISI Data Output                                                                        |

|       |          | ISI Master Input, Slave Output. Output data to ISI bus.                                |

| 21    | ISI_MOSI | ISI Data Input                                                                         |

|       |          | ISI Master Output, Slave Input. Input data from ISI bus.                               |

| 22    | SDCHa    | DC Monitor—Channel A                                                                   |

|       |          | DC-DC converter monitor input used to sense switch current in the Channel A converter. |

| 23    | SDCLa    | DC Monitor—Channel A                                                                   |

|       |          | DC-DC converter monitor input used to sense switch current in the Channel A converter. |

| 24    | DCDRVa   | DC Drive—Channel A                                                                     |

|       |          | DC-DC converter control signal output which drives external transistor on Channel A.   |

| 25    | GNDPAD   | Exposed paddle.                                                                        |

|       |          | Connect to ground.                                                                     |

| 26    | DCFF     | DC-DC Charge Pump Output                                                               |

| 27    | DCDRVb   | DC Drive—Channel B                                                                     |

|       |          | DC-DC converter control signal output which drives external transistor on Channel B.   |

| 28    | SDCLb    | DC Monitor—Channel B                                                                   |

|       |          | DC-DC converter monitor input used to sense switch current in the Channel B converter. |

| 29    | SDCHb    | DC Monitor—Channel B                                                                   |

|       |          | DC-DC converter monitor input used to sense switch current in the Channel B converter. |

| 30    | VDDD     | IC Voltage Supply                                                                      |

|       |          | 3.3 V digital supply for internal circuitry.                                           |

| 31    | VDDREG   | Regulated Core Power Supply                                                            |

| 32    | GNDPAD   | Exposed paddle.                                                                        |

|       |          | Connect to ground.                                                                     |

| 33    | NC       | No Connect                                                                             |

|       |          | This pin should be left unconnected.                                                   |

| Pin # | Pin Name | Description                                                                                                                   |

|-------|----------|-------------------------------------------------------------------------------------------------------------------------------|

| 34    | NC       | No Connect                                                                                                                    |

|       |          | This pin should be left unconnected.                                                                                          |

| 35    | NC       | No Connect                                                                                                                    |

|       |          | This pin should be left unconnected.                                                                                          |

| 36    | NC       | No Connect                                                                                                                    |

|       |          | This pin should be left unconnected.                                                                                          |

| 37    | GNDPAD   | Ground                                                                                                                        |

|       |          | Connect to ground.                                                                                                            |

| 38    | SVBATb   | VBAT Sense—Channel B                                                                                                          |

|       |          | Input used to sense voltage on Channel B dc-dc converter output voltage lead.                                                 |

| 39    | CAPMb    | SLIC Stabilization Capacitor—Channel B                                                                                        |

|       |          | Capacitor used in dc feed low-pass filter on channel B.                                                                       |

| 40    | CAPPb    | SLIC Stabilization Capacitor—Channel B                                                                                        |

|       |          | Capacitor used in dc feed low-pass filter on channel B.                                                                       |

| 41    | IREF     | Current Reference Input                                                                                                       |

|       |          | Connects to an external resistor used to provide a high accuracy reference current.                                           |

| 42    | STIPDCb  | TIP DC Sense—Channel B                                                                                                        |

|       |          | Analog dc input used to sense voltage on Channel B TIP lead.                                                                  |

| 43    | STIPACb  | TIP AC Sense—Channel B                                                                                                        |

|       |          | Analog ac input used to detect voltage on Channel B TIP lead.                                                                 |

| 44    | GNDPAD   | Exposed paddle.                                                                                                               |

|       |          | Connect to ground.                                                                                                            |

| 45    | SRINGACb | RING AC Sense—Channel B                                                                                                       |

|       |          | Analog ac input used to detect voltage on Channel B RING lead.                                                                |

| 46    | HVPAD    | Exposed paddle.                                                                                                               |

|       |          | Connect to electrically-isolated low thermal impedance inner layer and/or backside thermal plane using multiple thermal vias. |

| 47    | SRINGDCb | RING DC Sense—Channel B                                                                                                       |

|       |          | Analog dc input used to sense voltage on Channel B RING lead.                                                                 |

| 48    | STIPCb   | TIP Coarse Sense Input—Channel B                                                                                              |

|       |          | TIP Channel B voltage sensing outside protection circuit.                                                                     |

| 49    | SRINGCb  | RING Coarse Sense Input—Channel B                                                                                             |

|       |          | RING Channel B voltage sensing outside protection circuit.                                                                    |

| Pin # | Pin Name | Description                                                                                                                   |

|-------|----------|-------------------------------------------------------------------------------------------------------------------------------|

| 50    | VDDA     | Analog Supply Voltage                                                                                                         |

|       |          | Analog 3.3 V power supply for internal analog circuitry.                                                                      |

| 51    | NC       | No Connect                                                                                                                    |

|       |          | This pin should be left unconnected.                                                                                          |

| 52    | TIPb     | TIP Terminal—Channel B                                                                                                        |

|       |          | Connect to the Channel B TIP lead of the subscriber loop.                                                                     |

| 53    | NC       | No Connect                                                                                                                    |

|       |          | This pin should be left unconnected.                                                                                          |

| 54    | RINGb    | RING Terminal—Channel B                                                                                                       |

|       |          | Connect to the Channel B RING lead of the subscriber loop.                                                                    |

| 55    | NC       | No Connect                                                                                                                    |

|       |          | This pin should be left unconnected.                                                                                          |

| 56    | VBATb    | Battery Voltage Supply—Channel B                                                                                              |