# W5100S

# (W5100S-L & W5100S-Q)

## Version 1.0.0

## W5100S

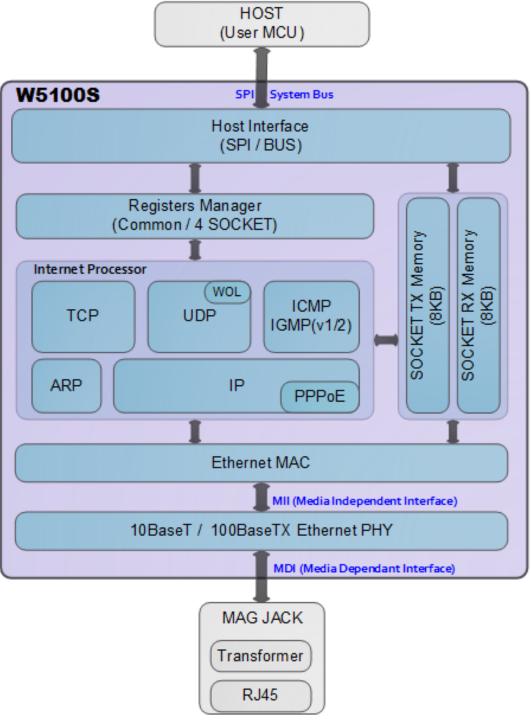

W5100S designed with Hardwired TCP/IP, WIZnet technology, is an embedded Internet Controller Chip. W5100S supporting Full Hardwired, Ethernet MAC (Media Access Control), and 10Base-T/100Base-TX Ethernet PHY is Internet Connectivity One-chip Solution for Internet Protocol (TCP/IP).

With W5100S, Host (User MCU) simply handles variety Internet Protocol such as IPv4, TCP, UDP, ICMP, IGMP, ARP, PPPoE and etc. And W5100S supports each 8KB Memory for Transmit and Receive to minimize using memory on Low-end level Host. Host also independently uses 4 Hardwired SOCKETs to develop vary Internet Applications in each Hardwired SOCKETs.

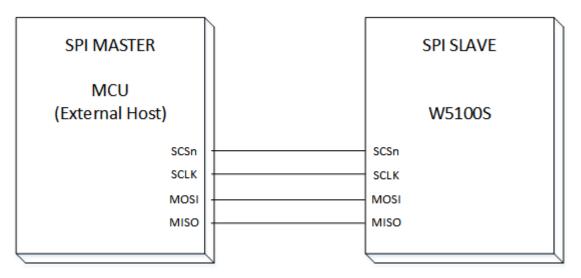

W5100S supports SPI and Parallel System BUS Interface for Host Interface. It also provides Low Power / Low Heat design, WOL (Wake On LAN), Ethernet PHY Power Down Mode and etc.

W5100S is Low-cost chip that improves on W5100. Any Firmware using on W5100 can be used on W5100S without any modification. Also, W5100S has 48 Pin LQFP & QFN Lead-Free Package, smaller than W5100 for product miniaturization.

## Features

- Support Hardwired Internet protocols

- : TCP, UDP, WOL over UDP, ICMP, IGMPv1/v2, IPv4, ARP, PPPoE

- Support 4 independent SOCKETs simultaneously

- Support SOCKET-less command

- : ARP-Request, PING-Request

- Support Ethernet Power down mode & Main Clock gating for power save

- Support Wake on LAN over UDP

- Support Serial & Parallel Host Interface

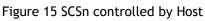

- : High Speed SPI (MODE 0/3), System Bus with 2 Address signal & 8bit Data

- Internal 16Kbytes Memory for TX/ RX Buffers

- 10BaseT/100BaseTX Ethernet PHY Integrated

- Support Auto Negotiation (Full and half duplex, 10 and 100-based )

- Support Auto-MDIX only when Auto-Negotiation mode

- Not support IP Fragmentation

- 3.3V operation with 5V I/O signal tolerance

- Network Indicator LEDs (Full/Half duplex, Link, 10/100 Speed, Active)

- 48 Pin LQFP & QFN Lead-Free Package (7x7mm, 0.5mm pitch)

## **Target Applications**

W5100S is well-suited for many embedded applications, including:

- User product based on W5100 : No modify firmware

- Home Network Devices: Set-Top Boxes, PVRs, Digital Media Adapters

- Serial-to-Ethernet: Access Controls, LED displays, Wireless AP relays, etc.

- Parallel-to-Ethernet: POS / Mini Printers, Copiers

- USB-to-Ethernet: Storage Devices, Network Printers

- GPIO-to-Ethernet: Home Network Sensors

- Security Systems: DVRs, Network Cameras, Kiosks

- Factory, Building, Home Automations

- Medical Monitoring Equipment

- Embedded Servers

- Internet of Thing (IoT) Devices

- IoT Cloud Devices

## **Block Diagram**

Figure 1 Block Diagram

## Contents

| 1 | PIN Desc | iption11                                                       | I |

|---|----------|----------------------------------------------------------------|---|

|   | 1.1      | PIN Description                                                | 2 |

| 2 | Memory   | Лар16                                                          | 5 |

|   | 2.1      | W5100S Registers                                               | 3 |

|   | 2.1.     | Common registers                                               | 3 |

|   | 2.1.     | SOCKET Registers                                               | ) |

| 3 | Register | Descriptions                                                   | 2 |

|   | 3.1      | Common Registers 24                                            | 1 |

|   | 3.1.     | MR (Mode Register) 24                                          | 1 |

|   | 3.1.     | GWR (Gateway IP Address Register) 24                           | 1 |

|   | 3.1.     | SUBR (Subnet Mask Register) 24                                 | 1 |

|   | 3.1.4    | SHAR (Source Hardware Address Register)                        | 5 |

|   | 3.1.     | SIPR (Source IP Address Register) 25                           | 5 |

|   | 3.1.     | INTPTMR (Interrupt Pending Time Register)                      | 5 |

|   | 3.1.     | IR (Interrupt Register)                                        | 5 |

|   | 3.1.     | IMR (Interrupt Mask Register)                                  | 5 |

|   | 3.1.     | RTR (Retransmission Time Register)27                           | 7 |

|   | 3.1.     | 0 RCR (Retransmission Count Register)27                        | 7 |

|   | 3.1.     | 1 RMSR (RX Memory Size Register) 27                            | 7 |

|   | 3.1.     | 2 TMSR (TX Memory Size Register) 28                            | 3 |

|   | 3.1.     | 3 IR2 (Interrupt Register 2)                                   | 3 |

|   | 3.1.     | 4 IMR2 (Interrupt Mask Register 2) 29                          | ) |

|   | 3.1.     | 5 PTIMER (PPP Link Control Protocol Request Timer Register) 29 | ) |

|   | 3.1.     | 6 PMAGIC (PPP Link Control Protocol Magic number Register) 29  | ) |

|   | 3.1.     | 7 UIPR (Unreachable IP Address Register)                       | ) |

|   | 3.1.     | 8 UPORTR (Unreachable Port Register)                           | ) |

|   | 3.1.     | 9 MR2 (Mode Register 2) 30                                     | ) |

|   | 3.1.     | 20 PHAR (Destination Hardware Address Register on PPPoE)       | 2 |

|   | 3.1.     | PSIDR (Session ID Register on PPPoE)                           | 2 |

|   | 3.1.     | 2 PMRUR (PPPoE Maximum Receive Unit Register)                  | 2 |

|   | 3.1.     | 23 PHYSR (PHY Status Register)                                 | 2 |

|   | 3.1.     | PHYRAR (PHY Register Address Register)                         | 3 |

|   | 3.1.     | 25 PHYDIR (PHY Data Input Register)                            | 1 |

|   | 3.1.     | 26 PHYDOR (PHY Data Output Register)                           | 1 |

|   | 3.1.     | PHYACR (PHY Access Control Register)                           | 1 |

|   | 3.1.     | 28 PHYDIVR (PHY Division Register)                             | 1 |

|   | 3.1.     | 9 PHYCR0 (PHY Control Register 0) 34                           | 1 |

|     | 3.1.30 | PHYCR1 (PHY Control Register 1)                           | 35 |

|-----|--------|-----------------------------------------------------------|----|

|     | 3.1.31 | SLCR (SOCKET-less Command Register)                       | 36 |

|     | 3.1.32 | SLRTR (SOCKET-less Retransmission Time Register)          | 36 |

|     | 3.1.33 | SLRCR (SOCKET-less Retransmission Count Register)         | 37 |

|     | 3.1.34 | SLPIPR (SOCKET-less Peer IP Address Register)             | 37 |

|     | 3.1.35 | SLPHAR (SOCKET-less Peer Hardware Address Register)       | 37 |

|     | 3.1.36 | PINGSEQR (PING Sequence-number Register)                  | 37 |

|     | 3.1.37 | PINGIDR (PING ID Register)                                | 38 |

|     | 3.1.38 | SLIMR (SOCKET-less Interrupt Mask Register)               | 38 |

|     | 3.1.39 | SLIR (SOCKET-less Interrupt Register)                     | 38 |

|     | 3.1.40 | CLKLCKR (Clock Lock Register)                             | 39 |

|     | 3.1.41 | NETLCKR (Network Lock Register)                           | 39 |

|     | 3.1.42 | PHYLCKR (PHY Lock Register)                               | 39 |

|     | 3.1.43 | VERR (Version Register)                                   | 39 |

|     | 3.1.44 | TCNTR (Ticker Counter Register)                           | 39 |

|     | 3.1.45 | TCNTCLR (Ticker Counter Clear Register)                   | 40 |

| 3.2 | SOC    | KET Register                                              | 41 |

|     | 3.2.1  | Sn_MR (SOCKET n Mode Register)                            | 41 |

|     | 3.2.2  | Sn_CR (SOCKET n Command Register)                         | 42 |

|     | 3.2.3  | Sn_IR (SOCKET n Interrupt Register)                       | 44 |

|     | 3.2.4  | Sn_SR (SOCKET n Status Register)                          | 45 |

|     | 3.2.5  | Sn_PORTR (SOCKET n Source Port Register)                  | 46 |

|     | 3.2.6  | Sn_DHAR (SOCKET n Destination Hardware Address Register)  | 46 |

|     | 3.2.7  | Sn_DIPR (SOCKET n Destination IP Address Register)        | 47 |

|     | 3.2.8  | Sn_DPORTR (SOCKET n Destination Port Register)            | 47 |

|     | 3.2.9  | Sn_MSS (SOCKET n Maximum Segment Size Register)           | 47 |

|     | 3.2.10 | Sn_PROTOR (SOCKET n IP Protocol Register)                 | 48 |

|     | 3.2.11 | Sn_TOS (SOCKET n IP Type Of Service Register)             | 48 |

|     | 3.2.12 | Sn_TTL (SOCKET n IP Time To Live Register)                | 48 |

|     | 3.2.13 | Sn_RXBUF_SIZE (SOCKET n RX Buffer Size Register)          | 48 |

|     | 3.2.14 | Sn_TXBUF_SIZE (SOCKET n TX Buffer Size Register)          | 49 |

|     | 3.2.15 | Sn_TX_FSR (SOCKET n TX Free Size Register)                | 49 |

|     | 3.2.16 | Sn_TX_RD (SOCKET n TX Read Pointer Register)              | 49 |

|     | 3.2.17 | Sn_TX_WR (SOCKET n TX Write Pointer Register)             | 50 |

|     | 3.2.18 | Sn_RX_RSR (SOCKET n RX Received Size Register)            | 50 |

|     | 3.2.19 | Sn_RX_RD (SOCKET n RX Read Pointer Register)              | 50 |

|     | 3.2.20 | Sn_RX_WR (SOCKET n RX Write Pointer Register)             | 51 |

|     | 3.2.21 | Sn_IMR (SOCKET n Interrupt Mask Register)                 | 51 |

|     | 3.2.22 | Sn_FRAGR (SOCKET n Fragment Offset in IP Header Register) | 51 |

|   |     | 3.2.23     | Sn_MR2 (SOCKET n Mode register 2)               | 51 |

|---|-----|------------|-------------------------------------------------|----|

|   |     | 3.2.24     | Sn_KPALVTR (SOCKET n Keep Alive Timer Register) | 53 |

|   |     | 3.2.25     | Sn_RTR (SOCKET n Retransmission Time Register)  | 53 |

|   |     | 3.2.26     | Sn_RCR (SOCKET n Retransmission Count Register) | 53 |

| 4 | Fun | ctional De | escription                                      | 54 |

|   | 4.1 | W51        | 00S RESET                                       | 54 |

|   | 4.2 | Initi      | alization                                       | 54 |

|   |     | 4.2.1      | Basic Setting                                   | 54 |

|   |     | 4.2.2      | Network Information Setting                     | 54 |

|   |     | 4.2.3      | SOCKET TX/RX Buffer Setting                     | 55 |

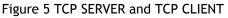

|   | 4.3 | ТСР        |                                                 | 56 |

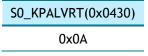

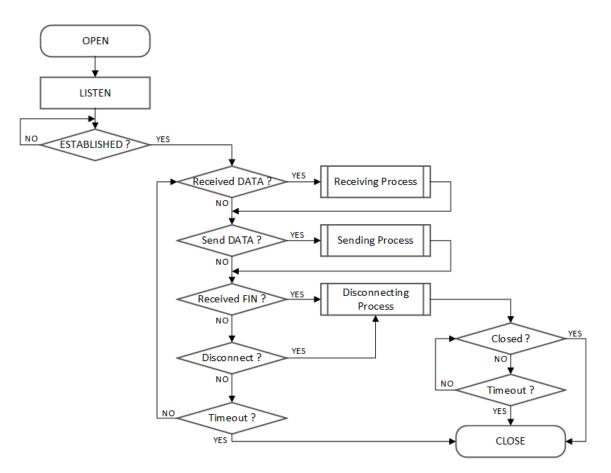

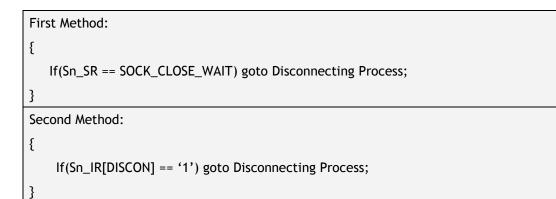

|   |     | 4.3.1      | TCP Server                                      | 57 |

|   |     | 4.3.2      | TCP Client                                      | 65 |

|   |     | 4.3.3      | Other Functions                                 | 67 |

|   | 4.4 | UDP        |                                                 | 68 |

|   |     | 4.4.1      | UDP Unicast                                     | 68 |

|   |     | 4.4.2      | UDP Broadcast                                   | 71 |

|   |     | 4.4.3      | UDP Multicast                                   | 72 |

|   |     | 4.4.4      | Other Functions                                 | 74 |

|   | 4.5 | IPRA       | .w                                              | 75 |

|   | 4.6 | MAC        | RAW                                             | 78 |

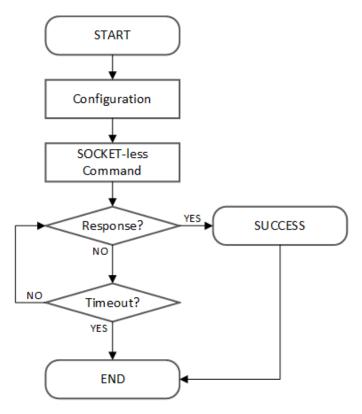

|   | 4.7 | SOC        | KET-less Command (SLCR)                         | 81 |

|   |     | 4.7.1      | ARP Request (SLCR [ARP] = '1')                  | 81 |

|   |     | 4.7.2      | PING Command (SLCR [PING] = '1')                | 83 |

|   | 4.8 | Retr       | ansmission                                      | 86 |

|   |     | 4.8.1      | ARP & PING Retransmission                       | 86 |

|   |     | 4.8.2      | TCP Retransmission                              | 86 |

|   | 4.9 | Othe       | ers Function                                    | 88 |

|   |     | 4.9.1      | System Clock(SYS_CLK) Switching                 | 88 |

|   |     | 4.9.2      | Ethernet PHY Operation Mode Configuration       | 88 |

|   |     | 4.9.3      | Ethernet PHY Parallel Detection                 | 89 |

|   |     | 4.9.4      | Ethernet PHY Auto MDIX                          | 89 |

|   |     | 4.9.5      | Ethernet PHY Power Down Mode                    | 90 |

|   |     | 4.9.6      | Ethernet PHY's Registers Control                | 91 |

| 5 | HOS | T Interfac | e Mode                                          | 92 |

|   | 5.1 | SPI /      | Node                                            | 92 |

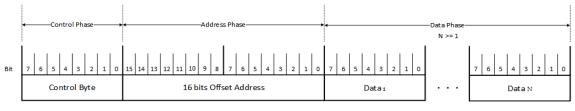

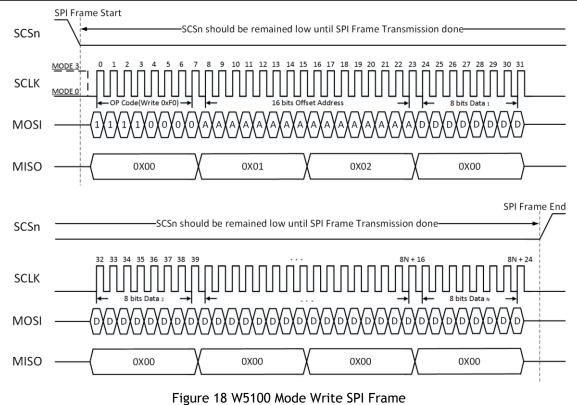

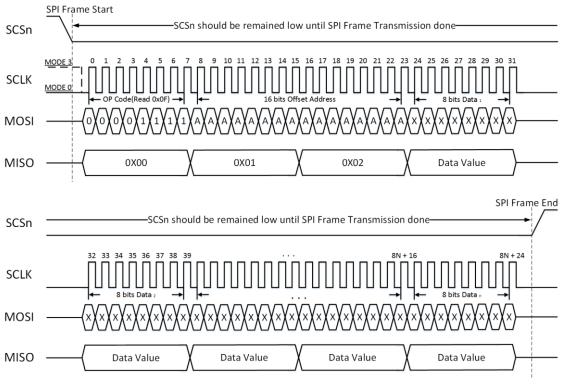

|   |     | 5.1.1      | SPI Frame                                       | 93 |

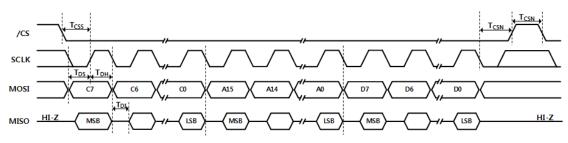

|   |     | 5.1.2      | SPI Write                                       | 93 |

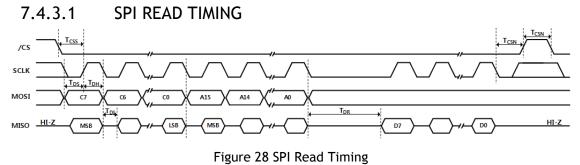

|   |     | 5.1.3      | SPI Read                                        | 94 |

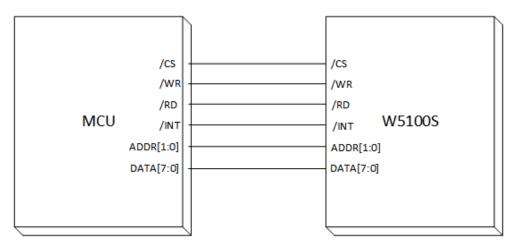

|   | 5.2  | Par       | allel Bus Mode                                 |     |

|---|------|-----------|------------------------------------------------|-----|

|   |      | 5.2.1     | Parallel Bus Data Write                        |     |

|   |      | 5.2.2     | Parallel Bus Data Write                        |     |

| 6 | Cloc | k & Tran  | sformer Requirements                           | 97  |

|   | 6.1  | Qua       | artz Crystal requirements                      |     |

|   | 6.2  | Osc       | illator requirements                           |     |

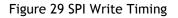

|   | 6.3  | Tra       | nsformer Characteristics                       |     |

| 7 | Elec | trical Sp | ecification                                    | 99  |

|   | 7.1  | Abs       | olute Maximum ratings                          |     |

|   | 7.2  | Abs       | olute Maximum ratings (Electrical Sensitivity) |     |

|   | 7.3  | DC        | Characteristics                                |     |

|   | 7.4  | AC        | Characteristics                                | 100 |

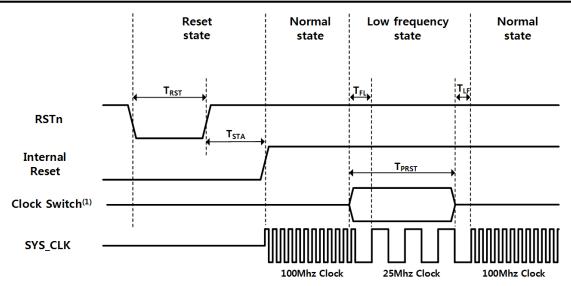

|   |      | 7.4.1     | Reset Timing                                   | 100 |

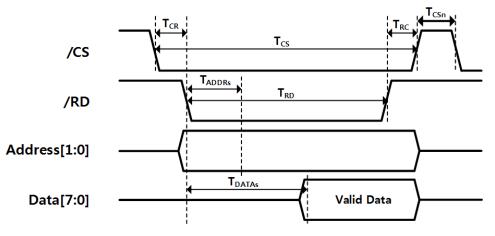

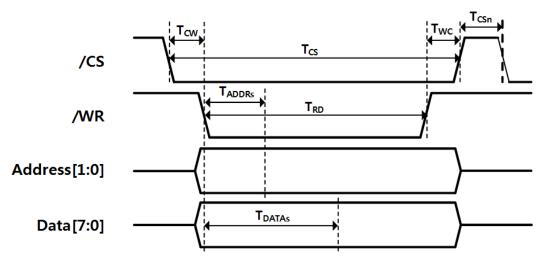

|   |      | 7.4.2     | BUS ACCESS TIMING                              | 102 |

|   |      | 7.4.3     | SPI ACCESS TIMING                              | 103 |

|   |      | 7.4.4     | Transformer Characteristics                    | 104 |

|   |      | 7.4.5     | MDIX                                           | 104 |

|   | 7.5  | PO\       | VER DISSPATION                                 | 104 |

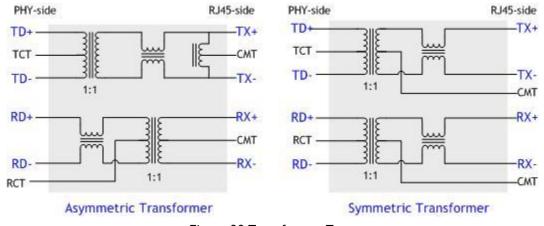

| 8 | Pac  | kage Info | rmation                                        | 106 |

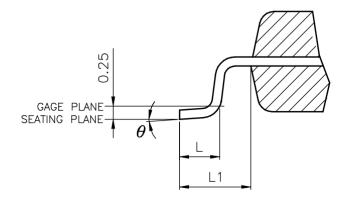

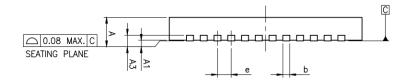

|   | 8.1  | LQF       | P48                                            | 106 |

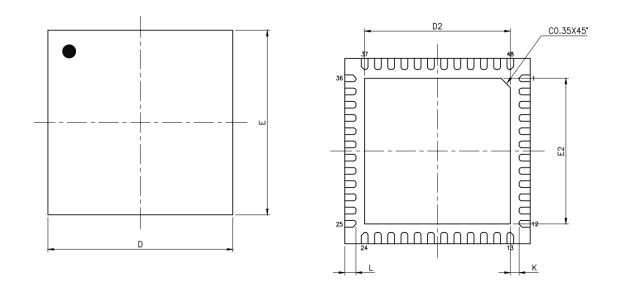

|   | 8.2  | QFN       | V48                                            | 107 |

| 9 | Doc  | ument Re  | evision History                                | 109 |

# List of Figures

| Figure 1 Block Diagram                                       | 4 |

|--------------------------------------------------------------|---|

| Figure 2 W5100S Pin Layout11                                 | 1 |

| Figure 3 Memory Map                                          | 5 |

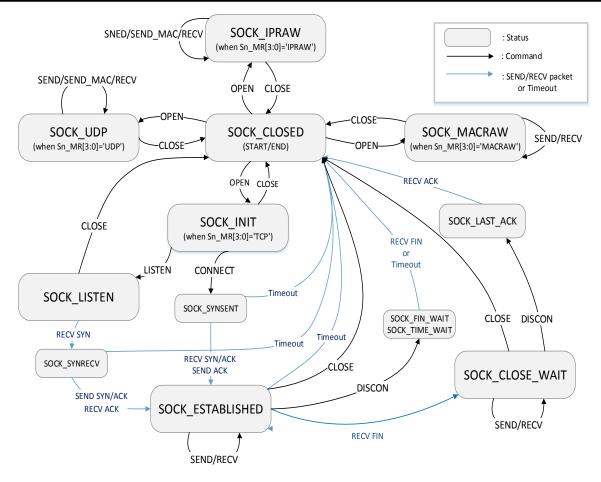

| Figure 4 State Diagram                                       | 5 |

| Figure 5 TCP SERVER and TCP CLIENT                           | 5 |

| Figure 6 TCP Server Operation Flow                           | 7 |

| Figure 7 TCP Client Operation Flow                           | 5 |

| Figure 8 UDP Operation Flow                                  | 3 |

| Figure 9 Received UDP DATA in SOCKETn RX Buffer Block        | 9 |

| Figure 10 IPRAW Operation Flow75                             | 5 |

| Figure 11 Received Data in IPRAW Mode SOCKET RX Buffer Block | 5 |

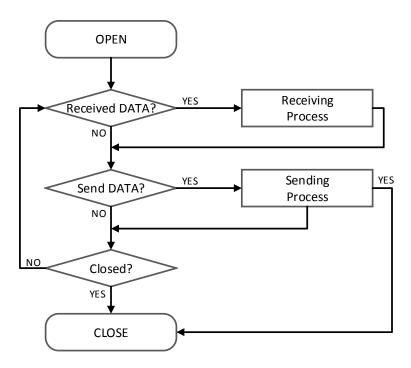

| Figure 12 MACRAW Operation Flow78                            | 3 |

| Figure 13 Received DATA Format in MACRAW79                   | 9 |

| Figure 14 SOCKET-less Command Operation Flow81               | 1 |

| Figure 15 SCSn controlled by Host92                          | 2 |

| Figure 16 SPI Mode 0 & Mode 392                              | 2 |

| Figure 17 SPI Frame                                          | 3 |

| Figure 18 W5100 Mode Write SPI Frame94                       | 4 |

| Figure 19 W5100 Mode Read SPI Frame94                        | 4 |

| Figure 20 Direct & Indirect Mode Control by Host95           | 5 |

| Figure 21 Parallel Bus N-Bytes Data Write96                  | 5 |

| Figure 22 Indirect Mode Continuous Read Access               | 5 |

| Figure 23 Quartz Crystal Model97                             | 7 |

| Figure 24 Transformer Type98                                 | 3 |

| Figure 25 Reset Timing 101                                   | 1 |

| Figure 26 Bus Read Timing 102                                | 2 |

| Figure 27 BUS Write Timing 102                               | 2 |

| Figure 28 SPI Read Timing 103                                | 3 |

| Figure 29 SPI Write Timing 103                               | 3 |

|                                                              |   |

| Figure 30 Transformer Type 104                               |   |

## List of Tables

| Table 1 Pin Type Notation                               | 11  |

|---------------------------------------------------------|-----|

| Table 2 PIN Description                                 | 12  |

| Table 3 Common Registers                                |     |

| Table 4 Socket Registers                                | 20  |

| Table 5 Internet Protocol Supported In IPRAW Mode       | 75  |

| Table 6 W5100 Mode SPI Command                          | 93  |

| Table 7 Indirect Mode Address Value                     | 95  |

| Table 8 Quartz Crystal                                  | 97  |

| Table 9 Crystal Recommendation Characteristics          | 97  |

| Table 10 Oscillator Characteristics                     | 98  |

| Table 11 Transformer Characteristics                    | 98  |

| Table 12 Absolute Maximum ratings                       | 99  |

| Table 13 Electro Static Discharge (ESD)                 | 99  |

| Table 14 Latch up Test                                  | 99  |

| Table 15 DC Characteristics                             | 99  |

| Table 16 Reset Table                                    | 101 |

| Table 17 BUS Read Timing                                | 102 |

| Table 18 BUS Write timing                               | 103 |

| Table 19 SPI Read Timing                                | 103 |

| Table 20 SPI Write Timing                               | 104 |

| Table 21 Transformer Characteristics                    | 104 |

| Table 22 Power Dissipation                              | 104 |

| Table 23 LQFP48 VARIATIONS (ALL DEMINSIONS SHOWN IN MM) | 106 |

| Table 24 QFN48 VARIATIONS (ALL DEMINSIONS SHOWN IN MM)  | 107 |

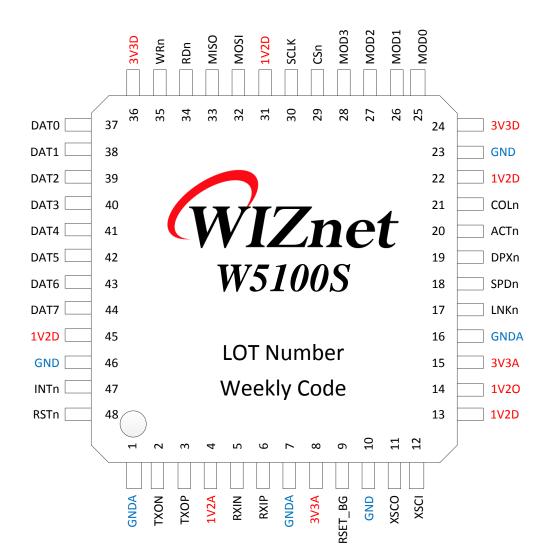

## 1 PIN Description

Figure 2 W5100S Pin Layout

#### Table 1 Pin Type Notation

| Туре | Description                                |

|------|--------------------------------------------|

| I    | Input                                      |

| 0    | Output                                     |

| м    | Alternate (Multi-function) Signal          |

| U    | Internal pulled-up 75K $\Omega$ resistor   |

| D    | Internal pulled-down 75K $\Omega$ resistor |

| А    | Analog                                     |

| Р    | Power & Ground                             |

## 1.1 PIN Description

|       |         |          | Table 2 PIN Description                                       |

|-------|---------|----------|---------------------------------------------------------------|

| PIN # | Symbol  | Туре     | Description                                                   |

| 1     | GNDA    | AP       | Analog Ground                                                 |

| 2     | TXON    | AO       | Differential Transmitted Signal Pair                          |

| 3     | ТХОР    | AO       | Differential Data is transmitted to Media via TXOP/TXON       |

|       |         |          | signal pair on MDI Mode.                                      |

| 4     | 1V2A    | AP       | Analog 1.2V Power                                             |

|       |         |          | Supplied from 1V20 voltage source                             |

| 5     | RXIN    | Al       | Differential Received Signal Pair                             |

| 6     | RXIP    | AI       | Differential Data is received from Media via RXIP/RXIN        |

|       |         |          | signal pair on MDI Mode.                                      |

| 7     | GNDA    | AP       | Analog Ground                                                 |

| 8     | 3V3A    | AP       | Analog 3.3V Power                                             |

|       |         |          | Off-chip Bias Resistor                                        |

| 9     | RSET_BG | AO       | Must be connected to analog Ground through external           |

|       |         |          | 12.3K $\Omega$ , error 1% Resistance.                         |

| 10    | GND     | AP       | Digital Ground                                                |

| 11    | XSCO    | AO       | 25MHz Clock                                                   |

|       |         |          | 25MHz Crystal Oscillator (TXAL) or Oscillator (OSC) are       |

|       |         |          | used for Internal oscillator stabilization.                   |

|       |         |          | W5100S uses 25MHz (Low Frequency Mode) or 100MHz              |

| 40    | VCCI    |          | (Normal Mode) as Internal Clock from External 25MHz           |

| 12    | XSCI    | Al       | Clock Source.                                                 |

|       |         |          | If OSC is used, 25MHz@1.2V must be used and only XSCI         |

|       |         |          | must be connected and XSCO must be floated.                   |

|       |         |          | For more information, refer to <u>Clock Selection Guide</u> . |

|       | (1/25   | _        | Digital 1.2V Power                                            |

| 13    | 1V2D    | P        | Supplied from 1V20 voltage source                             |

|       |         |          | Internal Regulator 1.2V Power Output                          |

|       |         |          | Internal Regulator for W5100S needs Max 150mA for 1.2V        |

|       |         |          | Power Output.                                                 |

|       |         |          | Make sure to supply 1V2D and 1V2A for External                |

| 14    | 1V2O    | РО       | Capacitor 3.3uF stabilization.                                |

|       |         |          | 1V20 must use Ferrite Bead. 1V2D and 1V2A must be             |

|       |         |          | separated and be supplied.                                    |

|       |         |          | This power is only for W5100S. It must not be used for        |

|       |         |          | other device.                                                 |

|       | I       | <u> </u> |                                                               |

|    | 1                |         |                                                          |

|----|------------------|---------|----------------------------------------------------------|

| 15 | 3V3A             | AP      | Analog 3.3V Power                                        |

| 16 | GNDA             | AP      | Analog Ground                                            |

|    |                  |         | Link Status LED -                                        |

|    |                  |         | It is valid on SPI and Parallel Bus Mode.                |

| 17 | LNKn             | OU      |                                                          |

|    |                  |         | Low : Link up                                            |

|    |                  |         | High : Link down                                         |

|    |                  |         | Link Speed LED-                                          |

|    |                  |         | It is valid on SPI and Parallel Bus Mode.                |

| 18 | SPDn             | OU      |                                                          |

|    |                  |         | Low: 100Mbps                                             |

|    |                  |         | High: 10Mbps                                             |

|    |                  |         | Link Duplex LED                                          |

|    |                  |         | It is valid on SPI and Parallel Bus Mode.                |

| 19 | DPXn             | OU      |                                                          |

|    |                  |         | Low : Full-Duplex                                        |

|    |                  |         | High : Half-Duplex                                       |

|    |                  |         | Link Activity LED                                        |

|    |                  |         | It is valid on SPI and Parallel Bus Mode.                |

| 20 | ACTn             | OU      |                                                          |

|    |                  |         | No Flash : Link up state without TX/RX                   |

|    |                  |         | Flash : Link up state with TX/RX data                    |

|    |                  |         | High : Link-down state                                   |

|    |                  |         | Link Collision Detect LED                                |

|    |                  |         | It is valid on SPI and Parallel Bus Mode.                |

| 21 | COLn             | OU      | It indicates a collision during Data transmission.       |

|    |                  |         | Louis Collision Detected                                 |

|    |                  |         | Low : Collision Detected                                 |

|    |                  |         | High : No Collision                                      |

| 22 | 1V2D             | Р       | Digital 1.2V Power<br>Supplied from 1V20 voltage source. |

| 23 | GND              | Р       | Digital Ground                                           |

| 23 | 3V3D             | г<br>Р  | Digital 3.3V power                                       |

| 24 | MOD[0]           | ۲<br>ID | W5100S Interface Mode Selection                          |

| 26 | MOD[0]<br>MOD[1] | ID      | Interface Mode is selected by MOD [3:0].                 |

| 27 | MOD[1]<br>MOD[2] | ID      | [2:0].                                                   |

|    |                  |         | "0000":SPI Mode                                          |

| 28 | MOD[3]           | ID      | "010X" : Parallel Bus Mode                               |

| 29 | CSn              | IU      | W5100S Chip Select                                       |

|    | <u>I</u>         |         | · · .                                                    |

|   |                                                                                                                                                                                        |          |      | Low : Select                                              |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|-----------------------------------------------------------|

|   |                                                                                                                                                                                        |          |      | High : No Select                                          |

|   |                                                                                                                                                                                        |          |      | SPI Clock                                                 |

|   | 30                                                                                                                                                                                     | SCLK     | ID   | On SPI Mode, it is used to SPI Clock.                     |

|   | 50                                                                                                                                                                                     | JCLK     | U    | But on Parallel Bus Mode, it must be connected to GND     |

|   |                                                                                                                                                                                        |          |      | or be floated.                                            |

|   | 24                                                                                                                                                                                     | 1V2D     | Р    | Digital 1.2V Power                                        |

|   | 21                                                                                                                                                                                     | TVZD     | Г    | Supplied from 1V20 voltage source.                        |

|   |                                                                                                                                                                                        | MOSI     |      | SPI Master Output Slave Input / Address 0                 |

|   | 32       N         32       N         33       N         33       /A         34       F         35       V         36       3         37       D         38       D         39       D | /ADDR0   | IDM  | MOSI : On SPI Mode, SPI Data is received from HOST.       |

|   |                                                                                                                                                                                        | / ADDRU  |      | ADDR0 : On Parallel Bus Mode, it is used to Address 0.    |

|   |                                                                                                                                                                                        | MISO     |      | SPI Master Input Slave Output / Address 1                 |

|   | 33                                                                                                                                                                                     | /ADDR1   | IOPM | MISO : On SPI Mode, SPI Data is transmitted to HOST.      |

|   |                                                                                                                                                                                        | / ADDK I |      | ADDR1 : On Parallel Bus Mode, It is used to Address 1.    |

| - |                                                                                                                                                                                        |          |      | Read Strobe                                               |

|   | 34                                                                                                                                                                                     | RDn      | IU   | On Parallel Bus Mode, it indicates Read Operation.        |

|   |                                                                                                                                                                                        |          |      | On SPI Mode, it must be connected to 3V3D or be floated.  |

| - | 25                                                                                                                                                                                     | \\/D     |      | Write Strobe                                              |

|   | 35                                                                                                                                                                                     | WRn      | IU   | On Parallel Bus Mode, it indicates Write Operation.       |

| - | 36                                                                                                                                                                                     | 3V3D     | Р    | Digital 3.3V Power                                        |

| - | 37                                                                                                                                                                                     | DAT0     | IOU  | 8 Bits Data Bus                                           |

| - | 38                                                                                                                                                                                     | DAT1     | IOU  | On Parallel Bus Mode, DAT [7:0] receives Data from HOST   |

| - | 39                                                                                                                                                                                     | DAT2     | IOU  | or W5100S.                                                |

| - | 40                                                                                                                                                                                     | DAT3     | IOU  |                                                           |

| - | 41                                                                                                                                                                                     | DAT4     | IOU  | On SPI Mode, DAT [7:0] must be floated.                   |

| - | 42                                                                                                                                                                                     | DAT5     | IOU  |                                                           |

| - | 43                                                                                                                                                                                     | DAT6     | IOU  |                                                           |

| - | 44                                                                                                                                                                                     | DAT7     | IOU  |                                                           |

| - | 45                                                                                                                                                                                     | 1V2D     | Р    | Digital 1.2V Power                                        |

| - | 46                                                                                                                                                                                     | GND      | Р    | Digital Ground                                            |

| - |                                                                                                                                                                                        |          |      | Interrupt                                                 |

|   |                                                                                                                                                                                        |          |      | When the event occurs during W5100S Ethernet              |

|   |                                                                                                                                                                                        |          |      | Communication, INTn notices to HOST.                      |

|   |                                                                                                                                                                                        |          |      |                                                           |

|   | 47                                                                                                                                                                                     | INTn     | OP   | Low : Interrupt Occurred                                  |

|   |                                                                                                                                                                                        |          |      | High : No Interrupt                                       |

|   |                                                                                                                                                                                        |          |      |                                                           |

|   |                                                                                                                                                                                        |          |      | Refer to IEN (Interrupt pin Enable) in MR2 (Mode Register |

|   |                                                                                                                                                                                        |          |      | 2), INTPTMR (Interrupt Pending Time Register), IMR        |

| - |                                                                                                                                                                                        | 1        | 1    |                                                           |

|    |      |    | (Interrupt Mask Register), IMR2 (Interrupt Mask Register |

|----|------|----|----------------------------------------------------------|

|    |      |    | 2), SLIMR (SOCKET-less Interrupt Mask Register)          |

|    |      |    | Reset                                                    |

|    |      |    | RSTn initializes W5100S. RSTn must be asserted to Low    |

|    |      |    | longer than 500ns. After asserted RSTn, W5100S spends    |

| 48 | RSTn | IP | 60.3ms for initialization. (Ref 7.4.1 Reset Timing)      |

|    |      |    |                                                          |

|    |      |    | Low : W5100S initialized.                                |

|    |      |    | High : Normal Operation.                                 |

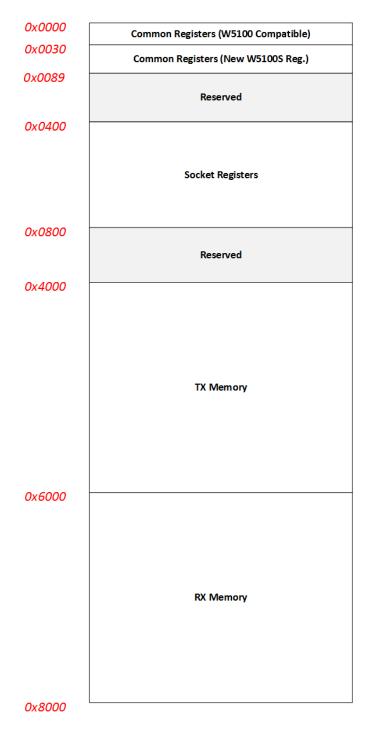

## 2 Memory Map

W5100S has the same Memory Map as W5100 for compatibility and additional Common Register for improved functionality. The below Figure 3 shows W5100S Memory Map.

Figure 3 shows the Address Offset of Common & SOCKET Register Block and TX/RX Memory Block. At W5100S Reset, each SOCKET n TX/RX Buffer are assigned with 2KB/2KB from TX/RX Memory Block.

After W5100S Reset, each SOCKET n TX/RX Buffer Size are set by TMSR (TX Memory Size Register) and RMSR (RX Memory Size Register) or by SOCKET n TX/RX Buffer Size Register (Sn\_TXBUF\_SIZE / Sn\_RXBUF\_SIZE). The total Buffer Size of SOCKET n TX/RX must not be exceeded by 8 Kbytes.

# 2.1 W5100S Registers

## 2.1.1 Common registers

Table 3 Common Registers

| Address                    | Register                |

|----------------------------|-------------------------|

| 0x0000                     | Mode (MR)               |

| 0x0001                     | Gateway Address         |

| 0x0001<br>0x0002           | (GAR0)                  |

| 0x0002<br>0x0003           | (GAR1)                  |

| 0x0003                     | (GAR2)                  |

| 0,0004                     | (GAR3)                  |

| 0x0005                     | Subnet Mask Address     |

| 0x0006                     | (SUBRO)                 |

| 0x0007                     | (SUBR1)                 |

| 0x0008                     | (SUBR2)                 |

|                            | (SUBR3)                 |

| 0x0009                     | Source Hardware Address |

| 0x000A                     | (SHARO)                 |

| 0x000B                     | (SHAR1)                 |

| 0x000C                     | (SHAR2)                 |

| 0x000D                     | (SHAR3)                 |

| 0x000E                     | (SHAR4)                 |

|                            | (SHAR5)                 |

| 0x000F                     | Source IP Address       |

| 0x0010<br>0x0011<br>0x0012 | (SIPRO)                 |

|                            | (SIPR1)                 |

|                            | (SIPR2)                 |

|                            | (SIPR3)                 |

| 0x0013                     | Interrupt Pending Time  |

| 0x0014                     | (INTPTMRO)              |

| 0.0045                     | (INTPTMR1)              |

| 0x0015                     | Interrupt (IR)          |

| 0x0016                     | Interrupt Mask (IMR)    |

| 0x0017                     | Retransmission Time     |

| 0x0018                     | (RTRO)                  |

|                            | (RTRO)                  |

| 0x0019                     | Retransmission Time     |

|                            | (RCR)                   |

| 0x001A                     | RX Memory Size          |

|                            | (RMSR)                  |

| 0x001B                     | TX Memory Size          |

|                            | (TMSR)                  |

| Address                                                  | Register                                                                                                   |

|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 0x001C<br>~<br>0x001F                                    | Reserved                                                                                                   |

|                                                          | Interrupt2 (ID2)                                                                                           |

| 0x0020<br>0x0021                                         | Interrupt2 (IR2)                                                                                           |

|                                                          | Interrupt2 Mask (IMR2)                                                                                     |

| 0x0022                                                   | Reserved                                                                                                   |

| 0x0027                                                   |                                                                                                            |

| 0x0028                                                   | PPP LCP Request Timer<br>(PTIMER)                                                                          |

| 0x0029                                                   | PPP LCP Magic Number<br>(PMAGIC)                                                                           |

| 0x002A<br>0x002B<br>0x002C<br>0x002D                     | Unreachable IP Address<br>(UIPR0)<br>(UIPR1)<br>(UIPR2)<br>(UIPR3)                                         |

| 0x002E<br>0x002F                                         | Unreachable Port<br>(UPORTR0)<br>(UPORTR1)                                                                 |

| 0x0030                                                   | Mode2 (MR2)                                                                                                |

| 0x0031                                                   | Reserved                                                                                                   |

| 0x0032<br>0x0033<br>0x0034<br>0x0035<br>0x0036<br>0x0037 | Destination Hardware Address<br>on PPPoE<br>(PHAR0)<br>(PHAR1)<br>(PHAR2)<br>(PHAR3)<br>(PHAR4)<br>(PHAR5) |

| 0x0038<br>0x0039                                         | Session ID on PPPoE<br>(PSIDR0)<br>(PSIDR1)                                                                |

| 0x003A<br>0x003B                                         | Maximum Receive Unit on PPPoE<br>(PMRUR0)<br>(PMRUR1)                                                      |

| 0x003C                                                   | PHY Status<br>(PHYSR0)                                                                                     |

| Address          | Register                                     |

|------------------|----------------------------------------------|

| 0x003E           | PHY Address Value (PHYAR)                    |

| 0x003F           | PHY Register Address (PHYRAR)                |

| 000.40           | PHY Data Input                               |

| 0x0040<br>0x0041 | (PHYDIR0)                                    |

| 0X0041           | (PHYDIR1)                                    |

| 0x0042           | PHY Data Output                              |

| 0x0042           | (PHYDOR0)                                    |

|                  | (PHYDOR1)                                    |

| 0x0044           | PHY Access (PHYACR)                          |

| 0x0045           | PHY Division (PHYDIVR)                       |

| 0x0046           | PHY Control                                  |

| 0x0047           | (PHYCRO)                                     |

|                  | (PHYCR1)                                     |

| 0x0048           |                                              |

| ~                | Reserved                                     |

| 0x004B           |                                              |

| 0x004C           | SOCKET-less Command (SLCR)                   |

| 0x004D           | SOCKET-less Retransmission Time              |

| 0x004E           | (SLRTRO)                                     |

|                  | (SLRTR1)<br>SOCKET-less Retransmission Count |

| 0x004F           | (SLRCR)                                      |

|                  | SOCKET-less Peer IP Address                  |

| 0x0050           | (SLPIPRO)                                    |

| 0x0051           | (SLPIPR1)                                    |

| 0x0052           | (SLPIPR2)                                    |

| 0x0053           | (SLPIPR3)                                    |

| 0.007.           | SOCKET-less Peer Hardware Address            |

| 0x0054           | (SLPHARO)                                    |

| 0x0055           | (SLPHAR1)                                    |

| 0x0056<br>0x0057 | (SLPHAR2)                                    |

| 0x0057<br>0x0058 | (SLPHAR3)                                    |

| 0x0058<br>0x0059 | (SLPHAR4)                                    |

| 070037           | (SLPHAR5)                                    |

| 0x005A           | PING Sequence Number                         |

| 0x005A           | (PINGSEQR0)                                  |

|                  | (PINGSEQR1)                                  |

| 0x005C           | PING ID                                      |

| 0x005D           | (PINGIDRO)                                   |

|                  | (PINGIDR1)                                   |

| Address | Register                     |

|---------|------------------------------|

| 0x005E  | SOCKET-less Interrupt        |

| UXUUSE  | Mask (SLIMR)                 |

| 0x005F  | SOCKET-less Interrupt (SLIR) |

| 0x0060  |                              |

| ~       | Reserved                     |

| 0x006A  |                              |

| 0x0070  | Clock Lock (CLKLCKR)         |

| 0x0071  | Network Lock (NETLCKR)       |

| 0x0072  | PHY Lock (PHYLCKR)           |

| 0x0073  |                              |

| ~       | Reserved                     |

| 0x007F  |                              |

| 0x0080  | Chip Version (VERR)          |

| 0x0081  | Reserved                     |

| 0x0082  | 100us Tick Counter           |

| 0x0082  | (TCNTR0)                     |

| 070003  | (TCNTR1)                     |

| 0x0084  |                              |

| ~       | Reserved                     |

| 0x0087  |                              |

| 0x0088  | TCNTCLR                      |

## 2.1.2 SOCKET Registers

Table 4 Socket Registers

| C             |                                 | Address             |        |        |        |        |  |

|---------------|---------------------------------|---------------------|--------|--------|--------|--------|--|

| Symbol        | Description                     | Sn_                 | S0_    | S1_    | S2_    | S3_    |  |

| Sn_MR         | SOCKET n<br>Mode                | 0x0400+(0x0100 x n) | 0x0400 | 0x0500 | 0x0600 | 0x0700 |  |

| Sn_CR         | SOCKET n<br>Command             | 0x0401+(0x0100 x n) | 0x0401 | 0x0501 | 0x0601 | 0x0701 |  |

| Sn_IR         | SOCKET n<br>Interrupt           | 0x0402+(0x0100 x n) | 0x0402 | 0x0502 | 0x0602 | 0x0702 |  |

| Sn_SR         | SOCKET n<br>Status              | 0x0403+(0x0100 x n) | 0x0403 | 0x0503 | 0x0603 | 0x0703 |  |

| Sn_PORTR0     | SOCKET n                        | 0x0404+(0x0100 x n) | 0x0404 | 0x0504 | 0x0604 | 0x0704 |  |

| Sn_PORTR1     | Source Port                     | 0x0405+(0x0100 x n) | 0x0405 | 0x0505 | 0x0605 | 0x0705 |  |

| Sn_DHAR0      |                                 | 0x0406+(0x0100 x n) | 0x0406 | 0x0506 | 0x0606 | 0x0706 |  |

| Sn_DHAR1      |                                 | 0x0407+(0x0100 x n) | 0x0407 | 0x0507 | 0x0607 | 0x0707 |  |

| Sn_DHAR2      | SOCKET n                        | 0x0408+(0x0100 x n) | 0x0408 | 0x0508 | 0x0608 | 0x0708 |  |

| Sn_DHAR3      | Destination<br>Hardware Address | 0x0409+(0x0100 x n) | 0x0409 | 0x0509 | 0x0609 | 0x0709 |  |

| Sn_DHAR4      |                                 | 0x040A+(0x0100 x n) | 0x040A | 0x050A | 0x060A | 0x070A |  |

| Sn_DHAR5      |                                 | 0x040B+(0x0100 x n) | 0x040B | 0x050B | 0x060B | 0x070B |  |

| Sn_DIPR0      |                                 | 0x040C+(0x0100 x n) | 0x040C | 0x050C | 0x060C | 0x070C |  |

| Sn_DIPR1      | SOCKET n                        | 0x040D+(0x0100 x n) | 0x040D | 0x050D | 0x060D | 0x070D |  |

| Sn_DIPR2      | Destination IP<br>Address       | 0x040E+(0x0100 x n) | 0x040E | 0x050E | 0x060E | 0x070E |  |

| Sn_DIPR3      | Address                         | 0x040F+(0x0100 x n) | 0x040F | 0x050F | 0x060F | 0x070F |  |

| Sn_DPORTR0    | SOCKET n                        | 0x0410+(0x0100 x n) | 0x0410 | 0x0510 | 0x0610 | 0x0710 |  |

| Sn_DPORTR0    | Destination Port                | 0x0411+(0x0100 x n) | 0x0411 | 0x0511 | 0x0611 | 0x0711 |  |

| Sn_MSS0       | SOCKET n                        | 0x0412+(0x0100 x n) | 0x0412 | 0x0512 | 0x0612 | 0x0712 |  |

| Sn_MSS1       | Maximum<br>Segment Size         | 0x0413+(0x0100 x n) | 0x0413 | 0x0513 | 0x0613 | 0x0713 |  |

| Sn_PROTOR     | SOCKET n<br>IP Protocol         | 0x0414+(0x0100 x n) | 0x0414 | 0x0514 | 0x0614 | 0x0714 |  |

| Sn_TOS        | SOCKET n<br>IP Type Of Service  | 0x0415+(0x0100 x n) | 0x0415 | 0x0515 | 0x0615 | 0x0715 |  |

| Sn_TTL        | SOCKET n<br>IP Time To Live     | 0x0416+(0x0100 x n) | 0x0416 | 0x0516 | 0x0616 | 0x0716 |  |

| Reserved      | Reserved                        | 0x0417+(0x0100 x n) | 0x0417 | 0x0517 | 0x0617 | 0x0717 |  |

| Reserved      | Reserved                        | 0x041D+(0x0100 x n) | 0x041D | 0x051D | 0x061D | 0x071D |  |

| Sn_RXBUF_SIZE | SOCKET n<br>RX Buffer Size      | 0x041E+(0x0100 x n) | 0x041E | 0x051E | 0x061E | 0x071E |  |

| Sn_TXBUF_SIZE | SOCKET n<br>TX Buffer Size      | 0x041F+(0x0100 x n) | 0x041F | 0x051F | 0x061F | 0x071F |  |

| Sn_TX_FSR0    | SOCKET n                        | 0x0420+(0x0100 x n) | 0x0420 | 0x0520 | 0x0620 | 0x0720 |  |

| Sn_TX_FSR1   | TX Free Size                        | 0x0421+(0x0100 x n) | 0x0421 | 0x0521 | 0x0621 | 0x0721 |

|--------------|-------------------------------------|---------------------|--------|--------|--------|--------|

| Sn_TX_RD0    | SOCKET n                            | 0x0422+(0x0100 x n) | 0x0422 | 0x0522 | 0x0622 | 0x0722 |

| Sn_TX_RD1    | TX Read Pointer                     | 0x0423+(0x0100 x n) | 0x0423 | 0x0523 | 0x0623 | 0x0723 |

| Sn_TX_WR0    | SOCKET n                            | 0x0424+(0x0100 x n) | 0x0424 | 0x0524 | 0x0624 | 0x0724 |

| Sn_TX_WR1    | TX Write Pointer                    | 0x0425+(0x0100 x n) | 0x0425 | 0x0525 | 0x0625 | 0x0725 |

| Sn_RX_RSR0   | SOCKET n                            | 0x0426+(0x0100 x n) | 0x0426 | 0x0526 | 0x0626 | 0x0726 |

| Sn_RX_RSR1   | RX Received Size                    | 0x0427+(0x0100 x n) | 0x0427 | 0x0527 | 0x0627 | 0x0727 |

| Sn_RX_RD0    | SOCKET n                            | 0x0428+(0x0100 x n) | 0x0428 | 0x0528 | 0x0628 | 0x0728 |

| Sn_RX_RD1    | RX Read Pointer                     | 0x0429+(0x0100 x n) | 0x0429 | 0x0529 | 0x0629 | 0x0729 |

| Sn_RX_WR0    | SOCKET n                            | 0x042A+(0x0100 x n) | 0x042A | 0x052A | 0x062A | 0x072A |

| Sn_RX_WR1    | RX Write Pointer                    | 0x042B+(0x0100 x n) | 0x042B | 0x052B | 0x062B | 0x072B |

| Sn_IMR       | SOCKET n<br>Interrupt Mask          | 0x042C+(0x0100 x n) | 0x042C | 0x052C | 0x062C | 0x072C |

| Sn_FRAGR0    | SOCKET n                            | 0x042D+(0x0100 x n) | 0x042D | 0x052D | 0x062D | 0x072D |

| Sn_FRAGR1    | Fragment Offset<br>in IP Header     | 0x042E+(0x0100 x n) | 0x042E | 0x052E | 0x062E | 0x072E |

| Sn_MR2       | SOCKET n Mode 2                     | 0x042F+(0x0100 x n) | 0x042F | 0x052F | 0x062F | 0x072F |

| Sn_KPALVTR   | SOCKET n<br>Keep-alive Timer        | 0x0430+(0x0100 x n) | 0x0430 | 0x0530 | 0x0630 | 0x0730 |

| Sn_RTR0      | SOCKET n                            | 0x0432+(0x0100 x n) | 0x0432 | 0x0532 | 0x0632 | 0x0732 |

| _<br>Sn_RTR1 | Retransmission<br>Time              | 0x0433+(0x0100 x n) | 0x0433 | 0x0533 | 0x0633 | 0x0733 |

| Sn_RCR       | SOCKET n<br>Retransmission<br>Count | 0x0434+(0x0100 x n) | 0x0434 | 0x0534 | 0x0634 | 0x0734 |

## 3 Register Descriptions

**Register Notation**

| * Register Symbol (Register full Name)                           |                 |              |                 |                |               |                |           |

|------------------------------------------------------------------|-----------------|--------------|-----------------|----------------|---------------|----------------|-----------|

| - [Register Type][Address Offset][Reset Value]                   |                 |              |                 |                |               |                |           |

| Register D                                                       | escription      |              |                 |                |               |                |           |

| 7                                                                | 7 6 5 4 3 2 1 0 |              |                 |                |               |                |           |

| Bit7                                                             | Bit6            | Bit5         | Bit4            | Bit3           | Bit2          | Bit1           | Bit0      |

| Bit Type                                                         | Bit Type        | Bit Type     | Bit Type        | Bit Type       | Bit Type      | Bit Type       | Bit Type  |

|                                                                  |                 |              |                 |                |               |                |           |

| Sn_IR [3: 0] indicates a Register Symbol [Upper Bit: Lower Bit]. |                 |              |                 |                |               |                |           |

| Sn_IR [3: 0]                                                     | = '0001' ind    | icates Sn_IF | R [3] = '0', Sr | n_IR [2] = '0' | , Sn_IR [1] = | = '0', Sn_IR [ | 0] = '1'. |

#### [Register/Bit Type]: Type of Register and Bit.

- [RW] : Both reading and writing are possible.

- [R=W] : The value read and written are the same.

- [RO] : Read Only

- [WO] : Write Only

- [W] : Write Only

- [WC] : Cleared by written '1'.

- [W0] : Must be written only '0'.

- [W1] : Must be written only '1'.

- [AC] : Auto Clear

- [1] : Always read '1'

- [0] : Always read '0'

- [-] : Not available

#### [Address Offset]: Register Address Offset [Reset Value]: Default Value.

#### Ex1)

3.1.1 MR (Mode Register)

#### [RW][0x0000][0x03]

MR is abbreviation for Mode Register. This Register is possible to be read and written. The Register Address Offset is '0x0000' and it is set to '0x03' after Reset.

| 7   | 6  | 5  | 4   | 3     | 2 | 1  | 0   |

|-----|----|----|-----|-------|---|----|-----|

| RST | -  | -  | PB  | PPPoE | - | AI | IND |

| AC  | W0 | W0 | R=W | R=W   | - | 1  | 1   |

Ex2) MR [RST] MR [RST] means RST Bit in MR.

Ex3) MR [7:0]

MR [7:0] means the Bits from  $7^{th}$  to  $0^{th}$  bit in MR.

### 3.1 Common Registers

#### 3.1.1 MR (Mode Register) [RW][0x0000] [0x03]

MR is used for Reset, PING Block and PPPoE Enable

| 7   | 6 | 5 | 4  | 3     | 2 | 1 | 0 |

|-----|---|---|----|-------|---|---|---|

| RST | - | - | РВ | PPPoE | - | - | - |

|     |   |   |    |       |   |   |   |

| Bit   | Symbol | Description                                                   |

|-------|--------|---------------------------------------------------------------|

|       |        | Reset                                                         |

| 7     | RST    | If this Bit is '1', All W5100S Registers will be initialized. |

|       |        | It will be automatically cleared as '0' after 3 SYS_CLK       |

| [6:5] | -      | Reserved                                                      |

|       |        | PING Response Block                                           |

| 4     | РВ     | If this Bit is '1', it blocks the Response to a ping request. |

| 7     | FD     | 1 : Disable PING Response                                     |

|       |        | 0 : Enable PING Response                                      |

|       |        | PPPoE Enable                                                  |

| 3     | PPPoE  | 1 : Enable PPPoE                                              |

|       |        | 0 : Disable PPPoE                                             |

| [2:0] | -      | Reserved                                                      |

#### 3.1.2 GWR (Gateway IP Address Register) [R=W] [0x0001-0x0004] [0x00]

GWR configures the Gateway Address when NETLCKR (Network Lock Register) is on Unlock Mode.

| GWR0(0x0001) | GWR1(0x0002) | GWR2(0x0003) | GWR3(0x0004) |

|--------------|--------------|--------------|--------------|

| 192 (0xC0)   | 168 (0xA8)   | 0 (0x00)     | 1 (0x01)     |

#### 3.1.3 SUBR (Subnet Mask Register) [R=W] [0x0005-0x0008] [0x00]

SUBR configures the Subnet Mask Address when NETLCKR (Network Lock Register) is on Unlock Mode.

Ex) SUBR = "255.255.255.255"

| SUBR0(0x0005) | SUBR0(0x0006) | SUBR0(0x0007) | SUBR0(0x0008) |

|---------------|---------------|---------------|---------------|

| 255 (0xFF)    | 255 (0xFF)    | 255 (0xFF)    | 255 (0xFF)    |

#### 3.1.4 SHAR (Source Hardware Address Register) [R=W] [0x0009-0x000E] [0x00]

SHAR configures the Source MAC Address when NETLCKR (Network Lock Register) is on Unlock Mode.

#### Ex) SHAR = "11:22:33:AA:BB:CC"

| SHAR0(0x0009) | SHAR1(0x000A) | SHAR2(0x000B) |  |  |

|---------------|---------------|---------------|--|--|

| 0x11          | 0x22          | 0x33          |  |  |

| SHAR3(0x000C) | SHAR4(0x000D) | SHAR5(0x000E) |  |  |

| 0xAA          | 0xBB          | 0xCC          |  |  |

#### 3.1.5 SIPR (Source IP Address Register) [R=W] [0x000F-0x0012] [0x00]

SIPR configures the Source IP Address when NETLCKR (Network Lock Register) is on Unlock Mode.

Ex) SIPR = "192.168.0.100"

| SIPR0(x000F) | SIPR0(x000F) SIPR1(0x0010) |          | SIPR3(0x0012) |  |

|--------------|----------------------------|----------|---------------|--|

| 192 (0xC0)   | 168 (0xA8)                 | 0 (0x00) | 100(0x64)     |  |

### 3.1.6 INTPTMR (Interrupt Pending Time Register) [RW][0x0013-0x0014][0x0000]

INTPTMR sets internal Interrupt Pending Timer Count. When INTn is de-asserted to High, Timer Count is initialized to INTPTMR and decreased by 1 from initial value to '0' every SYS\_CLK x 4. When Interrupt occurs and the corresponding Interrupt Mask is set and INTPTMR is '0', INTn is asserted to Low.

Ex) INTPTMR = 1000(0x03EB)

| INTPTMR0(0x0013) | INTPTMR1(0x0014) |

|------------------|------------------|

| 0x03             | 0xEB             |

### 3.1.7 IR (Interrupt Register) [RW] [0x0015] [0x00]

When W5100S or SOCKET n Event occurs, the corresponding Bit in IR is set to '1'. If the Event occurs and the corresponded Interrupt Mask Bit in IMR is set to '1' and internal Interrupt

Pending Timer Counter is '0', INTn is asserted to Low. When the Event is cleared or the corresponding Mask Bit is set to '0', INTn is de-asserted to High.

| 7        | 6       | 5       | 4 | 3      | 2      | 1      | 0      |

|----------|---------|---------|---|--------|--------|--------|--------|

| CONFLICT | UNREACH | PPPTERM | - | S3_INT | S2_INT | S1_INT | S0_INT |

| WC       | WC      | WC      | - | AC     | AC     | AC     | AC     |

| Bit   | Symbol   | Description                                                         |

|-------|----------|---------------------------------------------------------------------|

|       |          | IP Conflict                                                         |

| 7     | CONFLICT | Read 1 : IP Conflict                                                |

|       |          | Read 0 : -                                                          |

|       |          | Destination Port Unreachable                                        |

|       |          | When receiving the ICMP (Destination port unreachable) packet, this |

|       |          | Bit is set as '1'. And Destination Information, IP Address and Port |

| 6     | UNREACH  | Number, is written on UIPR & UPORTR.                                |

|       |          |                                                                     |

|       |          | Read 1 : Unreachable Packet receive                                 |

|       |          | Read 0 : -                                                          |

|       |          | PPPoE Terminated                                                    |

| 5     | PPPTERM  | Read 1 : Received PPPT or LCPT Packet only on PPPoE                 |

|       |          | Read 0 : -                                                          |

| 4     | -        | Reserved                                                            |

|       |          | SOCKET n Interrupt                                                  |

| [3:0] | Sn_INT   | Read 1 : Each n-th Bit describes SOCKET n-th Interrupt.             |

|       |          | Read 0 : When Sn_IR is 0x00, Sn_INT bit is Auto-Clear as '0'        |

#### 3.1.8 IMR (Interrupt Mask Register) [R=W] [0x0016] [0x00]

IMR is used for the corresponding IR Bit Mask.

| 7    | 6       | 5       | 4 | 3      | 2      | 1      | 0      |

|------|---------|---------|---|--------|--------|--------|--------|

| CNFT | UNREACH | PPPTERM | - | S3_INT | S2_INT | S1_INT | S0_INT |

| R=W  | R=W     | R=W     |   | R=W    | R=W    | R=W    | R=W    |

| Bit | Symbol  | Description                                 |

|-----|---------|---------------------------------------------|

|     |         | IP Conflict Interrupt Mask                  |

| 7   | CNFT    | 1 : Enable IP Conflict Interrupt            |

|     |         | 0 : Disable IP Conflict Interrupt           |

| 6   | UNREACH | Destination Port Unreachable Interrupt Mask |

|   |         | 1 : Enable Destination Port Unreachable Interrupt  |

|---|---------|----------------------------------------------------|

|   |         | 0 : Disable Destination Port Unreachable Interrupt |

|   |         | PADT/LCPT Interrupt Mask                           |

| 5 | PPPTERM | 1 : Enable PADT/LCPT Interrupt                     |

|   |         | 0 : Disable PADT/LCPT Interrupt                    |

| 4 | -       | Reserved                                           |

|   |         | SOCKET 3 Interrupt Mask                            |

| 3 | S3_INT  | 1 : Enable SOCKET 3 Interrupt                      |

|   |         | 0 : Disable SOCKET 3 Interrupt                     |

|   |         | SOCKET 2 Interrupt Mask                            |

| 2 | S2_INT  | 1 : Enable SOCKET 2 Interrupt                      |

|   |         | 0 : Disable SOCKET 2 Interrupt                     |

|   |         | SOCKET 1 Interrupt Mask                            |

| 1 | S1_INT  | 1 : Enable SOCKET 1 Interrupt                      |

|   |         | 0 : Disable SOCKET 1 Interrupt                     |

|   |         | SOCKET 0 Interrupt Mask                            |

| 0 | S0_INT  | 1 : Enable SOCKET 0 Interrupt                      |

|   |         | 0 : Disable SOCKET 0 Interrupt                     |

|   |         |                                                    |

#### 3.1.9 RTR (Retransmission Time Register) [R=W] [0x0017-0x0018] [0x07D0]

RTR sets initial value of Sn\_RTR (SOCKET n Retransmission Time Register). The unit is 100us. RTR and RCR (Retransmission Counter Register) set ARP & TCP Retransmission. (Ref 4.8 Retransmission)

Ex) RTR = 5000 (0x1388)

5000\*100us = 0.5s

| RTR0(0x0017) | RTR1(0x0018) |

|--------------|--------------|

| 0x13         | 0x88         |

#### 3.1.10 RCR (Retransmission Count Register) [R=W] [0x0019] [0x08]

RCR sets initial value of Sn\_RCR (SOCKET n Retransmission Count Register). RTR and RCR set ARP & TCP Retransmission. (Ref 4.8 Retransmission)

### 3.1.11 RMSR (RX Memory Size Register) [R=W] [0x001A] [0x55]

RMSR configures each SOCKET n RX Buffer Size. And the Sum of SOCKET n RX Buffer Size must not exceeded 8 Kbytes. (Ref Sn\_RXBUF\_SIZE (SOCKET n RX Buffer Size Register))

| 7        | 6  | 5        | 4  | 3        | 2  | 1        | 0  |

|----------|----|----------|----|----------|----|----------|----|

| SOCKET 3 |    | SOCKET 2 |    | SOCKET 1 |    | SOCKET 0 |    |

| S1       | SO | S1       | SO | S1       | SO | S1       | SO |

Each SOCKET n RX Buffer Size is set by SO and S1.

| Buffer Size | S1 | SO |

|-------------|----|----|

| 1 KB        | 0  | 0  |

| 2 KB        | 0  | 1  |

| 4 KB        | 1  | 0  |

| 8 KB        | 1  | 1  |

#### 3.1.12 TMSR (TX Memory Size Register) [R=W] [0x001B] [0x55]

TMSR configures each SOCKET n TX Buffer Block Size. And the sum of SOCKET n TX Buffer Block Size must not be exceeded 8 Kbytes. (Ref Sn\_TXBUF\_SIZE (SOCKET n TX Buffer Size Register))

| 7        | 6  | 5        | 4  | 3        | 2  | 1        | 0  |

|----------|----|----------|----|----------|----|----------|----|

| SOCKET 3 |    | SOCKET 2 |    | SOCKET 1 |    | SOCKET 0 |    |

| S1       | SO | S1       | SO | S1       | SO | S1       | S0 |

Each SOCKET n TX Buffer Block Size is set by S0 and S1.

| Buffer Size | S1 | SO |

|-------------|----|----|

| 1 KB        | 0  | 0  |

| 2 KB        | 0  | 1  |

| 4 KB        | 1  | 0  |

| 8 KB        | 1  | 1  |

# 3.1.13 IR2 (Interrupt Register 2) [RW] [0x0020] [0x00]

When WOL Event occurs, IR2 [WOL] is set to '1'. If the Event occurs and IMR2 [WOL] is set to '1' and internal Interrupt Pending Timer Counter is '0', INTn is asserted to Low. When the Event is cleared or IMR2 [WOL] is set to '0', INTn is de-asserted to High.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| ' | 0 | J | т | J | 2 | 1 | 0 |

| - | - | - | - | - | - | - | WOL |   |

|---|---|---|---|---|---|---|-----|---|

| - | - | - | - | - | - | - | WC  | ĺ |

| Bit   | Symbol | Description                              |

|-------|--------|------------------------------------------|

| [7:1] | -      | Reserved                                 |

|       |        | WOL MAGIC Packet Interrupt               |

| 0     | WOL    | 1 : Received UDP based WOL Magic Packet. |

|       |        | 0:-                                      |

# 3.1.14 IMR2 (Interrupt Mask Register 2) [R=W] [0x0021] [0x00]

IMR2 is used for the corresponding IR2 Bit Mask.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|---|---|---|---|---|---|---|-----|

| - | - | - | - | - | - | - | WOL |

| - | - | - | - | - | - | - | R=W |

| Bit   | Symbol | Description                            |

|-------|--------|----------------------------------------|

| [7:1] | -      | Reserved                               |

|       |        | WOL MAGIC Packet Interrupt Mask        |

| 0     | WOL    | 1 : Enable WOL MAGIC Packet Interrupt  |

|       |        | 0 : Disable WOL MAGIC Packet Interrupt |

# 3.1.15 PTIMER (PPP Link Control Protocol Request Timer Register)

#### [R=W] [0x0028] [0x28]

PTIMER configures the sending period for LCP Echo Request. The unit is 25ms.

```

Ex) PTIMER = 200 (0xC8),

```

200 \* 25ms = 5s

# 3.1.16 PMAGIC (PPP Link Control Protocol Magic number Register)

#### [R=W] [0x0029] [0x00]

PMAGIC configures 4 Bytes Magic Number for LCP Echo Request.

Ex) PMAGIC = 0x01

PMAGIC(0x0029)

0x01

#### LCP Magic Number = 0x01010101

#### 3.1.17 UIPR (Unreachable IP Address Register) [R0] [0x002A-0x002D] [0x0000]

When W5100S received Unreachable Packet (IR [UNR] = '1'), Peer IP Address in the Packet is written on UIPR.

Ex) UIPR = "192.169.0.21"

| UIPR0(0x002A) | UIPR1(0x002B) | UIPR2(0x002C) | UIPR3(0x002D) |

|---------------|---------------|---------------|---------------|

| 192(0xC0)     | 168(0xA8)     | 0(0x00)       | 21(0x15)      |

### 3.1.18 UPORTR (Unreachable Port Register) [RO] [0x002E-0x002F] [0x0000]

When W5100S received Unreachable Packet (IR [UNR] = '1'), Peer PORT Number in the Packet is written on UPORTR.

Ex) UPORTR = 3000 (0x0BB8)

| UPORTR0(0x002E) | UPORTR1(0x002F) |

|-----------------|-----------------|

| 0x0B            | 0xB8            |

#### 3.1.19 MR2 (Mode Register 2) [R=W] [0x0030] [0x40]

MR2 configures System Operation Clock (SYS\_CLK), Interrupt Activation, TCP & UDP Scan Prevention, WOL (Wake On LAN) and Force ARP.

| 7      | 6   | 5        | 4      | 3   | 2  | 1    | 0  |

|--------|-----|----------|--------|-----|----|------|----|

| CLKSEL | IEN | NOTCPRST | UDPURB | WOL | -  | FARP | -  |

| R=W    | R=W | R=W      | R=W    | R=W | W0 | R=W  | W0 |

| Bit | Symbol | Description                                                                                                                                                                                         |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CLKSEL | <pre>System Operation Clock(SYS_CLK) Select When CLKLCKR (Clock Lock Register) is Unlock, this bit can only set. (Ref to 3.1.40 CLKLCKR (Clock Lock Register) [WO] [0x0070] [0x00]) 1 : 25MHz</pre> |

|                                                                 |          | 0 : Depends on PHYCR1[PWDN]                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|-----------------------------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                 |          | SYS_CLK selected by PHCR1 configuration.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|                                                                 |          | PHYCR1[PWDN] SYS_CLK                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                                                                 |          | 0 100 MHz                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|                                                                 |          | 1 25 MHz                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|                                                                 |          | INTn Enable / Disable                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 6                                                               | IEN      | 1 : INTn Enable                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

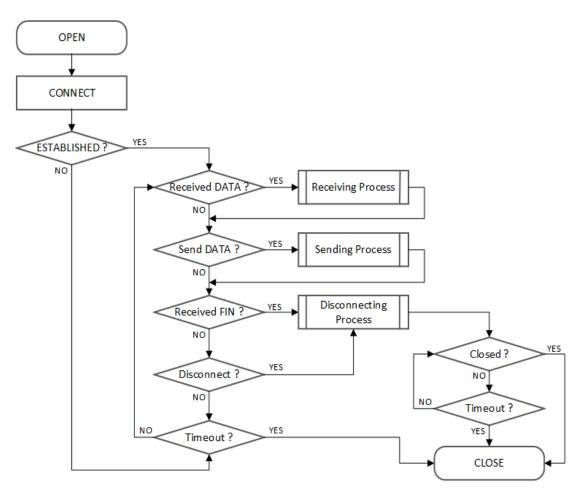

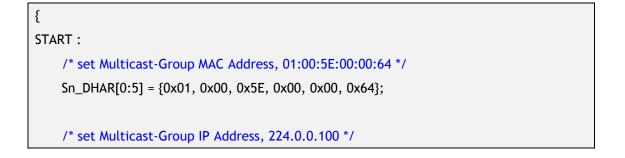

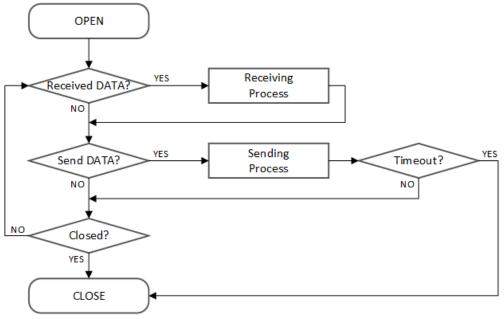

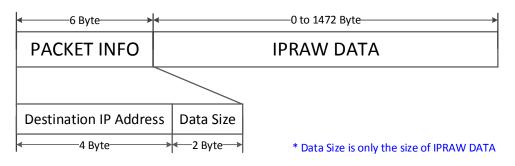

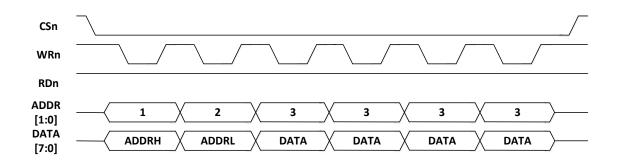

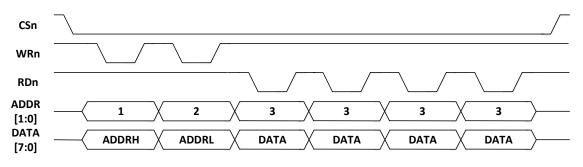

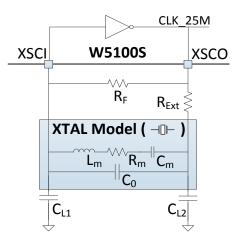

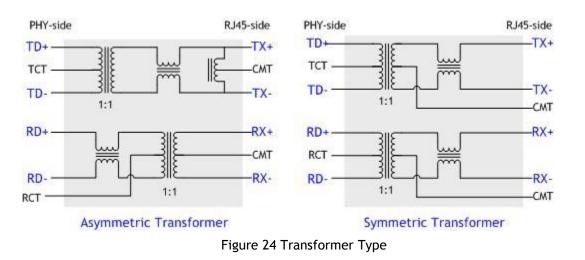

|                                                                 |          | 0 : INTn Disable (INTn is Always High)                                                                                                                                                                                                                                                                                                                                                                                    |  |  |