Wi2Wi, Inc. Doc No. ALT-PDT-DOC Rev.1.50 Data sheet, GPS Module – W2SG0008i January 22nd, 2014

# **Product Datasheet**

ALT-PDT-DOC Revision 1.50 January 22, 2014

## **Table of Contents**

| 1  | Ger          | neral Description                                                                       | 4        |

|----|--------------|-----------------------------------------------------------------------------------------|----------|

|    | 1.1          | Pin Definition                                                                          | 5        |

|    | 1.2          | Pin Configuration                                                                       |          |

|    | 1.3          | System Block Diagram                                                                    | 7        |

|    | 1.4          | Power Supply Considerations                                                             | 7        |

| 2  | Spe          | cifications                                                                             | 7        |

| 2  | 2.1          | Clock Frequency                                                                         | 7        |

| 2  | 2.2          | Interfaces                                                                              | 8        |

|    | 2.2.         |                                                                                         |          |

|    | 2.2.         |                                                                                         |          |

|    | 2.2.         |                                                                                         | 9        |

| 2  | 2.3          | Master Mode I <sup>2</sup> C Interface [Dead Reckoning (DR) I <sup>2</sup> C Interface] |          |

| 3  | Spe          | cific Pin Functions                                                                     | 9        |

| :  | 3.1          | Baud Rate Selection                                                                     | 9        |

|    | 3.2          | On / Off                                                                                | 10       |

| :  | 3.3          | Wake Up                                                                                 |          |

|    | 3.4          | External Interrupts (EIT1 & EIT2)                                                       |          |

|    | 3.5          | Time Mark (TM)                                                                          |          |

|    | 3.6          | Auto Start Feature                                                                      |          |

| 4  | WA           | AS with SBAS or Wide Area Differential GPS                                              |          |

|    | 4.1          | Differential GPS                                                                        |          |

|    | 4.2          | Wide Area DGPS or WAAS                                                                  |          |

|    | 4.3          | How do we enable WAAS-SBAS on the W2SG0008?                                             |          |

| 5  |              | ctrical/RF Characteristics: Operating                                                   |          |

| 6  | Per          | formance                                                                                | .15      |

| (  | 6.1          | Acquisition Time                                                                        | 15       |

|    | 6.2          | Position Accuracy (3-D NAV)                                                             |          |

|    | 5.3          | Environmental Characteristics                                                           |          |

| (  | 5.4          | Current and Power Consumption                                                           |          |

|    | 6.4.         |                                                                                         |          |

|    | 6.4.         |                                                                                         |          |

| 7  | Ant          | enna                                                                                    | 17       |

| 8  | Nor          | mal Mode of Operation                                                                   | .18      |

| 9  | Dev          | velopment Support                                                                       | .18      |

| 10 | Me           | chanical Information                                                                    | 19       |

|    | 10.1         | Mechanical Specification                                                                |          |

|    | 10.2         | Storage and Baking Instructions                                                         |          |

|    | 10.3         | Recommended Reflow Profile                                                              |          |

| 11 | Ord          | ering Information                                                                       |          |

|    | 11.1         | Evaluation Kits                                                                         |          |

|    |              |                                                                                         | .21      |

|    | 12.1         | Datasheet Status                                                                        |          |

| 13 |              | tifications                                                                             |          |

| 14 |              | erences                                                                                 |          |

|    | 14.1         | Specifications                                                                          |          |

|    | 14.1<br>14.2 | Trademarks, Patents and Licenses                                                        |          |

|    | 14.2         | Travemarks, I alemis and Licenses                                                       | <u> </u> |

#### List of Figures:

| Figure 1: Pin Configuration                                         | 6  |

|---------------------------------------------------------------------|----|

| Figure 2: System Block Diagram                                      |    |

| Figure 3: Power on Sequence                                         |    |

| Figure 4: Traditional DGPS System                                   |    |

| Figure 5: SBAS Example System                                       | 13 |

| Figure 6: Normal Mode of Operation (USB Dongle Reference Schematic) | 18 |

| Figure 7: Mechanical Dimensions                                     | 19 |

| Figure 10: Typical Lead-free Reflow Solder Profile                  | 20 |

| Figure 9: W2SG0008i Module on USB Dongle Evaluation Board           | 21 |

#### List of Tables:

| Table 1: Pin Definition                                        | . 5 |

|----------------------------------------------------------------|-----|

| Table 2: Absolute Maximum Ratings                              | . 8 |

| Table 3: Host Interface Selection                              | . 8 |

| Table 4: Pin Configuration for Baud Rate Selection at Start-up | . 9 |

| Table 5: Operating Electrical Characteristics                  | 14  |

| Table 6: Average Time to First Fix                             | 15  |

| Table 7: Positional Accuracy                                   | 15  |

| Table 8: Environmental Characteristics                         | 16  |

| Table 9: Current and Power Consumption                         | 16  |

| Table 10: Ordering Information                                 | 21  |

#### **Revision History:**

| Rev. | <b>Revision Date</b> | Originator | Changes                                                                                              |

|------|----------------------|------------|------------------------------------------------------------------------------------------------------|

| 1.0  | June 12, 2010        | WJL        | Initial draft                                                                                        |

| 1.1  | Dec 23, 2010         | WJL        | Updated Pin list, corrected text                                                                     |

| 1.31 | June 16, 2011        | WJL/ELK    | Added current consumption numbers/PN update                                                          |

| 1.32 | October 3, 2011      | WJL        | Updated power numbers, changed EMC status, added Time<br>Mark Pin info                               |

| 1.35 | December 16, 2011    | WJL        | Added 1Hz, Auto Start; and Updated Antenna Bias, SRESET                                              |

| 1.38 | February 22, 2012    | DDS        | Removed SRESET from text and reference schematic                                                     |

| 1.39 | March 8, 2012        | DDS        | Updated Figure 7 (Mechanical Dimensions) and Added<br>Section 12.3 (Baking, Storage Instructions)    |

| 1.4  | August 20, 2012      | DDS        | Added schematic, image and ordering information for USB<br>Dongle Eval-Board                         |

| 1.42 | October 4, 2012      | DDS        | Updated power and current consumption values                                                         |

| 1.45 | April 12, 2013       | DDS        | Added start-up configuration for baud-rate selection                                                 |

| 1.46 | May 30, 2013         | DDS        | Updated Section 2, added Table 3 for Host Interface Options                                          |

| 1.47 | June 6, 2013         | DDS        | Updated part-ordering information                                                                    |

| 1.48 | June 10, 2013        | WJL        | Added LNA gain settings                                                                              |

| 1.50 | January 22, 2014     | DDS        | Updated command to switch internal LNA from high-gain mode to low-gain mode, updated to MSL1 package |

## **1** General Description

This specification provides a general guideline on the performance and the integration of the Wi2Wi, Inc. NAVSTAR L1C/A Band, 48 Channel GPS Receiver Module Solution. The solder-down module, Part Number W2SG0008i is targeted to assist companies to easily integrate GPS functionally into their products. This is accomplished by reducing their development times and cost by using a complete, small form factor, low power, ready to integrate GPS Receiver System Solution.

W2SG0008i is a new and improved GPS solution based on SiRFStarIV<sup>TM</sup> chip set. The SiRFStarIV<sup>TM</sup> platform with SiRFAware<sup>TM</sup> GPS technology optimizes mobile phones, mobile computers, and mobile internet devices for location enabled services. Extremely low power consumption and fast location allows a broad range of location enabled services without compromising battery life or dependence on a network – from navigating to playing location-based games to searching for friends at the mall.

Key features of the W2SG0008i are as follows:

- GPS technology based upon SiRFStarIV<sup>TM</sup> by CSR/SiRF<sup>TM</sup>

- W2SG0008i uses a SiRFStarIV<sup>™</sup> Signature Series ROM v2.2

- Compact design for easy integration: 6.75 mm x 6.75 mm x 2 mm

- Fast, Responsive Location Experience

- 48 track verification channels

- SBAS (WAAS, EGNOS, MSAS, GAGAN)

- High Speed acquisition time and high sensitivity GPS Receiver

- High sensitivity navigation engine (PVT) tracks as low as -163dBm

- Breakthrough Power Consumption

- Adaptive micro power controller

- Ultra-low power consumption (Only 50 to 500µA maintains hot start capability)

- $\circ$  50 $\Omega$  Antenna Launch

- 48 verification channel GPS receiver

- Reliable in Difficult Environments

- Active Jammer Remover:

- Removes in-band jammers up to 80 dB-Hz

- Tracks up to 8 CW jammers

- SBAS/DGPS (WAAS, ENGOS, MSAS, GAGAN ) support

- Enhanced Navigation

- Smart MEMS sensor interface

- Multi-master I<sup>2</sup>C bus for smart sensors (Compass, Accelerometer)

- Interrupt input for context change alarms

### **1.1 Pin Definition**

The functional pin definition for the W2SG0008i is presented below in Table 1.

| 1  | GND0    | GND | Ground                       |                              |                                  |  |  |

|----|---------|-----|------------------------------|------------------------------|----------------------------------|--|--|

| 2  | I2C_CLK | CLK | Dead Reckoning I2C Clock     |                              |                                  |  |  |

| 3  | RTC     | 0   | Real Time Clock (32.768K H   | Real Time Clock (32.768K Hz) |                                  |  |  |

| 4  | CTS     | I/O | UART CTS                     | SPI Clock                    | HS0 PD                           |  |  |

| 5  | GND1    | GND | Ground                       |                              |                                  |  |  |

| 6  | I2C_DIO | I/O | Dead Reckoning I2C SDA       |                              |                                  |  |  |

| 7  | WAKEUP  | 0   | Wake up output for contro    | ol of external memory        |                                  |  |  |

| 8  | GND2    | GND | Ground                       |                              |                                  |  |  |

| 9  | EIT1    | I   | External Interrupt Trigger 1 | 1                            |                                  |  |  |

| 10 | GND3    | GND | Ground                       | Ground                       |                                  |  |  |

| 11 | NC      | I   | No Connection                |                              |                                  |  |  |

| 12 | GPS_TX  | 0   | SPI MISO (Default)           | UART Transmit                | I <sup>2</sup> C SCL             |  |  |

| 13 | RTS     | 0   | SPI nCS (Default)            | RTS                          | HS1 PU                           |  |  |

| 14 | ТМ      | 0   | UTC Time Mark Output         |                              |                                  |  |  |

| 15 | ANT_IN  | I   | Antenna input; 50 ohm im     | pedance                      |                                  |  |  |

| 16 | GPS_RX  |     | UART Receive Input port      | SPI MOSI                     | I <sup>2</sup> C SDA             |  |  |

| 17 | ON/OFF  | I   | Power State Control Pulse    | required to wake up d        | levice from power on sleep state |  |  |

| 18 | EIT2    |     | External Interrupt Trigger 2 | 2                            |                                  |  |  |

| 19 | GND4    | GND | Ground                       |                              |                                  |  |  |

| 20 | 1V8_IN  | PWR | 1.8V DC                      |                              |                                  |  |  |

| 21 | GND5    | GND | Ground (Corner Pad)          | Ground (Corner Pad)          |                                  |  |  |

| 22 | GND6    | GND | Ground (Corner Pad)          |                              |                                  |  |  |

| 23 | GND7    | GND | Ground (Corner Pad)          |                              |                                  |  |  |

| 24 | GND8    | GND | Ground (Corner Pad)          |                              |                                  |  |  |

#### **Table 1: Pin Definition**

\* Wi2Wi reserves the right to change the above information.

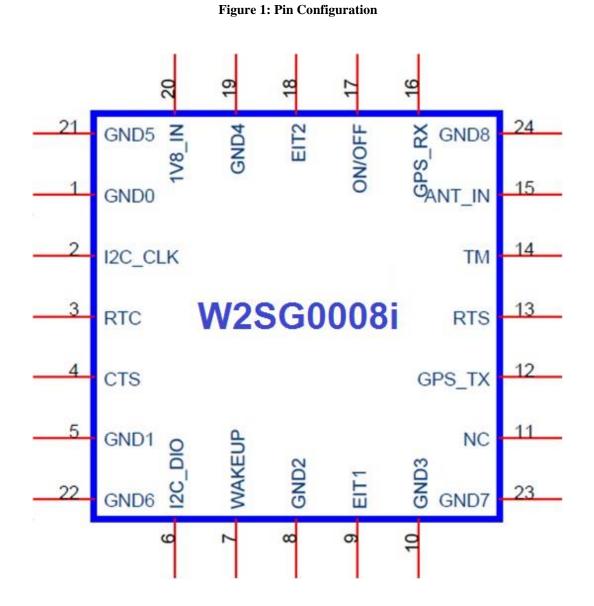

### **1.2 Pin Configuration**

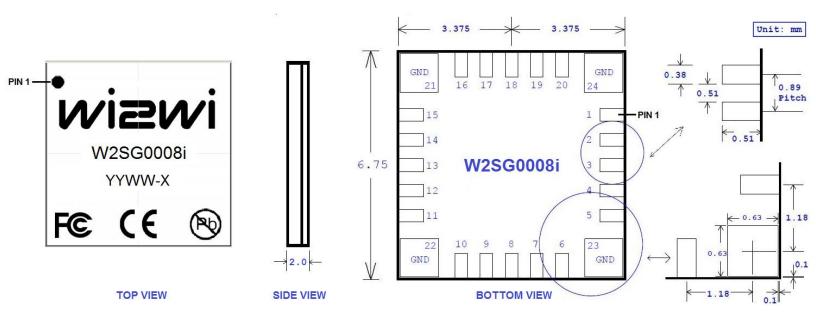

The W2SG0008i is a 24 pin SMD device with a board down antenna connection. The pin configuration is presented below in Figure 1.

Copyright © 2014 Wi2Wi, Inc.

Wi2Wi, Inc. Doc No. ALT-PDT-DOC Rev.1.50 Data sheet, GPS Module – W2SG0008i January 22nd, 2014

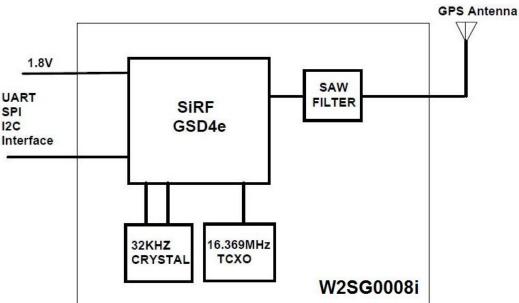

### 1.3 System Block Diagram

The System Block for the W2SG0008i is presented below in Figure 2.

Figure 2: System Block Diagram

The W2SG0008i provides an internal LNA, all required power regulation, and clocking. The TTL UART Interface is accessed via Pin 12 and 16.

### **1.4 Power Supply Considerations**

The W2SG0008i must be powered from a single 1.8V supply. The W2SG0008i does not support operation with separate voltage supply sources to different sections of the module. Customer designs with split voltage supply sources (for example, one for battery back-up supply and one for main current load), can be met by using a diode bridge combining the different sources into a single 1.8V supply to the W2SG0008i. The high current supply source can be enabled by the WAKEUP output pin; the low current back-up supply battery can be connected to one of the diode inputs. The supply controlled by WAKEUP must provide full power within 100  $\mu$ S of being enabled to prevent high current draw from the back-up source.

## 2 Specifications

### 2.1 Clock Frequency

The W2SG0008i features an internal clock and crystal and requires no external clock sources.

#### **Absolute Maximum Ratings:**

The values presented below in Table 2 are those parameters beyond which permanent damage could result. These values *do not* imply functional operation and should be considered as stress ratings only.

| Parameter                           | Symbol            | Rating     | Units |

|-------------------------------------|-------------------|------------|-------|

| Input Voltage                       | V <sub>DD</sub>   | 5.5        | V     |

| RF Input                            | RF <sub>IN</sub>  | 10         | dBm   |

| Case Temperature                    | T <sub>CASE</sub> |            | °C    |

| Lead Temperature (Soldering, 10sec) | T <sub>MFG</sub>  | 260        | °C    |

| Operating Temperature Range         | T <sub>A</sub>    | -40 to +85 | °C    |

| Storage Temperature Range           | Ts                | NA to +150 | °C    |

#### Table 2: Absolute Maximum Ratings

### 2.2 Interfaces

Table 3 below shows the pin configuration for GPIO6 / CTS (Pin 4) and GPIO 7 / RTS (Pin 13) for the selection of host interfaces.

#### Table 3: Host Interface Selection

| Host Interface                | GPIO6 / CTS (Pin 4) | GPIO7 / RTS (Pin 13) |

|-------------------------------|---------------------|----------------------|

| UART                          | High                | High                 |

| Slave SPI                     | Low                 | High                 |

| RESERVED                      | High                | Low                  |

| Multi-master I <sup>2</sup> C | Low                 | Low                  |

#### 2.2.1 Host UART Interface

The TTL UART Interface (Pins 12 and 16) has a baud rate 4800 BAUD. Protocol options for the W2SG0008i are NMEA and OSP<sup>TM</sup> (SiRF BINARY<sup>TM</sup>).

### 2.2.2 Host I<sup>2</sup>C Interface

The TTL I<sup>2</sup>C Interface (Pins 12 and 16) has a speed range of 400kbps. The default values for the I<sup>2</sup>C interface are: Rx: 0x60, Tx: 0x62

Operating mode is multi-master: The Transmit side operates as a master by seizing the I<sup>2</sup>C bus when detected idle, the Receive side operates as a slave when another master seizes bus and transmits to the module address. The I<sup>2</sup>C module implements the I<sup>2</sup>C bus standard contention resolution mechanism.

#### 2.2.3 Host Slave SPI

The Slave SPI (SSPI) is a 4-wire slave mode SPI port. The highest clock rate for Slave SPI is 6.840320MHz and supports both SPI and Micro wire formats. The transmitter and receiver have individual firmware-defined 2-byte idle patterns of 0xa7 & 0xb4. SPI detects synchronization errors and is reset by software.

The 4 SPI pins are:

- SSPI\_DO: slave SPI data output (MISO)

- SSPI\_DI: slave SPI data input (MOSI)

- SSPI\_CLK: slave SPI clock input (CLK)

- SSPI\_SS\_N: slave SPI chip select (CS#) active low

## 2.3 Master Mode I<sup>2</sup>C Interface [Dead Reckoning (DR) I<sup>2</sup>C Interface]

The W2SG0008i master mode I<sup>2</sup>C interface provides support for dead reckoning (DR). The master mode port has 2 pins: I2C\_DIO (Pin 6) and I2C\_CLK (Pin 2). Both pins are pseudo open-drain and require pull-up resistors on the external bus. Dead reckoning applications support the DR I<sup>2</sup>C interface. The I<sup>2</sup>C interface supports required sensor instruments such as gyros, accelerometers, compasses or other sensors that can operate with an I<sup>2</sup>C bus. DR I<sup>2</sup>C interface supports common sensor formats (accelerometer, gyro, magnetometer, altimeter, etc.). Typical data lengths are usually several bytes (command + in/out data). Standard I<sup>2</sup>C bus has a maximum data rate of 400 kbps and a minimum data rate of 100 kbps.

## **3** Specific Pin Functions

The pins related to special features of the W2SG0008i, which may or may not be used depending on a customer's design.

#### 3.1 Baud Rate Selection

I2C\_DIO (Pin 6) and I2C\_CLK (Pin 2) can be used to configure the W2SG0008i module to output NMEA at standard baud rates, if you are not using I2C or SPI flash devices on these pins. Table 4 below lists the settings for I2C\_DIO and I2C\_CLK to configure the baud rate at start-up. After start-up, these pins can be released for other purposes.

| I2C_DIO (Pin 6) | I2C_CLK (Pin 2) | Protocol | Baud Rate |

|-----------------|-----------------|----------|-----------|

| High            | High            | NMEA     | 4800      |

| High            | Low             | NMEA     | 9600      |

| Low             | High            | NMEA     | 38400     |

| Low             | Low             | OSP      | 115200    |

Table 4: Pin Configuration for Baud Rate Selection at Start-up

#### Note:

This flexibility is not available if any MEMS or non-volatile memory devices are attached to the auxiliary serial bus. The internal software default baud rate is 4800 when an EEPROM or SPI flash device is attached, but this can be changed via a CCK patch or an OSP message.

Failure to tie I2C\_DIO and I2C\_CLK high or low in the absence of both SPI flash and EEPROM causes an increase in standby and hibernate current, and also causes the startup configuration of the UART to be indeterminate.

### 3.2 On / Off

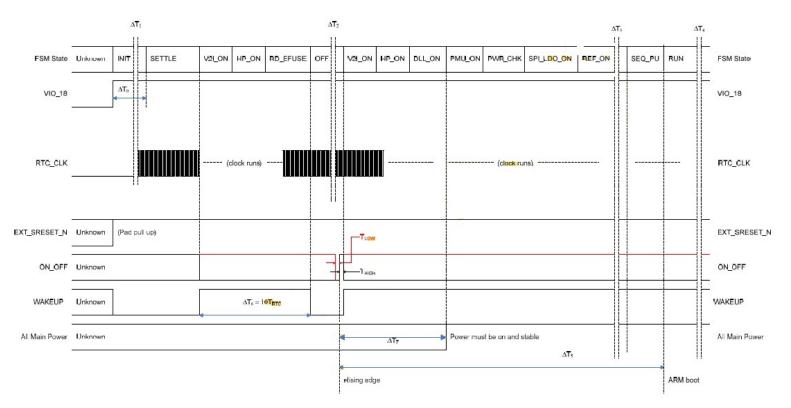

After power up, the W2SG0008i is in a hibernate state awaiting a pulse on the On/Off pin to put it into a fully active state. To enable the W2SG0008i a positive pulse for two RTC ticks (62uS) must be applied. To place the module back into a hibernate state, the same pulse needs to be applied to the On/Off signal after the Receiver has stabilized after a Fix (Stabilization can be up to 18 minutes depending on weather conditions). **This can be verified with a message ID 18, called "OK to Send", that comes out when the receiver is receptive to commands.** Figure 3 shows the internal state power up sequence of the SiRFStarIV<sup>TM</sup> inside the W2SG0008i, many of the signals listed are not accessible outside of the module, they are provided as reference only.

#### **Figure 3: Power on Sequence**

### 3.3 Wake Up

The WAKEUP pin is an output from the W2SG0008i used to enable an external PMIC (Power Management Integrated Circuit). A low on this output indicates that the W2SG0008i is in one of its low-power states (Hibernate or Standby mode) and requires no more than 60  $\mu$ A of current on the 1.8V power rail. A high on this output indicates that the W2SG0008i is in operational mode requiring an external regulator to provide enough current for normal operation of the W2SG0008i module.

### 3.4 External Interrupts (EIT1 & EIT2)

The EIT1 and EIT2 are external, level sensitive interrupts to the Modules internal ARM processor via the interrupt controller module. The EIT2 pin is also configurable as an edge-sensitive input. EIT is disabled at power-on hardware reset, and EIT2 is enabled as an input at power-on hardware reset.

Either pin can be used as a source of a level sensitive interrupt to wake-up the W2SG0008i from Standby and Hibernate low-power modes. This function allows external sensors, e.g. gyro, accelerometer, compass, etc., to provide an interrupt when a change of state is detected.

Either pin can be used as an interrupt source for the module.

### 3.5 Time Mark (TM)

The Time Mark pin [14] functions as follows: the Time Mark output provides a one pulse-per second (1pps) signal to the customer's application processor. When the receiver provides a valid navigation solution which consists of five satellite vehicles, the rising edge of each TMARK pulse is synchronized with the UTC one second epochs to within  $\pm 1$  microsecond. The receiver software produces a binary format data message containing the UTC time associated with each time mark pulse. This signal is a positive logic, buffered CMOS level output pulse that transitions from a logic "low" condition to logic "high" at a 1 Hz rate. The TMARK output pulse rise time is typically less than 2 nanoseconds and the pulse duration is typically 200 milliseconds.

#### **Patch Option:**

A patch exists that allows the Time Mark to output the 1 PPS with only four satellite vehicles instead of the default of five satellites. This patch can be downloaded from the Wi2Wi Extranet and implemented with the GPS patch manager that will run on Windows 7 and Linux operating systems. Please register at <u>www.wi2wi.com</u> to download from the extranet site.

#### 3.6 Auto Start Feature

It has been determined that by connecting the Wake-Up Pin [7] to the On/Off Pin [17] will automatically turn on the part upon power up. This will enable the customer to Auto enable or Auto Wake up the part. To put the part into sleep would require that this connection not be made and that a positive going pulse is initiated to put the part into a hibernate state.

## 4 WAAS with SBAS or Wide Area Differential GPS

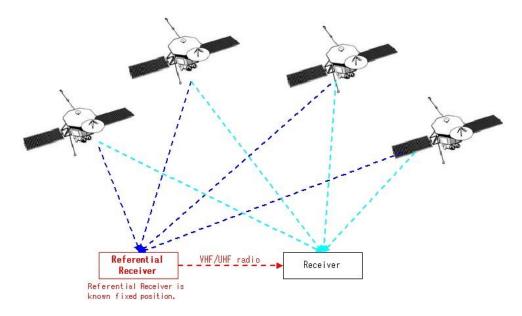

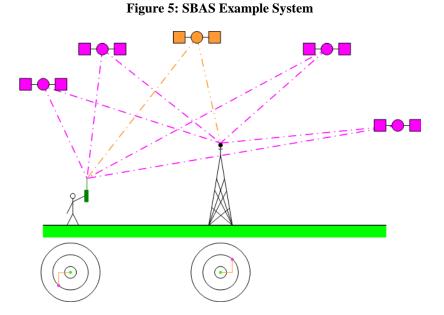

### 4.1 Differential GPS

Differential GPS (DGPS) is traditionally used with the fix of three to four satellites and the secondary fix from ground based GPS receiver based stations that retransmit the secondary fix via VHF/UHF and occasionally FM. DGPS can achieve positional accuracies of between 60 cm  $\sim 10$  cm/s. See Figure 4.

#### Figure 4: Traditional DGPS System

DGPS requires at least two antennas, one for the NavStar L1 CA signal from the satellite and one antenna for the secondary fix from the VHF/UHF/FM transmitter. Also a secondary application processor is used to perform "Mixing" calculations between the two fixes. This increases the size and the expenses of the system.

### 4.2 Wide Area DGPS or WAAS

Wide Area DGPS or WAAS (Wide Area Augmentation System) uses the same concept but eliminates the need for the secondary RF signal. It accomplishes this by reusing the already orbiting satellites to re-broadcast other secondary fixes that have been established by ground based master stations in North America and Hawaii, to measure small variations in the GPS satellites' signals in the western Hemisphere. Measurements from the reference stations are routed to master stations, which queue the received Deviation Correction (DC) and send the correction messages to geostationary WAAS satellites in a timely manner (every 5 seconds or better). These master stations rebroadcast the secondary fix to the NavStar satellites which broadcast the secondary fix on unused channel space. This enables a GPS receiver to utilize the same antenna to reprocess both fixes internal to it also eliminating the need for a secondary application processor. WAAS enables a GPS receiver to provide positional accuracy to 300 cm  $\sim$  200 cm. Of course a GPS receiver utilizing WAAS will need an expanded offering of GPS receiver channels to effective use this feature like the W2SG0008i which has 48 channels available for this function.

As noted this system was originally developed for the U.S. and Northern Hemisphere Geography. As GPS became ubiquitous in technology use throughout the world, similar systems called generically as Satellite-Based Augmentation System (SBAS). A SBAS is a system that supports wide-area or regional augmentation through the use of additional satellite-broadcast messages. Such systems are commonly composed of multiple ground stations, located at accurately-surveyed points. The ground stations take measurements of one or more of the GNSS satellites, the satellite signals, or other environmental factors which may impact the signal received by the users. Using these measurements, information messages are created and sent to one or more satellites for broadcast to the end users.

While SBAS designs and implementations may vary widely, with SBAS being a general term referring to any such satellite-based augmentation system, under the International Civil Aviation Organization (ICAO) rules a SBAS must transmit a specific message format and frequency which matches the design of the United State's Wide Area Augmentation System.

Some examples of these are (GPS Aided GEO Augmented Navigation) GAGAN developed for the Indian Sub-Continent, European Geostationary Navigation Overlay Service (EGNOS) developed for the European Union, and the Japanese Multi-functional Satellite Augmentation System (MSAS), respectively.

#### 4.3 How do we enable WAAS-SBAS on the W2SG0008?

WAAS-SBAS is enabled by issuing Message ID 133, (MID 133) is supported in One Socket Protocol (Formerly SiRF<sup>™</sup> Binary Protocol mode), and then the accuracy improves to 300 cm ~ 100 cm with it enabled, depending on Open Sky Conditions (Multi-Path interference). With MID 133 not enabled, the accuracy is near 1500 cm.

## 5 Electrical/RF Characteristics: Operating

Table 5 below presents the normal limits of operation for the W2SG0008i. Operations of the W2SG0008i beyond the limits of these tables are not recommended and may result in permanent damage of the device. Unless otherwise specified, operating conditions are over  $T_A = -30^{\circ}$ C to  $+85^{\circ}$ C. Typical is defined as  $T_A = +25^{\circ}$ C.

| Parameter <sup>1</sup>                              | Symbol             | Min.                    | Typ.   | Max.  | Units |  |  |

|-----------------------------------------------------|--------------------|-------------------------|--------|-------|-------|--|--|

| Power Supply (V <sub>cc</sub> )                     |                    |                         |        |       |       |  |  |

| Power Supply Voltage                                | V <sub>CC</sub>    | 1.71                    | 1.80   | 1.89  | V     |  |  |

| I/O Supply Voltage                                  | V <sub>IO</sub>    | 1.71                    | 1.80   | 1.89  | V     |  |  |

| Power Supply Ripple                                 | $V_{RIP}$          |                         |        | 100   | mV    |  |  |

| I/O Input Current                                   | I <sub>IO</sub>    |                         | 1.5    | 2.0   | mA    |  |  |

| Curre                                               | ent Consumpt       | tion (I <sub>CC</sub> ) |        |       |       |  |  |

| Acquisition Mode Current                            | $I_{CC\_ACQ}$      | 40                      | 44     | 50    | mA    |  |  |

| Tracking Mode Current                               | I <sub>CC_TR</sub> | 30                      | 34     | 40    | mA    |  |  |

| Power Save Mode Current                             | $I_{CC_{PS}}$      | 25                      | 27     | 30    | μA    |  |  |

| UAR                                                 | Г Interface (7     | ΓX, RX)                 |        |       |       |  |  |

| Input Pin Voltage                                   | VRX                |                         | 1.8    | 3.6   | V     |  |  |

| Output Pin Voltage                                  | VTX                |                         | 1.8    |       | V     |  |  |

|                                                     | nable (GPS_        | ON/OFF)                 |        |       |       |  |  |

| Input Pin Low Voltage                               | $V_{IL}$           | 0                       |        | 0.45  | V     |  |  |

| Input Pin High Voltage                              | $V_{IH}$           | 1.35                    | 1.8    | 3.6   | V     |  |  |

|                                                     | RF Input           |                         |        |       | -     |  |  |

| Input Impedance                                     | R <sub>ANT</sub>   |                         | 50     |       | Ω     |  |  |

| Operating Frequency                                 | F <sub>OPR</sub>   |                         | 1.575  |       | GHz   |  |  |

|                                                     | F Characteri       | stics                   |        |       | -     |  |  |

| Power In @1.5745 GHz                                | $P_{IN}$           | -157                    | -131   | -10   | dBm   |  |  |

| Noise Figure                                        | NF                 |                         | 3.0    |       | dB    |  |  |

| Input IP2 (f1=849MHz, f2=2424MHz) -30dBm in         | IIP2               |                         | 5      |       | dBm   |  |  |

| Input IP3 (f1=1574.5MHz, f2=1575.5MHz)<br>-30dBm in | IIP3               |                         | -2     |       | dBm   |  |  |

| Input Return Loss                                   | RL <sub>IN</sub>   |                         | -10.0  |       | dB    |  |  |

| Input VWR                                           | VWR <sub>IN</sub>  |                         | 1.50:1 | 1.8:1 |       |  |  |

| Reverse Isolation                                   | ISL                |                         | -28    |       | dB    |  |  |

|                                                     | lity (100 -100     | 00 MHz)                 |        |       | -     |  |  |

| Receiver Sensitivity:                               |                    |                         |        |       |       |  |  |

| •Signal Acquisition @ 31dBHz                        | P <sub>ACQ</sub>   |                         | -148   |       | dBm   |  |  |

| •Signal Tracking                                    | P <sub>TR</sub>    |                         | -163   | -     | dBm   |  |  |

#### **Table 5: Operating Electrical Characteristics**

Notes:

<sup>1</sup> All parameters are at TA = 25C°, unless otherwise specified.

<sup>2</sup> Defined as peak current drawn during initial acquisition operation of GPS Receiver.

## 6 Performance

### 6.1 Acquisition Time

The average Time to First Fix (TTFF) for the W2SG0008i when integrated with the W2SG0008i-DEV Development System is presented in Table 6 below:

| Parameter <sup>1</sup>             | Symbol                      | Min | Typ. | Max. | Units |

|------------------------------------|-----------------------------|-----|------|------|-------|

| Hot Start – Typ. Signal @ -140 dBm | TTFF <sub>TYP</sub>         | -   | 0.7  | <1.0 | S     |

| Hot Start – Low Signal @ - 146 dBm | <b>TTFF</b> <sub>LOW</sub>  | -   | 1.0  | -    | S     |

| Hot Start – Weak Signal@ - 150 dBm | <b>TTFF</b> <sub>WEAK</sub> | -   | 2.0  | -    | S     |

| Cold Start @ -130 dBm              | TTFF <sub>CLD</sub>         | -   | 35   | -    | S     |

| Cold Start @ -140 dBm              | TTFF <sub>CLD</sub>         | -   | 37   | -    | S     |

| Cold Start @ -146 dBm              | TTFF <sub>CLD</sub>         | -   | 38   | -    | S     |

| Cold Start @ -150 dBm              | TTFF <sub>CLD</sub>         | -   | 45   | -    | S     |

#### **Table 6: Average Time to First Fix**

#### Notes:

<sup>1</sup> Stationary receiver, unless otherwise specified.

<sup>2</sup> All parameters are at TA =  $25^{\circ}$ C, unless otherwise specified.

### 6.2 Position Accuracy (3-D NAV)

Table 7 below presents the Positional Accuracy for the W2SG0008i when integrated with the W2SG0008i-DEV Development System.

#### Table 7: Positional Accuracy

| Parameter <sup>1</sup>                    | Тур. | Units |

|-------------------------------------------|------|-------|

| Horizontal Position Accuracy: CEP (50%)   | 2.5  | m     |

| Horizontal Position Accuracy: 2dRMS (95%) | 5    | m     |

| Vertical Position Accuracy: CEP (50%)     | 3    | m     |

| Vertical Position Accuracy: 2dRMS (95%)   | 5    | m     |

| Horizontal Velocity Accuracy: Deviation   | 0.01 | m/s   |

| Vertical Velocity Accuracy: Deviation     | 0.4  | m/s   |

#### Notes:

<sup>1</sup> Stationary receiver, Open Sky at -130dBm, unless otherwise specified.

<sup>2</sup> All parameters are at TA = 25 °C, unless otherwise specified.

### 6.3 Environmental Characteristics

Table 8 establishes the environmental limits for operational use of the W2SG0008i.

| Parameter             | Symbol           | Min | Тур. | Max.          | Units            |

|-----------------------|------------------|-----|------|---------------|------------------|

| Storage Temperature   | T <sub>STR</sub> | NA  | -    | +150          | C°               |

| Operating Temperature | T <sub>OPR</sub> | -40 | +25  | +85           | C°               |

| Humidity              |                  | 5   | -    | 95            | %/Non-condensing |

| Altitude              |                  | -   | -    | 60,000/18,288 | ft/m             |

| Acceleration          |                  | -   | -    | 6.0           | g                |

| Velocity              |                  |     |      | <1,000        | knots            |

#### Table 8: Environmental Characteristics

### 6.4 Current and Power Consumption

Table 9 shows the current and power consumption values in different modes of operation for W2SG0008i.

| Made of Organstian                  | Current |      | I Init | <b>Power</b> @ 1.8V |       | TT *4 |

|-------------------------------------|---------|------|--------|---------------------|-------|-------|

| Mode of Operation                   | Тур     | Max  | Unit   | Тур                 | Max   | Unit  |

| Acquisition Mode                    | 50.5    | 63.5 | mA     | 90.9                | 114.3 | mW    |

| Tracking Mode                       | 33.5    | 48.5 | mA     | 60.3                | 87.3  | mW    |

| Hibernate Mode /<br>Power Save Mode | 10.5    | 14.5 | μΑ     | 18.9                | 26.1  | μW    |

#### **Table 9: Current and Power Consumption**

#### 6.4.1 Internal LNA Gain

The W2SG008i is provided with an internal LNA amplifier with two selectable gain levels. In general, the high gain mode is intended for use with passive antennas, while the low gain mode is used when there is an external LNA as part of the RF front end (e.g. active antenna).

#### Note: By default, the internal LNA is configured in high gain mode.

The internal LNA must be configured in low gain mode, when an active antenna with an external LNA has to be used. To change the internal LNA to low gain mode, use the following steps:

- 1. Switch GPS Communication Protocol from NMEA to OSP mode.

- 2. Send Tracker Configuration Message (OSP MID 178, 02) (Disable Internal LNA and drive GPS\_EXT-LNA\_EN signal):

- 3. Wait for SiRFStarIV ACK: A0 A2 00 03 0B B2 00 00 BD B0 B3

- 4. Perform a Hot Start reset; Tracker Configuration setting requests in message (OSP MID 178, 02) will apply after performing this reset.

- 5. Wait for SiRFStarIV ACK: A0 A2 00 03 0B 80 00 00 8B B0 B3

- 6. Switch GPS Communication Protocol back to NMEA mode.

#### 6.4.2 Maximum RF Gain

- In high gain mode, a passive antenna acts as input. Total RF gain (sum of internal LNA gain, cable and filter losses) of  $\leq 5$  dB is considered acceptable.

- In low gain mode, an active antenna acts as input. Total RF gain (sum of external antenna gain, internal LNA gain, cable and filter losses) of 14 to 24 dB is considered acceptable.

## 7 Antenna

The W2SG0008i is designed to work with a passive or an active antenna. The GPS module incorporates an integrated LNA and it will work with either an active or a passive antenna.

For W2SG0008i Evaluation Kit, the selection of antenna is based on the following configuration:

- Onboard Passive Chip Antenna: JP1 open, R15 open, R16 connected

- External Active Antenna: JP1 connected, R15 connected, R16 open

W2SG0008i EVK-1 consists of both, onboard passive chip antenna and external active antenna; while W2SG0008i EVK-2 consists of only onboard passive chip antenna.

Wi2Wi, Inc. Doc No. ALT-PDT-DOC Rev.1.50 Data sheet, GPS Module - W2SG0008i January 22nd, 2014

## 8 Normal Mode of Operation

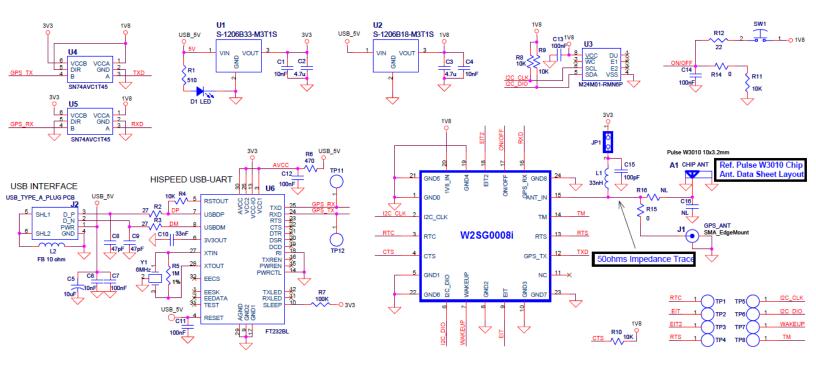

Figure 6 shows the normal mode of operation of W2SG0008i.

#### Figure 6: Normal Mode of Operation (USB Dongle Reference Schematic)

**Note:** Antenna selection is based on the following configuration:

**Onboard Passive Chip Antenna:**

JP1 open, R15 open, R16 connected

• External Active Antenna:

JP1 connected, R15 connected, R16 open

#### 9 **Development Support**

The W2SG0008i device is embedded with GPS software. This software is optimized to work in very weak signal environments to improve navigation availability and accuracy.

To enable GPS performance testing, Wi2Wi provides a W2SG0008i GPS Evaluation board, along with the SiRFLive software. SiRFLive is a PC tool that provides real-time monitoring of an attached GPS receiver's operation such as satellites being tracked, observed signal strength, and current position.

## **10 Mechanical Information**

### **10.1 Mechanical Specification**

The overall dimensions of the W2SG0008i are 6.75 mm x 6.75 mm x 2 mm. The module includes a shield. The general dimensions of the module are presented in Figure 7. The module is a Surface Mount Device (SMD). The measurements in Figure 7 are in mm, and are not to scale.

#### **Figure 7: Mechanical Dimensions**

Note: Refer to Ordering Information in Section 11.

- YY indicates Year

- WW indicates Work Week

- X indicates ROM version (e.g. B = ROM v2.2)

### **10.2 Storage and Baking Instructions**

W2SG0008i module is qualified as moisture sensitivity level MSL1 package, in accordance with JEDEC J-STD-020 standard.

MSL1 indicates that there are no special dry pack requirements or time limits from opening of static bag to reflow for floor conditions of  $\leq$  30°C and 85% RH

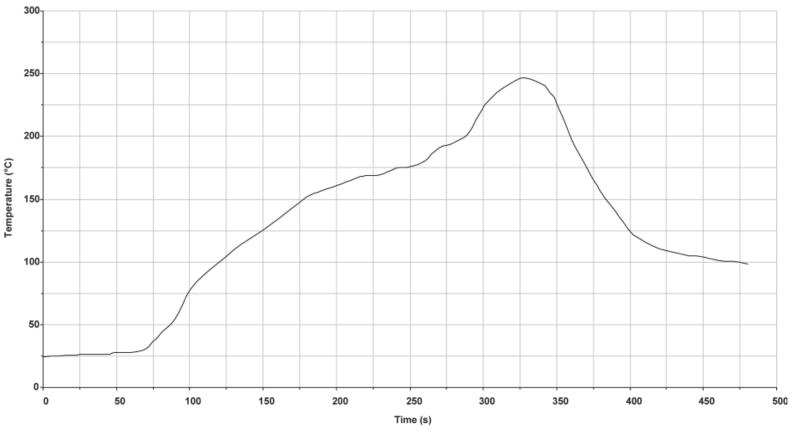

### **10.3 Recommended Reflow Profile**

The soldering profile depends on various parameters necessitating a setup for each application. The data here is given only for guidance on solder re-flow. There are four zones:

- <u>Preheat Zone</u>: This zone raises the temperature at a controlled rate, typically 1-2.5°C/s.

- <u>Equilibrium Zone</u>: This zone brings the board to a uniform temperature and also activates the flux. The duration in this zone (typically 2-3 minutes) will need to be adjusted to optimize the out gassing of the flux.

- <u>Reflow Zone</u>: The peak temperature should be high enough to achieve good wetting but not so high as to cause component discoloration or damage. Excessive soldering time can lead to intermetallic growth which can result in a brittle joint.

- <u>Cooling Zone</u>: The cooling rate should be fast, to keep the solder grains small which will give a longer lasting joint. Typical rates will be 2-5°C/s.

#### Figure 8: Typical Lead-free Reflow Solder Profile

Key features of the profile:

- Initial ramp =  $1-2.5^{\circ}$ C/sec to  $175^{\circ}$ C ±  $25^{\circ}$ C equilibrium

- Equilibrium time = 60 to 180 seconds

- Ramp to maximum temperature  $(245^{\circ}C) = 3^{\circ}C/sec$  max.

- Time above liquidus temperature  $(217^{\circ}C) = 45-90$  seconds

- Device absolute maximum reflow temperature =  $260^{\circ}$ C

## **11 Ordering Information**

| Table 10: Ordering Information |  |

|--------------------------------|--|

|--------------------------------|--|

| Part Order Number | Description                                                                    | Packing Method |  |

|-------------------|--------------------------------------------------------------------------------|----------------|--|

| W2SG0008i-B-T     | Baud Rate $= 4800$ bps                                                         | Tray           |  |

| W2SG0008i EVK-1   | USB Dongle with Integrated Passive Chip Antenna<br>and External Active Antenna | Box            |  |

| W2SG0008i EVK-2   | USB Dongle with Integrated Passive Chip Antenna                                | Box            |  |

### 11.1 Evaluation Kits

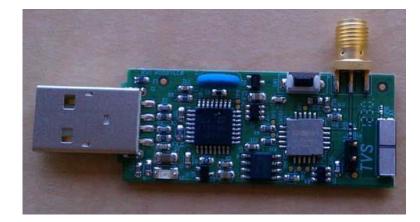

- <u>W2SG0008i EVK-1</u>: W2SG0008i USB Dongle Evaluation Kit with Active Antenna This kit is designed to provide a quick evaluation with the customer's host processor. It includes a USB Dongle with W2SG0008i module, onboard passive chip antenna, an external active antenna and an evaluation CD with Application Notes, Datasheet, Product Brief, Schematic, Quick Start Guide, SiRFLive software and other supporting documents.

- <u>W2SG0008i EVK-2</u>: W2SG0008i USB Dongle Evaluation Kit with Integrated Antenna This kit is designed to provide a quick evaluation with the customer's host processor. It includes a USB Dongle with W2SG0008i module, onboard passive chip antenna and an evaluation CD with Application Notes, Datasheet, Product Brief, Schematic, Quick Start Guide, SiRFLive software and other supporting documents.

#### Figure 9: W2SG0008i Module on USB Dongle Evaluation Board

## **12 Disclaimers**

Wi2Wi, Inc. PRODUCTS ARE NOT AUTHORISED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE MANAGING DIRECTOR OF Wi2Wi, Inc.

The definitions used herein are:

a) Life support devices or systems are devices which (1) are intended for surgical implant into the body, or (2) support or sustain life and whose failure to perform when properly used in accordance with the instructions for use provided in the labeling can reasonably be expected to result in a significant injury to the user. b) A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Wi2Wi does not assume responsibility for use of any of the circuitry described, no circuit patent licenses are implied and Wi2Wi reserves the right at any time to change without notice said circuitry and specifications.

#### **12.1 Datasheet Status**

Wi2Wi, Inc. reserves the right to change the specification without prior notice in order to improve the design and supply the best possible product. Updated information, firmware and release notes will be made available on <u>www.wi2wi.com</u>. Please check with Wi2Wi Inc. for the most recent data before initiating or completing a design.

## **13 Certifications**

The W2SG0008i conforms to the following standards when integrated to the Evaluation Kit.

EMC/Immunity

- FCC Part 15 Chapter B (USA)

- IC Canada (Canada)

- CE Mark (Europe)

## 14 References

#### 14.1 Specifications

- System Specification, SiRFStarIV<sup>™</sup> GSD4e BGA, Issue 5

- NMEA 0183 Version 3.01, January 2002, Addendum NMEA 0183-HS Version 1.0

- OSP Issue 9

- FAA WAAS Specification FAA-E 2892b

### 14.2 Trademarks, Patents and Licenses

- Trademarks: SiRF, SiRF logo, SiRFStar, are trademarks of SiRF Technology, Inc.

- Licenses: Software and firmware license from CSR/SiRF™

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Wi2Wi:

W2SG0008i-B-T W2SG0008i EVK-2 W2SG0008i EVK-1