www.vishay.com

## VS-FA57SA50LCP

**Vishay Semiconductors**

**RoHS** COMPLIANT

## Power MOSFET, 57 A

### FEATURES

- Fully isolated package

- Easy to use and parallel

- Low on-resistance

- Dynamic dV/dt rating

- Fully avalanche rated

- · Simple drive requirements

- · Low gate charge device

- Low drain to case capacitance

- Low internal inductance

- Designed for industrial level

- UL approved file E78996

- Material categorization: For definitions of compliance please see <u>www.vishay.com/doc?99912</u>

#### DESCRIPTION

Third Generation Power MOSFETs from Vishay Semiconductors provide the designer with the best combination of fast switching, ruggedized device design, low on-resistance and cost-effectiveness.

The SOT-227 package is universally preferred for all commercial-industrial applications at power dissipation levels to approximately 500 W. The low thermal resistance of the SOT-227 contribute to its wide acceptance throughout the industry.

| ABSOLUTE MAXIMUM RATINGS                         |                                   |                         |               |       |

|--------------------------------------------------|-----------------------------------|-------------------------|---------------|-------|

| PARAMETER                                        | SYMBOL                            | TEST CONDITIONS         | MAX.          | UNITS |

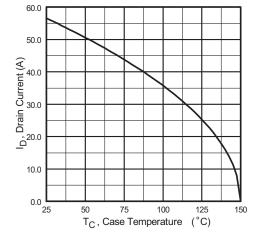

| Continuous drain current at V <sub>GS</sub> 10 V | I                                 | T <sub>C</sub> = 25 °C  | 57            |       |

| Continuous drain current at V <sub>GS</sub> 10 V | Ι <sub>D</sub>                    | T <sub>C</sub> = 100 °C | 36            | А     |

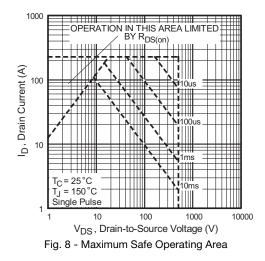

| Pulsed drain current                             | I <sub>DM</sub> <sup>(1)</sup>    |                         | 228           |       |

| Power dissipation                                | PD                                | T <sub>C</sub> = 25 °C  | 625           | W     |

| Linear derating factor                           |                                   |                         | 5.0           | W/°C  |

| Gate to source voltage                           | $V_{GS}$                          |                         | ± 20          | V     |

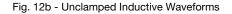

| Single pulse avalanche energy                    | E <sub>AS</sub> <sup>(2)</sup>    |                         | 725           | mJ    |

| Avalanche current                                | I <sub>AR</sub> <sup>(1)</sup>    |                         | 57            | А     |

| Repetitive avalanche energy                      | E <sub>AR</sub> <sup>(1)</sup>    |                         | 62.5          | mJ    |

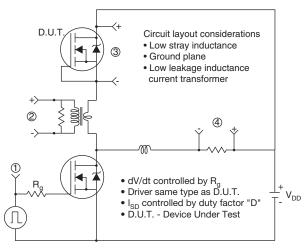

| Peak diode recovery dV/dt                        | dV/dt <sup>(3)</sup>              |                         | 10            | V/ns  |

| Operating junction and storage temperature range | T <sub>J</sub> , T <sub>Stg</sub> |                         | - 55 to + 150 | °C    |

| Insulation withstand voltage (AC-RMS)            | V <sub>ISO</sub>                  |                         | 2.5           | kV    |

| Mounting torque                                  |                                   | M4 screw                | 1.3           | Nm    |

Notes

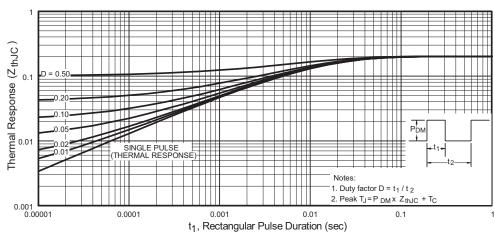

<sup>(1)</sup> Repetitive rating; pulse width limited by maximum junction temperature (see fig. 11)

$^{(2)}$  Starting  $T_J$  = 25 °C, L = 446  $\mu H,\,R_g$  = 25  $\Omega,\,I_{AS}$  = 57 A (see fig. 12)

$^{(3)}$  I\_{SD}  $\leq$  57 A, dI/dt  $\leq$  200 A/µs, V\_{DD}  $\leq$  V\_{(BR)DSS}, T\_J  $\leq$  150 °C

Revision: 08-Aug-13

1

Document Number: 94548

For technical questions within your region: <u>DiodesAmericas@vishay.com</u>, <u>DiodesAsia@vishay.com</u>, <u>DiodesEurope@vishay.com</u> THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT <u>www.vishay.com/doc?91000</u>

500 V

0.08 Ω

57 A

Modules - MOSFET

SOT-227

SOT-227

**PRODUCT SUMMARY**

VDSS

R<sub>DS(on)</sub>

$I_D$

Туре

Package

www.vishay.com

## VS-FA57SA50LCP

**Vishay Semiconductors**

| THERMAL AND MECHANICAL SPECIFICATIONS  |                                   |                       |      |      |      |       |

|----------------------------------------|-----------------------------------|-----------------------|------|------|------|-------|

| PARAMETER                              | SYMBOL                            | TEST CONDITIONS       | MIN. | TYP. | MAX. | UNITS |

| Junction and storage temperature range | T <sub>J</sub> , T <sub>Stg</sub> |                       | - 55 | -    | 150  | °C    |

| Junction to case                       | R <sub>thJC</sub>                 |                       | -    | -    | 0.20 | °C/W  |

| Case to heatsink                       | R <sub>thCS</sub>                 | Flat, greased surface | -    | 0.05 | -    | 0/10  |

| Weight                                 |                                   |                       | -    | 30   | -    | g     |

| Mounting torque                        |                                   |                       | -    | -    | 1.3  | Nm    |

| Case style                             | SOT-227                           |                       |      |      |      |       |

| <b>ELECTRICAL CHARACTERISTCS</b> (T <sub>J</sub> = 25 °C unless otherwise noted) |                                    |                                                                                              |      |        |       |       |  |

|----------------------------------------------------------------------------------|------------------------------------|----------------------------------------------------------------------------------------------|------|--------|-------|-------|--|

| PARAMETER                                                                        | SYMBOL                             | TEST CONDITIONS                                                                              | MIN. | TYP.   | MAX.  | UNITS |  |

| Drain to source breakdown voltage                                                | V <sub>(BR)DSS</sub>               | V <sub>GS</sub> = 0 V, I <sub>D</sub> = 1.0 mA                                               | 500  | -      | -     | V     |  |

| Breakdown voltage temperature coefficient                                        | $\Delta V_{(BR)DSS} / \Delta T_J$  | Reference to 25 °C, I <sub>D</sub> = 1 mA                                                    | -    | 0.62   | -     | V/°C  |  |

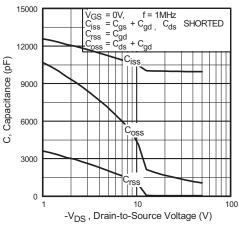

| Static drain to source on-resistance                                             | R <sub>DS(on)</sub> <sup>(1)</sup> | V <sub>GS</sub> = 10 V, I <sub>D</sub> = 34 A                                                | -    | -      | 0.08  | Ω     |  |

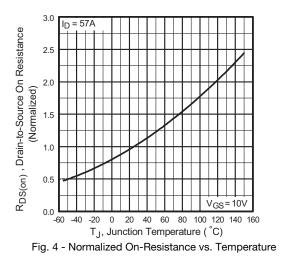

| Gate threshold voltage                                                           | V <sub>GS(th)</sub>                | $V_{DS} = V_{GS}, I_D = 250 \ \mu A$                                                         | 2.0  | -      | 4.0   | V     |  |

| Forward transconductance                                                         | 9 <sub>fs</sub>                    | V <sub>DS</sub> = 50 V, I <sub>D</sub> = 34 A                                                | 43   | -      | -     | S     |  |

|                                                                                  |                                    | $V_{DS} = 500 \text{ V}, \text{ V}_{GS} = 0 \text{ V}$                                       | -    | -      | 50    |       |  |

| Drain to source leakage current                                                  | IDSS                               | $V_{DS} = 400 \text{ V}, \text{ V}_{GS} = 0 \text{ V}, \text{ T}_{J} = 125 ^{\circ}\text{C}$ | -    | -      | 500   | μA    |  |

| Gate to source forward leakage                                                   |                                    | V <sub>GS</sub> = 20 V                                                                       | -    | -      | 200   | nA    |  |

| Gate to source reverse leakage                                                   | I <sub>GSS</sub>                   | V <sub>GS</sub> = - 20 V                                                                     | -    | -      | - 200 |       |  |

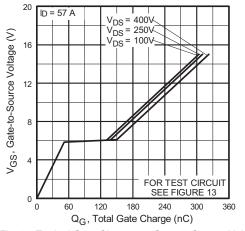

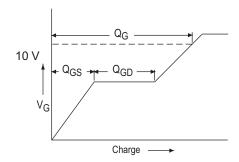

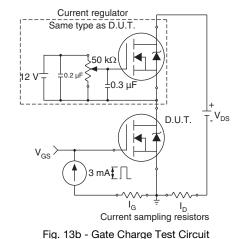

| Total gate charge                                                                | Qg                                 | I <sub>D</sub> = 57 A                                                                        | -    | 225    | 338   |       |  |

| Gate to source charge                                                            | Q <sub>gs</sub>                    | $V_{DS}$ = 400 V $V_{GS}$ = 10 V; see fig. 6 and 13 $^{(1)}$                                 | -    | 51     | 77    | nC    |  |

| Gate to drain ("Miller") charge                                                  | Q <sub>gd</sub>                    |                                                                                              | -    | 98     | 147   | 1     |  |

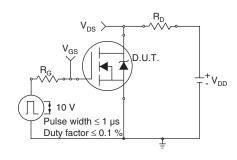

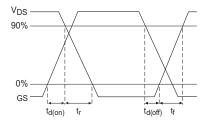

| Turn-on delay time                                                               | t <sub>d(on)</sub>                 | V <sub>DD</sub> = 250 V                                                                      | -    | 32     | -     |       |  |

| Rise time                                                                        | t <sub>r</sub>                     | $I_D = 57 \text{ A}$                                                                         | -    | 152    | -     |       |  |

| Turn-off delay time                                                              | t <sub>d(off)</sub>                | $R_g$ = 2.0 $\Omega$ (internal) $R_D$ = 4.3 $\Omega,$ see fig. 10 $^{(1)}$                   | -    | 108    | -     | - ns  |  |

| Fall time                                                                        | t <sub>f</sub>                     |                                                                                              | -    | 118    | -     |       |  |

| Internal source inductance                                                       | Ls                                 | Between lead, and center of die contact                                                      | -    | 5.0    | -     | nH    |  |

| Input capacitance                                                                | C <sub>iss</sub>                   | V <sub>GS</sub> = 0 V                                                                        | -    | 10 000 | -     |       |  |

| Output capacitance                                                               | C <sub>oss</sub>                   | $V_{DS} = 25 V$                                                                              | -    | 1500   | -     | pF    |  |

| Reverse transfer capacitance                                                     | C <sub>rss</sub>                   | f = 1.0 MHz, see fig. 5                                                                      | -    | 50     | -     | 1     |  |

#### Note

$^{(1)}\,$  Pulse width  $\leq 300~\mu s,~duty~cycle \leq 2~\%$

| SOURCE-DRAIN RATINGS AND CHARACTERISTICS |                                |                                                                                  |      |      |      |       |  |

|------------------------------------------|--------------------------------|----------------------------------------------------------------------------------|------|------|------|-------|--|

| PARAMETER                                | SYMBOL                         | TEST CONDITIONS                                                                  | MIN. | TYP. | MAX. | UNITS |  |

| Continuous source current (body diode)   | I <sub>S</sub>                 | MOSFET symbol showing                                                            | -    | -    | 57   |       |  |

| Pulsed source current (body diode)       | I <sub>SM</sub> <sup>(1)</sup> | the integral reverse p-n junction diode.                                         | -    | -    | 228  | A     |  |

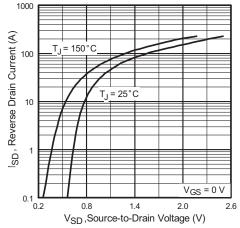

| Diode forward voltage                    | V <sub>SD</sub> <sup>(2)</sup> | $T_{J} = 25 \text{ °C}, I_{S} = 57 \text{ A}, V_{GS} = 0 \text{ V}$              | -    | -    | 1.3  | V     |  |

| Reverse recovery time                    | t <sub>rr</sub>                | − T <sub>J</sub> = 25 °C, I <sub>F</sub> = 57 A, dl/dt = 100 A/μs <sup>(2)</sup> | -    | 901  | 1351 | ns    |  |

| Reverse recovery charge                  | Q <sub>rr</sub>                | $1_{\rm J} = 25$ C, $1_{\rm F} = 57$ A, $dt/dt = 100$ A/ $\mu$ S $e^{-1}$        | -    | 15   | 23   | μC    |  |

| Forward turn-on time                     | t <sub>on</sub>                | Intrinsic turn-on time is negligible (turn-on is dominated by $L_{S} + L_{D}$ )  |      |      |      |       |  |

#### Notes

<sup>(1)</sup> Repetitive rating; pulse width limited by maximum junction temperature (see fig. 11)

$^{(2)}$  Pulse width  $\leq$  300  $\mu s,$  duty cycle  $\leq$  2  $\,\%$

Revision: 08-Aug-13

2

Document Number: 94548

For technical questions within your region: <u>DiodesAmericas@vishay.com</u>, <u>DiodesAsia@vishay.com</u>, <u>DiodesEurope@vishay.com</u> THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT <u>www.vishay.com/doc?91000</u>

VS-FA57SA50LCP

**Vishay Semiconductors**

Fig. 5 - Typical Capacitance vs. Drain to Source Voltage

Fig. 6 - Typical Gate Charge vs. Gate to Source Voltage

#### Revision: 08-Aug-13

3

Document Number: 94548

For technical questions within your region: <u>DiodesAmericas@vishay.com</u>, <u>DiodesAsia@vishay.com</u>, <u>DiodesEurope@vishay.com</u> THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT <u>www.vishay.com/doc?91000</u>

www.vishay.com

Fig. 7 - Typical Source Drain Diode Forward Voltage

VS-FA57SA50LCP

**Vishay Semiconductors**

Fig. 9 - Maximum Drain Current vs. Case Temperature

Fig. 10a - Switching Time Test Circuit

Fig. 10b - Switching Time Waveforms

## VS-FA57SA50LCP

Vishay Semiconductors

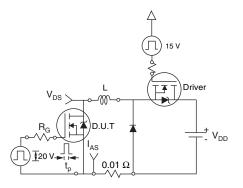

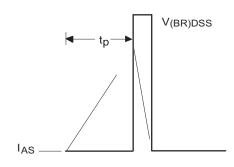

Fig. 12a - Unclamped Inductive Test Circuit

Fig. 12c - Maximum Avalanche Energy vs. Drain Current

VS-FA57SA50LCP

### **Vishay Semiconductors**

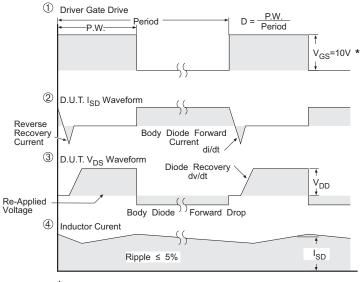

Fig. 13a - Basic Gate Charge Waveform

Fig. 13c - Peak Diode Recovery dV/dt Test Circuit

\* V<sub>GS</sub> = 5V for Logic Level Devices

Fig. 14 - For N-Channel Power MOSFETs

Revision: 08-Aug-13 Document Number: 94548 6 For technical questions within your region: DiodesAmericas@vishay.com, DiodesAsia@vishay.com, DiodesEurope@vishay.com THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

## VS-FA57SA50LCP

## Vishay Semiconductors

### **ORDERING INFORMATION TABLE**

| Device code | VS-                                                                                                                                                                         | F                                     | А                                                      | 57                                          | S                              | Α                    | 50 | LC | Р |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------------------------------------------|---------------------------------------------|--------------------------------|----------------------|----|----|---|

|             | 1                                                                                                                                                                           | 2                                     | 3                                                      | 4                                           | 5                              | 6                    | 7  | 8  | 9 |

|             | 1       -         2       -         3       -         3       -         4       -         5       -         6       -         7       -         8       -         9       - | Pov<br>Ger<br>Cur<br>Sin<br>SO<br>Vol | ver MOS<br>neration<br>rent rati<br>gle swite<br>T-227 | 3, MOS<br>ing (57 =<br>ch (see<br>ing (50 = | FET sili<br>57 A)<br>Circuit ( | icon, DE<br>Configur |    |    |   |

| CIRCUIT CONFIGURATION  |                               |            |                                                                         |  |  |  |

|------------------------|-------------------------------|------------|-------------------------------------------------------------------------|--|--|--|

| CIRCUIT                | CIRCUIT<br>CONFIGURATION CODE | CIRCUIT DR | AWING                                                                   |  |  |  |

| Single switch no diode | S                             | G (2)      | Lead assignment<br>$ \begin{array}{ccccccccccccccccccccccccccccccccccc$ |  |  |  |

| LINKS TO RELATED DOCUMENTS          |                          |  |  |  |  |  |

|-------------------------------------|--------------------------|--|--|--|--|--|

| Dimensions www.vishay.com/doc?95036 |                          |  |  |  |  |  |

| Packaging information               | www.vishay.com/doc?95037 |  |  |  |  |  |

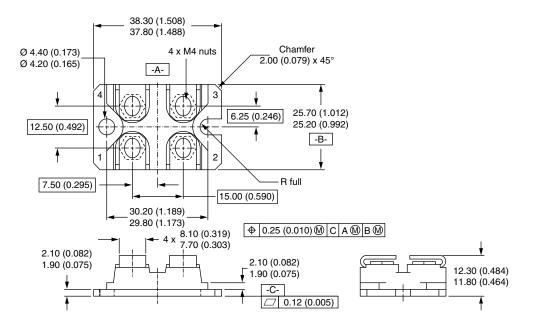

## **Outline Dimensions**

**Vishay Semiconductors**

SOT-227

### **DIMENSIONS** in millimeters (inches)

#### Notes

- Dimensioning and tolerancing per ANSI Y14.5M-1982

- Controlling dimension: millimeter

Vishay

## Disclaimer

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and/or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.

## **Material Category Policy**

Vishay Intertechnology, Inc. hereby certifies that all its products that are identified as RoHS-Compliant fulfill the definitions and restrictions defined under Directive 2011/65/EU of The European Parliament and of the Council of June 8, 2011 on the restriction of the use of certain hazardous substances in electrical and electronic equipment (EEE) - recast, unless otherwise specified as non-compliant.

Please note that some Vishay documentation may still make reference to RoHS Directive 2002/95/EC. We confirm that all the products identified as being compliant to Directive 2002/95/EC conform to Directive 2011/65/EU.

Vishay Intertechnology, Inc. hereby certifies that all its products that are identified as Halogen-Free follow Halogen-Free requirements as per JEDEC JS709A standards. Please note that some Vishay documentation may still make reference to the IEC 61249-2-21 definition. We confirm that all the products identified as being compliant to IEC 61249-2-21 conform to JEDEC JS709A standards.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Vishay: VS-FA57SA50LCP