## Dual N-Channel 2.5-V (G-S) Input Protected Load Switch

| PRODUCT SUMMARY     |                                 |                    |                      |

|---------------------|---------------------------------|--------------------|----------------------|

| V <sub>DS</sub> (V) | r <sub>DS(on)</sub> (Ω)         | I <sub>D</sub> (A) | Q <sub>g</sub> (Typ) |

| 20                  | 0.030 @ V <sub>GS</sub> = 4.5 V | 4.5                | 7.6                  |

|                     | 0.033 @ V <sub>GS</sub> = 3.0 V | 4.2                |                      |

|                     | 0.035 @ V <sub>GS</sub> = 2.5 V | 3.9                |                      |

**ESD Protected

2000 V**

### FEATURES

- Low r<sub>DS(on)</sub>

- V<sub>GS</sub> Max Rating: 14 V

- Exceeds 2-kV ESD Protection

### DESCRIPTION

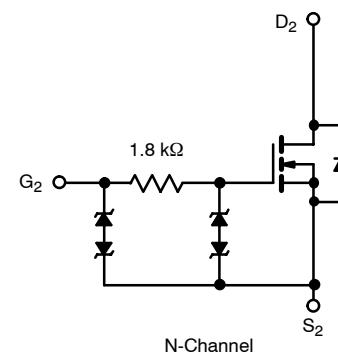

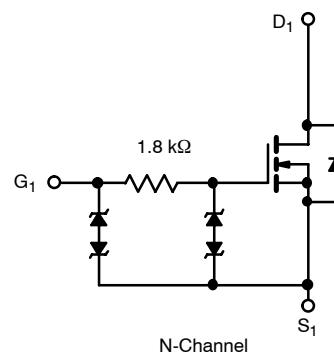

The Si6926AEDQ is a dual n-channel MOSFET with ESD protection and gate over-voltage protection circuitry incorporated into the MOSFET. The device is designed for use in Lithium Ion battery pack circuits. The 2-stage input protection circuit is a unique design, consisting of two stages of back-to-back zener diodes separated by a resistor. The first stage diode is designed to absorb most of the ESD energy. The second stage diode is designed to protect the gate from any

remaining ESD energy and over-voltages above the gates inherent safe operating range. The series resistor used to limit the current through the second stage diode during over voltage conditions has a maximum value which limits the input current to  $\leq 10$  mA @ 14 V and the maximum t<sub>off</sub> to 15  $\mu$ s. The Si6926AEDQ has been optimized as a battery or load switch in Lithium Ion applications with the advantage of both a 2.5-V r<sub>DS(on)</sub> rating and a safe 14-V gate-to-source maximum rating.

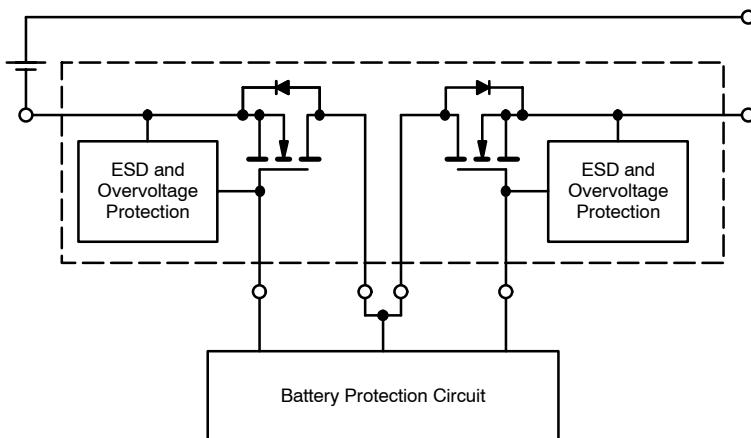

### APPLICATION CIRCUITS

Figure 1. Typical Use In a Lithium Ion Battery Pack

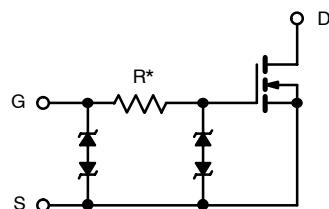

\*R typical value is 1.9 k $\Omega$  by design.

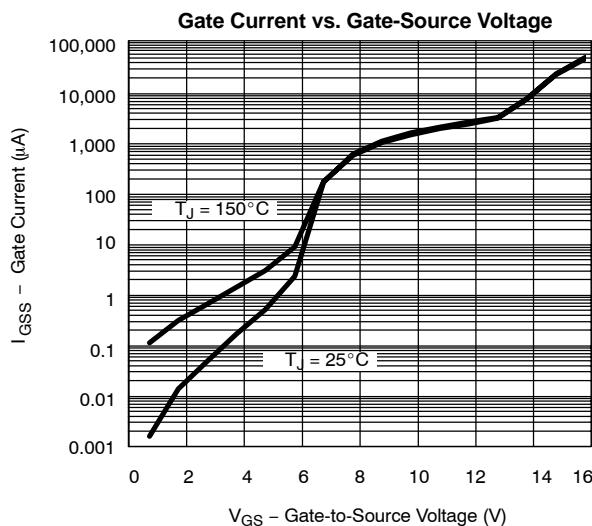

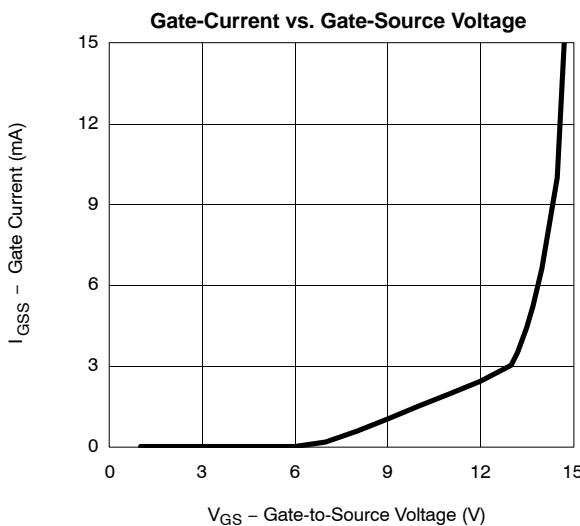

See Typical Characteristics,

Gate-Current vs. Gate-Source Voltage, Page 3.

Figure 2. Input ESD and Overvoltage Protection Circuit.

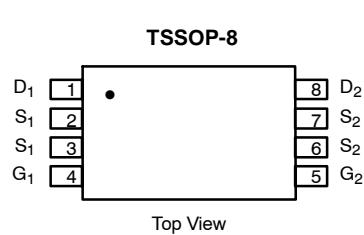

**FUNCTIONAL BLOCK DIAGRAM AND PIN CONFIGURATION**

Ordering Information: Si6926AEDQ-T1—E3

Figure 3.

Figure 4.

**ABSOLUTE MAXIMUM RATINGS ( $T_A = 25^\circ\text{C}$  UNLESS OTHERWISE NOTED)**

| Parameter                                                                     | Symbol         | 10 sec     | Steady State | Unit |

|-------------------------------------------------------------------------------|----------------|------------|--------------|------|

| Drain-Source Voltage, Source-Drain Voltage                                    | $V_{DS}$       | 20         | $\pm 14$     | V    |

| Gate-Source Voltage                                                           | $V_{GS}$       |            |              |      |

| Continuous Drain-to-Source Current ( $T_J = 150^\circ\text{C}$ ) <sup>a</sup> | $I_D$          | 4.5        | 4.1          | A    |

|                                                                               |                | 3.6        | 3.3          |      |

| Pulsed Drain-to-Source Current                                                | $I_{DM}$       | 20         |              |      |

| Pulsed Source Current (Diode Conduction) <sup>a</sup>                         | $I_S$          | 0.83       | 0.69         |      |

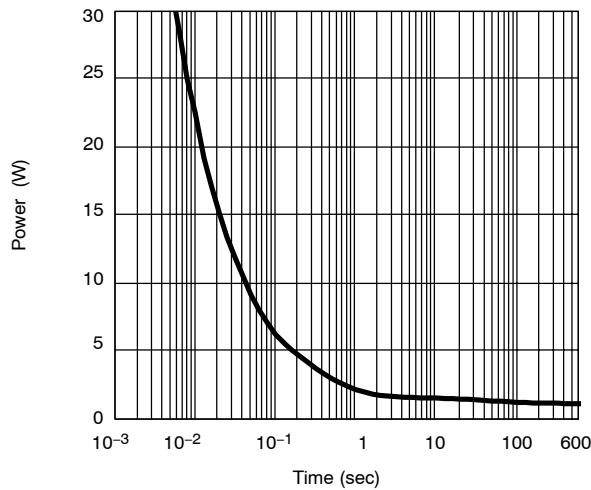

| Maximum Power Dissipation <sup>a</sup>                                        | $P_D$          | 1.0        | 0.83         | W    |

|                                                                               |                | 0.64       | 0.53         |      |

| Operating Junction and Storage Temperature Range                              | $T_J, T_{stg}$ | -55 to 150 |              | °C   |

**THERMAL RESISTANCE RATINGS**

| Parameter                                | Symbol                  | Typical    | Maximum | Unit |

|------------------------------------------|-------------------------|------------|---------|------|

| Maximum Junction-to-Ambient <sup>a</sup> | $t \leq 10 \text{ sec}$ | $R_{thJA}$ | 90      | 125  |

|                                          | Steady State            |            | 126     | 150  |

| Maximum Junction-to-Foot (Drain)         | $R_{thJF}$              | 65         | 80      |      |

Notes

a. Surface Mounted on FR4 Board.

**SPECIFICATIONS ( $T_J = 25^\circ\text{C}$  UNLESS OTHERWISE NOTED)**

| Parameter                                     | Symbol              | Test Condition                                                                                                 | Min | Typ   | Max      | Unit          |

|-----------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------|-----|-------|----------|---------------|

| <b>Static</b>                                 |                     |                                                                                                                |     |       |          |               |

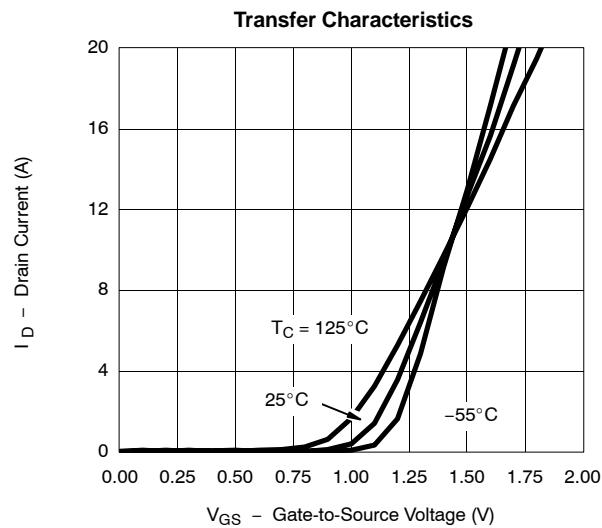

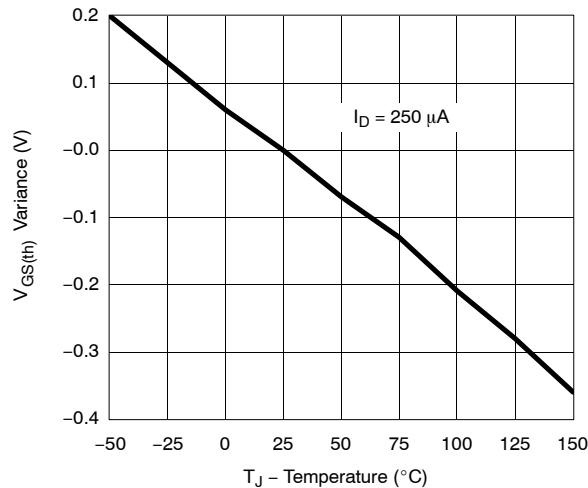

| Gate Threshold Voltage                        | $V_{GS(\text{th})}$ | $V_{DS} = V_{GS}, I_D = 250 \mu\text{A}$                                                                       | 0.4 |       | 1.2      | V             |

| Gate-Body Leakage                             | $I_{GSS}$           | $V_{DS} = 0 \text{ V}, V_{GS} = \pm 4.5 \text{ V}$                                                             |     |       | $\pm 1$  | $\mu\text{A}$ |

|                                               |                     | $V_{DS} = 0 \text{ V}, V_{GS} = \pm 12 \text{ V}$                                                              |     |       | $\pm 10$ | mA            |

| Zero Gate Voltage Drain Current               | $I_{DSS}$           | $V_{DS} = 20 \text{ V}, V_{GS} = 0 \text{ V}$                                                                  |     | 1     |          | $\mu\text{A}$ |

|                                               |                     | $V_{DS} = 20 \text{ V}, V_{GS} = 0 \text{ V}, T_J = 55^\circ\text{C}$                                          |     | 5     |          |               |

| On-State Drain Current <sup>b</sup>           | $I_{D(\text{on})}$  | $V_{DS} \geq 5 \text{ V}, V_{GS} = 5 \text{ V}$                                                                | 10  |       |          | A             |

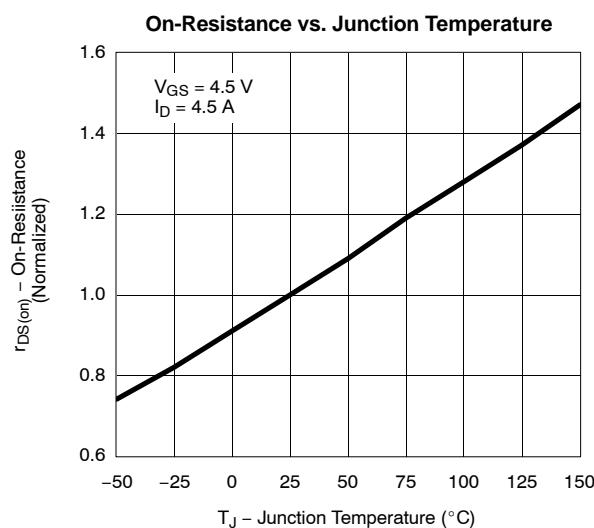

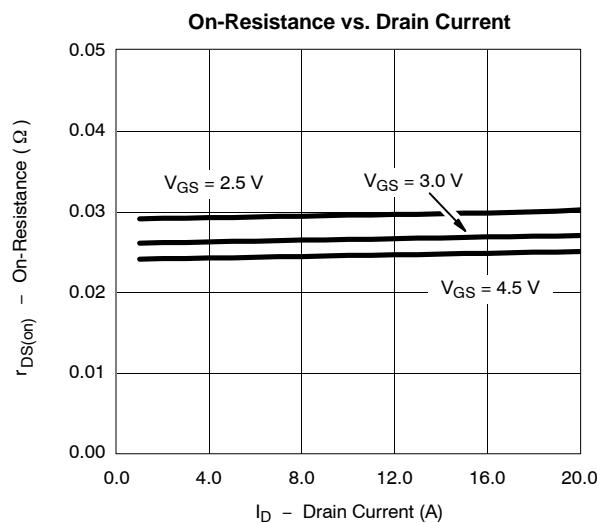

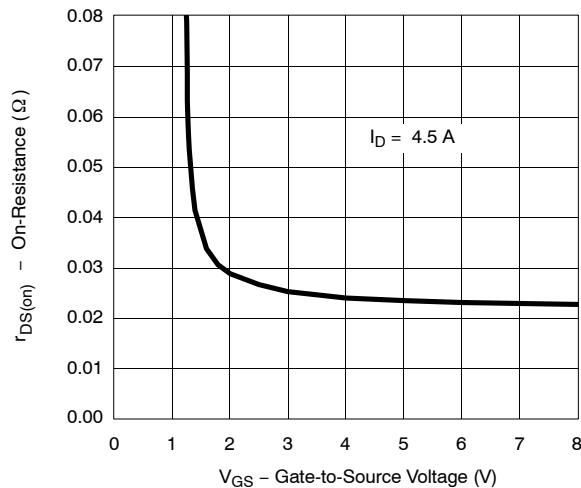

| Drain-Source On-State Resistance <sup>b</sup> | $r_{DS(\text{on})}$ | $V_{GS} = 4.5 \text{ V}, I_D = 4.5 \text{ A}$                                                                  |     | 0.023 | 0.030    | $\Omega$      |

|                                               |                     | $V_{GS} = 3.0 \text{ V}, I_D = 4.2 \text{ A}$                                                                  |     | 0.025 | 0.033    |               |

|                                               |                     | $V_{GS} = 2.5 \text{ V}, I_D = 3.9 \text{ A}$                                                                  |     | 0.027 | 0.035    |               |

| Forward Transconductance <sup>b</sup>         | $g_{fs}$            | $V_{DS} = 10 \text{ V}, I_D = 4.5 \text{ A}$                                                                   |     | 26    |          | S             |

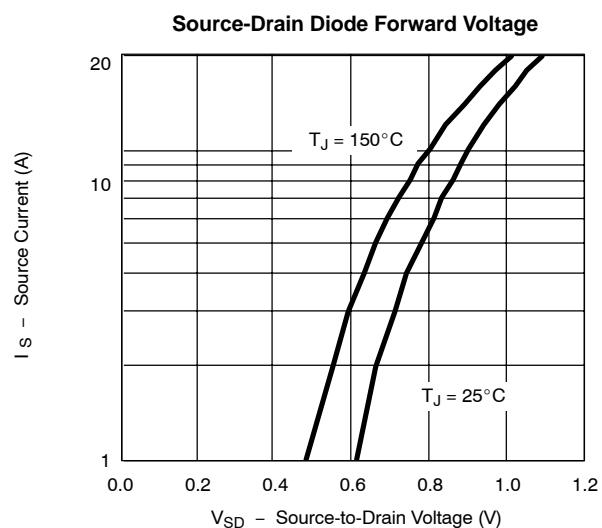

| Diode Forward Voltage <sup>b</sup>            | $V_{SD}$            | $I_S = 0.83 \text{ A}, V_{GS} = 0 \text{ V}$                                                                   |     | 0.65  | 1.1      | V             |

| <b>Dynamic<sup>a</sup></b>                    |                     |                                                                                                                |     |       |          |               |

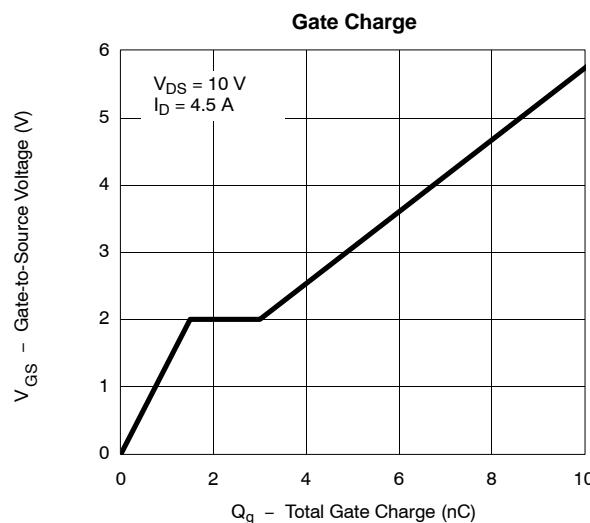

| Total Gate Charge                             | $Q_g$               | $V_{DS} = 10 \text{ V}, V_{GS} = 4.5 \text{ V}, I_D = 4.5 \text{ A}$                                           |     | 7.6   | 12       | nC            |

| Gate-Source Charge                            | $Q_{gs}$            |                                                                                                                |     | 1.5   |          |               |

| Gate-Drain Charge                             | $Q_{gd}$            |                                                                                                                |     | 1.5   |          |               |

| Turn-On Delay Time                            | $t_{d(\text{on})}$  | $V_{DD} = 10 \text{ V}, R_L = 10 \Omega$<br>$I_D \approx 1 \text{ A}, V_{GEN} = 4.5 \text{ V}, R_g = 6 \Omega$ |     | 0.43  | 0.7      | $\mu\text{s}$ |

| Rise Time                                     | $t_r$               |                                                                                                                |     | 0.8   | 1.2      |               |

| Turn-Off Delay Time                           | $t_{d(\text{off})}$ |                                                                                                                |     | 5.0   | 7.5      |               |

| Fall Time                                     | $t_f$               |                                                                                                                |     | 2.5   | 4.0      |               |

## Notes

- a. Guaranteed by design, not subject to production testing.

- b. Pulse test; pulse width  $\leq 300 \mu\text{s}$ , duty cycle  $\leq 2\%$ .

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

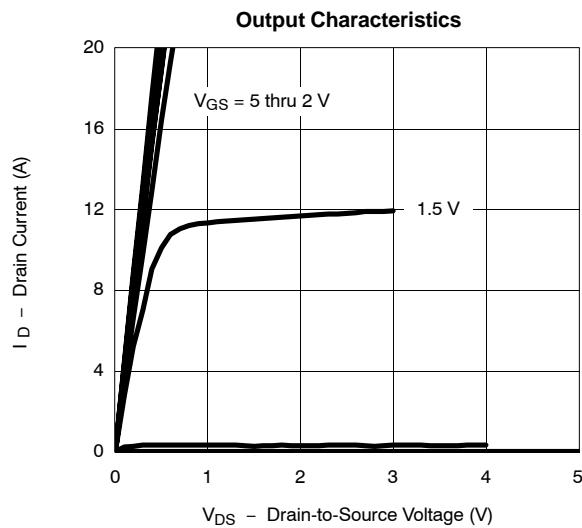

**TYPICAL CHARACTERISTICS (25°C UNLESS NOTED)**

**TYPICAL CHARACTERISTICS (25°C UNLESS NOTED)**

**TYPICAL CHARACTERISTICS (25°C UNLESS NOTED)**

**On-Resistance vs. Gate-to-Source Voltage**

**Threshold Voltage**

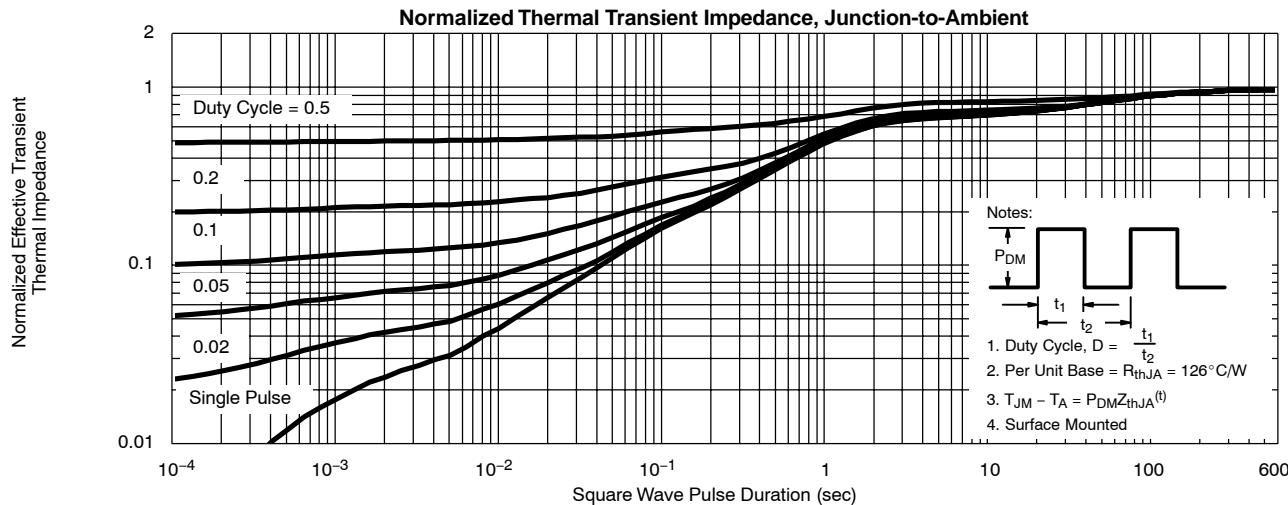

**Single Pulse Power, Junction-to-Ambient**

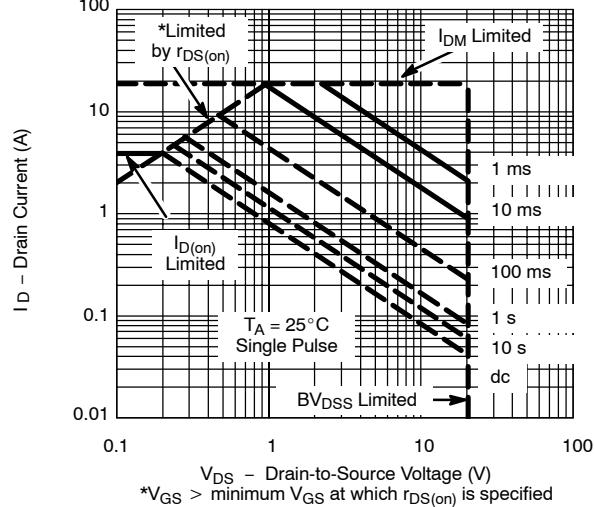

**Safe Operating Area, Junction-to-Case**

**TYPICAL CHARACTERISTICS (25°C UNLESS NOTED)**

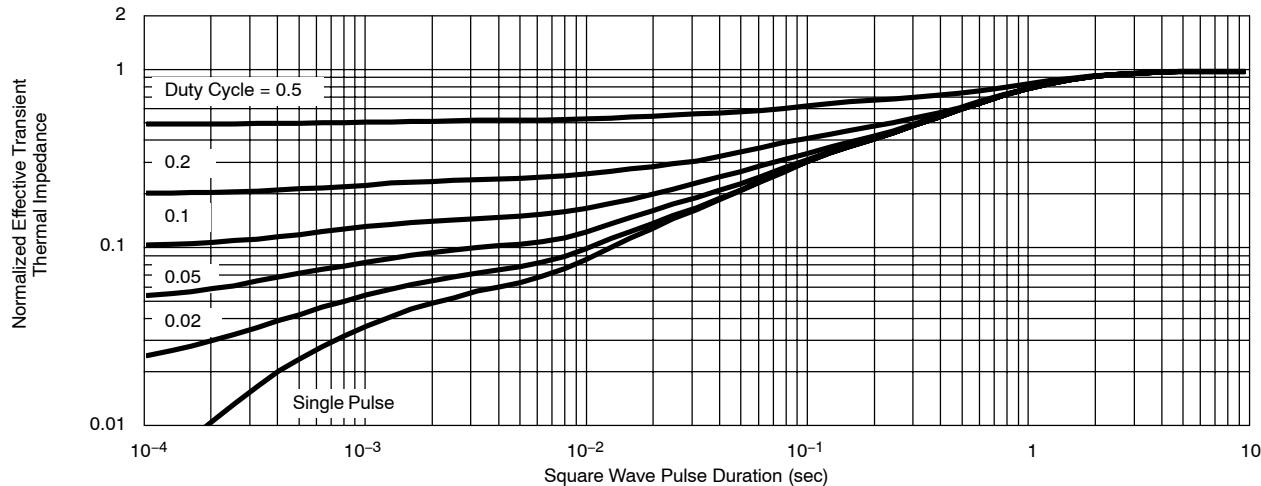

Normalized Thermal Transient Impedance, Junction-to-Foot

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see <http://www.vishay.com/ppg?73090>.

### Notice

Specifications of the products displayed herein are subject to change without notice. Vishay Intertechnology, Inc., or anyone on its behalf, assumes no responsibility or liability for any errors or inaccuracies.

Information contained herein is intended to provide a product description only. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Vishay's terms and conditions of sale for such products, Vishay assumes no liability whatsoever, and disclaims any express or implied warranty, relating to sale and/or use of Vishay products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright, or other intellectual property right.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications. Customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Vishay for any damages resulting from such improper use or sale.

# Mouser Electronics

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

[Vishay](#):

[SI6926AEDQ-T1-E3](#)