# 3V General Purpose/GSM Power Amplifier

#### **Product Overview**

The RF5110G is a high-power, high-gain, high-efficiency power amplifier. The device is manufactured with an advanced GaAs HBT process. It is designed for use as the final RF amplifier in GSM hand-held equipment in 900 MHz band, and General-Purpose radio application in standard sub-bands from 150 MHz to 960 MHz. An analog on-board power controller provides over 70 dB range of adjustment. Which allows for power down with a voltage equals to the logic "Low" to set the device in standby mode. The RF5110G RF Input is internally matched to 50  $\Omega$ . On its RF Output, it can be easily matched externally to obtain optimum power and efficiency for certain applications.

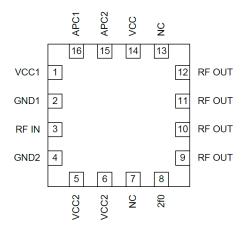

# **Functional Block Diagram**

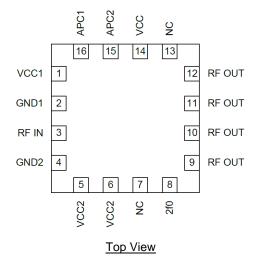

16 Pad 3 x 3 mm QFN Package

### **Key Features**

#### General Purpose:

- Single 2.8 V to 3.6 V Supply

- +32 dBm Output Power

- 53% Efficiency

- 150 MHz to 960 MHz Operation

#### GSM:

- Single 2.7 V to 4.8 V Supply

- +36 dBm Output Power at 3.6 V

- 32 dB Gain with Analog Gain Control

- 57% Efficiency

- 800 MHz to 950 MHz Operation

- Supports GSM and E-GSM

# **Applications**

- FM Radio Applications

150 MHz/220 MHz/450 MHz

865 MHz to 928 MHz

- 3 V GSM Cellular Handsets

- GPRS Compatible

## **Ordering Information**

| Part No.       | Description                          |

|----------------|--------------------------------------|

| RF5110GTR7     | 2,500 pieces on a 7" reel (standard) |

| RF5110GPCK-410 | GSM900 Fully Tested Evaluation Board |

#### 3 V General Purpose/GSM Power Amplifier

### **Absolute Maximum Ratings**

| Parameter                        | Rating            |

|----------------------------------|-------------------|

| Storage Temperature              | −55 °C to +150 °C |

| Device Voltage (Vcc, Vcc1, Vcc2) | -0.5 V to +6.0 V  |

| Control Voltage (VAPC1, VAPC2)   | -0.5 V to +3.0 V  |

| Device Current (Icc, Icc1, Icc2) | 2400 mA           |

| RF Input Power                   | +13 dBm           |

| Duty Cycle at Max Power          | 50%               |

Exceeding any one or a combination of the Absolute Maximum Rating conditions may cause permanent damage to the device. Extended application of Absolute Maximum Rating conditions to the device may reduce device reliability. This rating specified for GSM operation.

### **Recommended Operating Conditions**

| Parameter                           | Min  | Тур  | Max        | Units |

|-------------------------------------|------|------|------------|-------|

| Davis a Valta na                    |      | +3.5 |            |       |

| Device Voltage<br>(Vcc, Vcc1, Vcc2) | +2.7 |      | +4.8(1)    | V     |

| (VCC, VCC1, VCC2)                   |      |      | +5.5(1)(2) | V     |

| TCASE                               | -40  |      | +85        | °C    |

| TJ                                  |      |      | +150       | °C    |

#### Note:

- 1.  $P_{OUT} < +35 \text{ dBm}$

- 2. With maximum output load VSWR 6:1

Electrical specifications are measured at specified test conditions. Specifications are not guaranteed over all recommended operating conditions.

# **Electrical Specifications**

| Parameter    | Conditions (1)                                                           | Min  | Тур  | Max  | Units |

|--------------|--------------------------------------------------------------------------|------|------|------|-------|

| Output Power |                                                                          |      | 32   |      | dBm   |

| Gain         | 150 MHz                                                                  |      | 31.5 |      | dB    |

| Efficiency   |                                                                          |      | 53   |      | %     |

| Output Power |                                                                          |      | 32   |      | dBm   |

| Gain         | 220 MHz                                                                  |      | 32   |      | dB    |

| Efficiency   |                                                                          |      | 52   |      | %     |

| Output Power |                                                                          |      | 32   |      | dBm   |

| Gain         | 450 MHz; V <sub>CC</sub> , V <sub>CC1</sub> and V <sub>CC2</sub> = 3.0 V |      | 32.5 |      | dB    |

| Efficiency   |                                                                          |      | 50.5 |      | %     |

| Output Power | 205 MIL 4 200 MIL                                                        |      | 32   |      | dBm   |

| Gain         | 865 MHz to 928 MHz Equals typical at respective frequency corner         | 33.0 |      | 29.5 | dB    |

| Efficiency   | Equals typical at respective frequency confiel                           |      | 49   |      | %     |

#### Notes:

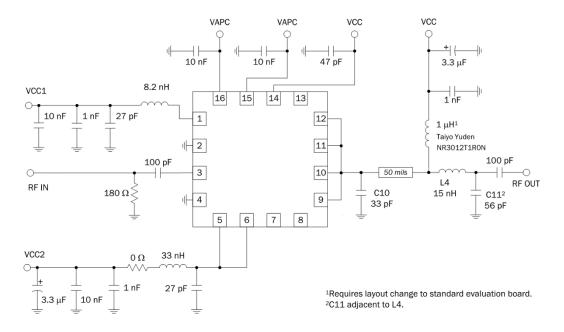

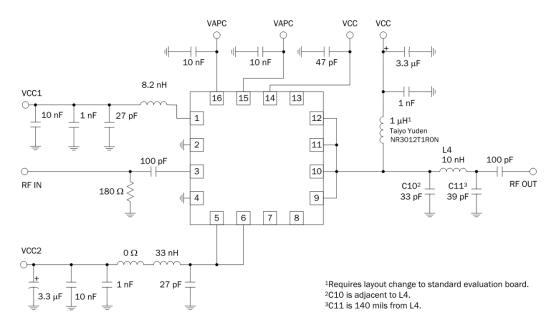

<sup>1.</sup> Test conditions unless otherwise noted:  $V_{APC1}$  and  $V_{APC2}$  = 2.8 V;  $V_{CC}$ ,  $V_{CC1}$  and  $V_{CC2}$  = 3.3 V; Duty Cycle = 100%; Temp = +25 °C; 50  $\Omega$  system; Refer to application circuits

### 3 V General Purpose/GSM Power Amplifier

# **Electrical Specifications (continue)**

| Parameter                    | Conditions (1)                                                                               | Min  | Тур        | Max   | Units |

|------------------------------|----------------------------------------------------------------------------------------------|------|------------|-------|-------|

| Operational Frequency Range  |                                                                                              | 880  |            | 915   | MHz   |

| Usable Frequency Range       | Using different EVB tune                                                                     | 800  |            | 950   | MHz   |

| Maximum Quinut Bayer         |                                                                                              | 33.8 | 34.5       |       | dBm   |

| Maximum Output Power         | Temp = +60 °C, Vcc, Vcc1 and Vcc2 = 3.3 V                                                    | 33.1 |            |       | dBm   |

|                              | At Maximum Output Power                                                                      | 50   | 57         |       | %     |

| Efficiency                   | P <sub>OUT</sub> = +20 dBm                                                                   |      | 12         |       | %     |

|                              | $P_{OUT} = +10 \text{ dBm}$                                                                  |      | 5          |       | %     |

| Input Power for Max. Output  |                                                                                              | 4.5  | 7.0        | 9.5   | dBm   |

| Output Noise Power           | RBW = 100 KHz; 925-935 MHz;<br>Vcc, Vcc1 and Vcc2 = 3.3 to 5.0V                              |      |            | -72   | dBm   |

| Output Noise Fower           | RBW =100 KHz; 935-960 MHz;<br>Vcc, Vcc1 and Vcc2 = 3.3 to 5.0V                               |      |            | -81   | dBm   |

| Forward Isolation            | Standby Mode $V_{APC1}$ and $V_{APC2} = 0.3 \text{ V}$ , $P_{IN} = +9.5 \text{ dBm}$         |      |            | -22   | dBm   |

| Second Harmonic              | $P_{IN} = +9.5 \text{ dBm}$                                                                  |      | -20        | -7    | dBm   |

| Third Harmonic               | $P_{IN} = +9.5 \text{ dBm}$                                                                  |      | -25        | -7    | dBm   |

| Non-Harmonic Spurious        |                                                                                              |      |            | -36   | dBm   |

| Input Impedance              |                                                                                              |      | 50         |       | Ω     |

| Optimum Source Impedance     | For best noise performance                                                                   |      | 40 + j10   |       | Ω     |

| Input VSWR                   | (Pout, max - 5 dB) < Pout < Pout.max                                                         |      |            | 2.5:1 |       |

| Input vovk                   | Pout < (Pout.max - 5 dB)                                                                     |      |            | 4.0:1 |       |

| Output Load VSWR, Stability  | Spurious < -36dBm, RBW=100KHz<br>V <sub>APC1</sub> and V <sub>APC2</sub> from 0.3 V to 2.6 V | 8:1  |            |       |       |

| Output Load VSWR, Ruggedness | No damage                                                                                    | 10:1 |            |       |       |

| Output Load Impedance        | Load Impedance presented at RF OUT pad                                                       |      | 2.6 – j1.5 |       | Ω     |

| Power Control "ON" Voltage   | V <sub>APC1</sub> , V <sub>APC2</sub> ; Maximum P <sub>OUT</sub>                             | 2.6  |            |       | V     |

| Power Control "OFF" Voltage  | V <sub>APC1</sub> , V <sub>APC2</sub> ; Minimum P <sub>OUT</sub>                             | 0.2  | 0.5        |       | V     |

| Gain Control Range           | V <sub>APC1</sub> and V <sub>APC2</sub> from 0.2 V to 2.6 V                                  | 75   |            |       | dB    |

| Gain Control Slope           | Pout from -10 dBm to +35 dBm                                                                 | 5    | 100        | 150   | dB/V  |

| APC Input Capacitance        | DC to 2 MHz                                                                                  |      |            | 10    | pF    |

| APC Input Current            | V <sub>APC1</sub> and V <sub>APC2</sub> = 2.8V                                               |      | 4.5        | 5     | mA    |

| AFC Input Current            | V <sub>APC1</sub> and V <sub>APC2</sub> = 0 V                                                |      |            | 25    | μA    |

| Turn ON/OFF Time             | V <sub>APC1</sub> and V <sub>APC2</sub> from 0 V to 2.8V                                     |      |            | 100   | ns    |

|                              | At Maximum Output Power                                                                      |      | 2          |       | Α     |

| Device Current               | Quiescent, P <sub>IN</sub> < -30dBm                                                          | 15   | 200        | 335   | mA    |

| (Icc, Icc1, and Icc2)        | Standby Mode, P <sub>IN</sub> < -30dBm                                                       |      | 1          | 10    | μA    |

|                              | Standby Mode, P <sub>IN</sub> < -30dBm, Temp = +85°C                                         |      | 1          | 10    | μA    |

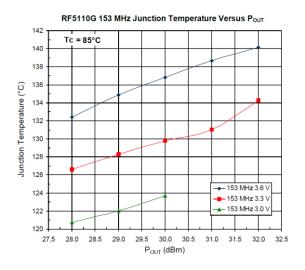

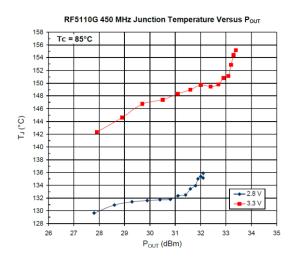

| Thermal Resistance           | CW Mode, Junction to Case                                                                    |      | 25.6       |       | °C/W  |

#### Notes:

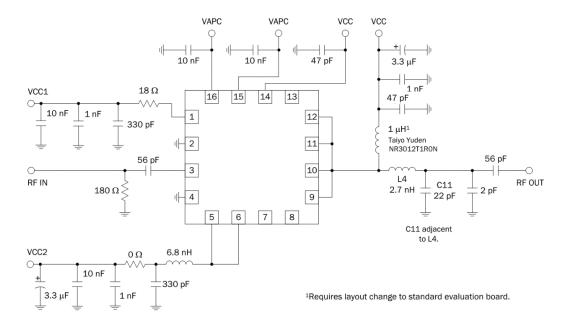

<sup>1.</sup> Test conditions unless otherwise noted:  $V_{APC1}$  and  $V_{APC2}$  = 2.8 V;  $V_{CC}$ ,  $V_{CC1}$  and  $V_{CC2}$  = 3.6 V;  $P_{IN}$  = +4.5 dBm; Pulse Width = 1731  $\mu$ s; Duty Cycle = 37.5%; Temp = +25 °C; 50  $\Omega$  system; Refer to RF5110GPCK-410 GSM900 evaluation board circuit.

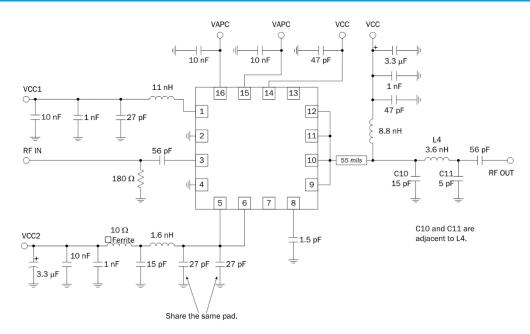

# 150 MHz FM Band Application Circuit

# **220 MHz FM Band Application Circuit**

# **450 MHz FM Band Application Circuit**

# 865 MHz and 902 MHz to 928 MHz ISM Band Application Circuit

# 850 MHz GSM Band Application Circuit

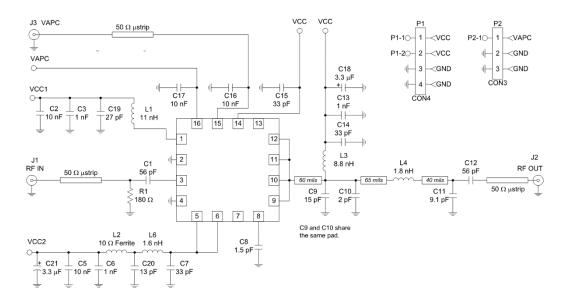

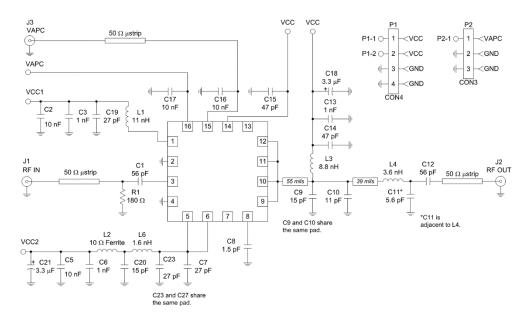

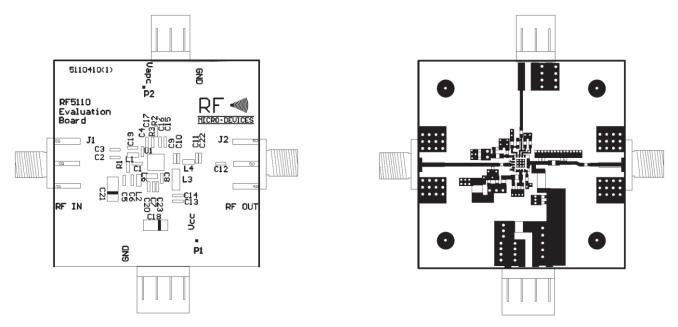

# **GSM900 Evaluation Board Circuit, RF5110GPCK-410**

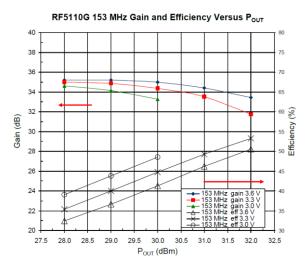

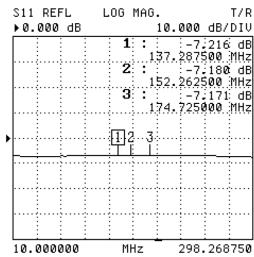

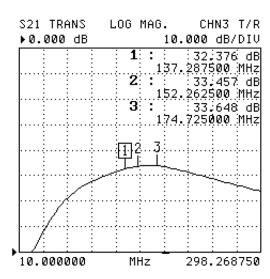

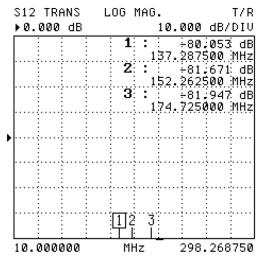

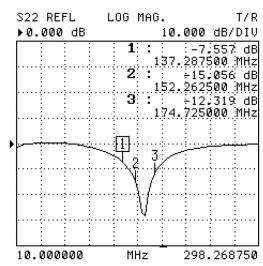

#### Performance Plots - 150 MHz

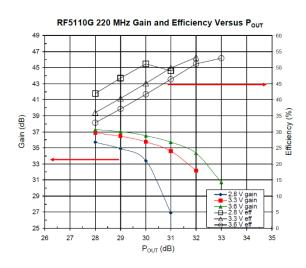

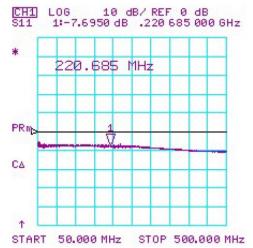

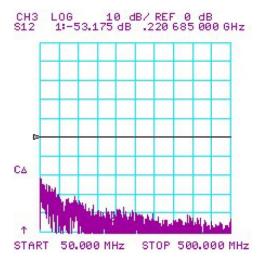

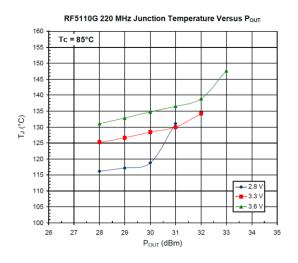

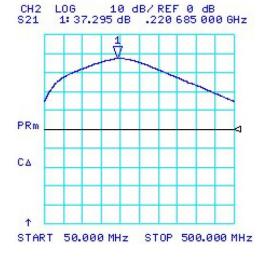

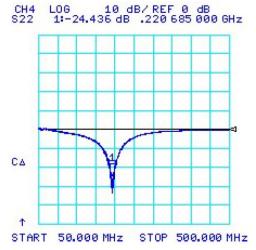

### Performance Plots - 220 MHz

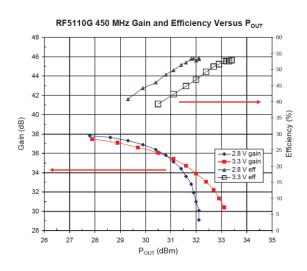

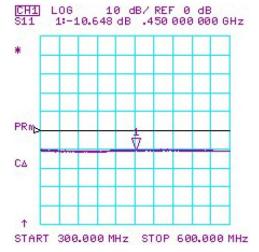

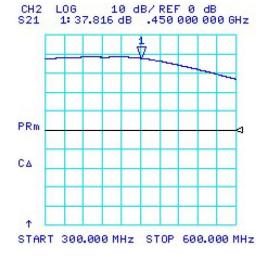

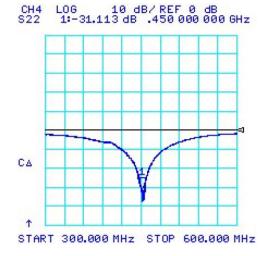

### Performance Plots - 450 MHz

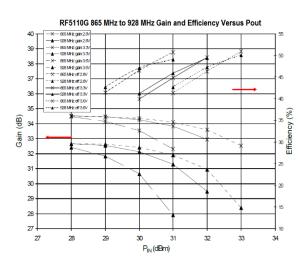

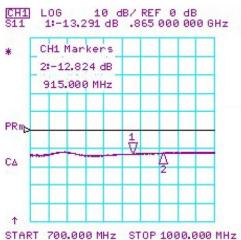

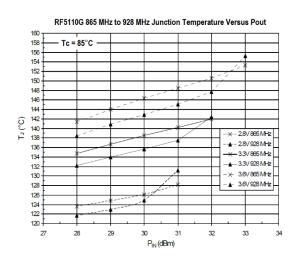

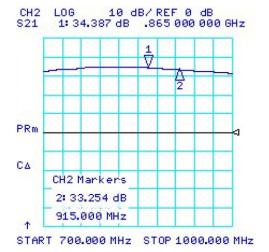

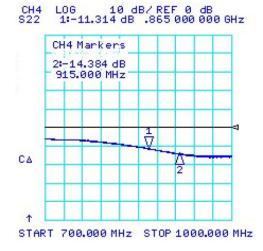

### Performance Plots - 865 MHz to 925 MHz

# **Pad Configuration and Description**

Top View

| Pad No.          | Label  | Description                                                                                                                                                                                                                                                                                                                                                | Interface Circuit                    |

|------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 1                | VCC1   | Power supply for the pre-amplifier stage and interstage matching. This pin forms the shunt inductance needed for proper tuning of the interstage match. Refer to the application circuit for proper configuration. Note that position and value of the components are important.                                                                           | VCC1                                 |

| 2                | GND1   | Ground connection for the pre-amplifier stage. Keep traces physically short and connect immediately to the ground plane for best performance. For stability concert, this pin requires dedicated ground via holes to the ground plane to minimize any common inductance.                                                                                   | RF INO                               |

| 3                | RF IN  | RF Input. This is a $50\Omega$ input, but the actual impedance could be affected by the interstage matching network connected on pin 1. An external DC blocking capacitor is required.                                                                                                                                                                     |                                      |

| 4                | GND2   | Ground connection for the driver stage. To minimize the noise power at the output, it is recommended to connect this pin with a trace of about 40mil long to the ground plane. This will slightly reduce the small signal gain. For stability concert, this pin requires dedicated ground via holes to the ground plane to minimize any common inductance. | VCC2                                 |

| 5, 6             | VCC2   | Power supply for the driver stage and interstage matching. This pin requires a shunt inductance for proper interstage matching. Please refer to the application schematic for proper configuration.                                                                                                                                                        | From Bias = GND2                     |

| 7, 13            | NC     | Not connected.                                                                                                                                                                                                                                                                                                                                             |                                      |

| 8                | 2F0    | Connection for the second harmonic trap. This pin is internally connected to the RF OUT pins. With the bonding wire together with an external capacitor form a series resonator. It should provide a second harmonic short termination to improve amplifier efficiency and reduce spurious outputs.                                                        | RF OUT                               |

| 9, 10, 11,<br>12 | RF OUT | RF Output and power supply for the output stage. Bias voltage for the final stage is provided through this wide output pins. An external matching network is required to provide the optimum performance.                                                                                                                                                  | From Bias = GND Stages GND PCKG BASE |

# **Pad Configuration and Description (continue)**

| Pad No.            | Label | Description                                                                                                                                                                                                                                                                                                                                                                                                                                       | Interface Circuit |

|--------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 14                 | VCC   | Power supply for the bias circuits.                                                                                                                                                                                                                                                                                                                                                                                                               |                   |

| 15                 | APC2  | Power Control for the output stage. See pin 16 for more details.                                                                                                                                                                                                                                                                                                                                                                                  | APC VCC           |

| 16                 | APC1  | Power Control for the driver and pre-amplifier stages. When this pin is "low," all circuits shut off. A "low" is typically 0.5V or less at room temperature. A shunt bypass capacitor is required. For a typical power control operation, the $V_{APC1}$ is about 1.0V for -10dBm to 2.6V for +35dBm RF output power. The maximum power that can be achieved depends on the actual output matching; see the application circuit for more details. | To RF Stages      |

| Backside<br>Paddle | GND   | RF/DC ground. Ground connection for the output stage. This pad should be connected to the ground plane by ground via holes directly under the device. A short path is required to obtain optimum performance, as well as to provide a good thermal path to the PCB for maximum heat dissipation.                                                                                                                                                  |                   |

## **Evaluation Board PCB Information**

Evaluation Board: Size 2.0" x 2.0"; Material FR-4; Multi-Layer; Thickness 0.032"

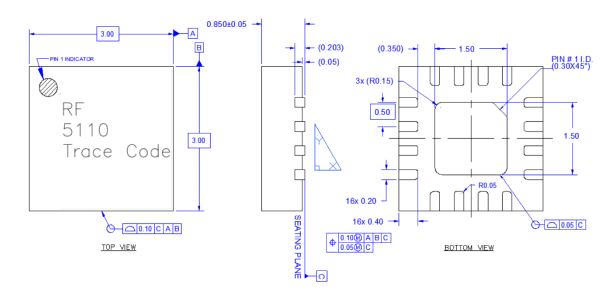

## **Package Marking and Dimensions**

Marking: Part Number - RF5110

Trace Code – Assigned by sub-contractor

#### Notes:

- 1. All dimensions are in millimeters. Angles are in degrees.

- 2. The terminal #1 identifier and terminal numbering conform to JESD 95-1 SPP-012.

- 3. Contact plating: Matte Sn

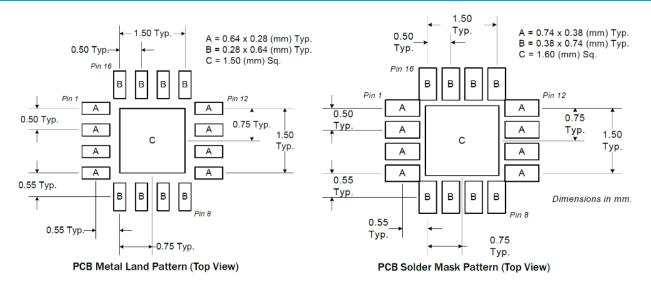

## **PCB Mounting Pattern**

#### Notes:

- 1. All dimensions are in millimeters. Angles are in degrees.

- 2. Use 1 oz. copper minimum for top and bottom layer metal.

- 3. ground via holes are required under the backside paddle of this device for proper RF/DC grounding and thermal dissipation. 0.203 mm to 0.330 mm finished hole size and 0.5 mm to 1.2 mm grid pattern recommended.

- 4. Ensure good package backside paddle solder attach for reliable operation and best electrical performance.

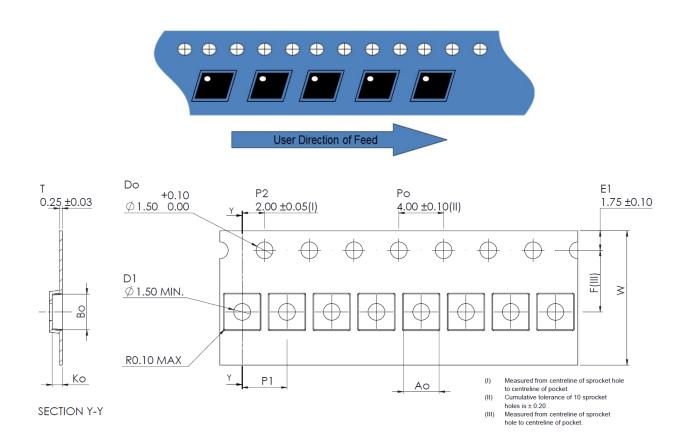

# **Tape and Reel Information – Carrier and Cover Tape Dimensions**

| Feature             | Measure                                  | Symbol | Size (in) | Size (mm) |

|---------------------|------------------------------------------|--------|-----------|-----------|

|                     | Length                                   | A0     | 0.125     | 3.20      |

| Covity              | Width                                    | B0     | 0.125     | 3.20      |

| Cavity              | Depth                                    | K0     | 0.040     | 1.00      |

|                     | Pitch                                    | P1     | 0.157     | 4.00      |

| Contouling Distance | Cavity to Perforation - Length Direction | P2     | 0.079     | 2.00      |

| Centerline Distance | Cavity to Perforation - Width Direction  | F      | 0.217     | 5.50      |

| Cover Tape          | Width                                    | С      | 0.362     | 9.20      |

| Carrier Tape        | Width                                    | W      | 0.472     | 12.0      |

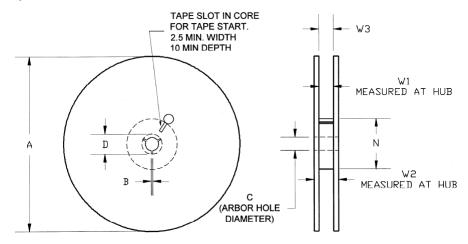

# **Tape and Reel Information – Reel Dimensions**

Standard T/R size = 2,500 pieces on a 7" reel.

| Feature | Measure              | Symbol | Size (in) | Size (mm) |

|---------|----------------------|--------|-----------|-----------|

|         | Diameter             | Α      | 6.969     | 177       |

| Flange  | Thickness            | W2     | 0.717     | 18.2      |

|         | Space Between Flange | W1     | 0.504     | 12.8      |

| Hub     | Outer Diameter       | N      | 2.283     | 58.0      |

|         | Arbor Hole Diameter  | С      | 0.512     | 13.0      |

|         | Key Slit Width       | В      | 0.079     | 2.0       |

|         | Key Slit Diameter    | D      | 0.787     | 20.0      |

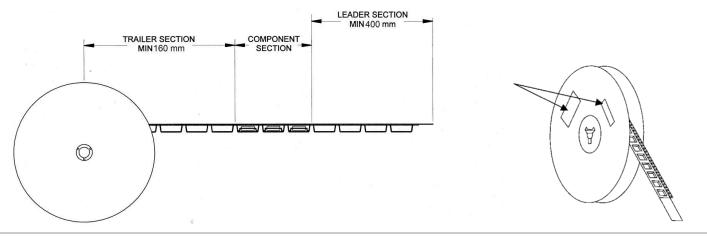

# Tape and Reel Information - Tape Length and Label Placement

#### Notes

- 1. Empty part cavities at the trailing and leading ends are sealed with cover tape. See EIA 481-1-A.

- 2. Labels are placed on the flange opposite the sprockets in the carrier tape.

### **Handling Precautions**

| Parameter                      | Rating  | Standard            |

|--------------------------------|---------|---------------------|

| ESD – Human Body Model (HBM)   | Class 0 | JESD22-A114         |

| ESD – Machine Model            | Class A | JESD22-A115         |

| MSL-Moisture Sensitivity Level | Level 2 | IPC/JEDEC J-STD-020 |

Caution! ESD-Sensitive Device

### **Solderability**

Compatible with both lead-free (260°C max. reflow temp.) and tin/lead (245°C max. reflow temp.) soldering processes. Solder profiles available upon request.

Contact plating: Matte Sn

## **RoHS Compliance**

This part is compliant with 2011/65/EU RoHS directive (Restrictions on the Use of Certain Hazardous Substances in Electrical and Electronic Equipment) as amended by Directive 2015/863/EU.

This product also has the following attributes:

- Lead Free

- Halogen Free (Chlorine, Bromine)

- Antimony Free

- TBBP-A (C<sub>15</sub>H<sub>12</sub>Br<sub>4</sub>O<sub>2</sub>) Free

- PFOS Free

- SVHC Free

#### **Contact Information**

For the latest specifications, additional product information, worldwide sales and distribution locations:

Web: <u>www.qorvo.com</u>

Tel: 1-844-890-8163

Email: customer.support@qorvo.com

## **Important Notice**

The information contained herein is believed to be reliable; however, Qorvo makes no warranties regarding the information contained herein and assumes no responsibility or liability whatsoever for the use of the information contained herein. All information contained herein is subject to change without notice. Customers should obtain and verify the latest relevant information before placing orders for Qorvo products. The information contained herein or any use of such information does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other intellectual property rights, whether with regard to such information itself or anything described by such information. THIS INFORMATION DOES NOT CONSTITUTE A WARRANTY WITH RESPECT TO THE PRODUCTS DESCRIBED HEREIN, AND QORVO HEREBY DISCLAIMS ANY AND ALL WARRANTIES WITH RESPECT TO SUCH PRODUCTS WHETHER EXPRESS OR IMPLIED BY LAW, COURSE OF DEALING, COURSE OF PERFORMANCE, USAGE OF TRADE OR OTHERWISE, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

Without limiting the generality of the foregoing, Qorvo products are not warranted or authorized for use as critical components in medical, life-saving, or life-sustaining applications, or other applications where a failure would reasonably be expected to cause severe personal injury or death.

Copyright 2020 © Qorvo, Inc. | Qorvo is a registered trademark of Qorvo, Inc.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Qorvo:

RF5110GTR7 RF5110GSR