# PAC5526EVK1 PAC5526 Evaluation Kit

#### Introduction

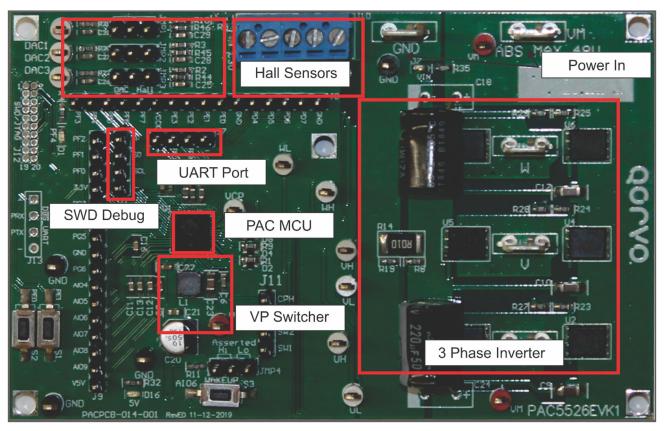

Qorvo's PAC5526EVK1 development platform is a complete hardware solution enabling users not only to evaluate the PAC5526 device, but also develop power applications revolving around this powerful and versatile ARM<sup>®</sup> Cortex<sup>®</sup>-M4F based microcontroller. The module contains a PAC5526 Power Application Controller<sup>®</sup> (MCU) and all the necessary circuitry to properly energize the MCU and its internal peripherals once power is applied.

To aid in the application development the PAC5526EVK1 offers access to each and every one of the PAC5526 device's signals by means of a series of male header connectors.

The PAC5526EVK1 also contains access to an external USB to UART module enabling users to connect the evaluation module to a PC computer through a conventional Virtual Comm Port which can then be used in the communication efforts by taking advantage of the PAC5526's UART interface. Graphical User Interface (GUI) software suites can be employed to externally control particular application's features.

Finally, the PAC5526EVK1 module gives access to the PAC5526's SWD and JTAG ports allowing users to both program the application into the device's FLASH memory, as well as debug the application in real time. The provided 4 pin connector is compatible with a decent variety of SWD based debugger/programmer modules, widely available. In parallel, a MIPI20 connector is made available to provide JTAG with TRACE functionality, greatly expanding the existent debugging capabilities.

Qorvo's PAC5526EVK1 evaluation kit consists of the following:

- PAC5526EVK1 Body module

- PAC5526EVK1 User's Guide

- Schematics, BOM and Layout Drawings

# PAC5526EVK1 Module

Figure 1: PAC5526EVK1 Block Diagram

#### Solution Benefits:

- Ideal for high voltage (up to 48V Abs Max) general purpose power applications and controllers

- Single-IC PAC5526 with configurable PWM outputs, ADC inputs, I2C, UART, SPI communication ports and GPIO.

- Intelligent gate driving for up to three half H Bridge (tri phase) inverter.

- Schematics, BOM, Layout drawings available

The following sections provide information about the hardware features of Qorvo's PAC5526EVK1 turnkey solution.

# PAC5526EVK1 Resources

### **Pinout and Signal Connectivity**

The following diagram shows the male header pinout for the PAC5526EVK1 evaluation module, as seen from above:

### **Power Input**

Power to the PAC5526EVK1 evaluation module can be applied to the VIN and GND spade connectors. Power to the PAC5526EVK1 evaluation module should not exceed 48V (Abs Max).

The PAC5526EVK1 is optimized to operate with voltages ranging from 8V to 20V Nominal (48V Abs Max). When the VIN input voltage goes above 8V, the system exits UVLO protection and all subsystems, including voltage regulators, analog front end and microcontroller, are enabled.

#### LED's

When an operational voltage is applied, LED D16 will light up. This is the LED which notifies VSYS (5V) rail is up and running. VP (12V gate drive), 3.3V (for analog circuitry) and 1.2V (for CPU core) regulators will also be operating at this point in time. Module is ready for use.

The following table shows the available LEDs and their associated diagnostic function.

| LED | Description                                                                    |

|-----|--------------------------------------------------------------------------------|

| D16 | VSYS (5V). Light up when the PAC5526 device is successfully powered up by VIN. |

| D7  | VIN. Lights up as VIN voltage is applied.                                      |

## SWD Debugging

Connector J1 offers access to the PAC5526 SWD port lines.

| J1 Pin | Terminal | Description         |      |

|--------|----------|---------------------|------|

| 1      | +        | VCCIO (3.3V)        | JTAG |

| 2      | SD       | SWD Serial Data     |      |

| 3      | CL       | SWD Serial Clock    |      |

| 4      | -        | GND (System Ground) |      |

|        |          |                     |      |

#### Debugging

Connector J12 is a standard MIPI20 offering access to the JTAG port as well as single data line TRACE debug.

| J12<br>Pins | Terminal        | Description                                                 |

|-------------|-----------------|-------------------------------------------------------------|

| 1           | VCC             | VCC Power                                                   |

| 2           | SWDIO/TMS       | Serial Wire Debug Data Input Output / JTAG Test Mode Select |

| 3           | GND             | GND (System GND)                                            |

| 4           | SWCLK/TCK       | Serial Wire Debug Clock / JTAG Clock                        |

| 5           | GND             | GND (System GND)                                            |

| 6           | SWO/TDO         | Serial Wire Debug Output / JTAG Data Output                 |

| 7           | NC              | Not Connected                                               |

| 8           | TDI             | JTAG Data Input                                             |

| 9           | GND             | GND (System GND)                                            |

| 10          | NC              | Not Connected                                               |

| 11          | GND             | GND (System GND)                                            |

| 12          | TRACE CLK       | ETM Trace Clock                                             |

| 13          | GND             | GND (System GND)                                            |

| 14          | TRACE DATA<br>0 | ETM Trace Data 0                                            |

| 15          | GND             | GND (System GND)                                            |

| 16          | TRACE DATA<br>1 | ETM Trace Data 1                                            |

| 17          | GND             | GND (System GND)                                            |

| 18 | TRACE DATA<br>2 | ETM Trace Data 2 |

|----|-----------------|------------------|

| 19 | GND             | GND (System GND) |

| 20 | TRACE DATA<br>3 | ETM Trace Data 3 |

#### **Serial Communications**

Connector J7 offers access to the PAC5526 UART port lines.

| J7 Pin | Terminal | Description             |

|--------|----------|-------------------------|

| 1      | +        | VCCIO (3.3V)            |

| 2      | ТХ       | MCU Transmit Line (PE3) |

| 3      | RX       | MCU Receive Line (PE2)  |

| 4      | -        | GND (System Ground)     |

### **Alternate Serial Communications**

When enabled, connector J13 provides access to a secondary UART port lines.

| J7 Pin | Terminal | Description                                                           |

|--------|----------|-----------------------------------------------------------------------|

| 1      | +        | VCCIO (3.3V)                                                          |

| 2      | ТХ       | MCU Transmit Line (PF3 – requires 0 ohm resistor R41 to be populated) |

| 3      | RX       | MCU Receive Line (PF2)                                                |

| 4      | -        | GND (System Ground)                                                   |

### Hall Sensor / DAC Interface

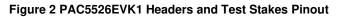

Connector J10 offers access to the PAC5526 resources on PORTD utilized for hall sensor based commutation. These resources can be alternatively utilized as PWM DAC outputs for in real time debugging. Jumpers JMP1/2/3 are used to select the preferred function.

NOTE: 2 pin shunts must be placed on the JMP1/2/3 in order for the respective PORTD resources to be made available.

Figure 3 DAC / Hall Sensor Jumper Selection

| Jumper<br>J14/15/16 | Description               |

|---------------------|---------------------------|

| 1:2                 | Hall Sensor Functionality |

| 2:3                 | DAC Functionality         |

NOTE: J10 functionality is only available when jumpers JMP1/2/3 have been shunted on the Hall Sensor respective position.

| J10 Pin | Terminal      | Description         |

|---------|---------------|---------------------|

| 1       | +             | VCCIO (3.3V)        |

| 2       | Hall Sensor U | PORTD4              |

| 3       | Hall Sensor V | PORTD5              |

| 4       | Hall Sensor W | PORTD6              |

| 5       | GND           | GND (System Ground) |

NOTE: Test stakes DAC1/2/3 are only available when jumpers JMP1/2/3 have been shunted on the DAC respective position

| Test Stake | Description |

|------------|-------------|

| DAC 1      | PORTD4      |

| DAC 2      | PORTD5      |

| DAC 3      | PORTD6      |

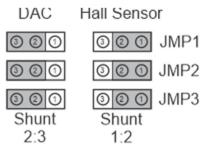

# PAC5526EVK1 SETUP

The setup for the PAC5526EVK1 evaluation module requires up to four simple connections.

- Connect the VIN power source via spade tab connectors VIN and GND. As VIN power is applied, the LED D7 will light up. Once VIN voltage goes above 8V, the PAC5526's Multi Mode Power Manager will be engaged and the VSYS (5V) regulator will be enabled. This event will result in LED D16 lighting up.

- 2. Connect the 3 Phase BLDC/PMSM motor via space tab connectors PHASE U, PHASE V and PHASE W.

- 3. If Serial Communications are desired, connect the USB to UART module 4 pin connection to J7.

- 4. For debugging/programming, connect a suitable USB SWD module to J1 by using a standard 4 wire cable.

Figure 4: PAC5526EVK1 Evaluation Module Connections

# **Contact Information**

For the latest specifications, additional product information, worldwide sales and distribution locations:

Web: www.qorvo.com

Tel: 1-844-890-8163

Email: customer.support@qorvo.com

### **Important Notice**

The information contained in this Data Sheet and any associated documents ("Data Sheet Information") is believed to be reliable; however, Qorvo makes no warranties regarding the Data Sheet Information and assumes no responsibility or liability whatsoever for the use of said information. All Data Sheet Information is subject to change without notice. Customers should obtain and verify the latest relevant Data Sheet Information before placing orders for Qorvo® products. Data Sheet Information or the use thereof does not grant, explicitly, implicitly or otherwise any rights or licenses to any third party with respect to patents or any other intellectual property whether with regard to such Data Sheet Information itself or anything described by such information.

DATA SHEET INFORMATION DOES NOT CONSTITUTE A WARRANTY WITH RESPECT TO THE PRODUCTS DESCRIBED HEREIN, AND QORVO HEREBY DISCLAIMS ANY AND ALL WARRANTIES WITH RESPECT TO SUCH PRODUCTS WHETHER EXPRESS OR IMPLIED BY LAW, COURSE OF DEALING, COURSE OF PERFORMANCE, USAGE OF TRADE OR OTHERWISE, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Without limiting the generality of the foregoing, Qorvo® products are not warranted or authorized for use as critical components in medical, life-saving, or life-sustaining applications, or other applications where a failure would reasonably be expected to cause severe personal injury or death. Applications described in the Data Sheet Information are for illustrative purposes only. Customers are responsible for validating that a particular product described in the Data Sheet Information is suitable for use in a particular application.

© 2020 Qorvo US, Inc. All rights reserved. This document is subject to copyright laws in various jurisdictions worldwide and may not be reproduced or distributed, in whole or in part, without the express written consent of Qorvo US, Inc. | QORVO® is a registered trademark of Qorvo US, Inc.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Qorvo: PAC5526EVK PAC5526EVK1