**Bi-CMOS Integrated Circuit Silicon Monolithic**

# TB9120AFTG

## Bipolar stepping motor driver with a clock input interface for automotive applications

### 1 Overview

TB9120AFTG is a two-phase bipolar stepping motor driver with a clock input interface and a PWM constant-current control system. It can be used for a small stepping motor in a wide range of automotive applications.

### 2 Applications

Small stepping motors for automotive applications such as an adjustment to an angle of a concave mirror in HUD, valves in motorcycles and valves/dampers for HVAC

### 3 Features

- A two-phase bipolar stepping motor can be driven with a single chip.

- Adoption of PWM constant-current control

- Built-in a mixed decay mode

- Excitation mode selectable: full, half, quarter, 1/8, 1/16, and 1/32 step

- On-resistance of power MOSFETs: Ron(H+L)=0.8Ω(typ.)

- Input power supply voltage(VBAT): 40V(max)

- Maximum output driving current: Overcurrent detection value, 2.0A(typ.)

- Internal voltage 5V(VccOUT)

- Anomaly detection functions: Over temperature detection, overcurrent detection, load open detection and low voltage detection

- DIAG output: Over temperature detection, overcurrent detection and load open detection

- Stall detection function and flag output function if detected

- Standby function

- Operating power supply voltage range: VBAT(opr.)=7V to 18V. Only some of the functions are guaranteed in 4.5V to 7V.

- Maximum clock input frequency: fCLK(max)=100kHz

- Operating temperature: -40 to 125°C

- Package: VQFN28(0.65)

- AEC-Q100 qualified

P-VQFN28-0606-0.65-002

Product weight : 0.10g(typ.)

Start of commercial production 2020-04

1

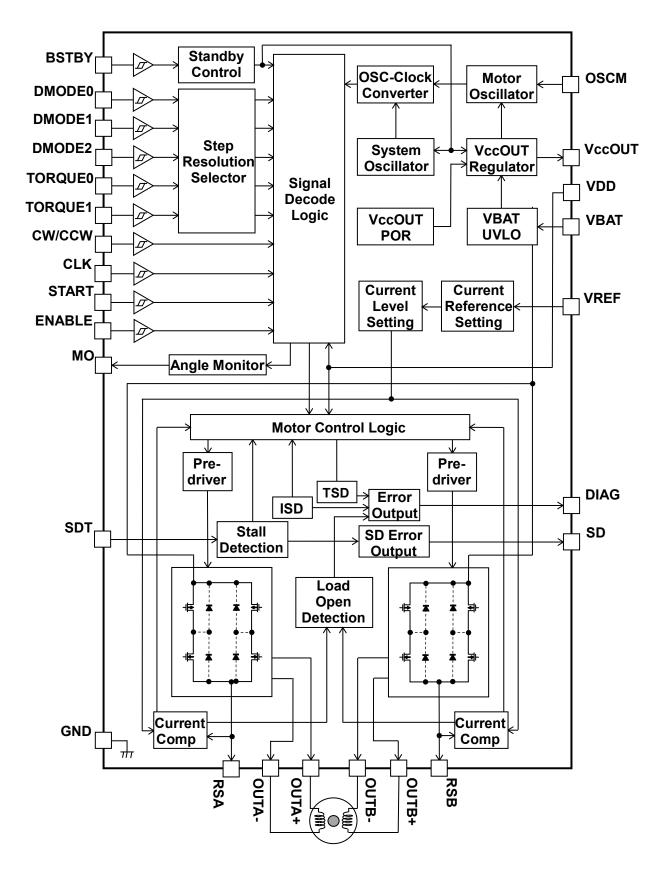

## 4 Block diagram

Besides the above, there are TEST 1 and TEST 2 as the test pins for shipping inspection. Some of the functional blocks, circuits, or constants in the block diagram may be omitted or simplified for explanatory purposes.

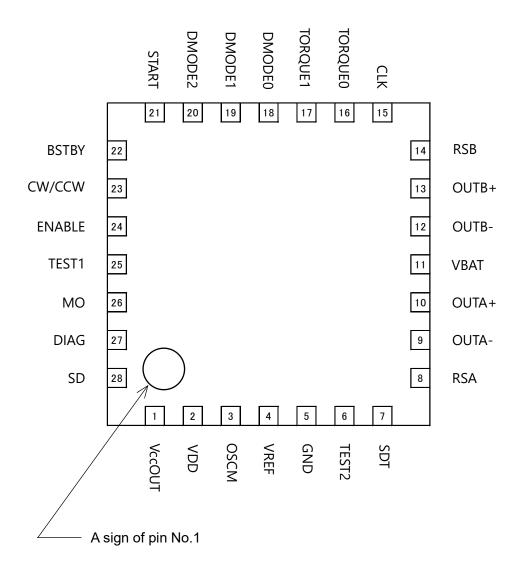

## 5 Pin Assignment (TOP View)

# 6 Pin Arrangement and Function Description

# 6.1 Pin Arrangement and Function Description

| Pin No. | Pin name | Description                                                                                                             |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------|

| 1       | VccOUT   | 5V output. Connect it to a power smoothing capacitor.                                                                   |

| 2       | VDD      | 5V input. Connect it to VccOUT pin (pin No.1) at the IC outside.                                                        |

| 3       | OSCM     | Resistor connected pin to set an output PWM frequency                                                                   |

| 4       | VREF     | Voltage applied pin to set an output current value                                                                      |

| 5       | GND      | GND pin                                                                                                                 |

| 6       | TEST2    | Test pin in shipping inspection. Do not connect anything.                                                               |

| 7       | SDT      | Resistor connected pin to set a stall detection threshold. When not using the stall detection function, use it as open. |

| 8       | RSA      | Current sensing resistor connected pin to set an output current value for phase A                                       |

| 9       | OUTA-    | Negative pin in phase A of a motor                                                                                      |

| 10      | OUTA+    | Positive pin in phase A of a motor                                                                                      |

| 11      | VBAT     | Battery power pin                                                                                                       |

| 12      | OUTB-    | Negative pin in phase B of a motor                                                                                      |

| 13      | OUTB+    | Positive pin in phase B of a motor                                                                                      |

| 14      | RSB      | Current sensing resistor connected pin to set an output current value for phase B                                       |

| 15      | CLK      | Step clock input pin. Built-in pull-down resistor 100 k $\Omega$                                                        |

| 16      | TORQUE0  | Constant current setting input 0. Built-in pull-down resistor 100 k $\Omega$                                            |

| 17      | TORQUE1  | Constant current setting input 1. Built-in pull-down resistor 100 k $\Omega$                                            |

| 18      | DMODE0   | Excitation mode setting input 0. Built-in pull-down resistor 100 k $\Omega$                                             |

| 19      | DMODE1   | Excitation mode setting input 1. Built-in pull-down resistor 100 k $\Omega$                                             |

| 20      | DMODE2   | Excitation mode setting input 2. Built-in pull-down resistor 100 k $\Omega$                                             |

| 21      | START    | Electrical angle initializing input. Built-in pull-down resistor 100 k $\Omega$                                         |

| 22      | BSTBY    | Standby input. Built-in pull-down resistor 100 k $\Omega$                                                               |

| 23      | CW/CCW   | Rotation direction setting input. Built-in pull-down resistor 100 k $\Omega$                                            |

| 24      | ENABLE   | Motor driving output enabling input. Built-in pull-down resistor 100 k $\Omega$                                         |

| 25      | TEST1    | Test pin in shipping inspection. Connect it to GND.                                                                     |

| 26      | MO       | Electrical angle monitoring signal output. Open drain output pin.                                                       |

| 27      | DIAG     | Anomaly detection flag signal output. Open drain output pin.                                                            |

| 28      | SD       | Stall detection flag signal output. Open drain output pin.                                                              |

| -       | E-PAD    | Reverse side of bed mounted with IC chip. Connect it to GND.                                                            |

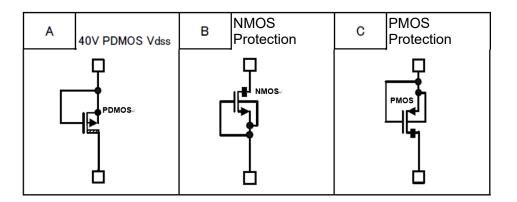

# 6.2 Layout of protection elements

|          |                    |              |                                                     | Protection el           | ements      | Conne                   | ct to       |

|----------|--------------------|--------------|-----------------------------------------------------|-------------------------|-------------|-------------------------|-------------|

| Pin name | Pull-down resistor | 1∕0          | Absolute maximum rating,<br>upper limit voltage (V) | Power<br>supply<br>side | GND<br>side | Power<br>supply<br>side | GND<br>side |

| VccOUT   | —                  | 0            | 6.0                                                 | А                       | В           | VBAT                    | GND         |

| VDD      | —                  | Power supply | 6.0                                                 | А                       | В           | VBAT                    | GND         |

| OSCM     | _                  | 0            | 6.0                                                 | С                       | В           | VccOUT                  | GND         |

| VREF     | —                  | Power supply | 6.0                                                 | —                       | В           | —                       | GND         |

| GND      | —                  | GND          | —                                                   | —                       | —           | —                       | —           |

| TEST2    | —                  | 0            | 6.0                                                 | С                       | В           | VccOUT                  | GND         |

| SDT      | —                  | 0            | 6.0                                                 | С                       | В           | VccOUT                  | GND         |

| RSA      | —                  | -            | 1.0                                                 | С                       | В           | VccOUT                  | GND         |

| OUTA-    | _                  | 0            | 40                                                  | —                       | —           | —                       | —           |

| OUTA+    | _                  | 0            | 40                                                  | —                       | —           | —                       | —           |

| VBAT     | _                  | Power supply | 40                                                  | -                       | А           | -                       | GND         |

| OUTB-    | _                  | 0            | 40                                                  | -                       | -           | _                       | _           |

| OUTB+    | —                  | 0            | 40                                                  | -                       | —           | -                       | —           |

| RSB      | _                  | -            | 1.0                                                 | С                       | В           | VccOUT                  | GND         |

| CLK      | Pull-down resistor | I            | 6.0                                                 | —                       | В           | —                       | GND         |

| TORQUE0  | Pull-down resistor | Ι            | 6.0                                                 | —                       | В           | —                       | GND         |

| TORQUE1  | Pull-down resistor | Ι            | 6.0                                                 | -                       | В           | -                       | GND         |

| DMODE0   | Pull-down resistor | I            | 6.0                                                 | —                       | В           | —                       | GND         |

| DMODE1   | Pull-down resistor | Ι            | 6.0                                                 | -                       | В           | _                       | GND         |

| DMODE2   | Pull-down resistor | Ι            | 6.0                                                 | -                       | В           | -                       | GND         |

| START    | Pull-down resistor | Ι            | 6.0                                                 | -                       | В           | -                       | GND         |

| BSTBY    | Pull-down resistor | Ι            | 6.0                                                 | -                       | В           | -                       | GND         |

| CW/CCW   | Pull-down resistor | I            | 6.0                                                 | -                       | В           | _                       | GND         |

| ENABLE   | Pull-down resistor | I            | 6.0                                                 | —                       | В           | _                       | GND         |

| TEST1    | Pull-down resistor | l            | 6.0                                                 | _                       | В           | _                       | GND         |

| MO       | —                  | 0            | 6.0                                                 | -                       | В           | —                       | GND         |

| DIAG     | —                  | 0            | 6.0                                                 | -                       | В           | _                       | GND         |

| SD       | —                  | 0            | 6.0                                                 | —                       | В           | —                       | GND         |

### Protection elements

## 7 Description of operation

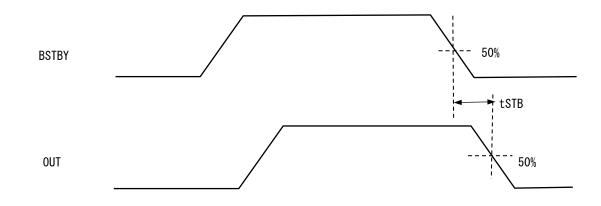

## 7.1 BSTBY Function

When BSTBY=L, the IC is kept in the standby mode.

| BSTBY | Function                                              |

|-------|-------------------------------------------------------|

|       | Standby mode                                          |

| L     | (Internal oscillator circuits, OSCS and OSCM stop and |

|       | operation of output MOSFETs to drive a motor stops)   |

| Н     | Active mode                                           |

Note: 0.5ms at the most is required so that the internal circuit related to 5V in the IC becomes stable right after switching from the standby mode state to the active mode. Refer to 7.2.

Truth table

| Input |        |       |        |       | Output state                       | Mode                |  |

|-------|--------|-------|--------|-------|------------------------------------|---------------------|--|

| CLK   | CW/CCW | START | ENABLE | BSTBY | Output state                       | wode                |  |

|       | Н      | L     | Н      | Н     | CW (Clockwise)                     | Normal operation    |  |

|       | L      | L     | Н      | Н     | CCW (Counterclockwise)             | Normal operation    |  |

| Х     | Х      | Н     | Н      | Н     | Initialization of electrical angle | Initial (Note 1)    |  |

| Х     | Х      | Х     | L      | Н     | High-impedance                     | Enable OFF (Note 2) |  |

| Х     | Х      | Х     | Х      | L     | High-impedance                     | Standby (Note 3)    |  |

X: Don't care.

Note 1. Initial: The current level that is fixed to the initial electrical angle indicated by the function of START is output.

Note 2. Enable OFF: The outputs enter a high-impedance state. On the other hand, when START=L and a signal is being input to CLK, the internal counter proceeds.

Note 3. Standby: BSTBY has higher priority than ENABLE. Therefore, regardless of a state of ENABLE, if BSTBY=L, the IC becomes a standby mode.

## 7.2 **Power supply**

VBAT is a battery power supply pin. VccOUT is an output pin of an internal generated power 5V. This IC has a power supply monitoring function.

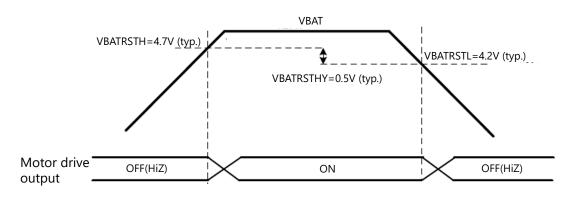

VBAT low-voltage detection circuit

Each output pin (OUTA +, OUTA-, OUTB +, and OUTB-) is turned off (high-impedance state) when VBAT voltage drops below the detection voltage 4.2V(typ.). It has 0.5V(typ.) hysteresis. Therefore, it recovers at 4.7V(typ.).

Threshold of VBAT low-voltage detection

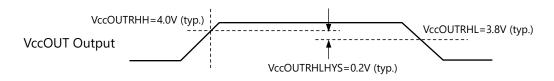

VccOUT low-voltage detection circuit

Each output pin (OUTA +, OUTA-, OUTB +, and OUTB-) is turned off (high-impedance state) and all control circuits including logic circuits are also reset when VccOUT output voltage drops below the detection voltage 3.8V(typ.). It has 0.2V(typ.) hysteresis. Therefore, it recovers at 4.0V(typ.).

Each input control signal is reflected when VBAT voltage is less than VBAT low-voltage detection threshold 4.2V(typ.) and VccOUT voltage is more than POR threshold 3.8V(typ.). However, each output pin (OUTA +, OUTA-, OUTB +, and OUTB-) is kept in high-impedance state if VBAT voltage still stays less than VBAT low-voltage detection threshold 4.2V(typ.).

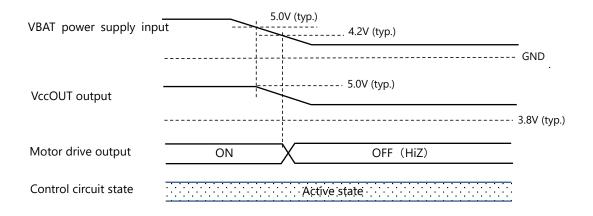

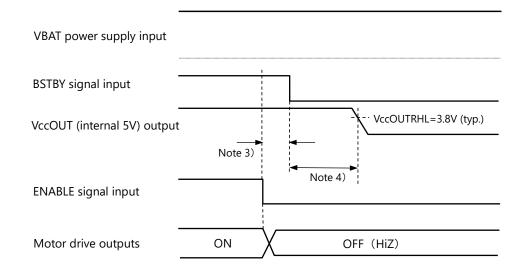

## 7.3 Power supply / control signal input sequence

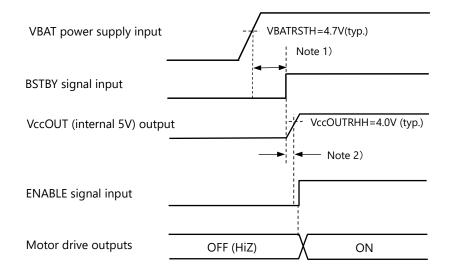

(1) Start-up

- Note 1) Make sure that VBAT voltage is more than 4.7V before a standby mode is released (BSTBY signal: L→H).

Note 2) It takes about 0.5ms at the most from releasing a standby mode to starting up VccOUT. Therefore, ENABLE signal should be input 0.5ms or more later than BSTBY signal.

- (2) Shutdown

- Note 3) Make sure that the outputs to drive a motor are switched off by using ENABLE signal input before a standby mode is turned on.

- Note 4) After BSTBY signal input switched(H→L), pay attention to the fact that It takes 5ms until VccOUT voltage becomes less than 3.8V, in which the internal logic circuit is off.

## 7.4 CLK input

The electrical angle advances by 1 for each CLK input. The signal is reflected at a rising edge.

| CLK input | Function                                |

|-----------|-----------------------------------------|

|           | Goes to the next step at a rising edge. |

|           | No change (stays in the previous state) |

## 7.5 ENABLE circuit

Switches the motor drive outputs ON / OFF. When ENABLE input is turned from H to L under the standby mode released (BSTBY=H), constant current operation starts, an internal counter which is synchronized with CLK input moves forward and then a motor begins to run.

Be sure to fix ENABLE pin to the L level during a power supply start-up and shutdown.

ENABLE controls only switching ON/OFF the motor drive outputs. However, the internal counter proceeds because the internal logic circuit counter is still working even when ENABLE=L; the outputs to drive a motor are turned off.

| ENABLE input | Output MOSFETs |

|--------------|----------------|

| Н            | ON             |

| L            | OFF            |

In addition, in the case where DIAG pin is latched to L level after either overcurrent detection or over temperature detection, refer to 7.10, the latch can be released by setting ENABLE pin to L level whose duration should be 0.2ms or more(Note). However, if an overcurrent state or an over temperature state continues, DIAG outputs L level again. Refer to 7.18 and 7.19.

Note) Inspection for it is not conducted at the time of shipment.

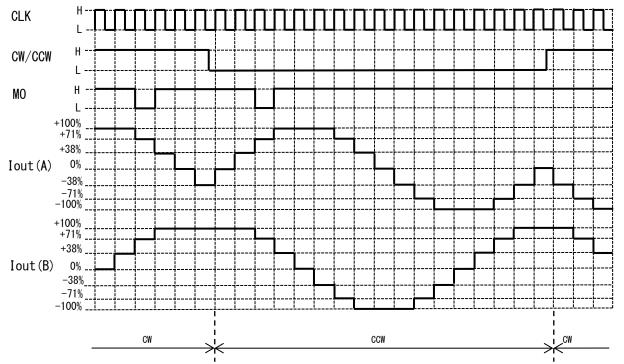

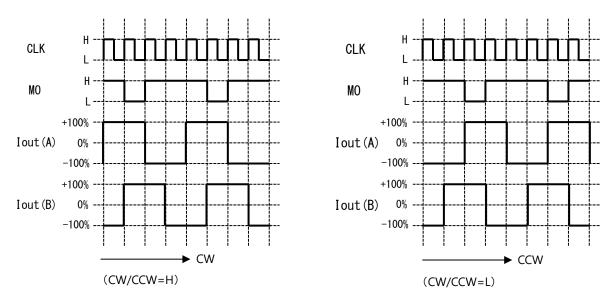

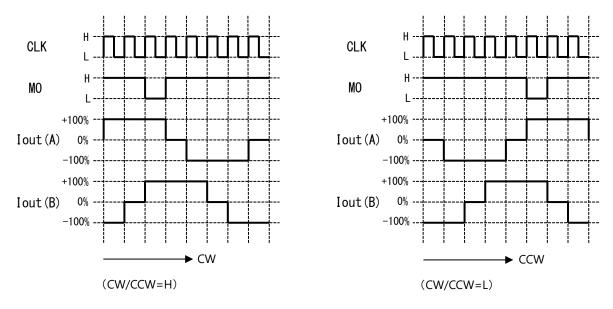

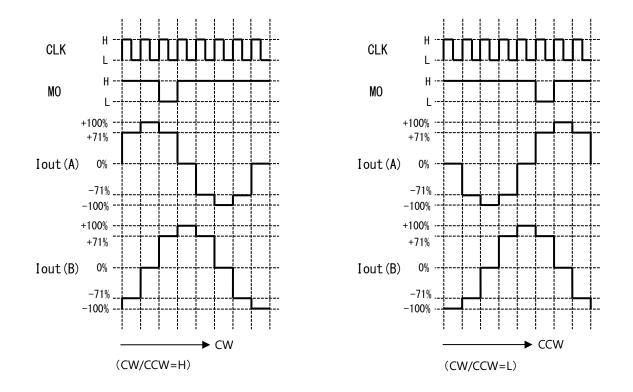

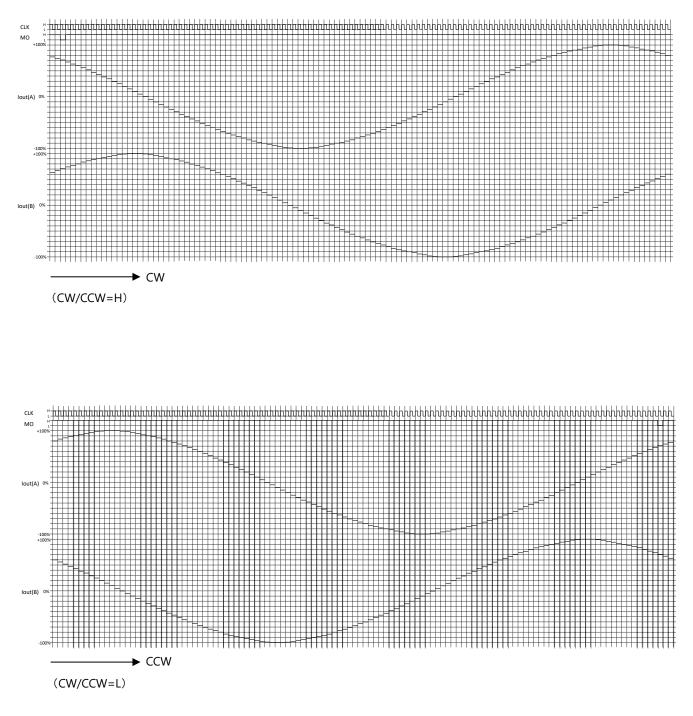

## 7.6 CW/CCW control circuit

Switches the rotation direction of the stepping motor. When CW/CCW=H, the current in the phase A is output with a phase advance of 90° relative to that in the phase B. When CW/CCW=L, the current in the phase B is output with a phase advance of 90° relative to that in the phase A.

| CW/CCW input | Function               |

|--------------|------------------------|

| Н            | Clockwise (CW)         |

| L            | Counterclockwise (CCW) |

e.g. when CW/CCW is changed at quarter step resolution:

Timing charts may be simplified for explanatory purposes.

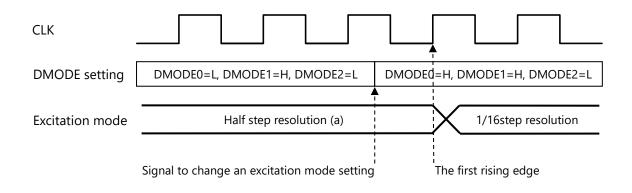

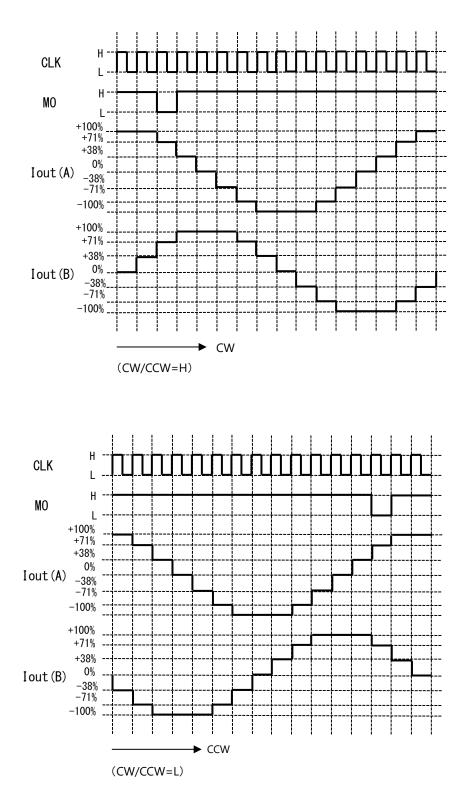

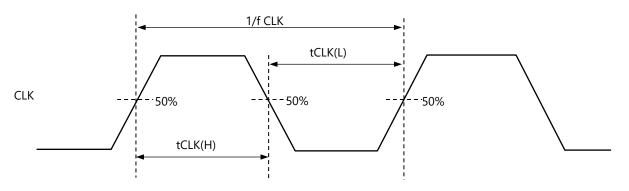

## 7.7 Excitation mode setting (DMODE)

DMODE0, DMODE1 and DMODE2 switch step resolution.

When DMODE 0 = DMODE 1 = DMODE 2 = L, the current setting of the phase A is set to 71% and the current setting of the phase B is also set to 71%. At this time, the L level is output from the MO pin.

| DMODE0 input | DMODE1 input | DMODE2 input | Function                         |

|--------------|--------------|--------------|----------------------------------|

| L            | L            | L            | A phase 71%, B phase 71%         |

| L            | L            | Н            | Full step resolution setting     |

| L            | Н            | L            | Half step resolution (a) setting |

| L            | Н            | Н            | Quarter step resolution setting  |

| Н            | L            | L            | Half step resolution (b) setting |

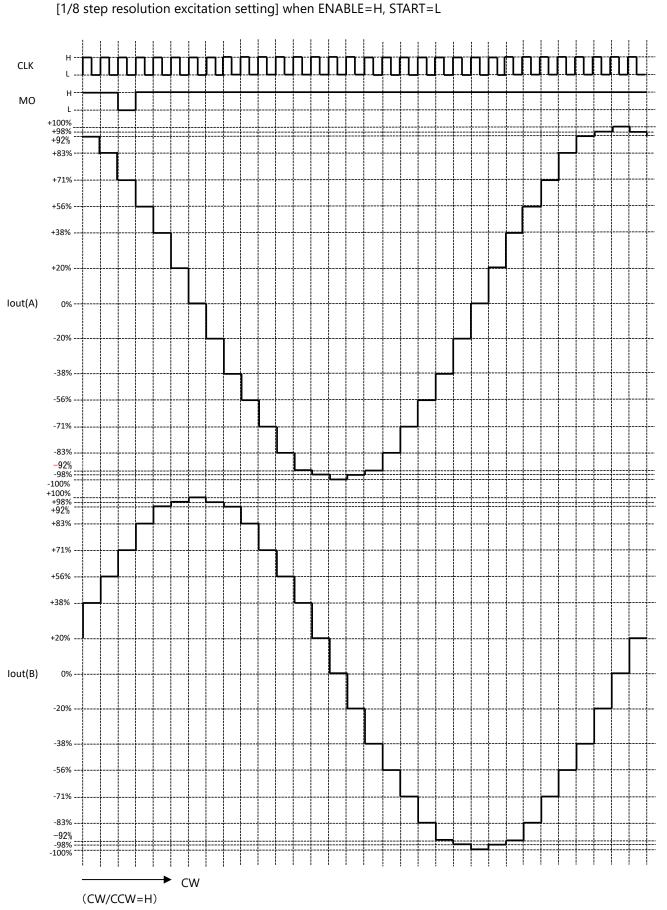

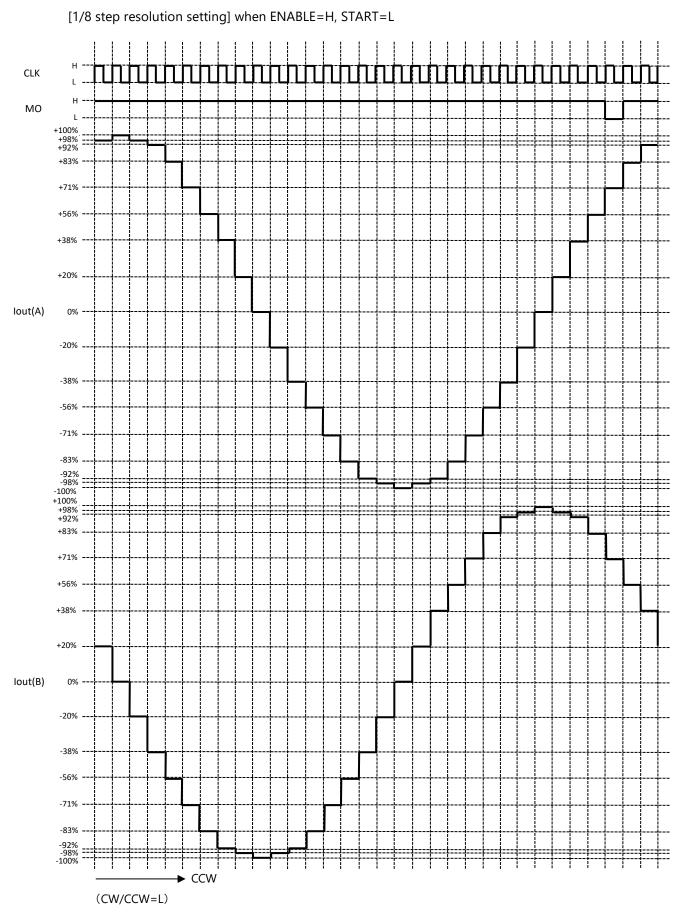

| Н            | L            | Н            | 1/8 step resolution setting      |

| Н            | Н            | L            | 1/16 step resolution setting     |

| Н            | Н            | Н            | 1/32 step resolution setting     |

As shown in the figure below, when step resolution is switched with DMODE pins, it is reflected at the first rising edge of CLK after the change.

Timing charts may be simplified for explanatory purposes.

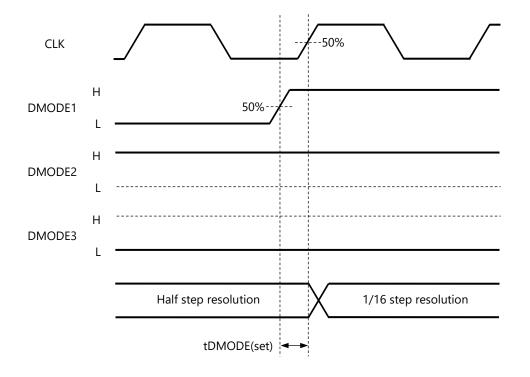

## 7.8 START Function

Initializes an electrical angle in the internal counter to set to an initial position.

| START input | Input function                                                   |

|-------------|------------------------------------------------------------------|

| Н           | Initialization of electrical angle (Setting to initial position) |

| L           | Normal operation                                                 |

When START is set to H, an electrical angle stays in the initial position, and then L level is output from MO pin.

| Excitation mode          | Current setting<br>in A phase | Current setting<br>in B phase | Initial electrical angle<br>and initial position |

|--------------------------|-------------------------------|-------------------------------|--------------------------------------------------|

| Full step resolution     | 100%                          | 100%                          | 45°                                              |

| Half step resolution (a) | 100%                          | 100%                          | 45°                                              |

| Half step resolution (b) | 71%                           | 71%                           | 45°                                              |

| Quarter step resolution  | 71%                           | 71%                           | 45°                                              |

| 1/8 step resolution      | 71%                           | 71%                           | 45°                                              |

| 1/16 step resolution     | 71%                           | 71%                           | 45°                                              |

| 1/32 step resolution     | 71%                           | 71%                           | 45°                                              |

When START is set to H, a current setting in each phase is as follows.

A position of the initial electrical angle in the above table is defined as the initial position, and when it reaches the initial position during motor rotation, an L level is output from MO pin. In addition, a change of the state of START pin is reflected in outputs as synchronized with a CLK signal.

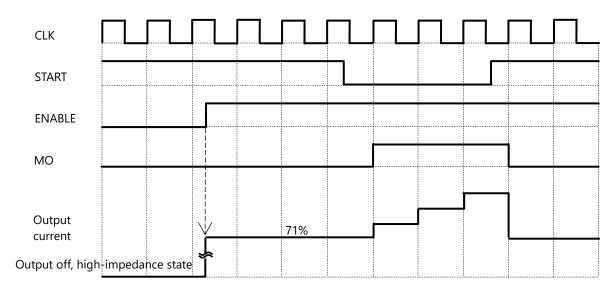

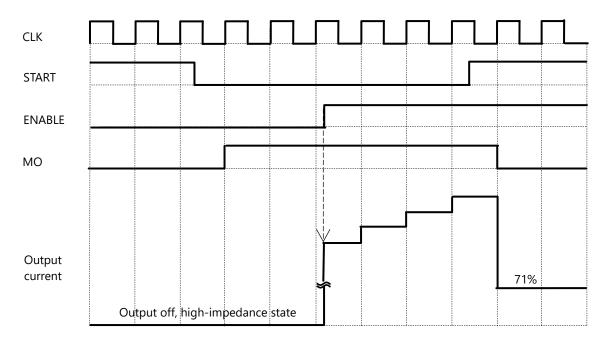

Examples of motor function operation

(1) Timing chart (In the case of ENABLE prior to START)

(2) Timing chart (In the case of START prior to ENABLE)

Regarding (1) and (2) above, the rise of output current starts coming out at the timing of a charge mode of output PWM chopping period after switching ENABLE from L to H. The output PWM chopping period is not synchronized with CLK input signal.

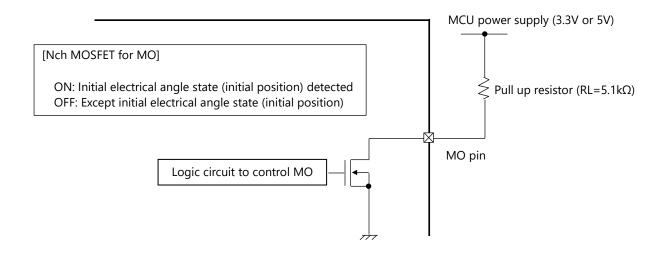

## 7.9 MO output

Monitors an electrical angle. MO pin outputs L in a state of an initial electrical angle (an initial position).

| State of electrical angle                      | MO output      |

|------------------------------------------------|----------------|

| Except initial state (except initial position) | High-impedance |

| Initial state (initial position)               | L              |

MO is an open drain pin of Nch MOSFET output; therefore, please pull up the pin with an external resistor to the same potential (3.3 V or 5.0 V) as an MCU power supply. The pin stays in high-impedance except for an initial electrical angle state(initial position), on the other hand, the internal Nch MOSFET is turned on if an initial electrical angle state (initial position) is detected. If the pin is not used, please leave it open.

The above circuit diagram is partially omitted and simplified in order to explain the operations.

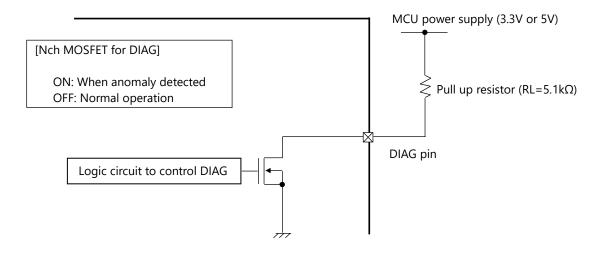

## 7.10 DIAG function (Anomaly state diagnosis)

If an anomaly state (a motor load open, over temperature (TSD) or overcurrent (ISD)) is detected, L is output from DIAG pin.

| Anomaly detection               | Output from DIAG |

|---------------------------------|------------------|

| Normal state (normal operation) | High-impedance   |

| Motor load open                 | L                |

| Over temperature (TSD)          | L                |

| Overcurrent (ISD)               | L                |

DIAG is an open drain pin of Nch MOSFET output; therefore, please pull up the pin with an external resistor to the same potential (3.3 V or 5.0 V) as an MCU power supply. The pin stays in high impedance during normal operation, on the other hand, the internal Nch MOSFET is turned on If an anomaly state (a motor load open, over temperature (TSD) or overcurrent (ISD)) is detected. When over temperature (TSD) or overcurrent (ISD)) is detected. When over temperature (TSD) or overcurrent (ISD)) is detected, DAIG works as a latch circuit. The latch can be released by either rebooting VBAT or setting ENABLE pin to L level whose duration should be 0.2ms or more(Note). If the pin is not used, please leave it open.

Note) Inspection for it is not conducted at the time of shipment.

The above circuit diagram is partially omitted and simplified in order to explain the operations.

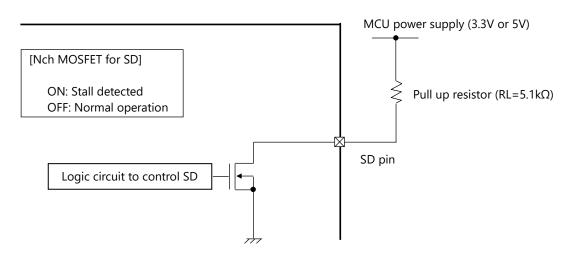

## 7.11 Stall detection (SD: Stall detection) function

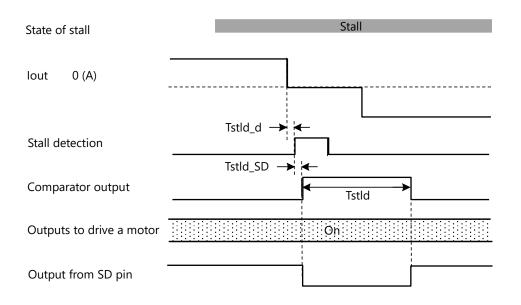

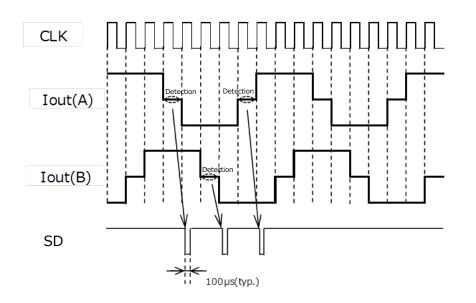

When a stall (step-out) is detected, L is output from SD pin.

| Mode                               | Output from SD       |

|------------------------------------|----------------------|

| In normal state (normal operation) | High impedance       |

| When stall (step-out) detected     | L pulse, 100µs(typ.) |

SD is an open drain pin of Nch MOSFET output; therefore, please pull up the pin with an external resistor to the same potential (3.3 V or 5.0 V) as an MCU power supply. The pin stays in high impedance during normal operation, on the other hand, if a stall detected, the internal Nch MOSFET is turned on and L pulse (100µs(typ.)) is output from the pin at every detection. If the pin is not used, please leave it open.

The above circuit diagram is partially omitted and simplified in order to explain the operations.

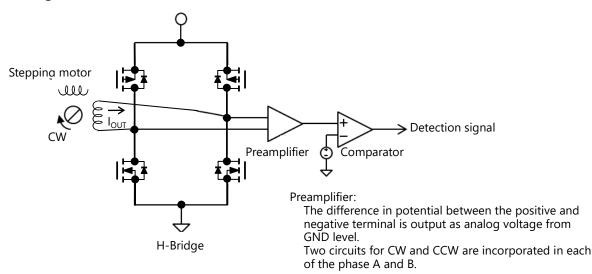

#### **Description of operation**

Certain voltage as the potential difference between both terminals of each coil of a motor (that is, OUTA + pin and OUTA- pin, and OUTB + pin and OUTB- pin) is normally generated by induced voltage during the period when a current level is set at 0 (zero) A as a motor is running. On the other hand, unless a motor runs, no voltage at both terminals of each coil of a motor can be generated because of no induced voltage.

In this function, unless induced voltage is generated more than the defined voltage at that period, the IC recognizes that a motor doesn't run and then judges that it is a stall.

#### **Configuration of stall detection circuit**

### Setting of stall detection threshold

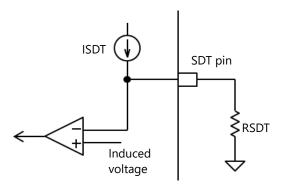

A stall detection threshold is set by either connecting an external resistor RSDT between SDT pin and GND or by applying DC voltage VSDT to SDT pin.

(1) In the case of an external resistor RSDT connected between SDT pin and GND

- The product of an SDT pin external resistance RSDT multiplied by an SDT pin current ISDT is an SDT pin threshold setting voltage VSDT.

- $VSDT(V) = RSDT(\Omega) \times ISDT(A)$

Refer to 10.5.

- Induced voltage from a motor is directly compared to the SDT pin voltage VSDT inside the IC.

- RSDT should be set as follows.  $0k\Omega \le RSDT \le 230k\Omega$

(2) In the case of DC voltage VSDT applied to SDT pin.

- Induced voltage from a motor is directly compared to applied voltage VSDT inside the IC.

- Applied voltage to SDT pin should range from 0V to 3.0V.

If the pin is not used, please leave it open.

#### Notes on the stall detection function

- When a motor runs with full step resolution, the stall detection function does not work because there is no period of current level 0 (zero) A setting in that step resolution.

- If either rotation speed of a motor is low or induced voltage is not sufficiently induced due to a type of motor, the stall detection function may not work properly. Therefore, a threshold value should be set after characteristics of a motor, driving conditions and so on have been validated certainly in advance.

- While a motor runs at low speed, for example, during a start-up from stopping, because induced voltage is not sufficiently induced, there is a possibility that the stall detection function may not work properly. This period need to be exempted to use the stall detection function effectively.

- Even if a stall is being detected, outputs to drive a motor keep turning on continuously. The stall detection circuit doesn't change the state of outputs to drive a motor.

- SD pin outputs L pulse, whose width is 100µs(typ.), as a stall detection signal while current is 0A, on the other hand, in other periods a state of SD pin stays in high-impedance. When a stall is being detected, that routine repeats.

#### Timing chart (1) when stall detected

Timing chart (2) when stall detected

Timing of neither a rising nor a falling edge of output signals from SD pin is synchronized with CLK and other signals.

## 7.12 OSC circuit

This IC has two oscillator circuits, OSCM and OSCS. They are used as a reference clock for other circuits.

- OSCM oscillator circuit : generation of a clock signal to set PWM chopping frequency

OSCS oscillator circuit : generation of a clock signal to work internal circuits except PWM chopping one in the IC

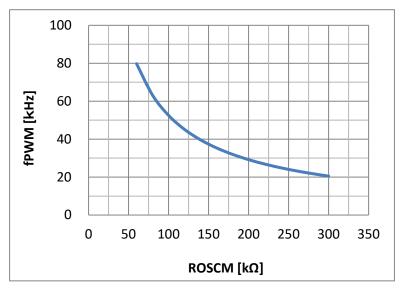

- (1) OSCM oscillation (to set PWM chopping frequency)

OSCM oscillation frequency fOSCM is determined by an external resistor ROSCM connected between OSCM pin and GND, and then PWM chopping frequency fPWM is set.

PWM chopping frequency fPWM and OSCM oscillation frequency fOSCM should be set as the following ranges:

- $20kHz \leq fPWM \leq 80kHz$

- 640kHz  $\leq$  fOSCM  $\leq$  2560kHz

OSCM oscillation frequency fOSCM and PWM frequency fPWM is calculated by the following equation.

• fPWM = 1 / 32 × fOSCM

The relationship between fPWM and ROSCM is shown in the below chart. This is just reference data and can be changed under some conditions.

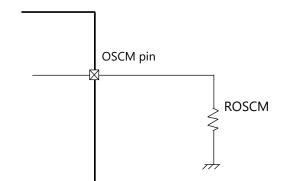

An external resistor ROSCM is required between OSCM pin and GND.

The above circuit diagram may be simplified for explanatory purposes.

(2) OSCS oscillation (to work internal circuits in the IC)

OSCS oscillation frequency is set at 4MHz(typ.) by internal circuit in the IC.

## 7.13 Operation of motor function

## Electrical angle and initial position in excitation mode setting

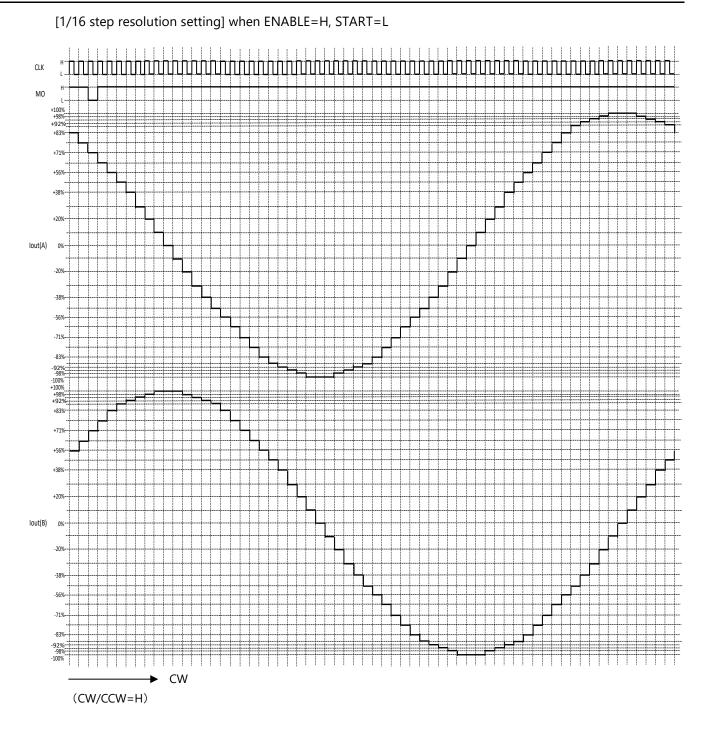

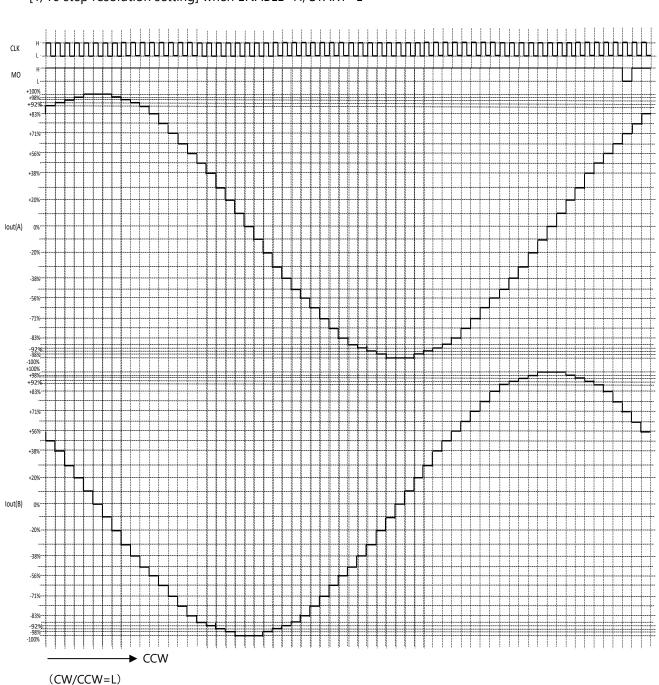

[Full step resolution setting] when ENABLE=H, START=L

[Half step resolution (a) setting] when ENABLE=H, START=L

\* The waveform can be output from MO pin when pulled up.

[Half step resolution (b) setting] when ENABLE=H, START=L

\* The waveform can be output from MO pin when pulled up.

[Quarter step resolution setting] when ENABLE=H, START=L

\* The waveform can be output from MO pin when pulled up.

\* The waveform can be output from MO pin when pulled up.

\* The waveform can be output from MO pin when pulled up.

\* The waveform can be output from MO pin when pulled up.

[1/16 step resolution setting] when ENABLE=H, START=L

\* The waveform can be output from MO pin when pulled up.

[1/32 step resolution setting] when ENABLE=H, START=L

\* The waveform can be output from MO pin when pulled up.

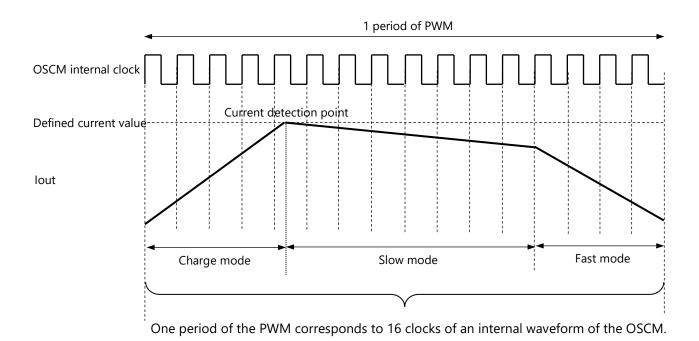

## 7.14 Constant current PWM control

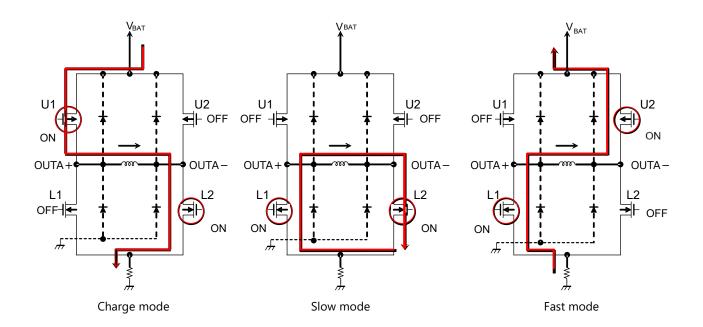

#### Mixed decay mode and operation of zero point detection

- Charge mode: A charge mode starts as synchronized with an OSCM internal clock.

- Slow mode : A slow mode starts at the point where output current lout reaches a defined current

value

- Fast mode : A period of a fast mode is between the 13th and 16th clock from the beginning of a charge mode, which is 25% of 1 period of PWM

Note: If output current lout reaches the zero point (0A) during 1 period of PWM, which corresponds to 16 clocks of OSCM internal clocks, outputs become high-impedance.

### **Output stage transistor operation mode (Mixed decay mode)**

(Ach is taken as an example. Bch is the same as Ach.)

\* Shoot-through preventive time is set inside the IC to prevent shoot-through current at the timing of a change of modes.

The equivalent circuit diagrams may be simplified or some parts of them may be omitted for explanatory purposes.

#### Function of transistor operation at output stage

$\langle\,$  When current path through a coil in a charge mode is from U1 to L2  $\,\rangle\,$

| Mode       | U1  | U2  | L1  | L2  |

|------------|-----|-----|-----|-----|

| Charge     | ON  | OFF | OFF | ON  |

| Slow decay | OFF | OFF | ON  | ON  |

| Fast decay | OFF | ON  | ON  | OFF |

$\langle$  When current path through a coil in a charge mode is from U2 to L1  $\rangle$

| Mode       | U1  | U2  | L1  | L2  |

|------------|-----|-----|-----|-----|

| Charge     | OFF | ON  | ON  | OFF |

| Slow decay | OFF | OFF | ON  | ON  |

| Fast decay | ON  | OFF | OFF | ON  |

### **Current value setting**

Current value at 100% to control constant currnet is determined by both an external resistor RRS to detect motor current and reference voltage Vref input from external power supply voltage.

RRSs are resistors between RSA pin and GND, and between RSB pin and GND, which should be the same value.

In addition, the external input reference voltage Vref is attenuated inside the IC and its attenuation ratio Vrefgain is 1/10 (typ.).

$$lout(Max) = Vrefgain \times \frac{Vref(V)}{RRS(\Omega)}$$

e.g. When RRS=0.4 $\Omega$ , Vref=2.0V input and TORQUE=100%, a defined current value at 100% is shown below:

lout(Max) =

$$1/10 \times 2.0$$

(V) / 0.4 (Ω)

= 0.5 (A)

### TORQUE pin

A weak excitation mode can be set by using TORQUE0 and TORQUE1 pin. Both TORQUE0 and TORQUE1 pin should always be set at L, unless a weak excitation mode is used.

| TORQUE0 | TORQUE1                       | Function                     |

|---------|-------------------------------|------------------------------|

| L       | L                             | Defined current value × 100% |

| Н       | L                             | Defined current value × 70%  |

| L       | Н                             | Defined current value × 50%  |

| Н       | H Defined current value × 30% |                              |

## 7.15 Load open detection

This IC incorporates a load open detection function at output pins (OUTA +, OUTA-, OUTB +, and OUTB-). If a load connected to output pins becomes disconnected, a load open at the output pin is detected.

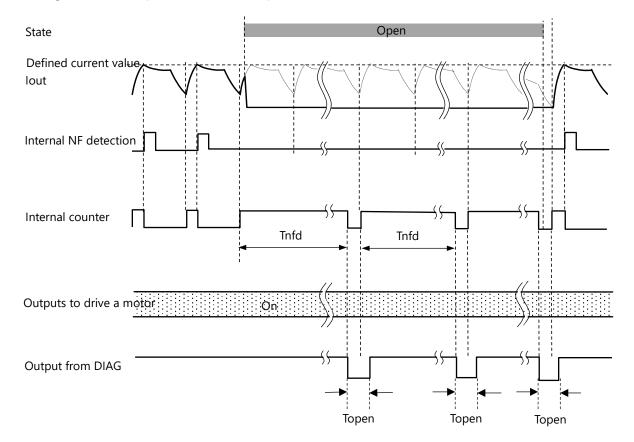

#### **Description of operation**

An internal counter starts to count at the starting point of a charge mode while constant current is operating. Moreover, when output current lout reaches a defined value within Tnfd (50ms(typ.)), an internal NF detection signal is output and the counter is reset.

On the other hand, unless output current lout reaches a defined value due to a load open, both an internal NF detection signal isn't output and an internal counter gets over Tnfd, and then L pulse Topen, whose width is 100µs(typ.), is output from DIAG pin. An OSCM internal clock for a constant current PWM control keeps operating and an internal counter starts to count at every starting point of a charge mode, in other words at intervals of 16 periods of OSCM internal clocks, refer to 7.14, except during Tnfd. Therefore, if a load open, where no output current passes, is still going on after a period of Tnfd, an internal counter starts to count again, and then L pulse is output from DIAG pin after Tnfd in the same way.

When a state changes from a load open to normal connection, output current lout begins to pass at the first charge mode after the last period of Tnfd, and the original sequence is recovered.

#### $\langle$ Timing chart for one phase when a load open detected $\rangle$

Timing charts may be simplified for explanatory purposes.

Note) It takes more than 50ms(typ.) to detect a load open because periods of PWM need to be counted again from an initial state, for example, if a load open occurs under the condition that output current lout is 0A.

## 7.16 Overcurrent Detection (ISD)

If either a power fault or a ground fault occurs at output pins to a motor, an overcurrent is detected at that time and L is output from DIAG pin. This IC incorporates overcurrent detection circuits as shown below:

#### (1) Drain current detection circuits on upper Pch MOSFETs

If drain current which passes through upper Pch MOSFETs in either phase A or B exceeds the threshold lovc=2A(typ.), outputs to drive a motor are turned off.

- If current which exceeds the threshold passes through upper Pch MOSFETs, outputs to drive a motor are turned off and L is output from DIAG pin.

- If overcurrent is detected, outputs to drive a motor are turned off and are latched. During a transitional period from on to off state a period of the current regeneration mode Tregene 5ms(typ.) is provide.

- An output from DIAG pin is turned from H to L after TpdOVC\_DIAG (3.5µs(typ.)) from a rising edge of an internal comparator output.

- The latch can be released by either rebooting VBAT or setting ENABLE pin to L level whose duration should be 0.2ms or more(Note1). In the case where L is input to ENABLE pin to release a latch, the release is done during L period on ENABLE and an output signal from DIAG changes from L to H at the same time.

- Outputs to drive a motor change from off to on after tpLH(EN) (4µs(typ.)) from a rising edge of ENABLE pin.

- A power fault and a ground fault have different regeneration modes. In the case of a power fault, a slow decay mode consists of an on state of upper Pch MOSFETs and an off state of lower Nch MOSFETs. On the other hand, in the case of a ground fault, a slow decay mode consists of an off state of upper Pch MOSFETs and on state of lower Nch MOSFETs.

| en overcurrent detected (1) >                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                             |

|                                                                                                                                             |

|                                                                                                                                             |

| t                                                                                                                                           |

| Int detection Latched Unlatched                                                                                                             |

| Regeneration period: Tregene 5ms(typ.)                                                                                                      |

| ON Regeneration OFF (HiZ) ON                                                                                                                |

| TpdOVC_DIAG                                                                                                                                 |

| 0.2ms or more (Note1) ← tpLH(EN)<br>(4µs(typ.))                                                                                             |

| ent detection<br>(Note2) Tovc<br>Regeneration period: Tregene 5ms(typ.)<br>ON<br>ON<br>Regeneration OFF (HiZ)<br>TpdOVC_DIAG<br>TpdOVC_DIAG |

Note1) Inspection for it is not conducted at the time of shipment. Note2) A masking period Tovc (1.2µs(typ.)) is provided so that circuits doesn't work due to noise.

#### (2) Current detection circuit with external resistor RRS

If voltage which is generated by current passing through each external resistor RRS connected to RSA and RSB exceeds the threshold 600mV(typ.), outputs to drive a motor are turned off.

Vovc  $\leq$  lout  $\times$  RRS

- If voltage between terminals of an external resistor RRS, through which current passes, exceeds the threshold 600mV(typ.), outputs to drive a motor are turned off and L is output from DIAG pin.

- If overcurrent is detected, outputs to drive a motor are turned off and are latched. During a transitional period from on to off state a period of the current regeneration mode Tregene 5ms(typ.) is provide.

- An output from DIAG pin is turned from H to L after TpdOVC\_DIAG (3.5µs(typ.)) from a rising edge of an internal comparator output.

- The latch can be released by either rebooting VBAT or setting ENABLE pin to L level whose duration should be 0.2ms or more(Note1). In the case where L is input to ENABLE pin to release a latch, the release is done during L period on ENABLE and an output signal from DIAG changes from L to H at the same time.

- Outputs to drive a motor change from off to on after tpLH(EN) (4µs(typ.)) from a rising edge of ENABLE pin.

- A power fault and a ground fault have different regeneration modes. In the case of a power fault, a slow decay mode consists of an on state of upper Pch MOSFETs and an off state of lower Nch MOSFETs. On the other hand, in the case of a ground fault, a slow decay mode consists of an off state of upper Pch MOSFETs and on state of lower Nch MOSFETs.

- $\langle$  Timing chart when overcurrent detected (2)  $\rangle$

| Overcurrent detection threshold voltage |                  |              | $\square$            |           |                         |

|-----------------------------------------|------------------|--------------|----------------------|-----------|-------------------------|

| Vovc=0.6V(typ.)                         |                  |              |                      |           |                         |

| Voltage at RSA<br>Voltage at RSB        |                  |              |                      |           | _ <b></b>               |

| Internal comparator ou                  | tput             |              | L                    |           |                         |

| Internal signal of overc                | urrent detection | (Note2) Tovc | Latched              |           | itched                  |

| Outputs to drive a mot                  | or ON            |              | Regeneration         | OFF (HiZ) | X on                    |

| Output from DIAG pin                    |                  | TpdOVC_D     | <b>▲→</b><br>IAG     |           |                         |

| Input to ENABLE pin                     |                  |              | 0.2ms or more (Note1 |           | tpLH(EN)<br>(4μs(typ.)) |

Note1) Inspection for it is not conducted at the time of shipment. Note2) A masking period Tovc (1.2µs(typ.)) is provided so that circuits doesn't work due to noise.

## 7.17 Over temperature detection (TSD)

If temperature on the chip reaches defined temperature TSDtemp, outputs to drive a motor are turned off, moreover, the IC is latched, and then L is output from DIAG pin. If over temperature is detected, the outputs are turned off after the regeneration period Tregene 5ms(typ.)

Over temperature detection shutdown temperature TSDtemp is set at 175°C (typ.) and it exhibits 10°C (typ.) of hysteresis.

It recovers right after either rebooting VBAT or setting ENABLE pin to L level whose duration should be 0.2ms or more (Note) after the temperature on the chip is less than the recovery temperature TSDL 165°C (typ.). In the case where L is input to ENABLE pin to release a latch, the release is done during L period on ENABLE and an output signal from DIAG changes from L to H at the same time.

$\langle$  Timing chart when over temperature detected  $\rangle$

|                                          |                      | Temperature on chip ( | (Tj)       |          |                  |    |

|------------------------------------------|----------------------|-----------------------|------------|----------|------------------|----|

| TSDtemp=175°C (typ.)<br>TSDL=165°C(typ.) |                      |                       | ~~~        |          |                  |    |

| Internal comparator<br>output –          |                      |                       |            |          |                  |    |

| –<br>Internal signal of over te          | emperature detection | Latched               |            | Unlato   | hed              |    |

| -                                        |                      | Regeneration period:  | Tregene 5m | ns(typ.) | ·                |    |

| Outputs to drive a moto                  | or ON                | <b>Regene</b> ration  | OFF (Hiz   | .)       | X                | ON |

| Output from DIAG pin                     |                      |                       |            |          |                  |    |

| –<br>Input to ENABLE pin                 |                      | 0.2ms or more (No     | ote)       |          | tpLH(E<br>(4µs(i |    |

Note) Inspection for it is not conducted at the time of shipment.

Timing charts may be simplified for explanatory purposes.

#### Notes:

The absolute maximum rating of the guaranteed storage temperature range of this product is 150°C (max.). Storage and use beyond this temperature cannot guarantee the normal operation of the IC afterwards, and it may also cause smoking and ignition. Please do not store or use it beyond this temperature in any case. Although this IC incorporates the following over temperature detection function, this function does not suppress the temperature of this IC below the over temperature detection shutdown temperature TSDtemp, and it is a function outside the guaranteed operation range. Please regard it as an auxiliary function. Regarding this function, although an actual temperature inspection is not conducted for each product at the time of shipment, circuit operation is checked as a substitute inspection.

## 7.18 Operation outside the scope of the operation voltage range

In the case of operation voltage range 7 V to 18 V, electrical characteristics values described in this document are guaranteed.

Operation at 4.5 V to 7 V, which isn't the above operation voltage range is described as follows. Only function operation is guaranteed, on the other hand, electrical characteristics values are not guaranteed.

The function operation mentioned here is that outputs operates corresponding to the truth tables with signals to input pins.

| Functions and circuits which work at 4.5 V to 7.0 V                        | Operation                  |

|----------------------------------------------------------------------------|----------------------------|

| VccOUT circuit                                                             |                            |

| OSC circuit                                                                |                            |

| • Each control logic circuit                                               |                            |

| • MO circuit                                                               | Function operation works.  |

| • DIAG circuit                                                             | Electrical characteristics |

| • SD circuit                                                               | values are not guaranteed. |

| $\cdot$ Motor function (CW/CCW rotation, each step resolution mode)        |                            |

| • Each detection circuit (overcurrent, over temperature, load open, stall) |                            |

| Constant current chopping control                                          |                            |

## 7.19 Regeneration Operation

In the following cases, outputs to drive a motor is switch into a high-impedance state after regeneration operation is done during a transitional period or a regeneration period Tregene.

- 1. When either TSD or ISD operates.

- 2. When either TSD or ISD operates after a load open occurs.

- 3. When ENABLE = H, moreover, BSTBY pin changes from H level to L level.

- 4. When ENABLE pin changes from H level to L level.

## 8. Absolute maximum rating (Ta = 25°C)

| Characterist                | ics              | Symbol  | Applicable pins                                                                         | Conditions                | Rating                               | Unit |

|-----------------------------|------------------|---------|-----------------------------------------------------------------------------------------|---------------------------|--------------------------------------|------|

| Power supply voltage        |                  |         |                                                                                         | DC                        | -0.3 to 18                           | V    |

|                             |                  | VBAT    | VBAT                                                                                    | 1min (Note1)              | 30                                   | V    |

|                             |                  | VDAI    | VDAI                                                                                    | Transient 0.5s<br>(Note2) | 40                                   | V    |

| Input voltage               |                  | VIN1    | CLK, TORQUE0, TORQUE1,<br>DMODE0, DMODE1,<br>DMODE2, START, ENABLE,<br>CW/CCW and BSTBY | DC                        | -0.3 to 6.0                          | V    |

| pat rona                    | 90               |         | VREF                                                                                    | DC (Note3)                | -0.3 to 6.0                          |      |

|                             |                  |         | VDD                                                                                     | DC                        | -0.3 to 6.0                          | V    |

|                             |                  | VIN2    | RSA and RSB                                                                             | _                         | -0.3 to 1.0                          | V    |

| Output voltage 1            |                  |         | VccOUT                                                                                  | DC                        | -0.3 to 6.0                          | V    |

| Output voltage              | Output voltage 2 |         | DIAG, SD and SDT                                                                        | DC                        | -0.3 to 6.0                          | V    |

| Output voltag               | Output voltage 3 |         | SDT                                                                                     | DC                        | -0.3 to 6.0                          | V    |

| Output voltage 4            |                  | VOUT    | OUTA+, OUTA-, OUTB+<br>and OUTB-                                                        | DC<br>(Note4, 5 and 6)    | -VF to<br>VBAT+VF and<br>VBAT+VF≤40V | V    |

| Output current 1            |                  | lout    | OUTA+, OUTA-, OUTB+<br>and OUTB-                                                        | (Note7)                   | Overcurrent detection value          | А    |

| Output current 2            |                  |         | DIAG, SD and MO                                                                         | DC                        | 2.5                                  | mA   |

| Allowable power dissipation | QFN28            | PD      | — (Note8)                                                                               |                           | 3.9                                  | W    |

| Operation temp              | erature          | Topr    | _                                                                                       | _                         | -40 to 125                           | °C   |

| Storage tempe               | rature           | Tstr    | -                                                                                       | _                         | -55 to 150                           | °C   |

| Junction tempe              | rature           | Tj(max) | _                                                                                       | —                         | 150                                  | °C   |

\* The inflow current to this IC is indicated by "+", and the outflow current from this IC is indicated by "-".

\* Inspections for some characteristics in the absolute maximum rating are not conducted at the time of shipment.

- Note1) The voltage over the upper limit of the operation voltage range; 18 V can be applied only for a jump start. In the case of a use at 18 V or more, thermal performance should be carefully designed.

- Note2) Voltage gap between VBAT and GND should be less than the maximal voltage 40V.

- Note3) Voltage gap between VREF and GND should be less than the maximal voltage 6V.

- Note4) The maximum rating including back-EMF voltage should not exceed.

- Note5) Voltage value which is generated by current flowing through a body diode in output MOSFET in a regeneration mode after outputs are turned off due to a load short circuit is taken into account as a VF value.

- Note6) The difference between GND, and each output pin OUTA+, OUTA , OUTB+ and OUTB in voltage should not exceed 40 V.

- Note7) Thermal performance should be carefully designed, moreover, evaluations should be thoroughly undergone so that the junction temperature can be less than 150°C,

- Note8) Under measurement conditions; Ta = 25°C, no wind and JEDEC 4-layer printed circuit board with 9 via holes right underneath the IC

The maximum rating is the rating that should never be exceeded, even for a shortest of moments. If the maximum rating is exceeded, it could result in damage and/or deterioration of the IC as well as other devices beside the IC. Regardless of the operating conditions, please design so that the maximum rating is never exceeded. Please use within the specified operating range.

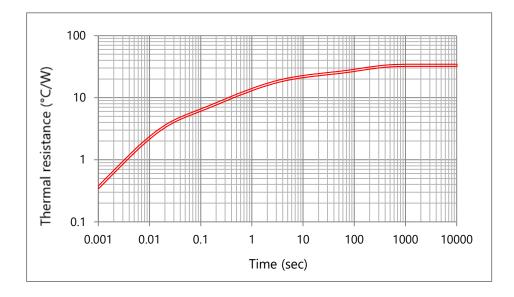

### Thermal resistance data on P-VQFN28-0606-0.65, for reference

<Measurement conditions>

TOSHIBA

- Ambient temretature Ta = 25°C

- 1W dissipated

- With no wind

- JEDEC 4-layer board with 9 via holes

<Saturation thermal resistance, for reference>

• Rthj-a = 31.3 °C/W

## 9. Operation Range (Ta = -40°C to 125°C)

| Characteristics                  |         | Symbol      | Min | Тур. | Max | Unit | Remarks                       |

|----------------------------------|---------|-------------|-----|------|-----|------|-------------------------------|

| Motor power supply voltage 1     |         | VBAT        | 4.5 | I    | 7   | V    | Function operation only, Note |

| Motor power supply voltage 2     |         | VBAT        | 7   | 13   | 18  | V    | —                             |

| Clock frequency input range      |         | fCLK        | 1   | I    | 100 | kHz  | —                             |

| Chopping frequency setting range |         | fPWM(range) | 20  | Ι    | 80  | kHz  | _                             |

| Vref voltage input range         |         | Vref        | 0.3 | 1.5  | 3.0 | V    | —                             |

| Power supply slew rate           | rising  | VBSLEW      |     | Ι    | 2   | V/µs | —                             |

| Fower supply siew rate           | falling | VBSLEW      | -2  |      | _   | V/µs |                               |

Note) Refer to 7.18 Operation outside the scope of the operation voltage range

## **10 Electrical characteristics**

## 10.1 Electrical characteristics 1 (Unless otherwise specified, Ta = -40°C to 125°C, VBAT = 7 to 18 V)

|                    |                               | (0        |                                                |                                                      |     | •    |     | - /  |

|--------------------|-------------------------------|-----------|------------------------------------------------|------------------------------------------------------|-----|------|-----|------|

| Characteris        | tics                          | Symbol    | Applicable pin                                 | Measurement conditions                               | Min | Тур. | Max | Unit |

| Logic input pin    | HIGH                          | VIN1(H)   | CLK, TORQUE0,                                  | -                                                    | 2.0 | —    | 5.5 | V    |

| input voltage 1    | LOW                           | VIN1(L)   | TORQUE1,                                       | _                                                    | 0   | —    | 0.8 | V    |

| Input hysteresis 1 |                               | VIN1(HYS) | CW/CCW,                                        | _                                                    | 0.1 | —    | 1.0 | V    |

| Logic input pin    | HIGH                          | IIN1(H)   | DMODE0,<br>DMODE1,<br>DMODE2,                  | Measurement LOGIC input<br>pin=5V                    | 30  | 50   | 100 | μA   |

| input current 1    | LOW                           | IIN1(L)   | START and<br>ENABLE                            | Measurement LOGIC input<br>pin=0V                    | -5  | _    | 5   | μA   |

| Logic input pin    | HIGH                          | VIN2(H)   |                                                | _                                                    | 2.2 | —    | 5.5 | V    |

| input voltage 2    | LOW                           | VIN2(L)   |                                                | _                                                    | 0   | —    | 0.5 | V    |

| Input hysteresis 2 |                               | VIN2(HYS) | BSTBY                                          | _                                                    | 0.1 | —    | 1.2 | V    |

| Logic input pin    | HIGH                          | IIN2(H)   |                                                | BSTBY=5V                                             | 36  | 60   | 120 | μA   |

| input current 2    | LOW                           | IIN2(L)   |                                                | BSTBY=0V                                             | -5  | —    | 5   | μA   |

| Standby settled pe | riod                          | tSTB      | BSTBY                                          | BSTBY from H to L and fixed                          |     | 5    | _   | ms   |

| Regeneration perio | bd                            | Tregene   | _                                              | After ISD, TSD and OSCM<br>pin anomaly               | -   | 5    | _   | ms   |

| MO pin output vol  | tage                          | VOL(MO)   | МО                                             | BSTBY=H, MO=L, RL=5.1k $\Omega$<br>and Pull-up to 5V | -   | 0.2  | 0.5 | v    |

| DIAG pin output v  | oltage                        | VOL(DIAG) | DIAG                                           | BSTBY=H, DIAG =L,<br>RL=5.1kΩ and Pull-up to 5V      | -   | 0.2  | 0.5 | v    |

| MD pin output vol  | tage                          | VOL(SD)   | SD                                             | BSTBY=H, SD=L, RL=5.1k $\Omega$<br>and Pull-up to 5V | -   | 0.2  | 0.5 | v    |

| IBAT1              |                               |           | Output: open and standby mode                  | -                                                    | 1   | 10   | μΑ  |      |

| Current consumpti  | irrent consumption IBAT2 VBAT |           | Output: open, standby<br>released and ENABLE=L | _                                                    | 3   | 9    | mA  |      |

|                    |                               | IBAT3     |                                                | Output: open, standby<br>released and ENABLE=H       | _   | 3    | 9   | mA   |

\* BSTBY signal input to the BSTBY pin and output pin OUTA+, OUTA-, OUTB+ and OUTB-

### **10.2** Electrical characteristics 2 (Unless otherwise specified, Ta=-40 to 125°C, VBAT=7 to 18V)

| Characteristics                              |           | Symbol   | Applicable<br>pin | Measurement conditions                   | Min | Тур. | Max | Unit |

|----------------------------------------------|-----------|----------|-------------------|------------------------------------------|-----|------|-----|------|

| MO pin output leakage<br>current             |           | IMO      | МО                | VOL(MO)=5V and Off                       |     | 1    | 3   | μΑ   |

| DIAG pin output leak<br>current              | age       | IDIAG    | DIAG              | VOL(DIAG)=5V and Off                     |     | 1    | 3   | μΑ   |

| SD pin output leakag                         | e current | I_SD     | SD                | VOL(SD)=5V and Off                       |     | 1    | 3   | μA   |

| Motor pin output                             | Upper     | IOHout   |                   | VBAT=18V and OUT A/B±=0V                 | Ι   | 1    | 10  | μA   |

| leakage current                              | Lower     | lOLout   |                   | VBAT= OUT A/B± =18V                      | _   | 1    | 10  | μA   |

| Error of motor outpu<br>between channels     | t current | ∆lout1   | OUTA+,            | Error of output current between channels | -10 | 0    | 10  | %    |

| Error of set current va<br>motor output      | alue for  | ∆lout2   | OUTA-,<br>OUTB+   | lout=0.5A or more<br>(TORQUE : 100%)     | -10 | 0    | 10  | %    |

| Dead time of motor of                        | output    | TDEAD    | and<br>OUTB-      | _                                        | 100 | 400  | 700 | ns   |

| Matar autout an rac                          | istanca   |          | 0010-             | Ta=25°C, VBAT=13.0V and lout=0.5A        |     | 0.8  | 1.8 | Ω    |

| Motor output on-resi<br>(Sum of upper and lo |           | Ron(H+L) |                   | Ta=125°C, VBAT=13.0V and lout=0.5A       | -   | 1.1  | 2.2 | Ω    |

| (Sum of upper and lo                         | wer)      |          |                   | Ta=25°C, VBAT=7.0V and lout=0.5A         | Ι   | 0.8  | 1.8 | Ω    |

## 10.3 Electrical characteristics 3 (Unless otherwise specified, Ta=-40 to 125°C, VBAT=7 to 18V)

| Characteristics        | Symbol   | Applicable<br>pin | Measurement conditions | Min  | Тур. | Max  | Unit |

|------------------------|----------|-------------------|------------------------|------|------|------|------|

| Vref input current     | Iref     | Vref              | Vref=2.0V              | I    | 0    | 1    | μA   |

| VccOUT pin voltage     | VccOUT   | VccOUT            | lccOUT=1mA             | 4.75 | 5.0  | 5.25 | V    |

| Vref attenuation ratio | Vrefgain | Vref              | Vref=2.0V              | 1/11 | 1/10 | 1/9  | —    |

## 10.4 AC electrical characteristics

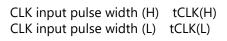

# Characteristics related to CLK (Unless otherwise specified, Ta=-40 to 125°C, VBAT=7 to 18V, ROSCM=100k $\Omega$ )

| Characteristics                     | Symbol       | Applicable<br>pin      | ivieasurement conditions in           |     | Тур. | Max | Unit |

|-------------------------------------|--------------|------------------------|---------------------------------------|-----|------|-----|------|

| CLK input pulse width (high)        | tCLK(H)      | CLK                    | CLK(H) pulse width                    | 2.5 | -    | —   | μs   |

| CLK input pulse width (low)         | tCLK(L)      | CLK                    | CLK(L) pulse width                    | 2.5 | _    | -   | μs   |

| DMODE set-up time                   | tDMODE(set)  | CLK and<br>DMODE       | —                                     |     | _    | _   | μs   |

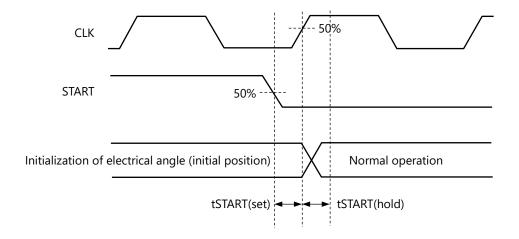

| START set-up time                   | tSTART(set)  | CLK and<br>START       | -                                     | 1   | _    | _   | μs   |

| START hold time                     | tSTART(hold) | CLK and<br>START       | _                                     | 1   | _    | -   | μs   |

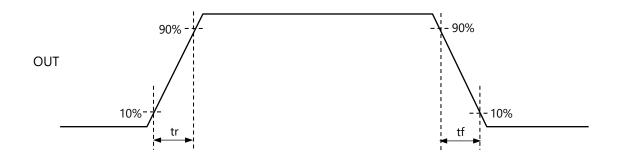

|                                     | tr           |                        | 27 Ω between output pins, and 10%-90% | 80  | 300  | 600 | ns   |

|                                     | tf           | OUTA+,                 | 27 Ω between output pins, and 10%-90% | 80  | 300  | 600 | ns   |

| Output transistor switching         | tpLH(CLK)    | OUTA-,<br>OUTB+<br>and | Between CLK and output<br>voltage     | 0.5 | 3    | 6   | μs   |

| characteristics                     | tpHL(CLK)    | OUTB-                  | Between CLK and output voltage        | 0.5 | 3    | 6   | μs   |

|                                     | tpHL(EN)     |                        | Between ENABLE and<br>output voltage  | 1   | 4    | 7   | μs   |

|                                     | tpLH(EN)     |                        | Between ENABLE and<br>output voltage  | 1   | 4    | 7   | μs   |

| Dead band time for noise<br>removal | tBLK         | RSGND                  | VBAT=12V and lout=0.5A                | 0.5 | 3    | 5   | μs   |

## AC characteristics timing chart

## • CLK signal input to the CLK pin

• CLK signal input to the CLK pin and signals input to the DMODE0, DMODE1 and DMODE2 pins

DMODE set-up time tDMODE(set)

e.g. When changing from half step resolution to 1/16 step resolution

## • CLK signal input to the CLK pin and signals input to the START pin

START set-up time tSTART(set) START hold time tSTART(hold)

(a) When START is changed from L to H

(b) When START is changed from H to L

• tr, tf of the output pins, OUTA+,OUTA-,OUTB+ and OUTB-

Timing charts may be simplified for explanatory purposes.

## • ENABLE signal input to the ENABLE pin, output pin OUTA+, OUTA-, OUTB+ and OUTB-

#### OSCM (Unless otherwise specified, Ta=-40 to 125°C, VBAT=7 to 18V)

| Characteristics                     | Symbol   | Applicable pin | Measurement conditions | Min  | Тур. | Max  | Unit |

|-------------------------------------|----------|----------------|------------------------|------|------|------|------|

| OSCM oscillation frequency accuracy | ⊿fOSCM B |                | BSTBY=H and            | -25  | Ι    | 25   | %    |

| OSCM oscillation frequency          | fOSCM    | OSCM           | ROSCM=100kΩ            | 1200 | 1600 | 2000 | kHz  |

#### fPWM (Unless otherwise specified, Ta=-40 to 125°C, VBAT=7 to 18V)

| Characteristics               | Symbol | Applicable pin | Measurement conditions                                | Min | Тур. | Max | Unit |

|-------------------------------|--------|----------------|-------------------------------------------------------|-----|------|-----|------|

| Chopping setting<br>frequency | fPWM   | OSCM           | BSTBY=H, ROSCM=100kΩ and<br>Output active (lout=0.5A) | _   | 50   | _   | kHz  |

### 10.5 Characteristics related to the safety function and electrical characteristics

#### Power supply monitoring (Unless otherwise specified, Ta=-40 to 125°C, VBAT=7 to 18V, OSCM=100kΩ)

| Characteristics                                   | Symbol       | Applicable<br>pin | Measurement conditions | Min  | Тур. | Max  | Unit |

|---------------------------------------------------|--------------|-------------------|------------------------|------|------|------|------|

| VBAT low-voltage detection voltage                | VBATRSTL     | VBAT              | _                      | 3.95 | 4.20 | 4.49 | V    |

| VBAT low-voltage<br>cancellation voltage          | VBATRSTH     | VBAT              | -                      | 4.45 | 4.70 | 5.10 | V    |

| VBAT low-voltage detection hysteresis width       | VBATRSTHY    | VBAT              | -                      | 0.1  | 0.5  | 1.0  | V    |

| VccOUT low-voltage POR detection voltage          | VccOUTRHL    | VccOUT            | Ι                      | 3.55 | 3.80 | 3.95 | V    |

| VccOUT low-voltage POR cancellation voltage       | VccOUTRHH    | VccOUT            | _                      | 3.75 | 4.00 | 4.15 | V    |

| VccOUT low-voltage POR detection hysteresis width | VccOUTRHLHYS | VccOUT            | _                      | 0.1  | 0.2  | 0.3  | V    |

#### Stall detection (Unless otherwise specified, Ta=-40 to 125°C, VBAT=7 to 18V, ROSCM=100kΩ)

| Characteristics                                             | Symbol    | Applicable<br>pin | Measurement<br>conditions | Min  | Тур. | Max | Unit |

|-------------------------------------------------------------|-----------|-------------------|---------------------------|------|------|-----|------|

| SDT pin external resistance                                 | RSDT      | SDT               | —                         | 0    | -    | 230 | kΩ   |

| SDT pin threshold setting voltage                           | VSDT      | SDT               | _                         | _    | 0.5  | 3.0 | V    |

| SDT pin current                                             | ISDT      | SDT               | VSDT=0V and 3V            | 7    | 10   | 13  | μΑ   |

| Error of difference between stall detection induced voltage | ΔVinduced | -                 | VSDT=3V                   | -0.4 | _    | 0.4 | V    |

| Stall detection delay                                       | Tstld_d   |                   | —                         | 10   | 20   | 40  | μs   |

| Stall alert period                                          | Tstld     | SD                | _                         | 67   | 100  | 200 | μs   |

| Stall alert response delay                                  | Tstld_SD  |                   | _                         | 0.5  | 3.5  | 6.5 | μs   |

\* The product of an SDT pin external resistance RSDT multiplied by an SDT pin current ISDT is an SDT pin threshold setting voltage VSDT, or

$VSDT(V) = RSDT(\Omega) \times ISDT(A)$

Load open detection (Unless otherwise specified, Ta=-40 to 125°C, VBAT=7 to 18V, ROSCM=100kΩ)

| Characteristics                    | Symbol | Applicable pin | Measurement conditions | Min | Тур. | Max | Unit |

|------------------------------------|--------|----------------|------------------------|-----|------|-----|------|

| Current detection period threshold | Tnfd   | _              | _                      | 30  | 50   | 100 | ms   |

| Load open DIAG period              | Topen  | DIAG           | —                      | 67  | 100  | 200 | μs   |

## Overcurrent detection (Unless otherwise specified, Ta=-40 to 125°C, VBAT=7 to 18V, ROSCM=100k $\Omega$ )

| Characteristics                                  | Symbol      | Applicable<br>pin   | Measurement conditions | Min | Тур | Ma<br>x | Uni<br>t |

|--------------------------------------------------|-------------|---------------------|------------------------|-----|-----|---------|----------|

| Upper side overcurrent threshold                 | lovc        | OUTA+,              | _                      | 1.5 | 2.0 | 2.5     | А        |

| Lower side overcurrent detection voltage         | Vovc        | OUTA-,<br>OUTB+ and | _                      | 450 | 600 | 750     | mV       |

| Detection filter time                            | Тоvс        | OUTB-               | _                      | 0.8 | 1.2 | 2.4     | μs       |

| Overcurrent detection DIAG output response delay | TpdOVC_DIAG | DIAG                | _                      | 1   | 3.5 | 6.5     | μs       |

## Over temperature detection (Unless otherwise specified, Ta=-40 to 125°C, VBAT=7 to 18V, ROSCM=100k $\Omega$ )

| Characteristics                                   | Symbol  | Applicable pin | Measurement conditions | Min | Тур. | Max | Unit |

|---------------------------------------------------|---------|----------------|------------------------|-----|------|-----|------|

| Over temperature detection shutdown temperature   | TSDtemp | _              | _                      | 155 | 175  | 195 | °C   |

| Over temperature detection hysteresis temperature | TSDhys  | _              | _                      | _   | 10   | -   | °C   |

| Recovery temperature                              | TSDL    | _              | _                      | 150 | 165  | 185 | °C   |

#### Notes:

The absolute maximum rating of the guaranteed storage temperature range of this product is 150°C (max.). Storage and use beyond this temperature cannot guarantee the normal operation of the IC afterwards, and it may also cause smoking and ignition. Please do not store or use it beyond this temperature in any case. Although this IC incorporates the following over temperature detection function, this function does not suppress the temperature of this IC below the over temperature detection shutdown temperature TSDtemp, and it is a function outside the guaranteed operation range. Please regard it as an auxiliary function. Regarding this function, although an actual temperature inspection is not conducted for each product at the time of shipment, circuit operation is checked as a substitute inspection.

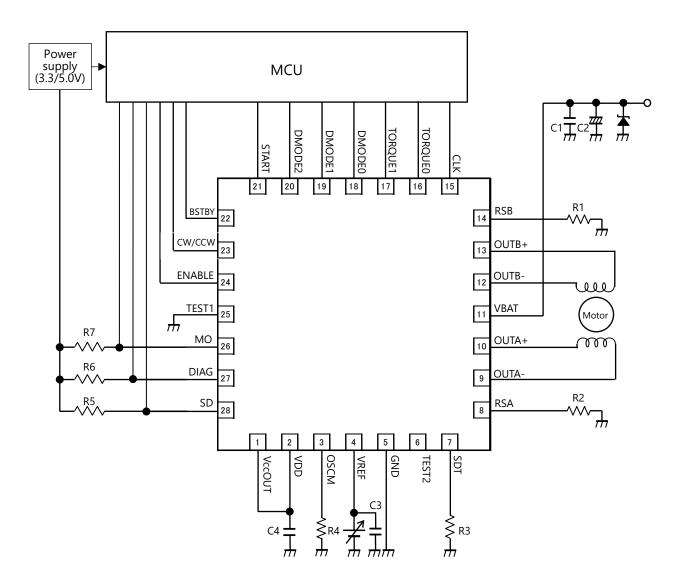

## 11 Example of Application Circuit

- The above is just one example of an application circuit, therefore, it can't be guaranteed as a design for a mass-produced product.

- GND wiring should be a GND plane and a point on the GND plane to connect to other areas outside the PCB should be a single point ground. Moreover, thermal performance should be paid attention to when a layout of circuit patterns is designed.

- VBAT lines, GND lines, and output lines should be designed with the utmost care because the IC may be destroyed if either the GND lines and outputs short-circuit, the power lines and outputs short-circuit or two of outputs short-circuit. If there is any wrong wiring, especially at pins for large currents such as VBAT, OUTA+/-, OUTB+/-, RSA, RSB and GND, the IC may malfunction and/or be destroyed.

- If there is any wrong wiring at input pins for logic signals, the IC may malfunction. Moreover, the malfunction may make over current pass over the specifications and finally the IC may be destroyed. With the utmost care, not only should circuit patterns around the IC on the PCB be designed, the IC should also be soldered.

- Please do not use VccOUT pin as pull-up power supply for input signal pins such as CLK, TORQUE0, TORQUE1, CW/CCW, DMODE0, DMODE1, DMODE2, START, ENABLE and BSTBY, as power supply for VREF, and as pull-up power supply for detection flag output signal pins such as MO, DIAG and SD although VccOUT pin outputs 5 voltage.

- An external resistor ROSCM should be placed between OSCM pin and GND to set PWM chopping frequency fPWM.

## **Reference value for parts**

| Symbol | Reference value                                                                   | Remarks                            |

|--------|-----------------------------------------------------------------------------------|------------------------------------|

| R1     | Resistor defined at Current value setting in 7.14<br>Constant current PWM control | -                                  |

| R2     | Resistor defined at Current value setting in 7.14<br>Constant current PWM control | -                                  |

| R3     | 0kΩ to 230kΩ                                                                      | -                                  |

| R4     | 60kΩ to 300kΩ                                                                     | Tolerance within 5% is recommended |

| R5     | 5.1kΩ                                                                             | -                                  |

| R6     | 5.1kΩ                                                                             | -                                  |

| R7     | 5.1kΩ                                                                             | -                                  |

| C1     | 0.1µF                                                                             | Multilayer ceramic capacitor       |

| C2     | 10μF to 100μF                                                                     | Electrolytic capacitor             |

| C3     | 0.1µF                                                                             | Multilayer ceramic capacitor       |

| C4     | 1000pF to 0.1µF                                                                   | Multilayer ceramic capacitor       |

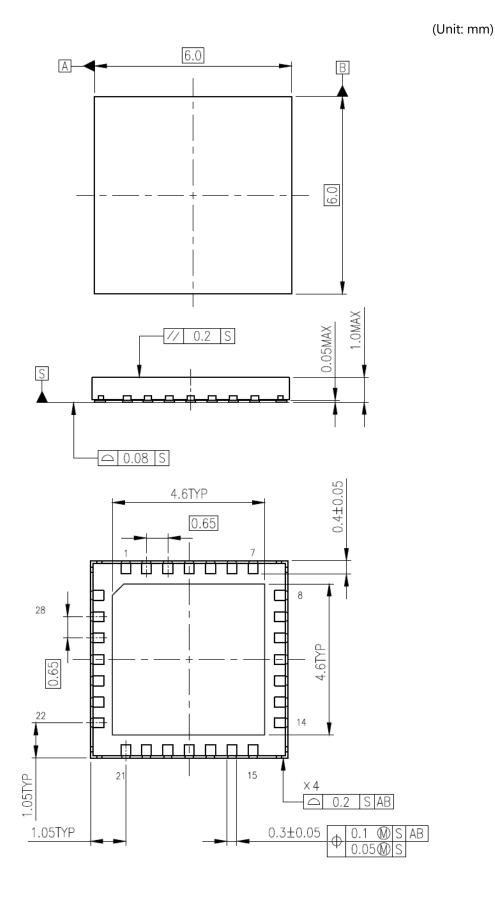

## 12. Package dimensions

## P-VQFN28-0606-0.65-002

## 13. Notes on Contents

## 1. Block Diagrams

Some of the functional blocks, circuits, or constants in the block diagram may be omitted or simplified for explanatory purposes.

## 2. Equivalent Circuits

The equivalent circuit diagrams may be simplified or some parts of them may be omitted for explanatory purposes.

### 3. Timing Charts

Timing charts may be simplified for explanatory purposes.

### 4. Application Circuits

The application circuits shown in this document are provided for reference purposes only. Thorough evaluation is required, especially at the mass production design stage. Toshiba does not grant any license to any industrial property rights by providing these examples of application circuits.

## 5. Test Circuits

Components in the test circuits are used only to obtain and confirm the device characteristics. These components and circuits are not guaranteed to prevent malfunction or failure from occurring in the application equipment.

## 14. IC Usage Considerations

## Notes on handling of ICs