# TDA7569BLV

## 4 x 50 W power amplifier with full I<sup>2</sup>C diagnostics, high efficiency and low voltage operation

## Features

- Multipower BCD technology

- MOSFET output power stage

- DMOS power output

- Class SB high efficiency

- High output power capability 4x28 W/4 Ω @ 14.4 V, 1 kHz, 10% THD, 4 x 45 W max power

- Max power 4 x 72 W / 2 Ω

- Full I<sup>2</sup>C bus driving:

- Standby

- Independent front/rear soft play/mute

- Selectable gain 26 dB /16 dB (for low noise line output function)

- High efficiency enable/disable

- I<sup>2</sup>C bus digital diagnostics (including DC bus AC load detection)

- Full fault protection

- DC offset detection

- Four independent short circuit protection

- Clipping detector pin with selectable threshold (2 %/10 %)

- Standby/mute pin

- Linear thermal shutdown with multiple thermal warning

- ESD protection

#### September 2014

#### DocID023498 Rev 9

This is information on a product in full production.

- Very robust against misconnections

- Improved SVR suppression during battery transients

- Capable to operate down to 6 V (e.g. "Startstop")

### Description

The TDA7569BLV is the most advanced BCD technology quad bridge car radio amplifier of his family, including a wide range of innovative features.

The TDA7569BLV is equipped with the most complete diagnostics array that communicates the status of each speaker through the  $I^2C$  bus.

The dissipated output power under average listening condition is significantly reduced when compared to the conventional class AB solutions, thanks to the patented solution. Moreover it has been designed to be very robust against several kinds of misconnections.

It is moreover compliant to the most recent OEM specifications for low voltage operation (so called 'start-stop' battery profile during engine stop and re-start), helping car manufacturers to reduce the overall emissions and thus contributing to environment protection.

#### Figure 1. Device summary

| Order code     | Package                     | Packing       |

|----------------|-----------------------------|---------------|

| TDA7569BLVSM   | Flexiwatt27                 | Tube          |

| TDA7569BLVSMTR | (SMD)                       | Tape and reel |

| TDA7569BLV     | Flexiwatt27<br>(vertical)   | Tube          |

| TDA7569BLVH    | Flexiwatt27<br>(horizontal) | Tube          |

| TDA7569BLVPD   | PowerSO36                   | Tube          |

| TDA7569BLVPDTR |                             |               |

## Contents

| 1 | Block               | diagram and application circuits6                 |

|---|---------------------|---------------------------------------------------|

| 2 | Pin de              | scription                                         |

| 3 | Electri             | cal specifications                                |

|   | 3.1 /               | Absolute maximum ratings 10                       |

|   | 3.2                 | Thermal data                                      |

|   | 3.3                 | Electrical characteristics                        |

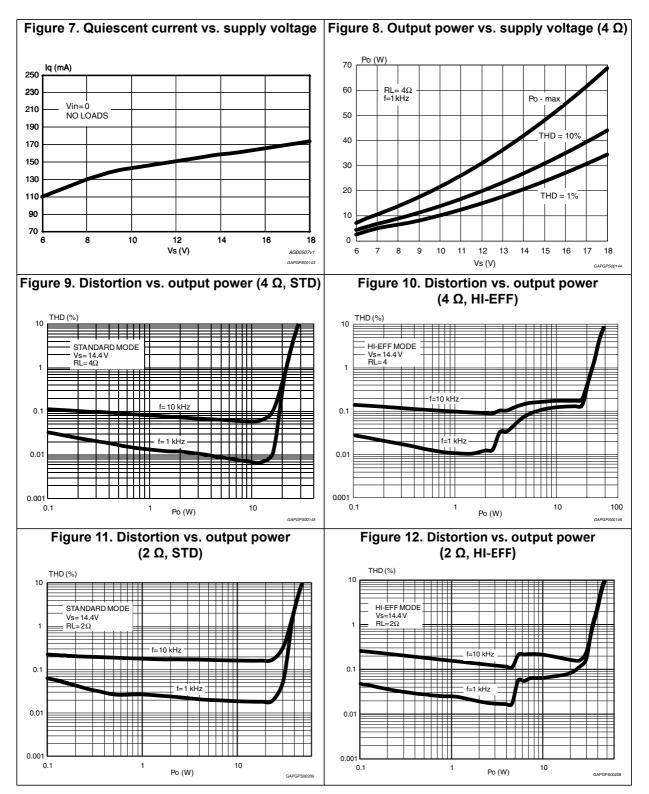

|   | 3.4                 | Electrical characteristics curves 14              |

| 4 | Diagno              | ostics functional description17                   |

|   | 4.1                 | Turn-on diagnostic                                |

|   | 4.2                 | Permanent diagnostics                             |

|   | 4.3                 | Output DC offset detection 20                     |

|   | 4.4                 | AC diagnostic                                     |

| 5 | Multip              | le faults                                         |

|   | 5.1                 | Faults availability                               |

| 6 | Therm               | al protection                                     |

|   | 6.1                 | Fast muting                                       |

| 7 | Battery             | y transitions management24                        |

|   | 7.1                 | Low voltage operation ("start stop") 24           |

|   | 7.2                 | Advanced battery management 25                    |

| 8 | Applic              | ation suggestion                                  |

|   | 8.1                 | Inputs impedance matching                         |

|   | 8.2                 | High efficiency introduction                      |

| 9 | l <sup>2</sup> C bu | s 28                                              |

|   | 9.1                 | <sup>12</sup> C programming/reading sequences     |

|   | 9.2                 | Address selection and I <sup>2</sup> C disable 28 |

|    | 9.3   | I <sup>2</sup> C bus | interface                 | 3 |

|----|-------|----------------------|---------------------------|---|

|    |       | 9.3.1                | Data validity             | 8 |

|    |       | 9.3.2                | Start and stop conditions | Э |

|    |       | 9.3.3                | Byte format               | Э |

|    |       | 9.3.4                | Acknowledge               | 9 |

| 10 | Softw | are spe              | cifications               | ) |

| 11 | Exam  | ples of I            | bytes sequence            | 5 |

| 12 | Packa | ige info             | rmation                   | 3 |

| 13 | Revis | ion hist             | ory                       | ) |

## List of tables

| Table 1.  | Pin list description                      |

|-----------|-------------------------------------------|

| Table 2.  | Absolute maximum ratings 10               |

| Table 3.  | Thermal data                              |

| Table 4.  | Electrical characteristics                |

| Table 5.  | Double fault table for turn-on diagnostic |

|           | IB1                                       |

|           | IB2                                       |

|           | DB1                                       |

| Table 9.  | DB2                                       |

| Table 10. | DB3                                       |

| Table 11. | DB4                                       |

| Table 12. | Document revision history                 |

# List of figures

| Figure 1.  | Device summary                                                                      | . 1  |

|------------|-------------------------------------------------------------------------------------|------|

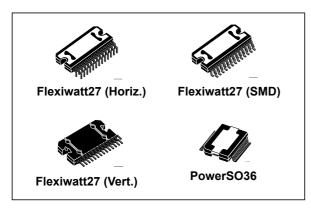

| Figure 2.  | Block diagram                                                                       |      |

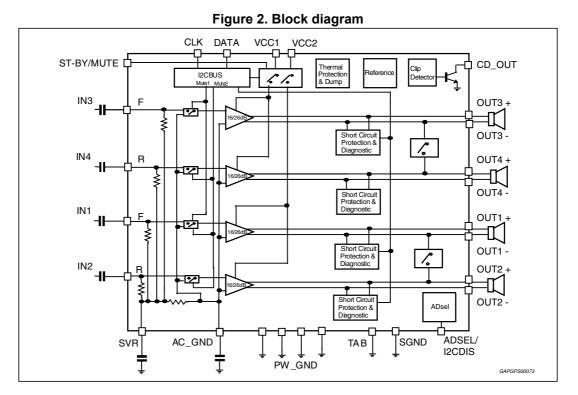

| Figure 3.  | Application circuit                                                                 | . 6  |

| Figure 4.  | Application circuit (TDA7569BLVPD)                                                  | . 7  |

| Figure 5.  | Pin connection diagram of the Flexiwatt27 (top of view)                             | . 8  |

| Figure 6.  | Pin connection diagram of the PowerSO36 slug up (top of view)                       | . 8  |

| Figure 7.  | Quiescent current vs. supply voltage                                                |      |

| Figure 8.  | Output power vs. supply voltage $(4 \Omega)$                                        | . 14 |

| Figure 9.  | Distortion vs. output power (4 Ω, STD).                                             |      |

| Figure 10. | Distortion vs. output power (4 Ω, HI-EFF).                                          |      |

| Figure 11. | Distortion vs. output power (2 Ω, STD).                                             |      |

| Figure 12. | Distortion vs. output power (2 Ω, HI-EFF).                                          |      |

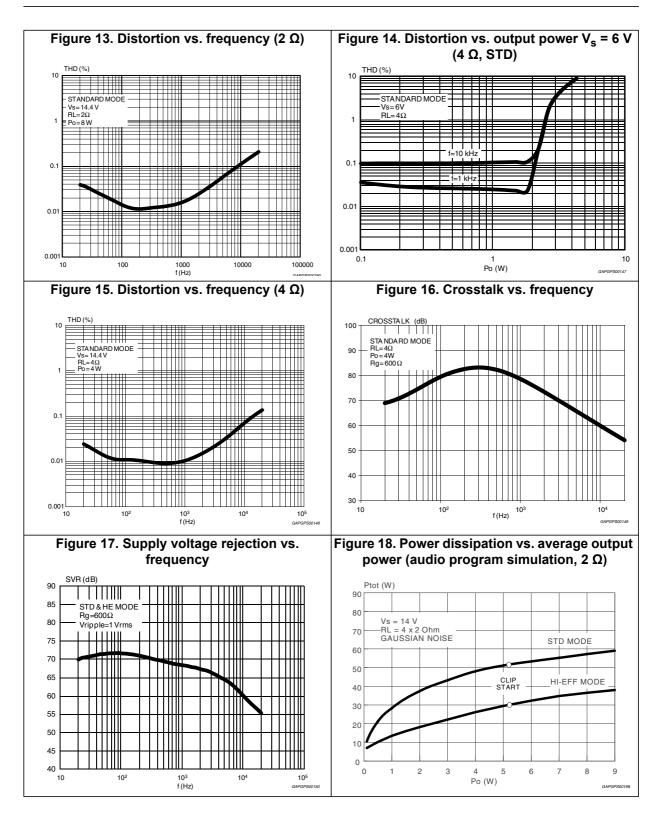

| Figure 13. | Distortion vs. frequency $(2 \Omega)$                                               |      |

| Figure 14. | Distortion vs. output power $V_s = 6 V (4 \Omega, STD)$ .                           |      |

| Figure 15. | Distortion vs. frequency $(4 \Omega)$ .                                             |      |

| Figure 16. | Crosstalk vs. frequency.                                                            |      |

| Figure 17. | Supply voltage rejection vs. frequency                                              |      |

| Figure 18. | Power dissipation vs. average output power (audio program simulation, 2 $\Omega$ )  |      |

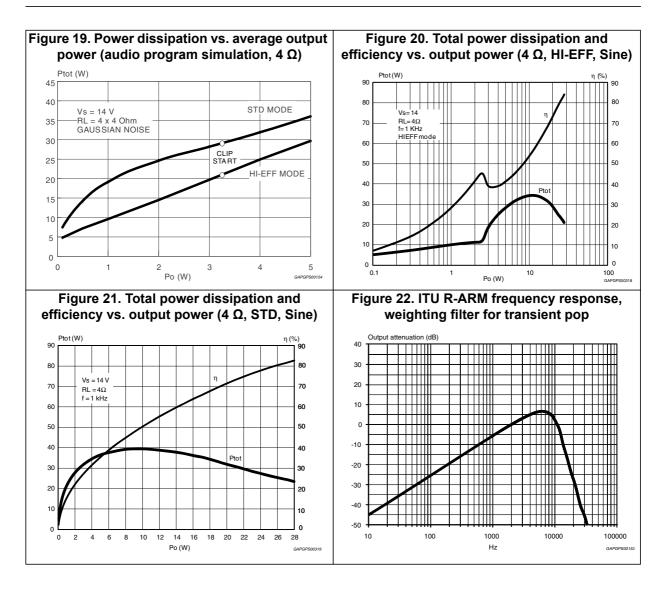

| Figure 19. | Power dissipation vs. average output power (audio program simulation, 4 $\Omega$ )  |      |

| Figure 20. | Total power dissipation and efficiency vs. output power (4 $\Omega$ , HI-EFF, Sine) |      |

| Figure 21. | Total power dissipation and efficiency vs. output power (4 Ω, STD, Sine)            |      |

| Figure 22. | ITU R-ARM frequency response, weighting filter for transient pop.                   |      |

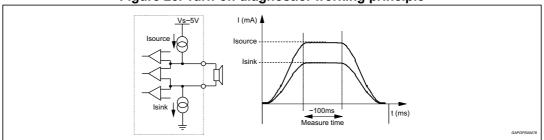

| Figure 23. | Turn-on diagnostic: working principle                                               |      |

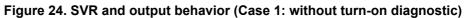

| Figure 24. | SVR and output behavior (Case 1: without turn-on diagnostic)                        |      |

| Figure 25. | SVR and output pin behavior (Case 2: with turn-on diagnostic)                       |      |

| Figure 26. | Short circuit detection thresholds                                                  |      |

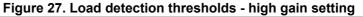

| Figure 27. | Load detection thresholds - high gain setting                                       |      |

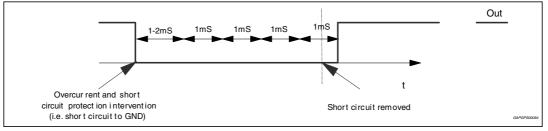

| Figure 28. | Load detection threshold - low gain setting.                                        |      |

| Figure 29. | Restart timing without diagnostic enable (permanent) - Each 1 mS time,              |      |

| 0          | a sampling of the fault is done                                                     | 19   |

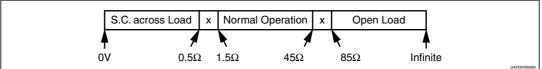

| Figure 30. | Restart timing with diagnostic enable (permanent).                                  |      |

| Figure 31. | Current detection high: load impedance  Z  vs. output peak voltage                  |      |

| Figure 32. | Current detection low: load impedance  Z  vs. output peak voltage                   |      |

| Figure 33. | Thermal foldback diagram                                                            |      |

| Figure 34. | Worst case battery cranking curve sample 1                                          |      |

| Figure 35. | Worst case battery cranking curve sample 2                                          |      |

| Figure 36. | Upwards fast battery transitions diagram                                            |      |

| Figure 37. | Inputs impedance matching circuit                                                   | 26   |

| Figure 38. | High efficiency - basic structure                                                   | 27   |

| Figure 39. | Data validity on the I <sup>2</sup> C bus                                           | 29   |

| Figure 40. | Timing diagram on the I <sup>2</sup> C bus                                          | 29   |

| Figure 41. | Acknowledge on the I <sup>2</sup> C bus.                                            | 29   |

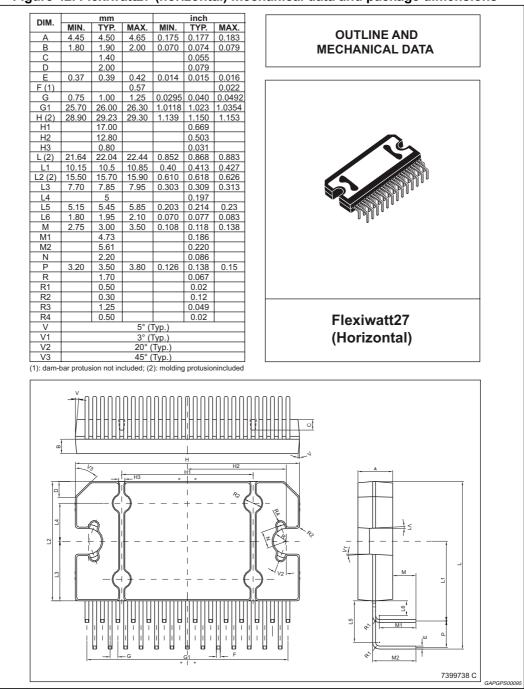

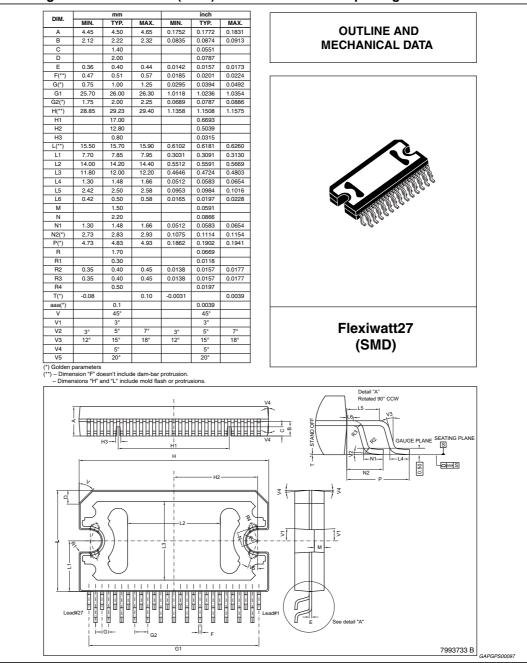

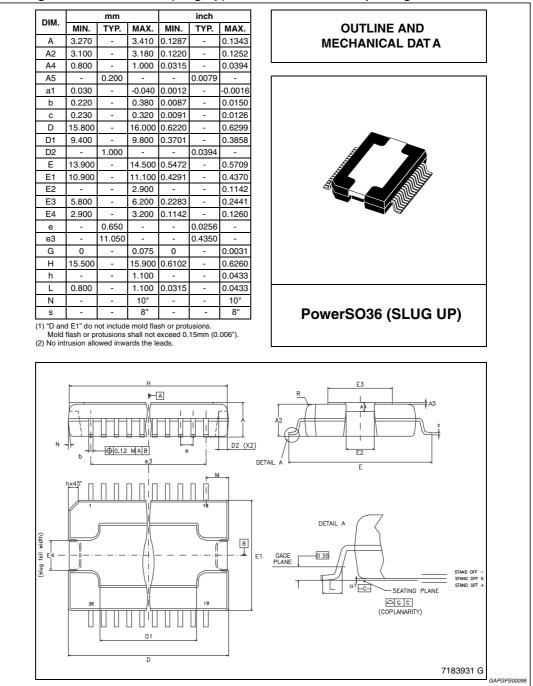

| Figure 42. | Flexiwatt27 (horizontal) mechanical data and package dimensions                     |      |

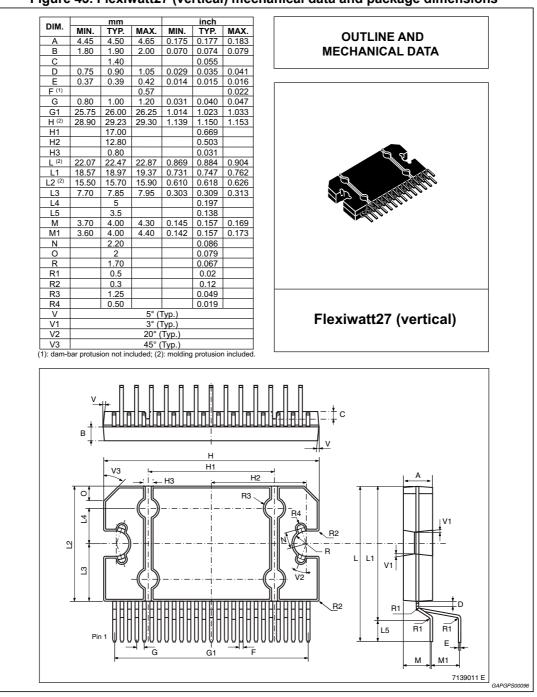

| Figure 43. | Flexiwatt27 (vertical) mechanical data and package dimensions                       |      |

| Figure 44. | Flexiwatt27 (SMD) mechanical data and package dimensions                            |      |

| Figure 45. | PowerSO36 (slug up) mechanical data and package dimensions                          | 39   |

## **1** Block diagram and application circuits

#### Figure 3. Application circuit

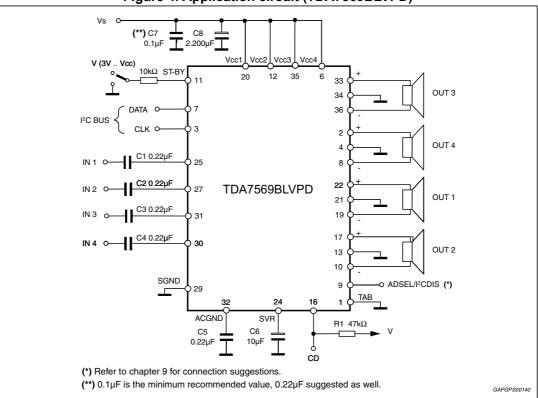

Figure 4. Application circuit (TDA7569BLVPD)

## 2 Pin description

For channel name reference: CH1 = LF, CH2 = LR, CH3 = RF and CH4 = RR.

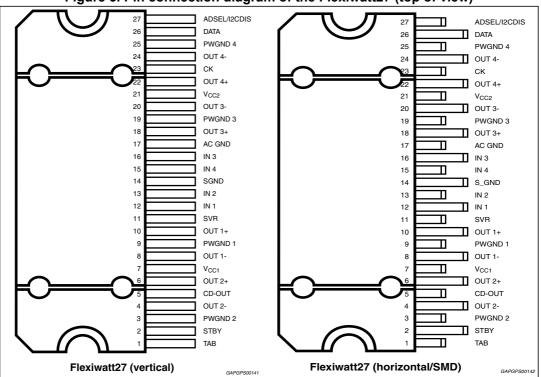

Figure 5. Pin connection diagram of the Flexiwatt27 (top of view)

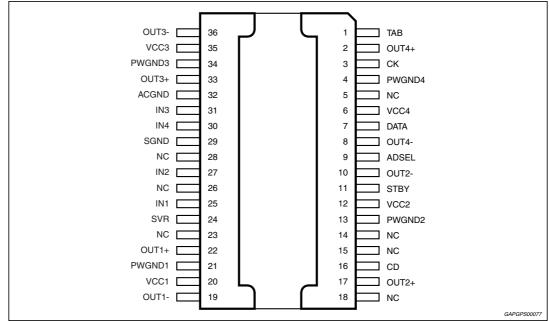

Figure 6. Pin connection diagram of the PowerSO36 slug up (top of view)

Table 1. Pin list description

| Pin #<br>(PowerSo36) | Pin #<br>(Flexiwatt27) | Pin name | Function                                                           |

|----------------------|------------------------|----------|--------------------------------------------------------------------|

| 1                    | 1                      | TAB      | -                                                                  |

| 2                    | 22                     | OUT4+    | Channel 4, + output                                                |

| 3                    | 23                     | СК       | I <sup>2</sup> C bus clock/HE selector                             |

| 4                    | 25                     | PWGND4   | Channel 4 output power ground                                      |

| 5                    | -                      | NC       | Not connected                                                      |

| 6                    | -                      | VCC4     | Supply voltage pin4                                                |

| 7                    | 26                     | DATA     | I <sup>2</sup> C bus data pin/gain selector                        |

| 8                    | 24                     | OUT4-    | Channel 4, - output                                                |

| 9                    | 27                     | ADSEL    | Address selector pin/ I <sup>2</sup> C bus disable (legacy select) |

| 10                   | 4                      | OUT2-    | Channel 2, - output                                                |

| 11                   | 2                      | STBY     | Standby pin                                                        |

| 12                   | 21                     | VCC2     | Supply voltage pin2                                                |

| 13                   | 3                      | PWGND2   | Channel 2 output power ground                                      |

| 14                   | -                      | NC       | Not connected                                                      |

| 15                   | -                      | NC       | Not connected                                                      |

| 16                   | 5                      | CD       | Clip detector output pin                                           |

| 17                   | 6                      | OUT2+    | Channel 2, + output                                                |

| 18                   | -                      | NC       | Not connected                                                      |

| 19                   | 8                      | OUT1-    | Channel 1, - output                                                |

| 20                   | 7                      | VCC1     | Supply voltage pin1                                                |

| 21                   | 9                      | PWGND1   | Channel 1 output power ground                                      |

| 22                   | 10                     | OUT1+    | Channel 1, + output                                                |

| 23                   | -                      | NC       | Not connected                                                      |

| 24                   | 11                     | SVR      | SVR pin                                                            |

| 25                   | 12                     | IN1      | Input pin, channel 1                                               |

| 26                   | -                      | NC       | Not connected                                                      |

| 27                   | 13                     | IN2      | Input pin, channel 2                                               |

| 28                   | -                      | NC       | Not connected                                                      |

| 29                   | 14                     | SGND     | Signal ground pin                                                  |

| 30                   | 15                     | IN4      | Input pin, channel 4                                               |

| 31                   | 16                     | IN3      | Input pin, channel 3                                               |

| 32                   | 17                     | AC GND   | AC ground                                                          |

| 33                   | 18                     | OUT3+    | Channel 3, + output                                                |

| 34                   | 19                     | PWGND3   | Channel 3 output power ground                                      |

| 35                   | -                      | VCC3     | Supply voltage pin3                                                |

| 36                   | 20                     | OUT3-    | Channel 3, - output                                                |

## 3 Electrical specifications

### 3.1 Absolute maximum ratings

#### Table 2. Absolute maximum ratings

| Symbol                             | Parameter                                                     | Value                   | Unit |

|------------------------------------|---------------------------------------------------------------|-------------------------|------|

| V <sub>op</sub>                    | Operating supply voltage <sup>(1)</sup>                       | 18                      | V    |

| V <sub>S</sub>                     | DC supply voltage                                             | 28                      | V    |

| V <sub>peak</sub>                  | Peak supply voltage (for t <sub>max</sub> = 50 ms)            | 50                      | V    |

| GNDmax                             | Ground pins voltage                                           | -0.3 to 0.3             | V    |

| V <sub>CK,</sub> V <sub>DATA</sub> | CK and DATA pin voltage                                       | -0.3 to 6               | V    |

| $V_{cd}$                           | Clip detector voltage                                         | -0.3 to V <sub>op</sub> | V    |

| V <sub>stby</sub>                  | STBY pin voltage                                              | -0.3 to V <sub>op</sub> | V    |

| 1                                  | Output peak current (not repetitive t <sub>max</sub> = 100ms) | 8                       | Α    |

| Ι <sub>Ο</sub>                     | Output peak current (repetitive f > 10 kHz)                   | 6                       |      |

| P <sub>tot</sub>                   | Power dissipation $T_{case} = 70^{\circ}C^{(2)}$              | 85                      | W    |

| T <sub>stg</sub> , T <sub>j</sub>  | Storage and junction temperature <sup>(3)</sup>               | -55 to 150              | °C   |

| T <sub>amb</sub>                   | Operative temperature range                                   | -40 to 105              | °C   |

1. For  $R_L = 2 \Omega$  the output current limit is reached for  $V_{OP} > 16 V$ ; at this supply level internal protections might be triggered.

2. This is maximum theoretical value; for power dissipation in real application conditions, please refer to curves reported in *Section 3.4: Electrical characteristics curves*.

3. A suitable dissipation system should be used to keep Tj inside the specified limits.

## 3.2 Thermal data

| Table | 3. | Thermal | data |

|-------|----|---------|------|

|-------|----|---------|------|

| Symbo                 | Symbol Parameter                        |   | Flexiwatt | Unit |

|-----------------------|-----------------------------------------|---|-----------|------|

| R <sub>th j-cas</sub> | Thermal resistance junction-to-case Max | 1 | 1         | °C/W |

## 3.3 Electrical characteristics

Refer to the test circuit,  $V_S = 14.4 \text{ V}$ ;  $R_L = 4 \Omega$ ; f = 1 kHz;  $G_V = 26 \text{ dB}$ ;  $T_{amb} = 25 \text{ °C}$ ; unless otherwise specified.

Tested at  $T_{amb}$  = 25 °C and  $T_{hot}$  = 105 °C; functionality guaranteed for  $T_j$  = -40 °C to 150 °C.

| Symbol    | Parameter               | Test condition         | Min. | Тур. | Max.              | Unit |

|-----------|-------------------------|------------------------|------|------|-------------------|------|

| General c | General characteristics |                        |      |      |                   |      |

| Vs        |                         | R <sub>L</sub> = 4 ohm | 6    | -    | 18                | V    |

| VS        | Supply voltage range    | R <sub>L</sub> = 2 ohm | 6    | -    | 16 <sup>(1)</sup> | v    |

| Symbol              | Parameter                                     | Test condition                                                                 | Min. | Тур.  | Max. | Unit |

|---------------------|-----------------------------------------------|--------------------------------------------------------------------------------|------|-------|------|------|

| I <sub>d</sub>      | Total quiescent drain current                 | -                                                                              | -    | 165   | 250  | mA   |

| R <sub>IN</sub>     | Input impedance                               | -                                                                              | 45   | 60    | 70   | kΩ   |

| V <sub>AM</sub>     | Min. supply mute threshold                    | IB1(D7) = 1;<br>Signal attenuation -6 dB                                       | 7    | -     | 8    | - V  |

| * AM                |                                               | IB1(D7) = 0 (default); <sup>(2)</sup><br>Signal attenuation -6 dB              | 5    | -     | 5.8  |      |

| V <sub>OS</sub>     | Offset voltage                                | Mute & play                                                                    | -80  | -     | 80   | mV   |

| V <sub>dth</sub>    | Dump threshold                                | -                                                                              | 18.5 | 19.5  | 20.5 | V    |

| I <sub>SB</sub>     | Standby current                               | V <sub>standby</sub> = 0                                                       | -    | 1     | 5    | μA   |

| SVR                 | Supply voltage rejection                      | f = 100 Hz to 10 kHz; V <sub>r</sub> = 1 Vpk;<br>R <sub>g</sub> = 600 Ω        | 60   | 70    | -    | dB   |

| T <sub>ON</sub>     | Turn on timing (Mute play transition)         | D2/D1 (IB1) 0 to 1                                                             | -    | 25    | 50   | ms   |

| T <sub>OFF</sub>    | Turn off timing (Play mute transition)        | D2/D1 (IB1) 1 to 0                                                             | -    | 25    | 50   | ms   |

| TH <sub>WARN1</sub> | Average junction temperature for TH warning 1 | DB1 (D7) = 1                                                                   | -    | 160   | -    |      |

| TH <sub>WARN2</sub> | Average junction temperature for TH warning 2 | DB4 (D7) = 1                                                                   | -    | 145   | -    | °C   |

| TH <sub>WARN3</sub> | Average junction temperature for TH warning 3 | DB4 (D6) = 1                                                                   | -    | 125   | -    |      |

| Audio per           | formances                                     |                                                                                |      |       |      |      |

|                     |                                               | Max. power <sup>(3)</sup> V <sub>s</sub> = 14.4 V, R <sub>L</sub> = 4 $\Omega$ | -    | 45    | -    | W    |

|                     |                                               | THD = 10 %, $R_1$ = 4 Ω                                                        | 25   | 28    |      | W    |

|                     |                                               | THD = 1 %, $R_L = 4 \Omega$                                                    | 20   | 22    | -    | W    |

| PO                  | Output power                                  | R <sub>L</sub> = 2 Ω; THD 10 %                                                 | 40   | 50    |      | W    |

|                     |                                               | $R_L = 2 \Omega; THD 1 \%$                                                     | 32   | 40    | -    | W    |

|                     |                                               | $R_L$ = 2 Ω; Max. power <sup>(3)</sup> V <sub>s</sub> = 14.4 V                 | 60   | 75    |      | W    |

|                     |                                               | Max power@ V <sub>s</sub> = 6 V, R <sub>L</sub> = 4 $\Omega$                   | -    | 6     | -    | W    |

|                     |                                               | $P_0 = 1$ W to 10 W; STD mode                                                  | -    | 0.015 | 0.1  | %    |

|                     |                                               | HE MODE; P <sub>O</sub> = 1.5 W                                                |      | 0.05  | 0.1  | %    |

|                     |                                               | HE MODE; P <sub>O</sub> = 8 W                                                  |      | 0.1   | 0.5  | %    |

| THD                 | Total harmonic distortion                     | P <sub>O</sub> = 1-10 W, f = 10 kHz;<br>STD mode                               | -    | 0.15  | 0.5  | %    |

|                     |                                               | G <sub>V</sub> = 16 dB; STD mode<br>V <sub>O</sub> = 0.1 to 5 VRMS             | -    | 0.02  | 0.05 | %    |

| CT                  | Cross talk                                    | f = 1 kHz to 10 kHz, $R_g$ = 600 $\Omega$                                      | 50   | 65    | -    | dB   |

| G <sub>V1</sub>     | Voltage gain 1                                | -                                                                              | 25   | 26    | 27   | dB   |

| $\Delta G_{V1}$     | Voltage gain match 1                          | -                                                                              | -1   | -     | 1    | dB   |

| G <sub>V2</sub>     | Voltage gain 2                                | -                                                                              | 15   | 16    | 17   | dB   |

| $\Delta G_{V2}$     | Voltage gain match 2                          | -                                                                              | -1   | -     | 1    | dB   |

| E <sub>IN1</sub>    | Output noise voltage 1                        | R <sub>g</sub> = 600 Ω 20 Hz to 22 kHz                                         | -    | 45    | 60   | μV   |

| E <sub>IN2</sub>    | Output noise voltage 2                        | R <sub>g</sub> = 600 Ω; GV = 16d B<br>20 Hz to 22 kHz                          | -    | 20    | 30   | μV   |

| Table 4. Electrical characteristics | (continued) | ) |

|-------------------------------------|-------------|---|

|                                     | Commuca     | , |

| Symbol             | Parameter                                                                                          | Test condition                                                                                                        | Min.    | Тур. | Max.    | Unit |

|--------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------|------|---------|------|

| BW                 | Power bandwidth                                                                                    | -                                                                                                                     | 100     | -    | -       | kHz  |

| CMRR               | Input CMRR                                                                                         | $V_{cm}$ = 1 Vpk-pk, R <sub>g</sub> = 0 Ω                                                                             | -       | 70   | -       | dB   |

|                    |                                                                                                    | Standby to Mute and<br>Mute to Standby transition<br>$T_{amb} = 25 \ ^{\circ}C$ ,<br>ITU-R 2K, $C_{svr} = 10 \ \mu F$ | -7.5    | -    | +7.5    | mV   |

| ΔV <sub>OITU</sub> | ITU Pop filter output voltage                                                                      | $V_s$ = 14.4 V<br><b>Mute to Play transition</b><br>$T_{amb}$ = 25 °C,<br>ITU-R 2K, $V_s$ = 14.4 V <sup>(4)</sup>     | -7.5    | -    | +7.5    | mV   |

|                    |                                                                                                    | Play to Mute transition<br>$T_{amb}$ = 25 °C,<br>ITU-R 2K, V <sub>s</sub> = 14.4 V <sup>(5)</sup>                     | -7.5    | -    | +7.5    | mV   |

| Clip detec         | tor                                                                                                |                                                                                                                       |         |      |         |      |

| CD <sub>LK</sub>   | Clip det. high leakage current                                                                     | CD off / V <sub>CD</sub> = 6 V                                                                                        | -       | 0    | 5       | μA   |

| CD <sub>SAT</sub>  | Clip det sat. voltage                                                                              | CD on; I <sub>CD</sub> = 1 mA                                                                                         | -       | -    | 300     | mV   |

|                    |                                                                                                    | D0 (IB1) = 1                                                                                                          | 5       | 10   | 15      | %    |

| CD <sub>THD</sub>  | Clip det THD level                                                                                 | D0 (IB1) = 0                                                                                                          | 1       | 2    | 3       | %    |

| Control pi         | in characteristics                                                                                 | I                                                                                                                     |         |      |         |      |

| V <sub>SBY</sub>   | Standby/mute pin for standby                                                                       | -                                                                                                                     | 0       | -    | 1.2     | V    |

| V <sub>MU</sub>    | Standby/mute pin for mute                                                                          | -                                                                                                                     | 2.9     | -    | 3.5     | V    |

| V <sub>OP</sub>    | Standby/mute pin for operating                                                                     | -                                                                                                                     | 4.5     | -    | 18      | V    |

|                    |                                                                                                    | V <sub>st-by/mute</sub> = 4.5 V                                                                                       | -       | 1    | 5       | μA   |

| I <sub>MU</sub>    | Standby/mute pin current                                                                           | V <sub>st-by/mute</sub> < 1.2 V                                                                                       | -       | 0    | 5       | μA   |

| A <sub>SB</sub>    | Standby attenuation                                                                                | -                                                                                                                     | 90      | 110  | -       | dB   |

| A <sub>M</sub>     | Mute attenuation                                                                                   | -                                                                                                                     | 80      | 100  | -       | dB   |

| Turn on d          | iagnostics 1 (Power amplifier mo                                                                   | de)                                                                                                                   |         |      | 11      |      |

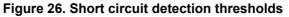

| Pgnd               | Short to GND det. (below this<br>limit, the Output is considered in<br>short circuit to GND)       | Dower emplifier in standby                                                                                            | -       | -    | 1.2     | V    |

| Pvs                | Short to Vs det. (above this limit,<br>the output is considered in short<br>circuit to Vs)         | Power amplifier in standby                                                                                            | Vs -1.2 | -    | -       | V    |

| Pnop               | Normal operation thresholds.<br>(Within these limits, the output is<br>considered without faults). |                                                                                                                       | 1.8     | -    | Vs -1.8 | V    |

| Lsc                | Shorted load det.                                                                                  | Power amplifier in standby                                                                                            | -       | -    | 0.5     | Ω    |

| Lop                | Open load det.                                                                                     |                                                                                                                       | 85      | -    | -       | Ω    |

| Lnop               | Normal load det.                                                                                   |                                                                                                                       | 1.5     | -    | 45      | Ω    |

| Turn on d          | iagnostics 2 (Line driver mode)                                                                    |                                                                                                                       |         |      |         |      |

| Pgnd               | Short to GND det. (below this limit, the output is considered in short circuit to GND)             | Power amplifier in standby                                                                                            | -       | -    | 1.2     | V    |

| Table 4. Electrical characteristics | (continued) |

|-------------------------------------|-------------|

|-------------------------------------|-------------|

| Symbol                  | Parameter                                                                                          | Test condition                                                                         | Min.    | Тур. | Max.    | Unit |

|-------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------|------|---------|------|

| Pvs                     | Short to Vs det. (above this limit,<br>the output is considered in short<br>circuit to Vs)         | -                                                                                      | Vs -1.2 | -    | -       | V    |

| Pnop                    | Normal operation thresholds.<br>(Within these limits, the output is<br>considered without faults). | -                                                                                      | 1.8     | -    | Vs -1.8 | V    |

| Lsc                     | Shorted load det.                                                                                  | -                                                                                      | -       | -    | 1.5     | Ω    |

| Lop                     | Open load det.                                                                                     | -                                                                                      | 330     | -    | -       | Ω    |

| Lnop                    | Normal load det.                                                                                   | -                                                                                      | 7       | -    | 180     | Ω    |

| Permaner                | nt diagnostics 2 (Power amplifier                                                                  | mode or line driver mode)                                                              |         |      |         |      |

| Pgnd                    | Short to GND det. (below this<br>limit, the Output is considered in<br>short circuit to GND)       |                                                                                        | -       | -    | 1.2     | V    |

| Pvs                     | Short to Vs det. (above this limit,<br>the output is considered in short<br>circuit to Vs)         | Power amplifier in mute or play,<br>one or more short circuits<br>protection activated | Vs -1.2 | -    | -       | V    |

| Pnop                    | Normal operation thresholds.<br>(Within these limits, the output is<br>considered without faults). |                                                                                        | 1.8     | -    | Vs -1.8 | V    |

| 1                       | Shorted load det.                                                                                  | Power amplifier mode                                                                   | -       | -    | 0.5     | Ω    |

| L <sub>SC</sub>         | Shorted load det.                                                                                  | Line driver mode                                                                       | -       | -    | 1.5     | Ω    |

| Vo                      | Offset detection                                                                                   | Power amplifier in play,<br>AC input signals = 0                                       | ±1.5    | ±2   | ±2.5    | V    |

| I <sub>NLH</sub>        | Normal load current detection                                                                      | $V_{1} = (V_{1} = 0)$                                                                  | 500     | -    | -       | mA   |

| I <sub>OLH</sub>        | Open load current detection                                                                        | V <sub>O</sub> < (V <sub>S</sub> -5)pk, IB2 (D7) = 0                                   | -       | -    | 250     | mA   |

| I <sub>NLL</sub>        | Normal load current detection                                                                      | V <sub>O</sub> < (V <sub>S</sub> -5)pk, IB2 (D7) = 1                                   | 250     | -    | -       | mA   |

| I <sub>OLL</sub>        | Open load current detection                                                                        | $V_0 < (V_S - 3) p K, IBZ (D7) = 1$                                                    | -       | -    | 125     | mA   |

| I <sup>2</sup> C bus in | terface                                                                                            |                                                                                        |         |      |         |      |

| S <sub>CL</sub>         | Clock frequency                                                                                    | -                                                                                      | -       | -    | 400     | kHz  |

| V <sub>IL</sub>         | Input low voltage                                                                                  | -                                                                                      | -       | -    | 1.5     | V    |

| V <sub>IH</sub>         | Input high voltage                                                                                 | -                                                                                      | 2.3     | -    | -       | V    |

Table 4. Electrical characteristics (continued)

1. When V<sub>S</sub> > 16 V the output current limit is reached (triggering embedded internal protections).

2. In legacy mode only low threshold option is available.

3. Saturated square wave output.

Voltage ramp on STBY pin: from 3.3 V to 4.2 V in t ≥ 40 ms. In case of I<sup>2</sup>C mode command IB1(D1) = 1 (Mute → Unmute rear channels) and/or IB1(D2) = 1 (Mute → Unmute front channels) must be transmitted before to start the voltage ramp on STBY pin.

Voltage ramp on STBY pin: from 4.05 V to 3.55 V in t ≥ 40 ms. In case of I<sup>2</sup>C mode command IB1(D1) = 0 Unmute → Mute rear channels) and/or IB1(D2) = 0 (Unmute → Mute front channels) must be NOT transmitted before to start the voltage ramp on STBY pin.

## 3.4 Electrical characteristics curves

## 4 Diagnostics functional description

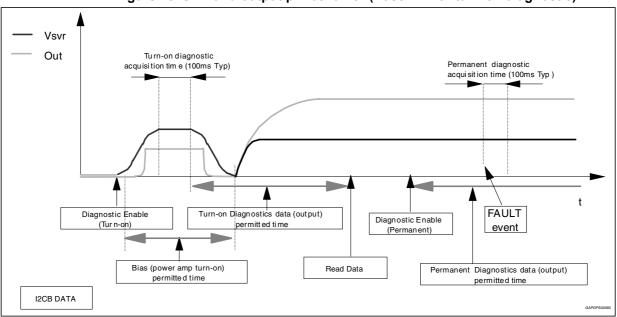

### 4.1 Turn-on diagnostic

It is strongly recommended to activate this function at turn on (standby out) through I<sup>2</sup>C bus request. Detectable output faults are:

- SHORT TO GND

- SHORT TO Vs

- SHORT ACROSS THE SPEAKER

- OPEN SPEAKER

To verify if any of the above misconnections are in place, a subsonic (inaudible) current pulse (*Figure 23*) is internally generated, sent through the speaker(s) and sunk back. The Turn On diagnostic status is internally stored until a successive diagnostic pulse is requested (after a  $I^2C$  reading).

If the "standby out" and "diag. enable" commands are both given through a single programming step, the pulse takes place first (during the pulse the power stage stays 'off', showing high impedance at the outputs).

Afterwards, when the Amplifier is biased, the PERMANENT diagnostic takes place. The previous Turn On state is kept until a short appears at the outputs.

Figure 23. Turn-on diagnostic: working principle

*Figure 24* and *25* show SVR and OUTPUT waveforms at the turn-on (stand-by out) with and without turn-on diagnostic.

Figure 25. SVR and output pin behavior (Case 2: with turn-on diagnostic)

The information related to the outputs status is read and memorized at the end of the current pulse plateau. The acquisition time is 100 ms (typ.). No audible noise is generated in the process. As for SHORT TO GND / Vs the fault-detection thresholds remain unchanged from 26 dB to 16 dB gain setting. They are as follows:

Concerning SHORT ACROSS THE SPEAKER / OPEN SPEAKER, the threshold varies from 26 dB to 16 dB gain setting, since different loads are expected (either normal speaker's impedance or high impedance). The values in case of 26 dB gain are as follows:

If the Line-Driver mode (Gv= 16 dB and Line Driver Mode diagnostic = 1) is selected, the same thresholds will change as follows:

Figure 28. Load detection threshold - low gain setting

|   | S.C. across Load | х | Normal Operation | x | Open Load |          |

|---|------------------|---|------------------|---|-----------|----------|

|   | 4                |   | ,                |   | k         | <b>A</b> |

| ( | Ω 1.5Ω           | 2 | 7Ω 180           | Ω | 330Ω i    | nfinite  |

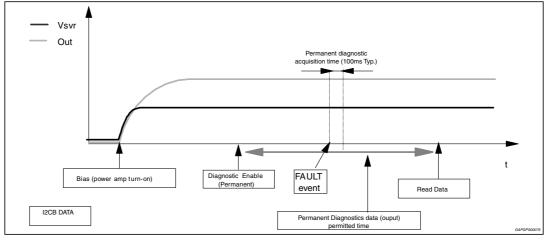

### 4.2 **Permanent diagnostics**

Detectable conventional faults are:

- Short to GND

- Short to Vs

- Short across the speaker

The following additional feature is provided:

Output offset detection

The TDA7569BLV has 2 operating status:

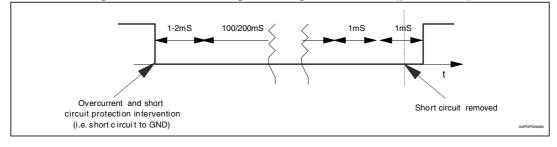

- RESTART mode. The diagnostic is not enabled. Each audio channel operates independently of each other. If any of the a.m. faults occurs, only the channel(s) interested is shut down. A check of the output status is made every 1 ms (*Figure 29*). Restart takes place when the overload is removed.

- DIAGNOSTIC mode. It is enabled via I<sup>2</sup>C bus and it self activates if an output overload (such as to cause the intervention of the short-circuit protection) occurs to the speakers outputs. Once activated, the diagnostics procedure develops as follows (*Figure 30*):

- To avoid momentary re-circulation spikes from giving erroneous diagnostics, a check of the output status is made after 1ms: if normal situation (no overloads) is detected, the diagnostic is not performed and the channel returns active.

- Instead, if an overload is detected during the check after 1 ms, then a diagnostic cycle having a duration of about 100 ms is started.

- After a diagnostic cycle, the audio channel interested by the fault is switched to RESTART mode. The relevant data are stored inside the device and can be read by the microprocessor. When one cycle has terminated, the next one is activated by an I<sup>2</sup>C reading. This is to ensure continuous diagnostics throughout the carradio operating time.

- To check the status of the device a sampling system is needed. The timing is chosen at microprocessor level (over half a second is recommended).

# Figure 29. Restart timing without diagnostic enable (permanent) - Each 1 mS time, a sampling of the fault is done

### 4.3 Output DC offset detection

Any DC output offset exceeding  $\pm 2$  V is signalled out. This inconvenient might occur as a consequence of initially defective or aged and worn-out input capacitors feeding a DC component to the inputs, so putting the speakers at risk of overheating.

This diagnostic has to be performed with low-level output AC signal (or Vin = 0).

The test is run with selectable time duration by microprocessor (from a "start" to a "stop" command):

- START = Last reading operation or setting IB1 D5 (OFFSET enable) to 1

- STOP = Actual reading operation

Excess offset it is signalled out if persistent for all the assigned testing time. This feature is disabled if any overloads leading to activation of the short-circuit protection occurs in the process.

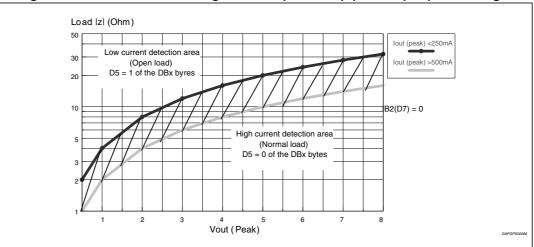

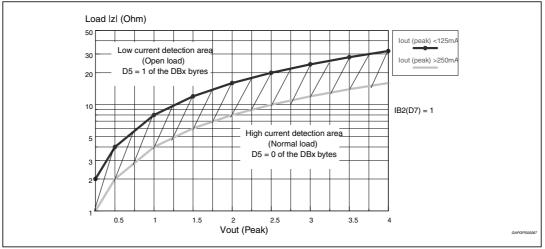

### 4.4 AC diagnostic

This function is design to detect accidental disconnection of tweeters in 2-way speaker and, more in general, presence of capacitive (AC) coupled loads.

This diagnostic is based on the notion that the overall speaker's impedance (woofer + parallel tweeter) will tend to increase towards high frequencies if the tweeter gets disconnected, because the remaining speaker (woofer) would be out of its operating range (high impedance). The diagnostic decision is made according to peak output current thresholds, and it is enabled by setting (IB2-D2) = 1. Two different detection levels are available:

- High current threshold IB2 (D7) = 0

lout > 500 mApk = normal status

lout < 250 mApk = open tweeter</li>

- Low current threshold IB2 (D7) = 1 lout > 250 mApk = normal status lout < 125 mApk = open tweeter</li>

To correctly implement this feature, it is necessary to briefly provide a signal tone (with the amplifier in "play") whose frequency and magnitude are such as to determine an output current higher than 500 mApk with IB2(D7) = 0 (higher than 250 mApk with IB2(D7) = 1) in normal conditions and lower than 250 mApk with IB2(D7) = 0 (lower than 125 mApk with IB2(D7) = 1) should the parallel tweeter be missing.

The test has to last for a minimum number of 3 sine cycles starting from the activation of the AC diagnostic function IB2<D2>) up to the  $I^2C$  reading of the results (measuring period). To confirm presence of tweeter, it is necessary to find at least 3 current pulses over the above threadless over all the measuring period, else an "open tweeter" message will be issued.

The frequency / magnitude setting of the test tone depends on the impedance characteristics of each specific speaker being used, with or without the tweeter connected (to be calculated case by case). High-frequency tones (> 10 kHz) or even ultrasonic signals are recommended for their negligible acoustic impact and also to maximize the impedance module's ratio between with tweeter-on and tweeter-off.

*Figure 31* and *32* shows the load impedance as a function of the peak output voltage and the relevant diagnostic fields.

It is recommended to keep output voltage always below 8 V (high threshold) or 4 V (low threshold) to avoid the circuit to saturate (causing wrong detection cases).

This feature is disabled if any overloads leading to activation of the short-circuit protection occurs in the process.

Figure 31. Current detection high: load impedance |Z| vs. output peak voltage

Figure 32. Current detection low: load impedance |Z| vs. output peak voltage

## 5 Multiple faults

When more misconnections are applied simultaneously at the audio outputs, it is guaranteed that at least one of them is initially read out. The others are notified after successive cycles of  $I^2C$  reading and faults removal, provided that the diagnostic is enabled. This is true for both kinds of diagnostic (Turn on and Permanent).

The table below shows all the couples of double-fault possible. It should be taken into account that a short circuit with the 4 ohm speaker unconnected is considered as double fault.

|              | S. GND | S. Vs          | S. Across L. | Open L.     |

|--------------|--------|----------------|--------------|-------------|

| S. GND       | S. GND | S. Vs + S. GND | S. GND       | S. GND      |

| S. Vs        | 1      | S. Vs          | S. Vs        | S. Vs       |

| S. Across L. | 1      | 1              | S. Across L. | N.A.        |

| Open L.      | 1      | 1              | 1            | Open L. (*) |

Table 5. Double fault table for turn-on diagnostic

In Permanent Diagnostic the table is the same, with only a difference concerning Open Load <sup>(\*)</sup>, which is not among the recognizable faults. Should an Open Load be present during the device's normal working, it would be detected at a subsequent Turn on Diagnostic cycle (i.e. at the successive Car Radio Turn on).

### 5.1 Faults availability

All the results coming from I<sup>2</sup>C bus, by read operations, are the consequence of measurements inside a defined period of time. If the fault is stable throughout the whole period, it will be sent out.

To guarantee always resident functions, every kind of diagnostic cycles (Turn on, Permanent, Offset) will be reactivate after any  $l^2C$  reading operation. So, when the micro reads the  $l^2C$ , a new cycle will be able to start, but the read data will come from the previous diag. cycle (i.e. The device is in Turn On state, with a short to Gnd, then the short is removed and micro reads  $l^2C$ . The short to Gnd is still present in bytes, because it is the result of the previous cycle. If another  $l^2C$  reading operation occurs, the bytes do not show the short). In general to observe a change in Diagnostic bytes, two  $l^2C$  reading operations are necessary.

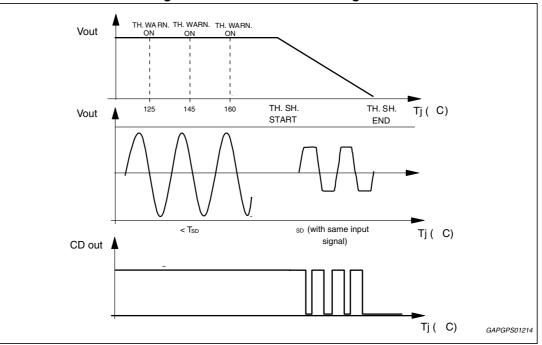

## 6 Thermal protection

Thermal protection is implemented through thermal foldback (Figure 33).

Thermal foldback begins limiting the audio input to the amplifier stage as the junction temperatures rise above the normal operating range. This effectively limits the output power capability of the device thus reducing the temperature to acceptable levels without totally interrupting the operation of the device.

The output power will decrease to the point at which thermal equilibrium is reached. Thermal equilibrium will be reached when the reduction in output power reduces the dissipated power such that the die temperature falls below the thermal foldback threshold. Should the device cool, the audio level will increase until a new thermal equilibrium is reached or the amplifier reaches full power. Thermal foldback will reduce the audio output level in a linear manner.

Three thermal warning are available through the  $I^2C$  bus data. After thermal shut down threshold is reached, the CD could toggle (as shown in *Figure 33*) or stay low, depending on signal level.

Figure 33. Thermal foldback diagram

### 6.1 Fast muting

The muting time can be shortened to less than 1.5ms by setting (IB2) D5 = 1. This option can be useful in transient battery situations (i.e. during car engine cranking) to quickly turnoff the amplifier to avoid any audible effects caused by noise/transients being injected by preamp stages. The bit must be set back to "0" shortly after the mute transition.

## 7 Battery transitions management

### 7.1 Low voltage operation ("start stop")

The most recent OEM specifications are requiring automatic stop of car engine at traffic light, in order to reduce emissions of polluting substances. The TDA7569BLV, thanks to its innovating design, allows a continuous operation when battery falls down to 6/7V during such conditions, without producing pop noise. The maximum system power will be reduced accordingly.

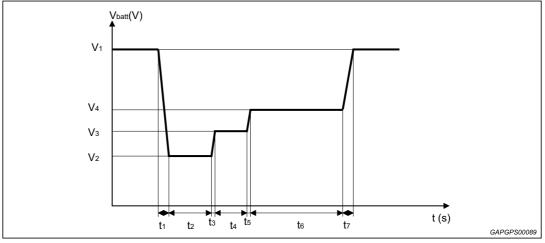

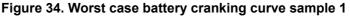

Worst case battery cranking curves are shown below, indicating the shape and durations of allowed battery transitions.

V1 = 12 V; V2 = 6 V; V3 = 7 V; V4 = 8 V

t1 = 2 ms; t2 = 50 ms; t3 = 5 ms; t4 = 300 ms; t5 =10 ms; t6 = 1 s; t7 = 2 ms

Figure 35. Worst case battery cranking curve sample 2

V1 = 12 V; V2 = 6 V; V3 = 7 V

t1 = 2 ms; t2 = 5 ms; t3 = 15 ms; t5 = 1 s; t6 = 50 ms

## 7.2 Advanced battery management

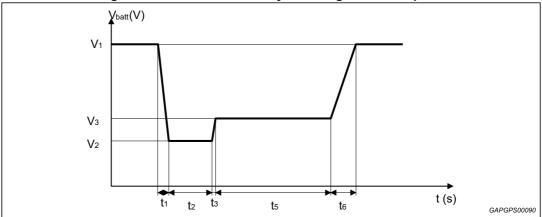

In addition to compatibility with low  $V_{batt}$ , the TDA7569BLV is able to sustain upwards fast battery transitions (like the one showed in *Figure 36*) without causing unwanted audible effect, thanks to the innovative circuit topology.

#### Figure 36. Upwards fast battery transitions diagram

## 8 Application suggestion

### 8.1 Inputs impedance matching

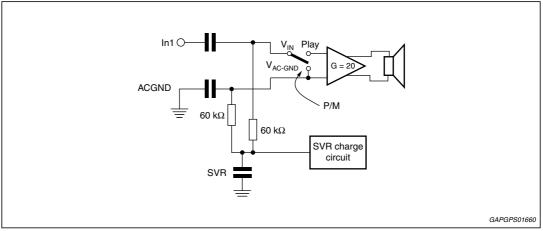

### Figure 37. Inputs impedance matching circuit

The above is a simplified input stage where it is visible that the AC-GND impedance (60 k $\Omega$ ) is the same as the input one.

During battery variations the SVR voltage is moved and  $V_{\text{IN}}$  and  $V_{\text{AC-GND}}$  tracks it through the two R-C networks.

Any differences of this two time constants can produce a differential input voltage, which can produce a noise.

Consequently, any additional passive components at the inputs (other than the input capacitors) such as series resistance or R dividers must be compensated for at AC-GND level by connecting the same equivalent resistance in series to  $C_{AC-GND}$ .

A good 1:1 matching ( $Z_{AC-GND} = Z_{IN}$ ) is therefore recommended to minimize pop. This rule applies to both "4-CH operation" and "2-CH operation", as any unused input has be AC-grounded (through the same  $C_{IN}$  value).

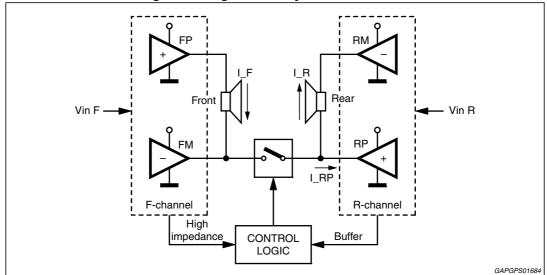

### 8.2 High efficiency introduction

Thanks to its operating principle, the TDA7569BLV obtains a substantial reduction of power dissipation from traditional class-AB amplifiers without being affected by the massive radiation effects and complex circuitry normally associated with class-D solutions.

The high efficiency operating principle is based on the use of bridge structures which are connected by means of a power switch. In particular, as shown in *Figure 2*, Ch1 is linked to Ch2, while Ch3 to Ch4. The switch, controlled by a logic circuit which senses the input signals, is closed at low volumes (output power steadily lower than 2.5 W) and the system acts like a "single bridge" with double load. In this case, the total power dissipation is a quarter of a double bridge.

Due to its structure, the highest efficiency level can be reached when symmetrical loads are applied on channels sharing the same switch.

Figure 38. High efficiency - basic structure

When the power demand increases to more than 2.5 W, the system behavior is switched back to a standard double bridge in order to guarantee the maximum output power, while in the 6 V start-stop devices the High Efficiency mode is automatically disabled at low V<sub>CC</sub> (7.3 V ± 0.3 V). No need to re-program it when V<sub>CC</sub> goes back to normal levels.

The results show (*Figure 19*) that in the range 2-4 W (@  $V_{CC}$  = 14.4 V,  $R_L$  = 4 $\Omega$ ), with the High Efficiency mode, the dissipated power gets up to 50 % less than the value obtained with the standard mode.

## 9 $I^2C$ bus

## 9.1 I<sup>2</sup>C programming/reading sequences

A correct turn on/off sequence with respect to the diagnostic timings and producing no audible noises could be as follows (after battery connection):

- TURN-ON: PIN2 > 4.5V --- 10 ms --- (STAND-BY OUT + DIAG ENABLE) --- 1 s (min) --- MUTING OUT

- TURN-OFF: MUTING IN wait for 50 ms HW ST-BY IN (ST-BY pin ≤ 1.2 V)

- Car Radio Installation: PIN2 > 4.5 V --- 10ms DIAG ENABLE (write) --- 200 ms --l<sup>2</sup>C read (repeat until All faults disappear).

- OFFSET TEST: Device in Play (no signal) -- OFFSET ENABLE 30 ms I<sup>2</sup>C reading (repeat I<sup>2</sup>C reading until high-offset message disappears).

## 9.2 Address selection and I<sup>2</sup>C disable

When the ADSEL/I2CDIS pin is left open the I<sup>2</sup>C bus is disabled and the device can be controlled by the STBY/MUTE pin.

In this status (no -  $I^2C$  bus) the CK pin enables the HIGH-EFFICIENCY MODE (0 = STD MODE; 1 = HE MODE) and the DATA pin sets the gain (0 = 26 dB; 1 = 16 dB).

When the ADSEL/I2CDIS pin is connected to GND the I<sup>2</sup>C bus is active with address <1101100-x>.

To select the other I<sup>2</sup>C address a resistor must be connected to ADSEL/I2CDIS pin as following:

$0 < R < 1 \text{ k}\Omega$ : I<sup>2</sup>C bus active with address <1101100x>

11 k $\Omega$  < R < 21 k $\Omega$ : I<sup>2</sup>C bus active with address <1101101x>

40 k $\Omega$  < R < 70 k $\Omega$ : I<sup>2</sup>C bus active with address <1101110x>

R > 120 k $\Omega$ : Legacy mode

(x: read/write bit sector)

## 9.3 I<sup>2</sup>C bus interface

Data transmission from microprocessor to the TDA7569BLV and viceversa takes place through the 2 wires  $I^2C$  bus interface, consisting of the two lines SDA and SCL (pull-up resistors to positive supply voltage must be connected).

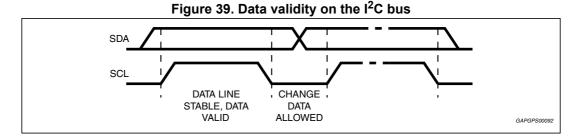

### 9.3.1 Data validity

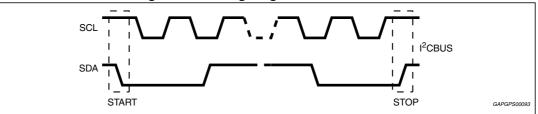

As shown by *Figure 39*, the data on the SDA line must be stable during the high period of the clock. The HIGH and LOW state of the data line can only change when the clock signal on the SCL line is LOW.

### 9.3.2 Start and stop conditions

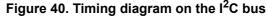

As shown by *Figure 40* a start condition is a HIGH to LOW transition of the SDA line while SCL is HIGH. The stop condition is a LOW to HIGH transition of the SDA line while SCL is HIGH.

### 9.3.3 Byte format

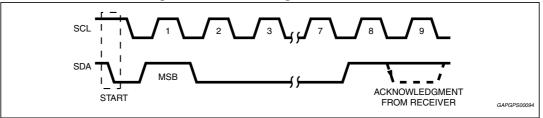

Every byte transferred to the SDA line must contain 8 bits. Each byte must be followed by an acknowledge bit. The MSB is transferred first.

### 9.3.4 Acknowledge

The transmitter<sup>\*</sup> puts a resistive HIGH level on the SDA line during the acknowledge clock pulse (see *Figure 41*). The receiver<sup>\*\*</sup> has to pull-down (LOW) the SDA line during the acknowledge clock pulse, so that the SDA line is stable LOW during this clock pulse.

\* Transmitter

- master (µP) when it writes an address to the TDA7569BLV

- slave (TDA7569BLV) when the  $\mu$ P reads a data byte from TDA7569BLV

\*\* Receiver

- slave (TDA7569BLV) when the  $\mu$ P writes an address to the TDA7569BLV

- master (μP) when it reads a data byte from TDA7569BLV

Figure 41. Acknowledge on the I<sup>2</sup>C bus

## **10** Software specifications

All the functions of the TDA7569BLV are activated by  $I^2C$  interface.

The bit 0 of the "ADDRESS BYTE" defines if the next bytes are write instruction (from  $\mu$ P to TDA7569BLV) or read instruction (from TDA7569BLV to  $\mu$ P).

#### Chip address

| D7 |   |   |   |   |     |     | D0 |        |

|----|---|---|---|---|-----|-----|----|--------|

| 1  | 1 | 0 | 1 | 1 | (*) | (*) | Х  | D8 Hex |

X = 0 Write to device

X = 1 Read from device

If R/W = 0, the  $\mu$ P sends 2 "Instruction Bytes": IB1 and IB2.

(\*) address selector bit, please refer to address selection description on Chapter 9.2.

| Bit | Instruction decoding bit                                                                        |

|-----|-------------------------------------------------------------------------------------------------|

| D7  | Supply transition mute threshold high (D7 = 1)<br>Supply transition mute threshold low (D7 = 0) |

| D6  | Diagnostic enable (D6 = 1)<br>Diagnostic defeat (D6 = 0)                                        |

| D5  | Offset Detection enable (D5 = 1)<br>Offset Detection defeat (D5 = 0)                            |

| D4  | Front Channel (CH1, CH3)<br>Gain = 26 dB (D4 = 0)<br>Gain = 16 dB (D4 = 1)                      |

| D3  | Rear Channel (CH2, CH4)<br>Gain = 26 dB (D3 = 0)<br>Gain = 16 dB (D3 = 1)                       |

| D2  | Mute front channels (D2 = 0)<br>Unmute front channels (D2 = 1)                                  |

| D1  | Mute rear channels (D1 = 0)<br>Unmute rear channels (D1 = 1)                                    |

| D0  | CD 2% (D0 = 0)<br>CD 10% (D0 = 1)                                                               |

### Table 6. IB1

| Bit | Instruction decoding bit                                                                                                    |

|-----|-----------------------------------------------------------------------------------------------------------------------------|

| D7  | Current detection threshold<br>High th (D7 = 0)<br>Low th (D7 =1)                                                           |

| D6  | 0                                                                                                                           |

| D5  | Normal muting time (D5 = 0)<br>Fast muting time (D5 = 1)                                                                    |

| D4  | Stand-by on - Amplifier not working - (D4 = 0)<br>Stand-by off - Amplifier working - (D4 = 1)                               |

| D3  | Power amplifier mode diagnostic (D3 = 0)<br>Line driver mode diagnostic (D3 = 1)                                            |

| D2  | Current Detection Diagnostic Enabled (D2 =1)<br>Current Detection Diagnostic Defeat (D2 =0)                                 |

| D1  | Right Channel Power amplifier working in standard mode (D1 = 0)<br>Power amplifier working in high efficiency mode (D1 = 1) |

| D0  | Left Channel Power amplifier working in standard mode (D0 = 0)<br>Power amplifier working in high efficiency mode (D0 = 1)  |

### Table 7. IB2

If R/W = 1, the TDA7569BLV sends 4 "Diagnostics Bytes" to  $\mu$ P: DB1, DB2, DB3 and DB4.

### Table 8. DB1

| Bit | Instruction decoding bit                                                                                                                                                |                                                                                                                                                                |  |  |  |  |  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| D7  | Thermal warning 1 active (D7 = 1), T <sub>j</sub> =160 °C                                                                                                               | -                                                                                                                                                              |  |  |  |  |  |

| D6  | Diag. cycle not activated or not terminated (D6 = 0)<br>Diag. cycle terminated (D6 = 1)                                                                                 | -                                                                                                                                                              |  |  |  |  |  |

| D5  | Channel LF (CH1)<br>Current detection IB2 (D7) = 0<br>Output peak current < 250 mA - Open load (D5 = 1)<br>Output peak current > 500 mA - Normal load (D5 = 0)          | Channel LF (CH1)<br>Current detection IB2 (D7) = 1<br>Output peak current < 125 mA - Open load (D5 = 1)<br>Output peak current > 250 mA - Normal load (D5 = 0) |  |  |  |  |  |

| D4  | Channel LF (CH1)<br>Turn-on diagnostic (D4 = 0)<br>Permanent diagnostic (D4 = 1)                                                                                        | -                                                                                                                                                              |  |  |  |  |  |

| D3  | Channel LF (CH1)<br>Normal load (D3 = 0)<br>Short load (D3 = 1)                                                                                                         | -                                                                                                                                                              |  |  |  |  |  |

| D2  | Channel LF (CH1)<br>Turn-on diag.: No open load (D2 = 0)<br>Open load detection (D2 = 1)<br>Offset diag.: No output offset (D2 = 0)<br>Output offset detection (D2 = 1) | -                                                                                                                                                              |  |  |  |  |  |

| Bit | Instruction decoding bit                                              |   |  |

|-----|-----------------------------------------------------------------------|---|--|

| D1  | Channel LF (CH1)<br>No short to Vcc (D1 = 0)<br>Short to Vcc (D1 = 1) | - |  |

| D0  | Channel LF (CH1)<br>No short to GND (D1 = 0)<br>Short to GND (D1 = 1) | - |  |

### Table 8. DB1 (continued)

#### Table 9. DB2

| Bit | Instruction decoding bit                                                                                                                                                   |                                                                                                                                                                |  |  |  |  |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| D7  | Offset detection not activated (D7 = 0)<br>Offset detection activated (D7 = 1)                                                                                             | -                                                                                                                                                              |  |  |  |  |  |

| D6  | x                                                                                                                                                                          | -                                                                                                                                                              |  |  |  |  |  |

| D5  | Channel LR (CH2)<br>Current detection IB2 (D7) = 0<br>Output peak current < 250 mA - Open load (D5 = 1)<br>Output peak current > 500 mA - Normal load (D5 = 0)             | Channel LR (CH2)<br>Current detection IB2 (D7) = 1<br>Output peak current < 125 mA - Open load (D5 = 1)<br>Output peak current > 250 mA - Normal load (D5 = 0) |  |  |  |  |  |

| D4  | Channel LR (CH2)<br>Turn-on diagnostic (D4 = 0)<br>Permanent diagnostic (D4 = 1)                                                                                           | -                                                                                                                                                              |  |  |  |  |  |

| D3  | Channel LR (CH2)<br>Normal load (D3 = 0)<br>Short load (D3 = 1)                                                                                                            | -                                                                                                                                                              |  |  |  |  |  |

| D2  | Channel LR (CH2)<br>Turn-on diag.: No open load (D2 = 0)<br>Open load detection (D2 = 1)<br>Permanent diag.: No output offset (D2 = 0)<br>Output offset detection (D2 = 1) | -                                                                                                                                                              |  |  |  |  |  |

| D1  | Channel LR (CH2)<br>No short to Vcc (D1 = 0)<br>Short to Vcc (D1 = 1)                                                                                                      | -                                                                                                                                                              |  |  |  |  |  |

| D0  | Channel LR (CH2)<br>No short to GND (D1 = 0)<br>Short to GND (D1 = 1)                                                                                                      | -                                                                                                                                                              |  |  |  |  |  |

| Bit | Instruction                                                                                                                                                                | decoding bit |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| D7  | Standby status (= IB2 - D4)                                                                                                                                                | -            |

| D6  | Diagnostic status (= IB1 - D6)                                                                                                                                             | -            |

| D5  | Channel RF (CH3)<br>Current detection IB2 (D7) = 0<br>Output peak current < 250 mA - Open load (D5 = 1)<br>Output peak current > 500 mA - Normal load (D5 = 0)             |              |

| D4  | Channel RF (CH3)<br>Turn-on diagnostic (D4 = 0)<br>Permanent diagnostic (D4 = 1)                                                                                           | -            |

| D3  | Channel RF (CH3)<br>Normal load (D3 = 0)<br>Short load (D3 = 1)                                                                                                            | -            |

| D2  | Channel RF (CH3)<br>Turn-on diag.: No open load (D2 = 0)<br>Open load detection (D2 = 1)<br>Permanent diag.: No output offset (D2 = 0)<br>Output offset detection (D2 = 1) | -            |

| D1  | Channel RF (CH3)<br>No short to Vcc (D1 = 0)<br>Short to Vcc (D1 = 1)                                                                                                      | -            |

| D0  | Channel RF (CH3)<br>No short to GND (D1 = 0)<br>Short to GND (D1 = 1)                                                                                                      | -            |

### Table 10. DB3

| Bit | t Instruction decoding bit                                                                                                                                                 |                                                                                                                                                                |  |  |  |  |  |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|     |                                                                                                                                                                            |                                                                                                                                                                |  |  |  |  |  |  |

| D7  | Thermal warning 2 active (D7 = 1), $T_j = 145 \text{ °C}$                                                                                                                  | -                                                                                                                                                              |  |  |  |  |  |  |

| D6  | Thermal warning 3 active (D6 = 1) T <sub>j</sub> = 125 °C                                                                                                                  | -                                                                                                                                                              |  |  |  |  |  |  |

| D5  | Channel RR (CH4)<br>Current detection IB2 (D7) = 0<br>Output peak current < 250 mA - Open load (D5 = 1)<br>Output peak current > 500 mA - Normal load (D5 = 0)             | Channel RR (CH4)<br>Current detection IB2 (D7) = 1<br>Output peak current < 125 mA - Open load (D5 = 1)<br>Output peak current > 250 mA - Normal load (D5 = 0) |  |  |  |  |  |  |

| D4  | Channel RR (CH4)<br>Turn-on diagnostic (D4 = 0)<br>Permanent diagnostic (D4 = 1)                                                                                           | -                                                                                                                                                              |  |  |  |  |  |  |

| D3  | Channel R (CH4)<br>R Normal load (D3 = 0)<br>Short load (D3 = 1)                                                                                                           | -                                                                                                                                                              |  |  |  |  |  |  |

| D2  | Channel RR (CH4)<br>Turn-on diag.: No open load (D2 = 0)<br>Open load detection (D2 = 1)<br>Permanent diag.: No output offset (D2 = 0)<br>Output offset detection (D2 = 1) | -                                                                                                                                                              |  |  |  |  |  |  |

| D1  | Channel RR (CH4)<br>No short to Vcc (D1 = 0)<br>Short to Vcc (D1 = 1)                                                                                                      | -                                                                                                                                                              |  |  |  |  |  |  |

| D0  | Channel RR (CH4)<br>No short to GND (D1 = 0)<br>Short to GND (D1 = 1)                                                                                                      | -                                                                                                                                                              |  |  |  |  |  |  |

Table 11. DB4

## 11 Examples of bytes sequence

#### 1 - Turn-On diagnostic - Write operation

| 01    |                          | 1.01/ |                   | 101 |     | 101 | OTOD |

|-------|--------------------------|-------|-------------------|-----|-----|-----|------|

| Start | Address byte with D0 = 0 | ACK   | IB1 with $D6 = 1$ | ACK | IB2 | ACK | STOP |

2 - Turn-On diagnostic - Read operation

| Start | Address byte with D0 = 1 | ACK | DB1 | ACK | DB2 | ACK | DB3 | ACK | DB4 | ACK | STOP |  |

|-------|--------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|--|

|-------|--------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|--|

The delay from 1 to 2 can be selected by software, starting from 1ms

3a - Turn-On of the power amplifier with 26dB gain, mute on, diagnostic defeat, CD = 2%

| Start | Address byte with D0 = 0 | ACK | IB1      | ACK | IB2      | ACK | STOP |

|-------|--------------------------|-----|----------|-----|----------|-----|------|

|       |                          |     | X0000000 |     | XXX1XX11 |     |      |

#### **3b** - Turn-Off of the power amplifier

| Start | Address byte with D0 = 0 | ACK | IB1      | ACK | IB2      | ACK | STOP |

|-------|--------------------------|-----|----------|-----|----------|-----|------|

|       |                          |     | X0XXXXXX |     | XXX0XXXX |     |      |

#### 4 - Offset detection procedure enable

| Start | Address byte with D0 = 0 | ACK | IB1      | ACK | IB2      | ACK | STOP |

|-------|--------------------------|-----|----------|-----|----------|-----|------|