## SPC584Bx

# 32-bit Power Architecture microcontroller for automotive ASIL-B applications

Datasheet - production data

#### **Features**

- · AEC-Q100 qualified

- High performance e200z420

- 32-bit Power Architecture technology CPU

- Core frequency as high as 120 MHz

- Variable Length Encoding (VLE)

- 2112 KB (2048 KB code flash + 64 KB data flash) on-chip flash memory: supports read during program and erase operations, and multiple blocks allowing EEPROM emulation

- 176 KB HSM dedicated flash memory (144 KB code + 32 KB data)

- 128 KB on-chip general-purpose SRAM (in addition to 64 KB core local data RAM

- Crossbar switch architecture for concurrent access to peripherals, Flash, or RAM from multiple bus masters with end-to-end ECC

- Multi-channel direct memory access controller (eDMA) with 64 channels

- 1 interrupt controller (INTC)

- Comprehensive new generation ASIL-B safety concept

- ASIL-B of ISO 26262

- FCCU for collection and reaction to failure notifications

- Memory Error Management Unit (MEMU) for collection and reporting of error events in memories

- Cyclic redundancy check (CRC) unit

- Enhanced low power support

- Ultra low power STANDBY

- Smart Wake-up Unit

- Fast wake-up and execute from RAM

- Enhanced modular IO subsystem (eMIOS): up to 64 timed I/O channels with 16-bit counter resolution

- Body cross triggering unit (BCTU)

- Triggers ADC conversions from any eMIOS channel

- Triggers ADC conversions from up to 2 dedicated PIT RTIs

- Enhanced analog-to-digital converter system with:

- 2 independent fast 12-bit SAR analog converters

- 1 supervisor 12-bit SAR analog converter

- 1 10-bit SAR analog converter with STDBY mode support

- Communication interfaces

- 1 Ethernet controller 10/100 Mbps, compliant IEEE 802.3-2008

- 8 MCAN interfaces with advanced shared memory scheme and ISO CAN-FD support

- 14 LINFlexD modules

- 7 Deserial Serial Peripheral Interface (DSPI) modules

- Dual phase-locked loops with stable clock domain for peripherals and FM modulation domain for computational shell

- Nexus Development Interface (NDI) per IEEE-ISTO 5001-2003 standard, with some support for 2010 standard

- Boot Assist Flash (BAF) supports factory programming using a serial bootload through the asynchronous CAN or LIN/UART

- Junction temperature range -40 °C to 150 °C

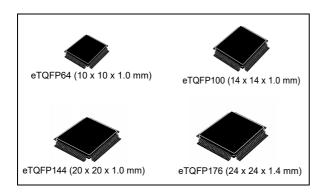

**Table 1. Device summary**

| Package  | Part number |             |             |  |  |  |  |  |

|----------|-------------|-------------|-------------|--|--|--|--|--|

| Package  | 1 MB        | 1.5 MB      | 2 MB        |  |  |  |  |  |

| eTQFP64  | SPC584B60E1 | SPC584B64E1 | SPC584B70E1 |  |  |  |  |  |

| eTQFP100 | SPC584B60E3 | SPC584B64E3 | SPC584B70E3 |  |  |  |  |  |

| eTQFP144 | SPC584B60E5 | SPC584B64E5 | SPC584B70E5 |  |  |  |  |  |

| eLQFP176 | SPC584B60E7 | SPC584B64E7 | SPC584B70E7 |  |  |  |  |  |

SPC584Bx Contents

# **Contents**

| 1 | Intro | duction6                                         |

|---|-------|--------------------------------------------------|

| 2 | Desc  | cription                                         |

|   | 2.1   | Device feature summary                           |

|   | 2.2   | Block diagram                                    |

|   | 2.3   | Features overview11                              |

| 3 | Pack  | age pinouts and signal descriptions              |

| 4 | Elec  | trical characteristics                           |

|   | 4.1   | Introduction                                     |

|   | 4.2   | Absolute maximum ratings                         |

|   | 4.3   | Operating conditions                             |

|   |       | 4.3.1 Power domains and power up/down sequencing |

|   | 4.4   | Electrostatic discharge (ESD)                    |

|   | 4.5   | Electromagnetic compatibility characteristics    |

|   | 4.6   | Temperature profile                              |

|   | 4.7   | Device consumption                               |

|   | 4.8   | I/O pad specification                            |

|   |       | 4.8.1 I/O input DC characteristics               |

|   |       | 4.8.2 I/O output DC characteristics              |

|   |       | 4.8.3 I/O pad current specifications             |

|   | 4.9   | Reset pad (PORST) electrical characteristics     |

|   | 4.10  | PLLs                                             |

|   |       | 4.10.1 PLL0                                      |

|   |       | 4.10.2 PLL1                                      |

|   | 4.11  | Oscillators                                      |

|   |       | 4.11.1 Crystal oscillator 40 MHz                 |

|   |       | 4.11.2 Crystal Oscillator 32 kHz                 |

|   |       | 4.11.3 RC oscillator 16 MHz                      |

|   |       | 4.11.4 Low power RC oscillator                   |

|   | 4.12  | ADC system                                       |

|   |       | 4.12.1 ADC input description                     |

|   |       |                                                  |

|   |      | 4.12.2   | SAR ADC 12 bit electrical specification                          | 48    |

|---|------|----------|------------------------------------------------------------------|-------|

|   |      | 4.12.3   | SAR ADC 10 bit electrical specification                          | 53    |

|   | 4.13 | Tempe    | rature sensor                                                    | 56    |

|   | 4.14 | LFAST    | pad electrical characteristics                                   | 57    |

|   |      | 4.14.1   | LFAST interface timing diagrams                                  | 57    |

|   |      | 4.14.2   | LFAST LVDS interface electrical characteristics                  | 58    |

|   |      | 4.14.3   | LFAST PLL electrical characteristics                             | 61    |

|   | 4.15 | Power    | management                                                       | 63    |

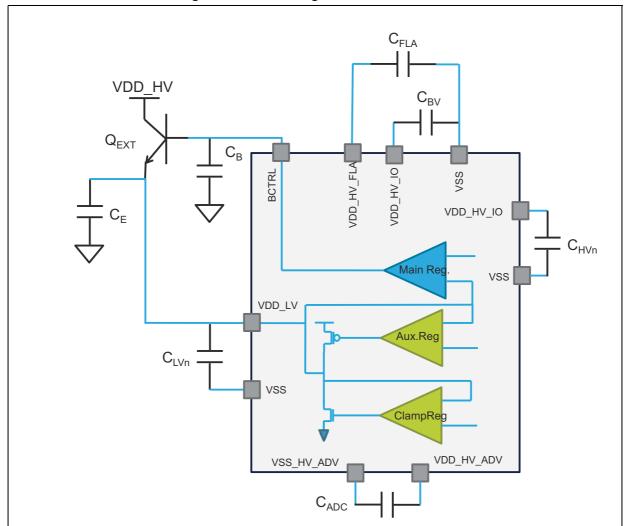

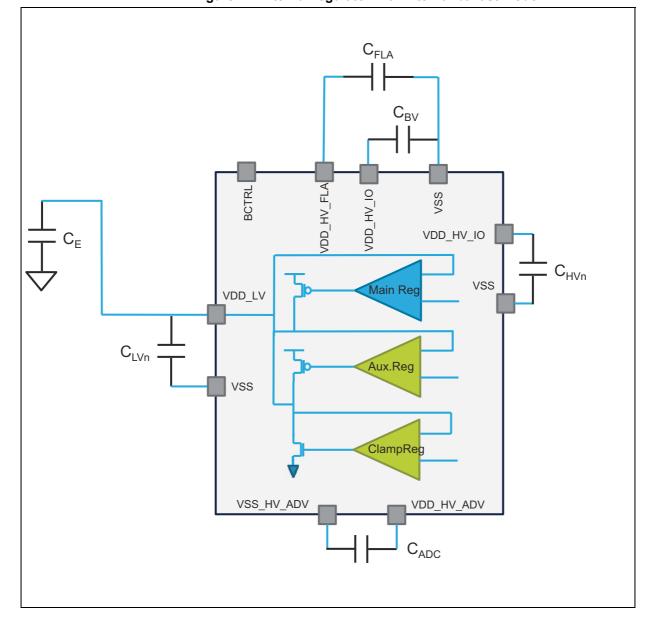

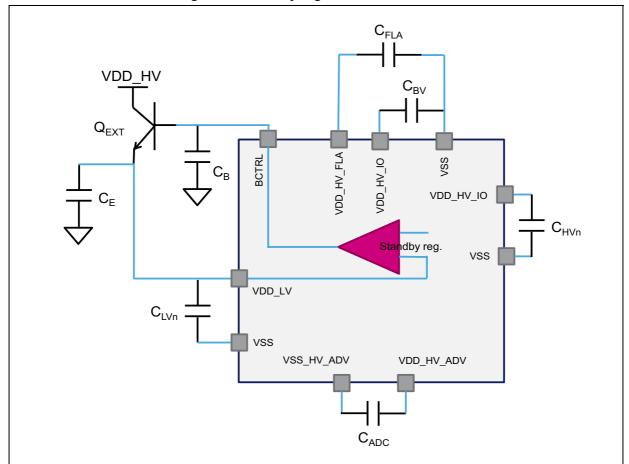

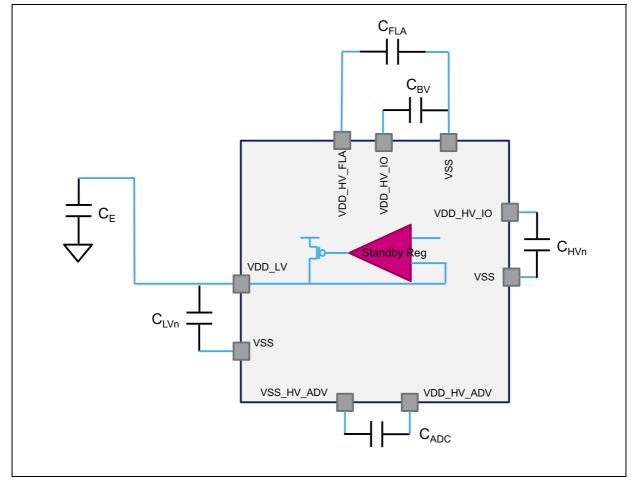

|   |      | 4.15.1   | Power management integration                                     | 63    |

|   |      | 4.15.2   | Voltage regulators                                               | 69    |

|   |      | 4.15.3   | Voltage monitors                                                 | 70    |

|   | 4.16 | Flash    |                                                                  | 73    |

|   | 4.17 | AC spe   | ecifications                                                     | 77    |

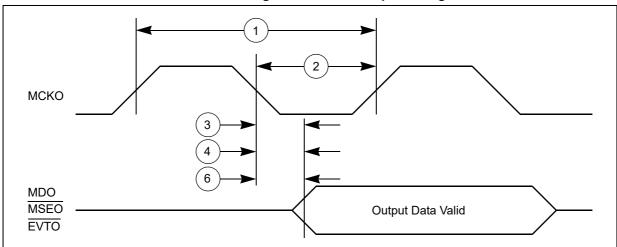

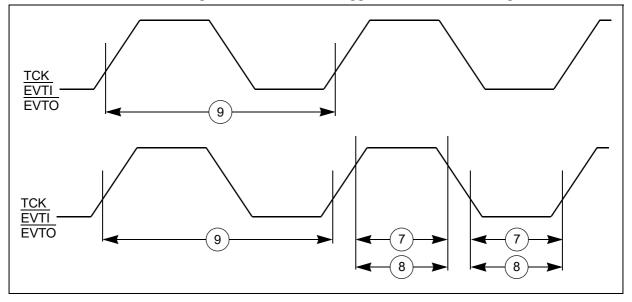

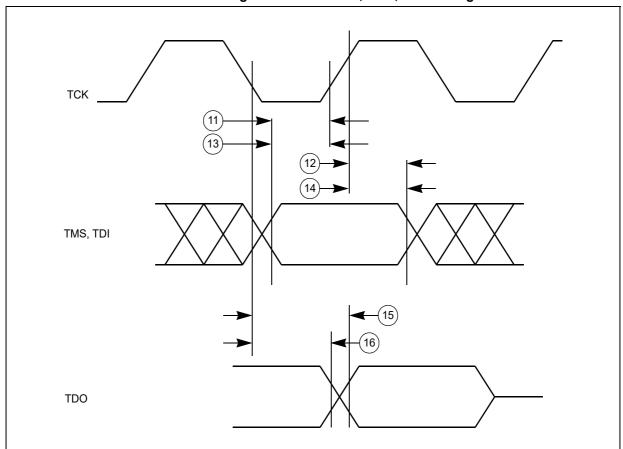

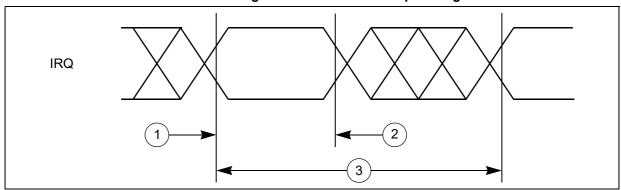

|   |      | 4.17.1   | Debug and calibration interface timing                           | 77    |

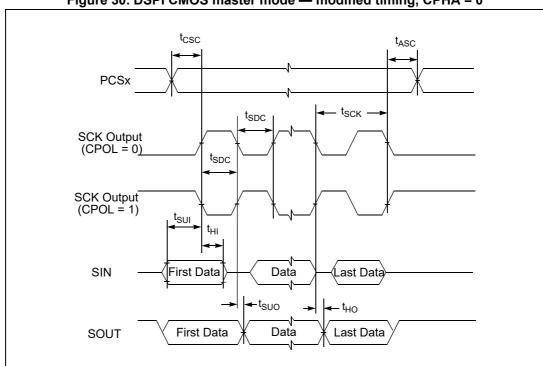

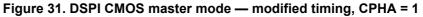

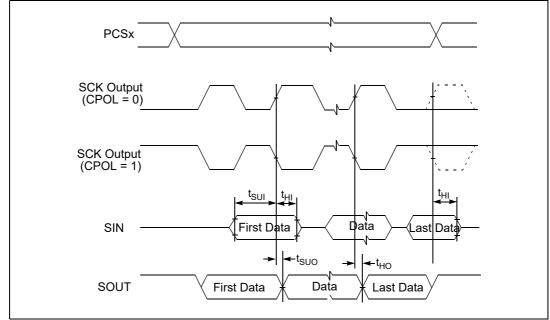

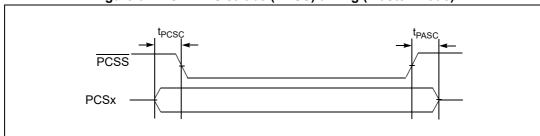

|   |      | 4.17.2   | DSPI timing with CMOS pads                                       | 83    |

|   |      | 4.17.3   | Ethernet timing                                                  | 93    |

|   |      | 4.17.4   | CAN timing                                                       | 99    |

|   |      | 4.17.5   | UART timing                                                      | 100   |

|   |      | 4.17.6   | I2C timing                                                       | 100   |

| 5 | Pack | age info | ormation                                                         | . 102 |

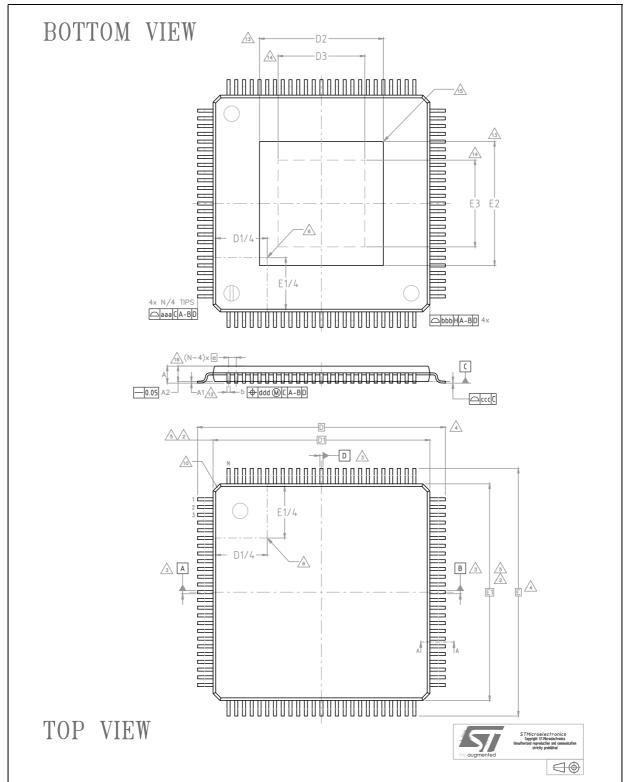

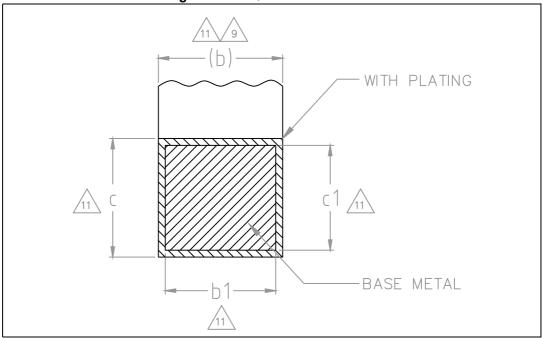

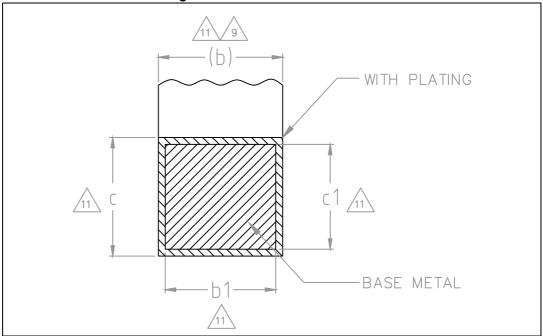

|   | 5.1  | eTQFP    | 64 package information                                           | . 102 |

|   |      | 5.1.1    | Package mechanical drawings and data information                 | 106   |

|   | 5.2  | eTQFP    | 100 package information                                          | . 107 |

|   |      | 5.2.1    | Package mechanical drawings and data information                 | 111   |

|   | 5.3  | eTQFP    | 144 package information                                          | 112   |

|   |      | 5.3.1    | Package mechanical drawings and data information                 | 116   |

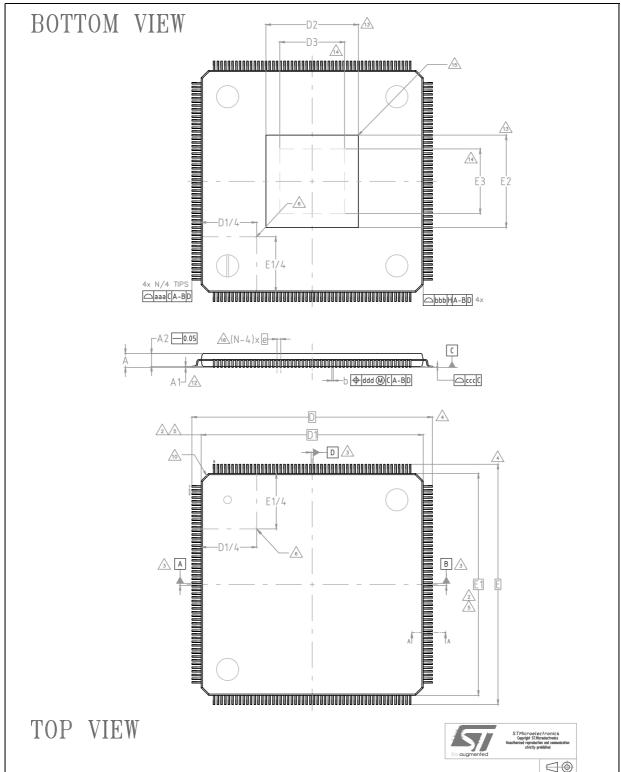

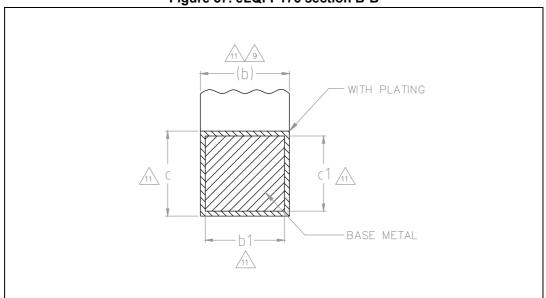

|   | 5.4  | eLQFP    | 176 package information                                          | 117   |

|   |      | 5.4.1    | Package mechanical drawings and data information                 | 121   |

|   | 5.5  | Packag   | ge thermal characteristics                                       |       |

|   |      | 5.5.1    | eTQFP64                                                          |       |

|   |      | 5.5.2    | eTQFP100                                                         |       |

|   |      | 5.5.3    | eTQFP144                                                         | 124   |

|   |      | 5.5.4    | LQFP176                                                          | 124   |

|   |      | 5.5.5    | General notes for specifications at maximum junction temperature | 125   |

| SPC584Bx | Co                   | ntents |

|----------|----------------------|--------|

| 6        | Ordering information | . 128  |

| 7        | Revision history     | . 130  |

Introduction SPC584Bx

# 1 Introduction

This document describes the features of the family and options available within the family members, and highlights important electrical and physical characteristics of the device. To ensure a complete understanding of the device functionality, refer also to the device reference manual and errata sheet.

SPC584Bx Description

## 2 Description

The SPC584Bx microcontroller is a member of the family of devices superseding the SPC560Bx family. SPC584Bx is built on the legacy of the SPC560Bx family, while introducing new features coupled with higher throughput to provide substantial reduction of cost per feature and significant power and performance improvement (MIPS per mW). On the SPC584Bx device, there is one processor core e200z420 and one e200z0 core embedded in the Hardware Security Module.

## 2.1 Device feature summary

*Table 2* lists a summary of major features for the SPC584Bx device. The feature column represents a combination of module names and capabilities of certain modules. A detailed description of the functionality provided by each on-chip module is given later in this document.

Table 2. Features list

| Feature                         | Description               |

|---------------------------------|---------------------------|

| SPC58 family                    | 40 nm                     |

| Number of Cores                 | 1                         |

| Local RAM                       | 64 KB Data                |

| Single Precision Floating Point | Yes                       |

| SIMD                            | No                        |

| VLE                             | Yes                       |

| Cache                           | 8 KB Instruction          |

| Cache                           | 4 KB Data                 |

| MPU                             | Core MPU: 24 per CPU      |

| WIFO                            | System MPU: 24 per XBAR   |

| Semaphores                      | No                        |

| CRC Channels                    | 2 x 4                     |

| Software Watchdog Timer (SWT)   | 2                         |

| Core Nexus Class                | 3+                        |

| Event Processor                 | 4 x SCU                   |

| Event Flocessor                 | 4 x PMC                   |

| Run control Module              | Yes                       |

| System SRAM                     | 128 KB (full standby RAM) |

| Flash                           | 2048 KB code / 64 KB data |

| Flash fetch accelerator         | 2 x 4 x 256-bit           |

| DMA channels                    | 32                        |

| DMA Nexus Class                 | 3                         |

Description SPC584Bx

Table 2. Features list (continued)

| Feature                             | Description                                                     |  |  |  |

|-------------------------------------|-----------------------------------------------------------------|--|--|--|

| LINFlexD                            | 14                                                              |  |  |  |

| MCAN (ISO CAN-FD compliant)         | 8                                                               |  |  |  |

| DSPI                                | 7                                                               |  |  |  |

| I2C                                 | 1                                                               |  |  |  |

| Ethernet                            | 1 MAC with Time Stamping, AVB and VLAN support                  |  |  |  |

| SIPI / LFAST Debugger               | High Speed                                                      |  |  |  |

|                                     | 8 PIT channels                                                  |  |  |  |

| System Timers                       | 1 AUTOSAR® (STM)                                                |  |  |  |

|                                     | RTC/API                                                         |  |  |  |

| eMIOS                               | 2 x 32 channels                                                 |  |  |  |

| BCTU                                | 64 channels                                                     |  |  |  |

| ADC (SAR)                           | 4                                                               |  |  |  |

| Temp. sensor                        | Yes                                                             |  |  |  |

| Self Test Controller                | Yes                                                             |  |  |  |

| PLL                                 | Dual PLL with FM                                                |  |  |  |

| Integrated linear voltage regulator | Yes                                                             |  |  |  |

| External Power Supplies             | 5 V, 3.3 V                                                      |  |  |  |

|                                     | HALT Mode                                                       |  |  |  |

| Low Power Modes                     | STOP Mode                                                       |  |  |  |

| LOW FOWEI MIDUES                    | Smart Standby with output controller, analog and digital inputs |  |  |  |

|                                     | Standby Mode                                                    |  |  |  |

# 2.2 Block diagram

The figures below show the top-level block diagrams.

SPC584Bx Description

JTAGM JTAGC DCI SPU NPC INTC SWT IAC e200 z420n3 – 120 MHz dual issue Main Core Nexus3p VLE EFPU2 I-Cache Control DMA CHMUX DMA CHMUX HSM Unified 8 KB 2 way **↑** 32 ADD Backdoor SIPI\_1 Interface 32 DATA D-MEM D-Cache With ¥ E2E ECC 64 Ch 64 KB D-MEM 4 KB eDMA (32 to 64) 2 way **↑** 32 ADD 32 ADD Core Memory Protection Unit (CMPU) Concentrator\_1 E2E ECC 64 DATA 64 DATA Vexus Data **↓**Nexus Data PAMU BIU with E2E ECC Decorated Storage Access Trace Trace Nexus Data Instruction Trace Load / Store 32 ADD ↑ 32 ADD 32 ADD 32 ADD 32 ADD64 DATA 64 DATA 64 DATA 64 DATA 64 DATA → AHB M AHB M AHB\_M AHB\_M AHB M Cross Bar Switch (XBAR) AMBA 2.0 v6 AHB - 64 bit System Memory Protection Unit AHB S AHB\_S AHB\_S AHB\_S AHB\_S AHB\_S 32 ADD 64 DATA 32 ADD 64 DATA ↑ 32 ADD ↑ 32 ADD 32 ADD 64 DATA 64 DATA 64 DATA Periph. Bridge Periph. Bridg PRAMC 256 Page Line PFLASHC Set-Associative AIPS\_2 E2E ECC AIPS\_1 E2E ECC with E2E ECC FLASH 2 MB Prefetch Buffers with E2E ECC 32 ADD 64 DATA ♣ 32 ADD ↑ 32 ADD EEPROM 32 DATA 32 DATA ٧ SRAM Non Volatile Memory Peripheral Peripheral Multiple RWW partition Array 2 128 KB Cluster 2 Cluster 1

Figure 1. Block diagram

Description SPC584Bx

BCTU\_0 PBRIDGE\_2 STDBY\_CTU\_0 XBAR\_1 eMIOS\_0 XBIC\_Concentrator\_0, 1 ETHERNET\_0 SMPU\_1 SAR\_ADC\_12bit\_0 XBIC\_1 SAR\_ADC\_10bit\_STDBY PCM\_0 SAR\_ADC\_12bit\_B0 PFLASH\_1 12C\_0 INTC\_1 DSPI\_0, 2, 4, 6 SWT\_2, 3 LINFlexD\_0, 2, 4, 6, 8, 10, 12 STM 2 eDMA\_1 CAN\_SUB\_0\_MESSAGE\_RAM PRAM\_2, 3 CAN\_SUB\_0\_M\_CAN\_0..3 CCCU TDM\_0 HSM DTS JDC STCU PBRIDGE\_2 - Peripheral Cluster 2 JTAGM MEMU IMA CRC\_0 DMAMUX\_0 PIT\_0 PBRIDGE\_1 eMIOS\_1 RTC/API SAR\_ADC\_12bit\_1 WKPU DSPI\_1, 3, 5 MC\_PCU PMC\_DIG LINFlexD\_1, 3, 5, 7, 9, 11, 15 MC\_RGM CAN\_SUB\_1\_MESSAGE\_RAM RCOSC\_DIG CAN\_SUB\_1\_M\_CAN\_1..4 PBRIDGE\_1 - Peripheral Cluster 1 RC1024K\_DIG FCCU OSC\_DIG CRC\_1 OSC32K\_DIG DMAMUX\_1 PLL\_DIG PIT\_1 CMU\_0\_PLL0\_XOSC\_IRCOSC CMU\_1\_CORE\_XBAR MC\_CGM CMU\_2\_HPBM CMU\_3\_PBRIDGE MC\_ME CMU 6 SARADC SIUL2 CMU\_11\_FBRIDGE FLASH\_0 FLASH\_ALT\_0 CMU\_12\_EMIOS CMU 14 PFBRIDGE PASS SSCM SIPI 1 LFAST\_1

Figure 2. Periphery allocation

SPC584Bx Description

#### 2.3 Features overview

On-chip modules within SPC584Bx include the following features:

- One main CPU, dual issue, 32-bit CPU core complexes (e200z4)

- Power Architecture embedded specification compliance

- Instruction set enhancement allowing variable length encoding (VLE), encoding a mix of 16-bit and 32-bit instructions, for code size footprint reduction

- Single-precision floating point operations

- 64 KB local data RAM for Core\_2

- 8 KB I-Cache and 4 KB D-Cache for Core\_2

- 2112 KB (2048 KB code flash + 64 KB data flash) on-chip flash memory

- Supports read during program and erase operations, and multiple blocks allowing EEPROM emulation

- 176 KB HSM dedicated flash memory (144 KB code + 32 KB data)

- 128 KB on-chip general-purpose SRAM (+ 64 KB local data RAM: 64 KB included in the CPU)

- Multi channel direct memory access controllers

- 32 eDMA channels

- One interrupt controller (INTC)

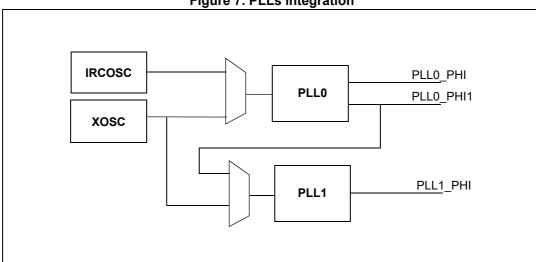

- Dual phase-locked loops with stable clock domain for peripherals and FM modulation domain for computational shell

- Crossbar switch architecture for concurrent access to peripherals, Flash, or RAM from multiple bus masters with end-to-end ECC

- Hardware security module (HSM) with HW cryptographic co-processor

- System integration unit lite (SIUL)

- Boot assist Flash (BAF) supports factory programming using a serial bootload through the asynchronous CAN or LIN/UART.

- Hardware support for safety ASIL-B level related applications

- Enhanced modular IO subsystem (eMIOS): up to 64 (2 x 32) timed I/O channels with 16-bit counter resolution

- Buffered updates

- Support for shifted PWM outputs to minimize occurrence of concurrent edges

- Supports configurable trigger outputs for ADC conversion for synchronization to channel output waveforms

- Shared or independent time bases

- DMA transfer support available

- Body Cross Triggering Unit (BCTU)

- Triggers ADC conversions from any eMIOS channel

- Triggers ADC conversions from up to 2 dedicated PIT RTIs

- One event configuration register dedicated to each timer event allows to define the corresponding ADC channel

- Synchronization with ADC to avoid collision

- Enhanced analog-to-digital converter system with:

- Two independent fast 12-bit SAR analog converters

577

DS11701 Rev 4 11/142

Description SPC584Bx

- One supervisor 12-bit SAR analog converter

- One 10-bit SAR analog converter with STDBY mode support

- Seven Deserial Serial Peripheral Interface (DSPI) modules

- Fourteen LIN and UART communication interface (LINFlexD) modules

- LINFlexD\_0 is a Master/Slave

- All others are Masters

- Eight modular controller area network (MCAN) modules, all supporting flexible data rate (ISO CAN-FD compliant)

- One ethernet controller 10/100 Mbps, compliant IEEE 802.3-2008

- IEEE 1588-2008 Time stamping (internal 64-bit time stamp)

- IEEE 802.1AS and IEEE 802.1Qav (AVB-Feature)

- IEEE 802.1Q VLAN tag detection

- IPv4 and IPv6 checksum modules

- Nexus development interface (NDI) per IEEE-ISTO 5001-2003 standard, with some support for 2010 standard

- Device and board test support per Joint Test Action Group (JTAG) (IEEE 1149.1 and IEEE 1149.7), 2-pin JTAG interface

- Standby power domain with smart wake-up sequence

# 3 Package pinouts and signal descriptions

Refer to the SPC584Bx IO\_ Definition document.

It includes the following sections:

- 1. Package pinouts

- 2. Pin descriptions

- a) Power supply and reference voltage pins

- b) System pins

- c) LVDS pins

- d) Generic pins

DS11701 Rev 4 13/142

## 4 Electrical characteristics

#### 4.1 Introduction

The present document contains the target Electrical Specification for the 40 nm family 32-bit MCU SPC584Bx products.

In the tables where the device logic provides signals with their respective timing characteristics, the symbol "CC" (Controller Characteristics) is included in the "Symbol" column.

In the tables where the external system must provide signals with their respective timing characteristics to the device, the symbol "SR" (System Requirement) is included in the "Symbol" column.

The electrical parameters shown in this document are guaranteed by various methods. To give the customer a better understanding, the classifications listed in *Table 3* are used and the parameters are tagged accordingly in the tables where appropriate.

**Table 3. Parameter classifications**

| Classification tag | Tag description                                                                                                                           |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Р                  | Those parameters are guaranteed during production testing on each individual device.                                                      |

| С                  | Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations. |

| Т                  | Those parameters are achieved by design validation on a small sample size from typical devices.                                           |

| D                  | Those parameters are derived mainly from simulations.                                                                                     |

## 4.2 Absolute maximum ratings

*Table 4* describes the maximum ratings for the device. Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Stress beyond the listed maxima, even momentarily, may affect device reliability or cause permanent damage to the device.

Table 4. Absolute maximum ratings

| Symbol                                                         |                           |   |                                                                                     | ute maximum rat                                              |      |     |     |      |

|----------------------------------------------------------------|---------------------------|---|-------------------------------------------------------------------------------------|--------------------------------------------------------------|------|-----|-----|------|

|                                                                |                           | С | Parameter                                                                           | Conditions                                                   | Min  | Тур | Max | Unit |

| V <sub>DD_LV</sub>                                             | SR                        | D | Core voltage<br>operating life<br>range <sup>(1)</sup>                              | _                                                            | -0.3 | _   | 1.4 | V    |

| V <sub>DD_HV_IO_MAIN</sub> VDD_HV_IO_ETH VDD_HV_OSC VDD_HV_FLA | SR                        | D | I/O supply<br>voltage <sup>(2)</sup>                                                | _                                                            | -0.3 | _   | 6.0 | V    |

| V <sub>SS_HV_ADV</sub>                                         | SR                        | D | ADC ground voltage                                                                  | Reference to digital ground                                  | -0.3 | _   | 0.3 | ٧    |

| V <sub>DD_HV_ADV</sub>                                         | SR                        | D | ADC Supply voltage <sup>(2)</sup>                                                   | Reference to V <sub>SS_HV_ADV</sub>                          | -0.3 | _   | 6.0 | V    |

| V <sub>SS_HV_ADR_S</sub>                                       | SR                        | D | SAR ADC<br>ground<br>reference                                                      | _                                                            | -0.3 | _   | 0.3 | V    |

| V <sub>DD_HV_ADR_S</sub>                                       | SR                        | D | SAR ADC<br>voltage<br>reference <sup>(2)</sup>                                      | Reference to V <sub>SS_HV_ADR_S</sub>                        | -0.3 | _   | 6.0 | V    |

| V <sub>SS</sub> -V <sub>SS_HV_ADR_S</sub>                      | SR                        | D | V <sub>SS_HV_ADR_S</sub><br>differential<br>voltage                                 | _                                                            | -0.3 | _   | 0.3 | V    |

| V <sub>SS</sub> -V <sub>SS_HV_ADV</sub>                        | SR                        | D | V <sub>SS_HV_ADV</sub><br>differential<br>voltage                                   | _                                                            | -0.3 | _   | 0.3 | V    |

|                                                                |                           |   |                                                                                     | _                                                            | -0.3 | _   | 6.0 |      |

|                                                                |                           |   | I/O input voltage                                                                   | Relative to V <sub>ss</sub>                                  | -0.3 | _   | _   |      |

| V <sub>IN</sub>                                                | V <sub>IN</sub> SR D 7701 |   | I/O input voltage range <sup>(2)(3)</sup> (4)                                       | Relative to V <sub>DD_HV_IO</sub> and V <sub>DD_HV_ADV</sub> |      |     | 0.3 | V    |

| T <sub>TRIN</sub>                                              | SR                        | D | Digital Input pad transition time <sup>(5)</sup>                                    | _                                                            | _    | _   | 1   | ms   |

| I <sub>INJ</sub>                                               | SR                        | Т | Maximum DC<br>injection current<br>for each<br>analog/digital<br>PAD <sup>(6)</sup> | _                                                            | -5   | _   | 5   | mA   |

Table 4. Absolute maximum ratings (continued)

| Symbol                 |    | C Parameter            |                                                                    | Conditions                                                                |             | Unit |                    |       |  |

|------------------------|----|------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------|-------------|------|--------------------|-------|--|

| Symbol                 |    | C Parameter Conditions |                                                                    | Conditions                                                                | Min Typ Max |      | Max                |       |  |

| T <sub>STG</sub>       | SR | Т                      | Maximum non-<br>operating<br>Storage<br>temperature<br>range       | _                                                                         | <b>–</b> 55 | _    | 125                | °C    |  |

| T <sub>PAS</sub>       | SR | С                      | Maximum nonoperating temperature during passive lifetime           | _                                                                         | -55         | _    | 150 <sup>(7)</sup> | °C    |  |

| T <sub>STORAGE</sub>   | SR | _                      | Maximum<br>storage time,<br>assembled part<br>programmed in<br>ECU | No supply; storage<br>temperature in<br>range –40 °C to<br>60 °C          | _           | _    | 20                 | years |  |

| T <sub>SDR</sub>       | SR | Т                      | Maximum solder<br>temperature Pb-<br>free packaged <sup>(8)</sup>  | _                                                                         | _           | _    | 260                | °C    |  |

| MSL                    | SR | Т                      | Moisture<br>sensitivity<br>level <sup>(9)</sup>                    | _                                                                         | _           | _    | 3                  |       |  |

| T <sub>XRAY</sub> dose | SR | Т                      | Maximum<br>cumulated<br>XRAY dose                                  | Typical range for X-rays source during inspection:80 ÷ 130 KV; 20 ÷ 50 μA | _           | _    | 1                  | grey  |  |

- V<sub>DD\_LV</sub>: allowed 1.335 V 1.400 V for 60 seconds cumulative time at the given temperature profile. Remaining time allowed 1.260 V 1.335 V for 10 hours cumulative time at the given temperature profile. Remaining time as defined in Section 4.3: Operating conditions.

- 2. V<sub>DD\_HV</sub>: allowed 5.5 V 6.0 V for 60 seconds cumulative time at the given temperature profile, for 10 hours cumulative time with the device in reset at the given temperature profile. Remaining time as defined in Section 4.3: Operating conditions.

- 3. The maximum input voltage on an I/O pin tracks with the associated I/O supply maximum. For the injection current condition on a pin, the voltage will be equal to the supply plus the voltage drop across the internal ESD diode from I/O pin to supply. The diode voltage varies greatly across process and temperature, but a value of 0.3 V can be used for nominal calculations.

- 4. Relative value can be exceeded if design measures are taken to ensure injection current limitation (parameter IINJ).

- 5. This limitation applies to pads with digital input buffer enabled. If the digital input buffer is disabled, there are no maximum limits to the transition time.

- The limits for the sum of all normal and injected currents on all pads within the same supply segment can be found in Section 4.8.3: I/O pad current specifications.

- 175 °C are allowed for limited time. Mission profile with passive lifetime temperature >150 °C have to be evaluated by ST to confirm that are granted by product qualification.

- 8. Solder profile per IPC/JEDEC J-STD-020D.

- 9. Moisture sensitivity per JDEC test method A112.

# 4.3 Operating conditions

*Table 5* describes the operating conditions for the device, and for which all the specifications in the data sheet are valid, except where explicitly noted. The device operating conditions must not be exceeded or the functionality of the device is not guaranteed.

**Table 5. Operating conditions**

| Complete I                                                                                         |    | С | Davamatav                                             | Conditions              |                        | - Unit |                         |      |

|----------------------------------------------------------------------------------------------------|----|---|-------------------------------------------------------|-------------------------|------------------------|--------|-------------------------|------|

| Symbol                                                                                             |    |   | Parameter                                             | Conditions              | Min                    | Тур    | Max                     | Unit |

| F <sub>SYS</sub>                                                                                   | SR | Р | Operating<br>system clock<br>frequency <sup>(2)</sup> | _                       | _                      | _      | 120                     | MHz  |

| T <sub>A_125 Grade</sub> <sup>(3)</sup>                                                            | SR | D | Operating<br>Ambient<br>temperature                   | _                       | -40                    | _      | 125                     | °C   |

| T <sub>J_125</sub> Grade <sup>(3)</sup>                                                            | SR | Р | Junction<br>temperature<br>under bias                 | T <sub>A</sub> = 125 °C | -40                    | _      | 150                     | °C   |

| T <sub>A_105 Grade</sub> <sup>(3)</sup>                                                            | SR | D | Ambient<br>temperature<br>under bias                  | _                       | -40                    | _      | 105                     | °C   |

| T <sub>J_105</sub> Grade (3)                                                                       | SR | D | Operating<br>Junction<br>temperature                  | T <sub>A</sub> = 105 °C | -40                    | _      | 130                     | °C   |

| V <sub>DD_LV</sub>                                                                                 | SR | Р | Core supply voltage <sup>(4)</sup>                    | _                       | 1.14                   | 1.20   | 1.26 <sup>(5) (6)</sup> | V    |

| V <sub>DD_HV_IO_MAIN</sub> V <sub>DD_HV_IO_ETH</sub> V <sub>DD_HV_FLA</sub> V <sub>DD_HV_OSC</sub> | SR | Р | IO supply<br>voltage                                  | _                       | 3.0                    | _      | 5.5                     | V    |

| V <sub>DD_HV_ADV</sub>                                                                             | SR | Р | ADC supply voltage                                    | _                       | 3.0                    | _      | 5.5                     | V    |

| V <sub>SS_HV_ADV</sub> -<br>V <sub>SS</sub>                                                        | SR | D | ADC ground<br>differential<br>voltage                 | _                       | -25                    | _      | 25                      | mV   |

| V <sub>DD_HV_ADR_</sub> s                                                                          | SR | Р | SAR ADC<br>reference<br>voltage                       | _                       | 3.0                    | _      | 5.5                     | V    |

| V <sub>DD_HV_ADR_S</sub> -<br>V <sub>DD_HV_ADV</sub>                                               | SR | D | SAR ADC<br>reference<br>differential<br>voltage       |                         |                        | 25     | mV                      |      |

| V <sub>SS_HV_ADR_S</sub>                                                                           | SR | Р | SAR ADC<br>ground<br>reference<br>voltage             | _                       | V <sub>SS_HV_ADV</sub> |        |                         | V    |

DS11701 Rev 4 17/142

| Symbol                                               |    | C Parameter |                                                                                                   | Conditions                   |      | Unit |     |      |

|------------------------------------------------------|----|-------------|---------------------------------------------------------------------------------------------------|------------------------------|------|------|-----|------|

| Зупівої                                              |    | C           | Parameter                                                                                         | meter Conditions Min         |      | Тур  | Max | Unit |

| V <sub>SS_HV_ADR_S</sub> -<br>V <sub>SS_HV_ADV</sub> | SR | D           | V <sub>SS_HV_ADR_S</sub><br>differential<br>voltage                                               | _                            | -25  | _    | 25  | mV   |

| V <sub>RAMP_HV</sub>                                 | SR | D           | Slew rate on<br>HV power<br>supply                                                                | _                            | _    | _    | 100 | V/ms |

| V <sub>IN</sub>                                      | SR | Р           | I/O input<br>voltage range                                                                        | _                            | 0    | _    | 5.5 | V    |

| I <sub>INJ1</sub>                                    | SR | Т           | Injection<br>current (per<br>pin) without<br>performance<br>degradation <sup>(7)</sup><br>(8) (9) | Digital pins and analog pins | -3.0 | _    | 3.0 | mA   |

| I <sub>INJ2</sub>                                    | SR | D           | Dynamic<br>Injection<br>current (per<br>pin) with<br>performance<br>degradation <sup>(9)</sup>    | Digital pins and analog pins | -10  | _    | 10  | mA   |

Table 5. Operating conditions (continued)

- 1. The ranges in this table are design targets and actual data may vary in the given range.

- Maximum operating frequency is applicable to the cores and platform of the device. See the Clock Chapter in the Microcontroller Reference Manual for more information on the clock limitations for the various IP blocks on the device.

- 3. In order to evaluate the actual difference between ambient and junction temperatures in the application, refer to Section 5.5: Package thermal characteristics.

- 4. Core voltage as measured on device pin to guarantee published silicon performance.

- Core voltage can exceed 1.26 V with the limitations provided in Section 4.2: Absolute maximum ratings, provided that HVD134\_C monitor reset is disabled.

- 1.260 V 1.290 V range allowed periodically for supply with sinusoidal shape and average supply value below or equal to 1.236 V at the given temperature profile.

- 7. Full device lifetime. I/O and analog input specifications are only valid if the injection current on adjacent pins is within these limits. See Section 4.2: Absolute maximum ratings for maximum input current for reliability requirements.

- 8. The I/O pins on the device are clamped to the I/O supply rails for ESD protection. When the voltage of the input pins is above the supply rail, current will be injected through the clamp diode to the supply rails. For external RC network calculation, assume typical 0.3 V drop across the active diode. The diode voltage drop varies with temperature.

- 9. The limits for the sum of all normal and injected currents on all pads within the same supply segment can be found in Section 4.8.3: I/O pad current specifications.

- 10. Positive and negative Dynamic current injection pulses are allowed up to this limit. I/O and ADC specifications are not granted. See the dedicated chapters for the different specification limits. See the Absolute Maximum Ratings table for maximum input current for reliability requirements. Refer to the following pulses definitions: Pulse1 (ISO 7637-2:2011), Pulse 2a(ISO 7637-2:2011 5.6.2), Pulse 3a (ISO 7637-2:2011 5.6.3).

#### 4.3.1 Power domains and power up/down sequencing

The following table shows the constraints and relationships for the different power domains. Supply1 (on rows) can exceed Supply2 (on columns), only if the cell at the given row and column is reporting 'ok'. This limitation is valid during power-up and power-down phases, as well as during normal device operation.

Table 6. Device supply relation during power-up/power-down sequence

|         |                                                        | Supply2            |                           |                                                                          |                        |                        |  |  |

|---------|--------------------------------------------------------|--------------------|---------------------------|--------------------------------------------------------------------------|------------------------|------------------------|--|--|

|         |                                                        | V <sub>DD_LV</sub> | V <sub>DD_HV_IO_ETH</sub> | V <sub>DD_HV_IO_MAIN</sub> V <sub>DD_HV_FLA</sub> V <sub>DD_HV_OSC</sub> | V <sub>DD_HV_ADV</sub> | V <sub>DD_HV_ADR</sub> |  |  |

|         | V <sub>DD_HV_IO_<b>ETH</b></sub>                       | ok                 |                           | not allowed                                                              | ok                     | ok                     |  |  |

| Supply1 | V <sub>DD_HV_IO_MAIN</sub><br>Vdd_hv_fla<br>Vdd_hv_osc | ok                 | ok                        |                                                                          | ok                     | ok                     |  |  |

| Sup     | V <sub>DD_HV_ADV</sub>                                 | ok                 | ok                        | not allowed                                                              |                        | ok                     |  |  |

|         | $V_{DD\_HV\_ADR}$                                      | ok                 | ok                        | not allowed                                                              | not allowed            |                        |  |  |

During power-up, all functional terminals are maintained in a known state as described in the device pinout Microsoft Excel file attached to the IO\_Definition document.

## 4.4 Electrostatic discharge (ESD)

The following table describes the ESD ratings of the device:

All ESD testing are in conformity with CDF-AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits.

• Device failure is defined as: "If after exposure to ESD pulses, the device does not meet the device specification requirements, which include the complete DC parametric and functional testing at room temperature and hot temperature, maximum DC parametric variation within 10 % of maximum specification".

Table 7. ESD ratings

| Parameter                                                       | С | Conditions  | Value | Unit |

|-----------------------------------------------------------------|---|-------------|-------|------|

| ESD for Human Body Model (HBM) <sup>(1)</sup>                   | Т | All pins    | 2000  | V    |

| ESD for field induced Charged Device Model (CDM) <sup>(2)</sup> | Т | All pins    | 500   | V    |

| ESD for field iffduced Charged Device Model (CDM)               | Т | Corner pins | 750   | V    |

<sup>1.</sup> This parameter tested in conformity with ANSI/ESD STM5.1-2007 Electrostatic Discharge Sensitivity Testing.

**577**

<sup>2.</sup> This parameter tested in conformity with ANSI/ESD STM5.3-1990 Charged Device Model - Component Level.

# 4.5 Electromagnetic compatibility characteristics

EMC measurements at IC-level IEC standards are available from STMicroelectronics on request.

DS11701 Rev 4 21/142

# 4.6 Temperature profile

The device is qualified in accordance to AEC-Q100 Grade1 requirements, such as HTOL 1,000 h and HTDR 1,000 hrs,  $T_J$  = 150 °C.

# 4.7 Device consumption

**Table 8. Device consumption**

| O. made at                             |    |   | Danier 8. Device con                                                                                      | <u>.</u>                |     | Value <sup>(1)</sup> |      | 11    |

|----------------------------------------|----|---|-----------------------------------------------------------------------------------------------------------|-------------------------|-----|----------------------|------|-------|

| Symbol                                 |    | С | Parameter                                                                                                 | Conditions              | Min | Тур                  | Max  | Unit  |

|                                        |    | С |                                                                                                           | T <sub>J</sub> = 40 °C  | _   | _                    | 7    |       |

|                                        |    | D |                                                                                                           | T <sub>J</sub> = 25 °C  | _   | 1.5                  | 5    |       |

| (2),(3)                                | СС | D | Leakage current on the                                                                                    | T <sub>J</sub> = 55 °C  | _   | _                    | 10   | mA    |

| I <sub>DD_LKG</sub> <sup>(2),(3)</sup> |    | D | V <sub>DD_LV</sub> supply                                                                                 | T <sub>J</sub> = 95 °C  | _   | _                    | 25   | IIIA  |

|                                        |    | D |                                                                                                           | T <sub>J</sub> = 120 °C | _   | _                    | 45   |       |

|                                        |    | Р |                                                                                                           | T <sub>J</sub> = 150 °C | _   | _                    | 90   |       |

| I <sub>DD_LV</sub> <sup>(3)</sup>      | СС | Р | Dynamic current on<br>the V <sub>DD_LV</sub> supply,<br>very high consumption<br>profile <sup>(4)</sup>   | _                       | _   | _                    | 125  | mA    |

| I <sub>DD_HV</sub>                     | СС | Р | Total current on the V <sub>DD_HV</sub> supply <sup>(4)</sup>                                             | $f_{MAX}$               | _   | _                    | 55   | mA    |

| I <sub>DD_LV_GW</sub>                  | СС | Т | Dynamic current on<br>the V <sub>DD_LV</sub> supply,<br>gateway profile <sup>(5)</sup>                    | _                       | _   | _                    | 98   | mA    |

| IDD_HV_GW                              | СС | Т | Dynamic current on<br>the V <sub>DD_HV</sub> supply,<br>gateway profile <sup>(5)</sup>                    | _                       | _   | _                    | 22   | mA    |

| I <sub>DD_LV_</sub> BCM                | СС | Т | Dynamic current on<br>the V <sub>DD_LV</sub> supply,<br>body profile <sup>(6)</sup>                       | _                       | _   | _                    | 79   | mA    |

| I <sub>DD_HV_BCM</sub>                 | СС | Т | Dynamic current on<br>the V <sub>DD_HV</sub> supply,<br>body profile <sup>(6)</sup>                       | _                       | _   | _                    | 29   | mA    |

| I <sub>DD_HSM_AC</sub>                 | СС | Т | HSM platform dynamic operating current <sup>(7)</sup>                                                     | f <sub>MAX</sub> /2     | _   | _                    | 15   | mA    |

| I <sub>DDHALT</sub> <sup>(8)</sup>     | СС | Т | Dynamic current on<br>the V <sub>DD_LV</sub> supply<br>+Total current on the<br>V <sub>DD_HV</sub> supply | _                       | _   | 54                   | 63   | mA    |

| I <sub>DDSTOP</sub> <sup>(9)</sup>     | СС | Т | Dynamic current on<br>the V <sub>DD_LV</sub> supply<br>+Total current on the<br>V <sub>DD_HV</sub> supply | _                       | _   | 18                   | 24   | mA    |

|                                        |    | D |                                                                                                           | T <sub>J</sub> = 25 °C  | _   | 55                   | 120  |       |

|                                        |    | С | Total standby mode                                                                                        | T <sub>J</sub> = 40 °C  |     | _                    | 180  | μΑ    |

| I <sub>DDSTBY8</sub>                   | СС | D | current on V <sub>DD_LV</sub> and V <sub>DD_HV</sub> supply, 8 KB                                         | T <sub>J</sub> = 55 °C  |     | _                    | 280  |       |

|                                        |    | D | V <sub>DD_HV</sub> supply, 8 KB<br>RAM <sup>(10)</sup>                                                    | T <sub>J</sub> = 120 °C | _   | 0.8                  | 1.65 | mA    |

|                                        |    | Р |                                                                                                           | T <sub>J</sub> = 150 °C | _   | 1.8                  | 3.8  | 111/4 |

SPC584Bx Electrical characteristics

| abi | e 6. Device consump | uon ( | Contin | uea) |  |

|-----|---------------------|-------|--------|------|--|

|     |                     |       |        |      |  |

| _   |                     |       |        |      |  |

| Symbol                 |    | С | Parameter                                                                                                                 | Canditions              |     | Value <sup>(1)</sup> | )   | Unit |

|------------------------|----|---|---------------------------------------------------------------------------------------------------------------------------|-------------------------|-----|----------------------|-----|------|

| Symbol                 |    |   | Parameter                                                                                                                 | Conditions              | Min | Тур                  | Max | Unit |

|                        |    | D | Total standby mode                                                                                                        | T <sub>J</sub> = 25 °C  | _   | 60                   | 130 |      |

|                        |    | С |                                                                                                                           | T <sub>J</sub> = 40 °C  | _   | _                    | 200 | μA   |

| I <sub>DDSTBY32</sub>  | СС | D | current on V <sub>DD_LV</sub> and V <sub>DD_UV</sub> supply. 32 KB                                                        | T <sub>J</sub> = 55 °C  | _   | _                    | 300 |      |

|                        |    | D | V <sub>DD_HV</sub> supply, 32 KB<br>RAM <sup>(10)</sup>                                                                   | T <sub>J</sub> = 120 °C | _   | _                    | 1.8 | mA   |

|                        |    | Р |                                                                                                                           | T <sub>J</sub> = 150 °C | _   | _                    | 4.1 | IIIA |

|                        |    | D |                                                                                                                           | T <sub>J</sub> = 25 °C  | _   | 90                   | 160 | μA   |

|                        |    | С | Total standby mode<br>current on V <sub>DD_LV</sub> and<br>V <sub>DD_HV</sub> supply,<br>128 KB RAM <sup>(10)</sup>       | $T_J = 40  ^{\circ}C$   | _   | _                    | 250 | μΑ   |

| I <sub>DDSTBY128</sub> | СС | D |                                                                                                                           | $T_J = 55 ^{\circ}C$    | _   | _                    | 370 | μA   |

|                        |    | D |                                                                                                                           | T <sub>J</sub> = 120 °C | _   | 1.2                  | 2.2 | mA   |

|                        |    | Р |                                                                                                                           | T <sub>J</sub> = 150 °C | _   | 2.8                  | 5.0 | IIIA |

| I <sub>DDSSWU1</sub>   | CC | D | SSWU running over all<br>STANDBY period with<br>OPC/TU commands<br>execution and keeping<br>ADC off <sup>(11)</sup>       | T <sub>J</sub> = 40 °C  | _   | 1.0                  | 3.5 | mA   |

| I <sub>DDSSWU2</sub>   | СС | D | SSWU running over all<br>STANDBY period with<br>OPC/TU/ADC<br>commands execution<br>and keeping ADC<br>on <sup>(12)</sup> | T <sub>J</sub> = 40 °C  | _   | 3.5                  | 5.0 | mA   |

- The ranges in this table are design targets and actual data may vary in the given range.

- The leakage considered is the sum of core logic and RAM memories. The contribution of analog modules is not considered, and they are computed in the dynamic  $I_{DD\ LV}$  and  $I_{DD\_HV}$  parameters.

- l<sub>DD\_LKG</sub> (leakage current) and l<sub>DD\_LV</sub> (dynamic current) are reported as separate parameters, to give an indication of the consumption contributors. The tests used in validation, characterization and production are verifying that the total consumption (leakage+dynamic) is lower or equal to the sum of the maximum values provided (I<sub>DD\_LKG</sub> + I<sub>DD\_LV</sub>). The two parameters, measured separately, may exceed the maximum reported for each, depending on the operative conditions and the software profile used.

- Use case: 1 x e200Z4 @120 MHz, HSM @60 MHz, all IPs clock enabled, Flash access with prefetch disabled, Flash consumption includes parallel read and program/erase, all SARADC in continuous conversion, DMA continuously triggered by ADC conversion, 2 DSPI / 8 CAN / 2 LINFlex transmitting, RTC and STM running, 1 x EMIOS running (4 channels in OPWMT mode), FIRC, SIRC, FXOSC, PLL0-1 running. The switching activity estimated for dynamic consumption does not include I/O toggling, which is highly dependent on the application. Details of the software configuration are available separately. The total device consumption is  $I_{\rm DD\_LV} + I_{\rm DD\_HV} + I_{\rm DD\_LKG}$  for the selected temperature.

- 5. Gateway use case: One core running at 120 MHz, HSM 40 MHz, DMA, PLL, FLASH read only 25%, 8xCAN, 1xSARADC.

- BCM use case: One Core running at 80 MHz, HSM 40 MHz, DMA, PLL, FLASH read only 25%, 1xCAN, 3xSARADC.

- Dynamic consumption of the HSM module, including the dedicated memories, during the execution of Electronic Code Book crypto algorithm on 1 block of 16 byte of shared RAM.

- Flash in Low Power. Sysclk at 120 MHz, HSM 60 MHz, PLL0\_PHI at 400 MHz, XTAL at 40 MHz, FIRC 16 MHz ON, RCOSC1M off. FlexCAN: instances: 0, 1, 2, 3, 4, 5, 6, 7 ON (configured but no reception or transmission), Ethernet ON (configured but no reception or transmission), ADC ON (continuously converting). All others IPs clock-gated.

- Sysclk = RC16 MHz, RC16 MHz ON, RC1 MHz ON, PLL OFF. All possible peripherals off and clock gated. Flash in power down mode.

- 10. STANDBY mode: device configured for minimum consumption, RC16 MHz off, RC1 MHz on.

- 11. SSWU1 mode adder: FIRC = ON, SSWU clocked at 8 MHz and running over all STANDBY period, ADC off. The total standby consumption can be obtained by adding this parameter to the IDDSTBY parameter for the selected memory size and temperature.

- 12. SSWU2 mode adder: FIRC = ON, SSWU clocked at 8 MHz and running over all STANDBY period, ADC on in continuous conversion. The total standby consumption can be obtained by adding this parameter to the IDDSTBY parameter for the selected memory size and temperature.

DS11701 Rev 4 25/142

## 4.8 I/O pad specification

The following table describes the different pad type configurations.

Table 9. I/O pad specification descriptions

| Pad type                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Weak configuration         | Provides a good compromise between transition time and low electromagnetic emission.                                                                                                                                                                                                                                                                                                                                                                                                             |

| Medium configuration       | Provides transition fast enough for the serial communication channels with controlled current to reduce electromagnetic emission.                                                                                                                                                                                                                                                                                                                                                                |

| Strong configuration       | Provides fast transition speed; used for fast interface.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Very strong configuration  | Provides maximum speed and controlled symmetric behavior for rise and fall transition.  Used for fast interface including Ethernet interface requiring fine control of rising/falling edge jitter.                                                                                                                                                                                                                                                                                               |

| Differential configuration | A few pads provide differential capability providing very fast interface together with good EMC performances.                                                                                                                                                                                                                                                                                                                                                                                    |

| Input only pads            | These low input leakage pads are associated with the ADC channels.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Standby pads               | These pads (LP pads) are active during STANDBY. They are configured in CMOS level logic and this configuration cannot be changed. Moreover, when the device enters the STANDBY mode, the pad-keeper feature is activated for LP pads. It means that:  – if the pad voltage level is above the pad keeper high threshold, a weak pull-up resistor is automatically enabled  – if the pad voltage level is below the pad keeper low threshold, a weak pull-down resistor is automatically enabled. |

|                            | For the pad-keeper high/low thresholds, consider(VDD_HV_IO_MAIN / 2) +/-20 %.                                                                                                                                                                                                                                                                                                                                                                                                                    |

Note:

Each I/O pin on the device supports specific drive configurations. See the signal description table in the device reference manual for the available drive configurations for each I/O pin. PMC\_DIG\_VSIO register has to be configured to select the voltage level (3.3 V or 5.0 V) for each IO segment.

Logic level is configurable in running mode while it is CMOS not-configurable in STANDBY for LP (low power) pads, so if a LP pad is used to wakeup from STANDBY, it should be configured as CMOS also in running mode in order to prevent device wrong behavior in STANDBY.

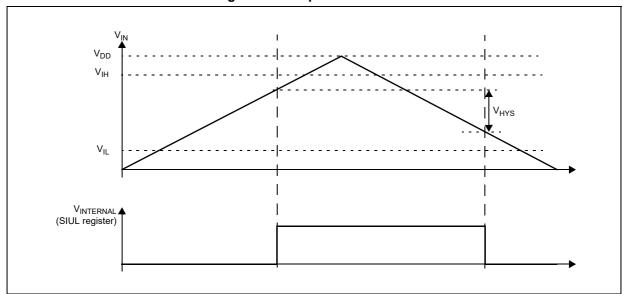

#### 4.8.1 I/O input DC characteristics

The following table provides input DC electrical characteristics, as described in Figure 3.

Figure 3. I/O input electrical characteristics

Table 10. I/O input electrical characteristics

| Symbol               | ı    | С | Parameter                | Conditions                                   |                        | Value |                                | Unit  |

|----------------------|------|---|--------------------------|----------------------------------------------|------------------------|-------|--------------------------------|-------|

| Symbol               |      | ٥ | Parameter                | Conditions                                   | Min                    | Тур   | Max                            | Oilit |

|                      |      |   |                          | TTL                                          |                        |       |                                |       |

| V <sub>ihttl</sub>   | SR   | Р | Input high level<br>TTL  | _                                            | 2                      | _     | V <sub>DD_HV_IO</sub><br>+ 0.3 | V     |

| V <sub>ilttl</sub>   | SR   | Р | Input low level<br>TTL   | _                                            | -0.3                   | _     | 0.8                            | V     |

| V <sub>hysttl</sub>  | СС   | С | Input hysteresis<br>TTL  | _                                            | 0.3                    | _     | _                              | V     |

|                      | смоѕ |   |                          |                                              |                        |       |                                |       |

| V <sub>ihcmos</sub>  | SR   | Р | Input high level CMOS    | _                                            | 0.65 * V <sub>DD</sub> | _     | V <sub>DD_HV_IO</sub><br>+ 0.3 | V     |

| V <sub>ilcmos</sub>  | SR   | Р | Input low level CMOS     | _                                            | -0.3                   | _     | 0.35 * V <sub>DD</sub>         | V     |

| V <sub>hyscmos</sub> | СС   | С | Input hysteresis<br>CMOS | _                                            | 0.10 * V <sub>DD</sub> | _     | _                              | V     |

|                      |      |   |                          | COMMON                                       |                        |       |                                |       |

| I <sub>LKG</sub>     | СС   | Р | Pad input<br>leakage     | INPUT-ONLY pads<br>T <sub>J</sub> = 150 °C   | _                      | _     | 200                            | nA    |

| I <sub>LKG</sub>     | СС   | Р | Pad input<br>leakage     | STRONG pads<br>T <sub>J</sub> = 150 °C       | _                      | _     | 1,000                          | nA    |

| I <sub>LKG</sub>     | СС   | Р | Pad input<br>leakage     | VERY STRONG pads,<br>T <sub>J</sub> = 150 °C | _                      | _     | 1,000                          | nA    |

Table 10. I/O input electrical characteristics (continued)

| Cymab a          | Symbol C Para |   | Daramatar                                                      | Barrana da un Garralidia na                           | Value |     |     | linis |

|------------------|---------------|---|----------------------------------------------------------------|-------------------------------------------------------|-------|-----|-----|-------|

| Symbo            | ı             |   | Parameter                                                      | Conditions                                            | Min   | Тур | Max | Unit  |

| C <sub>P1</sub>  | СС            | D | Pad<br>capacitance                                             | _                                                     | _     | _   | 10  | pF    |

| $V_{drift}$      | СС            | D | Input V <sub>il</sub> /V <sub>ih</sub><br>temperature<br>drift | In a 1 ms period, with a temperature variation <30 °C | _     | _   | 100 | mV    |

| $W_{FI}$         | SR            | С | Wakeup input filtered pulse <sup>(1)</sup>                     | _                                                     | _     | _   | 20  | ns    |

| W <sub>NFI</sub> | SR            | С | Wakeup input<br>not filtered<br>pulse <sup>(1)</sup>           | _                                                     | 400   | _   | _   | ns    |

In the range from W<sub>FI</sub> (max) to W<sub>NFI</sub> (min), pulses can be filtered or not filtered, according to operating temperature and voltage. Refer to the device pinout IO definition excel file for the list of pins supporting the wakeup filter feature.

Table 11. I/O pull-up/pull-down electrical characteristics

| Symbol           | ı          | С | Parameter                        | Conditions                                                       |     | Value |     | Unit  |

|------------------|------------|---|----------------------------------|------------------------------------------------------------------|-----|-------|-----|-------|

| Syllibol         | <b>5</b> , |   | Farameter                        | Conditions                                                       | Min | Тур   | Max | Oilit |

|                  |            | Т | Weak pull-up                     | $V_{IN} = 1.1 V^{(1)}$                                           |     | _     | 130 |       |

| I <sub>WPU</sub> | CC         | Р | current<br>absolute value        | $V_{IN} = 0.69 * V_{DD\_HV\_IO}^{(2)}$                           | 15  |       |     | μА    |

| R <sub>WPU</sub> | СС         | D | Weak Pull-up<br>resistance       | V <sub>DD_HV_IO</sub> = 5.0 V ± 10%                              | 33  | _     | 93  | ΚΩ    |

| R <sub>WPU</sub> | СС         | D | Weak Pull-up<br>resistance       | V <sub>DD_HV_IO</sub> = 3.3 V ± 10%                              | 19  | _     | 62  | ΚΩ    |

|                  | 00         | Т | Weak pull-                       | V <sub>IN</sub> = 0.69 *<br>V <sub>DD_HV_IO</sub> <sup>(1)</sup> | _   | _     | 130 |       |

| I <sub>WPD</sub> | CC         | Р | down current absolute value      | $V_{IN} = 0.9 V^{(2)}$                                           | 15  | _     | _   | μΑ    |

| R <sub>WPD</sub> | СС         | D | Weak Pull-<br>down<br>resistance | V <sub>DD_HV_IO</sub> = 5.0 V ± 10%                              | 29  | _     | 60  | ΚΩ    |

| R <sub>WPD</sub> | СС         | D | Weak Pull-<br>down<br>resistance | V <sub>DD_HV_IO</sub> = 3.3 V ± 10%                              | 19  | _     | 60  | ΚΩ    |

<sup>1.</sup> Maximum current when forcing a change in the pin level opposite to the pull configuration.

Note:

When the device enters into standby mode, the LP pads have the input buffer switched-on. As a consequence, if the pad input voltage VIN is  $V_{SS} < V_{IN} < V_{DD\_HV}$ , an additional consumption can be measured in the VDD\_HV domain. The highest consumption can be seen around mid-range (VIN ~=VDD\_HV/2), 2-3 mA depending on process, voltage and temperature.

<sup>2.</sup> Minimum current when keeping the same pin level state than the pull configuration.

This situation may occur if the PAD is used as a ADC input channel, and  $V_{SS} < V_{IN} < V_{DD\_HV}$ . The applications should ensure that LP pads are always set to VDD\_HV or VSS, to avoid the extra consumption. Refer to the device pinout IO definition excel file to identify the low-power pads which also have an ADC function.

#### 4.8.2 I/O output DC characteristics

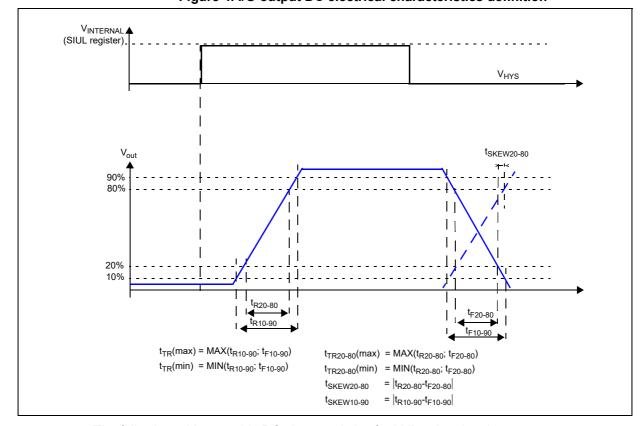

Figure 4 provides description of output DC electrical characteristics.

Figure 4. I/O output DC electrical characteristics definition

The following tables provide DC characteristics for bidirectional pads:

- Table 12 provides output driver characteristics for I/O pads when in WEAK/SLOW configuration.

- Table 13 provides output driver characteristics for I/O pads when in MEDIUM configuration.

- Table 14 provides output driver characteristics for I/O pads when in STRONG/FAST configuration.

- *Table 15* provides output driver characteristics for I/O pads when in VERY STRONG/VERY FAST configuration.

Note: 10 %/90 % is the default condition for any parameter if not explicitly mentioned differently.

577

Table 12. WEAK/SLOW I/O output characteristics

| Symbol               |                       | С | Parameter                                               | Conditions                                                                           |                     | Value                                                                          |                     | Unit  |   |     |

|----------------------|-----------------------|---|---------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------|---------------------|-------|---|-----|

| Symbol               |                       | ٥ | Parameter                                               | Conditions                                                                           | Min                 | Тур                                                                            | Max                 | Offic |   |     |

| V <sub>ol_W</sub>    | СС                    | D | Output low<br>voltage for Weak<br>type PADs             | $I_{ol}$ = 0.5 mA<br>$V_{DD}$ = 5.0 V ± 10 %<br>$V_{DD}$ = 3.3 V ± 10 %              | _                   | _                                                                              | 0.1*V <sub>DD</sub> | V     |   |     |

| V <sub>oh_W</sub>    | СС                    | D | Output high<br>voltage for Weak<br>type PADs            | Ioh = 0.5 mA<br>V <sub>DD</sub> = 5.0 V ± 10 %<br>V <sub>DD</sub> = 3.3 V ± 10 %     | 0.9*V <sub>DD</sub> | _                                                                              | _                   | V     |   |     |

|                      |                       | _ | Output                                                  | V <sub>DD</sub> = 5.0 V ± 10 %                                                       | 380                 | _                                                                              | 1040                |       |   |     |

| R <sub>_W</sub>      | CC                    | Р | impedance for<br>Weak type PADs                         | V <sub>DD</sub> = 3.3 V ± 10 %                                                       | 250                 | _                                                                              | 700                 | Ω     |   |     |

| _                    | 00                    | H | Maximum output frequency for                            | CL = 25 pF<br>V <sub>DD</sub> = 5.0 V ± 10 %<br>V <sub>DD</sub> = 3.3 V ± 10 %       | _                   | _                                                                              | 2                   | MHz   |   |     |

| Fmax_W               | F <sub>max_W</sub> CC | 1 | Т                                                       |                                                                                      | Weak type PADs      | CL = 50 pF<br>V <sub>DD</sub> = 5.0 V ± 10 %<br>V <sub>DD</sub> = 3.3 V ± 10 % | _                   | _     | 1 | MHz |

| t <sub>TR_W</sub>    | СС                    | Т | Transition time output pin weak                         | CL = 25 pF<br>V <sub>DD</sub> = 5.0 V +<br>10 %<br>V <sub>DD</sub> = 3.3 V +<br>10 % | 25                  | _                                                                              | 120                 | ns    |   |     |

|                      |                       |   | configuration,<br>10%-90%                               | CL = 50 pF<br>V <sub>DD</sub> = 5.0 V ± 10 %<br>V <sub>DD</sub> = 3.3 V ± 10 %       | 50                  | _                                                                              | 240                 | ns    |   |     |

| t <sub>SKEW_W</sub>  | СС                    | Т | Difference<br>between rise<br>and fall time,<br>90%-10% | _                                                                                    | _                   | _                                                                              | 25                  | %     |   |     |

| I <sub>DCMAX_W</sub> | СС                    | D | Maximum DC current                                      | $V_{DD}$ = 5.0 V ± 10 %<br>$V_{DD}$ = 3.3 V ± 10 %                                   | _                   | _                                                                              | 0.5                 | mA    |   |     |

Table 13. MEDIUM I/O output characteristics

| Cymbal            | mbol C Paramete |   | Davamatav                                         | 0                                                                                          |                     | Unit |                     |      |

|-------------------|-----------------|---|---------------------------------------------------|--------------------------------------------------------------------------------------------|---------------------|------|---------------------|------|

| Symbol            |                 | C | Parameter                                         | Conditions                                                                                 | Min                 | Тур  | Max                 | Unit |

| V <sub>ol_M</sub> | СС              | D | Output low<br>voltage for<br>Medium type<br>PADs  | I <sub>ol</sub> = 2.0 mA<br>V <sub>DD</sub> =5.0 V ± 10 %<br>V <sub>DD</sub> =3.3 V ± 10 % | _                   | _    | 0.1*V <sub>DD</sub> | V    |

| V <sub>oh_M</sub> | СС              | D | Output high<br>voltage for<br>Medium type<br>PADs | $I_{oh}$ =2.0 mA<br>$V_{DD}$ = 5.0 V ± 10 %<br>$V_{DD}$ = 3.3 V ± 10 %                     | 0.9*V <sub>DD</sub> | _    | _                   | V    |

Table 13. MEDIUM I/O output characteristics (continued)

| Symbol               |    | С | Parameter                                               | Conditions                                                                              |     | Value |     | Unit  |

|----------------------|----|---|---------------------------------------------------------|-----------------------------------------------------------------------------------------|-----|-------|-----|-------|

| Syllibol             |    |   | Parameter                                               | Conditions                                                                              | Min | Тур   | Max | Oilit |

|                      |    |   | Output                                                  | V <sub>DD</sub> = 5.0 V ± 10 %                                                          | 90  | _     | 260 |       |

| R <sub>_M</sub>      | СС | Р | impedance for<br>Medium type<br>PADs                    | V <sub>DD</sub> = 3.3 V ± 10 %                                                          | 60  | _     | 170 | Ω     |

| E                    | СС | Т | Maximum output frequency for                            | CL = 25  pF<br>$V_{DD} = 5.0 \text{ V} \pm 10 \%$<br>$V_{DD} = 3.3 \text{ V} \pm 10 \%$ | _   | _     | 12  | MHz   |

| F <sub>max_M</sub>   |    | ' | Medium type<br>PADs                                     | CL = 50 pF<br>V <sub>DD</sub> = 5.0 V ± 10 %<br>V <sub>DD</sub> = 3.3 V ± 10 %          | _   | _     | 6   | MHz   |

|                      |    | Т | Transition time output pin                              | CL = 25 pF<br>V <sub>DD</sub> = 5.0 V ± 10 %<br>V <sub>DD</sub> = 3.3 V ± 10 %          | 8   | _     | 30  | ns    |

| t <sub>TR_M</sub>    | CC | ' | MEDIUM<br>configuration,<br>10%-90%                     | CL = 50 pF<br>V <sub>DD</sub> = 5.0 V ± 10 %<br>V <sub>DD</sub> = 3.3 V ± 10 %          | 12  | _     | 60  | ns    |

| t <sub>SKEW_M</sub>  | СС | Т | Difference<br>between rise<br>and fall time,<br>90%-10% | _                                                                                       | _   | _     | 25  | %     |

| I <sub>DCMAX_M</sub> | СС | D | Maximum DC current                                      | V <sub>DD</sub> = 5.0 V ± 10 %<br>V <sub>DD</sub> = 3.3 V ± 10 %                        | _   | _     | 2   | mA    |

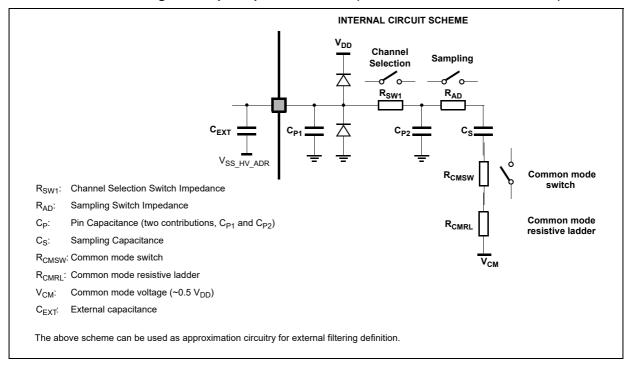

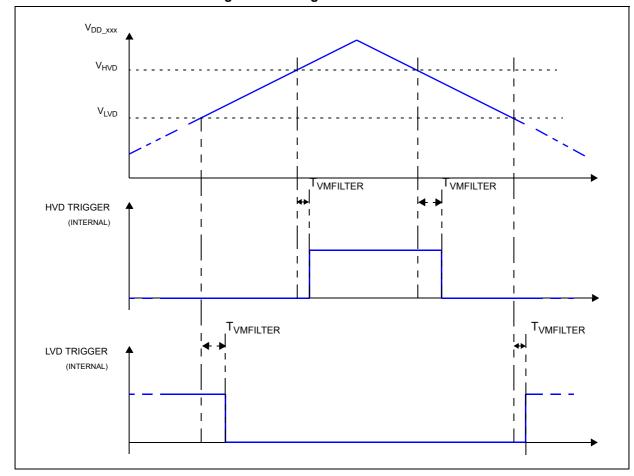

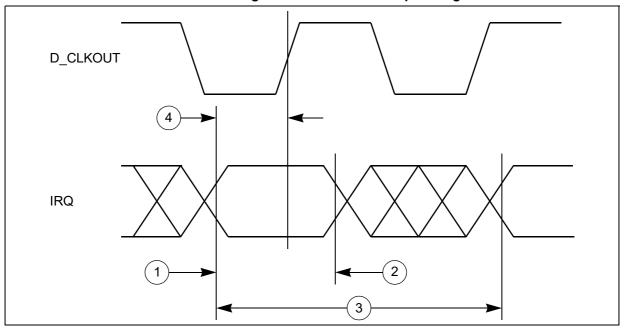

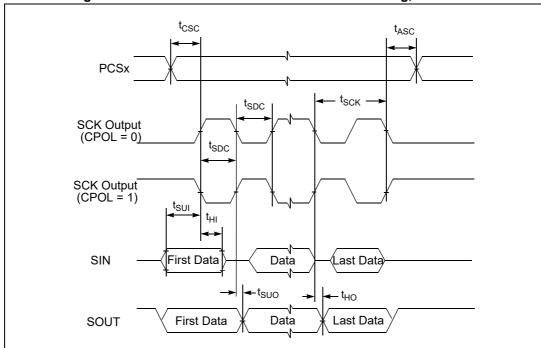

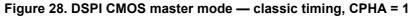

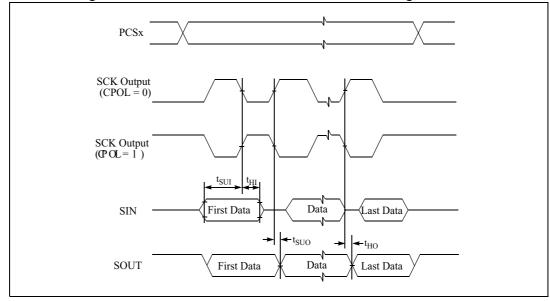

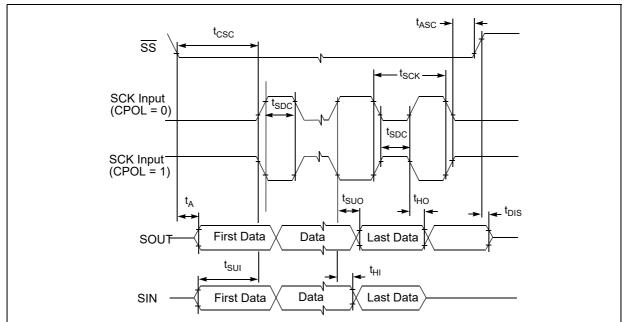

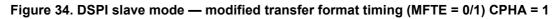

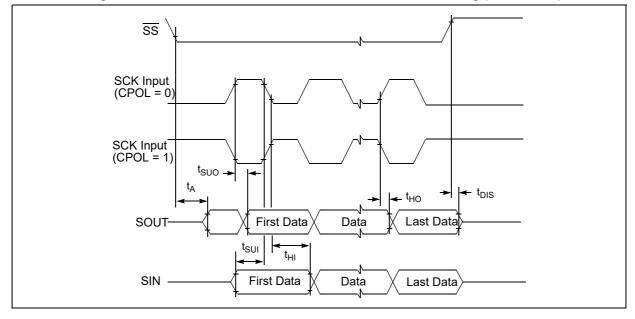

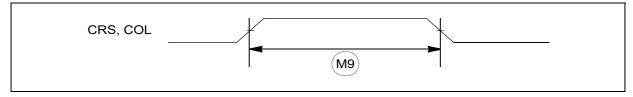

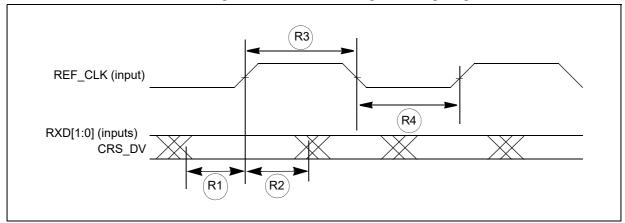

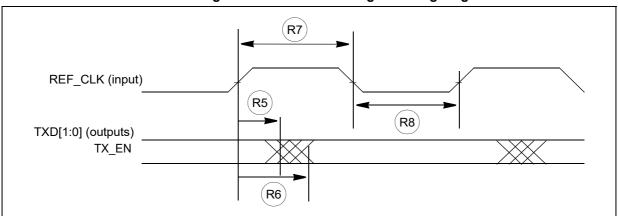

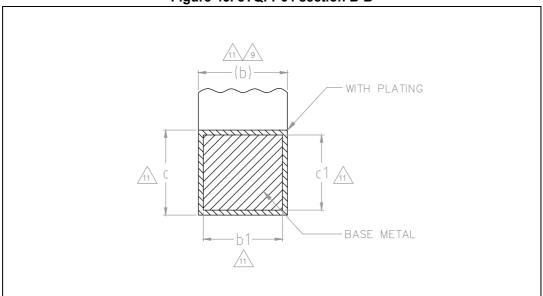

Table 14. STRONG/FAST I/O output characteristics