# Monolithic buck converter for DDR memory termination

Datasheet - production data

QFN20 3.5 x 4.0 mm

## **Features**

- Integrated MOSFETs for high efficiency

- · Current COT architecture

- 1 V to 3.5 V input voltage (V<sub>IN</sub>)

- 5.0 V supply voltage (V<sub>CC</sub>)

- Constant frequency mode

- 1% output voltage accuracy

- Two programmable switching frequencies (0.6 MHz or 1 MHz)

- ADJ output voltage from 0.5 V to 2 V

- Embedded bootstrap diode

- OV/UV/OC and overtemperature protection

- Soft-off with integrated discharge resistor

- External tracking

- Power Good output

- QFN20 3.5 x 4.0 mm compact package

## **Applications**

- Memory termination regulator for DDR3, DDR4 and low power DDR3/DDR4

- Notebook/desktop/server

- Low voltage application for 1 V to 3.5 V input rails

## Description

The PM8908 is a high efficiency monolithic stepdown switching regulator designed mainly for the DDR termination.

The IC operates from 1 V to 3.5 V input voltage  $(V_{IN})$ .

The device uses a COT control loop that provides very good performances in terms of load and line transients. The current sense is internally thermally compensated for optimum precision.

The output voltage is adjusted from 0.5 V to 2 V with ± 1% accuracy overtemperature variations.

The PM8908 also provides external tracking support.

The PM8908 provides positive and negative overcurrent protection as well as over/undervoltage and overtemperature protection. PGOOD output easily provides real-time information on the output voltage.

The PM8908 is available in a QFN20 3.5 x 4.0 mm package.

Table 1. Device summary

| Order code | Package              | Packaging     |

|------------|----------------------|---------------|

| PM8908TR   | QFN20 (3.5 x 4.0 mm) | Tape and reel |

# **Contents**

| 1 | Typi  | Typical application circuit and block diagram 4 |  |  |  |

|---|-------|-------------------------------------------------|--|--|--|

|   | 1.1   | Application circuit                             |  |  |  |

|   | 1.2   | Block diagram                                   |  |  |  |

| 2 | Pin o | description and connection diagrams 6           |  |  |  |

|   | Pin d | escription 6                                    |  |  |  |

| 3 | Ther  | mal data 8                                      |  |  |  |

| 4 | Elec  | trical specifications 9                         |  |  |  |

|   | 4.1   | Absolute maximum ratings                        |  |  |  |

|   | 4.2   | Electrical characteristics                      |  |  |  |

| 5 | Devi  | ce description13                                |  |  |  |

|   | 5.1   | Power section                                   |  |  |  |

|   | 5.2   | Device configuration                            |  |  |  |

|   | 5.3   | Startup and shutdown management                 |  |  |  |

|   |       | Soft-off                                        |  |  |  |

|   | 5.4   | Output voltage monitoring and protection        |  |  |  |

|   |       | 5.4.1 Overvoltage protection                    |  |  |  |

|   |       | 5.4.2 Undervoltage protection                   |  |  |  |

|   |       | 5.4.3 Power Good (PGOOD)                        |  |  |  |

|   |       | 5.4.4 Overcurrent protection                    |  |  |  |

|   |       | 5.4.5 Overtemperature protection                |  |  |  |

| 6 | App   | ication information19                           |  |  |  |

|   | 6.1   | Output voltage setting                          |  |  |  |

|   | 6.2   | Droop setting                                   |  |  |  |

|   | 6.3   | Non-droop setting                               |  |  |  |

|   | 6.4   | Inductor design                                 |  |  |  |

|   | 6.5   | Output capacitors                               |  |  |  |

|   | 6.6   | Input capacitors                                |  |  |  |

|   | 6.7   | Compensation network                            |  |  |  |

|   |       |                                                 |  |  |  |

| PM8908 |     |                           | Contents |

|--------|-----|---------------------------|----------|

| 7      | Pac | kage information          | 23       |

|        | 7.1 | QFN20 package information | 24       |

| Q      | Roy | ision history             | 27       |

# 1 Typical application circuit and block diagram

# 1.1 Application circuit

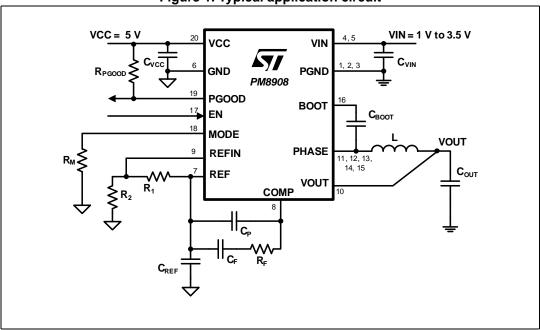

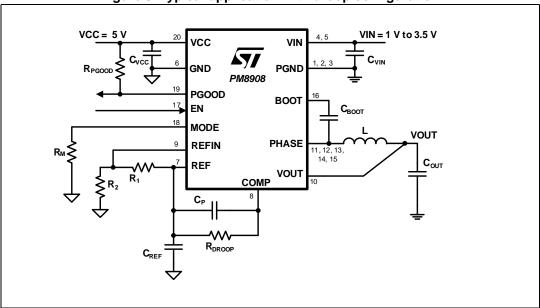

Figure 1. Typical application circuit

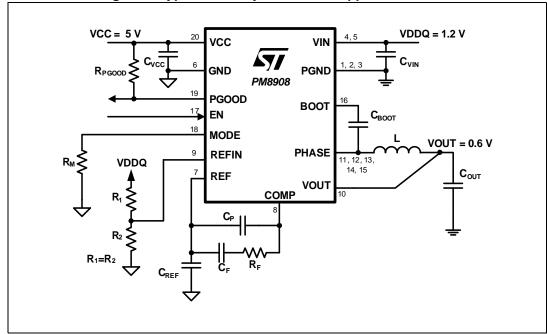

Figure 2. Typical memory termination application circuit

577

# 1.2 Block diagram

Figure 3. Block diagram

# 2 Pin description and connection diagrams

MODE VCC 20 19 18 17 16 PGND 15 PHASE 14 PHASE PGND **PM8908** 13 PGND PHASE VIN 12 PHASE 5 VIN 11 PHASE 6 7 8 9 10 COMP REFIN

Figure 4. Pin connection (top view)

## Pin description

Table 2. Pin description

| Pin |       | Function                                                                                                                                         |  |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|

| No. | Name  | Function                                                                                                                                         |  |

| 1   |       |                                                                                                                                                  |  |

| 2   | PGND  | Power ground connection, connected to the embedded low-side MOSFET source. Connect to the PGND PCB plane. See <i>Figure 1</i> .                  |  |

| 3   |       | ·                                                                                                                                                |  |

| 4   | \     | Power input voltage, connected to the embedded high-side MOS drain.                                                                              |  |

| 5   | VIN   | Supply range is from 1 V to 3.5 V. Bypass VIN pins to PGND pins close to the IC package with high quality MLCC capacitors. See <i>Figure 1</i> . |  |

| 6   | GND   | All the internal references are referred to this pin. Connect to the PCB signal ground.                                                          |  |

| 7   | REF   | Reference output. Connect a 1 µF MLCC capacitor to GND. See <i>Figure 1</i> .                                                                    |  |

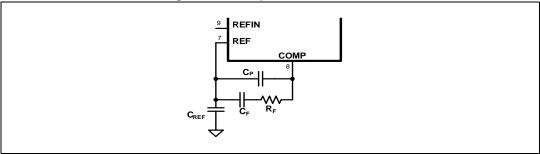

| 8   | COMP  | Error amplifier output. Connect with $R_F$ - $C_F$ to the REF pin for loop compensation. See <i>Figure 1</i> .                                   |  |

| 9   | REFIN | Reference input. Apply a voltage between 0.5 to 2.0 V. Filter with at least 0.01 μF MLCC capacitors to GND.                                      |  |

| 10  | VOUT  | Output voltage sense.                                                                                                                            |  |

Table 2. Pin description (continued)

| Pin |             | Function                                                                                                                                                                                                              |  |  |  |  |

|-----|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| No. | Name        | runction                                                                                                                                                                                                              |  |  |  |  |

| 11  |             |                                                                                                                                                                                                                       |  |  |  |  |

| 12  |             | Output inductor connection.                                                                                                                                                                                           |  |  |  |  |

| 13  | PHASE       | The pins are connected to the embedded MOSFETs (high-side source and                                                                                                                                                  |  |  |  |  |

| 14  |             | low-side drain). Connect directly to the output inductor. See Figure 1.                                                                                                                                               |  |  |  |  |

| 15  |             |                                                                                                                                                                                                                       |  |  |  |  |

| 16  | воот        | Bootstrap pin. It provides power supply for the floating high-side MOS driver. Connect with 0.1 µF to PHASE. See <i>Figure 1</i> .                                                                                    |  |  |  |  |

| 17  | EN          | Enable.                                                                                                                                                                                                               |  |  |  |  |

| 18  | MODE        | Switching frequency and the OCL programming pin. See <i>Table 6 on page 14</i> . This pin must not be left floating.                                                                                                  |  |  |  |  |

| 19  | PGOOD       | Power Good pin. Open drain output set free after SS has finished and pulled low when V <sub>OUT</sub> is out of the PGOOD window or any protection is triggered. Pull up to VCC, if not used it can be left floating. |  |  |  |  |

| 20  | VCC         | Device power supply. Operative voltage is 5.0 V. Filter with at least 1 µF MLCC vs. GND.                                                                                                                              |  |  |  |  |

|     | Thermal pad | The thermal pad of the device. Connect to the PCB ground plane with multiple VIAS.                                                                                                                                    |  |  |  |  |

Thermal data PM8908

# 3 Thermal data

Table 3. Thermal data

| Symbol            | Parameter                                                                       | Value      | Unit |

|-------------------|---------------------------------------------------------------------------------|------------|------|

| R <sub>thJA</sub> | Thermal resistance junction to ambient (Device soldered on demonstration board) | 40         | °C/W |

| T <sub>MAX</sub>  | Maximum junction temperature                                                    | 150        | °C   |

| T <sub>STG</sub>  | Storage temperature range                                                       | -55 to 150 | °C   |

| TJ                | Junction temperature range                                                      | -40 to 150 | °C   |

# 4 Electrical specifications

## 4.1 Absolute maximum ratings

Table 4. Absolute maximum ratings

| Symbol                 | Parameter               | Value <sup>(1)</sup>        | Unit |

|------------------------|-------------------------|-----------------------------|------|

| VCC                    | To PGND, GND            | -0.3 to 7                   | V    |

| VIN                    | To PGND, GND            | -0.3 to 4                   | V    |

|                        | To PGND, GND            | -0.3 to 11                  | V    |

| BOOT                   | To PGND, GND, t < 10 ns | -0.3 to 12.2 <sup>(2)</sup> | V    |

|                        | To PHASE                | -0.3 to 7                   | V    |

| PHASE                  | To PGND, GND            | -2 to 4                     | V    |

| PHASE                  | To PGND, GND, t < 10 ns | -2.2 to 7.5 <sup>(2)</sup>  | V    |

| PGOOD                  | To PGND, GND            | -0.3 to 7                   | V    |

| EN                     | To PGND, GND            | -0.3 to 7                   | V    |

| VOUT                   | To PGND, GND            | -1.0 to 3.6                 | V    |

| REFIN, COMP, REF, MODE | To GND                  | -0.3 to 3.6                 | V    |

<sup>1.</sup> All voltages need to be lower than  $V_{\mbox{\footnotesize CC}}$  under any condition.

Note:

Absolute maximum ratings are those values beyond which damage to the device may occur. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability. All voltage values are with respect to the network ground terminal.

Regardless of application configuration, it is mandatory not to exceed the AMR voltage value on the BOOT and PHASE pins.

## 4.2 Electrical characteristics

$V_{CC}$  = 5.0 V ± 5%,  $T_A$  = 70°C (unless otherwise specified).

**Table 5. Electrical characteristics**

| Symbol               | Parameter                                            | Test conditions                                                                                                           | Min. | Тур. | Max. | Unit    |  |

|----------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------|------|------|---------|--|

| Supply cur           | Supply current and undervoltage lockout              |                                                                                                                           |      |      |      |         |  |

| I <sub>IN</sub>      | VIN shutdown current                                 | Shutdown, EN = 0 V                                                                                                        |      | 0.3  | 5    | μΑ      |  |

| I <sub>CC</sub>      | V <sub>CC</sub> supply current                       | $EN = H, V_{BOOT} = 4.5 V, V_{CC} = 4.5 V, V_{IN} = 3.5 V, V_{M} = GND$                                                   |      | 2    | 3.6  | mA      |  |

| I <sub>CCSD</sub>    | V <sub>CC</sub> shutdown current                     | Shutdown, EN = 0 V                                                                                                        |      | 4    | 10   | μΑ      |  |

| I <sub>BSS</sub>     | Boot input current                                   | V <sub>BOOT</sub> = 9 V, V <sub>PHASE</sub> = 3.5 V,<br>V <sub>CC</sub> = 5.5 V                                           |      |      | 150  | μΑ      |  |

| V <sub>CC</sub>      | V <sub>CC</sub> supply voltage                       |                                                                                                                           | 4.5  | 5.0  | 5.5  | V       |  |

| V IIVI O             | V <sub>CC</sub> turn-on                              | V <sub>CC</sub> rising                                                                                                    | 4.2  | 4.37 | 4.5  | V       |  |

| V <sub>CC</sub> UVLO | Hysteresis                                           |                                                                                                                           |      | 440  |      | mV      |  |

| REF UVLO             | V <sub>REF</sub> turn-on                             | REF rising                                                                                                                |      | 1.8  |      | V       |  |

| KEF UVLO             | Hysteresis                                           |                                                                                                                           |      | 100  |      | mV      |  |

| Oscillator,          | off-time and on-time                                 |                                                                                                                           |      |      |      |         |  |

| ı                    | Ossillator assures:                                  | $R_{M} = 100 \text{ k}\Omega$                                                                                             |      | 1    |      | N 41 1- |  |

| f <sub>SW</sub>      | Oscillator accuracy                                  | $R_{M} = 47 \text{ k}\Omega$                                                                                              |      | 0.6  |      | MHz     |  |

| t <sub>OFF-min</sub> | Minimum off-time                                     | $V_{IN} = 1.5 \text{ V}, V_{OUT} = 0.9 \text{ V}, V_{REFIN} = 1 \text{ V},$<br>$f_{SW} = 1 \text{ MHz} / 0.6 \text{ MHz}$ |      | 170  |      | ns      |  |

| Reference a          | and GM amplifier                                     |                                                                                                                           |      |      |      |         |  |

| $\Delta V_{OUT}$     | Output voltage accuracy                              | V <sub>REFIN</sub> = 1 V, no droop                                                                                        | -1   |      | +1   | %       |  |

| V <sub>REF</sub>     | Voltage reference                                    | I <sub>REF</sub> = 0                                                                                                      | 1.95 | 2.0  | 2.05 | V       |  |

| G <sub>M</sub>       | Transconductance <sup>(1)</sup>                      |                                                                                                                           |      | 1.00 |      | mS      |  |

| I <sub>CSK</sub>     | COMP pin maximum sinking current                     | V <sub>COMP</sub> = 2 V, V <sub>REFIN</sub> - V <sub>OUT</sub> = -80 mV                                                   |      | 80   |      | μΑ      |  |

| I <sub>CSR</sub>     | COMP pin maximum sourcing current                    | V <sub>COMP</sub> = 2 V, V <sub>REFIN</sub> - V <sub>OUT</sub> = 80 mV                                                    |      | -80  |      | μΑ      |  |

| V <sub>CM</sub>      | Common mode input voltage range <sup>(1)</sup>       |                                                                                                                           | 0    |      | 2    | ٧       |  |

| $V_{DM}$             | Differential mode input voltage range <sup>(1)</sup> |                                                                                                                           | 0    |      | 80   | mV      |  |

| V <sub>OSet</sub>    | Input offset                                         |                                                                                                                           |      | 0    |      | mV      |  |

| F <sub>-3dB</sub>    | -3 dB frequency <sup>(1)</sup>                       |                                                                                                                           | 4.5  | 6.0  | 7.5  | MHz     |  |

| A <sub>CS</sub>      | Current sense gain                                   | Gain from the current of the LS to PWM comp when PWM = OFF                                                                | 47.3 |      | 59.3 | mV/A    |  |

Table 5. Electrical characteristics (continued)

| Symbol               | Parameter                                  | Test conditions                                                      | Min. | Тур.  | Max.  | Unit                    |

|----------------------|--------------------------------------------|----------------------------------------------------------------------|------|-------|-------|-------------------------|

| Soft-end             |                                            |                                                                      | I    | ı     |       |                         |

| R <sub>DS</sub>      | Phase discharge resistance                 |                                                                      |      | 51    |       | Ω                       |

| Overcurren           | nt protection                              |                                                                      |      |       |       |                         |

| l <sub>OCL</sub>     | Positive overcurrent threshold             | LS sourcing, $R_M = 47 \text{ k}\Omega$                              | 4    | 7.6   | 11    | Α                       |

| I <sub>OCLN</sub>    | Negative overcurrent threshold             | LS sourcing, $R_M = 47 \text{ k}\Omega$                              | -11  | - 7.6 | - 4   | Α                       |

| Bootstrap s          | switch                                     |                                                                      | Į.   |       |       |                         |

| R <sub>BSS</sub>     | Boot switch on-resistance                  | I <sub>BOOT</sub> = 10 mA, T <sub>A</sub> = 25 °C                    |      |       | 12.6  | Ω                       |

| Over and u           | ndervoltage protection                     |                                                                      | I.   | ı     | ·     |                         |

| OVP                  | OVP threshold                              | V <sub>OUT</sub> rising                                              | 117  | 120   | 123   | %<br>V <sub>REFIN</sub> |

| t <sub>OVPd</sub>    | OVP delay                                  | Time from the V <sub>OUT</sub> pinout of + 20% of REFIN to OVP fault |      | 10    |       | μs                      |

| UVP                  | UVP threshold                              | V <sub>OUT</sub> falling                                             | 65   | 68    | 71    | %<br>V <sub>REFIN</sub> |

| $t_{UVPd}$           | UVP delay                                  | Time from the V <sub>OUT</sub> pinout of -30% of REFIN to UVP fault  |      | 256   |       | μs                      |

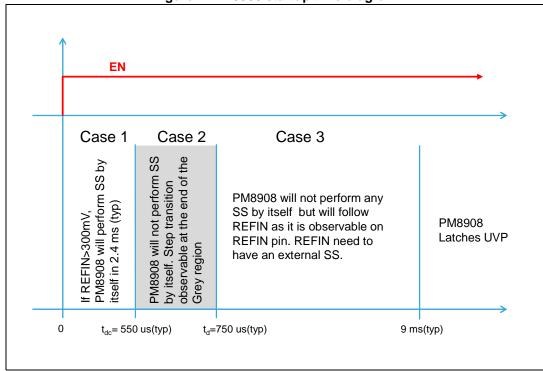

|                      | Undervoltage fault enable                  | Time from EN = H to undervoltage ready                               |      | 2.4   |       | ms                      |

|                      | delay                                      | External tracking<br>Time from EN = H to undervoltage ready          |      | 9     |       | ms                      |

| Overtempe            | rature protection                          |                                                                      |      |       |       |                         |

|                      | Thermal shutdown threshold <sup>(1)</sup>  |                                                                      |      | 145   |       | °C                      |

| OTP                  | Thermal shutdown hysteresis <sup>(1)</sup> |                                                                      |      | 10    |       | °C                      |

| PGOOD                |                                            |                                                                      |      |       |       |                         |

|                      | Linner threehold                           | V <sub>OUT</sub> rising                                              |      | 116   |       |                         |

| PGOOD                | Upper threshold                            | Hysteresis                                                           |      | 8     |       | %                       |

| FGOOD                | Lower threshold                            | V <sub>OUT</sub> falling                                             |      | 84    |       | $V_{REFIN}$             |

|                      | Lower tillesiloid                          | Hysteresis                                                           |      | 8     |       |                         |

| $V_{PGOOD,L}$        | PGOOD voltage low impedance                | I <sub>PGOOD_SINK</sub> = 4 mA, V <sub>CC</sub> = 4.5 V              |      |       | 0.338 | V                       |

| I <sub>PGOOD,H</sub> | PGOOD leakage high impedance               | V <sub>PGOOD</sub> = 5.5 V                                           |      |       | 1     | μΑ                      |

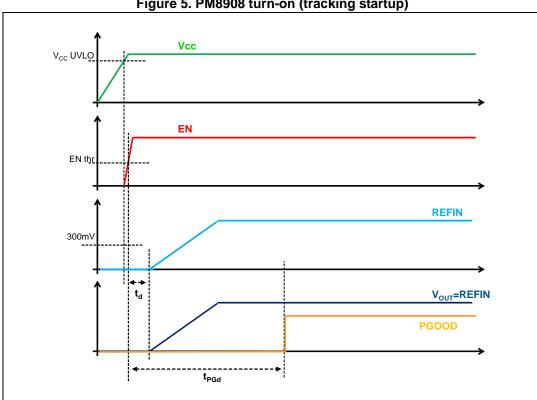

| t <sub>PGd</sub>     | PGOOD startup delay time                   | External tracking Time from EN = H to PGOOD high                     |      | 10    |       | ms                      |

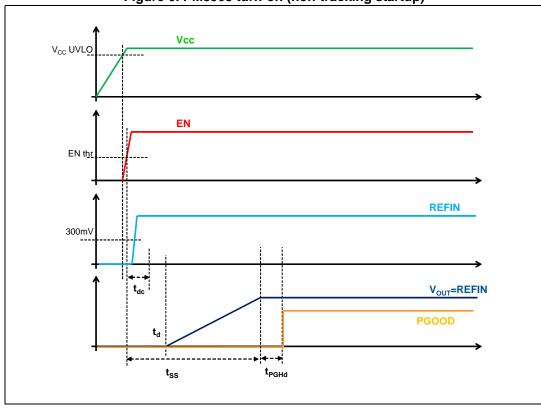

| t <sub>PGHd</sub>    | PGOOD high delay time                      | Rising edge                                                          | 0.8  | 1     | 1.2   | ms                      |

| t <sub>PGLd</sub>    | PGOOD low delay time                       | Falling edge <sup>(2)</sup>                                          |      | 10    |       | μs                      |

|                      |                                            |                                                                      |      |       |       |                         |

Table 5. Electrical characteristics (continued)

| Symbol          | Parameter             | Test conditions                             | Min. | Тур. | Max. | Unit |

|-----------------|-----------------------|---------------------------------------------|------|------|------|------|

| ENABLE          |                       |                                             |      |      |      |      |

| EN              | Input logic high      | EN rising                                   | 2    |      |      | V    |

| EIN             | Input logic low       | EN falling                                  |      |      | 0.5  | V    |

| I <sub>EN</sub> | EN input current      | V <sub>EN</sub> = 5 V                       |      |      | 3    | μΑ   |

| MODE            |                       |                                             |      |      |      |      |

| I <sub>M</sub>  | Mode current          | V <sub>MODE</sub> from GND to 2.4 V         |      | 15   |      | μΑ   |

| SOFT-STA        | RT                    | •                                           |      |      |      |      |

| t <sub>SS</sub> | Soft-start time       | From EN = H to V <sub>OUT</sub>             |      | 2.4  |      | ms   |

| td              | Delay soft-start time | From EN = H to V <sub>OUT</sub> ramp starts |      | 750  |      | μs   |

<sup>1.</sup> Guaranteed by design, not subject to test.

<sup>2.</sup> Delay time not valid if the UVLO or EN shutdown events are occurring.

PM8908 Device description

# 5 Device description

The PM8908 is a high efficiency synchronous step-down monolithic switching regulator capable to deliver or sink the current.

The power input voltage (VIN) can range from 1 V to 3.5 V, the signal input voltage (VCC) can range from 4.5 V to 5.5 V.

The output voltage is regulated to the REFIN voltage which comes from an external reference voltage. The output voltage accuracy is better than  $\pm$  1% over the line, load and temperature.

The PM8908 embeds low R<sub>DS(on)</sub> N-channel MOSFETs for both HS (high-side) and LS (low-side).

The high-switching frequency selectable in two values - 600 kHz or 1 MHz and the small package allows very compact VR solutions.

In the COT the  $t_{ON}$  is function of  $V_{IN}$ ,  $V_{OUT}$  and switching frequency ( $f_{SW}$ ), as shown in *Equation 1*:

### **Equation 1**

$$t_{ON} = \frac{V_{OUT}}{V_{IN} \cdot f_{SW}}$$

The PM8908 features a full set of protections and output voltage monitoring:

- Precise and accurate overcurrent limit (internally compensated against temperature variations)

- Over and undervoltage protection

- Overtemperature protection

- Undervoltage lockout on analog supply (VCC)

- Power Good open drain output easily provides real-time information about the output voltage.

The dedicated ENABLE pin (EN) offers easy control on the power sequencing. Forcing the EN low, the device enters the shutdown state and absorbs a total quiescent current from VCC and VIN less than 15  $\mu$ A.

## 5.1 Power section

The PM8908 integrates two low R<sub>DS(on)</sub> N-channel MOSFETs as low-side and high-side switches, optimized for fast switching transition and high efficiency over the entire load range.

The HS MOSFET drain is connected to the VIN pins (power input), the LS MOSFET source is connected to the PGND pins (power ground), and the HS MOSFET source and LS MOSFET drain are connected together and to the PHASE pins (see *Figure 1 on page 4*). The driving section is supplied from the VCC pins that assure the proper driving voltage over all the VIN range.

Device description PM8908

To properly supply the power section is advised following:

Bypass VIN pins to PGND pins as close as possible to the IC package with high quality MLCC capacitors.

Connect the bootstrap capacitor (typically a 100 nF ceramic capacitor rated to stand VIN voltage) from the BOOT pin to the PHASE pin to supply the HS driver.

#### Caution:

Do not connect an external bootstrap diode. The IC already integrates an active bootstrap switch to charge the bootstrap capacitor, saving the cost of this external component.

The PM8908 embodies the anti shoot-through and adaptive deadtime control to minimize low-side body diode conduction time and consequently to reduce power losses:

- When the gate driving voltage of the HS drops (to check high-side MOSFET turn-off), the LS MOSFET is suddenly switched on

- When the gate driving voltage of the LS drops (to check low-side MOSFET turn-off), the HS MOSFET is suddenly switched on.

## 5.2 Device configuration

The PM8908 has a programming pin - MODE (pin 18) - which allows choosing the regulator switching frequency and the OCL threshold. This programming feature is performed by selecting the proper resistor, to be mounted between the pin 18 to ground, as summarized in *Table 6*.

| R <sub>M</sub> | f <sub>SW</sub> [kHz] | OCL (A) |

|----------------|-----------------------|---------|

| 47 kΩ          | 600                   | 7.6     |

| 68 kΩ          | 600                   | 5.4     |

| 100 kΩ         | 1000                  | 5.4     |

Table 6. Switching frequency and OCL (see Figure 1 on page 4)

Note: The MODE pin must not be left floating.

## 5.3 Startup and shutdown management

The IC monitors the supply voltage on the VCC pin. Once VCC voltage is above the UVLO (undervoltage lockout) threshold and the EN pin is above the turn-on threshold:

- If the IC is configured for tracking application (see *Figure 2 on page 4*), the output voltage is regulated to the REFIN voltage. In order to discriminate between the non-tracking and the tracking, there is a delay time of 750 μs required between the EN or the VCC UVLO threshold and REFIN voltage. REFIN voltage must be applied within 9 ms (typ.) from the EN high (see *Figure 5*).

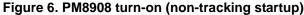

- If the IC is configured for non-tracking application, the output voltage is regulated to the REFIN voltage, and the device provides a precise 2.4 ms soft-start time (see *Figure 6*).

The power input (VIN) does not have a undervoltage protection function.

PM8908 **Device description**

Figure 5. PM8908 turn-on (tracking startup)

Device description PM8908

Figure 7. PM8908 startup time diagram

#### Soft-off

The PM8908 implements the soft-off sequence turning off both the HS and LS MOSFETs and connecting the integrated discharge resistor (47  $\Omega$ ) between the PHASE and PGND pin.

The PM8908 begins the soft-off sequence, and remains in a latched state, if one of the following conditions occurs:

- VCC voltage falls below UVLO threshold

- OVP (overvoltage protection)

- UVP (undervoltage protection)

- EN pin is pulled low.

The cycling VCC and EN the IC recover from the latched state with a new soft-start sequence.

# 5.4 Output voltage monitoring and protection

The PM8908 monitors the output voltage status through the V<sub>OUT</sub> pin and compares the voltage on this pin with the REFIN voltage in order to provide over and undervoltage protection as well as the PGOOD signal.

## 5.4.1 Overvoltage protection

Overvoltage protection is active as soon as the device is enabled, the VCC is above the respective undervoltage lockout level and REFIN is higher than 300 mV.

16/28 DocID027688 Rev 4

PM8908 Device description

The protection is triggered when the voltage sensed on the V<sub>OUT</sub> pin rises over the OVP threshold and the device acts as follows:

- De-asserts the PGOOD signal

- The HS MOSFET is suddenly forced OFF

- The LS MOSFET is turned on (to discharge the output and protect the load). When

V<sub>OUT</sub> drops below the UVP threshold the LS MOSFET is turned off and the discharge

resistor is on. If V<sub>OUT</sub> recrosses the UVP threshold, the LS is turned on again and the

discharge resistor is off.

In the overvoltage protection state the negative overcurrent limit (OCLN) is masked.

This protection is latched, cycled EN or VCC to recover.

## 5.4.2 Undervoltage protection

If VOUT falls below the UVP threshold for at least 256  $\mu$ s the IC stops switching and starts a soft-off sequence.

The device acts as follows:

- De-asserts the PGOOD signal

- The HS MOSFET and LS MOSFET are forced OFF

- The discharge resistor is on.

This protection is latched, cycled EN or VCC to recover.

The UVP protection is enabled after the soft-start end.

## 5.4.3 Power Good (PGOOD)

The PGOOD is an open drain output. During the startup, the PGOOD goes high after 1 ms from the threshold detected.

The PGOOD is forced low, to communicate that the output voltage is no longer in regulation, if one of the following conditions is verified:

- The voltage of the V<sub>OUT</sub> pin exits from the PGOOD window

- The device is disabled, EN is forced low

- VCC voltage is below the UVLO threshold

- Any protection is triggered (OVP, UVP, OTP).

## 5.4.4 Overcurrent protection

Overcurrent protection is active as soon as the device is enabled and VCC voltage is above the UVLO level.

The overcurrent function protects the converter from a shorted output or overload by sensing the output current information across the low-side integrated MOSFET.

Positive OCL

If the monitored current information is bigger than the overcurrent thresholds, an overcurrent event is detected. The IC delays the next  $t_{\text{ON}}$  until the current drops below the positive OCL limit.

Device description PM8908

The maximum available load current, with the valley current limit technique, is equal to *Equation 2*:

### **Equation 2**

$$I_{LOADmax} = I_{OCL} + \frac{1}{2} \cdot \Delta I$$

It is the sum of the valley current limit plus the half of the inductor current ripple.

During the overcurrent event the Vout drops until the UVP threshold, de-asserts the PGOOD pin and then enters into the latch state.

Negative OCL

The negative OCL circuit operates when the converter is sinking the current from the output load. The IC trigs the next toN until the current drops below the negative OCL limit.

During the overcurrent event the Vout goes up until the OVP threshold, de-asserts the PGOOD pin and then enters into the latch state.

## 5.4.5 Overtemperature protection

It is recommended that the device never exceeds the maximum allowable junction temperature. This temperature increase is mainly caused by the total power dissipated from the integrated power MOSFETs.

To avoid any damage to the device when reaching high temperature, the PM8908 implements a thermal shutdown feature: when the junction temperature reaches 145 °C the device turns off both MOSFETs. When the junction temperature drops to 135 °C, the device restarts with a new soft-start sequence.

18/28 DocID027688 Rev 4

# 6 Application information

## 6.1 Output voltage setting

The PM8908 integrates a 2 V internal reference ( $V_{REF}$ ), with the total accuracy of  $\pm$  1%.

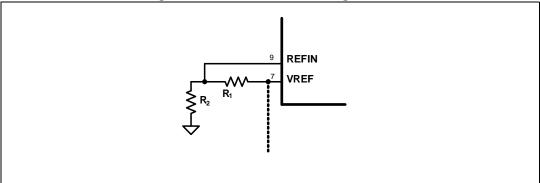

The output voltage, in non-tracking configuration, can be easily programmed connecting the  $R_1$  and  $R_2$  resistors as follows (see also *Figure 8*).

- Connect the REFIN to the REF pin through the R<sub>1</sub> resistor

- Connect the REFIN pin to the GND through the R<sub>2</sub> resistor

Therefore, the output voltage setting is easily achieved using Equation 3 to select the value of the  $R_{OS}$  resistor:

### **Equation 3**

$$V_{OUT} = \frac{V_{REF}}{1 + (R_1/R_2)}$$

Figure 8. Resistor divider configuration

# 6.2 Droop setting

In order to reduce the necessary output capacitance amount, the PM8908 can perform the load dependent behavior if the compensation network capacitor, CC, is avoided. The sensed current is used for reference voltage, in the PWM comparator inverting input. So doing, the programmed output voltage is:

### **Equation 4**

$$V_{OUT} = V_{REFIN} - V_{DROOP}$$

where:

$$V_{DROOP} = \frac{A_{CS} \cdot I_{LOAD}}{R_{DROOP} \cdot G_M}$$

with:

- R<sub>DROOP</sub> is the resistor between the COMP pin and the REF pin (see also Figure 9)

- *I<sub>I OAD</sub>* is the output current

- G<sub>M</sub> is the transconductance of the amplifier (1 mS)

- A<sub>CS</sub> is the current sense gain (53 mV/A)

Figure 9. Typical application with droop configuration

# 6.3 Non-droop setting

The advantage of a non-droop configuration is that the load regulation is flat. It can be implemented by connecting a resistor ( $R_C$ ) and a capacitor ( $C_C$ ) between the COMP pin and the REF pin (see also *Figure 1 on page 4*).

# 6.4 Inductor design

The inductance value is defined by a compromise between the dynamic response time, the efficiency, the cost, and the size. The inductor must be calculated to maintain the ripple current ( $\Delta I_L$ ) between 20% and 30% of the maximum output current (typ.). The inductance value can be calculated with the following relationship:

#### **Equation 5**

$$L \, = \, \frac{V_{IN} - V_{OUT}}{F_{SW} \cdot \Delta I_L} \cdot \frac{V_{OUT}}{V_{IN}}$$

where  $f_{SW}$  is the switching frequency,  $V_{IN}$  is the input voltage, and  $V_{OUT}$  is the output voltage.

5//

## 6.5 Output capacitors

The output capacitors are basic components to define the ripple voltage across the output and for the fast transient response of the power supply. They depend on the output voltage ripple requirements, as well as any output voltage deviation requirement during a load transient.

During steady-state conditions, the output voltage ripple is influenced by both the ESR and the capacitive value of the output capacitors as follows:

### **Equation 6**

$$\Delta V_{OUT ESR} = \Delta I_{I} \cdot ESR$$

#### **Equation 7**

$$\Delta V_{OUT\_C} = \Delta I_L \cdot \frac{1}{8 \cdot C_{OUT} \cdot F_{SW}}$$

where  $\Delta I_L$  is the inductor current ripple. In particular, the expression that defines  $\Delta V_{OUT\_C}$  takes into consideration the output capacitor charge and discharge as a consequence of the inductor current ripple.

## 6.6 Input capacitors

The input capacitor bank is designed considering, mainly, the input RMS current that depends on the output deliverable current (I<sub>OUT</sub>) and the duty cycle (D) for the regulation as follows:

#### **Equation 8**

$$I_{rms} = I_{OUT} \cdot \sqrt{D \cdot (1 - D)}$$

The equation reaches its maximum value,  $I_{OUT}/2$ , with D = 0.5. The losses depend on the input capacitor ESR and, in the worst case, are:

#### **Equation 9**

$$P = ESR \cdot (I_{OUT}/2)^2$$

## 6.7 Compensation network

The PM8908 device implements a constant on-time control loop. The compensation network is shown in *Figure 10*.

Figure 10. Compensation network

The following procedure shall be followed in order to calculate the best network external components value.

Select R<sub>F</sub> value in order to obtain the desired closed loop regulator bandwidth according to Equation 10:

### **Equation 10**

$$R_{F} = 2\pi \cdot f_{T} \cdot C_{OUT} \cdot \frac{R_{CS}}{g_{M}} \left( 1 + 2\pi \cdot \frac{f_{T}}{5} \cdot \frac{ESR \cdot C_{OUT}}{1 - 2\pi \cdot \frac{f_{T}}{5} \cdot ESR \cdot C_{OUT}} \right)$$

where:

- f<sub>T</sub> is the crossover frequency, it should be less than about 1/10 of the switching frequency

- $-R_{CS} = 53 \text{ m}\Omega$

- Select *C<sub>F</sub>* according to *Equation 11*:

#### **Equation 11**

$$C_F \geq \frac{1}{2\pi \cdot \frac{f_T}{5} \cdot R_F}$$

Select C<sub>P</sub> according to Equation 12:

### **Equation 12**

$$C_{P} = \frac{ESR \cdot C_{OUT}}{R_{C} \cdot \left(1 - 2\pi \cdot \frac{f_{T}}{5} \cdot ESR \cdot C_{OUT}\right)}$$

• Check the phase margin obtained and repeat the whole procedure if necessary.

# 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: <a href="www.st.com">www.st.com</a>. ECOPACK is an ST trademark.

Package information PM8908

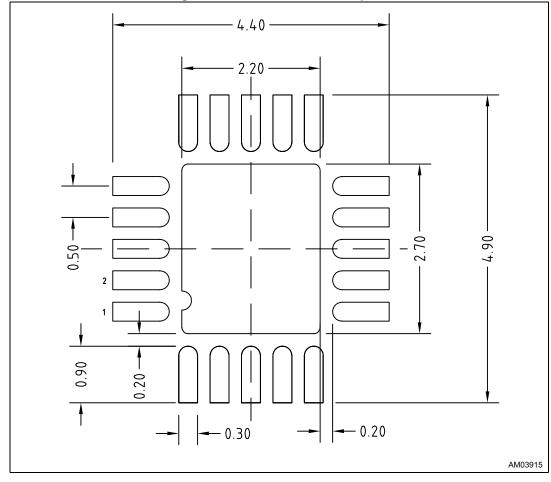

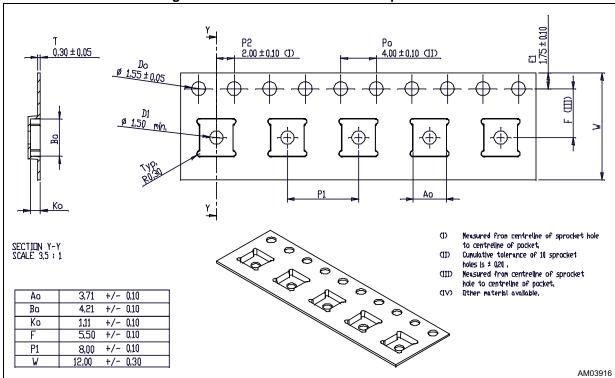

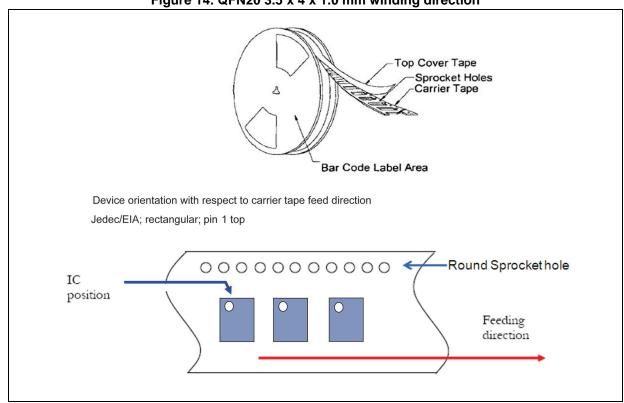

# 7.1 QFN20 package information

BOTTOM VIEW (DATUM A)-D2/2 ⊢NX L U U U U(DATUM B) E2/2 (NE-1) X e 🔲 R0.20 PIN#1 I.D. -их ь SEE DETAIL "F' 0.10M C A B 0.05(M) C — (NX−1) X e — 0.10 C  $\bigcirc$  0.05 C SEATING PLANE SIDE VIEW С <del>D</del> Ø0.30 TYP.- $\oplus$ 2X 0.100 C **TOP VIEW** 2X 0.100 C DATUM A OR B-TERMINAL TIP DETAIL "F" ODD LEADS/SIDE AM03914

Figure 11. QFN20 3.5 x 4 x 1.0 mm package outline

Table 7. QFN20 3.5 x 4 x 1.0 mm package mechanical data

| Symbol |      | Dimensions (mm) |      |  |  |  |

|--------|------|-----------------|------|--|--|--|

| Symbol | Min. | Тур.            | Max. |  |  |  |

| A      | 0.90 | 0.95            | 1.00 |  |  |  |

| A1     | 0.00 | 0.02            | 0.05 |  |  |  |

| A3     |      | 0.152           |      |  |  |  |

| b      | 0.18 | 0.25            | 0.30 |  |  |  |

| D      | 3.4  | 3.5             | 3.6  |  |  |  |

| D2     | 2.00 | 2.10            | 2.20 |  |  |  |

| E      | 3.9  | 4.0             | 4.1  |  |  |  |

| E2     | 2.50 | 2.60            | 2.70 |  |  |  |

| е      |      | 0.50            |      |  |  |  |

| L      | 0.35 | 0.40            | 0.45 |  |  |  |

| K      | 0.20 |                 |      |  |  |  |

Figure 12. Recommended footprint

Package information PM8908

Figure 13. QFN20 3.5 x 4 x 1.0 mm tape and reel

PM8908 Revision history

# 8 Revision history

**Table 8. Document revision history**

| Date        | Revision | Changes                                                                                                                              |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------|

| 30-Mar-2015 | 1        | Initial release.                                                                                                                     |

| 22-Oct-2015 | 2        | <ul> <li>Added footnote 2 to Table 4.</li> <li>Added minimum and maximum dimension values for symbols D and E in Table 7.</li> </ul> |

| 09-Nov-2015 | 3        | First public release.                                                                                                                |

| 25-Jul-2017 | 4        | Updated: A <sub>CS</sub> , R <sub>DS</sub> , R <sub>BSS</sub> and V <sub>PGOOD,L</sub> values in <i>Table 5</i> .                    |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics - All rights reserved

DocID027688 Rev 4

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

STMicroelectronics: PM8908TR