# L99UDL01 Automotive Universal Door Lock IC

#### Datasheet - production data

#### **Features**

- Integrated half bridges can be fully independent or paralleled up to three in parallel

- Two levels of standby

- Standby (SPI initiated)

- Sleep (VDD=0 V)

- · Very low current consumption in standby

- Only wake-up circuit active

- High level of programmability

- On-time duration

- Direction

- Current level

- Off-state fault detection

- 2 external half bridge controllers (using external N-channel MOSFETs or Smart Power devices)

- External half bridges protected by drain source monitoring and off-state fault detection

- 2 stage charge pump for low voltage operation

- PWM current regulation up to 25 kHz

- 4 MHz 24 bit SPI interface for control and diagnostics

- Output enable for high security

- · High level diagnostics

- 10 bit digital current feedback (via SPI) for load integrity check

- Thermal warning and shutdown protection

- Reverse battery protection using an external N-Ch MOSFET.

- TQFP64L exposed pad package

### Application

The L99UDL01 is designed for use in a central door lock system driving all of the door lock actuators. This device is able to adapt to most central door lock configurations.

### **Description**

The L99UDL01 is a multiple half-bridge IC with 6 integrated outputs that are PWM configurable and current regulated and up to two externally configured half bridges for higher current nodes. The level of diagnostics includes open load, short to battery, short to ground, and load integrity via 10 bit current feedback.

The L99UDL01 is commanded entirely by SPI using duration and current level commands.

**Table 1. Device summary**

| Package | Orde     | er codes      |

|---------|----------|---------------|

| Fackage | Tray     | Tape and reel |

| TQFP64L | L99UDL01 | L99UDL01TR    |

Contents L99UDL01

# **Contents**

| 1 | Bloc | k diagra | am and pin descriptions                    | 9  |

|---|------|----------|--------------------------------------------|----|

|   | 1.1  | Block    | diagram                                    | 9  |

|   | 1.2  | Pin de   | scription                                  | 10 |

|   | 1.3  | Pin co   | nnections (top view)                       | 13 |

| 2 | Devi | ce desc  | cription                                   | 14 |

|   | 2.1  | Overvi   | iew                                        | 14 |

|   | 2.2  | Supply   | y monitoring                               | 14 |

|   |      | 2.2.1    | Low Voltage Inhibit (VSLVI)                | 14 |

|   |      | 2.2.2    | Overvoltage (VSOVSD)                       | 14 |

|   |      | 2.2.3    | VDD monitoring                             | 14 |

|   |      | 2.2.4    | 3V3 monitoring                             | 14 |

|   | 2.3  | Charge   | e pump                                     | 15 |

|   | 2.4  | Output   | t functionality                            | 16 |

|   |      | 2.4.1    | Integrated half bridge drivers (OUT1-OUT6) | 17 |

|   |      | 2.4.2    | External FET controllers                   | 21 |

|   |      | 2.4.3    | DOUT                                       | 21 |

|   |      | 2.4.4    | EN_OUT                                     | 21 |

|   |      | 2.4.5    | Paralleling outputs                        | 21 |

|   |      | 2.4.6    | Output override                            | 22 |

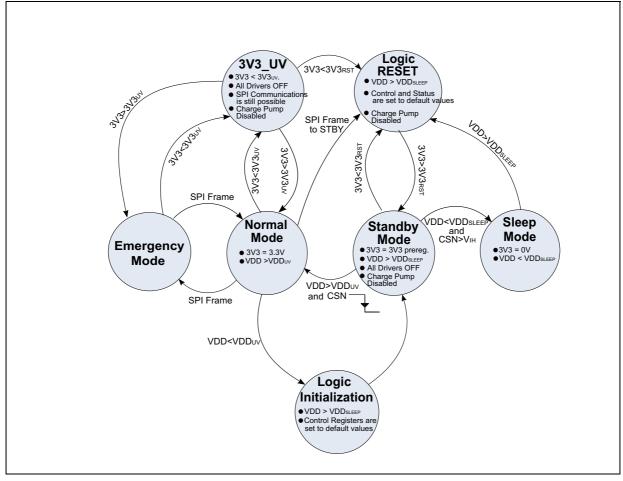

|   | 2.5  | Opera    | ting modes                                 | 23 |

|   |      | 2.5.1    | Sleep mode                                 | 23 |

|   |      | 2.5.2    | Standby mode                               | 24 |

|   |      | 2.5.3    | Normal mode                                | 24 |

|   |      | 2.5.4    | Emergency mode                             | 24 |

|   | 2.6  | Diagno   | ostics and protections                     | 25 |

|   |      | 2.6.1    | Shorted load detection                     | 25 |

|   |      | 2.6.2    | Thermal protection                         | 26 |

|   |      | 2.6.3    | Off state load detection                   | 26 |

|   |      | 2.6.4    | Enable-able weak pull-up/down currents     | 26 |

|   |      | 2.6.5    | Dynamic output state detection             | 26 |

| 3 | Арр  | lication | schematic                                  | 27 |

|   |      |          |                                            |    |

| 4 | Electi | rical characteristics                             | 28 |

|---|--------|---------------------------------------------------|----|

|   | 4.1    | Absolute maximum ratings                          | 28 |

|   | 4.2    | Thermal data                                      | 29 |

|   | 4.3    | Electrical characteristics                        | 29 |

|   |        | 4.3.1 Supply                                      | 30 |

|   |        | 4.3.2 Oscillator                                  | 32 |

|   |        | 4.3.3 Turn-on/off timing                          | 32 |

|   |        | 4.3.4 Integrated half bridge                      | 33 |

|   |        | 4.3.5 Integrated half bridge current control loop | 33 |

|   |        | 4.3.6 External half bridge                        | 34 |

|   |        | 4.3.7 Charge pump                                 | 35 |

|   |        | 4.3.8 Protections                                 | 35 |

|   |        | 4.3.9 Integrated half bridge AC characteristics   | 37 |

|   |        | 4.3.10 I/O and SPI                                | 38 |

|   |        | 4.3.11 SPI timing                                 | 39 |

|   | 4.4    | ESD protection                                    | 41 |

| F | Cautal |                                                   | 40 |

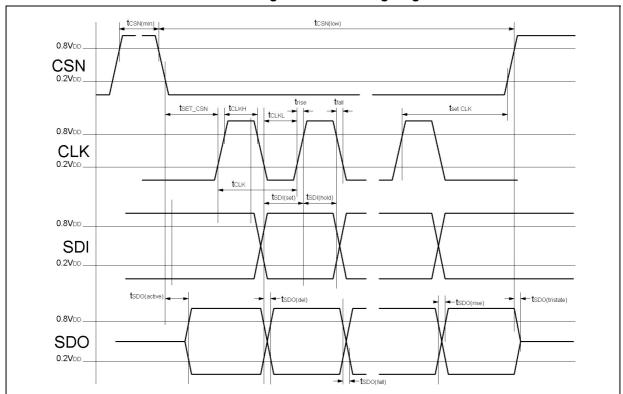

| 5 |        | Il communications                                 |    |

|   | 5.1    | General information                               |    |

|   | - 0    | 5.1.1 Physical Layer                              |    |

|   | 5.2    | Signal description                                |    |

|   |        | 5.2.1 Chip Select Not (CSN)                       |    |

|   |        | 5.2.2 Serial Clock (SCK)                          |    |

|   |        | 5.2.3 Serial Data Input (SDI)                     |    |

|   |        | 5.2.4 Serial Data Output (SDO)                    |    |

|   | 5.3    |                                                   | 43 |

|   | 5.4    | Protocol                                          | 43 |

|   | 5.5    | Operating codes                                   | 44 |

|   |        | 5.5.1 Advanced operation codes                    | 45 |

|   | 5.6    | Register change during communication              | 45 |

|   | 5.7    | GSB and payload inconsistency                     | 45 |

|   | 5.8    | Address                                           | 45 |

|   | 5.9    | Data-In payload                                   | 46 |

|   | 5.10   | SDO frame                                         | 46 |

|   | 5.11   | Global status byte                                |    |

|   |        |                                                   | •  |

Contents L99UDL01

|   | 5.12 | Parity  |                                                                                    | 47   |

|---|------|---------|------------------------------------------------------------------------------------|------|

|   | 5.13 |         | nonitor                                                                            |      |

|   | 5.13 |         | meout, (tCSN)                                                                      |      |

|   |      |         |                                                                                    |      |

|   | 5.15 |         | ead                                                                                |      |

|   | 5.16 |         | Information Registers                                                              |      |

|   |      | 5.16.1  | Device Identification Registers (00H => 0AH)                                       |      |

|   | 5.17 | SPI re  | gisters                                                                            |      |

|   |      | 5.17.1  | SPI control register description                                                   | 50   |

|   |      | 5.17.2  | Control register overview                                                          | 50   |

|   |      | 5.17.3  | Output configuration registers                                                     | 51   |

|   | 5.18 | SPI sta | tus register definitions                                                           | 52   |

|   |      | 5.18.1  | Status register overview                                                           | 52   |

|   |      | 5.18.2  | Diagnostics                                                                        | 53   |

| 6 | Prog | rammer  | rs guide                                                                           | 54   |

|   | 6.1  |         | Control Registers                                                                  |      |

|   |      | 6.1.1   | Register 00H (Integrated driver control registers)                                 |      |

|   |      | 6.1.2   | Register 01H (external driver control registers and Output On overribits) 56       |      |

|   | 6.2  | Output  | configuration registers                                                            | 59   |

|   | V    | 6.2.1   | Register 02H (Driver configuration register 1).                                    |      |

|   |      | 6.2.2   | Register 03H (Driver configuration register 2)                                     |      |

|   |      | 6.2.3   | Register 04H and 05H (Driver configuration registers 1 through 3, au through 6) 64 |      |

|   |      | 6.2.4   | Register 06H (external bridge VDS monitor and control)                             | 68   |

|   |      | 6.2.5   | Register 07H (diagnostic monitoring control)                                       | 71   |

|   |      | 6.2.6   | Register 08H (current regulation loop control)                                     | 72   |

|   | 6.3  | SPI dia | ignostic registers                                                                 | 74   |

|   |      | 6.3.1   | Global Status byte                                                                 |      |

|   |      | 6.3.2   | Register 10H Integrated H-Bridge diagnostic status register                        | 76   |

|   |      | 6.3.3   | Register 11H (dynamic output state register)                                       |      |

|   |      | 6.3.4   | Register 12H (General Fault information)                                           |      |

|   |      | 6.3.5   | Register 13H-(regulated current feedback out 1-6)                                  | 82   |

|   |      | 6.3.6   | Register 19H-1CH silicon test traceability data                                    | 83   |

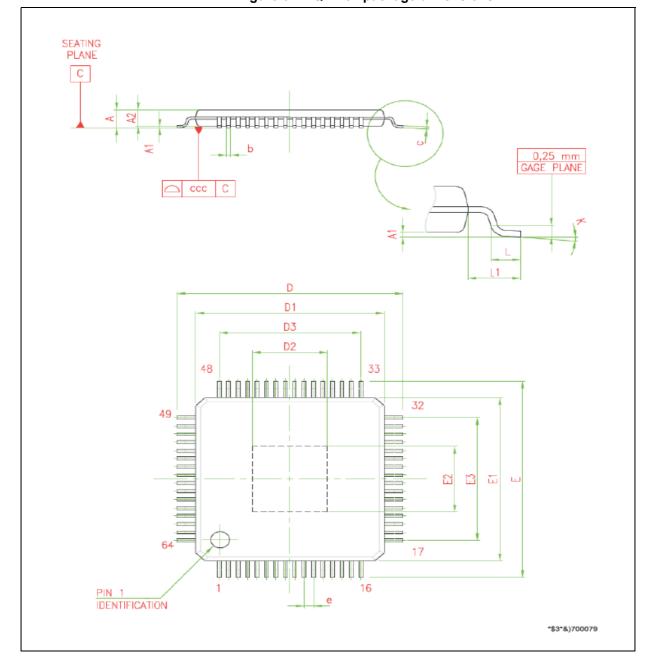

| 7 | Pack | age and | d packing information                                                              | 85   |

|   | 7.1  | _       | ACK                                                                                |      |

|   |      | ,,      |                                                                                    | . 55 |

| L99UDL01 |      | Contents                |

|----------|------|-------------------------|

|          | 7.2  | TQFP-64 mechanical data |

| 8        | Revi | sion history            |

List of tables L99UDL01

# List of tables

| Table 1.  | Device summary                                    | 1  |

|-----------|---------------------------------------------------|----|

| Table 2.  | Pin description                                   | 10 |

| Table 3.  | Absolute maximum ratings                          | 28 |

| Table 4.  | Thermal data                                      | 29 |

| Table 5.  | Electrical parameters numbering                   | 29 |

| Table 6.  | Supply voltage parameters                         | 30 |

| Table 7.  | Oscillator                                        | 32 |

| Table 8.  | On/Off timing parameters                          | 32 |

| Table 9.  | Integrated half-bridge DC parameters              | 33 |

| Table 10. | Integrated half-bridge current control parameters | 33 |

| Table 11. | External half-bridge parameters                   | 34 |

| Table 12. | Charge pump parameters                            | 35 |

| Table 13. | Protections                                       | 35 |

| Table 14. | Integrated half bridge AC characteristics         | 37 |

| Table 15. | I/O Parameters, CLK, SDO, SDI, CSN, EN_OUT, DOUT  | 38 |

| Table 16. | SPI timing parameters                             | 39 |

| Table 17. | ESD protection                                    | 41 |

| Table 18. | Op code description                               | 44 |

| Table 19. | Control register addresses                        | 45 |

| Table 20. | Status registers addresses                        | 46 |

| Table 21. | Device information registers                      | 48 |

| Table 22. | SPI modes register                                | 48 |

| Table 23. | SPI data length                                   | 49 |

| Table 24. | Data consistency bit definition                   | 49 |

| Table 25. | Control register overview                         | 50 |

| Table 26. | Status register overview                          | 52 |

| Table 27. | 00H Command description                           | 54 |

| Table 28. | Polarity command bits                             | 55 |

| Table 29. | PWM frequency select bits                         | 56 |

| Table 30. | 01H Command description                           | 56 |

| Table 31. | 01H emergency command description                 | 58 |

| Table 32. | External output polarity bits                     | 59 |

| Table 33. | 02H Configuration bit description                 |    |

| Table 34. | Brake duration bits                               | 60 |

| Table 35. | Run time duration bits                            | 61 |

| Table 36. | 03H register bit description                      | 62 |

| Table 37. | Grouping configuration bits                       |    |

| Table 38. | 04H register bit description                      | 64 |

| Table 39. | 05H register bit description                      | 65 |

| Table 40. | Current / duty cycle bit description              | 66 |

| Table 41. | Current bit description                           | 67 |

| Table 42. | Current / duty cycle switch bit description       | 68 |

| Table 43. | 06H Register bit description                      |    |

| Table 44. | VDS threshold bit description                     | 70 |

| Table 45. | VDS timer bit description                         |    |

| Table 46. | 07H Register bit description                      | 71 |

| Table 47. | 08H Register bit description                      |    |

| Table 48  | KP Gain settings                                  | 73 |

L99UDL01 List of tables

| Table 49. | KI gain settings                         | 73 |

|-----------|------------------------------------------|----|

| Table 50. | 09H register bit description             |    |

| Table 51. | GSB bit description                      |    |

| Table 52. | 10H register bit description             | 76 |

| Table 53. | Output status bit description            |    |

| Table 54. | 11H register bit description             | 79 |

| Table 55. | EXT output status register               | 80 |

| Table 56. | Device status bits                       |    |

| Table 57. | 12H register bit description             | 81 |

| Table 58. | 13H through 18H register bit description | 83 |

| Table 59. | TQFP-64 mechanical data                  | 85 |

| Table 60. | Document revision history                | 87 |

7/88

List of figures L99UDL01

# List of figures

| Figure 1.  | Block diagram                                        | 9    |

|------------|------------------------------------------------------|------|

| Figure 2.  | Pin connection diagram                               | . 13 |

| Figure 3.  | Charge pump low filtering and start-up               | . 15 |

| Figure 4.  | OUT1-6 block diagram                                 | . 17 |

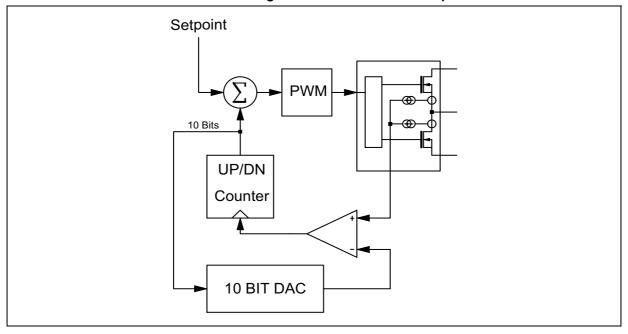

| Figure 5.  | Current Control Loop                                 | . 18 |

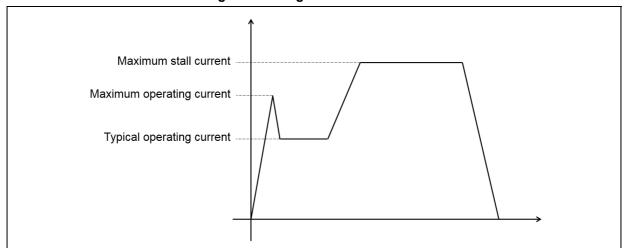

| Figure 6.  | Unregulated door lock motor current                  | . 19 |

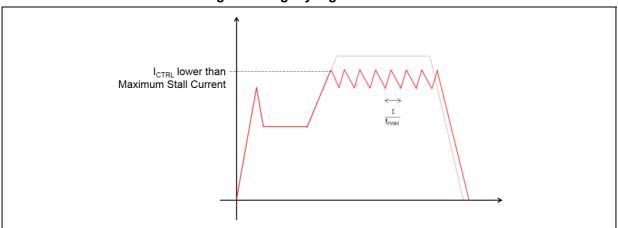

| Figure 7.  | Slightly regulated door lock current                 | . 19 |

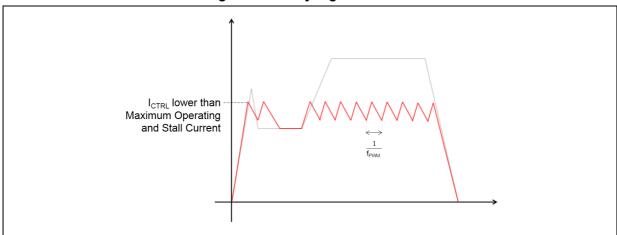

| Figure 8.  | Heavily regulated door lock current                  | . 19 |

| Figure 9.  | State diagram                                        | . 23 |

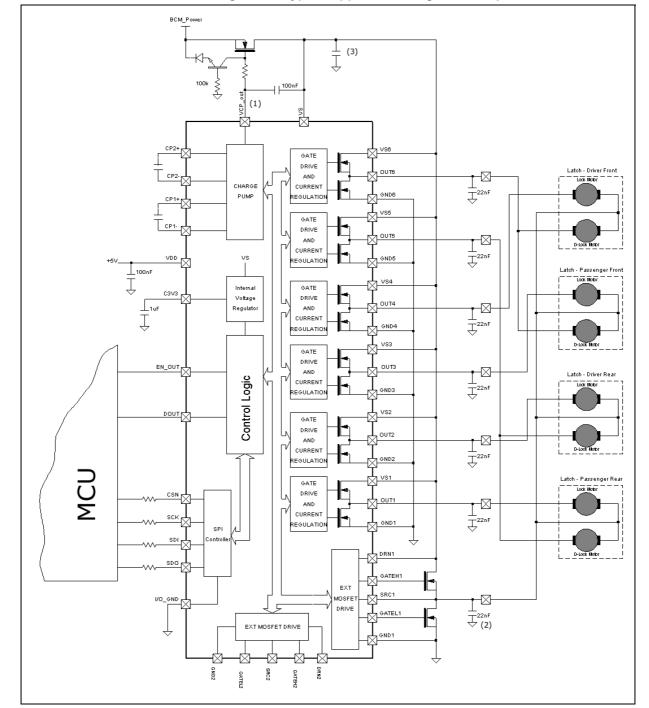

| Figure 10. | Typical application diagram example                  | . 27 |

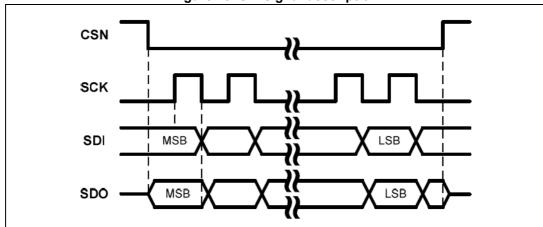

| Figure 11. | SPI timing diagram                                   |      |

| Figure 12. | SPI pin description                                  | . 42 |

| Figure 13. | SPI signal description                               | 43   |

| Figure 14. | SPI command protocol description                     | . 44 |

| Figure 15. | SDO frame                                            |      |

| Figure 16. | Register 00H Integrated output commands              |      |

| Figure 17. | 01H External driver commands                         | . 56 |

| Figure 18. | 02H Driver configuration register 1                  | . 59 |

| Figure 19. | 03H Driver config register 2                         | . 62 |

| Figure 20. | 04H driver configuration register 3                  | . 64 |

| Figure 21. | 05H driver configuration register 4                  | . 65 |

| Figure 22. | 06H external bridge VDS monitor and control register | . 69 |

| Figure 23. | 07H diagnostic monitoring control register           | . 71 |

| Figure 24. | 08H Current regulation loop control register         | . 72 |

| Figure 25. | 09 H spare control register                          | . 74 |

| Figure 26. | Global Status byte                                   | . 75 |

| Figure 27. | 10H integrated driver Diagnostic status register     | . 76 |

| Figure 28. | 11H dynamic output status register                   | . 79 |

| Figure 29. | 12H General fault information register               |      |

| Figure 30. | 13H through 18H Regulated current feedback registers | . 82 |

| Figure 31. | 19H through 1CH silicon traceability data            |      |

| Figure 32  | TOED-64 nackage dimensions                           | 98   |

# 1 Block diagram and pin descriptions

# 1.1 Block diagram

Figure 1. Block diagram CP2+ GATE DRIVE AND CP2-CURRENT PUMP REGULATION GATE DRIVE AND CURRENT REGULATION VDD DRIVE C3V3 Voltage AND Regulator CURRENT REGULATION GATE DRIVE Control Logic EN\_OUT CURRENT REGULATION GND3 GATE DOUT DRIVE AND CURRENT REGULATION GATE DRIVE AND OUT1 CSN CURRENT REGULATION SCK SDI EXT SDO MOSFET DRIVE GATEL1 EXT MOSFET DRIVE

# 1.2 Pin description

Table 2. Pin description

| Pin# | Name    | Description                                                                                                                                               |

|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | VS1_2   | Supply for half bridge 1                                                                                                                                  |

| 2    | OUT1_1  | Half bridge output 1                                                                                                                                      |

| 3    | OUT1_2  | Half bridge output 1                                                                                                                                      |

| 4    | GND1_1  | Ground for half bridge 1                                                                                                                                  |

| 5    | GND1_2  | Ground for half bridge 1                                                                                                                                  |

| 6    | VS2_1   | Supply for half bridge 2                                                                                                                                  |

| 7    | VS2_2   | Supply for half bridge 2                                                                                                                                  |

| 8    | OUT2_1  | Half bridge output 2                                                                                                                                      |

| 9    | OUT2_2  | Half bridge output 2                                                                                                                                      |

| 10   | GND2_1  | Ground for half bridge 2                                                                                                                                  |

| 11   | GND2_2  | Ground for half bridge 2                                                                                                                                  |

| 12   | VS3_1   | Supply for half bridge 3                                                                                                                                  |

| 13   | VS3_2   | Supply for half bridge 3                                                                                                                                  |

| 14   | OUT3_1  | Half bridge output 3                                                                                                                                      |

| 15   | OUT3_2  | Half bridge output 3                                                                                                                                      |

| 16   | GND3_1  | Ground for half bridge 3                                                                                                                                  |

| 17   | GND3_2  | Ground for half bridge 3                                                                                                                                  |

| 18   | EN_OUT  | Failsafe logic input. On its rising edge, EN_OUT activates outputs including External MOSFET drivers. Low disables all actuations.                        |

| 19   | DOUT    | Programmable I/O pin / Default as Global Fault Flag                                                                                                       |

| 20   | GNDEXT1 | Ground for VDS reference for low side MOSFET                                                                                                              |

| 21   | GATEL1  | Gate drive for low side external MOSFET                                                                                                                   |

| 22   | SRC1    | Source – Drain node between high and low side MOSFETS. Used for VDS detection of both high and low side MOSFETs                                           |

| 23   | GATEH1  | Gate drive for high side external MOSFET                                                                                                                  |

| 24   | DRN1    | Drain connection for external H-Bridge, Sensing for VDS fault                                                                                             |

| 25   | GNDEXT2 | Ground for VDS reference for low side MOSFET                                                                                                              |

| 26   | GATEL2  | Gate drive for low side external MOSFET                                                                                                                   |

| 27   | SRC2    | Programmable I/O pin / Optional Source – Drain node between high and low side auxiliary MOSFETS. Used for VDS detection of both high and low side MOSFETs |

| 28   | GATEH2  | Programmable I/O pin / optional external gate drive for auxiliary high side MOSFET                                                                        |

| 29   | DRN2    | Drain connection for external H-Bridge, Sensing for VDS fault                                                                                             |

| 30   | GND     | Ground pin                                                                                                                                                |

| 31   | NC      | Not Connected pin; to leave floating                                                                                                                      |

Table 2. Pin description (continued)

Block diagram and pin descriptions

| Pin# | Name   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32   | VS4_1  | Supply for half bridge 4                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 33   | VS4_2  | Supply for half bridge 4                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 34   | OUT4_1 | Half bridge output 4                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 35   | OUT4_2 | Half bridge output 4                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 36   | GND4_1 | Ground for half bridge 4                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 37   | GND4_2 | Ground for half bridge 4                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 38   | VS5_1  | Supply for half bridge 5                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 39   | VS5_2  | Supply for half bridge 5                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 40   | OUT5_1 | Half bridge output 5                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 41   | OUT5_2 | Half bridge output 5                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 42   | GND5_1 | Ground for half bridge 5                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 43   | GND5_2 | Ground for half bridge 5                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 44   | VS6_1  | Supply for half bridge 6                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 45   | VS6_2  | Supply for half bridge 6                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 46   | OUT6_1 | Half bridge output 6                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 47   | OUT6_2 | Half bridge output 6                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 48   | GND6_1 | Ground for half bridge 6                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 49   | GND6_2 | Ground for half bridge 6                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 50   | SCK    | SPI Clock - This SCK provides the clock of the SPI. Data present at Serial Data Input (SDI) is latched on the rising edge of Serial Clock (SCK) into the internal shift registers while on the falling edge data from the internal shift registers are shifted out to Serial Data Out (SDO).                                                                                                                                                                                  |

| 51   | CSN    | SPI Chip Select Not -The communication interface is deselected, when this input signal is logically high. A falling edge on CSN enables and starts the communication while a rising edge finishes the communication and the sent command is executed when a valid frame was sent. During communication start and stop the Serial Clock (SCK) has to be logically low. The Serial Data Out (SDO) is in high impedance when CSN is high or a communication timeout was detected |

| 52   | SDI    | Serial Data In - This input is used to transfer data serially into the device. Data is latched on the rising edge of Serial Clock (SCK).                                                                                                                                                                                                                                                                                                                                      |

| 53   | SDO    | Serial Data Out - This output signal is used to transfer data serially out of the device.  Data is shifted out on the falling edge of Serial Clock (SCK).                                                                                                                                                                                                                                                                                                                     |

| 54   | VDD    | I/O Supply (+5 V or 3.3 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 55   | C3V3   | Capacitor decoupling pin for internal 3.3 V regulator                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 56   | GND    | Ground for IC and I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 57   | NC     | Not Connected pin; to leave floating                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 58   | VS     | Supply for IC                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 59   | CP2-   | Charge pump capacitor pin                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

Table 2. Pin description (continued)

| Pin# | Name   | Description                                                   |

|------|--------|---------------------------------------------------------------|

| 60   | CP2+   | Charge pump capacitor pin                                     |

| 61   | CP_OUT | Charge pump out, also used for biasing reverse battery MOSFET |

| 62   | CP1+   | Charge pump capacitor pin                                     |

| 63   | CP1-   | Charge pump capacitor pin                                     |

| 64   | VS1_1  | Supply for half bridge 1                                      |

| TAB  |        | Connect to ground                                             |

## 1.3 Pin connections (top view)

GND6\_2 CP\_OUT S S 60 59 58 57 55 VS1\_2 \_ 1 GND6\_1 48 OUT1\_1 2 OUT6\_2 47 TAB OUT1\_2 \[ \] 3 OUT6\_1 46 GND1\_1 4 VS6\_2 45 GND1\_2 \_ 5 44 VS6\_1 VS2\_1 \( \Bar{\cap} \) 6 \_ GND5\_2 43 VS2\_2 7 GND5\_1 42 OUT2\_1 \[ 8\] OUT5\_2 41 TQFPL64 10X10 OUT2\_2 \[ 9 OUT5\_1 40 GND2\_1 \_ 10 VS5\_2 39 GND2\_2 \_ 11 38 \_\_ VS5\_1 VS3\_1 \_ 12 37 GND4\_2 VS3\_2 \[ \] 13 \_\_ GND4\_1 36 OUT3\_1 \_ 14 35 \_ OUT4\_2 OUT3\_2

15 \_\_ OUT4\_1 34 GND3\_1 \_ 16 VS4 2 33 18 22 24 25 28 29 30 31 32 GATEH2 GNDEXT2 GATEL2 GNDEXT1 GATEL1 GATEH1 SRC2 DOUT SRC1 DRN1 DRN2 EN\_OUT

Figure 2. Pin connection diagram

4

# 2 Device description

#### 2.1 Overview

The L99UDL01 is a 6+2 channel half bridge driver monolithic integrated circuit designed to power a centralized door lock system. This device is made possible by the incorporation of current regulated drivers limiting the current in the door lock motors to a preset level (for example the current levels seen at a 9 V battery).

The current is regulated by controlling the PWM duty cycle at a programmed frequency.

# 2.2 Supply monitoring

# 2.2.1 Low Voltage Inhibit (VS<sub>LVI</sub>)

The Vs supply has a low voltage warning function with hysteresis. When Vs drops below  $VS_{LVI\_F}$  the outputs (internal half bridges and drivers for external MOSFET) are disabled and the  $VS_{LVI}$  bit is set in register 12H (the SPI diagnostic register).

Once Vs rises above the rising  $VS_{LVI\_R}$  threshold the outputs are re-enabled and ready for use. Actuation can be restarted via SPI frame or EN\_OUT rising edge according to configuration registers. The  $VS_{LVI}$  bit remains set in the SPI diagnostic register and is cleared only upon read & clear.

# 2.2.2 Overvoltage (VS<sub>OVSD</sub>)

When VS rises above  $VS_{OVSD}$  the outputs (internal half bridges and drivers for external MOSFETs) are disabled and the  $V_{OVSD}$  bit is set in the SPI diagnostic register.

Once VS falls below VS<sub>OVSD</sub> the outputs are re-enabled and ready for use. Actuation can be restarted according to configuration registers via SPI frame or EN\_OUT rising edge. The VSOVSD bit (diagnostic register 12H) remains set until read & clear SPI frame.

#### 2.2.3 VDD monitoring

The VDD pin (5 V/3.3 V) is a supply pin for the L99UDL01 I/O. This pin is monitored by 2 under voltage conditions. In case of an undervoltage condition during Normal mode (VDD < VDD<sub>UV</sub>) the device will enter into stand-by mode and all of the control registers will be reset to their default values after  $t_{VDDUV}$ . In case of an undervoltage condition (VDD<VDD<sub>SLEEP</sub>), the device enters into the ultra-low quiescent sleep mode and the internal regulator is disabled. CSN must be held high while VDD falls below VDD<sub>SLEEP</sub> to ensure the L99UDL01 enters into sleep mode.

Upon rising out of VDD<sub>SLEEP</sub> the device will perform a power-on reset and enter into Standby mode until a CSN wake-up has occurred. The reset (RSTB) bit will remain set until the first SPI communication.

#### 2.2.4 3V3 monitoring

The internal 3.3 V regulator, 3V3, is monitored for under voltage conditions to ensure the logic integrity.

L99UDL01 Device description

The 3V3 supply has a low voltage warning function with hysteresis. When the 3V3 regulator drops below  $3V3_{UV}$  threshold for  $t_{3V3UV}$ , timed actuation is halted, the outputs (internal half bridges and drivers for external MOSFET) are disabled, and the V3V3UV bit is set in the SPI diagnostic register 13h.

If, for any reason the 3V3 supply falls below V3V3<sub>RST\_F</sub> the Logic State machine and all of the registers are RESET to their default state and held there.

Upon rising out of  $V3V3_{RST\_R}$  RESET will be disabled and the L99UDL01 will enter Standby mode.

The C3V3 pin is intended only for supply to the IC. It is not recommended that the C3V3 pin is used to power any other circuitry.

# 2.3 Charge pump

The charge pump uses two external flying capacitors, which are switched with  $f_{CP}$ . The output of the charge pump has a current limitation. In standby mode or after a global thermal shutdown has been triggered the charge pump is disabled.

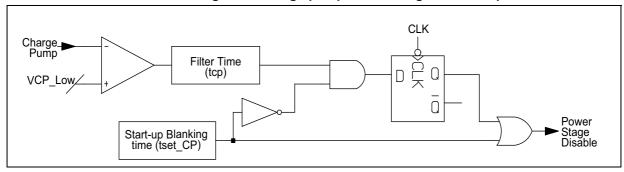

Figure 3. Charge pump low filtering and start-up

At coming out of standby the outputs are enabled  $t_{SET\_CP}$  seconds after the charge pump is re-enabled as long as the  $V_{CPLOW}$  threshold is achieved. The CPLOW bit will remain set, indicating that the charge pump was low since the last reading of the register.

At any time the charge pump output voltage drops below  $V_{CPLOW}$  the CPLOW bit is set and the internal half bridges and the external H-Bridge MOSFET gate drivers are pulled low. After a CPLOW event the outputs are re-enabled  $t_{CP}$  seconds after the charge pump voltage rises above  $V_{CPLOW}$ . Actuation can be restarted via SPI frame or EN\_OUT rising edge according to configuration registers. In this case the outputs that are actuated by the output override (OUTx\_on) bits will automatically turn back on when the charge pump is above CPLOW.

An over voltage or under voltage fault (VSovsd, VDDuv, V3V3uv) will disable the charge pump only while that condition exists. The charge pump will automatically restart once the over voltage or under voltage fault is no longer present.

In the case of a global TSD event all of the TSD flags must be cleared or the ACT\_OFF control bit must be reset to re-enable the Charge pump.

Any time the charge pump is enabled, re-enabled or restarted the drivers will not be available until after  $t_{set\_CP}$  and the charge pump voltage exceeds the  $V_{CPLOW}$  threshold (see *Figure 3*).

4

DS12511 Rev 5 15/88

In all cases the CPLOW bit will remain set indicating that the charge pump was low since the last read & clear of the register.

The charge pump frequency can be dithered to reduce the impact on radio frequency emissions. This option is set via bit DITHN in register 03H. By default DITHN=0 and dithering is enabled.

It is not recommended that the CP pin is used to power other circuits. The charge pump current capability is intended only for the IC and reverse battery MOSFET. This supply cannot be used for other circuits without potentially causing issues.

# 2.4 Output functionality

There are two groups with three drivers each. The three drivers in each group can be paralleled or driven independently.

The output configuration registers identify which outputs are tied together for driving and current regulation purposes.

The output configuration registers also provide for a range of current regulation levels and on-time durations.

The set up prior to command an actuation requires the following global commands. These are typically set at initialization and are not needed to be altered:

- 1. If initiating a timed actuation by SPI command:

- a) After power on reset, with all registers cleared, raise the EN\_OUT pin. If the EN\_OUT pin is hardwired no action needed.

- 2. Register 00H:

- a) Set the desired PWM regulation frequency.

- 3. Register 01H:

- a) No activity at this time.

- Register 02H:

- a) Set the on-time duration for the actuation.

- b) Set the braking time duration after the actuation.

- Disable any outputs not using dynamic braking (typically, these outputs would not participate in the locking system).

- 5. Register 03H:

- a) Set the groups. This determines which outputs are in parallel (if any).

- b) Set the Thermal shutdown reaction (Global or individual).

- c) Set the PWM frequency dithering on/off. Dithering is automatically on (DITH=0).

- d) Set the Global fault indication bit if desired.

- 6. Register 04H and 05H

- a) Set the current regulation /PWM duty cycle levels for each of the outputs / groups. If two internal switches are driving both ends of a load then only one should be current regulating / PWMming.

- Register 06H

- Set the Drain-Source monitoring parameters (amplitude and duration) for the external MOSFETs.

L99UDL01 Device description

Commanding the outputs then requires:

- 1. Register 00H:

- a) Set the polarity of the internal switches (HS/LS)

- 2. Register 01H:

- a) Set the polarity of the external switches (HS/LS)

- 3. Initiate the timed actuation:

- a) If by SPI, then the OUT\_ON bit may be set in register 01H. This can be done concurrently with programming register 01H (step 2 above) as long as the EN OUT pin is high.

- b) If initiating timed actuation by the EN\_OUT pin then raise the EN\_OUT pin. Timed actuation will occur as long as the EN\_OUT pin is high.

The unregulated side is protected by the overcurrent protection.

All outputs, internal and external, are driven with active circuitry. If indefinite dynamic braking is not enabled, once an actuation cycle is completed and all devices have been commanded off, the active circuitry is disabled after ~10 µs to reduce quiescent loading. All outputs are then in a passive off state that will keep the outputs off (gates tied to their sources) in the face of noise on the load or supply.

If indefinite braking is enabled, then the active circuitry will remain active for all outputs (even if dynamic braking is disabled for that output).

# 2.4.1 Integrated half bridge drivers (OUT1-OUT6)

These outputs are configured as switching drivers incorporating active recirculation to minimize power dissipation. The dead time between high and low side drivers is fixed within the functionality of the output drivers.

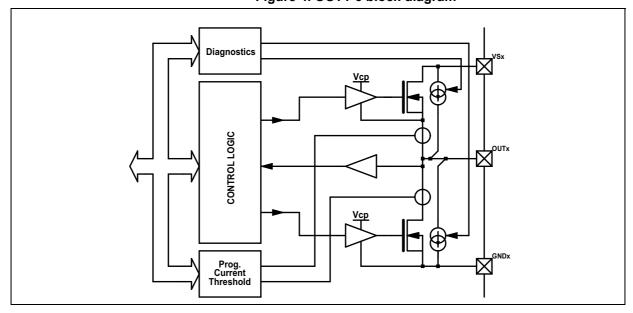

Figure 4. OUT1-6 block diagram

All the integrated outputs can be driven in timed voltage control (PWM duty cycle), timed current regulation control or on/off control.

DS12511 Rev 5 17/88

These outputs have over current protection, under current detection, and off-state diagnostics. Off state diagnostics may provide for non-active detection of Lock motor status. The output rising and falling times are controlled to provide the lowest EMI while minimizing the switching losses. This is done by controlling the edges to smooth out the corners of the waveform while maintaining a fast transition from one level to the other.

#### **Active freewheeling**

Active freewheeling is an automatic function. Whenever the output voltage approaches the freewheeling rail, the freewheeling element becomes active. That is, when the High side is driving the load and the low side MOSFET is acting as the freewheeling element the low side MOSFET is only enabled when the voltage falls below  $V_{DS\_ON\_LS}$  (50 mV typ). Conversely, if the low side MOSFET is the driving element the high side MOSFET is not active unless the voltage is above  $V_{DS\_ON\_HS}$  (Vs-1 V typ).

This poses some limitation with respect to shorted load diagnostics. See *Limitations due to active freewheeling*.

#### **Current regulation control**

All integrated outputs can work in current regulation mode. Each power MOS has a configurable bidirectional current sense which provides an image of the load current during on mode and recirculation phase. This current image is compared to the target value written in the configuration register in a digital algorithm so that mean current value through the load is equal to the chosen value.

Figure 5. Current Control Loop

L99UDL01 Device description

Figure 6. Unregulated door lock motor current

Figure 7. Slightly regulated door lock current

Figure 8. Heavily regulated door lock current

#### **Control loop parameters**

The control loop for the current regulation is programmable. There are two parameters that are adjustable through SPI. It should be noted that there is a default setting that will work for the most of the lock motor applications known. These parameters are provided to aid in any possible scenario. Typically, these parameters can be left alone:

- Integral Gain, Ki, (3 bits)

- Proportional Gain, Kp, (3 bits)

Integral and proportional gain settings are the standard control loop parameters for integral gain and proportional gain. The default settings for these parameters are  $Ki = 2^{-2} = 1/4$ , and  $Kp = 2^{6} = 64$ .

This register is set up for a nominal control loop. Most, if not all, applications will be stable enough to use this default setting.

Current regulation mode can be initiated via EN\_OUT rising edge or via OUT\_ON bit (register 01H) provided EN\_OUT=1 and OUTx\_on =0 for the timed output x. Once started, a timed actuation can be stopped only with EN\_OUT=0, fault condition, Emergency mode or at the natural end of timers. No other time controlled output can be started when a timed actuation is ongoing.

#### **Current feedback**

The Integrated drivers can provide a 10 bit word representing the current regulation loop current value. This is done to provide load integrity information in addition to the CNR bit (a current not reached, CNR, bit is set if the current in the output does not reach the regulated current level during the entire on-time actuation).

This is a buffered value of the 10 bit up/down counter in the current regulation loop. This information is retrieved at the falling edge of CSN when accessing the appropriate current loop register.

The conversion of the 10 bit information found in registers 13h – 18h to a typical value of current is a simple equation:

Typical Current =

$$\frac{Reg_x}{0xA0h}$$

The current feedback can be read during the actuation phase as well as during the dynamic braking. In the latter case, the current feedback cannot be read when the dynamic braking is disabled for that output (DBN\_x bit). The current feedback can be read for any actuated integrated output regardless of its configuration (current mode, voltage mode and overridden).

In indefinite braking mode, the current feedback is disabled after the first 100ms.

#### PWM frequency adjustment

The current regulation or PWM control PWM frequency can be adjusted to optimize the motor current regulation. This is accomplished in 2 kHz intervals from 10 kHz to 24 kHz using three FPWMx bits in register 00H.

L99UDL01 Device description

#### 2.4.2 External FET controllers

The external FET controllers are designed to be drivers for MOSFETS configured as half bridges. Alternatively, each half bridge controller may be configured as a single high-side driver or a single low side MOSFET controller. These outputs are not intended to be PWMmed and are limited in their switching speed to aid in reducing EMC issues.

The external MOSFETS are protected by a programmable drain to source voltage ( $V_{DS}$ ) monitor. Both the voltage threshold and reaction delay are programmable. The default setting is 1 V for 1  $\mu$ s.

In the event of a Drain-Source fault the appropriate fault bit will be set as well as a fault bit in the Global Status Byte. A faulted driver will be switched off and is enabled again only after clearing fault bit (register 11H).

Since these outputs are not intended to be PWMmed there is no active recirculation option.

The external MOSFET control has off-state diagnostic capability as well.

The external MOSFETs can be driven in timed on/off control or purely on/off control.

#### External MOSFET dead time control

At the end of every timed actuation all outputs are pulled to ground for the off-time duration as determined in the control register 02H. This requires that the external H-Bridge controller have a dead time between when the high side MOSFET is commanded off and when the low side MOSFET is commanded on. This is a fixed value set to t<sub>DT</sub> (6 µs).

#### 2.4.3 DOUT

The Data OUT pin may provide the host processor with real time fault indication. The GSBN (Global Status Bit NOT) bit may be reflected on this pin when this feature is enabled. This feature may be enabled by setting the Global Fault Indication (GFI) bit found in the control register 03H (bit7).

### 2.4.4 EN OUT

The output Enable pin has three states: It enables the output functionality while held high, and disables the outputs when held low. This pin can also be used to initiate an output timed actuation, based on programmed parameters, on a rising edge. There is a filter time on the rising edge of EN\_OUT of  $t_{\text{EN}}$ . This is used to prevent noise from accidentally actuating a timed actuation.

#### 2.4.5 Paralleling outputs

Up to three of the integrated outputs can be paralleled in two groups for the purpose of sharing higher current loads.

Some of the possible combinations:

- 2 groups of 3

- 2 groups of 2 and 2 single outputs

- 1 group of 2, 1 group of 3 and a single output

- 1 group of 3, and 3 single outputs

- 1 group of 2, and 4 single outputs

- 6 single outputs, no groups

DS12511 Rev 5 21/88

Paralleled outputs have all their current regulation, protection, and diagnostic information tied together. Once a set of outputs are grouped then the master registers are used to command and diagnose that group. The master registers are output 1 for outputs 1 through 3 and output 4 for outputs 4 through 6.

When paralleling multiple half bridges all the channels in the group will provide the current monitoring for the master current regulation loop.

Current values programmed for each channel in the group are added to create the total current for the group. Each output can have different values (for ex; 1 A for ch1 and 1.2 A for ch2 to generate 2.2 A total current regulation for the group). The Slave outputs must be programmed as current regulating when using current regulation.

PWM values will be taken from the master registers only. The remaining slave registers will be ignored when in PWM mode. The Slave outputs must be programmed as PWM when using PWM mode.

All diagnostics in a group must be cleared prior to restarting that group. For grouped outputs, only the Master registers (OUT1 or OUT 4) contain the correct fault information for their respective groups. Any diagnostic information must be gleaned from the Master. Slave registers may or may not indicate faults.

#### 2.4.6 Output override

The outputs can be driven directly, outside of a timed actuation, by the use of the Output Override bits (OUTx\_on, EX\_OUTx\_on in register 01H). When any of these bits are high then the corresponding output(s) will be enabled according to the configuration settings (polarity only). Overridden outputs are fully protected. Emergency Override affects the protections for overridden outputs in the same manner as timed outputs.

The overridden outputs will not current regulate nor will they be affected by a timed actuation.

Overridden outputs must not be modified (on, off, or polarity) at the initialization of (OUT\_ON=1) or during a timed actuation unless an emergency override is enabled. Indefinite dynamic braking must be disabled prior to change any of the output override bits (OUTx on and EX OUTx on in register 01H) or any of the overridden output polarities

L99UDL01 Device description

# 2.5 Operating modes

We can distinguish among 4 different operating modes: Normal mode, Standby mode, Sleep mode and Emergency override mode. The L99UDL01 powers up in Standby mode by default.

Figure 9. State diagram

In Sleep mode no active circuitry is supplied. In standby mode logic is initialized but not operational. There is no function present in either modes in order to minimize the current consumption. Only wake-up circuitry is active in Standby mode.

#### 2.5.1 Sleep mode

In sleep mode all circuitry is disabled. There is no charge pump or internal voltages. This is the lowest quiescent current mode.

Sleep mode is entered when the VDD input falls below VDD<sub>SLEEP\_F</sub>. Prior to entering sleep mode all control registers are reset to their default values. Sleep mode is exited when VDD rises above VDD<sub>SLEEP R</sub>. Sleep mode only exits into Standby mode.

To avoid anomalous behavior during transition into sleep mode, sleep mode should always be entered from standby mode. Entering sleep mode directly from any other mode is not supported.

4

DS12511 Rev 5 23/88

#### 2.5.2 Standby mode

Standby mode disables all circuitry except for the 3V3 pre-regulator and the circuitry related to watch for a wake-up event. Nothing else is active. The charge pump is off and the outputs are disabled.

Standby is entered by:

- SPI command from Normal Mode,

- When exiting Sleep Mode,

- When VDD falls below VDDUV

- When recovering from a 3V3 reset event.

Entering Standby by SPI command while in timed actuation, or when any output is active, is not supported. Doing this may cause adverse responses from the device.

In addition to Emergency override mode Standby is the only mode that Normal mode can be entered from. Transition to Standby Mode from Emergency Mode by SPI command is not supported.

To attain the low quiescent state in Standby mode, the EN\_OUT pin must be held low.

#### 2.5.3 Normal mode

The L99UDL01 will exit Standby mode to Normal mode when the CSN pin is pulled down as long as VDD>VDD $_{UV}$ . There is a delay from the falling edge of CSN to when Normal mode is active ( $t_{Wake\_up}$ ). This delay is related to the charge pump and 3V3 regulator stabilization. When the 3V3 voltage has reached its proper level, the SDO pin is pulled low from a tristated condition. At that point, logic is operating, all circuits are activated and the SPI controller can be used to update the register configuration.

When coming out from Standby, the configuration registers are set to their default values. In this startup phase, the Charge Pump circuit starts working. In this case the drivers can be enabled after  $t_{\text{set\_CP}}$  and the charge pump voltage exceeds the  $V_{\text{CPLOW}}$  threshold. An actuation can be initiated via EN\_OUT pin or via an appropriate SPI frame. The CPLOW bit is not cleared until the register is read and cleared.

#### 2.5.4 Emergency mode

Emergency mode is a crash override mechanism that will interrupt any current actuation command in progress and drives outputs according to the programmed values in the command and configuration registers.

This mode also overrides all protections. In an Emergency mode the device will not latch off if an overcurrent threshold is exceeded. Instead of latching off the driver and reporting a fault the output will continue to retry as in Normal mode.

All faults will be reported while not acted upon.

Emergency mode is initiated when (1, 0) is entered in the register containing the EMCY bits (register 01H). All other EMCY bit configurations result in normal mode.

When emergency is enabled any changes to the Output Override bits will be implemented and the current timed actuation activity will be stopped. To initiate a new timed actuation routine the OUT\_ON bit must be set or the EN\_OUT pin must be toggled.

While in Emergency mode the status bits (STAT [1:0]) will be automatically cleared whenever there is a write to CR01H.

L99UDL01 Device description

### 2.6 Diagnostics and protections

#### 2.6.1 Shorted load detection

All integrated drivers are protected for shorts to ground or supply by a simple over current detection and latch off strategy. At turn on there is a blanking time (t<sub>OC\_BLANKING</sub>) where the output is given time to turn on. After the blanking time if the output current exceeds (I<sub>OC</sub>) for longer than the filter time the faulted output(s) will be latched off.

If a shorted condition occurs after an output is active just the filtering time applies to the latch-off action.

The fault will be reported in the fault register (Register 10H). The Global fault Functional Error 1 bit (FE1) will also be set.

$I_{OC}$  applies to a single output. Multiple outputs in parallel will multiply the  $I_{OC}$  value accordingly. Two outputs in parallel will garner a 2x increase in the  $I_{OC}$  value. The same concept applies in order to have three outputs in parallel.

Since this system relies on current limitation for normal running  $I_{OC}$  can occur in one of two ways. First, the  $I_{OC}$  threshold can occur if the current rise time is longer than the minimum on time ( $t_{OC}$  BLANKING) of the driver. This occurs as a shorted load has very little inductance.

The second method is when the integrated driver is programmed as a simple switch and does not provide the current regulation. Then  $I_{OC}$  is the only means of overcurrent protection.

The external half bridges are used as a simple switch (not current regulated). However, when both sides of the H-Bridge are set up by the use of integrated half bridges (outputs 1-6) then one of the integrated half bridges should be programmed as a simple switch. This is done by programming the output to be Voltage controlled (by setting the PWM\_SW\_x bit to 1) and setting the duty cycle to 100%.

This allows the other half bridge to provide the lock motor current regulation without confusion.

Shorted outputs may be detected in the off-state as well (see Section 2.6.3).

#### Limitations due to active freewheeling

Due to how active freewheeling is performed (see *Active freewheeling*) a short to the drive rail (a short to B+ for high side drive / low side freewheeling and vice versa) prior to activation is not detected. The freewheeling element is never active and cannot experience a shorted condition.

As a result, a shorted drive element during current regulation (C/PWM\_SW\_x=0) may appear as a CNR (current not reached). A shorted drive element cannot be detected if PWM control (C/PWM\_SW\_x=1) is selected.

A shorted driving element can be detected by reading the current feedback for that output or by an off state fault detection. Only if the short occurs while freewheeling, can a short be detected on the freewheeling element of the output.

#### **External MOSFET protection**

In case of the external half bridges Drain-Source voltage detection is implemented as an overload protection once the driver is active. The Drain-Source threshold,  $V_{DS\_TH}$ , and duration,  $t_{VDS\_BLANK}$ , are both programmable with a wide range to select from.

DS12511 Rev 5 25/88

#### 2.6.2 Thermal protection

There is a thermal sensor associated with each of the internal half bridges. There are two reported thermal thresholds. These are thermal warning,  $T_{Wx}$ , and thermal shutdown,  $T_{SDx}$ .

Thermal warning only provides a SPI register indication of the condition ( $T_{Wx}$ ). Thermal shutdown either shuts down the offending half bridge or disables the entire device. This option is programmable via SPI command. Thermal shutdown is indicated in the SPI register via the  $T_{SDx}$  bits.

If more than one driver is linked in parallel the hottest driver will cause a thermal indication ( $T_{Wx}$  or  $T_{SDx}$ ). All linked drivers have their diagnostic bits linked as well. That is, they will all demonstrate the same diagnostic state.

Drivers cannot be activated until its corresponding temperature is below thermal shutdown threshold and corresponding fault register bit is cleared.

#### 2.6.3 Off state load detection

Along with the standard shorted load and thermal protections the L99UDL01 has the ability to verify load integrity without actuating loads.

This is done by incorporating enable-able weak pull-up (ODCHx) / pull-down (ODCLx) currents at each output. By using the weak pull-up/pull-down currents the following conditions can be determined:

- Shorted output to either ground or supply

- Open load

One method would be to first bias a motor node by either a weak pull-up or weak pull-down current then reading the Dynamic Output State (DOSx, DOS\_EXTx) bits. A weak pull-up on one output should cause all nodes associated with that output to pull high. A weak pull-down on one output should cause all nodes associated with that output to pull low. An open circuit or shorted output would prevent either one or the other from happening.

### 2.6.4 Enable-able weak pull-up/down currents

The weak pull-up/pull-down currents are enable-able through SPI command (register 06H and 07H). Each output can have enabled a weak pull up current or a weak pull down current individually.

Activating a weak pull-up on one of a paralleled output and a weak pull-down in another of the same parallel group will be ignored and set a WRT\_fail bit. Alternatively, activating a weak pull-up and a weak pull-down on the same output will be ignored and set a WRT\_fail bit

Weak pull-up/pull-down currents are available for both the integrated and the external Half-bridge controllers. This allows the user to determine if there is a short to ground or supply condition on these outputs prior to actuation.

# 2.6.5 Dynamic output state detection

All outputs, internal and external have the ability to detect if the output voltage is above or below a specific threshold (V<sub>OUT\_th</sub>). If the Output voltage at the time CSN falls is above the threshold the corresponding bit in Diagnostic register 11H is set high. If the output voltage is below the threshold then the corresponding bit is set low.

# 3 Application schematic

Figure 10. Typical application diagram example

- Recommended VCP\_out capacitors for optimum EMC performance. These capacitors need to be placed as close to the VS-VCP pins as possible to optimize their effectiveness at reducing EMC.

- 2. A 22 nF capacitor should be used on each output for ESD performance and output stability.

- 3. The Bulk capacitance should be dimensioned according to the user's design practices.

27/88

Electrical characteristics L99UDL01

# 4 Electrical characteristics

# 4.1 Absolute maximum ratings

The absolute maximum ratings are the values at which if exceeded the device may become damaged.

Table 3. Absolute maximum ratings

| DIN/Deveronter Neme                                           | Parameter                                                                              |                                            | Value                                     |                                                               | 11.7 |

|---------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------|-------------------------------------------|---------------------------------------------------------------|------|

| PIN/Parameter Name                                            | Parameter                                                                              |                                            | min                                       | max                                                           | Unit |

| VS <sub>X</sub>                                               | Supply Voltage (Continuous)                                                            |                                            | -0.3                                      | +28                                                           | V    |

| VS <sub>X</sub>                                               | Supply Voltage 400 ms transient (Loa                                                   | d Dump)                                    | -0.3                                      | +40                                                           | V    |

|                                                               | High voltage signal pin                                                                | V <sub>S</sub> ≤ 26 V                      | V <sub>S</sub> -0.3                       | to V <sub>S</sub> +14                                         | V    |

| V <sub>CP</sub>                                               | High voltage signal pili                                                               | V <sub>S</sub> > 26 V                      | V <sub>S</sub> -0.                        | 3 to +40                                                      | V    |

| VDD                                                           | VDD input                                                                              |                                            | -0.3                                      | +6                                                            | V    |

| 3V3                                                           | 3.3 V regulator maximum allowable vo                                                   | oltage                                     |                                           | 3.6                                                           | V    |

| GNDx                                                          | Differential voltage between Grounds                                                   | and TAB                                    | -0.3                                      | +0.3                                                          | V    |

| DRNx                                                          | -                                                                                      |                                            | -0.3                                      | V <sub>S</sub> +0.3                                           | V    |

| SDCv                                                          | t < 200 ns                                                                             |                                            | -5                                        |                                                               | V    |

| SRCx                                                          | Continuous                                                                             |                                            | -1                                        | V <sub>S</sub> +0.3                                           | V    |

| GATEHx                                                        | External high side MOSFET control                                                      |                                            | V <sub>SRCx</sub> - 0.3                   | V <sub>SRCX</sub> +12,<br>V <sub>CP</sub> +0.3 <sup>(1)</sup> | V    |

| GATELx External low side MOSFET control                       |                                                                                        | -0.3                                       | 12<br>V <sub>CP</sub> +0.3 <sup>(1)</sup> | V                                                             |      |

| DOUT, EN_OUT                                                  | -                                                                                      |                                            | -0.3                                      | VDD+0.3                                                       | V    |

| OUT <sub>X_max</sub>                                          | All half bridge outputs                                                                |                                            |                                           | V <sub>S</sub> +0.3 <sup>(1)</sup>                            | V    |

| OUT <sub>X_min</sub>                                          | All internal half bridge outputs 4 A fror outputs inactive, t <sub>Recirc</sub> <10 ms | n ground,                                  | -0.3                                      |                                                               | V    |

| V <sub>CP1M</sub> ,V <sub>CP2M</sub> High voltage signal pins |                                                                                        | V <sub>S</sub> -0.3 to V <sub>S</sub> +0.3 |                                           | V                                                             |      |

| V <sub>CP1P</sub>                                             | High voltage signal pins                                                               | High voltage signal pins                   |                                           | to V <sub>S</sub> +10                                         | V    |

| V <sub>CP2P</sub>                                             | High voltage signal pins                                                               |                                            | V <sub>S</sub> -0.6                       | to V <sub>S</sub> +10                                         | V    |

| CSN, SCK, SDI, DSO                                            | -                                                                                      |                                            | -0.3                                      | VDD+0.3                                                       | V    |

| T <sub>J(Operating)</sub>                                     | Junction temperature                                                                   |                                            | -40                                       | 175 <sup>(2),(3),(4)</sup>                                    | °C   |