### Twelve channel valve driver

### Datasheet - production data

### **Features**

- Four low side switched output drivers with 0.1 Ω R<sub>ds.ON</sub> at 25°C

- Possibly configurable as PWM controlled adding external freewheeling diodes

- Two low side PWM controlled output drivers with 0.1 Ω R<sub>ds,ON</sub> at 25 °C and integrated active freewheeling diodes

- Six low side current controlled output drivers with 0.16 Ω R<sub>ds,ON</sub> at 25 °C and integrated active freewheeling diodes

- Current accuracy:

- $-10\% (I_{load} < 800 \text{ mA})$

- $-6\% (I_{load} > 80 0mA)$

- All outputs with integrated 35 V zener clamp

- Five pin SPI port (four standard pins plus additional SPI enable input pin)

- Six serial high speed inputs for output control

- High level diagnostic, including silent valve driver test

- Direct disable of outputs with an external pin

- Programmable jitter frequency of PWM and current controlled outputs

- TQFP100 exposed pad package

# Description

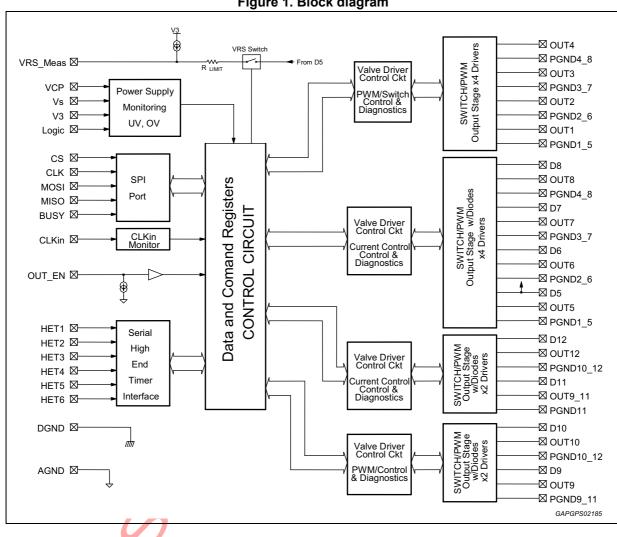

The L9390 is a twelve output low side valve driver designed for use in an ABS/ESP vehicle system. All outputs are PWM configurable, while six out of twelve are current regulated. Each of the twelve outputs is open drain configured and has a built-in 35 V clamp. Eight of the twelve have integrated active freewheeling diodes for active rectification of the PWM controlled load.

In order to minimize electromagnetic emissions during load actuation, the possibility to control output slopes is provided.

Two separate communication interfaces are present: the SPI port is primarily designated to provide diagnostics and secondary control. The serial High End Timer interface (HET) provides the primary output control functions from on/off switching to current level control commands.

Diagnostic includes over current protection, under current detection, open load detection, loss of ground detection, loss of freewheeling diode, and over temperature detection, output integrity check, SVDT, leakage current test, PWM integrity and functionality check, valve resistance sense check, loss of freewheeling diode detection and more.

Power supply monitoring is also included.

**Table 1. Device summary**

| Part number | Package                                | Packing |

|-------------|----------------------------------------|---------|

| L9390       | TQFP100 14x14x1.0mm (exposed pad down) | Tray    |

September 2013 DocID024635 Rev 2 1/55

# Contents

Contents

| 1 | Bloc  | k diagra  | ım                                                                   | 7    |

|---|-------|-----------|----------------------------------------------------------------------|------|

| 2 | Pins  | descrip   | tion                                                                 | 8    |

| 3 | Elec  | trical sp | ecifications                                                         | . 10 |

|   | 3.1   | Absolu    | te maximum ratings                                                   | . 10 |

|   | 3.2   | Therma    | al data                                                              | . 10 |

|   | 3.3   |           | cal characteristics                                                  |      |

| 4 | Appl  |           | information                                                          |      |

|   | 4.1   | Supply    | monitoring                                                           | . 18 |

|   |       | 4.1.1     | Low voltage inhibit (Vs(LVI))                                        | . 18 |

|   | 4.2   | Genera    | al output functionality                                              | . 18 |

|   |       | 4.2.1     | Edge shaping                                                         | . 19 |

|   |       | 4.2.2     | Out1-out4                                                            | . 19 |

|   |       | 4.2.3     | Out5-out8                                                            | . 20 |

|   |       | 4.2.4     | Out9-out10                                                           | . 21 |

|   |       | 4.2.5     | Out11-out12                                                          | . 22 |

| 5 | Seria | al comm   | unications                                                           | . 23 |

|   | 5.1   | SPI da    | ta bus                                                               | . 23 |

|   | 5.2   | SPI sat   | ety features                                                         | . 23 |

|   | 5.3   | SPI coi   | mmands / registers                                                   | . 24 |

|   |       | 5,3.1     | Revision ID, Device ID, SPI status                                   |      |

|   |       | 5.3.2     | Direct driving of outputs, edge shaping, feedback configuration      |      |

|   |       | 5.3.3     | Input diagnostic feedback                                            | . 27 |

|   |       | 5.3.4     | Output feedback, one address per output                              | . 28 |

|   |       | 5.3.5     | Current regulation commands, two outputs per address                 | . 29 |

|   |       | 5.3.6     | Diagnostics - feedback, Dx lost, over temperature, power ground lost | . 30 |

|   |       | 5.3.7     | Gate monitoring feedback                                             | . 30 |

|   |       | 5.3.8     | Current regulation P/I parameters                                    | . 31 |

|   |       | 5.3.9     | Built in self test functionality                                     | . 32 |

|   |       | 5.3.10    | Serial HET bus configuration                                         | . 32 |

Information classified ST Restricted - Do not copy (See last page for obligations)

L9390

Contents

| 6 | Diagr | nostics   |                                                   | 34   |

|---|-------|-----------|---------------------------------------------------|------|

|   | 6.1   | Conditio  | ons that cause a reset                            | 34   |

|   |       | 6.1.1     | Under voltage                                     | . 34 |

|   |       | 6.1.2     | OUT_EN = 0 ("EN_set" Bit = 0)                     | . 34 |

|   |       | 6.1.3     | CLKin-failure ("CLKin_fail" Bit = "1")            | . 35 |

|   | 6.2   | Fault m   | onitoring                                         | 35   |

|   |       | 6.2.1     | Open load detection (off-state)                   | . 35 |

|   |       | 6.2.2     | Under current detection                           | . 35 |

|   |       | 6.2.3     | Over current detection                            | . 36 |

|   |       | 6.2.4     | Over temperature detection                        | . 36 |

|   |       | 6.2.5     | Loss of PGND                                      | . 37 |

|   |       | 6.2.6     | Loss of freewheeling diode (Dx)                   | . 38 |

|   |       | 6.2.7     | Output integrity check                            | . 38 |

|   |       | 6.2.8     | PWM-Integrity monitor                             | . 39 |

|   |       | 6.2.9     | PWM-check functionality                           | . 40 |

|   |       | 6.2.10    | Current regulator PWM-Feedback                    | . 41 |

|   |       | 6.2.11    | Current not achieved detection                    | . 41 |

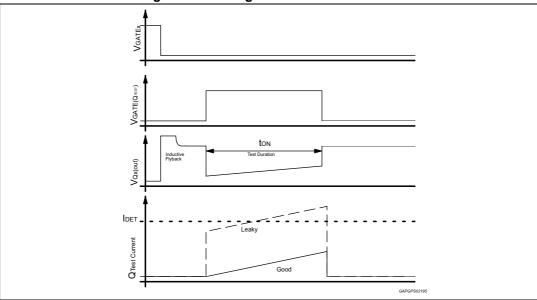

|   |       | 6.2.12    | Leakage current test                              | . 41 |

|   |       | 6.2.13    | Valve resistance sense switch                     | . 43 |

|   |       | 6.2.14    | Valve resistance test sequence:                   | . 44 |

|   | 6.3   | Addition  | al monitoring                                     | 44   |

|   |       | 6.3.1     | SGND-loss                                         | . 44 |

|   |       | 6.3.2     | SPI-monitoring (SPI-watchdog)                     | . 44 |

|   |       | 6.3.3     | Voltage reference monitoring (bandgap monitoring) | . 45 |

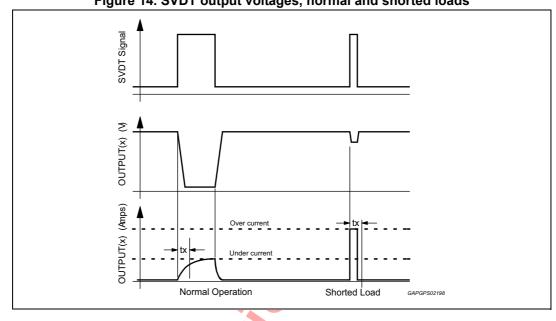

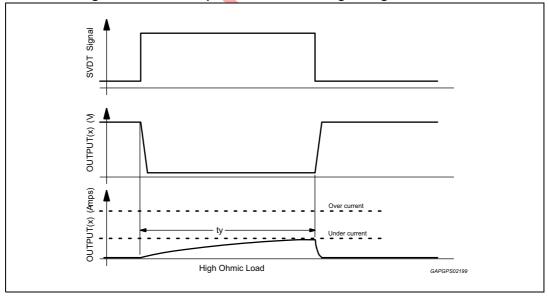

|   | 6.4   | Silent va | alve driver test (SVDT)                           | 45   |

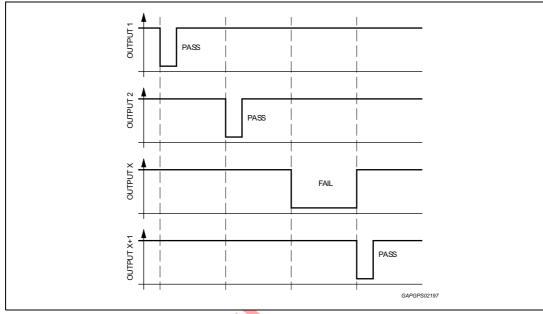

|   |       | 6.4.1     | The SVDT test sequence:                           | . 46 |

|   |       | 6.4.2     | Built in self-test (BIST)                         | . 48 |

|   |       | 6.4.3     | Built-in self test CRC initiator and results      | . 50 |

|   |       | 6.4.4     | SPI command / register summary                    | . 51 |

| _ |       |           |                                                   |      |

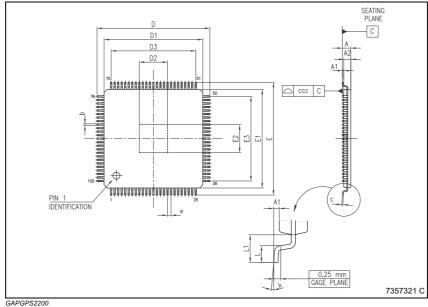

| 7 | Packa | age info  | rmations                                          | 53   |

| 8 | Revis | ion hist  | ory                                               | 54   |

List of tables L9390

# List of tables

| Table 1.  | Device summary                                                                       | 1    |

|-----------|--------------------------------------------------------------------------------------|------|

| Table 2.  | Pins description                                                                     |      |

| Table 3.  | Absolute maximum ratings                                                             |      |

| Table 4.  | Thermal data                                                                         |      |

| Table 5.  | V <sub>S</sub> supply voltage                                                        |      |

| Table 6.  | V3 3.3V supply                                                                       |      |

| Table 7.  | VCP operating                                                                        |      |

| Table 7.  | Band gap                                                                             |      |

|           | Output driver                                                                        |      |

| Table 9.  |                                                                                      |      |

| Table 10. | Active freewheeling diode                                                            |      |

| Table 11. | PWM output timing characteristics with edge shaping (SHAPE_EN=1)                     |      |

| Table 12. | PWM output timing characteristics without edge shaping (SHAPE_EN=0)                  |      |

| Table 13. | PWM output timing characteristics without edge shaping                               |      |

| Table 14. | Input buffer parameters, CLK, CS, MOSI                                               |      |

| Table 15. | Input buffer parameters, MISO, EN                                                    | . 14 |

| Table 16. | SPI timing parameters                                                                | . 14 |

| Table 17. | CLKin threshold parameters                                                           |      |

| Table 18. | CLKin timing parameters                                                              |      |

| Table 19. | Outputs disable registry map                                                         | . 18 |

| Table 20. | SPI outputs disable                                                                  | . 18 |

| Table 21. | Diagnostic output                                                                    | . 19 |

| Table 22. | Acknowledgement / wake-up                                                            | . 24 |

| Table 23. | Revision ID, Device ID, SPI status characteristics                                   | . 25 |

| Table 24. | Direct driving of outputs, edge shaping, feedback configuration characteristics      |      |

| Table 25. | Input diagnostic feedback characteristics                                            |      |

| Table 26. | Output feedback, one address per output characteristics                              |      |

| Table 27. | Current regulation commands, two outputs per address characteristics                 |      |

| Table 28. | Diagnostics - feedback, Dx lost, over temperature, power ground lost characteristics |      |

| Table 29. | Gate monitoring feedback characteristics                                             |      |

| Table 30. | Current regulation P/I parameters characteristics                                    |      |

| Table 31. | Built in self test functionality characteristics                                     |      |

| Table 32. | Serial HET input bit description                                                     |      |

| Table 33. | Under-voltage characteristics                                                        |      |

| Table 34. | Open load characteristics                                                            |      |

| Table 35. | Under current characteristics                                                        |      |

| Table 35. | Over current characteristics                                                         |      |

| Table 30. |                                                                                      |      |

| Table 37. | Sensor outputs                                                                       |      |

|           |                                                                                      |      |

| Table 39. | Power ground outputs                                                                 |      |

| Table 40. | Loss of PGND characteristics                                                         |      |

| Table 41. | Loss of freewheeling diode (Dx) characteristics                                      |      |

| Table 42. | Output integrity check outputs                                                       |      |

| Table 43. | Output integrity check characteristics                                               |      |

| Table 44. | PWM-Integrity monitor characteristics                                                |      |

| Table 45. | On-time level monitoring characteristics                                             |      |

| Table 46. | PWM-check outputs                                                                    |      |

| Table 47. | Current not achieved detection characteristics                                       |      |

| Tahla 18  | Leakage current test characteristics                                                 | 12   |

L9390 List of tables

| Table 49. | SGND-loss characteristics                       | . 44 |

|-----------|-------------------------------------------------|------|

| Table 50. | SPI-monitoring (SPI-watchdog) characteristics   | . 44 |

| Table 51. | Silent valve driver test (SVDT) outputs         | . 45 |

| Table 52. | Silent valve driver test (SVDT) characteristics | . 45 |

| Table 53. | Data results of SVDT                            | . 48 |

| Table 54. | Built-in self test CRC initiator and results    | . 50 |

| Table 55. | SPI command / register summary                  | . 51 |

| Table 56  | Document revision history                       | 54   |

List of figures L9390

# List of figures

| Figure 1.  | Block diagram                                   | 7    |

|------------|-------------------------------------------------|------|

| Figure 2.  | Pins connection diagram (top view)              | 8    |

| Figure 3.  | Output timing                                   | . 13 |

| Figure 4.  | SPI timing diagram                              | . 16 |

| Figure 5.  | Out1-4 block diagram                            | . 19 |

| Figure 6.  | Out5-8 block diagram                            | . 20 |

| Figure 7.  | Outputs 9 and 10 block diagram                  | . 21 |

| Figure 8.  | Outputs 11 and 12 block diagram                 | . 22 |

| Figure 9.  | SPI frame structure                             |      |

| Figure 10. | Leakage detection circuit                       |      |

| Figure 11. | Leakage detection waveforms                     | . 42 |

| Figure 12. | Valve resistance sensing circuit                | . 43 |

| Figure 13. | Sequential nature of the SDVT test              | . 46 |

| Figure 14. | SVDT output voltages, normal and shorted loads  | . 47 |

| Figure 15. | SVDT output waveforms during an high ohmic load | . 47 |

| Figure 16. | Current regulator block diagram                 | . 49 |

| Figure 17. | TOFP100 mechanical data and package dimensions  |      |

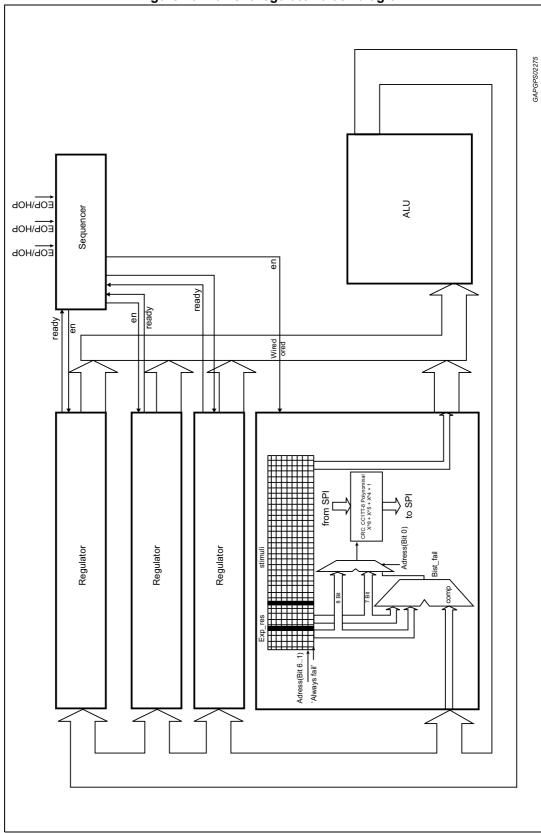

L9390 **Block diagram**

### **Block diagram** 1

Figure 1. Block diagram

ST Restricted

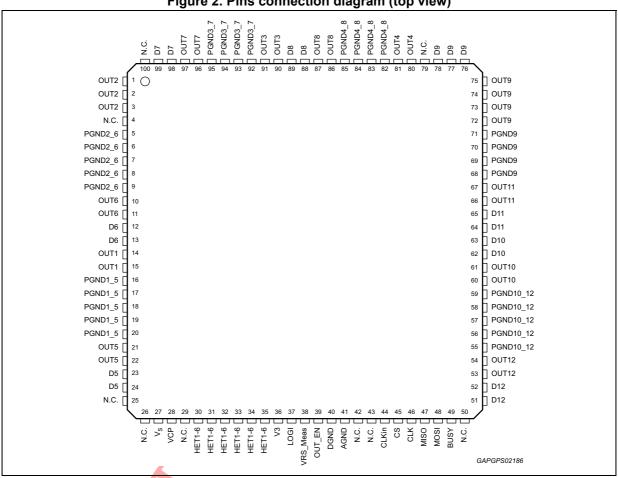

L9390 Pins description

### 2 **Pins description**

Figure 2. Pins connection diagram (top view)

Table 2. Pins description

| Pin#  | Name    | Description                                               |

|-------|---------|-----------------------------------------------------------|

| 1-3   | OUT2    | Valve low side driver output, switched or PWMmed          |

| 4     | N.C.    | Not connected                                             |

| 5-9   | PGND2_6 | Dedicated output power ground                             |

| 10-11 | OUT6    | Valve low side driver output, PWMmed or current regulated |

| 12-13 | D6      | Freewheeling diode cathode                                |

| 14-15 | OUT1    | Valve low side driver output, switched or PWMmed          |

| 16-20 | PGND1_5 | Dedicated output power ground                             |

| 21-22 | OUT5    | Valve low side driver output, PWMmed or current regulated |

| 23-24 | D5      | Freewheeling diode cathode                                |

| 25-26 | N.C.    | Not connected                                             |

| 27    | Vs      | Battery level supply input voltage                        |

| 28    | VCP     | Charge pump voltage input                                 |

L9390 Pins description

Table 2. Pins description (continued)

| Pin#  | Pin # Name Description (continued) |                                                                                      |  |  |  |  |

|-------|------------------------------------|--------------------------------------------------------------------------------------|--|--|--|--|

| 29    | N.C.                               | Not connected                                                                        |  |  |  |  |

| 30-35 | HET1-6                             | Serial high end timer inputs                                                         |  |  |  |  |

| 36    | V3                                 | 3.3V supply input                                                                    |  |  |  |  |

| 37    | LOGI                               | Logic supply input, must be tied to V3                                               |  |  |  |  |

| 38    | VRS Meas                           | Switch connection to pin D5 for the purpose of diagnosing specific load resistances. |  |  |  |  |

| 39    | OUT_EN                             | Enables/ disables all outputs asynchronous to any other commands                     |  |  |  |  |

| 40    | DGND                               | Circuit ground                                                                       |  |  |  |  |

| 41    | AGND                               | Signal ground                                                                        |  |  |  |  |

| 42-43 | N.C.                               | Not connected                                                                        |  |  |  |  |

| 44    | CLKin                              | Clock input for IC                                                                   |  |  |  |  |

| 45    | CS                                 | SPI chip select input                                                                |  |  |  |  |

| 46    | CLK                                | SPI clock input                                                                      |  |  |  |  |

| 47    | MISO                               | SPI master in slave out                                                              |  |  |  |  |

| 48    | MOSI                               | SPI master out slave in                                                              |  |  |  |  |

| 49    | BUSY                               | SPI enable input                                                                     |  |  |  |  |

| 50    | N.C.                               | Not connected                                                                        |  |  |  |  |

| 51-52 | D12                                | Freewheeling diode cathode                                                           |  |  |  |  |

| 53-54 | OUT12                              | Valve low side driver output, current regulated                                      |  |  |  |  |

| 55-59 | PGND10_12                          | Dedicated output power ground                                                        |  |  |  |  |

| 60-61 | OUT10                              | Valve low side driver output, current regulated                                      |  |  |  |  |

| 62-63 | D10                                | Freewheeling diode cathode                                                           |  |  |  |  |

| 64-65 | D11                                | Freewheeling diode cathode                                                           |  |  |  |  |

| 66-67 | OUT11                              | Valve Low Side Driver output, PWMmed                                                 |  |  |  |  |

| 68-71 | PGND9                              | Dedicated output power ground                                                        |  |  |  |  |

| 72-75 | OUT9                               | Valve low side driver output, PWMmed                                                 |  |  |  |  |

| 76-78 | D9                                 | Freewheeling diode cathode                                                           |  |  |  |  |

| 79    | N.C.                               | Not connected                                                                        |  |  |  |  |

| 80-81 | OUT4                               | Valve low side driver output, switched or PWMmed                                     |  |  |  |  |

| 82-85 | PGND4_8                            | Dedicated output power ground                                                        |  |  |  |  |

| 86-87 | OUT8                               | Valve low side driver output, PWMmed or current regulated                            |  |  |  |  |

| 88-89 | D8                                 | Freewheeling diode cathode                                                           |  |  |  |  |

| 90-91 | OUT3                               | Valve low side driver output, switched or PWMmed                                     |  |  |  |  |

| 92-95 | PGND3_7                            | Dedicated output power ground                                                        |  |  |  |  |

| 96-97 | OUT7                               | Valve low side driver output, PWMmed or current regulated                            |  |  |  |  |

| 98-99 | D7                                 | Freewheeling diode cathode                                                           |  |  |  |  |

| 100   | N.C.                               | Not connected                                                                        |  |  |  |  |

# 3 Electrical specifications

# 3.1 Absolute maximum ratings

Table 3. Absolute maximum ratings

| Pin/parameter name                      | Parameter                                | Min. | Max.                | Unit |

|-----------------------------------------|------------------------------------------|------|---------------------|------|

| V                                       | Supply voltage (continuous)              | -0.3 | +20                 | V    |

| V <sub>S</sub>                          | Supply voltage (t < 5 min)               | -    | +27                 | V    |

| V <sub>S</sub> , VCP                    | Supply voltage τ < 400 ms                | ,    | +35                 | V    |

| V3, VLOGIC                              |                                          |      | +3.6                | V    |

| CS, CLK, MOSI, MISO,<br>EN, CLKin, HETx |                                          | -0.3 | +3.6                | V    |

| OUT_EN                                  | Maximum voltage                          | -0.3 | +3.6                | V    |

| VRS_Meas                                |                                          | -0.3 | +3.6                | V    |

| OUTx, Dx                                |                                          | -0.3 | +35                 | V    |

| т                                       | Junction temperature                     | -40  | (1)                 | °C   |

| T <sub>j</sub>                          | Junction temperature (1h over life-time) |      | +190 <sup>(2)</sup> | °C   |

| T <sub>stg</sub>                        | Storage temperature                      | -65  | +150                | °C   |

<sup>1.</sup> Internally limited

Warning: The absolute maximum ratings are the values at which if exceeded the device may become damaged.

# 3.2 Thermal data

Table 4. Thermal data

| Symbol                  | Parameter                                             | Min. | Max. | Unit |

|-------------------------|-------------------------------------------------------|------|------|------|

| T <sub>j</sub>          | Junction temperature                                  | -40  | +150 | °C   |

| T <sub>amb</sub>        | Ambient temperature                                   | -40  | +105 | °C   |

| R <sub>th(j-amb)</sub>  | Thermal resistance junction to ambient <sup>(1)</sup> |      | 20   | °C/W |

| R <sub>th(j-case)</sub> | Thermal resistance junction to case                   |      | 2    | °C/W |

| E <sub>OUT(MAX)</sub>   | Maximum OUTx clamping energy, single pulse            |      | 50   | mJ   |

<sup>1.</sup> On a multilayer FR4 board with thermal vias and 2 Ounce copper covering >10mm<sup>2</sup>

577

<sup>2.</sup> Allowed only during switch-off

# 3.3 Electrical characteristics

(-40 °C <  $T_J$  < 150 °C, 7 V <  $V_S$  < 19 V unless otherwise specified.)

Table 5. V<sub>S</sub> supply voltage

| Symbol                  | Parameter                                       | Test condition                    | Min. | Тур. | Max. | Unit |

|-------------------------|-------------------------------------------------|-----------------------------------|------|------|------|------|

| $V_{SOPER}$             | Operating supply voltage                        | -                                 | 7.0  | -    | 19   | V    |

| I <sub>Q(Vs)</sub>      | Supply current on-state                         | $V_{S(LVI)} < V_{S} < V_{S(OVS)}$ | -    | -    | 5    | mA   |

| $V_{S(LVI)}$            | Supply voltage inhibit threshold <sup>(1)</sup> | Falling edge                      | 3.0  | 3.4  | 3.8  | ٧    |

| V <sub>S(LVI)</sub>     | Supply voltage inhibit threshold                | Rising edge                       | 6.6  | -    | 7.0  | ٧    |

| V <sub>S(LVI)HYST</sub> | Inhibit threshold hysteresis                    | -                                 | -    | 0.2  | -    | -    |

<sup>1.</sup> See the functional description for a detailed description of this function.

### Table 6. V3 3.3V supply

| Symbol               | Parameter                       | Test condition                                                       | Min. | Тур. | Max. | Unit |

|----------------------|---------------------------------|----------------------------------------------------------------------|------|------|------|------|

| V3 <sub>OPER</sub>   | Operating voltage               | -                                                                    | 3.0  | -    | 3.6  | V    |

| I <sub>Q(V3)</sub>   | Supply current in on-<br>state  | 3.0 V < V3 < 3.6 V                                                   | -    | -    | 40   | mA   |

| V3 <sub>LVI</sub>    | Supply low voltage inhibit      | L9390 enters RESET mode after t <sub>LVI(V3)</sub> , set 3V_Fail bit | 2.5  | 2.75 | 2.95 | ٧    |

| t <sub>LVI(V3)</sub> | Low voltage inhibit filter time | After delay device enters RESET mode, set V3_Fail bit                | 4    | -    | 20   | μS   |

### Table 7. VCP operating

| Symbol               | Parameter                      | Test condition                 | Min.              | Тур. | Max.              | Unit |

|----------------------|--------------------------------|--------------------------------|-------------------|------|-------------------|------|

| VCP <sub>OPER</sub>  | Operating voltage              | -                              | V <sub>S</sub> +6 | -    | 35                | V    |

| VCP <sub>CLAMP</sub> | Clamping voltage               | Built in zener protection      | 35                | -    | -                 | V    |

| I <sub>Q(VCP)</sub>  | Supply current in on-<br>state | V <sub>S</sub> +6 < VCP < 35 V | -                 | -    | 300               | μA   |

| VCP <sub>LVI</sub>   | Supply low voltage inhibit     | -                              | V <sub>S</sub> +3 | -    | V <sub>S</sub> +6 | V    |

### Table 8. Band gap

| Symbol                  | Parameter                   | Test Condition                                                                           | Min. | Тур. | Max. | Unit |

|-------------------------|-----------------------------|------------------------------------------------------------------------------------------|------|------|------|------|

| $\Delta V_{BG}$         | Band gap voltage<br>monitor | Voltage measured outside of this value will cause a RESET and setting of the V3_Fail bit | -7   | -    | +7   | %    |

| t <sub>VBG(error)</sub> | Band gap fault filter time  | After delay device enters RESET mode                                                     | 100  | -    | 200  | μs   |

Table 9. Output driver

| Symbol                       | Parameter                                           | Test condition                                                                 | Min. | Тур.  | Max.    | Unit |

|------------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------|------|-------|---------|------|

| R <sub>DS(on)OUT1-4</sub>    | Static drain to source on resistance outputs 1-4    | I <sub>OUT</sub> = 1 A<br>T <sub>J</sub> = 25 °C<br>T <sub>J</sub> = 175 °C    | -    | 0.076 | 0.2     | Ω    |

| R <sub>DS(on)OUT5-8</sub>    | Static drain to source on resistance outputs 5-8    | I <sub>OUT</sub> = 1 A<br>T <sub>J</sub> = 25 °C<br>T <sub>J</sub> = 175 °C    | -    | 0.12  | 0.32    | Ω    |

| R <sub>DS(on)OUT9-10</sub>   | Static drain to source on resistance, outputs 9-11  | I <sub>OUT</sub> = 1 A<br>T <sub>J</sub> = 25 °C<br>T <sub>J</sub> = 175 °C    | -    | 0.064 | 0.18    | Ω    |

| R <sub>DS(on)</sub> OUT11-12 | Static drain to source on resistance, outputs 11-12 | I <sub>OUT</sub> = 1 A<br>T <sub>J</sub> = 25 °C<br>T <sub>J</sub> = 175 °C    | -    | 0.12  | 0.32    | Ω    |

| Tj <sub>OTS</sub>            | Over temperature shutdown <sup>(1)</sup>            | OUTx disabled after tot                                                        | 190  | 205   | 220     | °C   |

| Tj <sub>OTSH</sub>           | Over temperature shutdown hysteresis                | - ,0                                                                           | -    | 20    | -       | °C   |

| V <sub>CLAMP</sub>           | Output clamping voltage                             | I <sub>OUT</sub> = 100 mA                                                      | 35   | -     | -       | V    |

| I <sub>OUT(PD)</sub>         | Output pull-down current                            | OUTx = off, EN_set = 1                                                         | 9    | 10    | 11      | μА   |

| I <sub>OUT(LEAK)</sub>       | Output leakage current                              | V <sub>OUT</sub> < 30 V, EN_set = 0<br>if T < 140 °C<br>if 140 °C < T < 175 °C | -    | -     | 4<br>19 | μΑ   |

| E <sub>CLAMP</sub>           | Output clamping energy                              |                                                                                | -    | -     | 30      | mJ   |

<sup>1.</sup> See the functional description for a detailed description of this function.

### Table 10. Active freewheeling diode

| Symbol                    | Parameter                                                             | Test condition                                                                                                                         | Min. | Тур.  | Max.  | Unit |

|---------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------|------|

| R <sub>DS(on)Diode1</sub> | Static drain to source on resistance diodes D5-D8, D11, D12           | T <sub>J</sub> = 25 °C                                                                                                                 | -    | 0.220 | 0.475 | Ω    |

| R <sub>DS(on)Diode2</sub> | Static drain to source on resistance diodes D9, D10                   | I <sub>OUT</sub> = 1.5 A, Vs = 13 V<br>T <sub>J</sub> = 25 °C<br>T <sub>J</sub> = 175 °C                                               | -    | 0.20  | 0.40  | Ω    |

| R <sub>SENSE</sub>        | Sense resistor for current regulated outputs(OUT5-OUT8, OUT11, OUT12) | Calculated:<br>(VD @ 1.5A - VD @ 0.25A) / 1.55A<br>VD = Voltage across Diode when<br>conducting (V <sub>OUTx</sub> - V <sub>Dx</sub> ) | -    | 0.25  | 0.40  | Ω    |

| t <sub>D(on)</sub>        | Additional on-time of freewheeling diode (transistor)                 | After deactivation of output                                                                                                           | -    | 20    | -     | ms   |

577

Table 10. Active freewheeling diode (continued)

| Symbol     | Parameter                                                  | Test condition                                                                        | Min. | Тур. | Max. | Unit |

|------------|------------------------------------------------------------|---------------------------------------------------------------------------------------|------|------|------|------|

| $V_{DON}$  | Freewheeling diode<br>(transistor) switch-on<br>threshold  | Above this voltage the transistor is turned on (V <sub>OUTx</sub> -V <sub>Dx</sub> )  | -150 | 0    | +150 | mV   |

| $V_{DOFF}$ | Freewheeling diode<br>(transistor) switch-off<br>threshold | Below this voltage the transistor is turned off (V <sub>OUTx</sub> -V <sub>Dx</sub> ) | -    | 0    | 1    | V    |

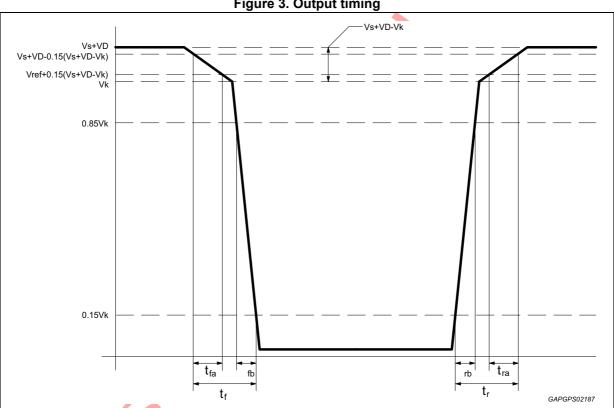

Figure 3. Output timing

Table 11. PWM output timing characteristics with edge shaping (SHAPE\_EN=1)

| Symbol          | Parameter                       | Test condition                                                   | Min.              | Тур. | Max.              | Unit |

|-----------------|---------------------------------|------------------------------------------------------------------|-------------------|------|-------------------|------|

| V <sub>K</sub>  | Slope a to slope b knee voltage | 0.5 A < I <sub>OUT</sub> < 0.5 A,<br>8 V < V <sub>S</sub> < 20 V | V <sub>S</sub> -2 |      | V <sub>S</sub> -1 | V    |

| t <sub>fa</sub> | Slope a falling slew rate       |                                                                  | 3.5               | 5    | 6.5               | V/μs |

| t <sub>fb</sub> | Slope b falling slew rate       |                                                                  | 14                | 20   | 26                | V/μs |

| t <sub>ra</sub> | Slope a rising slew rate        | 0.5 A < I <sub>OUT</sub> < 1.5 A                                 | 3.5               | 5    | 6.5               | V/μs |

| t <sub>rb</sub> | Slope b rising slew rate        | 10.5 A < 1 <sub>OUT</sub> < 1.5 A                                | 14                | 20   | 26                | V/μs |

| t <sub>f</sub>  | Fall time                       |                                                                  | 0.5               | 1.5  | 5                 | μS   |

| t <sub>r</sub>  | Rise time                       |                                                                  | 0.5               | 1.5  | 5                 | μS   |

Table 12. PWM output timing characteristics without edge shaping (SHAPE\_EN=0)

| Symbol         | Parameter        | Test condition                                                   | Min. | Тур. | Max. | Unit |

|----------------|------------------|------------------------------------------------------------------|------|------|------|------|

| t <sub>r</sub> | Output rise time | 0.5 A < I <sub>OUT</sub> < 1.5 A                                 | 7    | 10   | 13   | V/μs |

| t <sub>f</sub> | Output fall time | 0.5 A < I <sub>OUT</sub> < 1.5 A,<br>8 V < V <sub>S</sub> < 20 V | 7    | 10   | 13   | V/μs |

### Table 13. PWM output timing characteristics without edge shaping

| Symbol         | Parameter | Test condition                   | Min. | Тур. | Max. | Unit |

|----------------|-----------|----------------------------------|------|------|------|------|

| t <sub>f</sub> | Fall time | 050<1. <150                      | 0.5  | 1.5  | 5    | μS   |

| t <sub>r</sub> | Rise time | 0.5 A < I <sub>OUT</sub> < 1.5 A | 0.5  | 1.5  | 5    | μS   |

### Table 14. Input buffer parameters, CLK, CS, MOSI

| Symbol               | Parameter                       | Test condition                 | Min. | Тур. | Max.   | Unit |

|----------------------|---------------------------------|--------------------------------|------|------|--------|------|

| V <sub>IL</sub>      | Input low voltage               | -                              | -0.3 | -    | 1.0    | V    |

| V <sub>IH</sub>      | Input high voltage              | - , 0                          | 2.0  | -    | V3+0.3 | V    |

| V <sub>I(HYST)</sub> | Input threshold hysteresis      | -                              | 0.2  | 0.5  | 1.0    | ٧    |

| I <sub>P-U</sub>     | Internal pull-up current source | -0.3 <v<sub>IN&lt;2.0V</v<sub> | -35  | -    | -65    | μΑ   |

| f <sub>IN</sub>      | Input signal frequency range    |                                | DC   | -    | 11     | MHz  |

### Table 15. Input buffer parameters, MISO, EN

| Symbol                | Parameter                            | Test condition                              | Min.   | Тур. | Max. | Unit |

|-----------------------|--------------------------------------|---------------------------------------------|--------|------|------|------|

| V <sub>OL</sub>       | Output low voltage                   | 1 105 A OL 100 F                            | 0      | -    | 0.4  | V    |

| V <sub>OH</sub>       | Output high voltage                  | -I <sub>OUT</sub> < 25 μA, CL < 60pF        | V3-0.4 | -    | V3   | V    |

| R <sub>(ON)</sub>     | Pull-up/down switch resistance       | -25 μA < I <sub>OUT</sub> < 25 μA, CS = low | 20     | 50   | 100  | Ω    |

| R <sub>(OFF)</sub>    | Off-state switch resistance          | CS = high, outputs tri-stated               | 50     | 120  | 300  | kΩ   |

| I <sub>EN(P-U)</sub>  | Internal enable (EN) pull-up current | -0.3 V < V <sub>EN</sub> < 2.0 V            | -35    | -50  | -65  | μА   |

| f <sub>IN</sub>       | Signal frequency range               | I <sub>OUT</sub> <25μA, CL<60pF             | DC     | -    | 11   | MHz  |

| ΔV <sub>OUT</sub> /Δt | Output slew rate                     | CL<60pF                                     | -      | 150  | -    | V/μs |

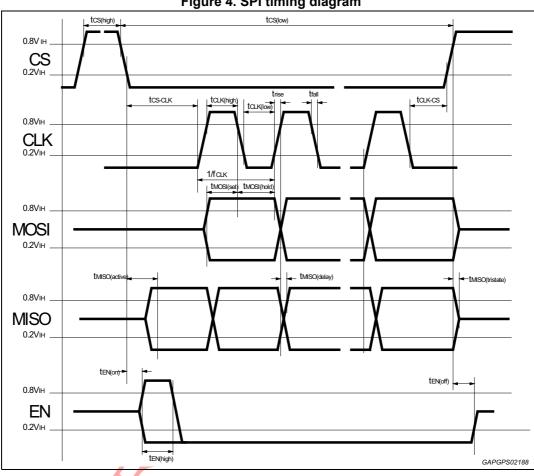

### Table 16. SPI timing parameters

| Symbol                 | Parameter       | Test condition           | Min. | Тур. | Max. | Unit |

|------------------------|-----------------|--------------------------|------|------|------|------|

| f <sub>CLK</sub>       | CLK frequency   | -                        | DC   | -    | 10   | MHz  |

| t <sub>CLK(high)</sub> | CLK high time   | -                        | 37   | -    | -    | ns   |

| t <sub>CLK(low)</sub>  | CLK low time    | -                        | 37   | -    | -    | ns   |

| t <sub>CS-CLK</sub>    | CS to CLK delay | 3*V <sub>CLK</sub> -13ns | 17   | -    | -    | ns   |

14/55 DocID024635 Rev 2

Table 16. SPI timing parameters (continued)

| Symbol                       | Parameter                 | Test condition                                                                                                    | Min. | Тур. | Max. | Unit |

|------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| t <sub>CLK-CS</sub>          | CLK to CS delay           | ~1/2CLK = 50 ns + VCLK - 13 ns                                                                                    | 45   | -    | -    | ns   |

| t <sub>MOSI(set)</sub>       | MOSI to CLK delay         | -                                                                                                                 | 27   | -    | -    | ns   |

| t <sub>MOSI(hold)</sub>      | CLK to MOSI delay         | -                                                                                                                 | 45   | -    | -    | ns   |

| t <sub>rise</sub>            | CLK, MOSI rise time       | C = 60 pF                                                                                                         | -    | -    | 13   | ns   |

| t <sub>fall</sub>            | CLK, MOSI fall time       | C <sub>LOAD</sub> = 60 pF                                                                                         | -    | -    | 13   | ns   |

| t <sub>MISO(delay)</sub>     | CLK to MISO delay         | $\sim$ t <sub>CLK(high)</sub> + t <sub>f</sub> -6ns, 9ns reserve t <sub>Fall</sub> , t <sub>Rise -</sub> symmetry | -    | -    | 35   | ns   |

| t <sub>MISO(active)</sub>    | CS to MISO active delay   |                                                                                                                   | -    | -    | 15   | ns   |

| t <sub>MISO(tri-state)</sub> | CS to MISO tristate delay | C <sub>LOAD</sub> = 60 pF                                                                                         | -    | -    | 15   | ns   |

| t <sub>MISO(rise)</sub>      | MISO rise time            |                                                                                                                   | -    | -    | 13   | ns   |

| t <sub>MISO(fall)</sub>      | MISO fall time            |                                                                                                                   | -    | -    | 13   | ns   |

| t <sub>CS(high)</sub>        | CS high time              | 3V <sub>CLK</sub> -∆tr, f, -6 ns                                                                                  | 20   | -    | -    | ns   |

| t <sub>CS(low)</sub>         | CS low time               | 34*t <sub>CLK</sub>                                                                                               | 3.4  | -    | -    | μs   |

| t <sub>EN(on)</sub>          | CS to EN delay            | Falling edge of CS, $C_{LOAD} = 60 \text{ pF}$<br>$C_{LOAD(MIN)} = 15 \text{ pF}$                                 | -    | -    | 100  | ns   |

| t <sub>EN(high)</sub>        | EN high time              | - 0                                                                                                               | -    | -    | 2    | μs   |

| $t_{EN(off)}$                | CS to EN delay            | Rising edge of CS,<br>3V <sub>CLK</sub> -Δt <sub>Rise/Fall</sub> , -6 ns                                          | -    | -    | 15   | ns   |

Figure 4. SPI timing diagram

Table 17. CLKin threshold parameters

|                          | 10010                            | 171 GETAIN ANGONOIG PARAMOTOR   |      |      |      |      |

|--------------------------|----------------------------------|---------------------------------|------|------|------|------|

| Symbol                   | Parameter                        | Test condition                  | Min. | Тур. | Max. | Unit |

| $V_{CLKin(low)}$         | Input low threshold              | -                               | 1.0  | -    | -    | V    |

| V <sub>CLKin(high)</sub> | Input high threshold             | -                               | -    | -    | 2.0  | V    |

| V <sub>CLKin(Hyst)</sub> | Input threshold hysteresis       | -                               | 0.2  | 0.5  | 1.0  | V    |

| I <sub>CLKin</sub>       | CLKin input current (pin to GND) | 0.5 V < V <sub>CLKin</sub> < V3 | 35   | 50   | 65   | μΑ   |

| f <sub>CLKin</sub>       | Input frequency range            | -                               | DC   | -    | 5    | MHz  |

Table 18. CLKin timing parameters

| Symbol               | Parameter                              | Test condition                                | Min. | Тур. | Max. | Unit |

|----------------------|----------------------------------------|-----------------------------------------------|------|------|------|------|

| $\Delta\% f_{CLKin}$ | Signal frequency accuracy requirements | Not including jitter, tested @ 4MHz           | -2   | -    | +2   | %    |

| %DC <sub>CLKin</sub> | Signal duty cycle                      | t <sub>High</sub> x f <sub>CLKin</sub> x 100% | 40   | 50   | 60   | %    |

| f <sub>Jitter</sub>  | CLKin jitter frequency                 | -                                             | 100  | 4    | -    | kHz  |

| $\Delta f_{Jitter}$  | CLKin jitter amplitude                 | -                                             | -    | 40   | -    | kHz  |

577

Table 18. CLKin timing parameters (continued)

| Symbol                   | Parameter                          | Test condition                                                                               | Min. | Тур. | Max. | Unit                 |

|--------------------------|------------------------------------|----------------------------------------------------------------------------------------------|------|------|------|----------------------|

| $\Delta f_{(low)}$       | Compares $f_{OSC}$ and $f_{CLKin}$ | Set CLKin_Fail = 1 if below this threshold                                                   | 0.1  | -    | 0.4  | x f <sub>CLKin</sub> |

| $\Delta f_{(high)}$      | Compares $f_{OSC}$ and $f_{CLKin}$ | Set CLKin_Fail = 1 if above this threshold                                                   | 2.5  | -    | 10   | x f <sub>CLKin</sub> |

| <sup>t</sup> CLKin(fail) | Failure detection filtering time   | Incorrect frequency must be detected for this length of time to post a failure on CLKin_Fail | 3    | 10   | 20   | μS                   |

# 4 Application information

The L9390 is a 12 channel open drain / low side valve driver for an ABS / Vehicle Stability system. All of the outputs can be PWMmed while some will require an external diode to do so. 6 of the outputs can drive a load using current regulation.

# 4.1 Supply monitoring

# 4.1.1 Low voltage inhibit (Vs(LVI))

The Vs supply has a low voltage warning function with hysteresis. When Vs drops below Vs(LVI) a bit is set in the SPI diagnostic register

# 4.2 General output functionality

Each of the 12 outputs are open drain configured. Each output has a built in 35V clamp and 8 of the 12 have integrated active freewheeling diodes for active rectification of the PWMmed loads. At loss of Dx, the output can be switched off and clamped regardless of the presence of a freewheeling diode.

The DMOS outputs have the option of having controlled switch on/off slopes to minimize EMC during actuation or PWM. This feature can be enabled or disabled via SPI.

All of the outputs can be asynchronously turned off either via the SPI "ALL\_OFF" command or via the "OUT\_EN" input pin. There are two (2) ALL\_OFF SPI register bits that must be specifically configured to disable the outputs.

Table 19. Outputs disable registry map

| BIT 0 | BIT 1 | ALL_OFF status                   |

|-------|-------|----------------------------------|

| 0     | 0     | Not allowed                      |

| 1     | 1     | Not allowed                      |

| 1     | 0     | All outputs disabled immediately |

| 0     | 1     | Normal Operation                 |

The outputs can be switched on directly using the SPI as well. When the OUT\_ON\_EN bit is set the OUT\_ONx bits are OR'ed with the appropriate HET input commands to drive the specified output (s) on.

Table 20. SPI outputs disable

| ALL_OFF | OUT_ONx | OUT_ON _EN | OUTx<br>Commanded<br>status1 | OUTx state      |

|---------|---------|------------|------------------------------|-----------------|

| 10      | Χ       | Х          | Х                            | All Outputs Off |

| 01      | 0       | Х          | Х                            | No Change       |

| 01      | Х       | 0          | Х                            | No Change       |

| 01      | 1       | 1          | Х                            | OUTx ON         |

Four possible states On / PWM / Current regulated / Off

Thermal protection is performed in on-state driver pairs. The pairs are set up to be configured with other driver types to minimize both drivers in the pair from being on at the same time. Refer to the over temperature detection portion in the Diagnostics section.

**Table 21. Diagnostic output**

| Outp | ut pairs |

|------|----------|

| 1    | 5        |

| 2    | 6        |

| 3    | 7        |

| 4    | 8        |

| 9    | 11       |

| 10   | 12       |

The power grounds are also paired in like manner to optimize the current flow through the ground leads and reduce ground offset.

## 4.2.1 Edge shaping

When the SHAPE\_En bit is set the output rising and falling edges are controlled in a manner to minimize the EMI that can be generated by continuous PWMming of a load. The edges have a dual slope to both minimize the EMI as well as minimize the power dissipated during switching. Refer to *Figure 3* for a graphic of the edge shaping.

When the SHAPE\_EN bit is not set the slope is fixed to 20 V/s.

### 4.2.2 Out1-out4

These outputs are configured as switching drivers. There is not internal active diode for PWMming. However these outputs can be PWMmed if an external diode is present. The PWM duty cycle and frequency is accomplished through the serial HET input commands.

Figure 5. Out1-4 block diagram

These outputs have over current protection, under current detection, open load (off state), voltage clamp, loss of ground detection, loss of freewheeling diode (when one is used in the circuit), and shared thermal shutdown.

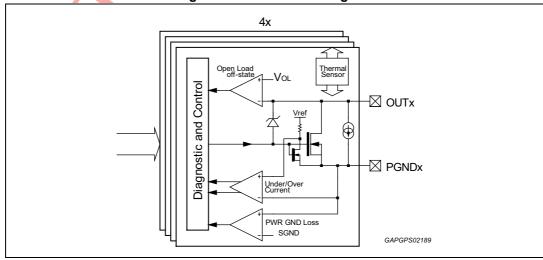

### 4.2.3 Out5-out8

Outputs 5 through 8 are Current Controlled outputs. They include a freewheeling MOSFET for synchronous rectification. These outputs will regulate to a commanded current within  $I_{OUT(tol)}$ %. The frequency and current levels are commanded via the serial HET interface. They can be selected as current controlled outputs, PWMmed outputs, or switched outputs via the SPI.

Figure 6. Out5-8 block diagram

4x

Thermal Sensor

Open Load Off-state

Open Load Off-state

Open Load

Open

These outputs have over current protection, under current detection, current not achieved detection, open load (off state), voltage clamp, loss of ground protection, loss of freewheeling diode and shared thermal shutdown.

# 4.2.4 Out9-out10

Outputs 9 and 10 are PWM controlled outputs. They include a freewheeling MOSFET for synchronous rectification. The PWM frequency and duty cycle is commanded through the serial HET interface. They can be selected as PWMmed outputs, or switched outputs via the SPI.

2x

Thermal Sensor

Open Load off-state

Outro

Vref

Open Load off-state

PWR GND Loss

SGND

SGND

GAPGPS02191

Figure 7. Outputs 9 and 10 block diagram

These outputs have over current protection, under current detection, open load (off state), voltage clamp, loss of ground protection, loss of freewheeling diode, and shared thermal shutdown.

### 4.2.5 Out11-out12

Outputs 11 through 12 are current controlled outputs. They include a freewheeling MOSFET for synchronous rectification. These outputs will regulate to a commanded current within IOUT(tol) %. The current level is commanded via the serial HET interface. They can be used as current controlled outputs, PWMmed outputs, or switched outputs.

2x

Thermal Serior

Resense

Outro

Verf

Open Load off-state

Verf

Open Load

Off-state

Verf

Open Load

Off-state

PWR GND Loss

SGND

GAPGP 502192

Figure 8. Outputs 11 and 12 block diagram

These outputs have over current protection, under current detection, current not achieved detection, open load (off state), voltage clamp, loss of ground protection, loss of freewheeling diode and shared thermal shutdown.

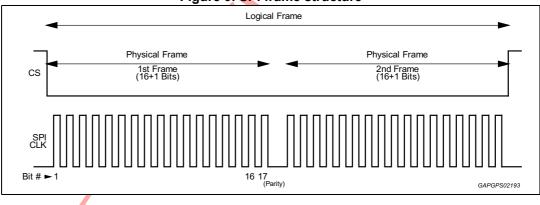

# 5 Serial communications

There are two separate conduits of communication into and out of the L9390. These are the 5 pin SPI port and the 6 serial HET inputs. The SPI port is primarily designated to provide diagnostics and secondary control. The serial HET inputs provide the primary output control functions from on/off switching to current level control commands.

### 5.1 SPI data bus

The SPI bus addresses several registers within the L9390. Each of the registers are 24 bits wide. The address, data and parity bits add up to a total of 31 for the SPI transmission.

# 5.2 SPI safety features

### **Parity**

To ensure proper communication every SPI frame has a parity bit (odd). If a parity error is detected then the data is discarded and the PAR\_Fail Bit is set.

### **Clock monitor**

The number of clock pulses for each frame is counted. If this number is incorrect then the data is discarded and the PAR Fail bit is set.

### Master to Slave address correlation

To verify a proper transmission a subsequent Slave frame contains the same address information as the initial Master frame.

### Unused addresses

The SPI addresses 00H and FFH are not used.

### SPI read error

Reading a non-existing address will cause a SPI read failure and set the RAd\_Fail bit.

### **SPI** write error

Writing to a non-existent or non-writable address will cause a SPI write error and will set the WAd\_Fail bit. Writing to an address that has both writable and only readable bit will not cause a failure. This also applies to addresses that have both writable and un-used bits.

Writing a bit combination that is not allowed will also cause a WAd\_Fail bit to be set. If this is attempted the bit values will not be changed.

Serial communications L9390

# 5.3 SPI commands / registers

### Acknowledgement / wake-up

The initial SPI Slave-to-Master transmission after a RESET contains all 1's except for bit 31. If a Master-to-Salve transmission contains an error (incorrect parity, etc) all 31 bits in the subsequent Slave-to-Master transmission will be all 1's.

Table 22. Acknowledgement / wake-up

| Bit                                    | 31 | 30-24 | 23-0 |

|----------------------------------------|----|-------|------|

| Initial Slave-to-Master Tx after RESET | 0  | 1     | 1    |

| Master-to-Slave Rx Error detected      | 1  | 1     | 1    |

### SPI command / register description

The SPI command word consists of parity (1 bit), address (7 bits), and Command/Data (24 bits) sections. The following descriptions are done by SPI address. The SPI addresses used are 20H through 35H.

Figure 9. SPI frame structure

# 5.3.1 Revision ID, Device ID, SPI status

| Address        | R,<br>R/W,<br>W | D23 | D22 | D21   | D20   | D19   | D18    | D17 | D16 | D15 | D14 | D13   | D12    | D11     | D10   | D9 | D8 | D7     | D6      | D5     | D4        | D3       | D2       | D1       | D0        |

|----------------|-----------------|-----|-----|-------|-------|-------|--------|-----|-----|-----|-----|-------|--------|---------|-------|----|----|--------|---------|--------|-----------|----------|----------|----------|-----------|

| 20H            | R               |     | Re  | evisi | on id | entif | icatio | on  |     |     | De  | evice | e ider | ntifica | ation | 1  |    | EN_Set | TEST_En | J_GN5S | AV_Config | Par_Fail | WAd_Fail | RAd_Fail | Takt_Fail |

| Norm<br>operat |                 | 0   | 0   | 0     | 1     | 0     | 0      | 0   | 1   | 0   | 1   | 1     | 0      | 1       | 0     | 0  | 0  | Х      | 0       | 0      | Х         | 0        | 0        | 0        | 0         |

Table 23. Revision ID, Device ID, SPI status characteristics

| Bit #    | Function    | Level                                                         | R<br>R/W<br>W | Status at SPI polling                                                            | Function<br>after SPI<br>polling   | After<br>POR | After<br>RESET<br>address |

|----------|-------------|---------------------------------------------------------------|---------------|----------------------------------------------------------------------------------|------------------------------------|--------------|---------------------------|

| 23 -16   | Revision ID | "11HEX"                                                       | Read          | "11HEX"                                                                          | no                                 | "11HEX"      | "11HEX"                   |

| 15 -8    | Device ID   | "60HEX"                                                       | Read          | "60HEX"                                                                          | no                                 | "60HEX"      | "60HEX"                   |

| 7        | EN_set      | "0" = OUT_EN < V <sub>IL</sub> "1" = OUT_EN > V <sub>IH</sub> | Read          | One or more low signal detected since last SPI polling                           | Set to "1" if<br>input =<br>"high" | X            | х                         |

| 6        | Test_eN     | "1" = ASIC testmode active                                    | Read          | "1" if ASIC testmode<br>activated one or more<br>times since last SPI<br>polling | Reset bit                          | 0            | 0                         |

| 5        | SGND_L      | "1" = SGND_L is lost "0" = normal operation                   | Read          | One or more failures<br>detected since last SPI<br>polling                       | set to "0"                         | 0            | 0                         |

| 4        | AV_config   | "0" = configuration 1 "1" = configuration 2                   | Read          | current                                                                          | no                                 | x            | х                         |

| 3        | Par_Fail    | "1" = SPI / parity failure detected                           | Read          | One or more SPI<br>messages failed since<br>last SPI polling                     | Reset bit                          | 0            | 0                         |

| 2        | WAd_Fail    | "1" = Write address<br>failure detected                       | Read          | One or more SPI<br>messages failed since<br>last SPI polling                     | Reset bit                          | 0            | 0                         |

| 1        | RAd_Fail    | "1" = Read address<br>failure detected                        | Read          | One or more SPI<br>messages failed since<br>last SPI polling                     | Reset bit                          | 0            | 0                         |

| 0<br>LSB | CLK_Fail    | "1" = CLK failure<br>detected                                 | Read          | One or more SPI<br>messages failed since<br>last SPI polling                     | Reset bit                          | 0            | 0                         |

# 5.3.2 Direct driving of outputs, edge shaping, feedback configuration

| Address          | R,<br>R/W,<br>W | D23      | D22      | D21      | D20     | D19     | D18     | D17     | D16     | D15     | D14     | D13     | D12     | D11      | D10 | D9       | D8 | D7     | D6       | D5 | D4 | D3       | D2        | D1 | D0 |

|------------------|-----------------|----------|----------|----------|---------|---------|---------|---------|---------|---------|---------|---------|---------|----------|-----|----------|----|--------|----------|----|----|----------|-----------|----|----|

| 21H              | R/W             | OUT_ON12 | OUT_ON11 | OLNO_TUO | 6NO_TUO | 8NO_TUO | 2NO_TUO | 9NO_TUO | SNO_TUO | OUT_ON4 | ENO_TUO | OUT_ON2 | 1NO_TUO | MWG GIIJ |     | SCOM SOM |    | LDT_En | SHAPE_En |    | ,l | Not Used | OUT_ON_EN | sv | DT |

| Norma<br>operati |                 | X        | Х        | X        | Х       | X       | X       | X       | X       | Х       | X       | X       | X       | 0        | 1   | X        | X  | 1      | 1        | 0  | 1  | X        | X         | X  | Х  |

Table 24. Direct driving of outputs, edge shaping, feedback configuration characteristics

| Bit#       | Function                                    | Level                                                                                                                | R<br>R/W<br>W  | Status at SPI polling | Function<br>after SPI<br>polling | Default<br>(After<br>POR) | After<br>RESET<br>address |

|------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------|-----------------------|----------------------------------|---------------------------|---------------------------|

| 23-12      | OUT_ONx                                     | Output enable OUT1OUT12                                                                                              | Read/<br>write | Present value         | Set to new value                 | 0                         | 0                         |

| 11-<br>10  | CUR_PWM<br>(For OUT5-OUT8,<br>OUT11, OUT12) | Current regulation or PWM control Switch:  "01" = Current regulation (default)  "10" = PWM actuated valve driver     | Read/<br>write | Present value         | Set to new value                 | 01                        | 01                        |

| 9-8        | VRS_Meas                                    | V <sub>RSsense</sub> switch:<br>"x1" = on<br>"x0" = off                                                              | Read/<br>write | Present value         | Set to new value                 | 00                        | 00                        |

| 7          | LDT_en                                      | Leakage detection test switch "1"= off (normal operation), "0"= on (Leakage test)                                    | Read/<br>write | Present value         | Set to new value                 | 1                         | 1                         |

| 6          | SHAPE_En                                    | Edge Shaping Switch  "1"= On (normal operation)  "x0" = off (no edge shaping)                                        | Read/<br>write | Present value         | Set to new value                 | 1                         | 1                         |

| 5-4        | ALL_OFF                                     | Output Disable Switch "01" = normal operation "10" = All outputs switched off                                        | Read/<br>write | Present value         | Set to new value                 | 01                        | 01                        |

| 3          |                                             | Not used                                                                                                             |                |                       |                                  | 0                         | 0                         |

| 2          | OUT_ON_EN                                   | SPI Driven outputs enable<br>switch<br>"1" = OUT_ONx commands<br>enabled<br>"0" = Disables SPI driving<br>capability | Read/<br>write | Present value         | Set to new value                 | 0                         | 0                         |

| 1-0<br>LSB | SVDT                                        | Enables Silent Valve Driver<br>Test:<br>"10" = Enabled<br>"01" = Disabled                                            | Read/<br>write | Present value         | Set to new value                 | 01                        | 01                        |

# 5.3.3 Input diagnostic feedback

| Address        | R,<br>R/W,<br>W | D23       | D22       | D21       | D20       | D19       | D18       | D17      | D16      | D15      | D14        | D13     | D12     | D11       | D10       | D9        | D8       | D7       | D6       | D5       | D4       | D3       | D2       | D1       | D0       |

|----------------|-----------------|-----------|-----------|-----------|-----------|-----------|-----------|----------|----------|----------|------------|---------|---------|-----------|-----------|-----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| 22H            | R               | HET_Fail6 | HET_Fail5 | HET_Fail4 | HET_Fail3 | HET_Fail2 | HET_Fail1 | Not Used | Osc_Fail | VCP_Fail | CLKin_Fail | Vs_Fail | V3_Fail | LD_Fail12 | LD_Fail11 | LD_Fail10 | LD_Fail9 | LD_Fail8 | LD_Fail7 | LD_Fail6 | LD_Fail5 | LD_Fail4 | LD_Fail3 | LD_Fail2 | LD_Fail1 |

| Norm<br>Operat |                 | 0         | 0         | 0         | 0         | 0         | 0         | 0        | 0        | 0        | 0          | 0       | 0       | 0         | 0         | 0         | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        |

Table 25. Input diagnostic feedback characteristics

| Bit#        | Function                     | Level                                                                                | R<br>R/W<br>W | Status at SPI polling                                      | Function<br>after SPI<br>polling | Default<br>(After<br>POR) | After<br>RESET<br>address |

|-------------|------------------------------|--------------------------------------------------------------------------------------|---------------|------------------------------------------------------------|----------------------------------|---------------------------|---------------------------|

| 23 -<br>18  | HET_Fail(x)<br>(HET6 – HET1) | "1" = Inx Tx failure "0" = normal operation                                          | Read          | One or more failures<br>detected since last SPI<br>polling | set to "0"                       | 0                         | 0                         |

| 17          |                              | No                                                                                   | t used        |                                                            |                                  | 0                         | 0                         |

| 16          | Osc_Fail                     | "1" = Oscillator failure detected                                                    | Read          | One or more failures<br>detected since last SPI<br>polling | set to "0"                       | 0                         | 0                         |

| 15          | VCP_Fail                     | "1" =VCP <vcp<sub>LVI</vcp<sub>                                                      | Read          | Present                                                    | no                               | 0                         | 0                         |

| 14          | CLKin_Fail                   | "1" = CLKIn failure detected                                                         | Read          | One or more failures detected since last SPI polling       | set to "0"                       | 0                         | 0                         |

| 13          | Vs_Fail                      | "1" = Vs < Vs <sub>(LVI)</sub> "0" = normal operation                                | Read          | One or more failures<br>detected since last SPI<br>polling | set to "0"                       | 0                         | 0                         |

| 12          | V3_Fail                      | "1" = V3 < V3 <sub>(LVI)</sub>                                                       | Read          | One or more failures<br>detected since last SPI<br>polling | set to "0"                       | 1                         | 0                         |

| 11-0<br>LSB | LD_Fail(x)                   | "1" = I <sub>OUTx</sub> >I <sub>DET</sub> "0" = I <sub>OUTx</sub> <i<sub>DET</i<sub> | Read          | One or more failures<br>detected since last SPI<br>polling | set to "0"                       | 0                         | 0                         |

Serial communications L9390

### 5.3.4 Output feedback, one address per output

| Address            | R,<br>R/W,<br>W | D23       | D22      | D21 | D20 | D19  | D18              | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10  | D9       | D8 | D7 | D6 | D5       | D4 | D3       | D2      | D1      | D0      |

|--------------------|-----------------|-----------|----------|-----|-----|------|------------------|-----|-----|-----|-----|-----|-----|-----|------|----------|----|----|----|----------|----|----------|---------|---------|---------|

| 23H-2EH            | R               | SVDT_OUTx | PWM_MUXx |     | E   | dge_ | _OU <sup>-</sup> | Тх  |     |     |     |     | LO  | W_C | )UT> | <b>(</b> |    |    |    | AND MIMA | 1  | Not Used | oc_outx | xTUO_OU | OL_OUTx |

| Norma<br>operation |                 | 0         | 0        | 0   | 0   | 0    | 0                | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0    | 0        | 0  | 0  | 0  | 0        | 0  | 0        | 0       | 0       | 0       |

There are 12 registers represented, from 23H to 2EH.

There is one register for each output.

OUT1 is referenced to 23H... OUT12 is referenced to 2EH

Table 26. Output feedback, one address per output characteristics

| Bit<br>#  | Function                                                          | Level                                                                       | R<br>R/W<br>W | Status at SPI<br>Polling                                   | Function<br>after SPI<br>polling | Default<br>(After<br>POR) | After<br>RESET<br>address |

|-----------|-------------------------------------------------------------------|-----------------------------------------------------------------------------|---------------|------------------------------------------------------------|----------------------------------|---------------------------|---------------------------|

| 23        | SVDT_OUTx 1-12<br>1 referenced to 23H<br><br>12 referenced to 2EH | "1" = SVDT failure detected                                                 | Read          | One or more failures<br>detected since last<br>SPI polling | set to "0"                       | 0                         | 0                         |

| 22        | PWM_MUXx                                                          | "0" = PWM-Check at OUTx "1" = PWM-Check performed at GATEx                  | Read          | Present                                                    | No                               | 0                         | 0                         |

| 21-<br>16 | Edge_OUTx                                                         | Number of positive edges in one HET sequence (6 bits)                       | Read          | Present                                                    | set to "0"                       | 0                         | 0                         |

| 15-6      | LOW_OUTx                                                          | Number of low time counts in one HET sequence                               | Read          | Present                                                    | set to "0"                       | 0                         | 0                         |

| 5-4       | PWM_CKx                                                           | "00" = Busy/Inactive: "01" = Sequence 1 "10" = Sequence 2 "11" = Sequence 3 | Read          | Present                                                    | no                               | 0                         | 0                         |

| 3         |                                                                   | Not used                                                                    |               |                                                            | 0                                | 0                         | 0                         |

| 2         | OC_OUTx                                                           | "1" = I <sub>OUTx</sub> > I <sub>OCx</sub><br>Over current detection        | Read          | One or more failures<br>detected since last<br>SPI polling | set to "0"                       | 0                         | 0                         |

| 1         | UC_OUTx                                                           | "1" = I <sub>OUTx</sub> < I <sub>UC</sub><br>Under current detection        | Read          | One or more failures<br>detected since last<br>SPI polling | set to "0"                       | 0                         | 0                         |

| 0<br>LSB  | OL_OUTx                                                           | "1" = V <sub>OUTx</sub> < V <sub>OL</sub> Off state open load detection     | Read          | One or more failures<br>detected since last<br>SPI polling | set to "0"                       | 0                         | 0                         |

577

# 5.3.5 Current regulation commands, two outputs per address

| Address        | R,<br>R/W,<br>W | D23      | D22      |            | D20 | D19 | D18 | D17 | D16              | D15        | D14 | D13       | D12 | D11 | D10 | D9  | D8  | D7  | D6  | D5 | D4 | D3 | D2 | D1 | D0 |

|----------------|-----------------|----------|----------|------------|-----|-----|-----|-----|------------------|------------|-----|-----------|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|

| 2FH            | R               | Not Used | Not Used | CNA_Fail6  |     |     |     | CF  | REG <sub>.</sub> | OU         |     | CNA_Fail5 |     |     |     | CR  | EG_ | OU  | IT5 |    |    |    |    |    |    |

| 30H            | R               | Not Used | Not Used | CNA_Fail8  |     |     |     | CF  | REG <sub>.</sub> | _OU        |     | CNA_Fail7 |     |     |     | CR  | EG_ | _OU | IT7 |    |    |    |    |    |    |

| 31H            | R               | Not Used | Not Used | CNA_Fail12 |     |     |     | CR  |                  | CNA_Fail11 |     |           |     | CRI | EG_ | OU. | T11 |     |     |    |    |    |    |    |    |

| Norm<br>Operat | -               | 0        | 0        | 0          | Х   | Х   | Х   | Х   | Х                | Х          | X   | X         | X   | Х   | 0   | Х   | Х   | Х   | Х   | Х  | Х  | X  | Х  | Х  | Х  |

Table 27. Current regulation commands, two outputs per address characteristics

| Bit #   | Function                      | Level                                         | R<br>R/W<br>W | Status at SPI<br>Polling | Function<br>after SPI<br>polling | Default(<br>After<br>POR) | After<br>RESET<br>address |

|---------|-------------------------------|-----------------------------------------------|---------------|--------------------------|----------------------------------|---------------------------|---------------------------|

| 23-22   |                               | Not Used                                      |               |                          | 0                                | 0                         | 0                         |

| 21      | CNA_Fail(x) OUT6, OUT8, OUT12 | Current for Out6, 8,<br>&12 is not achievable | Read          | Present                  | no                               | 0                         | 0                         |

| 20-11   | CREG_OUT(x) OUT6, OUT8, OUT12 | Current PWM values for Out6,8,&12             | Read          | Present                  | no                               | 0                         | 0                         |

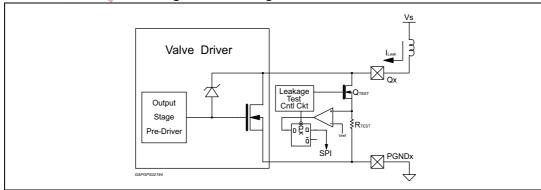

| 10      | CNA_Fail(x) OUT5, OUT7, OUT11 | Current for Out5, 7, &11 is not achievable    | Read          | Present                  | no                               | 0                         | 0                         |