## 16-BIT MCU WITH MAC UNIT, 256K BYTE FLASH MEMORY AND 12K BYTE RAM

#### PRELIMINARY DATA

- HIGH PERFORMANCE 40MHz CPU WITH DSP FUNCTION

- 16-BIT CPU WITH 4-STAGE PIPELINE

- 50ns INSTRUCTION CYCLE TIME AT 40MHz MAX CPU CLOCK

- MULTIPLY/ACCUMULATE UNIT (MAC) 16 x 16-BIT MULTIPLICATION, 40-BIT ACCUMULATOR

- REPEAT UNIT

- ENHANCED BOOLEAN BIT MANIPULATION FA-CILITIES

- ADDITIONAL INSTRUCTIONS TO SUPPORT HLL AND OPERATING SYSTEMS

- SINGLE-CYCLE CONTEXT SWITCHING SUP-PORT

- MEMORY ORGANIZATION

- 256K BYTE ON-CHIP FLASH MEMORY SINGLE VOLTAGE WITH ERASE/PROGRAM CONTROLLER.

- 100K FRASING/PROGRAMMING CYCLES.

- UP TO 16M BYTE LINEAR ADDRESS SPACE FOR CODE AND DATA (5M BYTES WITH CAN)

- 2K BYTE ON-CHIP INTERNAL RAM (IRAM)

- 10K BYTE ON-CHIP EXTENSION RAM (XRAM)

- FAST AND FLEXIBLE BUS

- PROGRAMMABLE EXTERNAL BUS CHARACTE-RISTICS FOR DIFFERENT ADDRESS RANGES

- 8-BIT OR 16-BIT EXTERNAL DATA BUS

- MULTIPLEXED OR DEMULTIPLEXED EXTERNAL ADDRESS/DATA BUSES

- FIVE PROGRAMMABLE CHIP-SELECT SIGNALS

- HOLD-ACKNOWLEDGE BUS ARBITRATION SUP-PORT

- INTERRUPT

- 8-CHANNEL PERIPHERAL EVENT CONTROLLER FOR SINGLE CYCLE INTERRUPT DRIVEN DATA TRANSFER

- 16-PRIORITY-LEVEL INTERRUPT SYSTEM WITH 56 SOURCES, SAMPLING RATE DOWN TO 25ns

- TIMERS

- TWO MULTI-FUNCTIONAL GENERAL PURPOSE TIMER UNITS WITH 5 TIMERS

- TWO 16-CHANNEL CAPTURE / COMPARE UNITS

- A/D CONVERTER

- 16-CHANNEL 10-BIT

- 4.85μs CONVERSION TIME AT 40MHz CPU CLOCK

- 4-CHANNEL PWM UNIT

- SERIAL CHANNELS

- SYNCHRONOUS / ASYNCHRONOUS SERIAL CHANNEL

- HIGH-SPEED SYNCHRONOUS CHANNEL

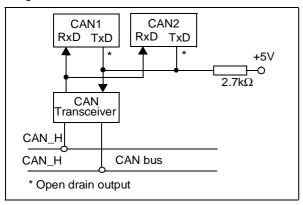

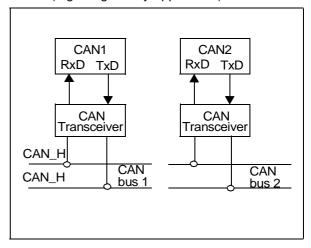

- TWO CAN 2.0B INTERFACES OPERATING ON ONE OR TWO CAN BUSSES (30 OR 2x15 MESSAGE OBJECTS)

- FAIL-SAFE PROTECTION

- PROGRAMMABLE WATCHDOG TIMER

- OSCILLATOR WATCHDOG

- ON-CHIP BOOTSTRAP LOADER

- CLOCK GENERATION

- ON-CHIP PLL

- DIRECT OR PRESCALED CLOCK INPUT

- REAL TIME CLOCK

- UP TO 111 GENERAL PURPOSE I/O LINES

- INDIVIDUALLY PROGRAMMABLE AS INPUT, OUTPUT OR SPECIAL FUNCTION

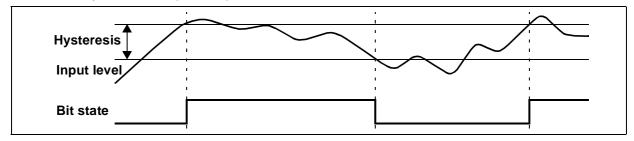

- PROGRAMMABLE THRESHOLD (HYSTERESIS)

- IDLE AND POWER DOWN MODES

- SINGLE VOLTAGE SUPPLY: 5V ±10% (EMBEDDED REGULATOR FOR 3.3 V CORE SUPPLY).

- TEMPERATURE RANGE: -40 +125°C

- 144-PIN PQFP PACKAGE

September 2013 DocID7588 Rev 3Á 1/160

| TABLE OF           | CONTENTS                                | PAGE     |

|--------------------|-----------------------------------------|----------|

| 1 -                | INTRODUCTION                            | 6        |

| 2 -                | PIN DATA                                | 7        |

| 3 -                | FUNCTIONAL DESCRIPTION                  | 13       |

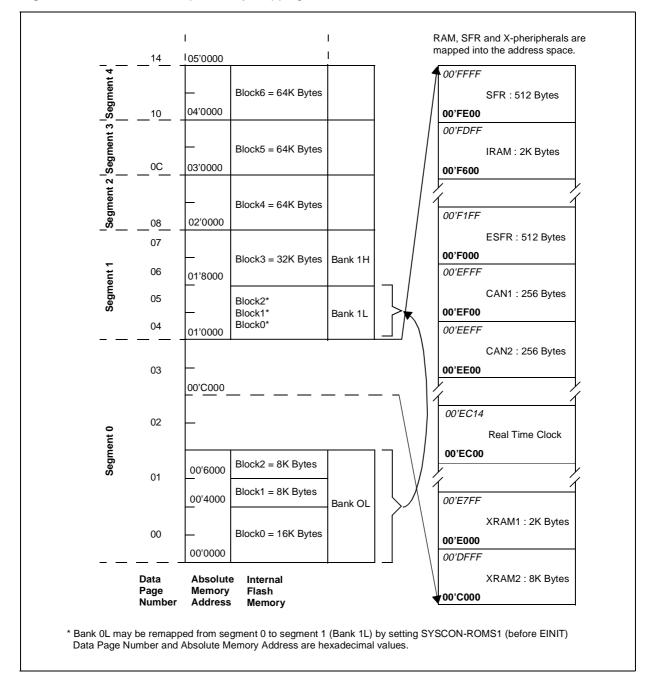

| 4 -                | MEMORY ORGANIZATION                     | 14       |

| 5 -                | INTERNAL FLASH MEMORY                   | 17       |

| 5.1 -              | OVERVIEW                                | 17       |

| 5.2 -              | OPERATIONAL OVERVIEW                    | 17       |

| 5.3 -              | ARCHITECTURAL DESCRIPTION               | 19       |

| 5.3.1 -            | Read Mode                               | 19       |

| 5.3.2 -            | Command Mode                            | 19       |

| 5.3.3 -            | Ready/Busy Signal                       | 19       |

| 5.3.4 -<br>5.3.5 - | Flash Status Register                   | 19<br>21 |

| 5.3.6 -            | Flash Protection Register               | 21       |

| 5.3.7 -            | Reset Processing and Initial State      | 25       |

| 5.4 -              | FLASH MEMORY CONFIGURATION              | 25       |

| 5.5 -              | APPLICATION EXAMPLES                    | 25       |

| 5.5.1 -            | Handling of Flash Addresses             | 25       |

| 5.5.2 -            | Basic Flash Access Control              | 26       |

| 5.5.3 -            | Programming Examples                    | 27       |

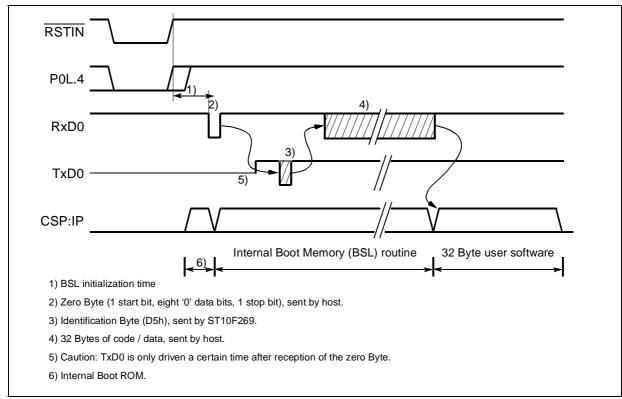

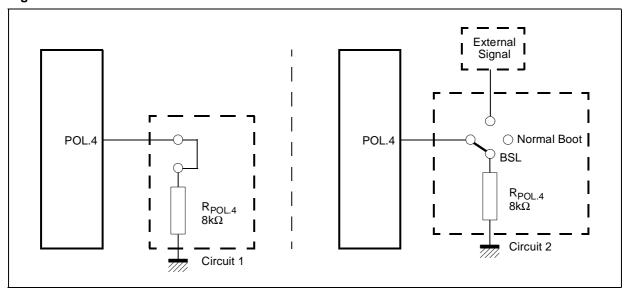

| 5.6 -              | BOOTSTRAP LOADER                        | 30       |

| 5.6.1 -            | Entering the Bootstrap Loader           | 30       |

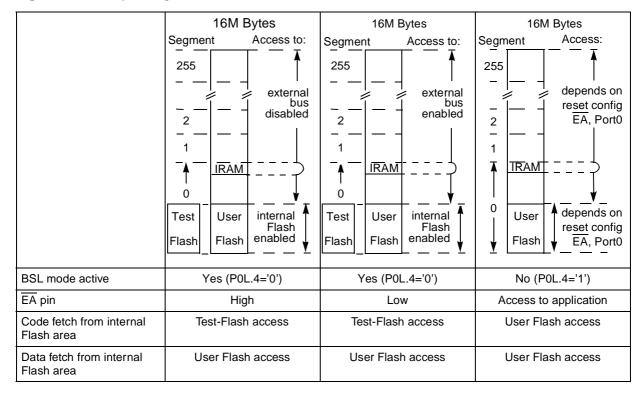

| 5.6.2 -            | Memory Configuration After Reset        | 31       |

| 5.6.3 -            | Loading the Startup Code                | 32       |

| 5.6.4 -<br>5.6.5 - | Exiting Bootstrap Loader Mode           | 32<br>33 |

| 3.0.3 -            | Choosing the Badd Nate for the BSL      | 33       |

| 6 -                | CENTRAL PROCESSING UNIT (CPU)           | 34       |

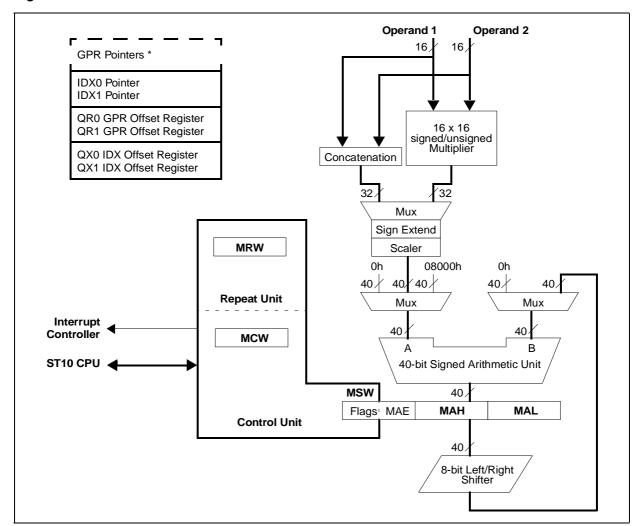

| 6.1 -              | MULTIPLIER-ACCUMULATOR UNIT (MAC)       | 35       |

| 6.1.1 -            | Features                                | 36       |

| 6.1.1.1 -          | Enhanced Addressing Capabilities        | 36       |

| 6.1.1.2 -          | Multiply-Accumulate Unit                | 36       |

| 6.1.1.3 -          | Program Control                         | 36       |

| 6.2 -              | INSTRUCTION SET SUMMARY                 | 37       |

| 6.3 -              | MAC COPROCESSOR SPECIFIC INSTRUCTIONS   | 38       |

| 7 -                | EXTERNAL BUS CONTROLLER                 | 42       |

| 7.1 -              | PROGRAMMABLE CHIP SELECT TIMING CONTROL | 42       |

| 72-                | READY PROGRAMMARI E POLARITY            | 42       |

| TABLE OF             | CONTENTS                                        | PAGE     |

|----------------------|-------------------------------------------------|----------|

| 8 -                  | INTERRUPT SYSTEM                                | 44       |

| 8.1 -                | EXTERNAL INTERRUPTS                             | 44       |

| 8.2 -                | INTERRUPT REGISTERS AND VECTORS LOCATION LIST   | 45       |

| 8.3 -                | INTERRUPT CONTROL REGISTERS                     | 46       |

| 8.4 -                | EXCEPTION AND ERROR TRAPS LIST                  | 47       |

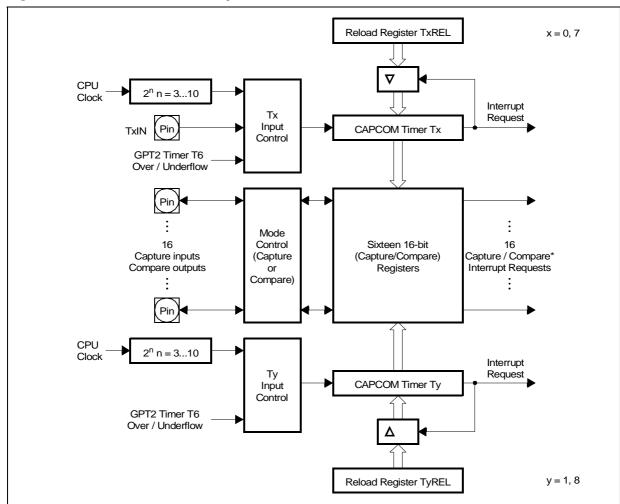

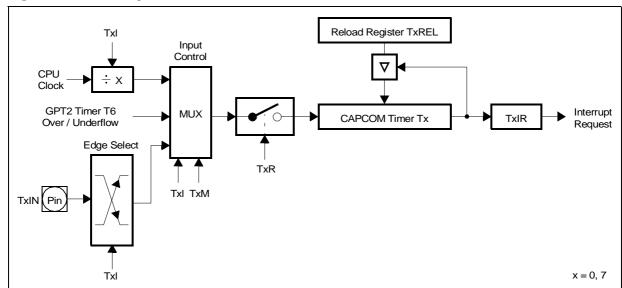

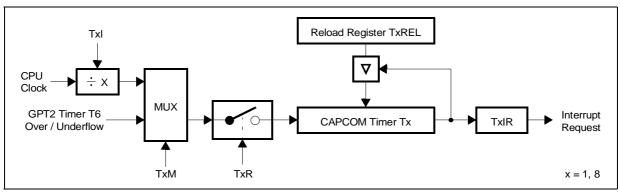

| 9 -                  | CAPTURE/COMPARE (CAPCOM) UNITS                  | 48       |

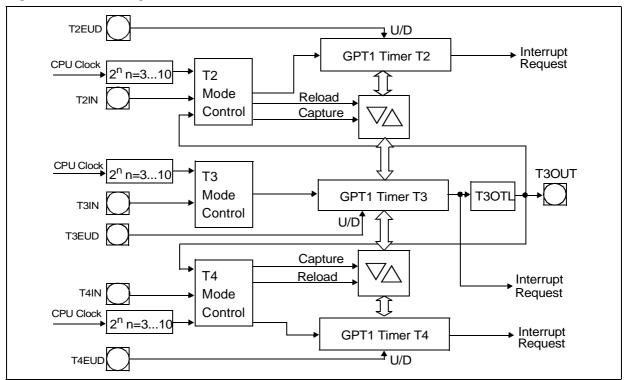

| 10 -                 | GENERAL PURPOSE TIMER UNIT                      | 51       |

| 10.1 -               | GPT1                                            | 51       |

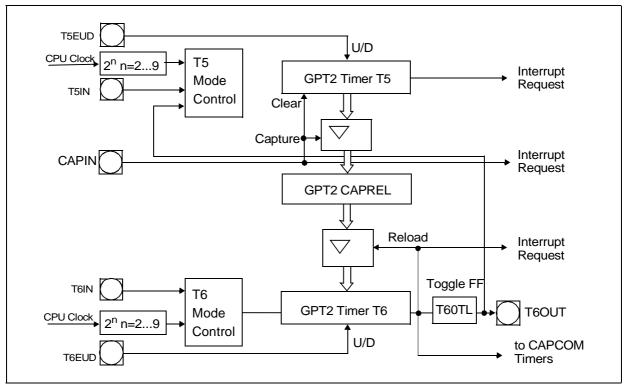

| 10.2 -               | GPT2                                            | 52       |

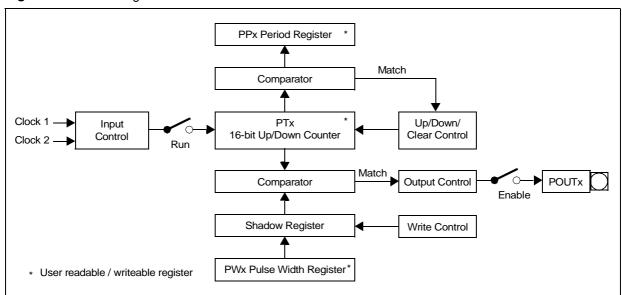

| 11 -                 | PWM MODULE                                      | 54       |

| 12 -                 | PARALLEL PORTS                                  | 55       |

| 12.1 -               | INTRODUCTION                                    | 55       |

| 12.2 -               | I/O'S SPECIAL FEATURES                          | 57       |

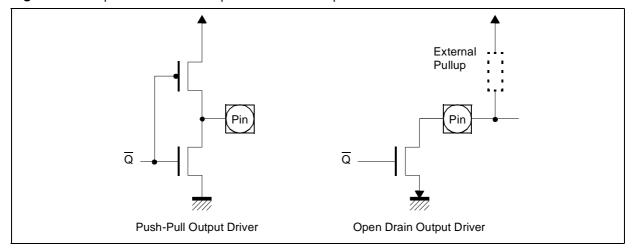

| 12.2.1 -             | Open Drain Mode                                 | 57       |

| 12.2.2 -<br>12.2.3 - | Input Threshold Control                         | 57<br>58 |

| 12.2.3 -             | Output Driver Control  Alternate Port Functions | 60       |

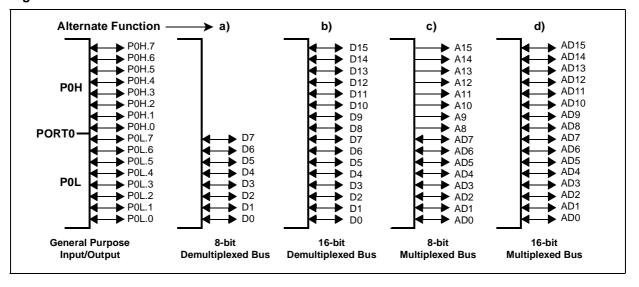

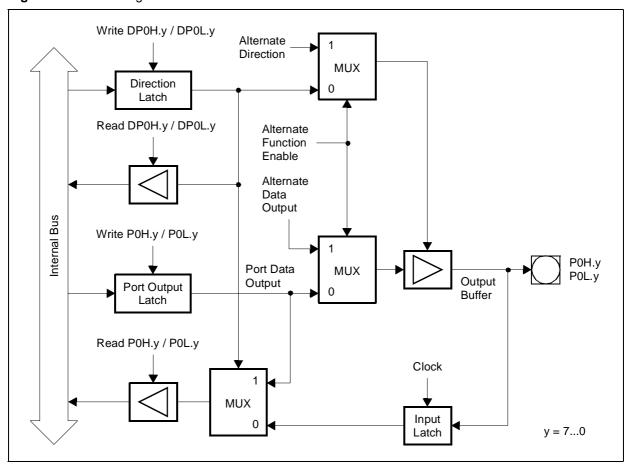

| 12.3 -               | PORT0                                           | 61       |

| 12.3.1 -             | Alternate Functions of PORT0                    | 62       |

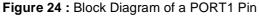

| 12.4 -               | PORT1                                           | 64       |

| 12.4.1 -             | Alternate Functions of PORT1                    | 64       |

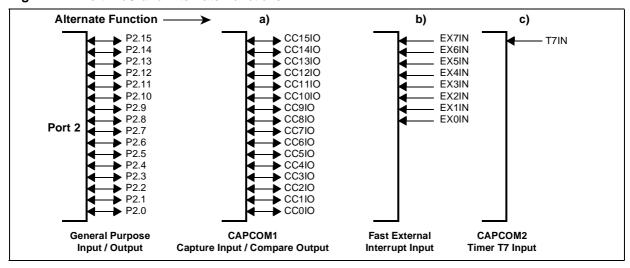

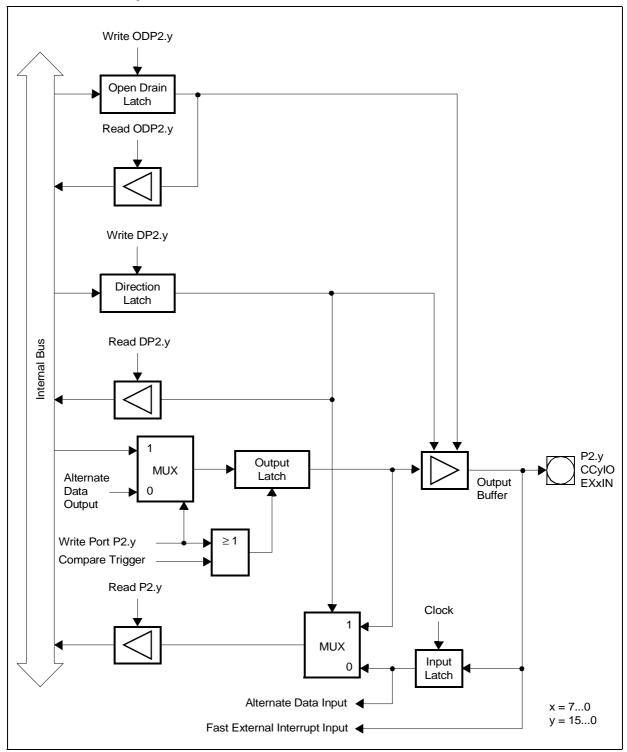

| 12.5 -               | PORT 2                                          | 66       |

| 12.5.1 -             | Alternate Functions of Port 2                   | 66       |

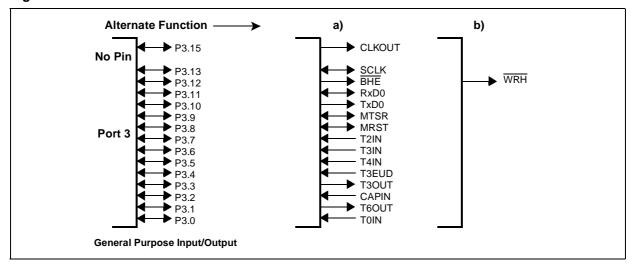

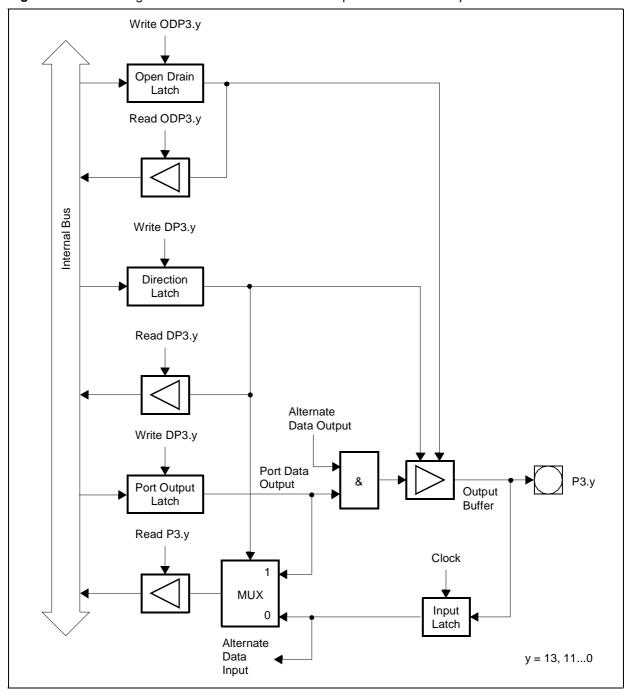

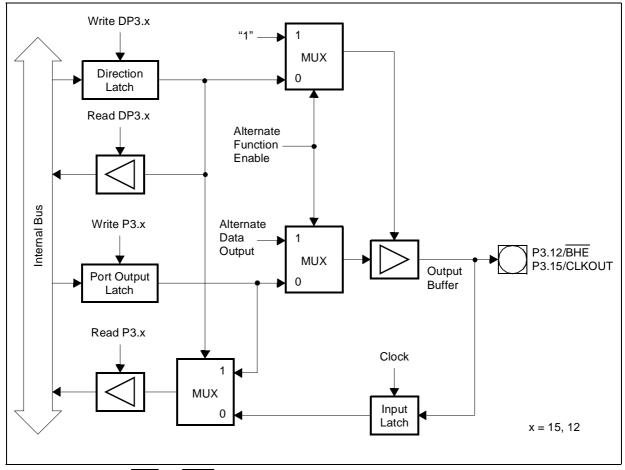

| 12.6 -               | PORT 3                                          | 69       |

| 12.6.1 -             | Alternate Functions of Port 3                   | 70       |

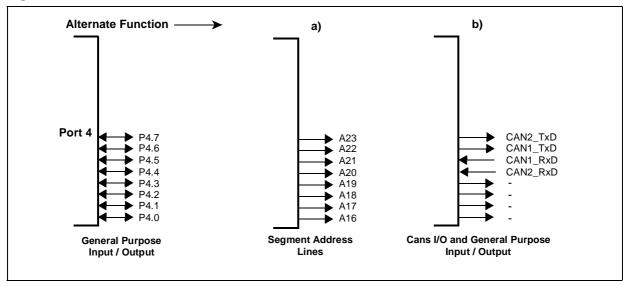

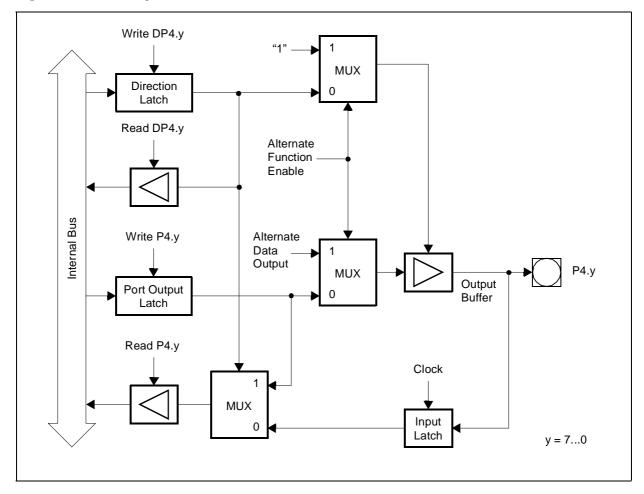

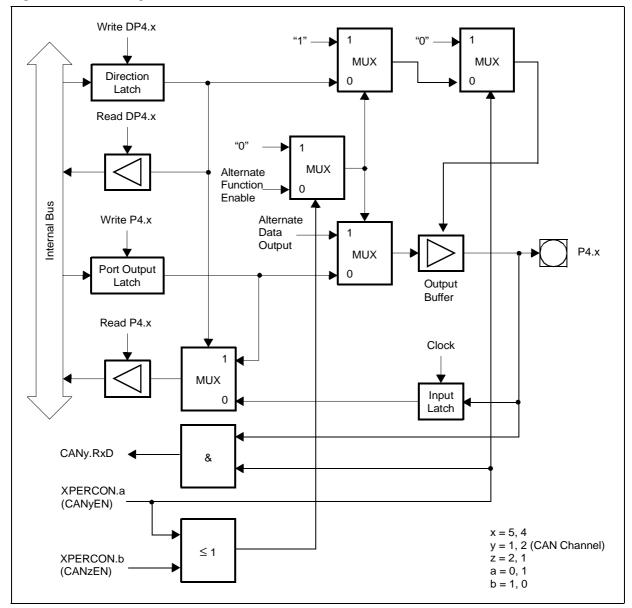

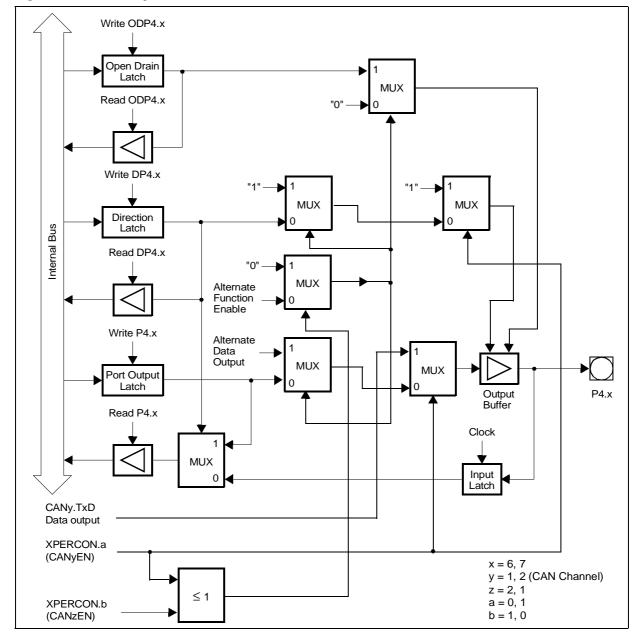

| 12.7 -               | PORT 4                                          | 73       |

| 12.7.1 -             | Alternate Functions of Port 4                   | 74       |

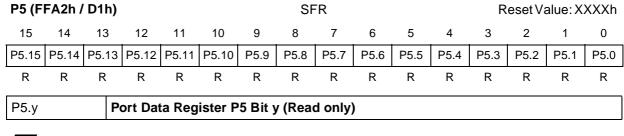

| 12.8 -               | PORT 5                                          | 77       |

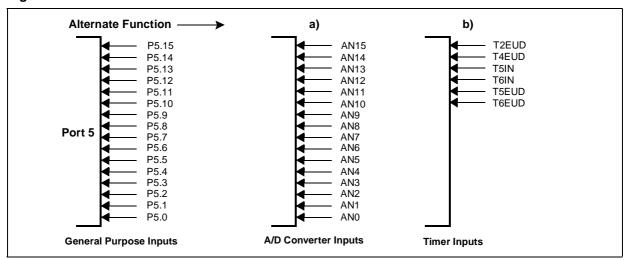

| 12.8.1 -             | Alternate Functions of Port 5                   | 78       |

| 12.8.2 -             | Port 5 Schmitt Trigger Analog Inputs            | 79       |

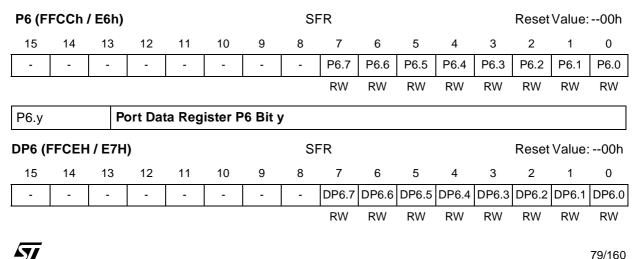

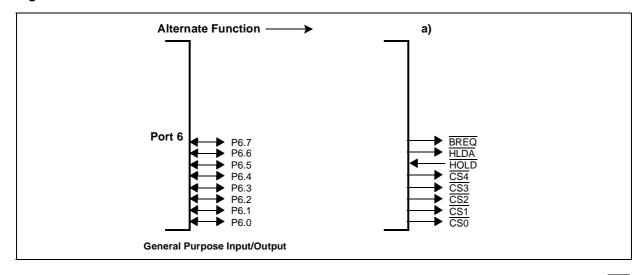

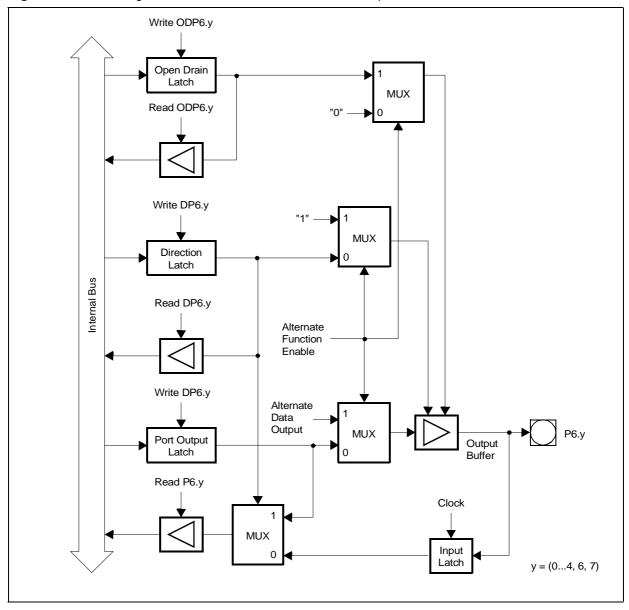

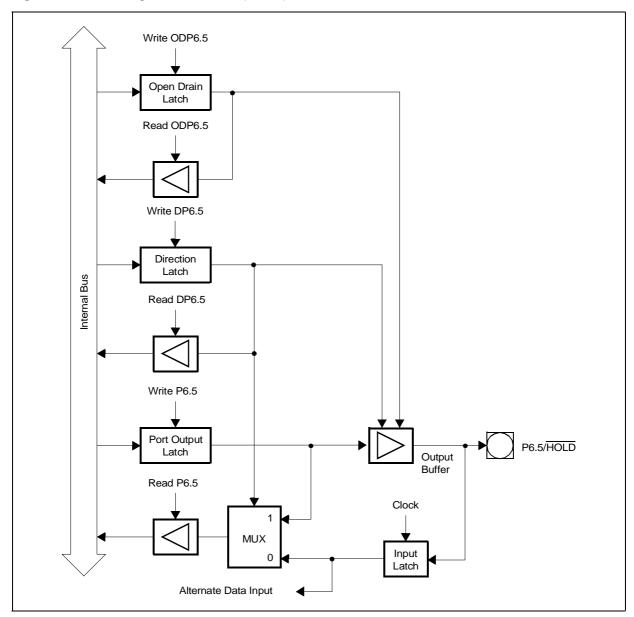

| 12.9 -               | PORT 6                                          | 79       |

| 12.9.1 -             | Alternate Functions of Port 6                   | 80       |

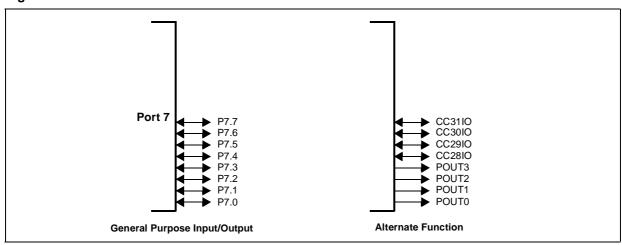

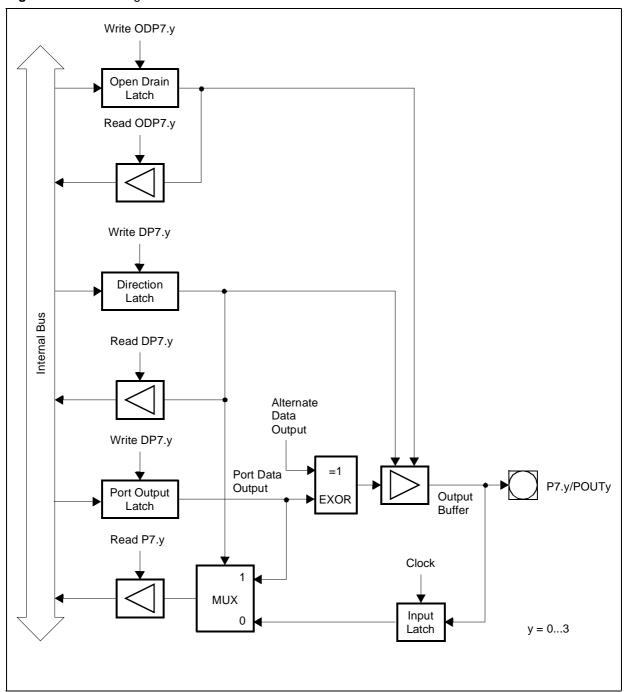

| 12.10 -              | PORT 7                                          | 83       |

| 12.10.1 -            | Alternate Functions of Port 7                   | 84       |

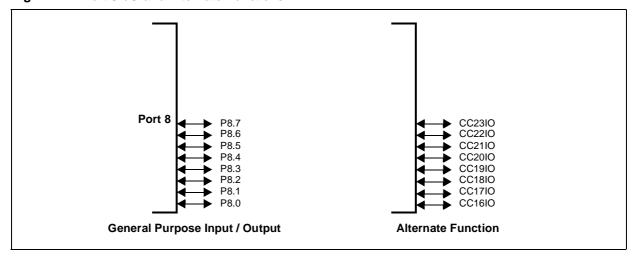

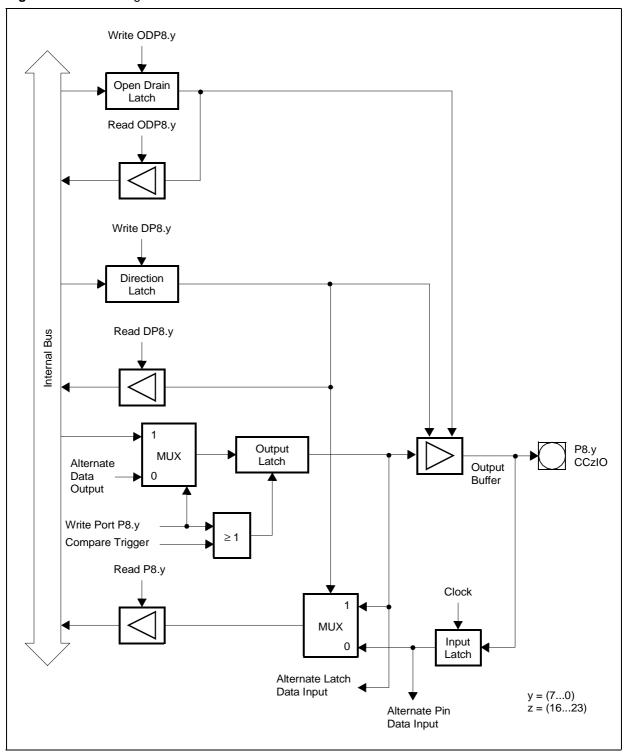

| 12.11 -              | PORT 8                                          | 87       |

| 12.11.1 -            | Alternate Functions of Port 8                   | 88       |

| TABLE OF             | CONTENTS                                                                                                             |

|----------------------|----------------------------------------------------------------------------------------------------------------------|

| 13 -                 | A/D CONVERTER                                                                                                        |

| 14 -                 | SERIAL CHANNELS                                                                                                      |

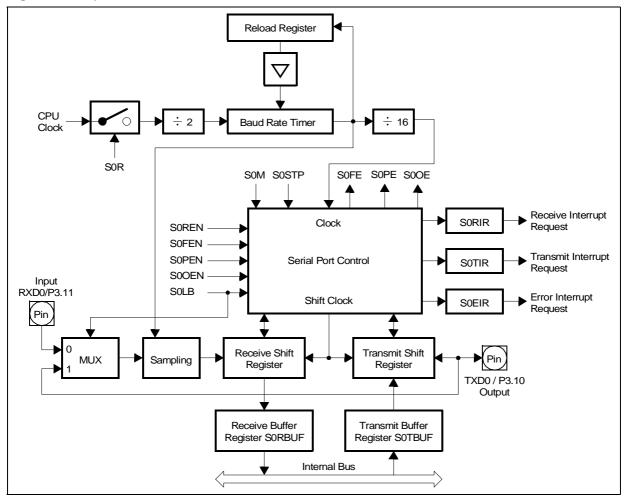

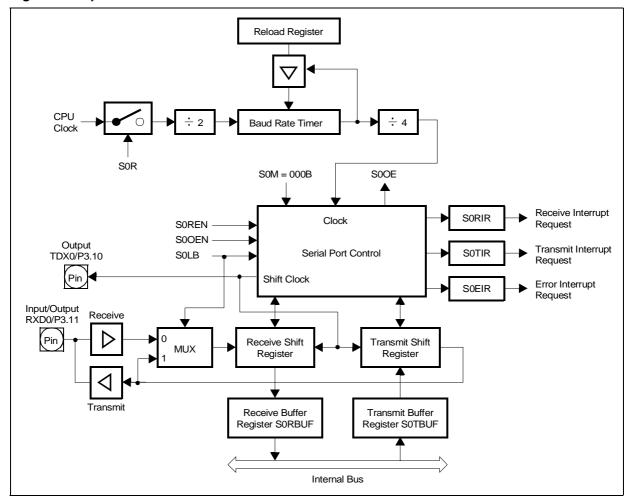

| 14.1 -               | ASYNCHRONOUS / SYNCHRONOUS SERIAL INTERFACE (ASCO)                                                                   |

| 14.1.1 -<br>14.1.2 - | ASCO in Asynchronous Mode                                                                                            |

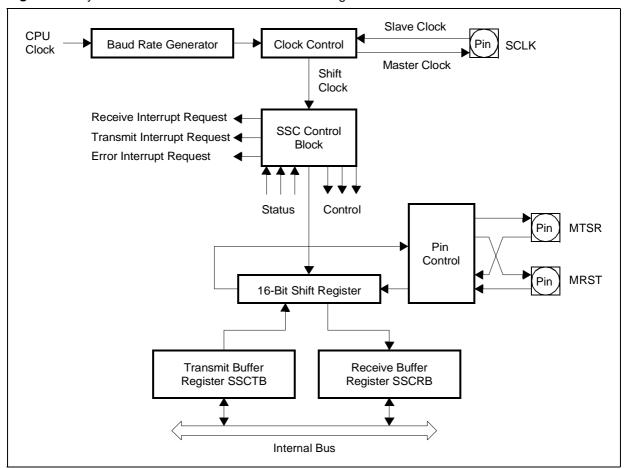

| 14.2 -               | HIGH SPEED SYNCHRONOUS SERIAL CHANNEL (SSC)                                                                          |

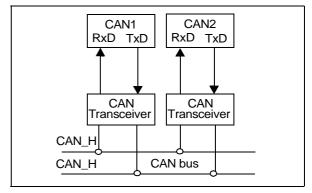

| 15 -                 | CAN MODULES                                                                                                          |

| 15.1 -               | CAN MODULES MEMORY MAPPING                                                                                           |

| 15.1.1 -             | CAN1                                                                                                                 |

| 15.1.2 -<br>15.2 -   | CAN BUS CONFIGURATIONS                                                                                               |

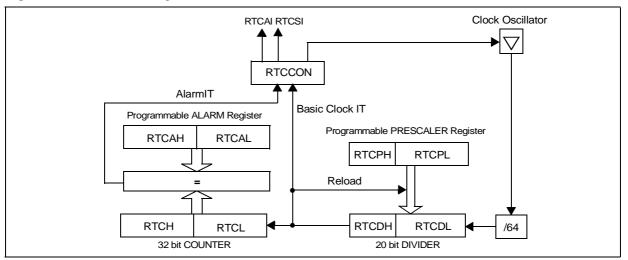

| 16 -                 | REAL TIME CLOCK                                                                                                      |

| 16.1 -               | RTC REGISTERS                                                                                                        |

| 16.1 -<br>16.1.1 -   | RTCCON: RTC Control Register                                                                                         |

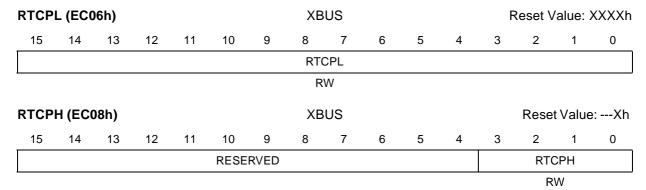

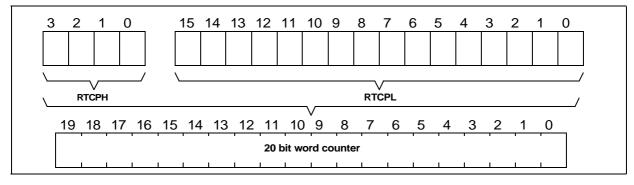

| 16.1.2 -             | RTCPH & RTCPL: RTC PRESCALER Registers                                                                               |

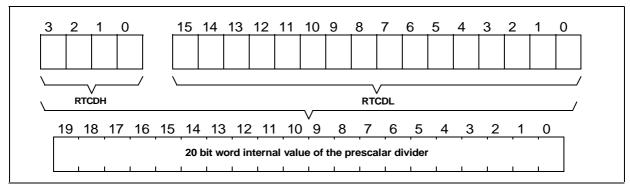

| 16.1.3 -             | RTCDH & RTCDL: RTC DIVIDER Counters                                                                                  |

| 16.1.4 -<br>16.1.5 - | RTCH & RTCL: RTC Programmable COUNTER Registers                                                                      |

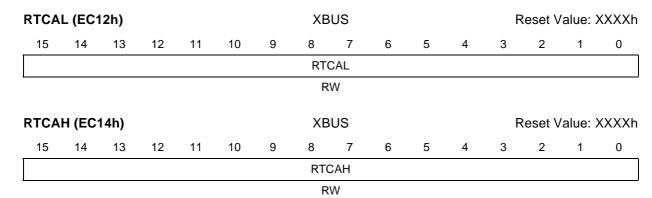

| 16.1.5 -             | RTCAH & RTCAL: RTC ALARM Registers PROGRAMMING THE RTC                                                               |

| 17 -                 | WATCHDOG TIMER                                                                                                       |

| 18 -                 | SYSTEM RESET                                                                                                         |

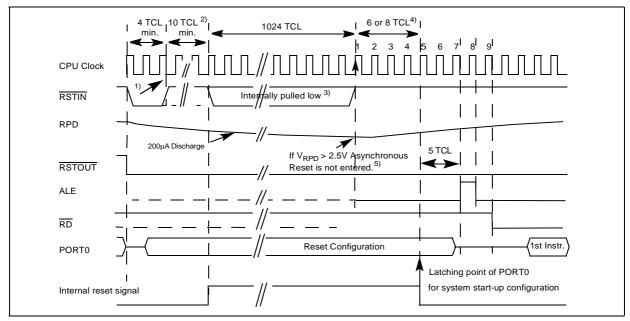

| 18.1 -               | LONG HARDWARE RESET                                                                                                  |

| 18.1.1 -             |                                                                                                                      |

| 18.1.2 -<br>18.1.3 - | Asynchronous Reset  Synchronous Reset (RSTIN pulse > 1040TCL and RPD pin at high level)  Exit of Long Hardware Reset |

| 18.2 -               | SHORT HARDWARE RESET                                                                                                 |

| 18.3 -               | SOFTWARE RESET                                                                                                       |

| 18.4 -               | WATCHDOG TIMER RESET                                                                                                 |

| 18.5 -               | RSTOUT, RSTIN, BIDIRECTIONAL RESET                                                                                   |

| 18.5.1 -             | RSTOUT Pin                                                                                                           |

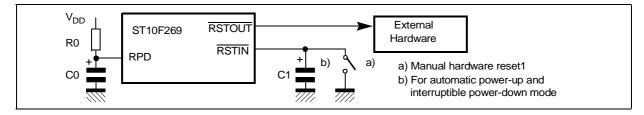

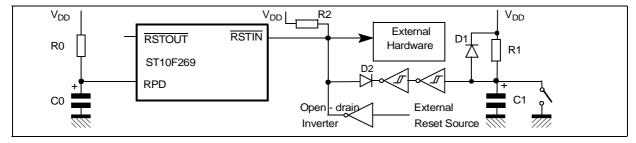

| 18.5.2 -<br>18.5.3 - | Bidirectional Reset                                                                                                  |

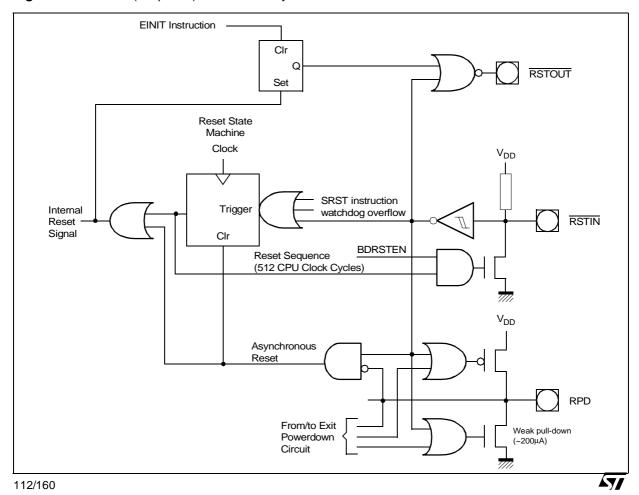

| 18.6 -               | RESET CIRCUITRY                                                                                                      |

| 19 -                 | POWER REDUCTION MODES                                                                                                |

| 19.1 -               | IDLE MODE                                                                                                            |

| 19.2 -               | POWER DOWN MODE                                                                                                      |

| 19.2.1 -<br>19.2.2 - | Protected Power Down Mode                                                                                            |

| 13.4.4               | Interruptable Power Down Mode                                                                                        |

| 4/160                |                                                                                                                      |

| TABLE OF<br>20 - | CONTENTS SPECIAL FUNCTION REGISTER OVERVIEW          | PAGE<br>117 |

|------------------|------------------------------------------------------|-------------|

| 20.1 -           | IDENTIFICATION REGISTERS                             | 123         |

| 20.2 -           | SYSTEM CONFIGURATION REGISTERS                       | 124         |

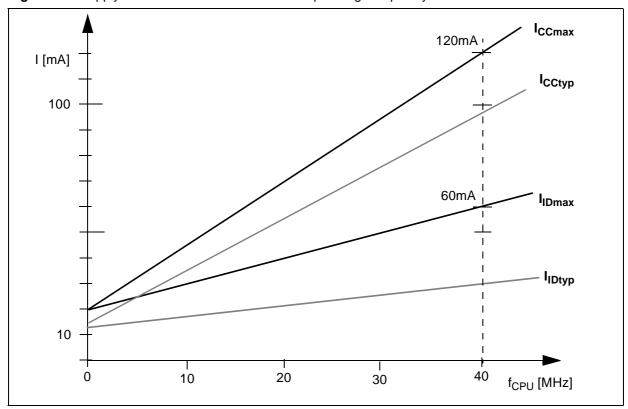

| 21 -             | ELECTRICAL CHARACTERISTICS                           | 131         |

| 21.1 -           | ABSOLUTE MAXIMUM RATINGS                             | 131         |

| 21.2 -           | PARAMETER INTERPRETATION                             | 131         |

| 21.3 -           | DC CHARACTERISTICS                                   | 131         |

| 21.3.1 -         | A/D Converter Characteristics                        | 134         |

| 21.3.2 -         | Conversion Timing Control                            | 135         |

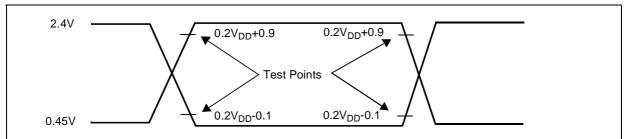

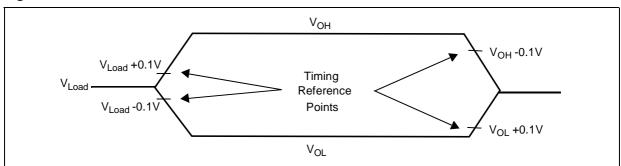

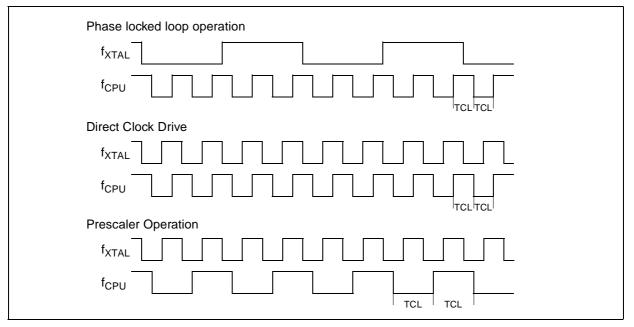

| 21.4 -           | AC CHARACTERISTICS                                   | 136         |

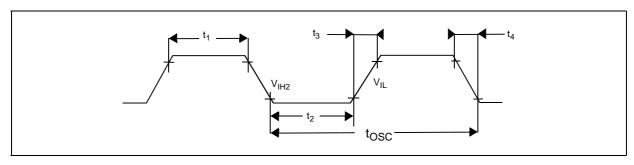

| 21.4.1 -         | Test Waveforms                                       | 136         |

| 21.4.2 -         | Definition of Internal Timing                        | 136         |

| 21.4.3 -         | Clock Generation Modes                               | 137         |

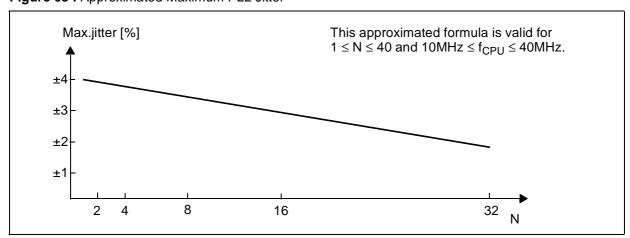

| 21.4.4 -         | Prescaler Operation                                  | 138         |

| 21.4.5 -         | Direct Drive                                         | 138         |

| 21.4.6 -         | Oscillator Watchdog (OWD)                            | 138         |

| 21.4.7 -         | Phase Locked Loop                                    | 138         |

| 21.4.8 -         | External Clock Drive XTAL1                           | 139         |

| 21.4.9 -         | Memory Cycle Variables                               | 140         |

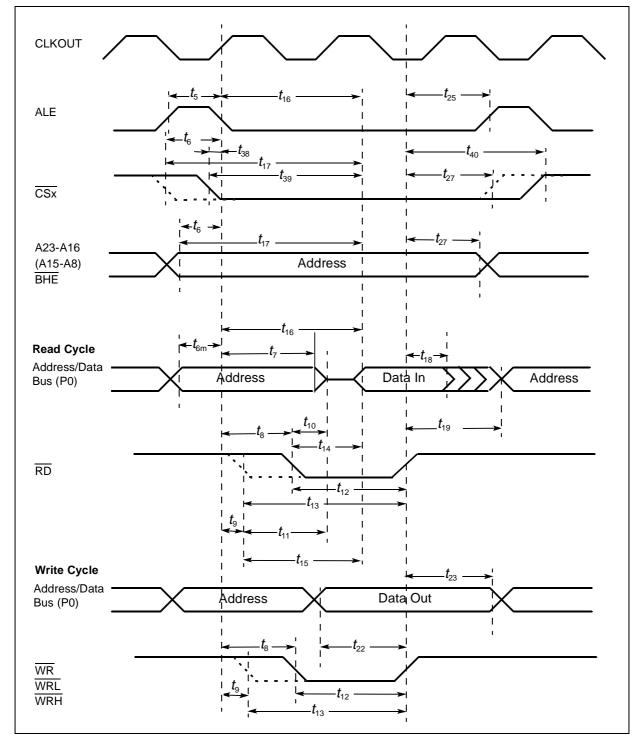

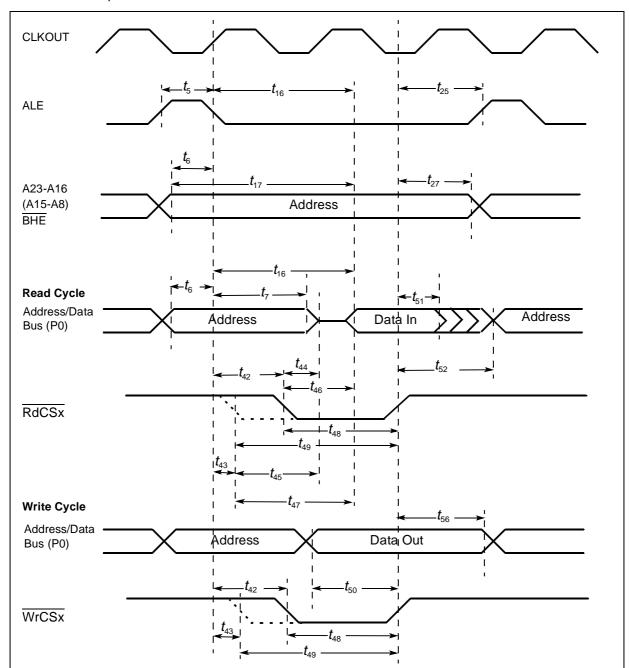

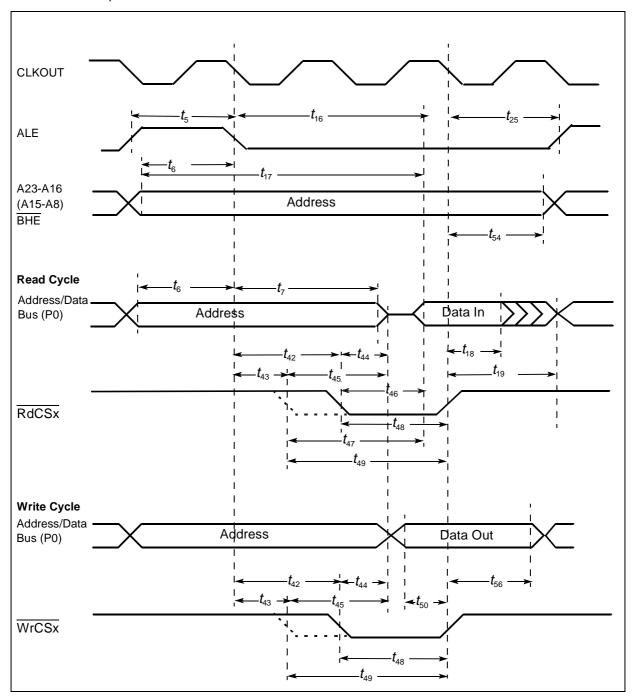

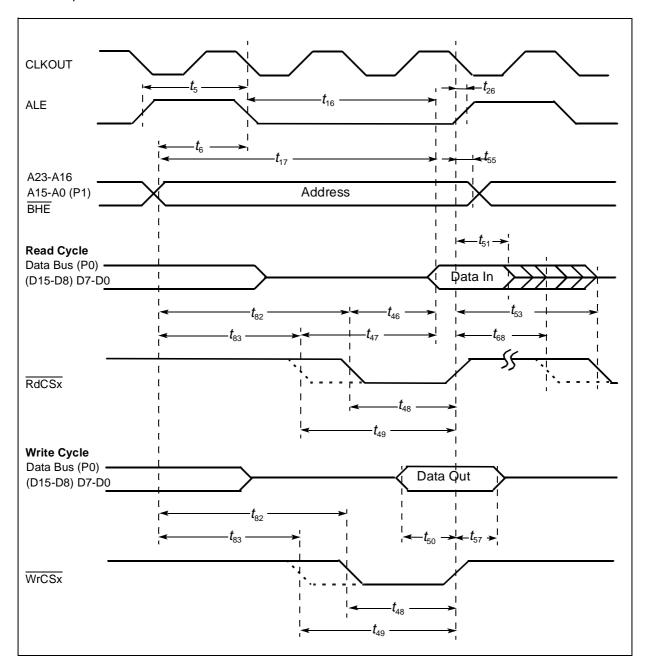

| 21.4.10 -        | Multiplexed Bus                                      | 141         |

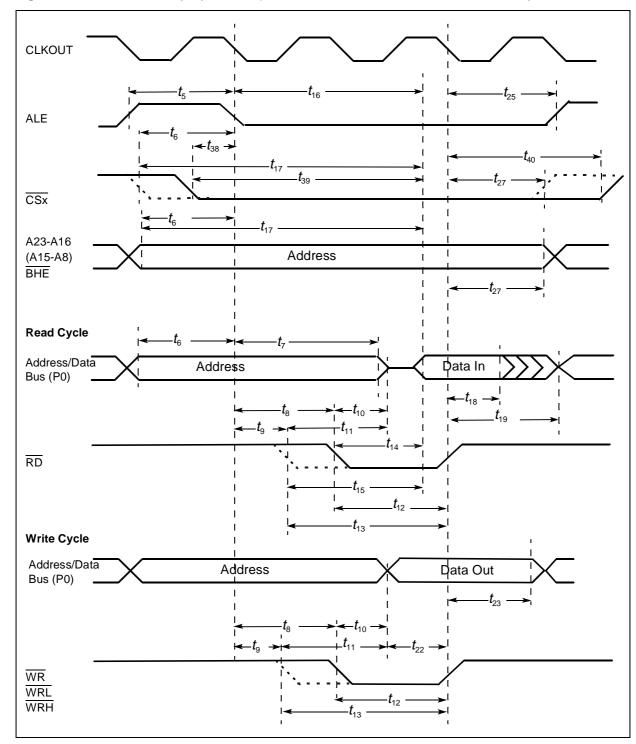

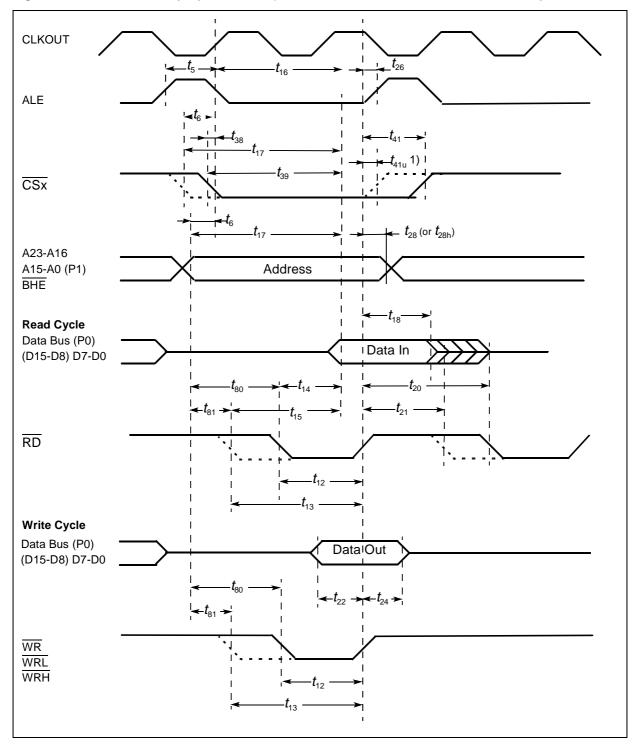

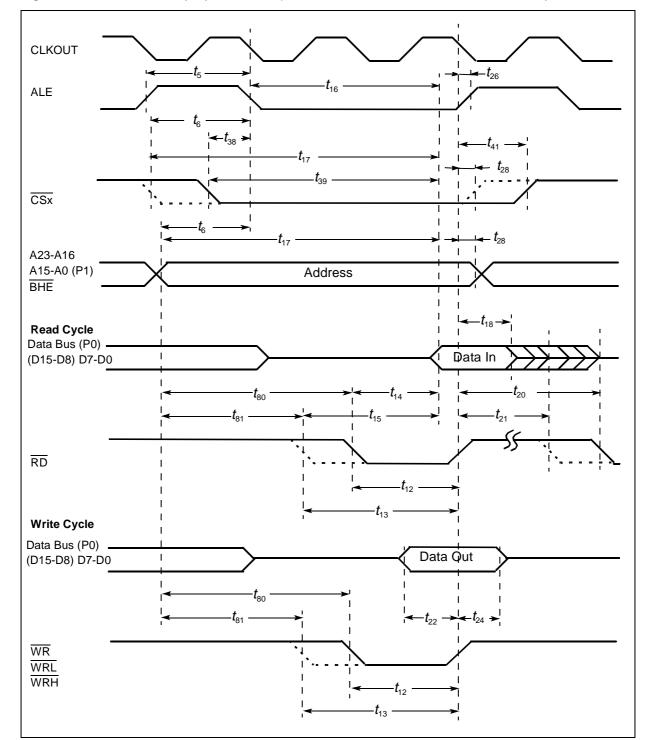

| 21.4.11 -        | Demultiplexed Bus                                    | 147         |

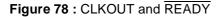

| 21.4.12 -        | CLKOUT and READY                                     | 153         |

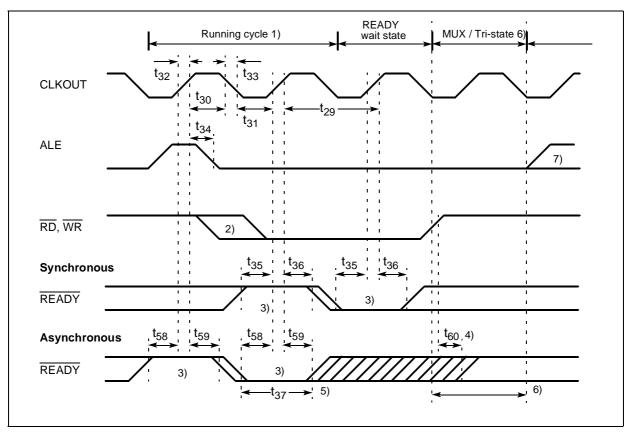

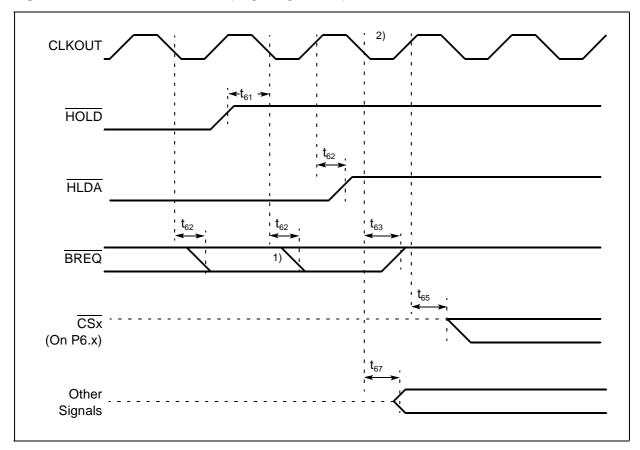

| 21.4.13 -        | External Bus Arbitration                             | 155         |

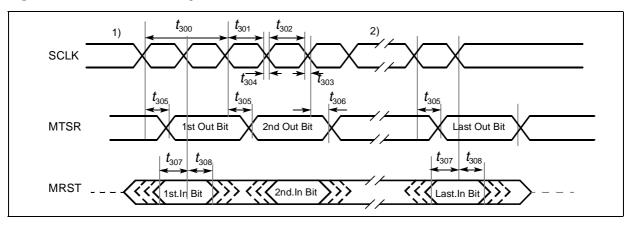

| 21.4.14 -        | High-Speed Synchronous Serial Interface (SSC) Timing | 157         |

| 21.4.14.1        | Master Mode                                          | 157         |

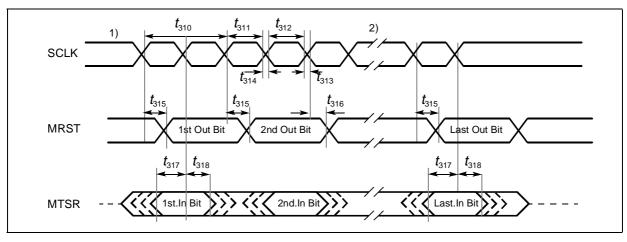

| 21.4.14.2        | Slave mode                                           | 158         |

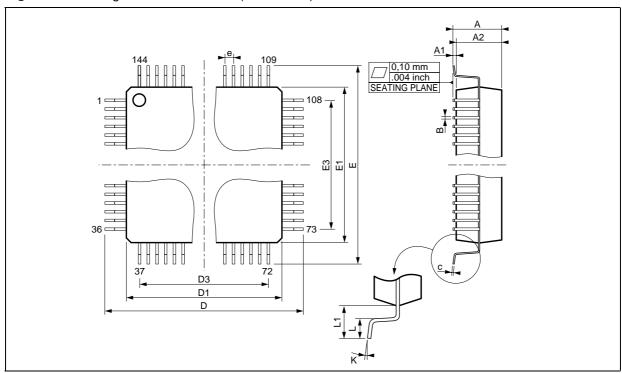

| 22 -             | PACKAGE MECHANICAL DATA                              | 159         |

| 22               | ODDEDING INFORMATION                                 | 450         |

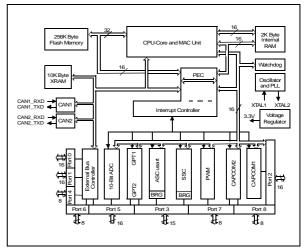

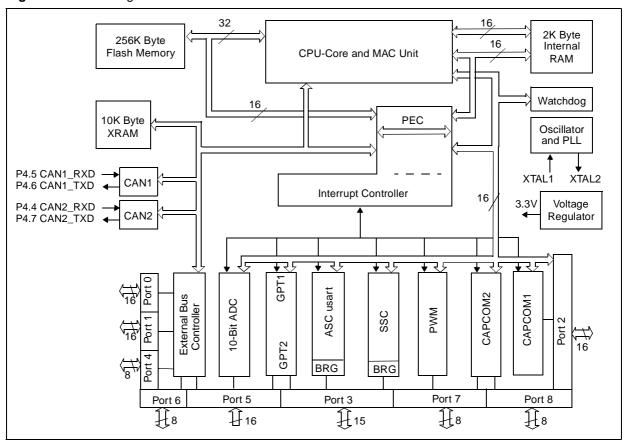

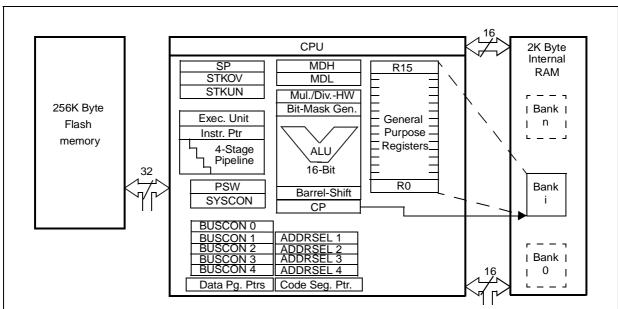

## 1 - INTRODUCTION

The ST10F269 is a derivative of the STMicroelectronics ST10 family of 16-bit single-chip CMOS microcontrollers. It combines high CPU performance (up to 20 million instructions per second) with high peripheral functionality and enhanced I/O-capabilities. It also provides on-chip high-speed single voltage Flash memory, on-chip high-speed RAM, and clock generation via PLL.

ST10F269 is processed in  $0.35\mu m$  CMOS technology. The MCU core and the logic is supplied with a 5V to 3.3V on chip voltage regulator. The part is supplied with a single 5V supply and I/Os work at 5V.

The device is upward compatible with the ST10F168 device, with the following set of differences:

- The Multiply/Accumulate unit is available as standard. This MAC unit adds powerful DSP functions to the ST10 architecture, but maintains full compatibility for existing code.

- Flash control interface is now based on STMicroelectronics third generation of stand-alone Flash memories, with an embedded Erase/Program Controller. This completely

- frees up the CPU during programming or erasing the Flash.

- Two dedicated pins (DC1 and DC2) on the PQFP-144 package are used for decoupling the internally generated 3.3V core logic supply. Do not connect these two pins to 5.0V external supply. Instead, these pins should be connected to a decoupling capacitor (ceramic type, value ≥ 330 nF).

- The A/D Converter characteristics are different from previous ST10 derivatives ones. Refer to Section 21.3.1 - A/D Converter Characteristics.

- The AC and DC parameters are adapted to the 40MHz maximum CPU frequency. The characterization is performed with  $C_L = 50 pF$  max on output pins. Refer to Section 21.3 DC Characteristics.

- In order to reduce EMC, the rise/fall time and the sink/source capability of the drivers of the I/O pads are programmable. Refer to Section 12.2 I/ O's Special Features.

- The Real Time Clock functionnality is added.

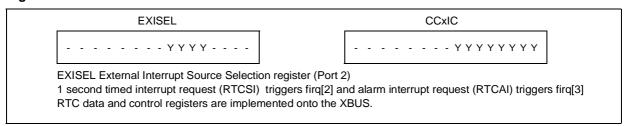

- The external interrupt sources can be selected with the EXISEL register.

- The reset source is identified by a dedicated status bit in the WDTCON register.

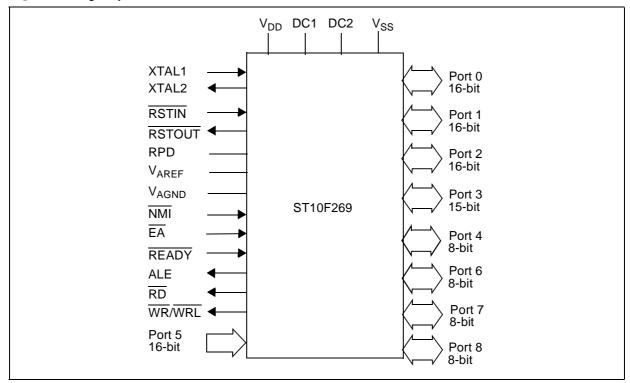

Figure 1 : Logic Symbol

#### 2 - PIN DATA

Figure 2 : Pin Configuration (top view)

```

V<sub>SS</sub>

NIMI

\begin{array}{c} 444444888\\ 48244888\\ 2824888\\ 2824888\\ 2824888\\ 2824888\\ 282488\\ 282488\\ 282488\\ 282488\\ 282488\\ 282488\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28248\\ 28

P6.0/<u>CS0</u> = 1

P6.1/<u>CS1</u> = 2

P6.2/<u>CS2</u> = 3

P6.3/<u>CS3</u> = 4

P6.4/<u>CS4</u> = 5

108 POH.0/AD8

107 POL.7/AD7

106 POL.6/AD6

105 - POL.5/AD5

104 - POL.4/AD4

103 - POL.3/AD3

P6.5/<u>HOLD</u> = 6

P6.6/<u>HLDA</u> = 7

P6.7/BREQ = 8

P8.0/CC16IO = 9

102 POL.2AD2

101 POL.A/AD1

100 POL.0/AD0

P8.1/CC17IO =

10

99 🗕 EA

P8.2/CC18IO P8.3/CC19IO

98 - ALE

97 - READY

P8.4/CC20IO = 13

96 - WR/WRL

95 - RD

94 - V<sub>SS</sub>

P8.5/CC21IO -

14

P8.6/CC22IO = P8.7/CC23IO =

15

16

93 P V<sub>DD</sub>

92 P P4.7A23/CAN2_TxD

DC2

17

V<sub>SS</sub> P7.0/POUT0 P

92 P P4.7A23/CAN2_IXD

91 P P4.6A22/CAN1_TXD

90 P P4.5A21/CAN1_RXD

89 P P4.4A20/CAN2_RXD

88 P P4.3/A19

87 P P4.2/A18

86 P P4.1/A17

18

19

ST10F269-Q3

P7.1/POUT1 = 20

P7.2/POUT2 -

21

P7.3/POUT3 = 22

P7.4/CC2810 = 23

P7.5/CC2910 = 24

P7.6/CC3010 = 25

P7.7/CC3110 = 26

86 P P4.1/A17

85 P P4.0/A16

84 P RPD

83 P V<sub>SS</sub>

82 P V<sub>DD</sub>

81 P P3.15/CLKOUT

80 P P3.13/SCLK

79 P P3.12/BHE/WRH

78 P P3.11/RXD0

77 P P3.10/TXD0

76 P P3.9/MTSR

P5.0/AN0 = 27

P5.1/AN1 = 28

P5.2/AN2 - 29

P5.3/AN3 = 30

P5.4/AN4 = 31

P5.5/AN5 = 32

P5.6/AN6 = 33

76 P P3.9/MTSR

75 P P3.8/MRST

74 P P3.7/T2IN

73 P P3.6/T3IN

P5.7/AN7

34

P5.8/AN8 =

P5.9/AN9 - 36

\begin{array}{c} 33.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\ 23.3\\

P2.8/CC8IO/EXJIN P2.9/CC9IO/EXJIN P2.10/CC10IOEXZIN P2.11/CC11IOEXZIN P2.12/CC12IO/EXZIN P2.13/CC13IO/EXZIN P2.14/CC14IO/EXZIN P2.14/CC14IO/EXZIN P2.14/CC14IO/EXZIN P3.17/FIN P

VAGND

VAGND

P5.10/AN10/T6EUD

P5.11/AN11/T5EUD

P5.13/AN12/T5IN

P5.14/AN14/T4EUD

P5.15/AN15/T2EUD

P2.0/CC10

P2.1/CC10

P2.1/CC10

P2.2/CC210

P2.3/CC310

P2.3/CC310

P2.3/CC310

P2.3/CC310

P2.4/CC10

P2.4/CC10

P2.4/CC10

P2.4/CC10

P2.4/CC10

P2.4/CC10

P2.5/CC510

P2.5/CC510

P2.5/CC510

P2.5/CC510

P2.5/CC510

P2.5/CC510

P2.5/CC510

P2.5/CC510

P2.

```

Table 1: Pin Description

| Symbol                       | Pin            | Туре   | e Function                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                        |                                                                                                                                                                                                                                |  |  |  |  |  |

|------------------------------|----------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| P6.0 - P6.7                  | 1 - 8          | I/O    | 8-bit bidirectional I/O port, bit-wise programmable for input or output via direction bit. Programming an I/O pin as input forces the corresponding output driver to hig impedance state. Port 6 outputs can be configured as push-pull or open draid drivers. The following Port 6 pins have alternate functions:                                                               |                                                                                                                                                        |                                                                                                                                                                                                                                |  |  |  |  |  |

|                              | 1              | 0      | P6.0                                                                                                                                                                                                                                                                                                                                                                             | CS0                                                                                                                                                    | Chip Select 0 Output                                                                                                                                                                                                           |  |  |  |  |  |

|                              |                |        |                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                        |                                                                                                                                                                                                                                |  |  |  |  |  |

|                              | 5              | 0      | P6.4                                                                                                                                                                                                                                                                                                                                                                             | CS4                                                                                                                                                    | Chip Select 4 Output                                                                                                                                                                                                           |  |  |  |  |  |

|                              | 6              | - 1    | P6.5                                                                                                                                                                                                                                                                                                                                                                             | HOLD                                                                                                                                                   | External Master Hold Request Input                                                                                                                                                                                             |  |  |  |  |  |

|                              | 7              | 0      | P6.6                                                                                                                                                                                                                                                                                                                                                                             | HLDA                                                                                                                                                   | Hold Acknowledge Output                                                                                                                                                                                                        |  |  |  |  |  |

|                              | 8              | 0      | P6.7                                                                                                                                                                                                                                                                                                                                                                             | BREQ                                                                                                                                                   | Bus Request Output                                                                                                                                                                                                             |  |  |  |  |  |

| P8.0 - P8.7                  | 9-16           | I/O    | 8-bit bidirectional I/O port, bit-wise programmable for input or output via directio bit. Programming an I/O pin as input forces the corresponding output driver to high impedance state. Port 8 outputs can be configured as push-pull or open drain drivers. The input threshold of Port 8 is selectable (TTL or special). The following Port 8 pins have alternate functions: |                                                                                                                                                        |                                                                                                                                                                                                                                |  |  |  |  |  |

|                              | 9              | I/O    | P8.0                                                                                                                                                                                                                                                                                                                                                                             | CC16IO                                                                                                                                                 | CAPCOM2: CC16 Capture Input / Compare Output                                                                                                                                                                                   |  |  |  |  |  |

|                              |                |        |                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                        |                                                                                                                                                                                                                                |  |  |  |  |  |

|                              | 16             | I/O    | P8.7                                                                                                                                                                                                                                                                                                                                                                             | CC23IO                                                                                                                                                 | CAPCOM2: CC23 Capture Input / Compare Output                                                                                                                                                                                   |  |  |  |  |  |

| P7.0 - P7.7                  | 19-26          | I/O    | bit. Pro<br>impeda<br>drivers.                                                                                                                                                                                                                                                                                                                                                   | gramming an I/C<br>nce state. Port<br>The input thresh                                                                                                 | ort, bit-wise programmable for input or output via direction pin as input forces the corresponding output driver to high 7 outputs can be configured as push-pull or open drain hold of Port 7 is selectable (TTL or special). |  |  |  |  |  |

|                              | 19             | 0      | P7.0                                                                                                                                                                                                                                                                                                                                                                             | POUT0                                                                                                                                                  | PWM Channel 0 Output                                                                                                                                                                                                           |  |  |  |  |  |

|                              |                |        |                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                        |                                                                                                                                                                                                                                |  |  |  |  |  |

|                              | 22             | 0      | P7.3                                                                                                                                                                                                                                                                                                                                                                             | POUT3                                                                                                                                                  | PWM Channel 3 Output                                                                                                                                                                                                           |  |  |  |  |  |

|                              | 23             | I/O    | P7.4                                                                                                                                                                                                                                                                                                                                                                             | CC28IO                                                                                                                                                 | CAPCOM2: CC28 Capture Input / Compare Output                                                                                                                                                                                   |  |  |  |  |  |

|                              |                |        |                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                        |                                                                                                                                                                                                                                |  |  |  |  |  |

|                              | 26             | I/O    | P7.7                                                                                                                                                                                                                                                                                                                                                                             | CC31IO                                                                                                                                                 | CAPCOM2: CC31 Capture Input / Compare Output                                                                                                                                                                                   |  |  |  |  |  |

| P5.0 - P5.9<br>P5.10 - P5.15 | 27-36<br>39-44 | l<br>I | the ana                                                                                                                                                                                                                                                                                                                                                                          | th Schmitt-Trigger characteristics. The pins of Port 5 can be els (up to 16) for the A/D converter, where P5.x equals ANx ), or they are timer inputs: |                                                                                                                                                                                                                                |  |  |  |  |  |

|                              | 39             | - 1    | P5.10                                                                                                                                                                                                                                                                                                                                                                            | T6EUD                                                                                                                                                  | GPT2 Timer T6 External Up / Down Control Input                                                                                                                                                                                 |  |  |  |  |  |

|                              | 40             | 1      | P5.11                                                                                                                                                                                                                                                                                                                                                                            | T5EUD                                                                                                                                                  | GPT2 Timer T5 External Up / Down Control Input                                                                                                                                                                                 |  |  |  |  |  |

|                              | 41             | 1      | P5.12                                                                                                                                                                                                                                                                                                                                                                            | T6IN                                                                                                                                                   | GPT2 Timer T6 Count Input                                                                                                                                                                                                      |  |  |  |  |  |

|                              | 42             | 1      | P5.13                                                                                                                                                                                                                                                                                                                                                                            | T5IN                                                                                                                                                   | GPT2 Timer T5 Count Input                                                                                                                                                                                                      |  |  |  |  |  |

|                              | 43             | 1      | P5.14                                                                                                                                                                                                                                                                                                                                                                            | T4EUD                                                                                                                                                  | GPT1 Timer T4 External Up / Down Control Input                                                                                                                                                                                 |  |  |  |  |  |

|                              | 44             | 1      | P5.15                                                                                                                                                                                                                                                                                                                                                                            | T2EUD                                                                                                                                                  | GPT1 Timer T2 External Up / Down Control Input                                                                                                                                                                                 |  |  |  |  |  |

| Symbol                                | Pin                    | Туре              |                                                                                                                                                                                                                                                                                                                                                                                      |        | Function                                                |  |  |  |  |

|---------------------------------------|------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------------------------------------------|--|--|--|--|

| P2.0 - P2.7<br>P2.8 - P2.15           | 47-54<br>57-64         | I/O               | 16-bit bidirectional I/O port, bit-wise programmable for input or output via direction bit. Programming an I/O pin as input forces the corresponding output driver to high impedance state. Port 2 outputs can be configured as push-pull or open drain drivers. The input threshold of Port 2 is selectable (TTL or special). The following Port 2 pins have alternate functions:   |        |                                                         |  |  |  |  |

|                                       | 47                     | I/O               | P2.0                                                                                                                                                                                                                                                                                                                                                                                 | CC0IO  | CAPCOM: CC0 Capture Input / Compare Output              |  |  |  |  |

|                                       |                        |                   |                                                                                                                                                                                                                                                                                                                                                                                      |        |                                                         |  |  |  |  |

|                                       | 54                     | I/O               | P2.7                                                                                                                                                                                                                                                                                                                                                                                 | CC7IO  | CAPCOM: CC7 Capture Input / Compare Output              |  |  |  |  |

|                                       | 57                     | I/O               | P2.8                                                                                                                                                                                                                                                                                                                                                                                 | CC8IO  | CAPCOM: CC8 Capture Input / Compare Output              |  |  |  |  |

|                                       |                        | 1                 |                                                                                                                                                                                                                                                                                                                                                                                      | EX0IN  | Fast External Interrupt 0 Input                         |  |  |  |  |

|                                       |                        |                   |                                                                                                                                                                                                                                                                                                                                                                                      |        |                                                         |  |  |  |  |

|                                       | 64                     | I/O               | P2.15                                                                                                                                                                                                                                                                                                                                                                                | CC15IO | CAPCOM: CC15 Capture Input / Compare Output             |  |  |  |  |

|                                       |                        | - 1               |                                                                                                                                                                                                                                                                                                                                                                                      | EX7IN  | Fast External Interrupt 7 Input                         |  |  |  |  |

|                                       |                        | 1                 |                                                                                                                                                                                                                                                                                                                                                                                      | T7IN   | CAPCOM2 Timer T7 Count Input                            |  |  |  |  |

| P3.0 - P3.5<br>P3.6 - P3.13,<br>P3.15 | 65-70,<br>73-80,<br>81 | I/O<br>I/O<br>I/O | 15-bit (P3.14 is missing) bidirectional I/O port, bit-wise programmable for inpoutput via direction bit. Programming an I/O pin as input forces the correspor output driver to high impedance state. Port 3 outputs can be configured as push or open drain drivers. The input threshold of Port 3 is selectable (TTL or special The following Port 3 pins have alternate functions: |        |                                                         |  |  |  |  |

|                                       | 65                     | 1                 | P3.0                                                                                                                                                                                                                                                                                                                                                                                 | TOIN   | CAPCOM Timer T0 Count Input                             |  |  |  |  |

|                                       | 66                     | 0                 | P3.1                                                                                                                                                                                                                                                                                                                                                                                 | T6OUT  | GPT2 Timer T6 Toggle Latch Output                       |  |  |  |  |

|                                       | 67                     | - 1               | P3.2                                                                                                                                                                                                                                                                                                                                                                                 | CAPIN  | GPT2 Register CAPREL Capture Input                      |  |  |  |  |

|                                       | 68                     | 0                 | P3.3                                                                                                                                                                                                                                                                                                                                                                                 | T3OUT  | GPT1 Timer T3 Toggle Latch Output                       |  |  |  |  |

|                                       | 69                     | 1                 | P3.4                                                                                                                                                                                                                                                                                                                                                                                 | T3EUD  | GPT1 Timer T3 External Up / Down Control Input          |  |  |  |  |

|                                       | 70                     | 1                 | P3.5                                                                                                                                                                                                                                                                                                                                                                                 | T4IN   | GPT1 Timer T4 Input for Count / Gate / Reload / Capture |  |  |  |  |

|                                       | 73                     | 1                 | P3.6                                                                                                                                                                                                                                                                                                                                                                                 | T3IN   | GPT1 Timer T3 Count / Gate Input                        |  |  |  |  |

|                                       | 74                     | 1                 | P3.7                                                                                                                                                                                                                                                                                                                                                                                 | T2IN   | GPT1 Timer T2 Input for Count / Gate / Reload / Capture |  |  |  |  |

|                                       | 75                     | I/O               | P3.8                                                                                                                                                                                                                                                                                                                                                                                 | MRST   | SSC Master-Receiver / Slave-Transmitter I/O             |  |  |  |  |

|                                       | 76                     | I/O               | P3.9                                                                                                                                                                                                                                                                                                                                                                                 | MTSR   | SSC Master-Transmitter / Slave-Receiver O/I             |  |  |  |  |

|                                       | 77                     | 0                 | P3.10                                                                                                                                                                                                                                                                                                                                                                                | TxD0   | ASC0 Clock / Data Output (Asynchronous / Synchronous)   |  |  |  |  |

|                                       | 78                     | I/O               | P3.11                                                                                                                                                                                                                                                                                                                                                                                | RxD0   | ASC0 Data Input (Asynchronous) or I/O (Synchronous)     |  |  |  |  |

|                                       | 79                     | 0                 | P3.12                                                                                                                                                                                                                                                                                                                                                                                | BHE    | External Memory High Byte Enable Signal                 |  |  |  |  |

|                                       |                        |                   |                                                                                                                                                                                                                                                                                                                                                                                      | WRH    | External Memory High Byte Write Strobe                  |  |  |  |  |

|                                       | 80                     | I/O               | P3.13                                                                                                                                                                                                                                                                                                                                                                                | SCLK   | SSC Master Clock Output / Slave Clock Input             |  |  |  |  |

|                                       | 81                     | 0                 | P3.15                                                                                                                                                                                                                                                                                                                                                                                | CLKOUT | System Clock Output (=CPU Clock)                        |  |  |  |  |

| Symbol          | Pin   | Туре |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                 | Function                                                                                                                                                     |  |  |  |  |

|-----------------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| P4.0 -P4.7      | 85-92 | I/O  | Port 4 is an 8-bit bidirectional I/O port. It is bit-wise programmable for input or output via direction bit. Programming an I/O pin as input forces the corresponding output driver to high impedance state. The input threshold is selectable (TTL or special). Port 4.6 & 4.7 outputs can be configured as push-pull or open drain drivers. In case of an external bus configuration, Port 4 can be used to output the segment address lines: |                 |                                                                                                                                                              |  |  |  |  |

|                 | 85    | 0    | P4.0                                                                                                                                                                                                                                                                                                                                                                                                                                             | A16             | Segment Address Line                                                                                                                                         |  |  |  |  |

|                 | 86    | 0    | P4.1                                                                                                                                                                                                                                                                                                                                                                                                                                             | A17             | Segment Address Line                                                                                                                                         |  |  |  |  |

|                 | 87    | 0    | P4.2                                                                                                                                                                                                                                                                                                                                                                                                                                             | A18             | Segment Address Line                                                                                                                                         |  |  |  |  |

|                 | 88    | 0    | P4.3                                                                                                                                                                                                                                                                                                                                                                                                                                             | A19             | Segment Address Line                                                                                                                                         |  |  |  |  |

|                 | 89    | 0    | P4.4                                                                                                                                                                                                                                                                                                                                                                                                                                             | A20             | Segment Address Line                                                                                                                                         |  |  |  |  |

|                 |       | - 1  |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CAN2_RxD        | CAN2 Receive Data Input                                                                                                                                      |  |  |  |  |

|                 | 90    | 0    | P4.5                                                                                                                                                                                                                                                                                                                                                                                                                                             | A21             | Segment Address Line                                                                                                                                         |  |  |  |  |

|                 |       | 1    |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CAN1_RxD        | CAN1 Receive Data Input                                                                                                                                      |  |  |  |  |

|                 | 91    | 0    | P4.6                                                                                                                                                                                                                                                                                                                                                                                                                                             | A22             | Segment Address Line                                                                                                                                         |  |  |  |  |

|                 |       | 0    |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CAN1_TxD        | CAN1 Transmit Data Output                                                                                                                                    |  |  |  |  |

|                 | 92    | 0    | P4.7                                                                                                                                                                                                                                                                                                                                                                                                                                             | A23             | Most Significant Segment Address Line                                                                                                                        |  |  |  |  |

|                 |       | 0    |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CAN2_TxD        | CAN2 Transmit Data Output                                                                                                                                    |  |  |  |  |

| RD              | 95    | 0    | Externa<br>read ac                                                                                                                                                                                                                                                                                                                                                                                                                               |                 | Strobe. RD is activated for every external instruction or data                                                                                               |  |  |  |  |

| WR/WRL          | 96    | 0    | External Memory Write Strobe. In WR-mode this pin is activated for every external data write access. In WRL mode this pin is activated for low Byte data write accesses on a 16-bit bus, and for every data write access on an 8-bit bus. See WRCFG in the SYSCON register for mode selection.                                                                                                                                                   |                 |                                                                                                                                                              |  |  |  |  |

| READY/<br>READY | 97    | I    | Ready Input. The active level is programmable. When the Ready function is enabled, the selected inactive level at this pin, during an external memory access, will force the insertion of waitstate cycles until the pin returns to the selected active level.                                                                                                                                                                                   |                 |                                                                                                                                                              |  |  |  |  |

| ALE             | 98    | 0    | Address Latch Enable Output. In case of use of external addressing or of multiplexed mode, this signal is the latch command of the address lines.                                                                                                                                                                                                                                                                                                |                 |                                                                                                                                                              |  |  |  |  |

| ĒĀ              | 99    | I    | forces                                                                                                                                                                                                                                                                                                                                                                                                                                           | the ST10F269 to | e pin. A low level applied to this pin during and after Reset o start the program from the external memory space. A high start in the internal memory space. |  |  |  |  |

| Symbol                                   | Pin                         | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|------------------------------------------|-----------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

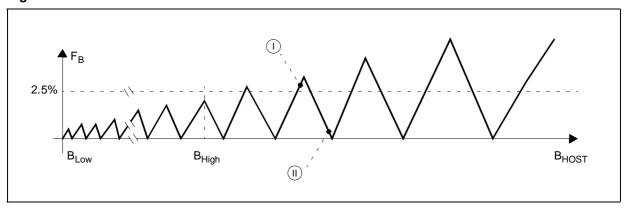

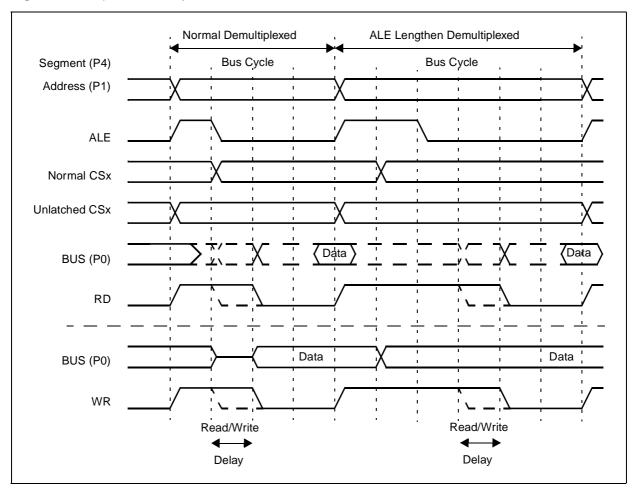

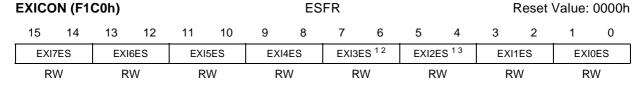

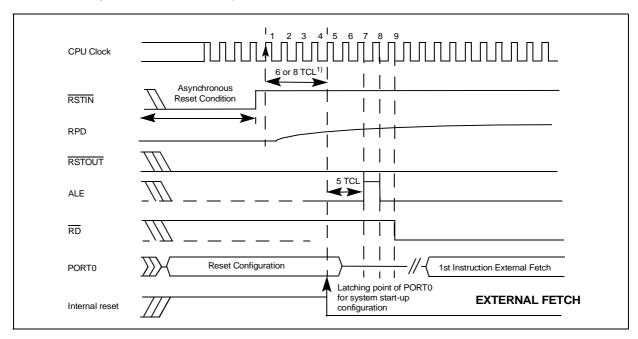

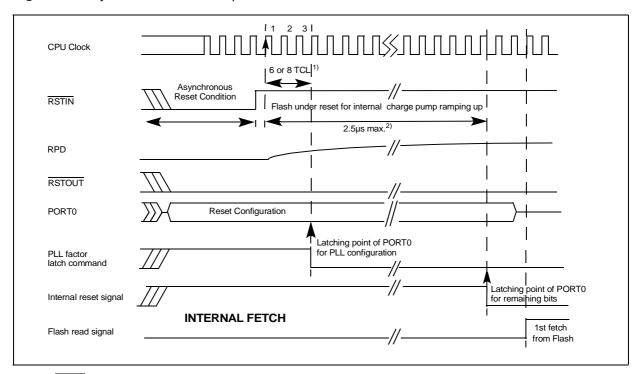

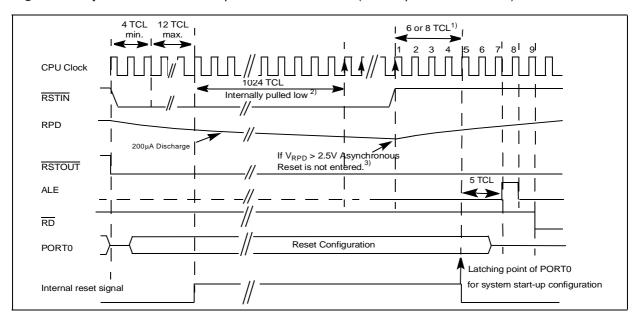

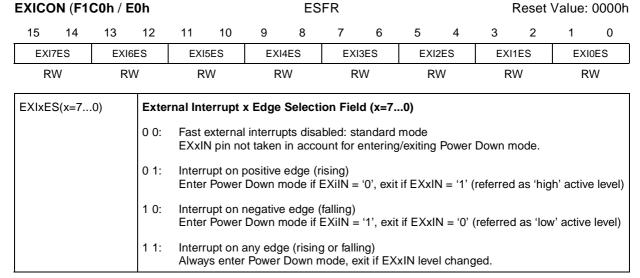

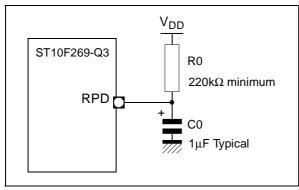

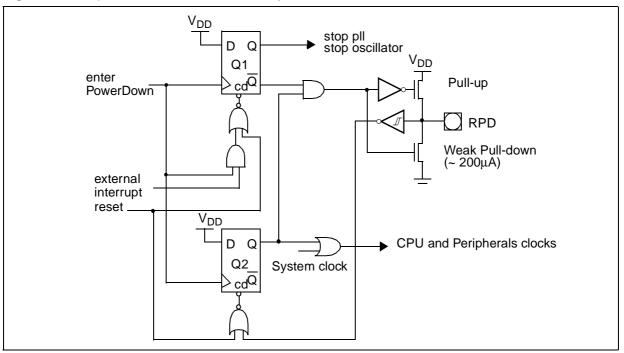

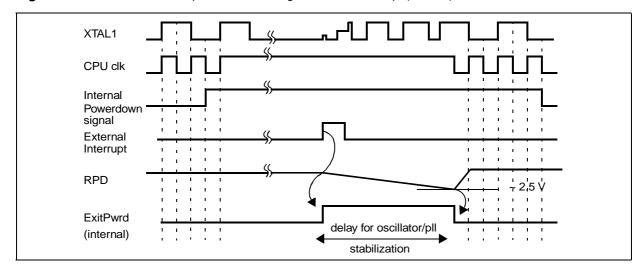

| P0L.0 - P0L.7,<br>P0H.0<br>P0H.1 - P0H.7 | 100-107,<br>108,<br>111-117 | I/O  | Two 8-bit bidirectional I/O ports P0L and P0H, bit-wise programmable for input or output via direction bit. Programming an I/O pin as input forces the corresponding output driver to high impedance state. In case of an external bus configuration, PORT0 serves as the address (A) and as the address / data (AD) bus in multiplexed bus modes and as the data (D) bus in demultiplexed bus modes.                                                                                 |  |  |  |  |  |  |