# ZGM230S Z-Wave 800 SiP Module Data Sheet

The ZGM230S is a system-in-package (SiP) module for Z-Wave connectivity and networking built for the performance, security, and energy demands of the Smart Home.

Based on the EFR32ZG23 SoC, it delivers robust RF performance, long-range, industryleading security features, low-current consumption, a rich set of MCU peripherals, and ample memory, all in a 6.5 x 6.5 mm package.

The ZGM230S is a complete solution supported by powerful and fully-upgradeable software, advanced development and debugging tools, and documentation that will simplify and minimize the development cycle, certification process, and deployment of your endproduct, helping to accelerate its time-to-market significantly.

The ZGM230S is targeted for a broad range of applications, including:

- Smart Home

- Security

- Lighting

- Building Automation

#### KEY FEATURES

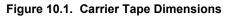

- Z-Wave connectivity

- · RF pin for external antenna

- +14 dBm TX power

- -109.8 dBm RX sensitivity @100 kbps

- 32-bit ARM Cortex-M33 core at 39 MHz

- · 512/64 kB of Flash/RAM memory

- Advanced security features

- Rich set of MCU peripherals

- Integrated DC-DC converter

- 34 GPIO pins

- -40 to 85 °C

- 6.5 mm x 6.5 mm

# 1. Features

- Supported Protocols

- Z-Wave

- Z-Wave Long Range

# Wireless System-on-Chip

- Sub-GHz radio

- TX power up to +14 dBm

- 32-bit ARM Cortex<sup>®</sup>-M33 with DSP instruction and floatingpoint unit for efficient signal processing

- 512 kB flash program memory

- 64 kB RAM data memory

- Embedded Trace Macrocell (ETM) for advanced debugging

# Receiver Performance

- -109.9 dBm sensitivity at 9.6 kbps FSK, 868.42 MHz

- -110 dBm sensitivity at 40 kbps FSK, 868.4 MHz

- -108.6 dBm sensitivity at 100 kbps GFSK, 869.85 MHz

- -109.3 dBm sensitivity at 9.6 kbps FSK, 908.42 MHz

- -109.7 dBm sensitivity at 40 kbps FSK, 908.4 MHz

- -108.1 dBm sensitivity at 100 kbps GFSK, 916 MHz

- -109.8 dBm sensitivity at 100 kbps O-QPSK, 912 MHz

# Current Consumption

- 4.1 mA RX current at 9.6 kbps FSK, 868.42 MHz

- 4.1 mA RX current at 100 kbps GFSK, 869.85 MHz

- 4.1 mA RX current at 9.6 kbps FSK, 908.4 MHz

- 4.1 mA RX current at 100 kbps GFSK, 916 MHz

- 4.6 mA RX current at 100 kbps O-QPSK, 912 MHz

- 10.7 mA TX current at 0 dBm, 916 MHz

- 20.8 mA TX current at +10 dBm, 916 MHz

- 30.0 mA TX current at +14 dBm, 916 MHz

- + 26  $\mu\text{A}/\text{MHz}$  in Active Mode (EM0) at 39.0 MHz

- 1.5 µA in Deep Sleep (EM2) at 64 kB RAM retention and RTC running from LFRCO

- 0.7 µA in Shutoff Mode (EM4)

# Operating Range

- 1.8 to 3.8 V

- -40 to +85°C

- Dimensions

- 6.5 mm x 6.5 mm

- Security

- Hardware Cryptographic Acceleration for AES128/192/256, ChaCha20-Poly1305, SHA-1, SHA-2/256/384/512, ECDSA +ECDH(P-192, P-256, P-384, P-521), Ed25519 and Curve25519, J-PAKE, PBKDF2

- True Random Number Generator (TRNG)

- ARM® TrustZone®

- Secure Boot (Root of Trust Secure Loader)

- Secure Debug Unlock

- DPA Countermeasures

- · Secure Key Management with PUF

- Anti-Tamper

- Secure Attestation

- MCU Peripherals

- 12-bit 1 Msps or 16-bit 76.9 ksps SAR Analog to Digital Converter (ADC)

- 2 × Analog Comparator (ACMP)

- 2 × Digital to Analog Converter (VDAC)

- Low-Energy Sensor Interface (LESENSE)

- 34 General Purpose I/O pins with output state retention and asynchronous interrupts

- 8 Channel DMA Controller

- 12 Channel Peripheral Reflex System (PRS)

- 4 × 16-bit Timer/Counter with 3 Compare/Capture/PWM channels

- 1 × 32-bit Timer/Counter with 3 Compare/Capture/PWM channels

- 32-bit Real Time Counter

- 24-bit Low Energy Timer for waveform generation

- 2 × Watchdog Timer

- 3× Enhanced Universal Synchronous/Asynchronous Receiver/Transmitter (EUSART)

- 1× Universal Synchronous/Asynchronous Receiver/Transmitter (UART/SPI/SmartCard (ISO 7816)/IrDA/I<sup>2</sup>S)

- \*  $2 \times I^2C$  interface with SMBus support

- Integrated Low-Energy LCD Controller supporting up to 80 segments

- Die temperature sensor

# 2. Ordering Information

| Ordering Code  | Protocol<br>Stack                                        | TX Power | Freq<br>Band | Anten-<br>na | Flash<br>(kB) | RAM<br>(kB) | Security   | GPIO | Temp<br>Range | Carrier |

|----------------|----------------------------------------------------------|----------|--------------|--------------|---------------|-------------|------------|------|---------------|---------|

| ZGM230SA27HGN3 | <ul><li> Z-Wave</li><li> Z-Wave<br/>Long Range</li></ul> | +14 dBm  | Sub-GHz      | RF pin       | 512           | 64          | Vault-Mid  | 34   | -40 to 85 °C  | Tray    |

| ZGM230SB27HGN3 | <ul><li> Z-Wave</li><li> Z-Wave<br/>Long Range</li></ul> | +14 dBm  | Sub-GHz      | RF pin       | 512           | 64          | Vault-High | 34   | -40 to 85 °C  | Tray    |

#### Table 2.1. ZGM230S Ordering Part Numbers

See Section 4.5 Sub-GHz RF Transceiver Characteristics of the Electrical Specifications for maximum TX power figures.

ZGM230S modules are not pre-programmed with a bootloader.

Throughout this document, the modules may be referred to by their product family name (ZGM230S) or by their full ordering code as seen in the table above.

The **ZWAVE-PK800A Z-Wave 800 Series Pro Kit** is available for ZGM230S evaluation and development, as well as **ZGM230-RB4205B** radio boards.

# **Table of Contents**

| 1. | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 2                                    | ?                     |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------|

| 2. | Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 3                                    | ,                     |

| 3. | System Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 6                                    | )                     |

|    | 3.1 Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 6                                    | ;                     |

|    | 3.2 EFR32ZG23 SoC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 6                                    | ;                     |

|    | 3.3 Antenna                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 6                                    | ;                     |

|    | 3.4 Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 6                                    | ;                     |

|    | 3.5 Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 7<br>. 7<br>. 8<br>. 8<br>. 8<br>. 8 | 7<br>7<br>8<br>8<br>8 |

|    | 3.6 Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 9                                    | )                     |

| 4. | Electrical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 10                                   | )                     |

|    | 4.1 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | .10                                    | )                     |

|    | 4.2 Absolute Maximum Ratings.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .10                                    | )                     |

|    | 4.3 General Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | .11                                    |                       |

|    | 4.4 Current Consumption       4.4.1 MCU Current Consumption at 3.3 V input       4.4.1 MCU Current Consumption at 3.3 V input       4.4.1 MCU Current Consumption at 3.3 V input       4.4.2 MCU Current Consumption at 1.8 V input       4.4.2 MCU Current Consumption at 3.3 V input       4.4.2 MCU Current Consumption at 3.3 V input       4.4.2 MCU Current Consumption at 3.3 V input       4.4.4 Z-Wave Radio Current Consumption at 1.8 V input       4.4.4 Z-Wave Radio Current Consumption at 1.8 V input       4.4.4 Z-Wave Radio Current Consumption at 1.8 V input       4.4.4 Z-Wave Radio Current Consumption at 1.8 V input       4.4.4 Z-Wave Radio Current Consumption at 1.8 V input       4.4.4 Z-Wave Radio Current Consumption at 1.8 V input       4.4.4 Z-Wave Radio Current Consumption at 1.8 V input       4.4.4 Z-Wave Radio Current Consumption at 1.8 V input       4.4.4 Z-Wave Radio Current Consumption at 1.8 V input       4.4.4 Z-Wave Radio Current Consumption at 1.8 V input       4.4.4 Z-Wave Radio Current Consumption at 1.8 V input       4.4.4 Z-Wave Radio Current Consumption at 1.8 V input       4.4.4 Z-Wave Radio Current Consumption at 1.8 V input       4.4.4 Z-Wave Radio Current Consumption at 1.8 V input       4.4.4 Z-Wave Radio Current Consumption at 1.8 V input       4.4.4 Z-Wave Radio Current Consumption At 1.8 V input       4.4.4 Z-Wave Radio Current Consumption At 1.8 V input       4.4.4 Z-Wave Radio Current Consumptinput       4.4.4 Z-Wave Radio Current | .12<br>.12<br>.13<br>.14               | 2 2 3                 |

|    | 4.5 Sub-GHz RF Transceiver Characteristics4.5.1 RF Transmitter Characteristics4.5.2 RF Receiver Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | .16                                    | 5                     |

|    | 4.6 High-Frequency Crystal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | .24                                    | ŀ                     |

|    | 4.7 GPIO Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                        |                       |

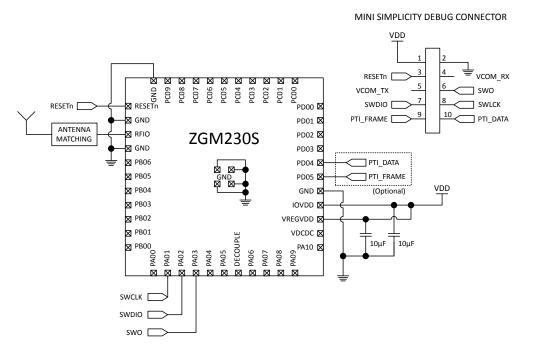

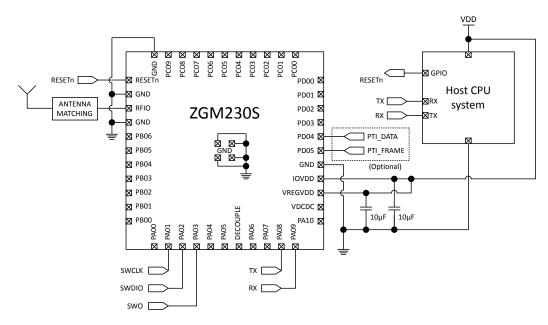

| 5. | Reference Diagrams.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 27                                     | ,                     |

|    | 5.1 Standalone Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                        |                       |

|    | 5.2 Network Co-Processor (NCP) Application with UART Host                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | .28                                    | ;                     |

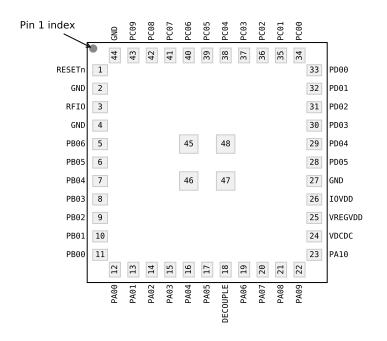

| 6. | Pin Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                        | )                     |

|    | 6.1 Module Pinout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                        |                       |

|    | 6.2 Alternate Pin Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                        |                       |

| 6.   | 3 Analog Peripheral Connectivity   |       | • |   |  |   | • |   |   |   | • |   |   |   |   |   | • |   |   |   |   | .32  |

|------|------------------------------------|-------|---|---|--|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|------|

| 6.   | 4 Digital Peripheral Connectivity. |       | • |   |  |   | • |   |   |   | • |   |   |   |   |   | • |   | • |   |   | .33  |

| 7. D | esign Guidelines                   |       | • | • |  | • | • | • | • |   | • | • | • | • | • | • |   |   | • | • | • | . 37 |

| 7.   | 1 Layout and Placement             |       |   |   |  |   | • |   |   |   |   |   |   |   |   |   |   |   |   |   |   | .37  |

| 7.   | 2 Proximity to Other Materials .   |       |   |   |  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | .39  |

| 7.   | 3 Reset                            |       |   |   |  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | .39  |

| 7.   | 4 Debug                            |       |   |   |  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | .40  |

| 7.   | 5 Packet Trace Interface (PTI) .   |       | • | • |  |   | • |   |   |   | • | • |   |   |   |   | • |   | • | • |   | .40  |

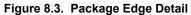

| 8. P | ackage Specifications              |       |   |   |  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | .41  |

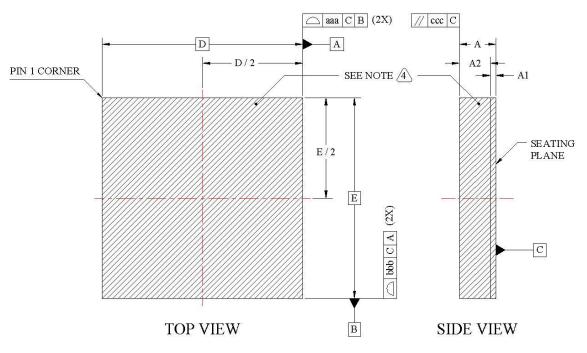

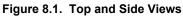

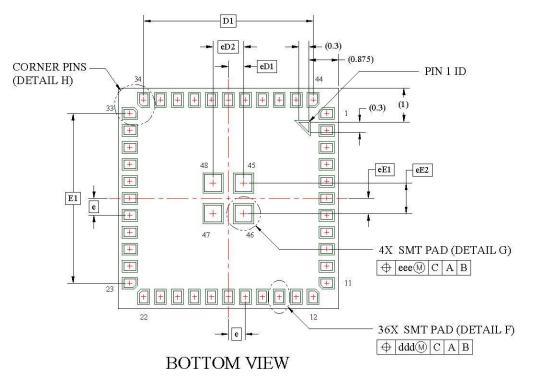

| 8.   | 1 Package Outline                  |       |   |   |  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | .41  |

| 8.   | 2 PCB Land Pattern                 |       |   |   |  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | .44  |

| 8.   | 3 Package Marking                  |       |   |   |  |   | • |   |   |   | • |   |   |   |   |   |   |   | • |   |   | .45  |

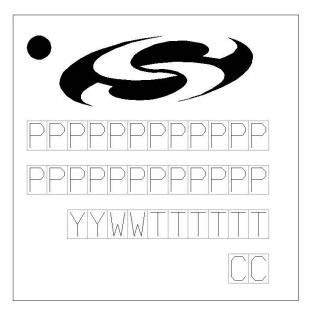

| 9. S | oldering Recommendations           |       | • |   |  |   | • |   | • |   |   |   |   |   |   | • | • | • |   |   | • | . 46 |

| 10.  | Tape and Reel                      |       |   |   |  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | .47  |

| 11.  | Certifications                     | <br>• |   |   |  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 48   |

| 12.  | Revision History                   | •     |   |   |  |   |   |   |   | • |   |   |   |   |   |   | • |   |   |   |   | 49   |

# 3. System Overview

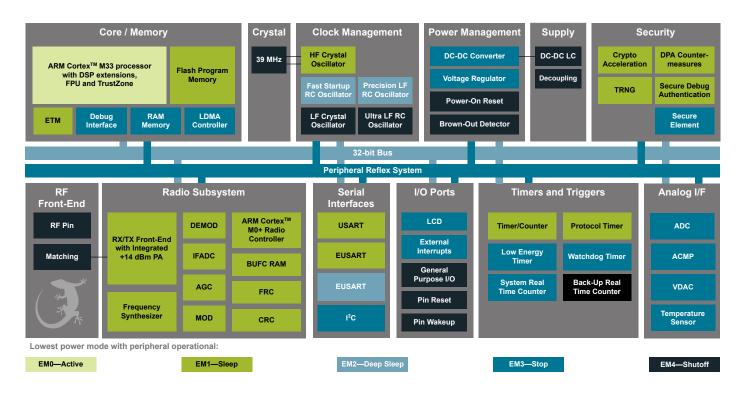

#### 3.1 Block Diagram

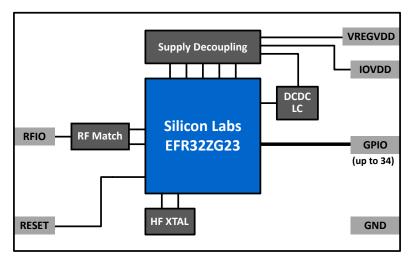

The ZGM230S module is a highly-integrated, high-performance system in a package with all the hardware components needed to enable Sub-GHz wireless connectivity and support robust networking capabilities via the Z-Wave protocol.

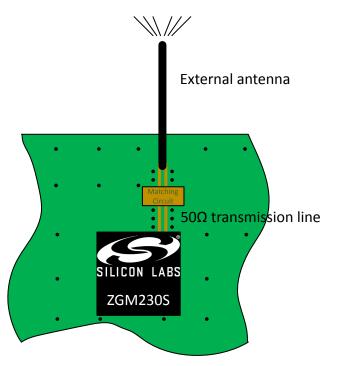

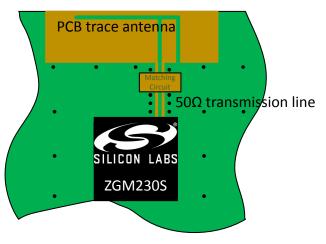

Built around the EFR32ZG23 Wireless Gecko SoC, the ZGM230S includes a 50  $\Omega$  RF pin to attach an external antenna, a matching network optimized for transmit power efficiency, supply decoupling and filtering components, an LC tank for DCDC conversion, and a 39 MHz crystal.

Figure 3.1. ZGM230S Block Diagram

#### 3.2 EFR32ZG23 SoC

The EFR32ZG23 SoC features a 32-bit ARM Cortex M33 core, a Sub-GHz high-performance radio, 512 kB of Flash memory, a dedicated core for security, a rich set of MCU peripherals, and various clock management and serial interfacing options. Consult the EFR32xG23 Reference Manual and the EFR32ZG23 Data Sheet for details.

#### 3.3 Antenna

The ZGM230S modules include a 50  $\Omega$ -matched RFIO pin to attach an external antenna to the module.

#### 3.4 Power Supply

The nominal supply level of the ZGM230S is 3.3 V, but due to its integrated DCDC converter and built-in LDOs, the device can operate over a supply range of 1.8—3.8 V.

Only a few external decoupling capacitors are required (see Reference Diagrams). Since all smaller caps are integrated in the module, there is no need for fast decoupling externally. L and C for the DCDC converter are integrated in the module as well.

#### 3.5 Security

ZGM230S modules support one of two levels in the Security Portfolio offered by Silicon Labs: Secure Vault Mid or Secure Vault High.

Secure Vault is a collection of technologies that deliver state-of-the-art security and upgradability features to protect and future-proof IoT devices against costly threats, attacks and tampering. A dedicated security CPU enables the Secure Vault functions and isolates cryptographic functions and data from the Cortex-M33 core. ZGM230S<u>B</u> part numbers support Secure Vault High and ZGM230S<u>A</u> part numbers support Secure Vault Mid.

| Feature                                                 | Secure Vault Mid | Secure Vault High |

|---------------------------------------------------------|------------------|-------------------|

| Secure Boot with Root of Trust and Secure Loader (RTSL) | Х                | Х                 |

| Cryptographic Accelerator                               | Х                | Х                 |

| True Random Number Generator (TRNG)                     | Х                | Х                 |

| Secure Debug with Lock/Unlock                           | Х                | Х                 |

| DPA Countermeasures                                     | Х                | Х                 |

| Secure Key Management with PUF                          |                  | Х                 |

| Anti-Tamper                                             |                  | Х                 |

| Secure Attestation                                      |                  | X                 |

#### Table 3.1. Security Features and Levels

#### 3.5.1 Secure Boot with Root of Trust and Secure Loader (RTSL)

The Secure Boot with RTSL authenticates a chain of trusted firmware that begins from an immutable memory (ROM).

It prevents malware injection, prevents rollback, ensures that only authentic firmware is executed, and protects Over The Air updates.

For more information about this feature, see AN1218: Series 2 Secure Boot with RTSL.

#### 3.5.2 Cryptographic Accelerator

The Cryptographic Accelerator is an autonomous hardware accelerator with Differential Power Analysis (DPA) countermeasures to protect keys.

It supports AES encryption and decryption with 128/192/256-bit keys, ChaCha20 encryption, and Elliptic Curve Cryptography (ECC) to support public key operations, and hashes.

Supported block cipher modes of operation for AES include:

- ECB (Electronic Code Book)

- CTR (Counter Mode)

- CBC (Cipher Block Chaining)

- CFB (Cipher Feedback)

- GCM (Galois Counter Mode)

- CCM (Counter with CBC-MAC)

- CBC-MAC (Cipher Block Chaining Message Authentication Code)

- GMAC (Galois Message Authentication Code)

The Cryptographic Accelerator accelerates Elliptical Curve Cryptography and supports the NIST (National Institute of Standards and Technology) recommended curves including P-192, P-256, P-384, and P-521 for ECDH (Elliptic Curve Diffie-Hellman) key derivation, and ECDSA (Elliptic Curve Digital Signature Algorithm) sign and verify operations. Also supported is the non-NIST Curve25519 for ECDH and Ed25519 for EdDSA (Edwards-curve Digital Signature Algorithm) sign and verify operations.

Secure Vault also supports ECJ-PAKE (Elliptic Curve variant of Password Authenticated Key Exchange by Juggling) and PBKDF2 (Password-Based Key Derivation Function 2).

Supported hashes include SHA-1, SHA-2/256/384/512 and Poly1305.

This implementation provides a fast and energy efficient solution to state of the art cryptographic needs.

#### 3.5.3 True Random Number Generator

The True Random Number Generator module is a non-deterministic random number generator that harvests entropy from a thermal energy source. It includes start-up health tests for the entropy source as required by NIST SP800-90B and AIS-31 as well as online health tests required for NIST SP800-90C.

The TRNG is suitable for periodically generating entropy to seed an approved pseudo random number generator.

#### 3.5.4 Secure Debug with Lock/Unlock

For obvious security reasons, it is critical for a product to have its debug interface locked before being released in the field.

In addition, Secure Vault High also provides a secure debug unlock function that allows authenticated access based on public key cryptography. This functionality is particularly useful for supporting failure analysis while maintaining confidentiality of IP and sensitive enduser data.

For more information about this feature, see AN1190: Series 2 Secure Debug.

#### 3.5.5 DPA Countermeasures

The AES and ECC accelerators have Differential Power Analysis (DPA) countermeasures support. This makes it very expensive from a time and effort standpoint to use DPA to recover secret keys.

#### 3.5.6 Secure Key Management with PUF

Key material in Secure Vault High products is protected by "key wrapping" with a standardized symmetric encryption mechanism. This method has the advantage of protecting a virtually unlimited number of keys, limited only by the storage that is accessible by the Cortex-M33, which includes off-chip storage as well. The symmetric key used for this wrapping and unwrapping must be highly secure because it can expose all other key materials in the system. The Secure Vault Key Management system uses a Physically Unclonable Function (PUF) to generate a persistent device-unique seed key on power up to dynamically generate this critical wrapping/unwrapping key which is only visible to the AES encryption engine and is not retained when the device loses power.

#### 3.5.7 Anti-Tamper

Secure Vault High devices provide internal tamper protection which monitors parameters such as voltage, temperature, and electromagnetic pulses as well as detecting tamper of the security sub-system itself. Additionally, 8 external configurable tamper pins support external tamper sources, such as enclosure tamper switches.

For each tamper event, the user is able to select the severity of the tamper response ranging from an interrupt, to a reset, to destroying the PUF reconstruction data which will make all protected key materials un-recoverable and effectively render the device inoperable. The tamper system also has an internal resettable event counter with programmable trigger threshold and refresh periods to mitigate false positive tamper events.

For more information about this feature, see AN1247: Anti-Tamper Protection Configuration and Use.

#### 3.5.8 Secure Attestation

Secure Vault High products support Secure Attestation, which begins with a secure identity that is created during the Silicon Labs manufacturing process. During device production, each device generates its own public/private keypair and securely stores the wrapped private key into immutable OTP memory and this key never leaves the device. The corresponding public key is extracted from the device and inserted into a binary DER-encoded X.509 device certificate, which is signed into a Silicon Labs CA chain and then programmed back into the chip into an immutable OTP memory.

The secure identity can be used to authenticate the chip at any time in the life of the product. The production certification chain can be requested remotely from the product. This certification chain can be used to verify that the device was authentically produced by Silicon Labs. The device unique public key is also bound to the device certificate in the certification chain. A challenge can be sent to the chip at any point in time to be signed by the device private key. The public key in the device certificate can then be used to verify the challenge response, proving that the device has access to the securely-stored private key, which prevents counterfeit products or impersonation attacks.

For more information about this feature, see AN1268: Authenticating Silicon Labs Devices Using Device Certificates.

# 3.6 Memory Map

The ZGM230S memory map is shown in the figures below.

|                      | 0x3fffffff<br>0x20010000 |   |                      | 0x0fe00400               |

|----------------------|--------------------------|---|----------------------|--------------------------|

| Peripherals (secure) | 0×87ffffff<br>0×40000000 |   | FLASH_DEVINFO        | 0x0fe08000               |

| Peripherals          | 0×50000000               |   |                      | 0x0fe08400               |

|                      | 0x88000000<br>0xa7ffffff |   | FLASH CHIPCONFIG     | 0x0fe08a00               |

|                      | 0xa0000000<br>0x4fffffff |   |                      |                          |

| SEQRAM_S             | 0xa0003fff               |   |                      | _                        |

| FRCRAM_S             | 0xa0004000               |   | ITM                  | 0xe0001000<br>0xe0000000 |

|                      | 0xa0005000<br>0xa0004fff |   | FPB<br>DWT           | 0xe0002000               |

|                      | 0xafffffff               |   |                      | 0xe000e000               |

|                      | 0×9fffffff<br>0×a8000000 |   | System Control Space | 0xe000f000               |

| SEQRAM               | 0×b0000000               |   | TPIU                 | 0xe0041000               |

|                      | 0×b0004000<br>0×b0003fff |   | ETM                  | 0xe0042000               |

| FRCRAM               | 0xb0004fff               |   | m33 ROM Table        | 0xe0100000<br>0xe00ff000 |

|                      | 0×b0005000               | \ |                      | _                        |

|                      | 0xe0000000<br>0xdfffffff |   |                      |                          |

| m33 Peripherals      | 0xe00fffff ``            |   |                      |                          |

|                      | 0×e0100000               |   |                      |                          |

# Figure 3.2. ZGM230S Memory Map — Core Peripherals and Code Space

# 4. Electrical Specifications

#### 4.1 Electrical Characteristics

All electrical parameters in all tables are specified under the following conditions, unless stated otherwise:

- Typical values are based on T<sub>A</sub>=25 °C and all supplies at 3.3 V, by production test and/or technology characterization.

- Radio performance numbers are measured in conducted mode, based on Silicon Laboratories reference designs using output power-specific external RF impedance-matching networks for interfacing to a 50 Ω antenna.

- Minimum and maximum values represent the worst conditions across supply voltage, process variation, and operating temperature, unless stated otherwise.

#### 4.2 Absolute Maximum Ratings

Stresses beyond those listed below may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at those or any other conditions beyond those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. For more information on the available quality and reliability data, see the Quality and Reliability Monitor Report at http://www.silabs.com/support/quality/pages/default.aspx.

| Parameter                               | Symbol                | Test Condition | Min  | Тур | Мах                      | Unit   |

|-----------------------------------------|-----------------------|----------------|------|-----|--------------------------|--------|

| Storage temperature range               | T <sub>STG</sub>      |                | -50  | _   | +150                     | °C     |

| Voltage on any supply pin               | V <sub>DDMAX</sub>    |                | -0.3 | —   | 3.8                      | V      |

| Voltage ramp rate on any supply pin     | VDDRAMPMAX            |                | _    | _   | 1.0                      | V / µs |

| DC voltage on any GPIO pin <sup>1</sup> | V <sub>DIGPIN</sub>   |                | -0.3 | _   | V <sub>IOVDD</sub> + 0.3 | V      |

| DC voltage on RESETn pin <sup>2</sup>   | V <sub>RESETn</sub>   |                | -0.3 | —   | 3.8                      | V      |

| Total current into VDD power lines      | IVDDMAX               | Source         | _    | _   | 200                      | mA     |

| Total current into VSS ground lines     | IVSSMAX               | Sink           | _    | _   | 200                      | mA     |

| Current per I/O pin                     | I <sub>IOMAX</sub>    | Sink           | _    | _   | 50                       | mA     |

|                                         |                       | Source         | _    | _   | 50                       | mA     |

| Current for all I/O pins                | I <sub>IOALLMAX</sub> | Sink           | —    | —   | 200                      | mA     |

|                                         |                       | Source         | —    | —   | 200                      | mA     |

#### Table 4.1. Absolute Maximum Ratings

#### Note:

1. When operating as an LCD driver, the output voltage on a GPIO may safely exceed this specification. The pin output voltage may be up to 3.8 V in this case.

2. The RESETn pin has a pull-up device to the internally-regulated DVDD supply, which is generated by the DC-DC converter. DVDD is equal to 1.8 V when DC-DC is active and bypassed to VREGVDD when DC-DC is inactive. For minimum leakage, it is recommended to not drive RESETn high, and instead rely on the internall pull-up.

# 4.3 General Operating Conditions

| Parameter                                        | Symbol                   | Test Condition      | Min | Тур  | Мах | Unit |

|--------------------------------------------------|--------------------------|---------------------|-----|------|-----|------|

| Operating ambient tempera-<br>ture range         | T <sub>A</sub>           |                     | -40 | _    | +85 | °C   |

| IOVDDx operating supply voltage (All IOVDD pins) | V <sub>IOVDDx</sub>      |                     | 1.8 | 3.3  | 3.8 | V    |

| VREGVDD operating supply voltage                 | V <sub>VREGVDD</sub>     |                     | 1.8 | 3.3  | 3.8 | V    |

| HCLK and SYSCLK frequen-<br>cy                   | f <sub>HCLK</sub>        | VSCALE1, MODE = WS0 | _   | _    | 39  | MHz  |

| PCLK frequency                                   | f <sub>PCLK</sub>        | VSCALE1             | —   | _    | 39  | MHz  |

| EM01 Group A clock fre-<br>quency                | f <sub>EM01GRPACLK</sub> | VSCALE1             | _   | _    | 39  | MHz  |

| HCLK Radio frequency                             | fhclkradio               | VSCALE1             | _   | 39.0 | -   | MHz  |

# Table 4.2. General Operating Conditions

#### 4.4 Current Consumption

# 4.4.1 MCU Current Consumption at 3.3 V input

Unless otherwise indicated, typical conditions are: VREGVDD = IOVDD = 3.3V. Voltage scaling level = VSCALE1. T<sub>A</sub> = 25 °C. Minimum and maximum values in this table represent the worst conditions across process variation at T<sub>A</sub> = 25 °C.

#### Table 4.3. MCU Current Consumption at 3.3 V input

| Parameter                                                                                  | Symbol               | Test Condition                                                 | Min | Тур  | Max | Unit   |

|--------------------------------------------------------------------------------------------|----------------------|----------------------------------------------------------------|-----|------|-----|--------|

| Current consumption in EM0 mode with all peripherals dis-                                  | I <sub>ACTIVE</sub>  | 39 MHz crystal, CPU running Prime from flash                   | _   | 27   | _   | µA/MHz |

| abled                                                                                      |                      | 39 MHz crystal, CPU running while loop from flash              | —   | 26   | _   | µA/MHz |

|                                                                                            |                      | 39 MHz crystal, CPU running CoreMark loop from flash           | _   | 36   | _   | µA/MHz |

| Current consumption in EM1 mode with all peripherals disabled                              | I <sub>EM1</sub>     | 39 MHz crystal                                                 | _   | 18   | _   | µA/MHz |

| Current consumption in EM2 mode, VSCALE0                                                   | I <sub>EM2_VS</sub>  | 64 kB RAM and full Radio RAM retention, RTC running from LFXO  | _   | 1.5  | _   | μΑ     |

|                                                                                            |                      | 64 kB RAM and full Radio RAM retention, RTC running from LFRCO | _   | 1.5  | _   | μΑ     |

| Current consumption in EM4 mode                                                            | I <sub>EM4</sub>     | BURTC with LFRCO                                               | _   | 0.7  | _   | μΑ     |

| Current consumption for re-<br>tained RAM bank in EM2 or<br>EM3                            | I <sub>RAM</sub>     | Per 16 kB RAM bank                                             | _   | 0.1  | _   | μA     |

| Additional current in EM2 or<br>EM3 when any peripheral in<br>PD0B is enabled <sup>1</sup> | IPDOB_VS             |                                                                | _   | 0.85 | _   | μA     |

| Additional current in EM2 or<br>EM3 when any peripheral in<br>PD0C is enabled <sup>1</sup> | IPDOC_VS             |                                                                | -   | 0.13 | _   | μΑ     |

| Additional current in EM2 or<br>EM3 when any peripheral in<br>PD0D is enabled <sup>1</sup> | I <sub>PD0D_VS</sub> |                                                                | -   | 0.98 | _   | μΑ     |

| Additional current in EM2 or<br>EM3 when any peripheral in<br>PD0E is enabled <sup>1</sup> | IPDOE_VS             |                                                                | -   | 0.06 | _   | μΑ     |

Note:

1. Extra current consumed by power domain. Does not include current associated with the enabled peripherals. See the "Power Domains" section in the SoC datasheet for a list of the peripherals in each power domain.

#### 4.4.2 MCU Current Consumption at 1.8 V input

Unless otherwise indicated, typical conditions are: VREGVDD = IOVDD = 1.8 V. Voltage scaling level = VSCALE1.  $T_A = 25$  °C. Minimum and maximum values in this table represent the worst conditions across process variation at  $T_A = 25$  °C.

| Table 4.4. | MCU Current | Consumption | at 1.8 V input |

|------------|-------------|-------------|----------------|

|------------|-------------|-------------|----------------|

| Parameter                                                                                  | Symbol               | Test Condition                                                 | Min | Тур  | Мах | Unit   |

|--------------------------------------------------------------------------------------------|----------------------|----------------------------------------------------------------|-----|------|-----|--------|

| Current consumption in EM0 mode with all peripherals dis-                                  | I <sub>ACTIVE</sub>  | 39 MHz crystal, CPU running<br>Prime from flash                | _   | 44   | _   | µA/MHz |

| abled                                                                                      |                      | 39 MHz crystal, CPU running while loop from flash              | _   | 42   |     | µA/MHz |

|                                                                                            |                      | 39 MHz crystal, CPU running<br>CoreMark loop from flash        | _   | 58   |     | µA/MHz |

| Current consumption in EM1 mode with all peripherals disabled                              | I <sub>EM1</sub>     | 39 MHz crystal                                                 | _   | 29   | _   | µA/MHz |

| Current consumption in EM2<br>mode, VSCALE0                                                | I <sub>EM2_VS</sub>  | 64 kB RAM and full Radio RAM retention, RTC running from LFXO  | _   | 2.2  | _   | μA     |

|                                                                                            |                      | 64 kB RAM and full Radio RAM retention, RTC running from LFRCO | -   | 2.2  | _   | μA     |

| Current consumption for re-<br>tained RAM bank in EM2 or<br>EM3                            | I <sub>RAM</sub>     | Per 16 kB RAM bank                                             | _   | 0.15 | _   | μA     |

| Current consumption in EM4 mode                                                            | I <sub>EM4</sub>     | BURTC with LFRCO                                               | _   | 0.52 |     | μΑ     |

| Current consumption during reset                                                           | I <sub>RST</sub>     | Hard pin reset held                                            | _   | 384  | _   | μΑ     |

| Additional current in EM2 or<br>EM3 when any peripheral in<br>PD0B is enabled <sup>1</sup> | IPDOB_VS             |                                                                | _   | 1.38 | _   | μA     |

| Additional current in EM2 or<br>EM3 when any peripheral in<br>PD0C is enabled <sup>1</sup> | IPDOC_VS             |                                                                | -   | 0.21 | _   | μA     |

| Additional current in EM2 or<br>EM3 when any peripheral in<br>PD0D is enabled <sup>1</sup> | I <sub>PD0D_VS</sub> |                                                                | -   | 1.59 | _   | μA     |

| Additional current in EM2 or<br>EM3 when any peripheral in<br>PD0E is enabled <sup>1</sup> | I <sub>PD0E_VS</sub> |                                                                | -   | 0.10 | _   | μA     |

Note:

1. Extra current consumed by power domain. Does not include current associated with the enabled peripherals. See the "Power Domains" section in the SoC datasheet for a list of the peripherals in each power domain.

#### 4.4.3 Z-Wave Radio Current Consumption at 3.3 V

RF current consumption measured with MCU in EM1, HCLK = 39.0 MHz, and all MCU peripherals disabled. Unless otherwise indicated, typical conditions are: VREGVDD = IOVDD = 3.3 V.  $T_A$  = 25 °C. Minimum and maximum values in this table represent the worst conditions across process variation at  $T_A$  = 25 °C.

| Parameter                                                       | Symbol                 | Test Condition                               | Min | Тур  | Мах | Unit |

|-----------------------------------------------------------------|------------------------|----------------------------------------------|-----|------|-----|------|

| Current consumption in re-                                      | I <sub>RX_ACTIVE</sub> | f = 868.4 MHz, 2-FSK, 40 kbps                | _   | 4.1  | _   | mA   |

| ceive mode, active packet reception, VSCALE1, EM1P <sup>1</sup> |                        | f = 868.42 MHz, 2-FSK, 9.6 kbps              | _   | 4.1  | _   | mA   |

|                                                                 |                        | f = 869.85 MHz, 2-GFSK, 100<br>kbps          | _   | 4.1  | _   | mA   |

|                                                                 |                        | f = 908.42 MHz, 2-FSK, 9.6 kbps              | _   | 4.1  | _   | mA   |

|                                                                 |                        | f = 908.4 MHz, 2-FSK, 40 kbps                | _   | 4.1  | _   | mA   |

|                                                                 |                        | f = 916 MHz, 2-GFSK, 100 kbps                | _   | 4.1  | _   | mA   |

|                                                                 |                        | f = 912 MHz, O-QPSK 100 kbps                 | _   | 4.6  | _   | mA   |

| Current consumption in re-                                      | I <sub>RX_LISTEN</sub> | f = 868.4 MHz, 2-FSK, 40 kbps                | _   | 4.2  | _   | mA   |

| ceive mode, listening for<br>packet, VSCALE1, EM1P <sup>1</sup> |                        | f = 868.42 MHz, 2-FSK, 9.6 kbps              | _   | 4.2  |     | mA   |

|                                                                 |                        | f = 869.85 MHz, 2-GFSK, 100<br>kbps          | _   | 4.2  |     | mA   |

|                                                                 |                        | f = 908.42 MHz, 2-FSK, 9.6 kbps              | _   | 4.2  |     | mA   |

|                                                                 |                        | f = 908.4 MHz, 2-FSK, 40 kbps                | _   | 4.2  | _   | mA   |

|                                                                 |                        | f = 916 MHz, 2-GFSK, 100 kbps                | _   | 4.2  |     | mA   |

|                                                                 |                        | f = 912 MHz, O-QPSK 100 kbps                 | _   | 4.5  | _   | mA   |

| Current consumption in transmit mode                            | I <sub>TX</sub>        | f = 868.42 MHz, CW, 0 dBm out-<br>put power  | _   | 10.5 | _   | mA   |

|                                                                 |                        | f = 868.42 MHz, CW, 4 dBm out-<br>put power  | _   | 13.3 | _   | mA   |

|                                                                 |                        | f = 868.42 MHz, CW, 10 dBm out-<br>put power | _   | 20.5 | _   | mA   |

|                                                                 |                        | f = 868.42 MHz, CW, 14 dBm out-<br>put power | _   | 30.1 | _   | mA   |

|                                                                 |                        | f = 916 MHz, CW, 0 dBm output<br>power       | _   | 10.7 | _   | mA   |