# Ultra Series<sup>™</sup> Crystal Oscillator Si547 Data Sheet

# Ultra Low Jitter Quad Any-Frequency XO (80 fs), 0.2 to 1500 MHz

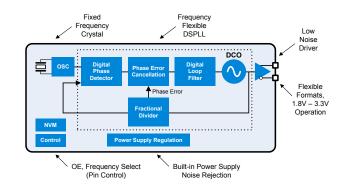

The Si547 Ultra Series<sup>™</sup> oscillator utilizes Silicon Laboratories' advanced 4<sup>th</sup> generation DSPLL® technology to provide an ultra-low jitter, low phase noise clock at four selectable frequencies. The device is factory-programmed to provide any four selectable frequencies from 0.2 to 1500 MHz with <1 ppb resolution and maintains exceptionally low jitter for both integer and fractional frequencies across its operating range. The Si547 offers excellent reliability and frequency stability as well as guaranteed aging performance. On-chip power supply filtering provides industry-leading power supply noise rejection, simplifying the task of generating low litter clocks in noisy systems that use switched-mode power supplies. Offered in industry-standard footprints, the Si547 has a dramatically simplified supply chain that enables Silicon Labs to ship custom frequency samples 1-2 weeks after receipt of order. Unlike a traditional XO, where a different crystal is required for each output frequency, the Si547 uses one simple crystal and a DSPLL IC-based approach to provide the desired output frequencies. This process also guarantees 100% electrical testing of every device. The Si547 is factory-configurable for a wide variety of user specifications, including frequency, output format, and OE pin location/polarity. Specific configurations are factory-programmed at time of shipment, eliminating the long lead times associated with custom oscillators.

# Si547

5 x 7 mm and 3.2 x 5 mm 2.5

#### Pin Assignments

| Pin # | Descriptions                                                       |

|-------|--------------------------------------------------------------------|

| 1, 2  | Selectable via ordering option OE = Output enable; NC = No Connect |

| 3     | GND = Ground                                                       |

| 4     | CLK+ = Clock output                                                |

| 5     | CLK- = Complementary clock output. Not used for CMOS.              |

| 6     | VDD = Power supply                                                 |

| 7     | FS1 = Frequency Select 1                                           |

| 8     | FS0 = Frequency Select 0                                           |

#### **KEY FEATURES**

- Available with any four selectable frequencies from 200 kHz to 1500 MHz

- Ultra low jitter: 80 fs Typ RMS (12 kHz – 20 MHz)

- Excellent PSNR and supply noise immunity: –80 dBc Typ

- 7 ppm stability option (-40 to 85C)

- 3.3 V, 2.5 V and 1.8 V V<sub>DD</sub> supply operation from the same part number

- LVPECL, LVDS, CML, HCSL, CMOS, and Dual CMOS output options

- 2.5x3.2, 3.2x5, 5x7 mm package options

- · Samples available with 1-2 week lead times

#### APPLICATIONS

- 100G/200G/400G OTN, coherent optics

- 10G/25G/40G/100G Ethernet

- 3G-SDI/12G-SDI/24G-SDI broadcast video

- Servers, switches, storage, NICs, search acceleration

- Test and measurement

- · Clock and data recovery

- FPGA/ASIC clocking

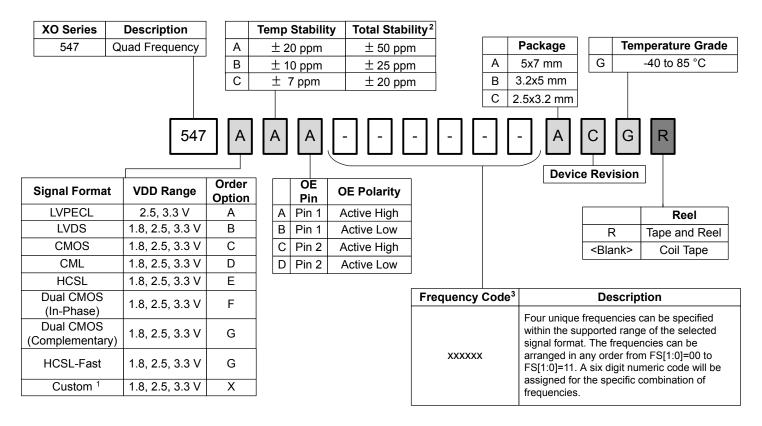

#### 1. Ordering Guide

The Si547 XO supports a variety of options including frequency, output format, and OE pin location/polarity, as shown in the chart below. Specific device configurations are programmed into the part at time of shipment, and samples are available in 1-2 weeks. Silicon Laboratories provides an online part number configuration utility to simplify this process. Refer to www.silabs.com/oscillators to access this tool and for further ordering instructions.

#### Notes:

- 1. Contact Silicon Labs for non-standard configurations.

- 2. Total stability includes temp stability, initial accuracy, load pulling, VDD variation, and 20 year aging at 70 °C.

- 3. Create custom part numbers at www.silabs.com/oscillators.

#### 1.1 Technical Support

| Frequently Asked Questions (FAQ)      | www.silabs.com/Si547-FAQ                     |  |  |

|---------------------------------------|----------------------------------------------|--|--|

| Oscillator Phase Noise Lookup Utility | www.silabs.com/oscillator-phase-noise-lookup |  |  |

| Quality and Reliability               | www.silabs.com/quality                       |  |  |

| Development Kits                      | www.silabs.com/oscillator-tools              |  |  |

# 2. Electrical Specifications

**Table 2.1. Electrical Specifications**

$V_{DD}$  = 1.8 V, 2.5 or 3.3 V ± 5%,  $T_A$  = –40 to 85 °C

| Parameter                                | Symbol                         | Test Condition/Comment                                                                 | Min                   | Тур | Max                   | Unit |

|------------------------------------------|--------------------------------|----------------------------------------------------------------------------------------|-----------------------|-----|-----------------------|------|

| Temperature Range                        | T <sub>A</sub>                 |                                                                                        | -40                   | _   | 85                    | °C   |

| Frequency Range                          | F <sub>CLK</sub>               | LVPECL, LVDS, CML                                                                      | 0.2                   | _   | 1500                  | MHz  |

|                                          |                                | HCSL                                                                                   | 0.2                   | _   | 400                   | MHz  |

|                                          |                                | CMOS, Dual CMOS                                                                        | 0.2                   | _   | 250                   | MHz  |

| Supply Voltage                           | V <sub>DD</sub>                | 3.3 V                                                                                  | 3.135                 | 3.3 | 3.465                 | V    |

|                                          |                                | 2.5 V                                                                                  | 2.375                 | 2.5 | 2.625                 | V    |

|                                          |                                | 1.8 V                                                                                  | 1.71                  | 1.8 | 1.89                  | V    |

| Supply Current                           | I <sub>DD</sub>                | LVPECL (output enabled)                                                                | _                     | 107 | 153                   | mA   |

|                                          |                                | LVDS/CML (output enabled)                                                              | _                     | 83  | 121                   | mA   |

|                                          |                                | HCSL (output enabled)                                                                  | _                     | 86  | 126                   | mA   |

|                                          |                                | HCSL-Fast (output enabled)                                                             | _                     | 94  | 138                   | mA   |

|                                          |                                | CMOS (output enabled)                                                                  | _                     | 87  | 127                   | mA   |

|                                          |                                | Dual CMOS (output enabled)                                                             | _                     | 92  | 141                   | mA   |

|                                          |                                | Tristate Hi-Z (output disabled)                                                        | _                     | 73  | 112                   | mA   |

| Temperature Stability                    |                                | Frequency stability Grade A                                                            | -20                   | _   | 20                    | ppm  |

|                                          |                                | Frequency stability Grade B                                                            | -10                   | _   | 10                    | ppm  |

|                                          |                                | Frequency stability Grade C                                                            | -7                    | _   | 7                     | ppm  |

| Total Stability <sup>1</sup>             | F <sub>STAB</sub>              | Frequency stability Grade A                                                            | -50                   | _   | 50                    | ppm  |

|                                          |                                | Frequency stability Grade B                                                            | -25                   | _   | 25                    | ppm  |

|                                          |                                | Frequency stability Grade C                                                            | -20                   | _   | 20                    | ppm  |

| Rise/Fall Time                           | T <sub>R</sub> /T <sub>F</sub> | LVPECL/LVDS/CML                                                                        | _                     | _   | 350                   | ps   |

| (20% to 80% V <sub>PP</sub> )            |                                | CMOS / Dual CMOS<br>(C <sub>L</sub> = 5 pF)                                            | _                     | 0.5 | 1.5                   | ns   |

|                                          |                                | HCSL, F <sub>CLK</sub> >50 MHz                                                         | _                     | _   | 550                   | ps   |

|                                          |                                | HCSL-Fast, F <sub>CLK</sub> >50 MHz                                                    | _                     | _   | 275                   | ps   |

| Duty Cycle                               | D <sub>C</sub>                 | All formats                                                                            | 45                    | _   | 55                    | %    |

| Output Enable (OE)                       | V <sub>IH</sub>                |                                                                                        | 0.7 × V <sub>DD</sub> | _   | _                     | V    |

| Frequency Select (FS0, FS1) <sup>2</sup> | V <sub>IL</sub>                |                                                                                        | _                     | _   | 0.3 × V <sub>DD</sub> | V    |

|                                          | T <sub>D</sub>                 | Output Disable Time, F <sub>CLK</sub> > 10 MHz                                         | _                     | _   | 3                     | μs   |

|                                          | T <sub>E</sub>                 | Output Enable Time, F <sub>CLK</sub> > 10 MHz                                          | _                     | _   | 20                    | μs   |

|                                          | T <sub>FS</sub>                | Settling Time after FS Change                                                          | _                     | _   | 10                    | ms   |

| Powerup Time                             | tosc                           | Time from 0.9 × V <sub>DD</sub> until output frequency (F <sub>CLK</sub> ) within spec | _                     | _   | 10                    | ms   |

| Parameter                            | Symbol          | Test Condition/Comment                               | Min                    | Тур  | Max                    | Unit            |

|--------------------------------------|-----------------|------------------------------------------------------|------------------------|------|------------------------|-----------------|

| Powerup V <sub>DD</sub> Ramp Rate    | $V_{RAMP}$      | Fastest V <sub>DD</sub> ramp rate allowed on startup | _                      | _    | 100                    | V/ms            |

| LVPECL Output Option <sup>3</sup>    | V <sub>OC</sub> | Mid-level                                            | V <sub>DD</sub> – 1.42 | _    | V <sub>DD</sub> – 1.25 | V               |

|                                      | Vo              | Swing (diff)                                         | 1.1                    | _    | 1.9                    | $V_{PP}$        |

| LVDS Output Option <sup>4</sup>      | V <sub>OC</sub> | Mid-level (2.5 V, 3.3 V VDD)                         | 1.125                  | 1.20 | 1.275                  | V               |

|                                      |                 | Mid-level (1.8 V VDD)                                | 0.8                    | 0.9  | 1.0                    | V               |

|                                      | Vo              | Swing (F <sub>CLK</sub> ≤ 1.4 GHz)                   | 0.6                    | 0.7  | 0.9                    | $V_{PP}$        |

|                                      |                 | Swing (F <sub>CLK</sub> > 1.4 GHz)                   | 0.5                    | 0.7  | 0.9                    | $V_{PP}$        |

| HCSL Output Option <sup>5</sup>      | V <sub>OH</sub> | Output voltage high                                  | 660                    | 750  | 850                    | mV              |

| HCSL-Fast Output Option <sup>5</sup> | V <sub>OL</sub> | Output voltage low                                   | -150                   | 0    | 150                    | mV              |

|                                      | V <sub>C</sub>  | Crossing voltage                                     | 250                    | 350  | 550                    | mV              |

| CML Output Option (AC-Coupled)       | Vo              | Swing (diff)                                         | 0.6                    | 0.8  | 1.0                    | V <sub>PP</sub> |

| CMOS Output Option                   | V <sub>OH</sub> | I <sub>OH</sub> = 8/6/4 mA for 3.3/2.5/1.8 V VDD     | 0.85 × V <sub>DD</sub> | _    | _                      | V               |

|                                      | V <sub>OL</sub> | I <sub>OL</sub> = 8/6/4 mA for 3.3/2.5/1.8 V VDD     | _                      | _    | 0.15 × V <sub>DD</sub> | V               |

- 1. Total Stability includes temperature stability, initial accuracy, load pulling, VDD variation, and aging for 20 yrs at 70 °C.

- 2. OE includes a 50 k $\Omega$  pull-up to VDD for OE active high. Includes a 50 k $\Omega$  pull-down to GND for OE active low. FS0 and FS1 pins each include a 50 k $\Omega$  pull-up to VDD. NC (No Connect) pins include a 50 k $\Omega$  pull-down to GND.

- 3.50  $\Omega$  to V<sub>DD</sub> 2.0 V. Additional DC current from the output driver will flow through the 50 $\Omega$  resistors, resulting in a shift in common mode voltage. The measurements in this table have accounted for this.

- 4.  $R_{term}$  = 100 Ω (differential).

- 5.50  $\Omega$  to GND.

## Table 2.2. Clock Output Phase Jitter and PSNR

$V_{DD}$  = 1.8 V, 2.5 or 3.3 V ± 5%,  $T_A$  = –40 to 85 °C

| Parameter                                                                  | Symbol | Test Condition/Comment               | Min | Тур | Max | Unit |

|----------------------------------------------------------------------------|--------|--------------------------------------|-----|-----|-----|------|

| Phase Jitter (RMS, 12kHz - 20MHz) <sup>1</sup>                             | фл     | F <sub>CLK</sub> ≥ 200 MHz           | _   | 80  | 110 | fs   |

| 3.2 x 5 mm, All Differential Formats                                       |        | 100 MHz ≤ F <sub>CLK</sub> < 200 MHz | _   | 100 | 150 | fs   |

|                                                                            |        | LVPECL @ 156.25 MHz                  | _   | 90  | 125 | fs   |

| Phase Jitter (RMS, 12kHz - 20MHz) <sup>1</sup>                             | ФЈ     | F <sub>CLK</sub> ≥ 200 MHz           | _   | 80  | 130 | fs   |

| 5 x 7 mm, All Differential Formats                                         |        | 100 MHz ≤ F <sub>CLK</sub> < 200 MHz | _   | 100 | 150 | fs   |

|                                                                            |        | LVPECL @ 156.25 MHz                  | _   | 90  | 125 | fs   |

| Phase Jitter (RMS, 12kHz - 20MHz) <sup>1</sup>                             | ФЈ     | F <sub>CLK</sub> ≥ 200 MHz           | _   | 90  | 130 | fs   |

| 2.5 x 3.2 mm, All Differential Formats                                     |        | LVDS @ 625 MHz                       | _   | 90  | 130 | fs   |

|                                                                            |        | 100 MHz ≤ F <sub>CLK</sub> < 200 MHz | _   | 100 | 150 | fs   |

| Phase Jitter (RMS, 12kHz - 20MHz) <sup>1</sup><br>CMOS / Dual CMOS Formats | фЈ     | 10 MHz ≤ F <sub>CLK</sub> ≤ 250 MHz  | _   | 200 | _   | fs   |

| Spurs Induced by External Power Supply                                     | PSNR   | 100 kHz sine wave                    | _   | -83 | _   |      |

| Noise, 50 mVpp Ripple. LVDS 156.25 MHz<br>Output                           |        | 200 kHz sine wave                    | _   | -83 | _   | dD.a |

|                                                                            |        | 500 kHz sine wave                    | _   | -82 | _   | dBc  |

|                                                                            |        | 1 MHz sine wave                      | _   | -85 | _   |      |

#### Note:

1. Guaranteed by characterization. Jitter inclusive of any spurs.

Table 2.3. 3 x 2.5 mm Clock Output Phase Noise (Typical, 50 ppm Total Stability Option)

| Offset Frequency (f) | 156.25 MHz LVDS      | 200 MHz LVDS      | 644.53125 MHz LVDS      | Unit   |

|----------------------|----------------------|-------------------|-------------------------|--------|

| 100 Hz               | -106                 | -102              | -92                     |        |

| 1 kHz                | <b>–133</b>          | <b>–129</b>       | <b>–119</b>             |        |

| 10 kHz               | -140                 | -138              | -127                    |        |

| 100 kHz              | <b>–145</b>          | -142              | -132                    | dBc/Hz |

| 1 MHz                | <b>–</b> 152         | <b>–150</b>       | -139                    |        |

| 10 MHz               | <b>–160</b>          | -160              | -154                    |        |

| 20 MHz               | <b>–</b> 161         | -161              | <b>–155</b>             |        |

| Offset Frequency (f) | 156.25 MHz<br>LVPECL | 200 MHz<br>LVPECL | 644.53125 MHz<br>LVPECL | Unit   |

| 100 Hz               | -103                 | -104              | <b>–</b> 91             |        |

| 1 kHz                | -130                 | <b>–128</b>       | <b>–118</b>             |        |

| 10 kHz               | -140                 | -138              | <b>–127</b>             |        |

| 100 kHz              | <b>–145</b>          | -142              | -132                    | dBc/Hz |

| 1 MHz                | <b>–</b> 152         | <b>–150</b>       | -140                    |        |

| 10 MHz               | -162                 | -162              | <b>–155</b>             |        |

| 20 MHz               | -163                 | -163              | -156                    |        |

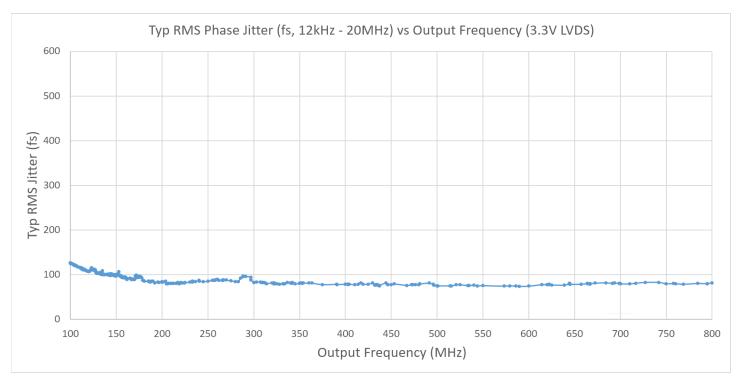

Figure 2.1. Phase Jitter vs. Output Frequency

Phase jitter measured with Agilent E5052 using a differential-to-single ended converter (balun or buffer). Measurements collected for >700 commonly used frequencies. Phase noise plots for specific frequencies are available using our free, online Oscillator Phase Noise Lookup Tool at <a href="https://www.silabs.com/oscillators">www.silabs.com/oscillators</a>.

Table 2.4. Environmental Compliance and Package Information

| Parameter                                                 | Test Condition                                          |  |  |  |

|-----------------------------------------------------------|---------------------------------------------------------|--|--|--|

| Mechanical Shock                                          | MIL-STD-883, Method 2002                                |  |  |  |

| Mechanical Vibration                                      | MIL-STD-883, Method 2007                                |  |  |  |

| Solderability                                             | MIL-STD-883, Method 2003                                |  |  |  |

| Gross and Fine Leak                                       | MIL-STD-883, Method 1014                                |  |  |  |

| Resistance to Solder Heat                                 | MIL-STD-883, Method 2036                                |  |  |  |

| Moisture Sensitivity Level (MSL): 3.2 x 5, 5 x 7 packages | 1                                                       |  |  |  |

| Moisture Sensitivity Level (MSL): 2.5 x 3.2 package       | 2                                                       |  |  |  |

| Contact Pads: 3.2x5, 5x7 packages                         | Au/Ni (0.3 - 1.0 μm / 1.27 - 8.89 μm)                   |  |  |  |

| Contact Pads: 2.5x3.2 packages                            | Au/Pd/Ni (0.03 - 0.12 μm / 0.1 - 0.2 μm / 3.0 - 8.0 μm) |  |  |  |

#### Note:

**Table 2.5. Thermal Conditions**

Max Junction Temperature = 125 °C

| Package                   | Parameter                                | Symbol        | Test Condition   | Value | Unit |

|---------------------------|------------------------------------------|---------------|------------------|-------|------|

|                           | Thermal Resistance Junction to Ambient   | $\Theta_{JA}$ | Still Air, 85 °C | 80    | °C/W |

| 2.5 x 3.2 mm<br>8-pin DFN | Thermal Parameter Junction to Board      | $\Psi_{JB}$   | Still Air, 85 °C | 39    | °C/W |

| ·                         | Thermal Parameter Junction to Top Center | $\Psi_{JT}$   | Still Air, 85 °C | 17    | °C/W |

|                           | Thermal Resistance Junction to Ambient   | $\Theta_{JA}$ | Still Air, 85 °C | 55    | °C/W |

| 3.2 × 5 mm<br>8-pin CLCC  | Thermal Parameter Junction to Board      | $\Psi_{JB}$   | Still Air, 85 °C | 20    | °C/W |

|                           | Thermal Parameter Junction to Top Center | $\Psi_{JT}$   | Still Air, 85 °C | 20    | °C/W |

|                           | Thermal Resistance Junction to Ambient   | $\Theta_{JA}$ | Still Air, 85 °C | 53    | °C/W |

| 5 × 7 mm<br>8-pin CLCC    | Thermal Parameter Junction to Board      | $\Psi_{JB}$   | Still Air, 85 °C | 26    | °C/W |

| ,                         | Thermal Parameter Junction to Top Center | $\Psi_{JT}$   | Still Air, 85 °C | 26    | °C/W |

<sup>1.</sup> For additional product information not listed in the data sheet (e.g. RoHS Certifications, MDDS data, qualification data, REACH Declarations, ECCN codes, etc.), refer to our "Corporate Request For Information" portal found here: www.silabs.com/support/quality/Pages/RoHSInformation.aspx.

<sup>1.</sup> Based on PCB Dimensions: 4.5" x 7", PCB Thickness: 1.6 mm, Number of Cu Layers: 4.

Table 2.6. Absolute Maximum Ratings<sup>1</sup>

| Parameter                                     | Symbol            | Rating                        | Unit |

|-----------------------------------------------|-------------------|-------------------------------|------|

| Maximum Operating Temp.                       | T <sub>AMAX</sub> | 95                            | °C   |

| Storage Temperature                           | T <sub>S</sub>    | -55 to 125                    | °C   |

| Supply Voltage                                | V <sub>DD</sub>   | -0.5 to 3.8                   | °C   |

| Input Voltage                                 | V <sub>IN</sub>   | -0.5 to V <sub>DD</sub> + 0.3 | V    |

| ESD HBM (JESD22-A114)                         | НВМ               | 2.0                           | kV   |

| Solder Temperature <sup>2</sup>               | T <sub>PEAK</sub> | 260                           | °C   |

| Solder Time at T <sub>PEAK</sub> <sup>2</sup> | T <sub>P</sub>    | 20–40                         | sec  |

- 1. Stresses beyond those listed in this table may cause permanent damage to the device. Functional operation specification compliance is not implied at these conditions. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2. The device is compliant with JEDEC J-STD-020.

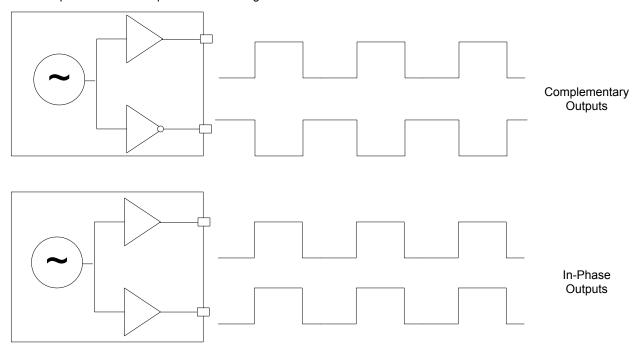

#### 3. Dual CMOS Buffer

Dual CMOS output format ordering options support either complementary or in-phase signals for two identical frequency outputs. This feature enables replacement of multiple XOs with a single Si547 device.

Figure 3.1. Integrated 1:2 CMOS Buffer Supports Complementary or In-Phase Outputs

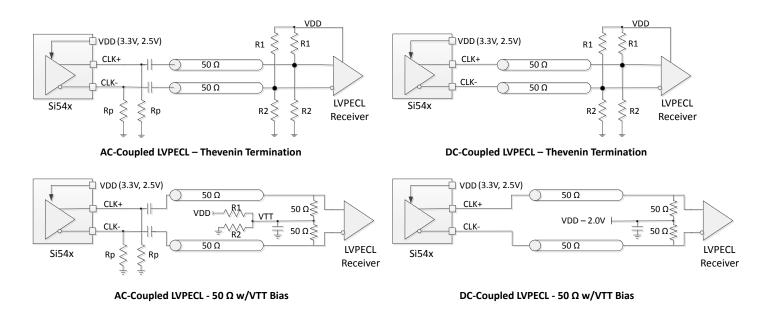

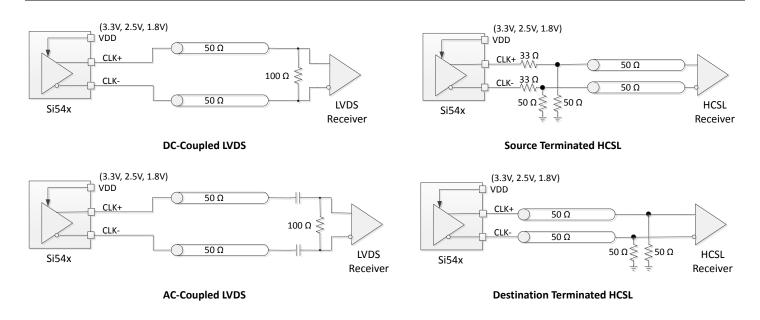

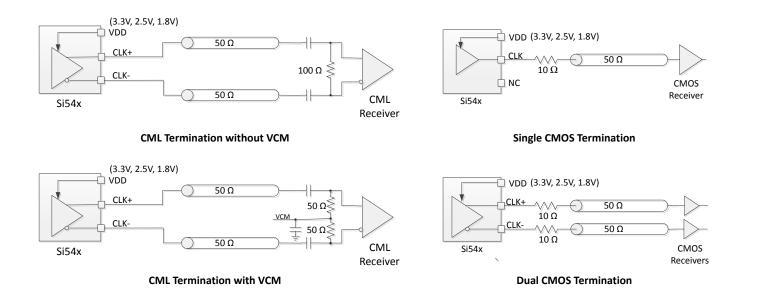

#### 4. Recommended Output Terminations

The output drivers support both AC-coupled and DC-coupled terminations as shown in figures below.

Figure 4.1. LVPECL Output Terminations

| AC Coupled LVPECL Termination Resistor Values |        |       |       | DC Coupled LVPECL Termination Resistor Values |       |        |  |  |

|-----------------------------------------------|--------|-------|-------|-----------------------------------------------|-------|--------|--|--|

| VDD                                           | R1     | R2    | Rp    | VDD                                           | R1    | R2     |  |  |

| 3.3 V                                         | 82.5 Ω | 127 Ω | 130 Ω | 3.3 V                                         | 127 Ω | 82.5 Ω |  |  |

| 2.5 V                                         | 62.5 Ω | 250 Ω | 90 Ω  | 2.5 V                                         | 250 Ω | 62.5 Ω |  |  |

Figure 4.2. LVDS and HCSL Output Terminations

Figure 4.3. CML and CMOS Output Terminations

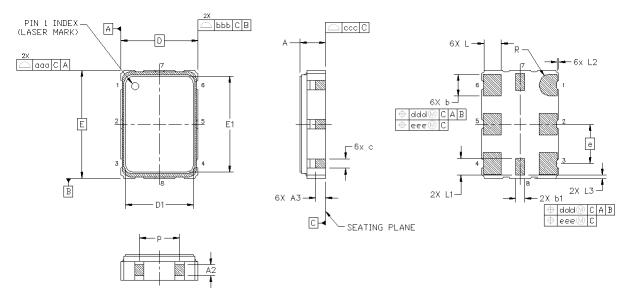

#### 5. Package Outline

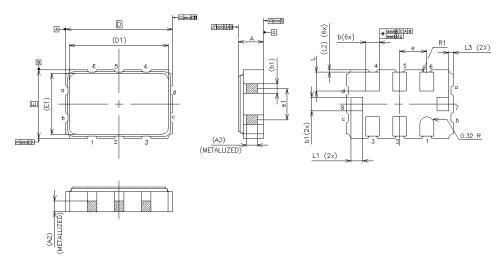

#### 5.1 Package Outline (5x7 mm)

The figure below illustrates the package details for the 5x7 mm Si547. The table below lists the values for the dimensions shown in the illustration.

Figure 5.1. Si547 (5x7 mm) Outline Diagram

Table 5.1. Package Diagram Dimensions (mm)

| Dimension | Min      | Nom      | Max  | Dimension | Min  | Nom      | Max  |

|-----------|----------|----------|------|-----------|------|----------|------|

| А         | 1.07     | 1.18     | 1.33 | L         | 1.07 | 1.17     | 1.27 |

| A2        | 0.40     | 0.50     | 0.60 | L1        | 1.00 | 1.10     | 1.20 |

| A3        | 0.45     | 0.55     | 0.65 | L2        | 0.05 | 0.10     | 0.15 |

| b         | 1.30     | 1.40     | 1.50 | L3        | 0.15 | 0.20     | 0.25 |

| b1        | 0.50     | 0.60     | 0.70 | р         | 1.70 |          | 1.90 |

| С         | 0.50     | 0.60     | 0.70 | R         |      | 0.70 REF |      |

| D         |          | 5.00 BSC |      | aaa       | 0.15 |          |      |

| D1        | 4.30     | 4.40     | 4.50 | bbb       |      | 0.15     |      |

| е         | 2.54 BSC |          |      | ccc       |      | 0.08     |      |

| E         | 7.00 BSC |          |      | ddd       |      | 0.10     |      |

| E1        | 6.10     | 6.20     | 6.30 | eee       |      | 0.05     |      |

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

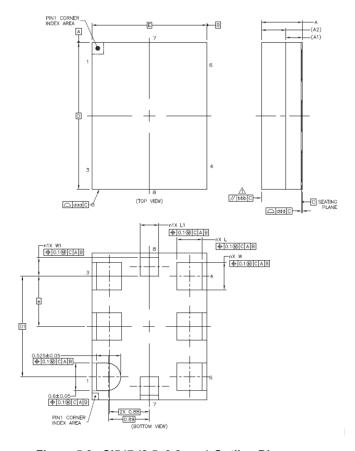

#### 5.2 Package Outline (3.2x5 mm)

The figure below illustrates the package details for the 3.2x5 mm Si547. The table below lists the values for the dimensions shown in the illustration.

Figure 5.2. Si547 (3.2x5 mm) Outline Diagram

Table 5.2. Package Diagram Dimensions (mm)

| Dimension | MIN       | NOM      | MAX  |  | Dimension | MIN  | NOM      | MAX  |

|-----------|-----------|----------|------|--|-----------|------|----------|------|

| А         | 1.02      | 1.17     | 1.33 |  | E1        |      | 2.85 BSC |      |

| A2        | 0.50      | 0.55     | 0.60 |  | L         | 0.8  | 0.9      | 1.0  |

| A3        | 0.45      | 0.50     | 0.55 |  | L1        | 0.45 | 0.55     | 0.65 |

| b         | 0.54      | 0.64     | 0.74 |  | L2        | 0.05 | 0.10     | 0.15 |

| b1        | 0.54      | 0.64     | 0.75 |  | L3        | 0.15 | 0.20     | 0.25 |

| D         |           | 5.00 BSC |      |  | aaa       | 0.15 |          |      |

| D1        |           | 4.65 BSC |      |  | bbb       |      | 0.15     |      |

| е         |           | 1.27 BSC |      |  | ccc       | 0.08 |          |      |

| e1        | 1.625 TYP |          |      |  | ddd       | 0.10 |          |      |

| E         |           | 3.20 BSC |      |  | eee       |      | 0.05     |      |

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

#### 5.3 Package Outline (2.5x3.2 mm)

The figure below illustrates the package details for the 2.5x3.2 mm Si547. The table below lists the values for the dimensions shown in the illustration.

Figure 5.3. Si547 (2.5x3.2 mm) Outline Diagram

Table 5.3. Package Diagram Dimensions (mm)

| Dimension | MIN      | NOM  | MAX  | Dimension | MIN  | NOM     | MAX  |

|-----------|----------|------|------|-----------|------|---------|------|

| А         | _        | _    | 1    | L1        | 0.35 | 0.4     | 0.45 |

| A1        | 0.36 REF |      |      | е         |      | 1.1 BSC |      |

| A2        | 0.53 REF |      |      | n         |      | 5       |      |

| D         | 3.2 BSC  |      |      | n1        | 2    |         |      |

| E         | 2.5 BSC  |      |      | D1        |      | 2.2 BSC |      |

| W         | 0.55     | 0.6  | 0.65 | aaa       |      | 0.10    |      |

| L         | 0.5      | 0.55 | 0.6  | bbb       |      | 0.10    |      |

| W1        | 0.35     | 0.4  | 0.45 | ddd       |      | 0.08    |      |

- 1. The dimensions in parentheses are reference.

- 2. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 3. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

#### 6. PCB Land Pattern

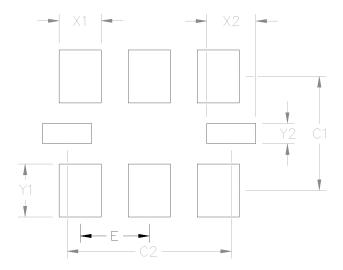

#### 6.1 PCB Land Pattern (5x7 mm)

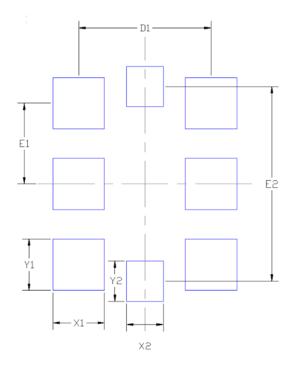

The figure below illustrates the 5x7 mm PCB land pattern for the Si547. The table below lists the values for the dimensions shown in the illustration.

Figure 6.1. Si547 (5x7 mm) PCB Land Pattern

Table 6.1. PCB Land Pattern Dimensions (mm)

| Dimension | (mm) | Dimension | (mm) |

|-----------|------|-----------|------|

| C1        | 4.20 | Y1        | 1.95 |

| C2        | 6.05 | X2        | 1.80 |

| E         | 2.54 | Y2        | 0.75 |

| X1        | 1.55 |           |      |

#### Notes:

#### General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification.

- 3. This Land Pattern Design is based on the IPC-7351 guidelines.

- 4. All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05 mm.

#### Solder Mask Design

1. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \mu m$  minimum, all the way around the pad.

#### Stencil Design

- 1. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125 mm (5 mils).

- 3. The ratio of stencil aperture to land pad size should be 1:1.

#### **Card Assembly**

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

#### 6.2 PCB Land Pattern (3.2x5 mm)

The figure below illustrates the 3.2x5.0 mm PCB land pattern for the Si547. The table below lists the values for the dimensions shown in the illustration.

Figure 6.2. Si547 (3.2x5 mm) PCB Land Pattern

Table 6.2. PCB Land Pattern Dimensions (mm)

| Dimension | (mm) | Dimension | (mm) |

|-----------|------|-----------|------|

| C1        | 2.70 | X2        | 0.90 |

| E         | 1.27 | Y1        | 1.60 |

| E1        | 4.30 | Y2        | 0.70 |

| X1        | 0.74 |           |      |

#### Notes:

#### General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification.

- 3. This Land Pattern Design is based on the IPC-7351 guidelines.

- 4. All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05 mm.

#### Solder Mask Design

1. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \mu m$  minimum, all the way around the pad.

#### Stencil Design

- 1. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125 mm (5 mils).

- 3. The ratio of stencil aperture to land pad size should be 1:1.

#### **Card Assembly**

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

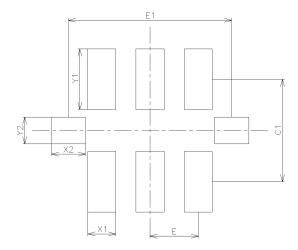

#### 6.3 PCB Land Pattern (2.5x3.2 mm)

The figure below illustrates the 2.5x3.2 mm PCB land pattern for the Si547. The table below lists the values for the dimensions shown in the illustration.

Figure 6.3. Si547 (2.5x3.2 mm) PCB Land Pattern

Table 6.3. PCB Land Pattern Dimensions (mm)

| Dimension | Description                           | Value (mm) |

|-----------|---------------------------------------|------------|

| X1        | Width - leads on long sides           | 0.7        |

| Y1        | Height - leads on long sides          | 0.7        |

| X2        | Width - single leads on short sides   | 0.5        |

| Y2        | Height - single leads on short sides  | 0.55       |

| D1        | Pitch in X directions of XL, Y1 leads | 1.80       |

| E1        | Lead pitch X1, Y1 leads               | 1.10       |

| E2        | Lead pitch X2,Y2 leads                | 2.65       |

| Dimension Description Value (mm) | Dimension | Description | Value (mm) |

|----------------------------------|-----------|-------------|------------|

|----------------------------------|-----------|-------------|------------|

#### Notes:

#### General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification.

- 3. This Land Pattern Design is based on the IPC-7351 guidelines.

- 4. All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05 mm.

#### Solder Mask Design

1. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 µm minimum, all the way around the pad.

#### Stencil Design

- 1. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125 mm (5 mils).

- 3. The ratio of stencil aperture to land pad size should be 0.8:1 for the pads.

#### **Card Assembly**

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

## 7. Top Marking

### 7.1 Top Marking (5x7 and 3.2x5 Packages)

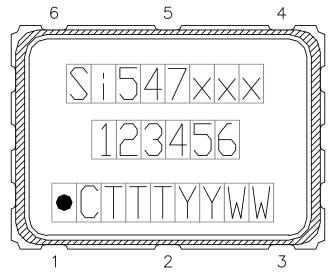

The figure below illustrates the mark specification for the Si547 5x7 and 3.2x5 package sizes. The table below lists the line information.

Figure 7.1. Mark Specification

Table 7.1. Si547 Top Mark Description

| Line         | Position     | Description                                                                         |

|--------------|--------------|-------------------------------------------------------------------------------------|

| 1            | 1–8          | "Si547", xxx = Ordering Option 1, Option 2, Option 3 (e.g. Si547AAA)                |

| 2            | 1–6          | Frequency Code (6-digit custom code as described in the Ordering Guide)             |

| 3            |              | Trace Code                                                                          |

|              | Position 1   | Pin 1 orientation mark (dot)                                                        |

|              | Position 2   | Product Revision (C)                                                                |

|              | Position 3–5 | Tiny Trace Code (3 alphanumeric characters per assembly release instructions)       |

| Position 6–7 |              | Year (last two digits of the year), to be assigned by assembly site (ex: 2017 = 17) |

|              | Position 8–9 | Calendar Work Week number (1–53), to be assigned by assembly site                   |

#### 7.2 Top Marking (2.5x3.2 Package)

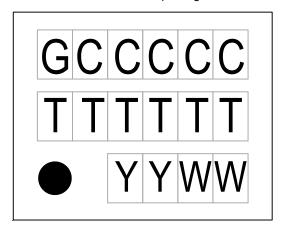

The figure below illustrates the mark specification for the Si547 2.5x3.2 package size. The table below lists the line information.

Figure 7.2. Mark Specification

Table 7.2. Si547 Top Mark Description

| Line         | Position     | Description                                                                         |

|--------------|--------------|-------------------------------------------------------------------------------------|

| 1            | 1–6          | G = Si547, CCCCC = Custom Mark Code                                                 |

| 2            | Trace Code   |                                                                                     |

|              | 1–6          | 6 digit trace code per assembly release instructions                                |

| 3            | Position 1   | Pin 1 orientation mark (dot)                                                        |

|              | Position 2–3 | Year (last two digits of the year), to be assigned by assembly site (ex: 2017 = 17) |

| Position 4–5 |              | Calendar Work Week number (1–53), to be assigned by assembly site                   |

#### 8. Revision History

#### **Revision 1.3**

June. 2021

- Updated Ordering Guide and topmark for RevC silicon

- · Added HCSL-Fast (faster tR/tF) ordering option

- Updated Table 2.1, Powerup VDD Ramp Rate

#### Revision 1.2

September, 2020

- Added 2.5x3.2 mm package option.

- · Updated Table 2.1, Powerup VDD Ramp Rate and LVDS Swing

#### **Revision 1.0**

August, 2018

· Added 20 ppm total stability option.

#### Revision 0.75

March, 2018

• Added 25 ppm total stability option.

#### Revision 0.71

December 11, 2017

• Added 5x7 package and land pattern.

#### Revision 0.7

June 27, 2017

· Initial release.

**Timing Portfolio** www.silabs.com/timing

**SW/HW** www.silabs.com/CBPro

**Quality** www.silabs.com/quality

**Support & Community** www.silabs.com/community

#### Disclaimer

Silicon Labs intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Labs products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Labs reserves the right to make changes without further notice to the product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Without prior notification, Silicon Labs may update product firmware during the manufacturing process for security or reliability reasons. Such changes will not alter the specifications or the performance of the product. Silicon Labs shall have no liability for the consequences of use of the information supplied in this document. This document does not imply or expressly grant any license to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any FDA Class Ill devices, applications for which FDA premarket approval is required or Life Support Systems without the specific written consent of Silicon Labs. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Labs products are not designed or authorized for military applications. Silicon Labs products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons. Silicon Labs disclaims all express and implied warranties and shall not be responsible or liable for any injuries or damages related to use of a Silicon Labs p

#### Trademark Information

Silicon Laboratories Inc.®, Silicon Laboratories®, Silicon Labs®, SiLabs® and the Silicon Labs logo®, Bluegiga®, Bluegiga Logo®, Clockbuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZRadio®, EZRadioPRO®, Gecko®, Gecko OS, Gecko OS Studio, ISOmodem®, Precision32®, ProSLIC®, Simplicity Studio®, SiPHY®, Telegesis, the Telegesis Logo®, USBXpress®, Zentri, the Zentri logo and Zentri DMS, Z-Wave®, and others are trademarks or registered trademarks of Silicon Labs. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. Wi-Fi is a registered trademark of the Wi-Fi Alliance. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

#### Silicon Laboratories:

```

547CAB002433BAG 547FAA002436BAG 547BAA002437BAG 547DAA002435BAG 547CAA002438BAG

547CAA002444BAG 547AAA002451BAG 547FAA000612BAG 547AAA002457BAG 547DAA002457BAG

547CAA002453BAG 547ABA002480BBG 547ACA002502BBG 547BAA002537BBG 547BCA002546BBG

547FAA002544BBG 547AAA002422BAG 547AAA002422BAGR 547BAA002420BAG 547BAA002420BAGR

547CAA002444BAGR 547CAA002447BAG 547ACA002547BBGR 547ACD002548ABG 547BCC000189BBGR

547BCC002547BBG 547BCC002547BBGR 547CCA002477BBG 547CCA002477BBGR 547ACA002547BBG

547ACA002541BBGR 547BAA002537BBGR 547FAA002544BBGR 547ACD002548ABGR 547BCA002546BBGR

547BCC000189BBG 547DAB002468BBGR 547FAA002478BBG 547FAA002478BBGR 547ABA002532ABG

547ABA002532ABGR 547ACA002541BBG 547CCA002480BBGR 547CCA002540BBG 547CCA002540BBGR

547DAB002467BBG 547DAB002467BBGR 547DAB002468BBG 547BCA002536BBGR 547BCA002543ABG

547BCA002543ABGR 547CBC002535BBG 547CBC002535BBGR 547CCA002480BBG 547BCB002502BBG

547BCB002502BBGR 547BCC002520BBG 547BCC002520BBGR 547BCC002521BBG 547BCA002536BBG

547BCA002516BBG 547BCA002516BBGR 547BCA002517BBG 547BCA002517BBGR 547BCA002532BBG

547BCA002532BBGR 547BCA002410BBG 547BCA002410BBGR 547BCA002503BBG 547BCA002503BBGR

547BCA002515BBG 547BCA002515BBGR 547ACA000283ABG 547ACA000283ABGR 547BAA002534BBG

547BAA002534BBGR 547ACA002510ABG 547ACA002510ABGR 547AAA002470BBGR 547ABA002470BBG

547ABA002470BBGR 547ABA002480BBGR 547ACA000189BBG 547ACA000189BBGR 547DAB002465BBGR

547DAB002466BBG 547DAB002466BBGR 547AAA002469BBG 547AAA002469BBGR 547AAA002470BBG

547CAA002477BBGR 547DAA002477BBG 547DAA002477BBGR 547DAA002479BBG 547DAA002479BBGR

547DAB002465BBG 547AAA002420BAGR 547ACA000454BBG 547ACA000454BBGR 547ACA002502BBGR

```