# **BGM210L Wireless Gecko Bluetooth<sup>®</sup> Lighting Module Data Sheet**

The BGM210L is a module designed and built to meet the performance, security, and reliability requirements of line-powered, smart LED lighting products.

Based on the EFR32BG21 Gecko SoC, it enables Bluetooth 5.x and Bluetooth Mesh connectivity delivering best-in-class RF performance, CA Title 20 energy consumption compliance, future-proof capability for feature and OTA firmware updates, enhanced security, and a form factor and temperature rating suited for enclosed operation in lightbulb housings.

The BGM210L is a complete solution that comes with fully-upgradeable, robust software stacks, world-wide regulatory certifications, advanced development and debugging tools, and support that will simplify and minimize the development cycle of your product helping to accelerate its time-to-market.

The BGM210L is targeted for key applications that include:

- · Smart LED lightbulbs

- · Connected lighting

#### **KEY FEATURES**

- Bluetooth 5.x and Bluetooth Mesh connectivity

- · PCB Trace antenna

- +12.5 dBm Max TX power

- -97 dBm Bluetooth RX sensitivity @ 1 Mbps

- · 32-bit ARM Cortex-M33 core at 38.4 MHz

- · 1024/96 kB of flash/RAM memory

- · Enhanced security features

- · Optimal set of MCU peripherals

- 12 GPIO pins

- -40 to (105 or 125)°C

- 15.5 mm x 22.5 mm (custom form factor)

#### 1. Features

#### · Supported Protocols

- Bluetooth 5.x

- AoA/AoD

- · Bluetooth Mesh

#### · Wireless System-on-Chip

- · 2.4 GHz radio

- TX power up to +12.5 dBm

- 32-bit ARM Cortex<sup>®</sup>-M33 with DSP instruction and floatingpoint unit for efficient signal processing

- · 1024 kB flash program memory

- · 96 kB RAM data memory

- · Embedded Trace Macrocell (ETM) for advanced debugging

#### Receiver Performance

- · -104.4 dBm sensitivity (0.1% BER) at 125 kbps GFSK

- -100.1 dBm sensitivity (0.1% BER) at 500 kbps GFSK

- -97 dBm sensitivity (0.1% BER) at 1 Mbps GFSK

- -93.9 dBm sensitivity (0.1% BER) at 2 Mbps GFSK

#### · Current Consumption

- 9.3 mA RX current at 1 Mbps GFSK

- 70 mA TX current at +12.5 dBm output power

- 50.9 µA/MHz in Active Mode (EM0)

- 5.1 μA EM2 DeepSleep current (RTCC running from LFXO, Bluetooth Stack not running)

- 8.5  $\mu$ A EM2 DeepSleep current (RTCC running from LFXO, Bluetooth Stack running)

#### · Regulatory Certifications

- · CE, UKCA, Serbia

- · ISED, FCC, Dominican Republic

- · Japan, South Korea, Taiwan

- · China, Hong Kong, Thailand, Australia

- · Bahrain, Israel, Qatar

- · Egypt, Morocco

#### · Operating Range

- 1.8 to 3.8 V

- -40 to +105 °C or -40 to +125 °C

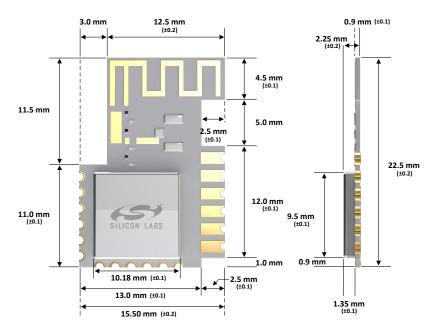

#### Dimensions

• 15.5 mm x 22.5 mm (custom form factor)

#### Security

- Secure Boot with Root of Trust and Secure Loader (RTSL)<sup>1</sup>

- Hardware Cryptographic Acceleration with DPA countermeasures<sup>1</sup> for AES128/256, SHA-1, SHA-2 (up to 256-bit), ECC (up to 256-bit), ECDSA, and ECDH

- True Random Number Generator (TRNG) compliant with NIST SP800-90 and AIS-31

- ARM® TrustZone®

- Secure Debug Interface lock/unlock

#### MCU Peripherals

- 12-bit 1 Msps SAR Analog to Digital Converter (ADC)

- 2 × Analog Comparator (ACMP)

- 12 General Purpose I/O pins with output state retention and asynchronous interrupts

- · 8 Channel DMA Controller

- 12 Channel Peripheral Reflex System (PRS)

- 3 × 16-bit Timer/Counter (3 Compare/Capture/PWM channels)

- 1 × 32-bit Timer/Counter (3 Compare/Capture/PWM channels)

- · 32-bit Real Time Counter

- 24-bit Low Energy Timer for waveform generation

- 2 × Watchdog Timer

- 3 × Universal Synchronous/Asynchronous Receiver/Transmitter (UART/SPI/SmartCard (ISO 7816)/IrDA/I<sup>2</sup>S)

- 2 × I<sup>2</sup>C interface with SMBus support

<sup>1.</sup> With Secure Engine (SE) firmware v1.1.2 or newer

## 2. Ordering Information

**Table 2.1. Ordering Information**

| Ordering Code   | Protocol Stack | Max TX<br>Power | Freq<br>Band | Antenna                 | Flash<br>(kB) | RAM<br>(kB) | GPIO | Temp Range    | Packaging |

|-----------------|----------------|-----------------|--------------|-------------------------|---------------|-------------|------|---------------|-----------|

| BGM210LA22JIF2  | Bluetooth 5.x  | 12.5 dBm        | 2.4 GHz      | Inverted-F<br>PCB Trace | 1024          | 96          | 12   | -40 to 125 °C | Cut Tape  |

| BGM210LA22JIF2R | Bluetooth 5.x  | 12.5 dBm        | 2.4 GHz      | Inverted-F<br>PCB Trace | 1024          | 96          | 12   | -40 to 125 °C | Reel      |

| BGM210LA22JNF2  | Bluetooth 5.x  | 12.5 dBm        | 2.4 GHz      | Inverted-F<br>PCB Trace | 1024          | 96          | 12   | -40 to 105 °C | Cut Tape  |

| BGM210LA22JNF2R | Bluetooth 5.x  | 12.5 dBm        | 2.4 GHz      | Inverted-F<br>PCB Trace | 1024          | 96          | 12   | -40 to 105 °C | Reel      |

Bluetooth 5.x: As the Bluetooth standard evolves, Silicon Labs is regularly adding new features. For more information on supported Bluetooth capabilities, visit https://www.silabs.com/bluetooth-hardware.

End-product manufacturers must verify that the module is configured to meet regulatory limits for each region in accordance with the formal certification test reports.

BGM210L modules are pre-programmed with BGAPI UART DFU bootloader.

**SLWRB4309B** radio board is available for BGM210L evaluation and development.

The modules may be referred to by their product family name (BGM210L), model name (BGM210L22F) or full ordering code throughout this document.

# **Table of Contents**

| 1. | Features                                                                | . 2  |

|----|-------------------------------------------------------------------------|------|

| 2. | Ordering Information                                                    | . 3  |

| 3. | System Overview                                                         | . 6  |

|    | 3.1 Block Diagram                                                       | . 6  |

|    | 3.2 EFR32BG21 SoC                                                       | . 6  |

|    | 3.3 Antenna                                                             |      |

|    | 3.4 Power Supply                                                        |      |

| 4. | Electrical Specifications                                               |      |

|    | 4.1 Electrical Characteristics                                          |      |

|    | 4.1.1 Absolute Maximum Ratings                                          |      |

|    | 4.1.2 General Operating Conditions                                      | . 8  |

|    | 4.1.3 MCU Current Consumption at 3.0V                                   |      |

|    | 4.1.4 Radio Current Consumption at 3.0V                                 |      |

|    | 4.1.5 RF Transmitter General Characteristics for the 2.4 GHz Band       |      |

|    | 4.1.6 RF Receiver General Characteristics for the 2.4 GHz Band          |      |

|    | 4.1.7 RF Receiver Characteristics for Bluetooth Low Energy at 1 Mbps    |      |

|    | 4.1.8 RF Receiver Characteristics for Bluetooth Low Energy at 2 Mbps    |      |

|    | 4.1.9 RF Receiver Characteristics for Bluetooth Low Energy at 500 kbps  |      |

|    | 4.1.10 RF Receiver Characteristics for Bluetooth Low Energy at 125 kbps |      |

|    | 4.1.12 GPIO Pins                                                        |      |

|    | 4.1.13 Microcontroller Peripherals                                      |      |

|    | 4.2 Typical Performance Curves                                          |      |

|    | 4.2.1 Antenna Radiation and Efficiency                                  |      |

| _  |                                                                         |      |

|    | Reference Diagrams                                                      |      |

| 6. | Pin Definitions                                                         | . 21 |

|    | 6.1 Module Pinout                                                       | .21  |

|    | 6.2 Alternate Pin Functions                                             | .22  |

|    | 6.3 Analog Peripheral Connectivity                                      |      |

|    | 6.4 Digital Peripheral Connectivity                                     | .23  |

| 7. | Design Guidelines                                                       | . 26 |

|    | 7.1 Module Placement                                                    | .26  |

|    | 7.2 Antenna Optimization                                                |      |

|    | 7.3 Reset                                                               |      |

|    | 7.4 Debug                                                               |      |

|    |                                                                         |      |

|    | 7.5 Packet Trace Interface (PTI)                                        |      |

| 8. | Package Specifications                                                  | . 29 |

|    | 8.1 Package Outline                                                     | .29  |

| 8.2 PCB Land Pattern               | .30  |

|------------------------------------|------|

| 8.3 Marking                        | .31  |

| 9. Soldering Recommendations       | . 32 |

| 10. Tape and Reel                  | .33  |

| 11. Certifications                 | 34   |

| 11.1 CE and UKCA                   | .34  |

| 11.2 FCC                           | .35  |

| 11.3 ISED Canada                   | .36  |

| 11.4 Australia (ACMA).             | .37  |

| 11.5 Dominican Republic (INDOTEL). | .37  |

| 11.6 Hong Kong (OFCA)              | .38  |

| 11.7 Israel (MOC)                  | .38  |

| 11.8 Serbia (RATEL)                | .38  |

| 11.9 Bahrain (BTRA)                | .38  |

| 11.10 China (SRRC)                 | .38  |

| 11.11 Egypt (NTRA)                 | .38  |

| 11.12 Japan (MIC)                  | .39  |

| 11.13 South Korea (KC)             | .39  |

| 11.14 Morocco (ANRT)               | .39  |

| 11.15 Qatar (CRA)                  | .39  |

| 11.16 Thailand (NBTC)              | .40  |

| 11.17 NCC Taiwan                   | .40  |

| 11.18 Bluetooth Qualification      | .40  |

| 12. Revision History               | 41   |

## 3. System Overview

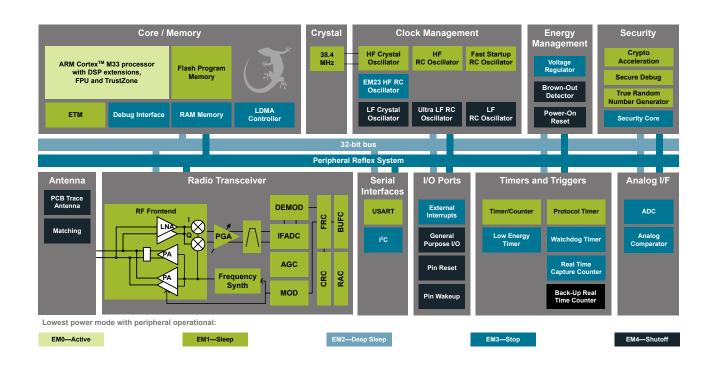

#### 3.1 Block Diagram

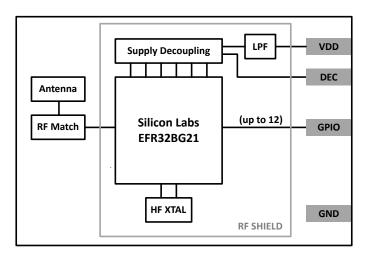

The BGM210L module is a highly-integrated, high-performance system with all the hardware components needed to enable 2.4 GHz wireless connectivity and support robust networking capabilities via multiple protocols.

Built around the EFR32BG21 Wireless Gecko SoC, the BGM210L includes a built-in PCB trace antenna, an RF matching network (optimized for transmit power efficiency), supply decoupling and filtering components, a 38.4 MHz reference crystal, and an RF shield. A general block diagram of the module is shown below.

Figure 3.1. BGM210L Block Diagram

#### 3.2 EFR32BG21 SoC

The EFR32BG21 SoC features a 32-bit ARM Cortex M33 core, a 2.4 GHz high-performance radio, 1 MB of Flash memory, a dedicated core for security, a rich set of MCU peripherals, and various clock management and serial interfacing options. Consult the EFR32xG21 Wireless Gecko Reference Manual and the EFR32BG21 Data Sheet for details (See EFR32BG21A020F1024IM32).

#### 3.3 Antenna

BGM210L modules include a meandered inverted-F antenna (MIFA) with the characteristics seen below.

Table 3.1. Antenna Efficiency and Peak Gain

| Parameter  | With optimal layout | Note                                                                                                                                                                             |

|------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Efficiency | -2 to -2.5 dB       | Antenna efficiency, gain and radiation pattern are highly depend-                                                                                                                |

| Peak gain  | 0.5 dBi             | ent on the application PCB layout and mechanical design. Refer to Section 7. Design Guidelines for PCB layout and antenna integration guidelines to achieve optimal performance. |

#### 3.4 Power Supply

The BGM210L requires a single nominal supply level of 3.0 V. All the necessary decoupling and filtering components are included in the module. The module can tolerate supply voltage noise of up to 700 mVpp.

The supply voltage is filtered internally in the module with a 100 kHz low-pass filter to guarantee operation across the full supply range of 1.8 to 3.8 V. Additional external filtering is neither required nor recommended as it may cause voltage drops below the minimum level tolerable by the SoC (1.71 V) during transmit bursts.

For typical use cases, the decouple pin (DEC) should be left disconnected.

## 4. Electrical Specifications

#### 4.1 Electrical Characteristics

All electrical parameters in all tables are specified under the following conditions, unless stated otherwise:

- Typical values are based on T<sub>A</sub>=25 °C and VDD = 3.0 V, by production test and/or technology characterization.

- Radio performance numbers are measured in conducted mode, based on Silicon Laboratories reference designs using output power-specific external RF impedance-matching networks for interfacing to a 50 Ω antenna.

- Minimum and maximum values represent the worst conditions across supply voltage, process variation, and operating temperature, unless stated otherwise.

#### 4.1.1 Absolute Maximum Ratings

Stresses above those listed below may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. For more information on the available quality and reliability data, see the Quality and Reliability Monitor Report at <a href="http://www.silabs.com/support/quality/pages/default.aspx">http://www.silabs.com/support/quality/pages/default.aspx</a>.

**Table 4.1. Absolute Maximum Ratings**

| Parameter                             | Symbol                 | Test Condition | Min  | Тур | Max                   | Unit   |

|---------------------------------------|------------------------|----------------|------|-----|-----------------------|--------|

| Storage temperature range             | T <sub>STG</sub>       |                | -50  | _   | +150                  | °C     |

| Voltage on VDD supply pin             | V <sub>DDMAX</sub>     |                | -0.3 | _   | 3.8                   | V      |

| Voltage ramp rate on VDD supply pin   | V <sub>DDRAMPMAX</sub> |                | _    | _   | 1.0                   | V / µs |

| DC voltage on any GPIO pin            | V <sub>DIGPIN</sub>    |                | -0.3 | _   | V <sub>DD</sub> + 0.3 | V      |

| DC voltage on RESETn pin <sup>1</sup> | V <sub>RESETn</sub>    |                | -0.3 | _   | 3.8                   | V      |

| Total current into VDD pin            | I <sub>VDDMAX</sub>    | Source         | _    | _   | 200                   | mA     |

| Total current into GND pin            | I <sub>GNDMAX</sub>    | Sink           | _    | _   | 200                   | mA     |

| Current per I/O pin                   | I <sub>IOMAX</sub>     | Sink           | _    | _   | 50                    | mA     |

|                                       |                        | Source         | _    | _   | 50                    | mA     |

| Current for all I/O pins              | I <sub>IOALLMAX</sub>  | Sink           | _    | _   | 200                   | mA     |

|                                       |                        | Source         | _    | _   | 200                   | mA     |

| Junction temperature                  | T <sub>JMAX</sub>      |                | _    | _   | +125                  | °C     |

#### Note:

1. The RESETn pin has a pull-up device to the VDD supply. For minimum leakage, RESETn should not exceed the voltage at VDD.

## 4.1.2 General Operating Conditions

This table specifies the general operating temperature range and supply voltage range for all supplies. The minimum and maximum values of all other tables are specifed over this operating range, unless otherwise noted.

**Table 4.2. General Operating Conditions**

| Parameter                    | Symbol                   | Test Condition                       | Min | Тур  | Max  | Unit |

|------------------------------|--------------------------|--------------------------------------|-----|------|------|------|

| Operating ambient tempera-   | T <sub>A</sub>           | -N temperature grade                 | -40 | _    | +105 | °C   |

| ture range                   |                          | -I temperature grade                 | -40 | _    | +125 | ° C  |

| VDD Supply Voltage           | V <sub>DD</sub>          |                                      | 1.8 | 3.0  | 3.8  | V    |

| HCLK and Core frequency      | f <sub>HCLK</sub>        | MODE = WS1, RAMWSEN = 1 <sup>1</sup> | _   | _    | 80   | MHz  |

|                              |                          | MODE = WS1, RAMWSEN = 0 <sup>1</sup> | _   | _    | 50   | MHz  |

|                              |                          | MODE = WS0, RAMWSEN = 0 <sup>1</sup> | _   | _    | 39   | MHz  |

| PCLK frequency               | f <sub>PCLK</sub>        |                                      | _   | _    | 50   | MHz  |

| EM01 Group A clock frequency | f <sub>EM01GRPACLK</sub> |                                      | _   | _    | 80   | MHz  |

| HCLK Radio frequency         | f <sub>HCLKRADIO</sub>   |                                      | _   | 38.4 | _    | MHz  |

| External Clock Input         | f <sub>CLKIN</sub>       | VSCALE2 or VSCALE1, IOVDD ≥ 2.7 V    | _   | _    | 40   | MHz  |

| DPLL Reference Clock         | f <sub>DPLLREFCLK</sub>  | VSCALE2 or VSCALE1                   | _   | _    | 40   | MHz  |

<sup>1.</sup> Flash wait states are set by the MODE field in the MSC\_READCTRL register. RAM wait states are enabled by setting the RAMW-SEN bit in the SYSYCFG\_DMEMORAMCTRL register.

## 4.1.3 MCU Current Consumption at 3.0V

Unless otherwise indicated, typical conditions are: VDD = 3.0 V.  $T_A$  = 25 °C. Minimum and maximum values in this table represent the worst conditions across process variation at  $T_A$  = 25 °C.

Table 4.3. MCU Current Consumption at 3.0V

| Parameter                                                 | Symbol              | Test Condition                                                             | Min | Тур  | Max  | Unit   |

|-----------------------------------------------------------|---------------------|----------------------------------------------------------------------------|-----|------|------|--------|

| Current consumption in EM0 mode with all peripherals dis- | I <sub>ACTIVE</sub> | 80 MHz HFRCO, CPU running<br>Prime from flash                              | _   | 50.9 | _    | μA/MHz |

| abled <sup>1</sup>                                        |                     | 80 MHz HFRCO, CPU running while loop from flash                            | _   | 45.6 | 55.5 | μA/MHz |

|                                                           |                     | 80 MHz HFRCO, CPU running<br>CoreMark loop from flash                      | _   | 59.8 | _    | μA/MHz |

|                                                           |                     | 38.4 MHz crystal, CPU running while loop from flash                        | _   | 63.8 | _    | μΑ/MHz |

| Current consumption in EM1                                | I <sub>EM1</sub>    | 80 MHz HFRCO                                                               | _   | 28.7 | 37.6 | μΑ/MHz |

| mode with all peripherals disabled <sup>1</sup>           |                     | 38.4 MHz crystal                                                           | _   | 46.9 | _    | μA/MHz |

| Current consumption in EM2 mode                           | ІЕМ2                | Full RAM retention and RTC running from LFXO (Bluetooth Stack not running) | _   | 5.1  | _    | μА     |

|                                                           |                     | Full RAM retention, RTCC running, and Bluetooth Stack running from LFXO    | _   | 8.5  | _    | μА     |

|                                                           |                     | 1 bank (16 kB) RAM retention and RTC running from LFRCO                    | _   | 4.5  | 10.5 | μA     |

| Current consumption in EM3 mode                           | I <sub>EM3</sub>    | Full RAM retention and RTC running from ULFRCO                             | _   | 4.8  | 11.4 | μА     |

|                                                           |                     | 1 bank (16 kB) RAM retention and RTC running from ULFRCO                   | _   | 4.3  | _    | μА     |

| Current consumption in EM4 mode                           | I <sub>EM4</sub>    | No BURTC, no LF oscillator                                                 | _   | 0.21 | 0.5  | μА     |

| Current consumption during reset                          | I <sub>RST</sub>    | Hard pin reset held                                                        | _   | 146  | _    | μА     |

| Current consumption per retained 16kB RAM bank in EM2     | I <sub>RAM</sub>    |                                                                            | _   | 0.10 | _    | μА     |

<sup>1.</sup> The typical EM0/EM1 current measurement includes some current consumed by the security core for periodical housekeeping purposes. This does not include current consumed by user-triggered security operations, such as cryptographic calculations.

#### 4.1.4 Radio Current Consumption at 3.0V

RF current consumption measured with MCU in EM1, HCLK = 38.4 MHz, and all MCU peripherals disabled. Unless otherwise indicated, typical conditions are: VDD = 3.0V.  $T_A$  = 25 °C. Minimum and maximum values in this table represent the worst conditions across process variation at  $T_A$  = 25 °C.

Table 4.4. Radio Current Consumption at 3.0V

| Parameter                                          | Symbol                 | Test Condition                                             | Min | Тур | Max | Unit |

|----------------------------------------------------|------------------------|------------------------------------------------------------|-----|-----|-----|------|

| Current consumption in receive mode, active packet | I <sub>RX_ACTIVE</sub> | 125 kbit/s, 2GFSK, f = 2.4 GHz,<br>Bluetooth stack running | _   | 9.3 | _   | mA   |

| reception                                          |                        | 500 kbit/s, 2GFSK, f = 2.4 GHz,<br>Bluetooth stack running | _   | 9.3 | _   | mA   |

|                                                    |                        | 1 Mbit/s, 2GFSK, f = 2.4 GHz,<br>Bluetooth stack running   | _   | 9.3 | _   | mA   |

|                                                    |                        | 2 Mbit/s, 2GFSK, f = 2.4 GHz,<br>Bluetooth stack running   | _   | 9.9 | _   | mA   |

| Current consumption in receive mode, Stack running | I <sub>RX_LISTEN</sub> | 125 kbit/s, 2GFSK, f = 2.4 GHz,<br>Bluetooth stack running | _   | 9.1 | _   | mA   |

|                                                    |                        | 500 kbit/s, 2GFSK, f = 2.4 GHz,<br>Bluetooth stack running | _   | 9.1 | _   | mA   |

|                                                    |                        | 1 Mbit/s, 2GFSK, f = 2.4 GHz,<br>Bluetooth stack running   | _   | 9.1 | _   | mA   |

|                                                    |                        | 2 Mbit/s, 2GFSK, f = 2.4 GHz,<br>Bluetooh stack running    | _   | 9.8 |     | mA   |

| Current consumption in transmit mode               | I <sub>TX</sub>        | f = 2.4 GHz, CW, 12.5 dBm output power, VDD = 3.3 V        | _   | 70  | _   | mA   |

#### 4.1.5 RF Transmitter General Characteristics for the 2.4 GHz Band

Unless otherwise indicated, typical conditions are: T<sub>A</sub> = 25 °C, VDD = 3.0V. RF center frequency 2.45 GHz. <sup>1</sup>

Table 4.5. RF Transmitter General Characteristics for the 2.4 GHz Band

| Parameter                                                                           | Symbol                | Test Condition                                                                                                 | Min  | Тур       | Max  | Unit |

|-------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------|------|-----------|------|------|

| RF tuning frequency range                                                           | F <sub>RANGE</sub>    | Frequency Range for Bluetooth Low-Energy                                                                       | 2402 | _         | 2480 | MHz  |

| Maximum TX power <sup>23</sup>                                                      | POUT <sub>MAX</sub>   | 12 dBm PA, VDD = 3.3 V                                                                                         | _    | 12.5      | _    | dBm  |

| Minimum active TX Power                                                             | POUT <sub>MIN</sub>   | 12 dBm PA, VDD = 3.3 V                                                                                         | _    | -20.5     | _    | dBm  |

| Output power variation vs<br>VDD supply voltage varia-<br>tion, frequency = 2450MHz | POUT <sub>VAR_V</sub> | 12 dBm PA P <sub>out</sub> = POUT <sub>MAX</sub> output power with VDD voltage swept from 3.8V to 3.0V.        | _    | +/- 0.5   | _    | dB   |

|                                                                                     |                       | 12 dBm PA P <sub>out</sub> = POUT <sub>MAX</sub> out-<br>put power with VDD voltage swept<br>from 3.8V to 1.8V | _    | +0.5/-4.5 | _    | dB   |

| Output power variation vs RF frequency                                              | POUT <sub>VAR_F</sub> | 12 dBm PA, POUT <sub>MAX</sub> , VDD = 3.3 V.                                                                  | _    | +/- 0.1   | _    | dB   |

#### Note:

- 1. For regulatory compliance please refer to the official certification test reports

- 2. Supported transmit power levels are determined by the ordering part number (OPN). Transmit power ratings for all devices covered in this data sheet can be found in the TX Power column of the Ordering Information Table.

- 3. The maximum TXP to comply with ETSI PSD and EIRP limits depend on antenna gain which in turn depend on the end product mechanical design. In optimal conditions the module is compliant to the ETSI PSD and EIRP limits at maximum TXP of 8.2 dBm. End product manufacturer must ensure compliance to the limits for CE marking of the end product.

#### 4.1.6 RF Receiver General Characteristics for the 2.4 GHz Band

Unless otherwise indicated, typical conditions are: T<sub>A</sub> = 25 °C, VDD = 3.0V. RF center frequency 2.45 GHz.

Table 4.6. RF Receiver General Characteristics for the 2.4 GHz Band

| Parameter                 | Symbol             | Test Condition | Min  | Тур | Max    | Unit |

|---------------------------|--------------------|----------------|------|-----|--------|------|

| RF tuning frequency range | F <sub>RANGE</sub> |                | 2400 | _   | 2483.5 | MHz  |

#### 4.1.7 RF Receiver Characteristics for Bluetooth Low Energy at 1 Mbps

Unless otherwise indicated, typical conditions are:  $T_A$  = 25 °C, VDD = 3.0V. RF center frequency 2.45 GHz.

Table 4.7. RF Receiver Characteristics for Bluetooth Low Energy at 1 Mbps

| Parameter                                        | Symbol              | Test Condition                                                                               | Min | Тур   | Max | Unit |

|--------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------|-----|-------|-----|------|

| Rx Max Strong Signal Input<br>Level for 0.1% BER | RX <sub>SAT</sub>   | Signal is reference signal, packet length is 37 bytes <sup>1</sup>                           | _   | 10    | _   | dBm  |

| Sensitivity                                      | SENS                | Signal is reference signal, 37 byte payload <sup>1</sup>                                     | _   | -97   | _   | dBm  |

|                                                  |                     | With non-ideal signals <sup>2</sup> 1                                                        | _   | -96.5 | Max | dBm  |

| Signal to co-channel interferer                  | C/I <sub>CC</sub>   | (see notes) <sup>1 3</sup>                                                                   | _   | +6.6  | _   | dB   |

| N ± 1 Adjacent channel selectivity               | C/I <sub>1</sub>    | Interferer is reference signal at +1 MHz offset <sup>1 4 3 5</sup>                           | _   | -8.3  | _   | dB   |

|                                                  |                     | Interferer is reference signal at -1 MHz offset <sup>1 4 3 5</sup>                           | _   | -8.7  |     | dB   |

| N ± 2 Alternate channel selectivity              | C/I <sub>2</sub>    | Interferer is reference signal at +2 MHz offset <sup>1 4 3 5</sup>                           | _   | -42.1 | _   | dB   |

|                                                  |                     | Interferer is reference signal at -2 MHz offset <sup>1 4 3 5</sup>                           | _   | -48.9 | _   | dB   |

| N ± 3 Alternate channel selectivity              | C/I <sub>3</sub>    | Interferer is reference signal at +3 MHz offset <sup>1 4 3 5</sup>                           | _   | -42.4 | _   | dB   |

|                                                  |                     | Interferer is reference signal at -3 MHz offset <sup>1 4 3 5</sup>                           | _   | -54.8 | Max | dB   |

| Selectivity to image frequency                   | C/I <sub>IM</sub>   | Interferer is reference signal at image frequency with 1 MHz precision <sup>1 5</sup>        | _   | -42.1 | _   | dB   |

| Selectivity to image frequency ± 1 MHz           | C/I <sub>IM_1</sub> | Interferer is reference signal at image frequency +1 MHz with 1 MHz precision <sup>1 5</sup> | _   | -42.4 | _   | dB   |

|                                                  |                     | Interferer is reference signal at image frequency -1 MHz with 1 MHz precision <sup>1 5</sup> | _   | -8.3  |     | dB   |

| Intermodulation performance                      | IM                  | n = 3 <sup>6</sup>                                                                           | _   | -23   | _   | dBm  |

- 1.0.1% Bit Error Rate.

- 2. With non-ideal signals as specified in Bluetooth Test Specification RF-PHY.TS.5.0.1 section 4.7.1

- 3. Desired signal -67 dBm.

- 4. Desired frequency 2402 MHz ≤ Fc ≤ 2480 MHz.

- 5. With allowed exceptions.

- 6. As specified in Bluetooth Core specification version 5.1, Vol 6, Part A, Section 4.4

#### 4.1.8 RF Receiver Characteristics for Bluetooth Low Energy at 2 Mbps

Unless otherwise indicated, typical conditions are:  $T_A$  = 25 °C, VDD = 3.0V. RF center frequency 2.45 GHz.

Table 4.8. RF Receiver Characteristics for Bluetooth Low Energy at 2 Mbps

| Parameter                              | Symbol              | Test Condition                                                                               | Min | Тур   | Max                                       | Unit |

|----------------------------------------|---------------------|----------------------------------------------------------------------------------------------|-----|-------|-------------------------------------------|------|

| Max usable receiver input level        | SAT                 | Signal is reference signal, packet length is 37 bytes <sup>1</sup>                           | _   | 10    | _                                         | dBm  |

| Sensitivity                            | SENS                | Signal is reference signal, 37 byte payload <sup>1</sup>                                     | _   | -93.9 | _                                         | dBm  |

|                                        |                     | With non-ideal signals <sup>2</sup> 1                                                        | _   | -93.4 | _                                         | dBm  |

| Signal to co-channel interferer        | C/I <sub>CC</sub>   | (see notes) <sup>1 3</sup>                                                                   | _   | +6.0  | _                                         | dB   |

| N ± 1 Adjacent channel selectivity     | C/I <sub>1</sub>    | Interferer is reference signal at +2 MHz offset <sup>1 4 3 5</sup>                           | _   | -8.0  | _                                         | dB   |

|                                        |                     | Interferer is reference signal at -2 MHz offset <sup>1 4 3 5</sup>                           | _   | -8.8  |                                           | dB   |

| N ± 2 Alternate channel selectivity    | C/I <sub>2</sub>    | Interferer is reference signal at +4 MHz offset <sup>1 4 3 5</sup>                           | _   | -42.2 | _                                         | dB   |

|                                        |                     | Interferer is reference signal at -4 MHz offset <sup>1 4 3 5</sup>                           | _   | -50.3 | _                                         | dB   |

| N ± 3 Alternate channel selectivity    | C/I <sub>3</sub>    | Interferer is reference signal at +6 MHz offset <sup>1 4 3 5</sup>                           | _   | -54.4 | _                                         | dB   |

|                                        |                     | Interferer is reference signal at -6 MHz offset <sup>1 4 3 5</sup>                           | _   | -55.4 | Max — — — — — — — — — — — — — — — — — — — | dB   |

| Selectivity to image frequency         | C/I <sub>IM</sub>   | Interferer is reference signal at image frequency with 1 MHz precision 1 5                   | _   | -8.0  | _                                         | dB   |

| Selectivity to image frequency ± 1 MHz | C/I <sub>IM_1</sub> | Interferer is reference signal at image frequency +2 MHz with 1 MHz precision <sup>1 5</sup> | _   | -42.2 | _                                         | dB   |

|                                        |                     | Interferer is reference signal at image frequency -2 MHz with 1 MHz precision <sup>1 5</sup> | _   | +6.0  |                                           | dB   |

| Intermodulation performance            | IM                  | n = 3 <sup>6</sup>                                                                           | _   | -22.3 | _                                         | dBm  |

- 1.0.1% Bit Error Rate.

- 2. With non-ideal signals as specified in Bluetooth Test Specification RF-PHY.TS.5.0.1 section 4.7.1

- 3. Desired signal -67 dBm.

- 4. Desired frequency 2402 MHz  $\leq$  Fc  $\leq$  2480 MHz.

- 5. With allowed exceptions.

- 6. As specified in Bluetooth Core specification version 5.1, Vol 6, Part A, Section 4.4

#### 4.1.9 RF Receiver Characteristics for Bluetooth Low Energy at 500 kbps

Unless otherwise indicated, typical conditions are:  $T_A$  = 25 °C, VDD = 3.0V. RF center frequency 2.45 GHz.

Table 4.9. RF Receiver Characteristics for Bluetooth Low Energy at 500 kbps

| Parameter                              | Symbol              | Test Condition                                                                                      | Min | Тур    | Max | Unit |

|----------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------|-----|--------|-----|------|

| Max usable receiver input level        | SAT                 | Signal is reference signal, packet length is 37 bytes <sup>1</sup>                                  | _   | 10     | _   | dBm  |

| Sensitivity                            | SENS                | Signal is reference signal <sup>1</sup>                                                             | _   | -100.1 | _   | dBm  |

|                                        |                     | With non-ideal signals <sup>2</sup> 1                                                               | _   | -99.5  | _   | dBm  |

| Signal to co-channel interferer        | C/I <sub>CC</sub>   | (see notes) <sup>1 3</sup>                                                                          | _   | +2.1   | _   | dB   |

| N ± 1 Adjacent channel selectivity     | C/I <sub>1</sub>    | Interferer is reference signal at +1 MHz offset <sup>1 4 3 5</sup>                                  | _   | -9.0   | _   | dB   |

|                                        |                     | Interferer is reference signal at -1 MHz offset <sup>1 4 3 5</sup>                                  | _   | -9.5   | _   | dB   |

| N ± 2 Alternate channel selectivity    | C/I <sub>2</sub>    | Interferer is reference signal at +2 MHz offset <sup>1</sup> <sup>4</sup> <sup>3</sup> <sup>5</sup> | _   | -44.4  | _   | dB   |

|                                        |                     | Interferer is reference signal at -2 MHz offset <sup>1</sup> <sup>4</sup> <sup>3</sup> <sup>5</sup> | _   | -51.9  | _   | dB   |

| N ± 3 Alternate channel selectivity    | C/I <sub>3</sub>    | Interferer is reference signal at +3 MHz offset <sup>1 4 3 5</sup>                                  | _   | -44.3  | _   | dB   |

|                                        |                     | Interferer is reference signal at -3 MHz offset <sup>1 4 3 5</sup>                                  | _   | -58.3  | _   | dB   |

| Selectivity to image frequency         | C/I <sub>IM</sub>   | Interferer is reference signal at image frequency with 1 MHz precision <sup>15</sup>                | _   | -44.4  | _   | dB   |

| Selectivity to image frequency ± 1 MHz | C/I <sub>IM_1</sub> | Interferer is reference signal at image frequency +1 MHz with 1 MHz precision <sup>1 5</sup>        | _   | -44.3  | _   | dB   |

|                                        |                     | Interferer is reference signal at image frequency -1 MHz with 1 MHz precision <sup>1 5</sup>        | _   | -9.0   | _   | dB   |

- 1.0.1% Bit Error Rate.

- 2. With non-ideal signals as specified in Bluetooth Test Specification RF-PHY.TS.5.0.1 section 4.7.1

- 3. Desired signal -72 dBm.

- 4. Desired frequency 2402 MHz ≤ Fc ≤ 2480 MHz.

- 5. With allowed exceptions.

#### 4.1.10 RF Receiver Characteristics for Bluetooth Low Energy at 125 kbps

Unless otherwise indicated, typical conditions are:  $T_A$  = 25 °C, VDD = 3.0V. RF center frequency 2.45 GHz.

Table 4.10. RF Receiver Characteristics for Bluetooth Low Energy at 125 kbps

| Parameter                              | Symbol              | Test Condition                                                                                      | Min | Тур    | Max | Unit |

|----------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------|-----|--------|-----|------|

| Max usable receiver input level        | SAT                 | Signal is reference signal, packet length is 37 bytes <sup>1</sup>                                  | _   | 10     | _   | dBm  |

| Sensitivity                            | SENS                | Signal is reference signal <sup>1</sup>                                                             | _   | -104.4 | _   | dBm  |

|                                        |                     | With non-ideal signals <sup>2</sup> 1                                                               | _   | -104.1 | _   | dBm  |

| Signal to co-channel interferer        | C/I <sub>CC</sub>   | (see notes) <sup>1 3</sup>                                                                          | _   | +0.8   | _   | dB   |

| N ± 1 Adjacent channel selectivity     | C/I <sub>1</sub>    | Interferer is reference signal at +1 MHz offset <sup>1 4 3 5</sup>                                  | _   | -13.1  | _   | dB   |

|                                        |                     | Interferer is reference signal at -1 MHz offset <sup>1</sup> <sup>4</sup> <sup>3</sup> <sup>5</sup> | _   | -13.6  | _   | dB   |

| N ± 2 Alternate channel selectivity    | C/I <sub>2</sub>    | Interferer is reference signal at +2 MHz offset <sup>1 4 3 5</sup>                                  | _   | -49.5  | _   | dB   |

|                                        |                     | Interferer is reference signal at -2 MHz offset <sup>1 4 3 5</sup>                                  | _   | -56.9  | _   | dB   |

| N ± 3 Alternate channel selectivity    | C/I <sub>3</sub>    | Interferer is reference signal at +3 MHz offset <sup>1 4 3 5</sup>                                  | _   | -47.0  | _   | dB   |

|                                        |                     | Interferer is reference signal at -3 MHz offset <sup>1 4 3 5</sup>                                  | _   | -63.1  | _   | dB   |

| Selectivity to image frequency         | C/I <sub>IM</sub>   | Interferer is reference signal at image frequency with 1 MHz precision <sup>15</sup>                | _   | -49.5  | _   | dB   |

| Selectivity to image frequency ± 1 MHz | C/I <sub>IM_1</sub> | Interferer is reference signal at image frequency +1 MHz with 1 MHz precision <sup>1 5</sup>        | _   | -47.0  | _   | dB   |

|                                        |                     | Interferer is reference signal at image frequency -1 MHz with 1 MHz precision <sup>1 5</sup>        | _   | -13.1  | _   | dB   |

- 1.0.1% Bit Error Rate.

- 2. With non-ideal signals as specified in Bluetooth Test Specification RF-PHY.TS.5.0.1 section 4.7.1

- 3. Desired signal -79 dBm.

- 4. Desired frequency 2402 MHz ≤ Fc ≤ 2480 MHz.

- 5. With allowed exceptions.

## 4.1.11 High-Frequency Crystal

## Table 4.11. High-Frequency Crystal

| Parameter                   | Symbol                  | Test Condition                     | Min | Тур  | Max | Unit |

|-----------------------------|-------------------------|------------------------------------|-----|------|-----|------|

| Crystal frequency           | f <sub>HFXTAL</sub>     |                                    | _   | 38.4 | _   | MHz  |

| Initial calibrated accuracy | ACC <sub>HFXTAL</sub>   |                                    | -10 | _    | +10 | ppm  |

| Temperature drift           | DRIFT <sub>HFXTAL</sub> | Across specified temperature range | -30 | _    | +30 | ppm  |

## 4.1.12 **GPIO Pins**

Unless otherwise indicated, typical conditions are: VDD = 3.0 V.

Table 4.12. GPIO Pins

| Parameter                            | Symbol                 | Test Condition                                                                                                          | Min       | Тур  | Max       | Unit |

|--------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------|------|-----------|------|

| Leakage current                      | I <sub>LEAK_IO</sub>   | MODEx = DISABLED, VDD = 1.71V                                                                                           | _         | 1.9  | _         | nA   |

|                                      |                        | MODEx = DISABLED, VDD = 3.0<br>V                                                                                        | _         | 2.5  | _         | nA   |

|                                      |                        | MODEx = DISABLED, VDD = 3.8<br>V T <sub>A</sub> = 125 °C                                                                | _         |      | 200       | nA   |

| Input low voltage                    | V <sub>IL</sub>        | Any GPIO pin and RESETn                                                                                                 | _         | _    | 0.3 * VDD | V    |

| Input high voltage                   | V <sub>IH</sub>        | Any GPIO pin and RESETn                                                                                                 | 0.7 * VDD | _    | _         | V    |

| Output low voltage                   | V <sub>OL</sub>        | Sinking 20mA, VDD = 3.0 V                                                                                               | _         | _    | 0.2 * VDD | V    |

|                                      |                        | Sinking 8mA, VDD = 1.62 V                                                                                               | _         | _    | 0.4 * VDD | V    |

| Output high voltage                  | V <sub>OH</sub>        | Sourcing 20mA, VDD = 3.0 V                                                                                              | 0.8 * VDD | _    | _         | V    |

|                                      |                        | Sourcing 8mA, VDD = 1.62 V                                                                                              | 0.6 * VDD | _    | _         | V    |

| GPIO rise time                       | T <sub>GPIO_RISE</sub> | VDD = 3.0V, C <sub>load</sub> = 50pF, SLEW-<br>RATE = 4, 10% to 90%                                                     | _         | 8.4  | _         | ns   |

|                                      |                        | VDD = 1.7V, C <sub>load</sub> = 50pF, SLEW-<br>RATE = 4, 10% to 90%                                                     | _         | 13   | _         | ns   |

| GPIO fall time                       | T <sub>GPIO_FALL</sub> | VDD = 3.0V, C <sub>load</sub> = 50pF, SLEW-<br>RATE = 4, 90% to 10%                                                     | _         | 7.1  | _         | ns   |

|                                      |                        | VDD = 1.7V, C <sub>load</sub> = 50pF, SLEW-<br>RATE = 4, 90% to 10%                                                     | _         | 11.9 | _         | ns   |

| Pull up/down resistance <sup>1</sup> | R <sub>PULL</sub>      | Any GPIO pin. Pull-up to IOVDD:<br>MODEn = DISABLE DOUT=1.<br>Pull-down to VSS: MODEn =<br>WIREDORPULLDOWN DOUT =<br>0. | 35        | 44   | 55        | kΩ   |

| Maximum filtered glitch width        | T <sub>GF</sub>        | MODE = INPUT, DOUT = 1                                                                                                  | _         | 26   | _         | ns   |

| RESETn low time to ensure pin reset  | T <sub>RESET</sub>     |                                                                                                                         | 100       | _    | _         | ns   |

#### Note

1. GPIO and RESETn pull-ups connect to the VDD supply. Pull-downs on GPIO connect to VSS.

#### 4.1.13 Microcontroller Peripherals

The MCU peripherals set available in BGM210L modules includes:

- · 12-bit 1 Msps ADC

- · Analog Comparators

- · 16-bit and 32-bit Timers/Counters

- 24-bit Low Energy Timer for waveform generation

- · 32-bit Real Time Counter

- USART (UART/SPI/SmartCards/IrDA/I2S)

- I<sup>2</sup>C peripheral interfaces

- · 12 Channel Peripheral Reflex System

For details on their electrical performance, consult the relevant portions of Section 4 in the SoC datasheet.

To learn which GPIO ports provide access to every peripheral, consult Section 6.3 Analog Peripheral Connectivity and Section 6.4 Digital Peripheral Connectivity.

## 4.2 Typical Performance Curves

Typical performance curves indicate typical characterized performance under the stated conditions.

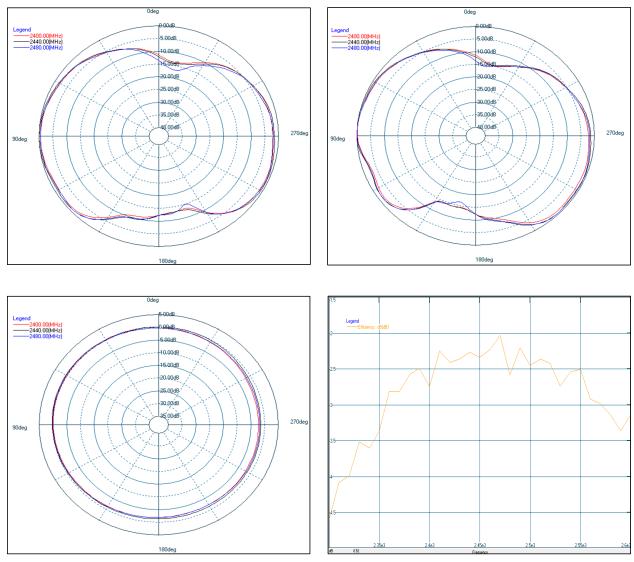

#### 4.2.1 Antenna Radiation and Efficiency

Typical BGM210L antenna radiation patterns and efficiency under optimal operating conditions are plotted in the figure below. Antenna gain and radiation patterns have a strong dependence on the size and shape of the application PCB the module is mounted on and, also, on the proximity of any mechanical design to the antenna.

Figure 4.1. Typical 2D Antenna Radiation Patterns and Efficiency

Top Left: Phi 0°, Top Right: Phi 90°, Bottom Left: Theta 90°, Bottom Right: Radiation Efficiency

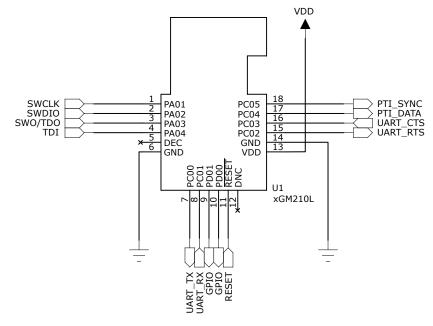

## 5. Reference Diagrams

A typical application circuit for the BGM210L module is shown below.

Figure 5.1. BGM210L Application Schematic

Interconnection labels correspond to supported pin functions described in 7.4 Debug, 7.5 Packet Trace Interface (PTI) and 6.4 Digital Peripheral Connectivity.

Placing the module horizontally on the end-application board permits access to all module pins. Placing it vertically restricts access to pins 13 through 18 only. The reference schematic above is applicable for the former case only. Refer to 7. Design Guidelines for more details.

#### 6. Pin Definitions

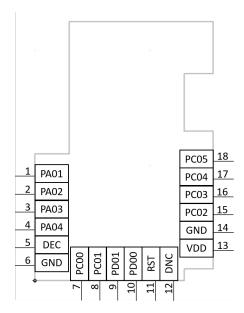

#### **6.1 Module Pinout**

Figure 6.1. BGM210L Lighting Module Pinout

The next table shows the BGM210L pinout and general descriptions for each pin. Refer to 6.2 Alternate Pin Functions, 6.3 Analog Peripheral Connectivity, and 6.4 Digital Peripheral Connectivity for details on functions and peripherals supported by GPIOs.

Table 6.1. BGM210L Lighting Module Pin Definitions

| Pin Name | Pin(s) | Description            | Pin Name | Pin(s) | Description       |

|----------|--------|------------------------|----------|--------|-------------------|

| PA01     | 1      | GPIO/Debug             | PA02     | 2      | GPIO/Debug        |

| PA03     | 3      | GPIO/Debug             | PA04     | 4      | GPIO/Debug        |

| DEC      | 5      | Decouple <sup>1</sup>  | GND      | 6      | Ground            |

| PC00     | 7      | GPIO                   | PC01     | 8      | GPIO              |

| PD01     | 9      | GPIO                   | PD00     | 10     | GPIO              |

| RESETn   | 11     | Reset Pin <sup>3</sup> | DNC      | 12     | Do not connect    |

| VDD      | 13     | VDD                    | GND      | 14     | Ground            |

| PC02     | 15     | GPIO <sup>2</sup>      | PC03     | 16     | GPIO <sup>2</sup> |

| PC04     | 17     | GPIO <sup>2</sup>      | PC05     | 18     | GPIO <sup>2</sup> |

- 1. Available for powering module through external PMIC. Should be left disconnected typically. Do not use Decouple supply to power external circuitry.

- 2. Internally terminated with series 56 ohm resistor.

- 3. Connected to pull-up resistor to VDD internally. External pull-up is not required.

#### 6.2 Alternate Pin Functions

Some GPIOs support alternate functions like debugging, wake-up from EM4, access to an external low frequency crystal, etc.. The following table shows which module pins have alternate capabilities and the functions they support. Refer to the SoC's reference manual for more information.

**Table 6.2. GPIO Alternate Functions Table**

| GPIO |               | Alternate Function |                 |  |  |  |

|------|---------------|--------------------|-----------------|--|--|--|

| PA01 | GPIO.SWCLK    |                    |                 |  |  |  |

| PA02 | GPIO.SWDIO    |                    |                 |  |  |  |

| PA03 | GPIO.SWV      | GPIO.TDO           | GPIO.TRACEDATA0 |  |  |  |

| PA04 | GPIO.TDI      | GPIO.TRACECLK      |                 |  |  |  |

| PC00 | GPIO.EM4WU6   |                    |                 |  |  |  |

| PD01 | LFXO.LFXTAL_I | LFXO.LF_EXTCLK     |                 |  |  |  |

| PD00 | LFXO.LFXTAL_O |                    |                 |  |  |  |

| PC05 | GPIO.EM4WU7   |                    |                 |  |  |  |

## 6.3 Analog Peripheral Connectivity

Many analog resources are routable and can be connected to numerous GPIO's. The table below indicates which peripherals are avaliable on each GPIO port. When a differential connection is being used Positive inputs are restricted to the EVEN pins and Negative inputs are restricted to the ODD pins. When a single ended connection is being used positive input is avaliable on all pins. See the device Reference Manual for more details on the ABUS and analog peripherals.

Table 6.3. ABUS Routing Table

| Peripheral | Signal  | Р    | Α   | Р    | C   | Р    | D   |

|------------|---------|------|-----|------|-----|------|-----|

|            |         | EVEN | ODD | EVEN | ODD | EVEN | ODD |

| ACMP0      | ana_neg | Yes  | Yes | Yes  | Yes | Yes  | Yes |

|            | ana_pos | Yes  | Yes | Yes  | Yes | Yes  | Yes |

| ACMP1      | ana_neg | Yes  | Yes | Yes  | Yes | Yes  | Yes |

|            | ana_pos | Yes  | Yes | Yes  | Yes | Yes  | Yes |

|            | ana_neg | Yes  | Yes | Yes  | Yes | Yes  | Yes |

|            | ana_pos | Yes  | Yes | Yes  | Yes | Yes  | Yes |

## 6.4 Digital Peripheral Connectivity

Many digital resources are routable and can be connected to numerous GPIO's. The table below indicates which peripherals are avaliable on each GPIO port.

Table 6.4. DBUS Routing

| Peripheral.Resource |           | PORT      |           |

|---------------------|-----------|-----------|-----------|

|                     | PA        | PC        | PD        |

| ACMP0.DIGOUT        | Available | Available | Available |

| ACMP1.DIGOUT        | Available | Available | Available |

| CMU.CLKIN0          |           | Available | Available |

| CMU.CLKOUT0         |           | Available | Available |

| CMU.CLKOUT1         |           | Available | Available |

| CMU.CLKOUT2         | Available |           |           |

| FRC.DCLK            |           | Available | Available |

| FRC.DFRAME          |           | Available | Available |

| FRC.DOUT            |           | Available | Available |

| I2C0.SCL            | Available | Available | Available |

| I2C0.SDA            | Available | Available | Available |

| I2C1.SCL            |           | Available | Available |

| I2C1.SDA            |           | Available | Available |

| LETIMER0.OUT0       | Available |           |           |

| LETIMER0.OUT1       | Available |           |           |

| PRS.ASYNCH0         | Available |           |           |

| PRS.ASYNCH1         | Available |           |           |

| PRS.ASYNCH10        |           | Available | Available |

| PRS.ASYNCH11        |           | Available | Available |

| PRS.ASYNCH2         | Available |           |           |

| PRS.ASYNCH3         | Available |           |           |

| PRS.ASYNCH4         | Available |           |           |

| PRS.ASYNCH5         | Available |           |           |

| PRS.ASYNCH6         |           | Available | Available |

| PRS.ASYNCH7         |           | Available | Available |

| PRS.ASYNCH8         |           | Available | Available |

| PRS.ASYNCH9         |           | Available | Available |

| PRS.SYNCH0          | Available | Available | Available |

| PRS.SYNCH1          | Available | Available | Available |

| PRS.SYNCH2          | Available | Available | Available |

| PRS.SYNCH3          | Available | Available | Available |

| Peripheral.Resource |           | PORT      |           |

|---------------------|-----------|-----------|-----------|

|                     | PA        | PC        | PD        |

| TIMER0.CC0          | Available | Available | Available |

| TIMER0.CC1          | Available | Available | Available |

| TIMER0.CC2          | Available | Available | Available |

| TIMER0.CDTI0        | Available | Available | Available |

| TIMER0.CDTI1        | Available | Available | Available |

| TIMER0.CDTI2        | Available | Available | Available |

| TIMER1.CC0          | Available | Available | Available |

| TIMER1.CC1          | Available | Available | Available |

| TIMER1.CC2          | Available | Available | Available |

| TIMER1.CDTI0        | Available | Available | Available |

| TIMER1.CDTI1        | Available | Available | Available |

| TIMER1.CDTI2        | Available | Available | Available |

| TIMER2.CC0          | Available |           |           |

| TIMER2.CC1          | Available |           |           |

| TIMER2.CC2          | Available |           |           |

| TIMER2.CDTI0        | Available |           |           |

| TIMER2.CDTI1        | Available |           |           |

| TIMER2.CDTI2        | Available |           |           |

| TIMER3.CC0          |           | Available | Available |

| TIMER3.CC1          |           | Available | Available |

| TIMER3.CC2          |           | Available | Available |

| TIMER3.CDTI0        |           | Available | Available |

| TIMER3.CDTI1        |           | Available | Available |

| TIMER3.CDTI2        |           | Available | Available |

| USART0.CLK          | Available | Available | Available |

| USART0.CS           | Available | Available | Available |

| USARTO.CTS          | Available | Available | Available |

| USART0.RTS          | Available | Available | Available |

| USART0.RX           | Available | Available | Available |

| USART0.TX           | Available | Available | Available |

| USART1.CLK          | Available |           |           |

| USART1.CS           | Available |           |           |

| USART1.CTS          | Available |           |           |

| USART1.RTS          | Available |           |           |

| USART1.RX           | Available |           |           |

| USART1.TX           | Available |           |           |

| Peripheral.Resource |    | PORT      |           |  |  |  |

|---------------------|----|-----------|-----------|--|--|--|

|                     | PA | PC        | PD        |  |  |  |

| USART2.CLK          |    | Available | Available |  |  |  |

| USART2.CS           |    | Available | Available |  |  |  |

| USART2.CTS          |    | Available | Available |  |  |  |

| USART2.RTS          |    | Available | Available |  |  |  |

| USART2.RX           |    | Available | Available |  |  |  |

| USART2.TX           |    | Available | Available |  |  |  |

## 7. Design Guidelines

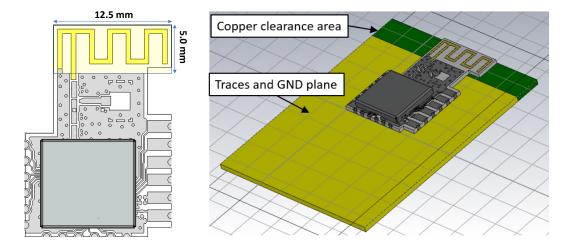

#### 7.1 Module Placement

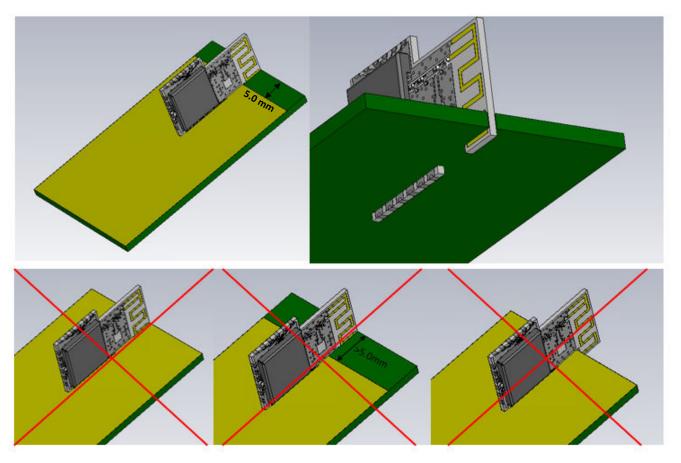

The BGM210L should be placed at the edge of the end-application PCB as seen below. The copper clearance area under the antenna must be void of traces or components to prevent parasitic loading or undesired coupling of signals or noise to the antenna. The width of the GND pour on the end-application PCB should match at least the width of the antenna (e.g. 12.5 mm or greater) to have negligible effect on antenna performance.

Figure 7.1. Inverted-F Antenna Clearance

BGM210L modules do not support the use of an external, alternative antenna. The U.FL connector land pattern on the top layer of the module should not be used, populated or tampered with.

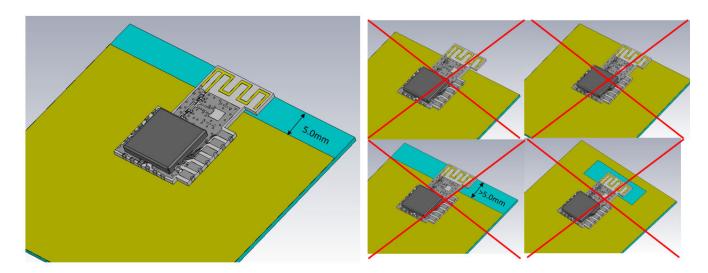

Figure 7.2 Horizontal Mounting on page 26 illustrates the placement recommended when mounting the module horizontally to an end-application PCB. It also shows examples of layout cases that will result in severe RF performance degradation for the module.

Figure 7.2. Horizontal Mounting

Vertical mounting provides mechanical design flexibility that could be advantageous for certain applications. Figure 7.3 Vertical Mounting on page 27 illustrates the placement recommended when mounting the module vertically to an end-application PCB. It also shows layout examples that will result in severe RF performance degradation for the module.

Notice that vertical mounting limits the number of pins available to interact with the module to six (VDD, GND and four GPIOs) which may be suitable for specific use cases only (e.g. to generate PWM outputs for LED control). The trade offs of vertical mounting should be carefully considered prior to choosing such arrangement.

Figure 7.3. Vertical Mounting

#### 7.2 Antenna Optimization

Due to the nature of PCB trace antennas, the BGM210L is sensitive to the thickness of the application PCB on which it is mounted, as well as to any plastics, metal or dielectric materials in close proximity to the antenna. The layout guide shown in Figure 7.2 Horizontal Mounting on page 26 is optimal for an application board thickness of 0.8 mm.

For cases where the application board is of a thickness different than the optimal, the impedance and performance of the antenna may be experimentally adjusted by

- 1. Cutting out the end-application PCB's FR4 material that is under the antenna, or by

- Adjusting the separation between the lower side of the antenna and the edge of the application board's GND plane underneath the module

Impedance and performance optimization can be verified by measuring RSSI or radiated output power until either is maximized.

#### 7.3 Reset

The BGM210L can be reset by pulling the RESET line low, by the internal watchdog timer, or by software command. All three methods are applicable when the module is mounted horizontally on a given end-application board and, hence, all module pins are accessible. When mounted vertically, however, only the second and third methods apply.

The reset state does not provide power saving functionality and it is not recommended as a means to conserve power.

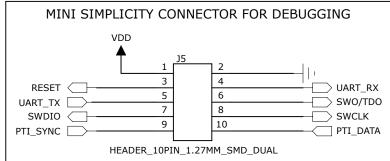

#### 7.4 Debug

See AN958: Debugging and Programming Interfaces for Custom Designs.

The BGM210L supports hardware debugging via 4-pin JTAG or 2-pin serial-wire debug (SWD) interfaces. It is recommended to expose the debug pins in your own hardware design for firmware update and debug purposes. The table below lists the required pins for JTAG and SWD debug interfacing, which are also presented in 6.2 Alternate Pin Functions.

If JTAG interfacing is enabled, the module must be power cycled to return to a SWD debug configuration if necessary.

Table 7.1. Debug Pins

| Pin Name | Pin Number | JTAG Signal | SWD Signal | Comments                                                                       |

|----------|------------|-------------|------------|--------------------------------------------------------------------------------|

| PA04     | 4          | TDI         | N/A        | This pin is disabled after reset. Once enabled the pin has a built-in pull-up. |

| PA03     | 3          | TDO         | N/A        | This pin is disabled after reset.                                              |

| PA02     | 2          | TMS         | SWDIO      | Pin is enabled after reset and has a built-in pull-up.                         |

| PA01     | 1          | TCK         | SWCLK      | Pin is enabled after reset and has a built-in pull-down.                       |

#### 7.5 Packet Trace Interface (PTI)

The BGM210L integrates a true PHY-level packet trace interface (PTI) peripheral that can capture packets non-intrusively to monitor and log device and network traffic without burdening processing resources in the module's SoC. The PTI generates two output signals that can serve as a powerful debugging tool, especially in conjunction with other hardware and software development tools available from Silicon Labs. The PTI\_DATA and PTI\_SYNC signals can be accessed through any GPIO on ports C and D (see FRC.DOUT and FRC.DFRAME peripheral resources in Table 6.4 DBUS Routing on page 23).

## 8. Package Specifications

## 8.1 Package Outline

Figure 8.1. Top and Side Views

Figure 8.2. Bottom View

NOTE: Solder paste thickness adds  $0.1 \pm 0.05$  mm to overall module height

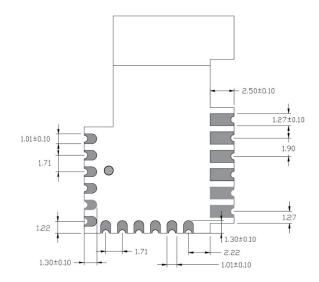

#### 8.2 PCB Land Pattern

Figure 8.3. Recommended Module PCB Land Pattern

Table 8.1. Pad Sizing and Location

| Pad Number | X Coordinate | Y Coordinate | Pad Dimensions |

|------------|--------------|--------------|----------------|

| 1          | 0.5          | 9.78         | 1.1 x 1.6      |

| 6          | 0.5          | 1.23         | 1.1 x 1.6      |

| 7          | 2.23         | 0.5          | 1.1 x 1.6      |

| 12         | 10.78        | 0.5          | 1.1 x 1.6      |

| 13         | 14.67        | 2.25         | 1.3 x 3.3      |

| 18         | 14.67        | 11.75        | 1.3 x 3.3      |

- 1. All dimensions in mm unless otherwise stated.

- 2. X and Y coordinates are specified relative to origo at indicated package corner in the figure above.

- 3. The module has a test point for VDD on the bottom layer at (X=2.65, Y=6.45). A keep-out area of 1.4 mm x 1.4 mm around this point is recommended to prevent the possibility of a short circuit.

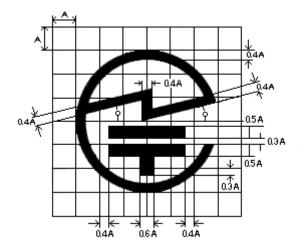

#### 8.3 Marking

The figure below shows the markings engraved on the RF shield of the module.

Figure 8.4. BGM210L Shield Marking

### **Mark Description**

The module shield marking includes the following:

- BGM210Lxxxxxxx Part number designation

- Model: BGM210L22F Model number designation

- QR Code: YYWWMMABCDE

- · YY Last two digits of the assembly year.

- WW Two-digit workweek when the device was assembled.

- MMABCDE Silicon Labs unit code

- YYWWTTTTTT

- YY Last two digits of the assembly year.

- WW Two-digit workweek when the device was assembled.

- TTTTTT Manufacturing trace code. The first letter is the device revision.

- Certification marks such as the CE logo, FCC and IC IDs, etc. will be engraved on the grayed out area or printed on the back side of the module, according to regulatory body requirements.

## 9. Soldering Recommendations

It is recommended that final PCB assembly of the BGM210L follows the industry standard as identified by the Institute for Printed Circuits (IPC). This product is assembled in compliance with the J-STD-001 requirements and the guidelines of IPC-AJ-820. Surface mounting of this product by the end user is recommended to follow IPC-A-610 to meet or exceed class 2 requirements.

#### **CLASS 1 General Electronic Products**

Includes products suitable for applications where the major requirement is function of the completed assembly.

#### **CLASS 2 Dedicated Service Electronic Products**

Includes products where continued performance and extended life is required, and for which uninterrupted service is desired but not critical. Typically the end-use environment would not cause failures.

#### **CLASS 3 High Performance/Harsh Environment Electronic Products**

Includes products where continued high performance or performance-on-demand is critical, equipment downtime cannot be tolerated, end-use environment may be uncommonly harsh, and the equipment must function when required, such as life support or other critical systems.

Note: General SMT application notes are provided in the AN1223 document.

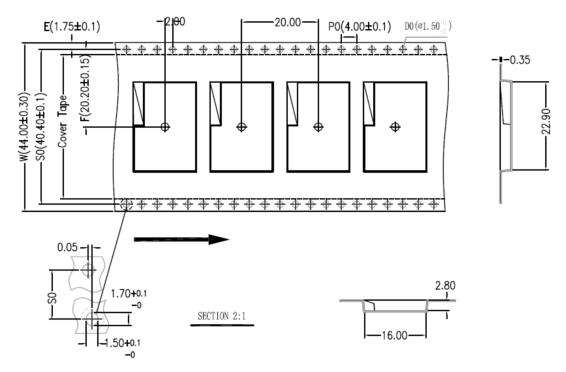

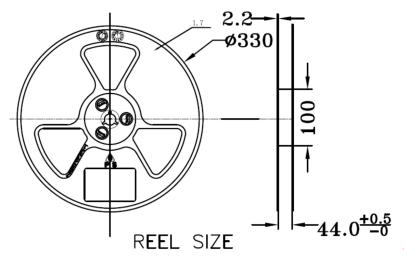

## 10. Tape and Reel

All dimensions are given in mm unless otherwise indicated.

Figure 10.1. Carrier Tape Dimensions

Figure 10.2. Reel Dimensions

#### 11. Certifications

This section details the regulatory certification status of the BGM210L modules in various regions. For certification purposes, the modules are mainly referred to by their formal Model Name of BGM210L22F.

The address of the modules' legal manufacturer and certification applicant is:

SILICON LABORATORIES FINLAND OY Alberga Business Park, Bertel Jungin aukio 3, 02600 Espoo, Finland

The BGM210L22F modules have Brand Name of "SILICON LABS".

#### 11.1 CE and UKCA

BGM210L modules have been tested against the relevant harmonized/designated standards and are in conformity with the essential requirements and other relevant requirements of the EU's Radio Equipment Directive (RED) (2014/53/EU) and of the UK's Radio Equipment Regulations (RER) (S.I. 2017/1206).

Every end-product integrating the BGM210L module will need to perform radio EMC tests on the whole assembly according to the ETSI 301 489-x relevant standard.

Furthermore, it is ultimately the responsibility of the manufacturers to ensure the compliance of their end-products as a whole. The specific product assembly is likely to have an impact on the RF radiated characteristics, when compared to the bare module. Hence, manufacturers should also carefully consider RF radiated testing with the final product assembly to confirm the compliance.

The modules are entitled to carry the CE and UKCA compliance marks, and a formal Declaration of Conformity (DoC) is available at the product web page which is reachable starting from https://www.silabs.com/ or upon request.

#### 11.2 FCC

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions:

- 1. This device may not cause harmful interference, and

- 2. This device must accept any interference received, including interference that may cause undesirable operation.

Any changes or modifications not expressly approved by Silicon Labs could void the user's authority to operate the equipment.

#### **FCC RF Radiation Exposure Statement:**

This equipment complies with FCC radiation exposure limits set forth for an uncontrolled environment. End users must follow the specific operating instructions for satisfying RF exposure compliance. This transmitter meets both portable and mobile requirements in accordance to the limits exposed in the RF Exposure Analysis. This transmitter must not be co-located or operating in conjunction with any other antenna or transmitter except in accordance with FCC multi-transmitter product procedures.

#### **OEM Responsibilities to comply with FCC Regulations:**

OEM integrator is responsible for testing their end-product for any additional compliance requirements needed with this module installed (for example, digital device emissions, PC peripheral requirements, etc.). Additionally, investigative measurements and spot checking are strongly recommended to verify that the full system compliance is maintained when the module is integrated, in accordance to the "Host Product Testing Guidance" in FCC's KDB 996369 D04 Module Integration Guide V01.

- In the typical case when the integral antenna of the BGM210L is used, a minimum separation distance of 12 mm must be maintained at all times between the human body and the radiator (antenna) to meet the SAR exemption for portable conditions.

- The transmitter module must not be co-located or operating in conjunction with any other antenna or transmitter except in accordance with FCC multi-transmitter product procedures.

#### **Important Note:**

In the event that these conditions cannot be met, then for the FCC authorization to remain valid the final product will have to undergo additional testing to evaluate the RF exposure, and a permissive change will have to be applied with the help of the customer's own Telecommunication Certification Body.

#### **End Product Labeling**

The variants of BGM210L Modules are labeled with their own FCC ID. If the FCC ID is not visible when the module is installed inside another device, then the outside of the device into which the module is installed must also display a label referring to the enclosed module. In that case, the final end product must be labeled in a visible area with the following:

#### "Contains Transmitter Module FCC ID: QOQMGM210L"

Or

#### "Contains FCC ID: QOQMGM210L"

The OEM integrator has to be aware not to provide information to the end user regarding how to install or remove this RF module or change RF related parameters in the user manual of the end product.

#### **Class B Device Notice**

**Note:** This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- · Reorient or relocate the receiving antenna

- · Increase the separation between the equipment and receiver

- · Connect the equipment into an outlet on a circuit different from that to which the receiver is connected

- Consult the dealer or an experienced radio/TV technician for help

#### 11.3 ISED Canada

#### **ISEDC**

This radio transmitter (IC: 5123A-MGM210L) has been approved by Industry Canada to operate with the embedded antenna. Any other antenna types are strictly prohibited for use with this device.

This device complies with Industry Canada's license-exempt RSS standards. Operation is subject to the following two conditions:

- 1. This device may not cause interference; and

- 2. This device must accept any interference, including interference that may cause undesired operation of the device

#### RF Exposure Statement

Exception from routine SAR evaluation limits are given in RSS-102 Issue 5.

The module meets the given requirements when the minimum separation distance to human body is 20 mm.

RF exposure or SAR evaluation is not required when the separation distance is same or more than stated above. If the separation distance is less than stated above the OEM integrator is responsible for evaluating the SAR.

#### **OEM Responsibilities to comply with IC Regulations**

The module has been certified for integration into products only by OEM integrators under the following conditions:

- The antenna must be installed such that a minimum separation distance as stated above is maintained between the radiator (antenna) and all persons at all times.

- The transmitter module must not be co-located or operating in conjunction with any other antenna or transmitter.

As long as the two conditions above are met, further transmitter testing will not be required. However, the OEM integrator is still responsible for testing their end-product for any additional compliance requirements required with this module installed (for example, digital device emissions, PC peripheral requirements, etc.).

#### **IMPORTANT NOTE**

In the event that these conditions cannot be met (for certain configurations or co-location with another transmitter), then the ISEDC authorization is no longer considered valid and the IC ID cannot be used on the final product. In these circumstances, the OEM integrator will be responsible for re-evaluating the end product (including the transmitter) and obtaining a separate ISEDC authorization.

#### **End Product Labeling**

The BGM210L module is labeled with its own IC ID. If the IC ID is not visible when the module is installed inside another device, then the outside of the device into which the module is installed must also display a label referring to the enclosed module. In that case, the final end product must be labeled in a visible area with the following:

"Contains Transmitter Module IC: 5123A-MGM210L"

or

#### "Contains IC: 5123A-MGM210L"

The OEM integrator has to be aware not to provide information to the end user regarding how to install or remove this RF module or change RF related parameters in the user manual of the end product.

#### **ISEDC** (Français)

Industrie Canada a approuvé l'utilisation de cet émetteur radio (IC: 5123A-MGM210L) en conjonction avec l'antenne intégrée. L'utilisation de tout autre type d'antenne avec ce composant est proscrite.

Ce composant est conforme aux normes RSS, exonérées de licence d'Industrie Canada. Son mode de fonctionnement est soumis aux deux conditions suivantes:

- 1. Ce composant ne doit pas générer d'interférences.

- 2. Ce composant doit pouvoir est soumis à tout type de perturbation y compris celle pouvant nuire à son bon fonctionnement.

#### **Déclaration d'exposition RF**

L'exception tirée des limites courantes d'évaluation SAR est donnée dans le document RSS-102 Issue 5.

Le module répondent aux exigences requises lorsque la distance minimale de séparation avec le corps humain est de 20 mm.