# SIC1181KQ / SIC1182KQ SCALE-iDriver Family

Up to 8 A Single Channel SiC MOSFET and IGBT Gate Driver for Automotive Applications Providing Advanced Active Clamping and Reinforced Isolation up to 1200 V

### **Product Highlights**

#### **Highly Integrated, Compact Footprint**

- ±8 A peak gate output current

- Integrated FluxLink™ technology providing reinforced isolation

- SiC MOSFET optimized Advanced Active Clamping

- Ultrafast short-circuit detection

- · UVLO primary and secondary side

- · Rail-to-rail stabilized output voltage

- · Unipolar supply voltage for secondary-side

- Up to 150 kHz switching frequency

- Propagation delay jitter ±5 ns

- -40 °C to +125 °C operating ambient temperature

- High common-mode transient immunity

- eSOP package with 9.5 mm creepage and clearance, CTI 600

#### **Protection / Safety Features**

- Undervoltage lock-out protection for primary and secondary-side including fault feedback

- Over-current detection for SiC MOSFETs with current-sense terminal

- Ultrafast short-circuit monitoring, turn-off and reporting

- · Overvoltage limitation during SiC MOSFET turn-off

#### **Full Safety and Regulatory Compliance**

- 100% production partial discharge test

- 100% production HIPOT compliance testing at 8000 V peak for 1 s

- Reinforced insulation pending VDE V 0884-11 certification

- UL 1577 recognized

- AEC Q-100 qualified for automotive grade level 1

#### **Green Package**

· Halogen free and RoHS compliant

#### **Applications**

- Electric vehicle BEV traction drives

- Hybrid electric vehicle PHEV traction drives

- Electric vehicle on-board and off-board chargers

#### **Description**

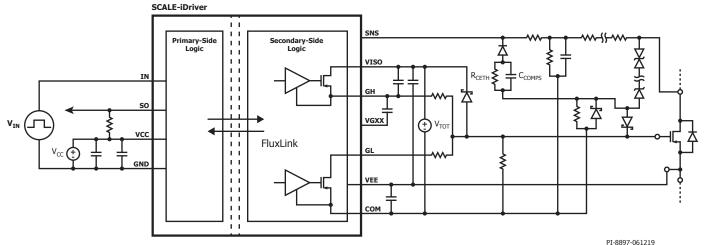

The SIC1181KQ and SIC1182KQ are single channel gate drivers for SiC MOSFETs. Reinforced galvanic isolation is provided by Power Integrations' revolutionary solid insulator FluxLink technology. Up to ±8 A peak output drive current enables the product to drive devices with nominal currents of up to 600 / 800 A (typical).

Additional features such as undervoltage lock-out (UVLO) for primary-side and secondary-side and rail-to-rail output with temperature and process compensated output impedance guarantee safe operation even in harsh conditions.

Furthermore, this gate driver IC comes along with short-circuit protection (at and during turn-on phase) as well as overvoltage limitation by AAC advanced active clamping (at turn-off phase) through a single sensing pin. For SIC MOSFET with current-sense terminal, an adjustable over-current detection can be realized.

#### **Product Portfolio**

| Product <sup>1</sup> | Peak Output<br>Drive Current | Switch Rating |

|----------------------|------------------------------|---------------|

| SIC1181KQ            | 8.0 A                        | 750 V         |

| SIC1182KQ            | 8.0 A                        | 1200 V        |

Table 1. SCALE-iDriver Portfolio.

Notes:

1. Package: eSOP-R16B.

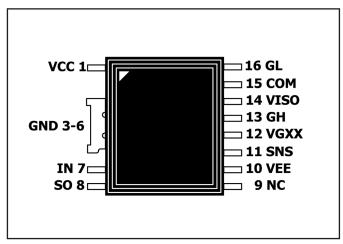

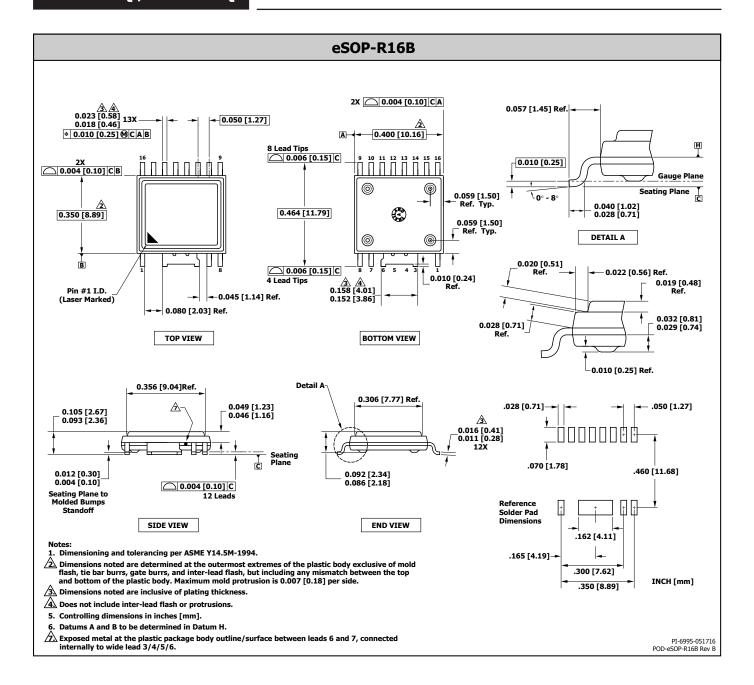

Figure 2. eSOP-R16B Package.

Figure 1. Typical Application Schematic.

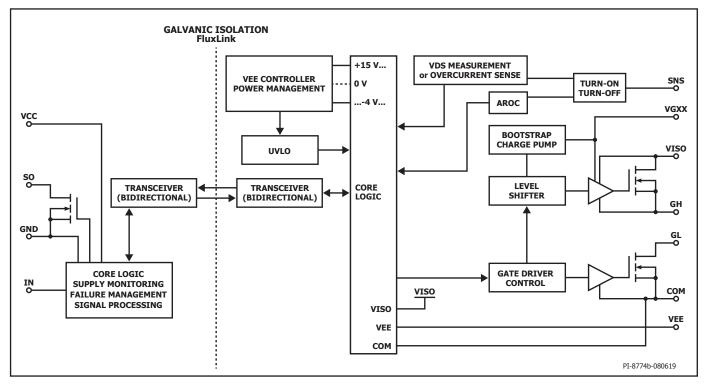

Figure 3. Functional Block Diagram.

### **Pin Functional Description**

#### VCC Pin (Pin 1)

This pin is the primary-side supply voltage connection.

#### GND Pin (Pin 3-6)

This pin is the connection for the primary-side ground potential. All primary-side voltages refer to this pin.

#### IN Pin (Pin 7)

This pin is the input for the logic command signal.

#### SO Pin (Pin 8)

This pin is the output for the logic fault signal (open drain).

#### NC Pins (Pin 9)

This pin must be un-connected. Minimum PCB pad size for soldering is required.

#### VEE Pin (Pin 10)

Common (MOSFET source) output supply voltage.

#### SNS Pin (Pin 11)

This pin is the sense input detecting short-circuit events at turn-on and limiting overvoltages at turn-off.

SiC MOSFET with sense function can be used with SNS pin as over-current monitor.

#### VGXX Pin (Pin 12)

This pin is the bootstrap and charge pump supply voltage source.

#### GH Pin (Pin 13)

This pin is the driver output-sourcing current (turn-on) connection.

#### VISO Pin (Pin 14)

This pin is the secondary-side positive supply voltage.

#### COM Pin (Pin 15)

This pin provides the secondary-side reference potential.

#### GL Pin (Pin 16)

This pin is the driver output-sinking current (turn-off) connection.

Figure 4. Pin Configuration.

#### SCALE-iDriver SIC118xKQ Functional Description

The single channel SCALE-iDriver™ family SIC118xKQ drives SiC MOSFET semiconductor devices with a blocking voltage of up to 1200 V and provides reinforced isolation between controller and the semiconductor device. The logic input (PWM) command signal applied via IN and the primary supply voltage supplied via VCC are both referenced to GND. The working status of the semiconductor device and SCALE-iDriver is monitored via SO.

Command signals are transferred from the primary (IN) to secondaryside via FluxLink isolation technology. GH supplies a positive gate voltage and charges the semiconductor gate during the turn-on process. GL supplies a negative gate voltage and discharges the gate during turn-off process.

Short-circuit protection as well as overvoltage limitation can be implemented by connecting a network between SNS and drain terminal of the semiconductor device. In case of a turn-on event SNS senses short-circuits, which will lead to a driver initiated turn-off to protect the semiconductor device from short-circuit damage. In case of a turn-off event SNS senses turn-off overvoltages and limits them by AAC advanced active clamping) to a save value below the semiconductor devices blocking voltage. In case the semiconductor device offers a current-sense terminal, an adjustable over-current detection can be realized as alternative to a short-circuit monitoring.

#### **Power Supplies**

The SIC118xKQ is equipped with an integrated power and voltage failure management. These features control IC power and voltage. It also generates and regulates secondary-side bipolar supply voltage. Two supply voltages are required. One for the primary-side  $(V_{vcc})$ , which powers the primary-side logic and communication with the secondary (insulated) side. The other supply voltage  $(V_{TOT})$  is required for the secondary-side as a unipolar voltage.  $V_{\text{TOT}}$  is applied between VISO and COM.  $V_{TOT}$  has to be insulated from the primary-side and should provide at least the same insulation capabilities as the SCALE-iDriver.  $\,V_{\text{\tiny TOT}}\,\text{should}$  have a low coupling capacitance to the primary or any other secondary-side. The positive gate-source voltage is provided by  $V_{_{VISO'}}$  which is internally generated and stabilized to 15 V (typically) with respect to VEE. The negative gate-source voltage is provided by  $\mathbf{V}_{_{\text{VFF}}}$  with respect to COM. Due to the limited current sourcing/sinking capabilities of VEE, any additional load needs to be applied between VISO and COM. No additional load between VISO and VEE or between VEE and COM is allowed.

#### Input and Fault Logic (Primary-Side)

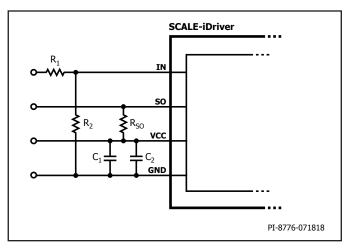

The input (IN) logic is designed to work directly with controllers using 5 V CMOS logic. It is recommended to use a pull-down resistor R1 close to the input pin of the SIC118xKQ.

If the physical distance between the controller and the SCALE-iDriver is large a line driver is recommended or increase the logic level to  $15\ V$ . For  $15\ V$  logic level, the resistive divider in Figure 6 is recommended. This solution adjusts the logic level as necessary and will also improve driver's noise immunity.

Gate driver commands are transferred from IN to GH (turn-on) and GL (turn-off) with a propagation delay  $t_{p(I|H)}$  and  $t_{p(H|I)}$ .

During normal operation, when there is no fault detected, the SO pin stays at high impedance (open drain). Any fault is reported by connecting the SO pin to GND. SO stays low as long as  $\rm V_{vcc}$  (primary-side) stays below  $\rm UVLO_{vcc}$ . If a short-circuit is detected or the supply voltage  $\rm V_{VISO'}$  (secondary-side) drops below  $\rm UVLO_{VISO'}$  the SO status changes with a delay time  $\rm t_{FAULT}$  and keeps status low for a time defined as  $\rm t_{SO}$ . In case of a fault condition the driver applies the off-state (GL is connected to COM). During the  $\rm t_{SO}$  period, command

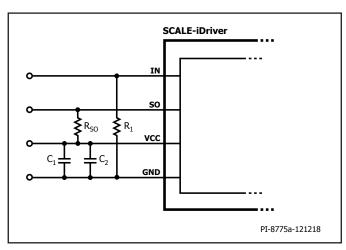

Figure 5. Recommended Circuitry for Standard 5 V IN Logic Level.

Figure 6. Recommended Circuitry for Increased IN Logic Levels. For R $_{_1}$  = 3.3 k $\Omega$  and R $_{_2}$  = 1.2 k $\Omega$  the IN Logic Level is 15 V.

signal transitions from IN are ignored. A new turn-on command transition is required before the driver will enter the on-state.

#### **Output (Secondary-Side)**

The gate of the semiconductor device to be driven can be connected to the SCALE-iDriver output via GH and GL, using two different resistor values. Turn-on gate resistor  $R_{\mbox{\tiny GON}}$  needs to be connected to the GH pin and turn-off gate resistor  $R_{\mbox{\tiny GOFF}}^{\mbox{\tiny GOFF}}$  to GL. If both gate resistors have the same value, GL and GH can be connected together. The SCALE-iDriver data sheet defines the  $\rm R_{GH}$  and  $\rm R_{GL}$  values as total resistances connected to the respective GH and GL. Note that most semiconductor device data sheets specify an internal gate resistor  $\boldsymbol{R}_{\text{GINT}}$  which is already integrated into the semiconductor device. In addition to  $R_{\text{GINT}}$ , external resistor devices  $R_{\text{GON}}$  and  $R_{\text{GOFF}}$  are specified to setup the gate current levels to the application requirements. Consequently,  $R_{\rm GH}$  is the sum of  $R_{\rm GON}$  and  $R_{\rm GINT}$  . Careful consideration should be given to the power dissipation and peak current associated with the external gate resistors. The GH pin output current source  $(I_{GH})$  of SIC118xKQ is capable of handling up to 7.8 A during turnon, and the GL pin output current source  $(I_{GI})$  is able to sink up to 7.3 A during turn-off. The SCALE-iDriver's internal resistances are described as  $\boldsymbol{R}_{\text{GHI}}$  and  $\boldsymbol{R}_{\text{GLI}}$  respectively. If the gate resistors for SCALE-iDriver attempt to draw a higher peak current, the peak current will be internally limited to a safe value.

## **SIC1181KQ / SIC1182KQ**

#### Safe Power-Up and Power-Down

It is recommended during power-up and power-down that the IN pin stays at logic low. Any supply voltage related to VCC, VISO, VEE and VGXX pins should be stabilized using ceramic capacitors  $C_1$ ,  $C_2$ ,  $C_{S1}$ ,  $C_{S2}$ , and  $C_{GXX}$  respectively as shown in Figure 5, 6, 7 and 8. After supply voltages reach their nominal values, the driver will begin to function after a time delay  $t_{CTART}$ .

#### **Short-Pulse Operation**

If command signals applied to IN are shorter than the minimum specified by  $t_{\mbox{\tiny GE(MIN)}},$  then SIC118xKQ output signals at GH and GL will extend to a value of  $t_{\mbox{\tiny GE(MIN)}}.$  The duration of pulses longer than  $t_{\mbox{\tiny GE(MIN)}}$  will not be changed.

#### **Short-Circuit Protection**

The SIC118xKQ uses the semiconductor device drain to source voltage to detect a short-circuit utilizing a sensing resistor network. With the help of a well stabilized  $V_{\mbox{\tiny VISO}}$  and a Schottky diode connected between semiconductor device gate and VISO the  $V_{\mbox{\tiny GS}}$  is clamped to the regulated VISO and the short-circuit current as well related SiC semiconductor energy will be limited.

During the off-state, SNS is internally connected to the COM pin. In case an optional filter-capacitor is applied between SNS pin and COM this capacitor is discharged.

When the driver is in turn-on transition or in on-state, the short-circuit detection algorithm through SNS is activated after an ASIC internally blanking time has elapsed. If now a voltage drop of about 0.4 V (typically) is detected at SNS referenced to VEE, this is interpreted as a detected short-circuit. The driver initiates a short-circuit turn-off without receiving a primary-side command. A fault command is sent to the primary side and SO is pulled to GND for typically  $10~\mu s$ . During this time the driver ignores any command signal at the IN pin. In parallel to the short-circuit turn-off transition phase, the SCALE-iDriver's internal Advanced Active Clamping overvoltage limitation scheme is activated.

### **V<sub>ps</sub>** Overvoltage Limitation (Advanced Active Clamping)

If the driver is in turn-off transition or in off-state the overvoltage limitation algorithm is activated at SNS and the internal reference is COM. In case a current of typically 440  $\mu A$  (turn-off transition) to 520  $\mu A$  (off-state) is feed to SNS, the driver will regulate the gate current to limit the turn-off di/dt and therefore the overvoltage at drain to source during turn-off.

#### **Over-Current Detection**

In case the semiconductor device offers a so called current-sense terminal, this signal can be fed into SNS with reference to VEE. As described in the short-circuit protection section, a voltage of about 0.4 V at SNS with reference to VEE will now be handled as an over-current. That leads to an over-current turn-off, following the same scheme as for a short-circuit condition.

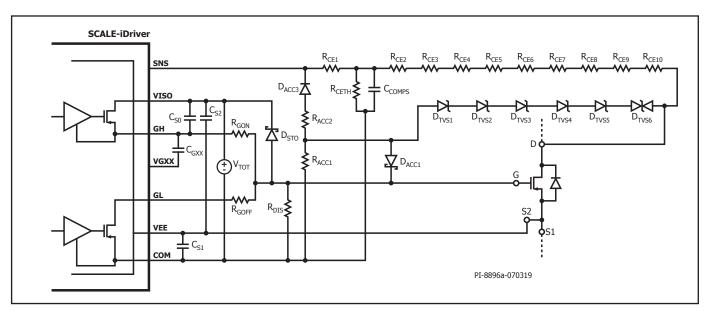

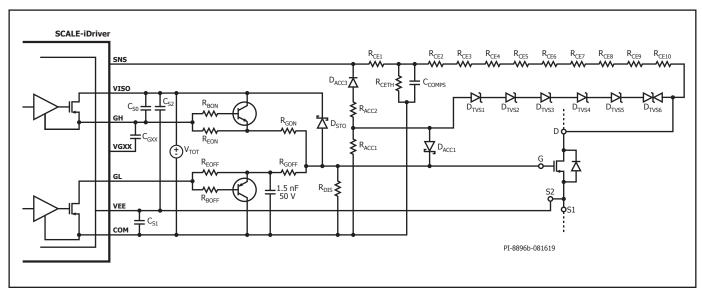

## **Application Example**

This example describes how to set up the SIC118xKQ to use overvoltage limitation with a chain of TVS-diodes between the SiC MOSFET device Drain and SIC118xKQ SNS pin as well as a short-circuit detection via a resistive network also connected to the SNS pin.

#### **Primary-Side**

For the input the circuitry of Figure 6 is recommended, when using 15 V input logic.  $R_{_1}$  and  $R_{_2}$  represent a voltage divider to get a 5 V signal at the IN pin. If additional filtering is required a capacitor  $C_{_F}$  can be placed in parallel to  $R_{_2}$  as depicted in Figure 7. The time constant  $\tau$  can be calculated by Equation (1). In case direct 5 V logic is used at the IN pin,  $R_{_2}$  is recommended at any case and  $R_{_1}$  can be reduced to  $100~\Omega$ .

$$t = \frac{R_1 \times R_2}{R_1 + R_2} \times C_F \tag{1}$$

The pull up resistor  $R_{SO}$  shall be connected to VCC and SO, with a value of 1  $k\Omega$ , to provide around 5 mA to SO (open drain) in a fault condition. The primary-side power supply is connected to VCC and COM, where  $C_{_1}$  is buffering  $V_{\text{VCC}}$  and  $C_{_2}$  acts as high frequency filter.

Figure 7. Primary-Side of Example Circuitry.

#### **Secondary-Side**

The secondary-side power supply is connected to VISO and COM as shown in Figure 8. It is for instance recommended for SiC MOSFET to use  $V_{\text{TOT}} = 20 \text{ V}$ , to get  $V_{\text{GH}} = 15 \text{ V}$  for turn-on referenced to VEE and  $V_{\text{GL}} = -5 \text{ V}$  referenced to VEE for turn-off, to avoid additional components. In any case parasitic turn-on effects need to get considered.

For each  $\mu$ C of semiconductor's gate charge a buffer capacitor of at least 3  $\mu$ F shall be placed at VEE to COM ( $C_{s1}$ ) as well as between VISO and VEE ( $C_{s2}$ ). A 10 nF capacitor is connected between GH and VGXX.

To ensure gate voltage stabilization and drain current limitation during short-circuit the gate is connected to  $V_{\rm VISO}$  through Schottky diode  $D_{\rm STO}$ .

To avoid parasitic turn-on during system power-on, the gate is connected to COM via a 22  $k\Omega$  resistor  $R_{\rm DIS}.$

The SNS pin has an alternating function that can be used for an overvoltage limitation, the so called Advanced Active Clamping, via a TVS-diodes chain during the turn-off transient as well as for a short-circuit detection via a resistive network during the turn-on transient.

The SiC MOSFET AAC is triggered with the current  $I_{\rm SNS}$  flowing into the SNS pin of the SIC118xKQ which gradually reduces the GL-current down to typically 20 mA with increased  $I_{\rm SNS}$ . This increases the effectiveness of the Active Clamping function provided by the TVS-diodes drastically. For example: the total voltage limit of the TVS chain is set to 900 V for a 1200 V-SiC MOSFET device.

During the turn-on transition the SNS pin serves the short-circuit detection and shut-down is triggered by a detection level referenced to COM of  $\rm V_{SNS}.$  The resistor chain to the Drain of the SiC MOSFET is consisting of the resistors from  $\rm R_{CE2}$  to  $\rm R_{CE10}.$  For example 2.43  $\rm M\Omega$  for a 1200 V-SiC MOSFET device.

If the SiC MOSFET has a sense terminal referenced to VEE which provides a fraction of the actual Source current this signal can also be fed back to the SNS pin via a shunt resistor. If here the SNS detection level of  $V_{\text{SNS}}$  is reached the SIC118xKQ will turn-off the SiC MOSFET and thus provide an over-current detection.

Figure 8. Secondary-Side of Example Circuitry without Booster Transistors.

Figure 9. Secondary-Side of Example Circuitry with Booster Transistors to Increase Gate Current.

#### Power Dissipation and IC Junction Temperature Estimation

The first step in designing the power semiconductor switch gate driver stage is to calculate the required gate power  $P_{DRV}$ . The power is calculated based on equation (2):

$$P_{DRV} = Q_{GATE} \times f_S \times V_{TOT}$$

(2)

Where,

$Q_{\text{GATE}}$  – Controlled power semiconductor switch gate charge derived for the particular gate potential range defined by  $V_{\text{TOT}}$ .

$f_{\rm S}-$  Switching frequency which is the same as applied to the IN pin of SCALE-iDriver.

V<sub>TOT</sub> - SCALE-iDriver secondary-side supply voltage.

In addition to  $P_{DRV'}$  the primary-side IC power dissipation  $P_p$  and the secondary-side IC power dissipation without capacitive load  $P_{SNL}$  must be considered according to Equation (3) and (4). Both are ambient temperature and switching frequency dependent (see Typical Performance Characteristics).

$$P_P = V_{VCC} \times I_{VCC} \tag{3}$$

$$P_{SNL} = V_{TOT} \times I_{VISO} \tag{4}$$

During IC operation, the  $P_{\tiny DRV}$  is shared between the external turn-on gate resistor  $R_{\tiny GIP}$  turn-off gate resistor  $R_{\tiny GLP}$  the internal gate resistor  $R_{\tiny GINT}$  of the power switch (if available) and internal driver resistances  $R_{\tiny GHI}$  and  $R_{\tiny GLI}$ .

For junction temperature estimation purposes, the dissipated power under load  $P_{\text{Ol}}$  inside the IC can be calculated according to Equation (5).

$$P_{OL} = 0.5 \times Q_{GATE} \times f_S \times V_{TOT} \times \left(\frac{R_{GHI}}{R_{GHI} + R_{GH}} + \frac{R_{GLI}}{R_{GLI} + R_{GL}}\right)$$

(5)

$R_{\text{GH}}$  and  $R_{\text{GL}}$  represent the sum of the external gate resistors ( $R_{\text{GON'}}$ ) as well as the internal gate resistance of the SiC MOSFET power semiconductor  $R_{\text{GINT}}$  as shown in Equation (6) and (7).

$$R_{GH} = R_{GON} + R_{GINT} \tag{6}$$

$$R_{GL} = R_{GOFF} + R_{GINT} \tag{7}$$

Total IC power dissipation  $P_{DIS}$  is estimated as per Equation (8) as sum of Equation (3), (4) and (5).

$$P_{DIS} = P_P + P_{SNL} + P_{OL}$$

(8)

The operating junction temperature  $T_j$  for a given ambient temperature  $T_A$  can be estimated with the thermal resistance from junction to ambient  $\theta_{1a}$  according to Equation (9).

$$T_{J} = \theta_{JA} \times P_{DIS} + T_{A} \tag{9}$$

## **SIC1181KQ / SIC1182KQ**

| Parameter                                | Symbol            | Conditions                                                             | Min  | Max                    | Units |

|------------------------------------------|-------------------|------------------------------------------------------------------------|------|------------------------|-------|

| Absolute Maximum Ratings <sup>1</sup>    |                   |                                                                        |      |                        |       |

| Primary-Side Supply Voltage <sup>2</sup> | V <sub>vcc</sub>  | VCC to GND                                                             | -0.5 | 6.5                    | V     |

| Secondary-Side Total Supply Voltage      | V <sub>TOT</sub>  | VISO to COM                                                            | -0.5 | 30                     | V     |

| Secondary-Side Positive Supply Voltage   | V <sub>VISO</sub> | VISO to VEE                                                            | -0.5 | 20                     | V     |

| Secondary-Side Negative Supply Voltage   | V <sub>VEE</sub>  | VEE to COM                                                             | -0.5 | 15                     | V     |

| Logic Input Voltage (command signal)     | V <sub>IN</sub>   | IN to GND                                                              | -0.5 | V <sub>vcc</sub> + 0.5 | V     |

| Logic Output Voltage (fault signal)      | V <sub>so</sub>   | SO to GND                                                              | -0.5 | V <sub>vcc</sub> + 0.5 | V     |

| Logic Output Current (fault signal)      | $I_{so}$          | Positive Current Flowing into the Pin                                  |      | 10                     | mA    |

| Switching Frequency                      | f <sub>s</sub>    |                                                                        |      | 150                    | kHz   |

| Storage Temperature                      | T <sub>s</sub>    |                                                                        | -65  | 150                    | °C    |

| Operating Junction Temperature           | T,                |                                                                        | -40  | 150³                   | °C    |

| Operating Ambient Temperature            | T <sub>A</sub>    |                                                                        | -40  | 125                    | °C    |

| Operating Case Temperature               | T <sub>c</sub>    |                                                                        | -40  | 125                    | °C    |

| Input Power Dissipation <sup>4</sup>     | P <sub>P</sub>    | V - EV V - 20 V                                                        |      | 188                    |       |

| Output Power Dissipation <sup>4</sup>    | P <sub>s</sub>    | $V_{VCC} = 5 \text{ V}, V_{TOT} = 28 \text{ V},$ $T_A = 25 \text{ °C}$ |      | 1602                   | mW    |

| Total IC Power Dissipation               | P <sub>DIS</sub>  | $f_s = 150 \text{ kHz}$                                                |      | 1790                   | mW    |

#### NOTES:

- 1. Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device.

- 2. Defined as peak voltage measured directly on VCC pin.

- 3. Transmission of command signals could be affected at junction temperatures higher than recommended.

- 4. Input Power Dissipation refers to Equation (3). Output Power Dissipation is secondary-side IC power dissipation without capacitive load (P<sub>SNL</sub>, Equation (4)) and dissipated power under load (P<sub>OL</sub>, Equation (5)). Total IC power dissipation is sum of P<sub>P</sub> and P<sub>S</sub>.

#### **Thermal Resistance**

Thermal Resistance: eSOP-R16B Package:  $(\theta_{JA}) \qquad \qquad 67 \text{ °C/W}^{\text{L}} \\ (\theta_{JC}) \qquad \qquad 34 \text{ °C/W}^{\text{2}}$

Notes:

- 1. 2 oz. (610 g/m<sup>2</sup>) copper clad.

- 2. The case temperature is measured at the plastic surface at the top of the package.

| Parameter                                                                                         | Symbol                        | Conditions $T_{j} = -40 \text{ °C to } +125 \text{ °C}$ See Note 1 (Unless Otherwise Specified) | Min  | Тур   | Max  | Units |

|---------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------|------|-------|------|-------|

| Recommended Operation                                                                             | Conditions                    |                                                                                                 |      |       |      |       |

| Primary-Side<br>Supply Voltage                                                                    | $V_{\rm vcc}$                 | VCC – GND                                                                                       | 4.75 |       | 5.25 | V     |

| Secondary-Side<br>Total Supply Voltage                                                            | $V_{\scriptscriptstyle TOT}$  | VISO - COM                                                                                      | 18   |       | 28   | V     |

| Logic Low Input Voltage                                                                           | $V_{_{\rm IL}}$               |                                                                                                 |      |       | 0.5  | V     |

| Logic High<br>Input Voltage                                                                       | $V_{_{\mathrm{IH}}}$          |                                                                                                 | 3.3  |       |      | V     |

| Switching Frequency                                                                               | $f_s$                         |                                                                                                 | 0    |       | 150  | kHz   |

| Operating IC Junction<br>Temperature                                                              | T,                            |                                                                                                 | -40  |       | 125  | °C    |

| Electrical Characteristics                                                                        |                               |                                                                                                 | I    |       | I    | ı     |

| Logic Low Input<br>Threshold Voltage                                                              | $V_{IN+LT}$                   |                                                                                                 | 0.6  | 1.25  | 1.8  | V     |

| Logic High Input<br>Threshold Voltage                                                             | $V_{_{\mathrm{IN+HT}}}$       |                                                                                                 | 1.7  | 2.2   | 3.05 | V     |

| Logic Input<br>Voltage Hysteresis                                                                 | $V_{_{\mathrm{IN+HS}}}$       | See Note 8                                                                                      | 0.1  |       |      | V     |

| Input Bias Current                                                                                | $\mathbf{I}_{\text{IN}}$      | $V_{IN} = 4 V$                                                                                  | 14   | 23    | 30   | μА    |

|                                                                                                   | $I_{ m VCC}$                  | $V_{IN} = 0 V$                                                                                  |      | 15    | 22   | - mA  |

| Supply Current                                                                                    |                               | $V_{IN} = 5 V$                                                                                  |      | 25    | 35   |       |

| (Primary-Side)                                                                                    |                               | $f_s = 20 \text{ kHz}$                                                                          |      | 22    | 30   | IIIA  |

|                                                                                                   |                               | f <sub>s</sub> = 75 kHz                                                                         |      | 25    | 35   |       |

|                                                                                                   |                               | $V_{IN} = 0 V$                                                                                  |      | 7     | 9    |       |

| Supply Current                                                                                    | T                             | V <sub>IN</sub> = 5 V                                                                           |      | 7.5   | 9    | m 1   |

| (Secondary-Side)                                                                                  | $I_{\scriptscriptstyle VISO}$ | f <sub>s</sub> = 20 kHz                                                                         |      | 8     | 10   | mA    |

|                                                                                                   |                               | f <sub>s</sub> = 75 kHz                                                                         |      | 11    | 14   |       |

|                                                                                                   |                               | Resume Operation                                                                                |      | 4.3   | 4.65 |       |

| Power Supply<br>Monitoring Threshold                                                              | UVLO <sub>vcc</sub>           | Suspend Operation                                                                               | 3.85 | 4.15  |      | V     |

| (Primary-Side)                                                                                    | VCC                           | Hysteresis<br>See Note 8                                                                        | 0.02 |       |      |       |

| Power Supply                                                                                      |                               | Resume Operation                                                                                |      | 12.85 | 13.5 |       |

| Power Supply Monitoring Threshold                                                                 | UVLO <sub>VISO</sub>          | Suspend Operation                                                                               | 11.7 | 12.35 |      | V     |

| (Secondary-Side,<br>Positive Rail V <sub>viso</sub> )                                             | VISO                          | Hysteresis<br>See Note 8                                                                        | 0.3  |       |      |       |

| Power Supply Monitoring<br>Blanking Time<br>(Secondary-Side,<br>Positive Rail V <sub>viso</sub> ) | UVLO <sub>VISO(BL)</sub>      | VISO Voltage Drop 13.5 V to 11.5 V<br>See Note 8                                                | 0.5  |       |      | μS    |

| Parameter                                               | Symbol                            | Conditions $T_{j} = -40 \text{ °C to } +125 \text{ °C}$ Conditions                                                                                                                                                                                                         | Min  | Тур | Max   | Units |

|---------------------------------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|-------|

|                                                         |                                   | See Note 1 (Unless Otherwise Specified)                                                                                                                                                                                                                                    |      |     |       |       |

| <b>Electrical Characteristics</b>                       | (cont.)                           |                                                                                                                                                                                                                                                                            |      |     |       |       |

| Secondary-Side<br>Positive Supply Voltage<br>Regulation | $V_{\text{VISO(HS)}}$             | $21 \text{ V} < \text{V}_{\text{TOT}} \le 30 \text{ V}:  \text{I}_{\text{VEE}}  \le 1500 \text{ μA}$ $\text{V}_{\text{TOT}} = 19 \text{ V},  \text{I}_{\text{VEE}}  \le 750 \text{ μA}$ $\text{V}_{\text{TOT}} = 18 \text{ V},  \text{I}_{\text{VEE}}  \le 400 \text{ μA}$ | 14.4 |     | 15.75 | V     |

| VEE Course Comphility                                   | т                                 | V <sub>TOT</sub> = 15 V, V <sub>VEE</sub> set to 0 V                                                                                                                                                                                                                       | 0.1  |     |       | A     |

| VEE Source Capability                                   | $I_{\text{VEE(SO)}}$              | $V_{TOT} = 25 \text{ V}, V_{EE} \text{ set to 7.5 V}, \text{ See Note 9}$                                                                                                                                                                                                  | 1.85 | 3.3 | 4.5   | - mA  |

| VEE Sink Capability                                     | $\boldsymbol{I}_{\text{VEE(SI)}}$ | $V_{TOT} = 25 \text{ V}, V_{EE} \text{ set to } 12.5 \text{ V}, \text{ See Note } 9$                                                                                                                                                                                       | 1.74 | 3.1 | 4.5   | mA    |

| SNS Fault Monitoring<br>Threshold                       | $V_{\scriptscriptstyle{\sf SNS}}$ | During turn-On transient,<br>referenced to COM, See Note 8                                                                                                                                                                                                                 |      | 400 |       | mV    |

| SNS Fault Monitoring<br>Blanking Time                   | t <sub>sns(BL)</sub>              | Time between SNS rises at V <sub>SNS</sub> and GH falls at 16 V                                                                                                                                                                                                            | 450  | 650 | 900   | ns    |

| SNS Current Required to Reduce GL-Current to 20 mA      | $\mathbf{I}_{SNS}$                | During turn-off transient, $T_1 = 25$ °C                                                                                                                                                                                                                                   |      | 535 |       | μА    |

| Turn-On<br>Propagation Delay                            | t <sub>P(LH)</sub>                | T <sub>J</sub> = 25 °C<br>See Note 3                                                                                                                                                                                                                                       | 250  | 265 | 305   | ns    |

|                                                         |                                   | T <sub>3</sub> = 125 °C<br>See Note 3                                                                                                                                                                                                                                      | 255  | 282 | 300   | 113   |

| Turn-Off                                                | t <sub>P(HL)</sub>                | T <sub>1</sub> = 25 °C<br>See Note 4                                                                                                                                                                                                                                       | 240  | 270 | 325   | ns    |

| Propagation Delay                                       |                                   | T <sub>J</sub> = 125 °C<br>See Note 4                                                                                                                                                                                                                                      | 250  | 288 | 320   | 113   |

| Minimum Turn-On and<br>Turn-Off Pulses                  | $t_{\text{GE(MIN)}}$              | See Note 8                                                                                                                                                                                                                                                                 |      |     | 650   | ns    |

|                                                         |                                   | No C <sub>G</sub> ,<br>See Note 5                                                                                                                                                                                                                                          |      | 22  | 45    |       |

| Output Rise Time                                        | t <sub>R</sub>                    | C <sub>G</sub> = 10 nF,<br>See Note 5                                                                                                                                                                                                                                      | 55   | 113 | 150   | ns    |

|                                                         |                                   | C <sub>G</sub> = 47 nF,<br>See Note 5                                                                                                                                                                                                                                      | 300  | 475 | 650   |       |

|                                                         |                                   | No C <sub>G</sub><br>See Note 6                                                                                                                                                                                                                                            |      | 18  | 45    |       |

| Output Fall Time                                        | t <sub>F</sub>                    | C <sub>G</sub> = 10 nF                                                                                                                                                                                                                                                     | 55   | 105 | 150   | ns    |

|                                                         |                                   | C <sub>G</sub> = 10 nF                                                                                                                                                                                                                                                     | 300  | 447 | 650   |       |

| Propagation Delay Jitter                                | $\Delta_{TP}$                     | See Note 8                                                                                                                                                                                                                                                                 |      | ±5  |       | ns    |

| Fault Signalization<br>Delay Time                       | t <sub>FAULT</sub>                | See Note 13                                                                                                                                                                                                                                                                |      | 0.8 | 1.4   | μS    |

| SO Fault<br>Signalization Time                          | t <sub>so</sub>                   |                                                                                                                                                                                                                                                                            | 6.8  | 10  | 13.4  | μS    |

| Power-On<br>Start-Up Time                               | t <sub>start</sub>                | See Note 7, 8                                                                                                                                                                                                                                                              |      |     | 10    | ms    |

|                                                          |                                                                                                                                                        |                                                                                                 |                         |      | 1    |       |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------|------|------|-------|

| Parameter                                                | Symbol                                                                                                                                                 | Conditions $T_{J} = -40 \text{ °C to } +125 \text{ °C}$ See Note 1 (Unless Otherwise Specified) | Min                     | Тур  | Max  | Units |

| Electrical Characteristics                               | (cont.)                                                                                                                                                |                                                                                                 |                         |      |      |       |

| Gate Sourcing                                            |                                                                                                                                                        | $V_{GH} \ge V_{TOT} - 11 \text{ V}$ $C_{G} = 470 \text{ nF}$ See Note 9                         | 3.6                     | 4.35 | 5.5  |       |

| Peak Current,<br>GH Pin                                  | $I_{\text{G(H)}} \\ R_{\text{G}} = 0 \ \Omega \\ T_{\text{A}} = 25 \ ^{\circ}\text{C} \\ f_{\text{S}} = 1 \ \text{kHz} \\ \text{See Notes 2, 8, 9} \\$ | $T_A = 25 ^{\circ}\text{C}$<br>$f_S = 1 \text{kHz}$                                             |                         | 7.8  |      | A     |

| Gate Sinking                                             |                                                                                                                                                        | $V_{GL} \le 7.5 \text{ V, } C_G = 470 \text{ nF}$<br>$V_{GL}$ referenced to COM                 | 3.6                     | 4.55 | 5.5  |       |

| Peak Current,<br>GL Pin                                  | $I_{G(L)}$                                                                                                                                             | $R_{\rm G} = 0~\Omega,$ $f_{\rm S} = 1~{\rm kHz}$ See Notes 2, 8                                |                         | 7.3  |      | A     |

| Internal Turn-On<br>Gate Resistance                      | R <sub>GHI</sub>                                                                                                                                       | $I_G = 250 \text{ mA}$ $V_{IN} = 5 \text{ V}$ See Note 9                                        |                         | 0.74 | 1.2  | Ω     |

| Turn-Off Internal<br>Gate Resistance                     | R <sub>GLI</sub>                                                                                                                                       | $I_{\rm G} = 250 \text{ mA}$ $V_{\rm IN} = 0 \text{ V}$ See Note 9                              |                         | 0.68 | 1.1  | Ω     |

| Turn-On Gate<br>Output Voltage<br>(Referred to COM Pin)  | V <sub>GH(ON)</sub>                                                                                                                                    | $I_G = 20 \text{ mA}$ $V_{IN} = 5 \text{ V}$ See Note 9                                         | V <sub>TOT</sub> - 0.04 |      |      | V     |

| Turn-Off Gate<br>Output Voltage<br>(Referred to COM Pin) | $V_{\text{GL(OFF)}}$                                                                                                                                   | $I_G = -20 \text{ mA}$ $V_{IN} = 5 \text{ V}$ See Note 9                                        |                         |      | 0.04 | V     |

| SO Output Voltage V <sub>SO(FAULT)</sub>                 |                                                                                                                                                        | Fault Condition, $I_{SO} = 3.4 \text{ mA} \\ V_{VCC} \ge 3.9 \text{ V}$                         |                         | 210  | 450  | mV    |

| Package Characteristics                                  | (See Notes 8,                                                                                                                                          | 10)                                                                                             |                         |      |      |       |

| Distance Through the<br>Insulation                       | DTI                                                                                                                                                    | Minimum Internal Gap (Internal Clearance)                                                       | 0.4                     |      |      | mm    |

| Minimum Air Gap<br>(Clearance)                           | L1 (IO1)                                                                                                                                               | Shortest Terminal-to-Terminal Distance<br>Through Air                                           | 9.5                     |      |      | mm    |

| Minimum External<br>Tracking (Creepage)                  | L2 (IO2)                                                                                                                                               | Shortest Terminal-to-Terminal Distance Across the Package Surface                               | 9.5                     |      |      | mm    |

| Tracking Resistance<br>(Comparative Tracking<br>Index)   | СТІ                                                                                                                                                    | DIN EN 60112 (VDE 0303-11): 2010-05 EN / IEC<br>60112:2003 + A1:2009                            | 600                     |      |      |       |

| Isolation Resistance,                                    | D                                                                                                                                                      | V <sub>IO</sub> = 500 V, T <sub>J</sub> = 25 °C<br>See Note 12                                  | 1012                    |      |      |       |

| Input to Output                                          | $R_{IO}$ $V_{IO} = 50$                                                                                                                                 | $V_{IO}$ = 500 V, 100 °C $\leq$ T $_{J}$ $\leq$ T $_{C(MAX)}$ See Note 12                       | 1011                    |      |      | Ω     |

| Isolation Capacitance,<br>Input to Output                | C <sub>IO</sub>                                                                                                                                        | See Note 12                                                                                     |                         | 1    |      | pF    |

|                                       |                   | 1                                                                                                            |                    |     |           |      | 1                   |

|---------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------|--------------------|-----|-----------|------|---------------------|

| Parameter                             | Symbol            | Conditions $T_{j} = -40 \text{ °C to } +125 \text{ °C}$ See Note 1 (Unless Otherwise Specified)              |                    | Min | Тур       | Max  | Units               |

| Package Insulation Chara              | cteristics        |                                                                                                              |                    |     |           |      |                     |

| Maximum RMS Working                   | N/                | SIC1181KQ                                                                                                    |                    |     |           | 531  | .,,                 |

| Isolation Voltage                     | V <sub>IORM</sub> | SIC1182KQ                                                                                                    |                    |     |           | 849  | V <sub>RMS</sub>    |

| Maximum Repetitive                    |                   | SIC1181KQ                                                                                                    |                    |     |           | 750  | M                   |

| Peak Isolation Voltage                | V <sub>IORM</sub> | SIC1182KQ                                                                                                    |                    |     |           | 1200 | V <sub>PEAK</sub>   |

| Input to Output Test<br>Peak Voltage  |                   | Method A, After Environmental Tests Subgroup 1, $V_{PD} = 1.6 \times$                                        | SIC1181KQ          |     |           | 1200 |                     |

|                                       |                   | V = 10 s (qualification)                                                                                     | SIC1182KQ          |     |           | 1920 |                     |

|                                       | $V_{PD}$          | Method A, After Input/Output<br>Safety Test Subgroup 2/3,                                                    | SIC1181KQ          |     |           | 900  | V <sub>PEAK</sub>   |

|                                       |                   | $V_{PD} = 1.2 \times V_{IORM}$ , t = 10 s, (qualification) Partial Discharge < 5 pC                          | SIC1182KQ          |     |           | 1440 | _                   |

|                                       |                   | $V_{PD} = 1.875 \times V_{IORM}, t = 1 s$                                                                    | SIC1181KQ          |     |           | 1407 |                     |

|                                       |                   |                                                                                                              | SIC1182KQ          |     |           | 2250 |                     |

| Maximum Transient                     | N.                | $V_{TEST} = V_{IOTM}$ , $t = 60 \text{ s}$                                                                   | SIC1181KQ          |     |           | 6000 | V                   |

| Peak Isolation Voltage                | V <sub>IOTM</sub> | (qualification),<br>t = 1 s (100% production)                                                                | SIC1182KQ          |     |           | 8000 | - V <sub>PEAK</sub> |

| Insulation Resistance                 | R <sub>s</sub>    | $V_{IO} = 500 \text{ V at T}_{S}$                                                                            |                    |     |           | >109 | Ω                   |

| Maximum Case<br>Temperature           | T <sub>s</sub>    |                                                                                                              |                    |     |           | 150  | °C                  |

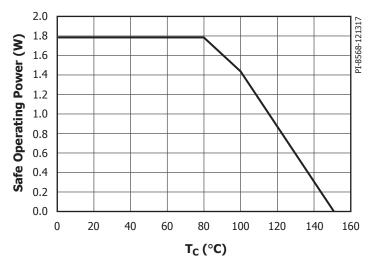

| Safety Total<br>Dissipated Power      | P <sub>s</sub>    | T <sub>A</sub> = 25 °C<br>Derating See Figure 10                                                             |                    |     |           | 1.79 | W                   |

| Pollution Degree                      |                   |                                                                                                              |                    |     | 2         |      |                     |

| Climatic Classification               |                   |                                                                                                              |                    |     | 40/125/21 |      |                     |

| RMS Withstanding<br>Isolation Voltage | V <sub>ISO</sub>  | $V_{TEST} = V_{ISO}$ , t = 60 s (qualific $V_{TEST} = 1.2 \times V_{ISO} = 6000 V_{RMS}$ , (100% production) | ation),<br>t = 1 s |     | 5000      |      | V <sub>RMS</sub>    |

Figure 10. Thermal Derating Curve Showing Dependence of Limited Dissipated Power  $P_S$  on Case Temperature  $T_C$  (DIN V VDE 0884-11).

Operation is allowed until reaching  $T_A$  and/or case temperature of 125 °C. Thermal stress beyond those values but below thermal derating curve may lead to permanent functional product damage. Operating beyond thermal SOP derating curve may affect product reliability.

#### NOTES:

- 1.  $V_{VCC} = 5 \text{ V}$ ,  $V_{TOT} = 25 \text{ V}$ .  $R_G = 5.6 \Omega$ , no  $C_G$ . The VGXX pin is connected to the G pin through a 10 nF capacitor. Typical values are defined at  $T_J = 25 \, ^{\circ}\text{C}$ ,  $f_S = 150 \, \text{kHz}$ , duty cycle = 50%. Positive currents are assumed to be flowing into pins.

- 2. Pulse width  $\leq$  10  $\mu$ s, duty cycle  $\leq$  1%. The maximum value is controlled by the ASIC to a safe level. The internal peak power is safely controlled for  $R_{_{G}} \geq 0$   $\Omega$  and power semiconductor module input gate capacitance  $C_{_{IES}} \leq 47$  nF. The gate sourcing peak current was determined by the time required to charge a gate capacitance of 388 nF with  $R_{_{GH}} = 0$  (and  $R_{_{GL}} = 4$   $\Omega$ ) from a voltage level of 2.5 V to a voltage level of 12.5 V. The gate sinking peak current was determined by the time required to discharge a gate capacitance of 388 nF with  $R_{_{GL}} = 0$  (and  $R_{_{GH}} = 4$   $\Omega$ ) from a voltage level of 22.5 V to a voltage level of 12.5 V.

- 3. V<sub>IN</sub> potential changes from 0 V to 5 V within 10 ns. Delay is measured from 50% voltage increase on IN pin to 10% voltage increase on G pin.

- 4. V<sub>IN</sub> potential changes from 5 V to 0 V within 10 ns. Delay is measured from 50% voltage decrease on IN pin to 10% voltage decrease on G pin.

- 5. Measured from 10% to 90% of V<sub>GF</sub> (C<sub>G</sub> simulates semiconductor gate capacitance). The V<sub>GF</sub> is measured across C<sub>G</sub>.

- 6. Measured from 90% to 10% of V<sub>GF</sub> (C<sub>G</sub> simulates semiconductor gate capacitance). The V<sub>GF</sub> is measured across C<sub>G</sub>.

- The amount of time after primary and secondary-side supply voltages (V<sub>VCC</sub> and V<sub>TOT</sub>) reach minimal required level for driver proper operation. No signal is transferred from primary to secondary-side during that time.

- 8. Guaranteed by design.

- 9. Positive current is flowing out of the pin.

- 10. Safety distances are application dependent and the creepage and clearance requirements should follow specific equipment isolation standards of an application. Board design should ensure that the soldering pads of an IC maintain required safety relevant distances.

- 11. Measured accordingly to IEC 61000-4-8 ( $f_s = 50$  Hz, and 60 Hz) and IEC 61000-4-9.

- 12. All pins on each side of the barrier tied together creating a two-terminal device.

- 13. The amount of time needed to transfer fault event (UVLO or SNS fault) from secondary-side to SO pin.

#### **MSL Table**

| Part Number | MSL Rating |

|-------------|------------|

| SIC118xKQ   | 3          |

### **ESD and Latch-Up Table**

| Test                     | Conditions   | Results                                              |

|--------------------------|--------------|------------------------------------------------------|

| Latch-up at 125 °C       | AEC-Q100-002 | $> \pm 100$ mA or $> 1.5 \times V_{MAX}$ on all pins |

| Human Body Model ESD     | AEC-Q100-002 | > ±2000 V on all pins                                |

| Charged Device Model ESD | AEC-Q100-002 | > ±500 V on all pins                                 |

### IEC 60664-1 Rating Table

| Parameter                   | Conditions                       | Specifications           |

|-----------------------------|----------------------------------|--------------------------|

| Basic Isolation Group       | Material Group                   | I                        |

|                             | Rated mains RMS voltage ≤ 150 V  | I - IV                   |

| Tookallakian Classification | Rated mains RMS voltage ≤ 300 V  | I - IV                   |

| Installation Classification | Rated mains RMS voltage ≤ 600 V  | I - IV                   |

|                             | Rated mains RMS voltage ≤ 1000 V | I - III (SIC1182KQ only) |

### **Electrical Characteristics (EMI) Table**

| Parameter                                        | Symbol             | Conditions                                                                       | Min | Тур      | Max        | Units  |

|--------------------------------------------------|--------------------|----------------------------------------------------------------------------------|-----|----------|------------|--------|

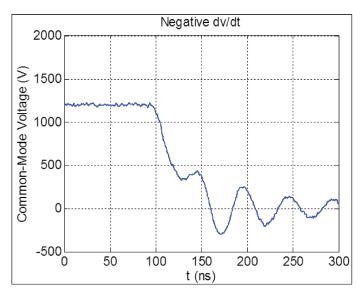

| Common-Mode<br>Transient Immunity,<br>Logic High | CM <sub>H</sub>    | Typical values measured according to Figure                                      |     | 25 / 50  | 100 / 100  | 101/ 0 |

| Common-Mode<br>Transient Immunity,<br>Logic Low  | $CM_L$             | 11 and Figure 12. Maximum values are design values assuming trapezoid waveforms. |     | -35 / 50 | -100 / 100 | kV/μs  |

| Variable Magnetic Field<br>Immunity              | H <sub>HPEAK</sub> | See Note 11                                                                      |     | 1000     |            | A/m    |

Figure 11. Applied Common Mode Pulses for Generating Positive dv/dt (Shown for SIC1182KQ).

Figure 12. Applied Common Mode Pulses for Generating Negative dv/dt (Shown for SIC1182KQ).

## **SIC1181KQ / SIC1182KQ**

## **Regulatory Information Table**

| Product   | VDE                                                                                                                                                           | UL                                                                       | CSA                                                                      |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------|

| SIC1181KQ | Pending certification to DIN VDE V<br>0884-11 (VDE V 0884-11):2017-01                                                                                         | UL recognition under UL 1577<br>Component Recognition Program            | CSA Component Acceptance Service<br>No. 5A                               |

|           | Reinforced insulation for Max. Transient<br>Isolation voltage 6 kV,<br>Max. Surge Isolation voltage 6 kV,<br>Max. Repetitive Peak Isolation voltage<br>750 V  | Single protection,<br>5000 V <sub>RMS</sub> dielectric voltage withstand | Single protection,<br>5000 V <sub>RMS</sub> dielectric voltage withstand |

|           | File No. Pending                                                                                                                                              | File No. E358471                                                         | File No. E358471                                                         |

| SIC1182KQ | Pending certification to DIN VDE V<br>0884-11 (VDE V 0884-11):2017-01                                                                                         | UL recognition under UL 1577<br>Component Recognition Program            | CSA Component Acceptance Service<br>No. 5A                               |

|           | Reinforced insulation for Max. Transient<br>Isolation voltage 8 kV,<br>Max. Surge Isolation voltage 8 kV,<br>Max. Repetitive Peak Isolation voltage<br>1200 V | Single protection,<br>5000 V <sub>RMS</sub> dielectric voltage withstand | Single protection,<br>5000 V <sub>RMS</sub> dielectric voltage withstand |

|           | File No. Pending                                                                                                                                              | File No. E358471                                                         | File No. E358471                                                         |

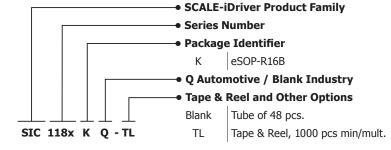

## **Part Ordering Information**

# Notes

| Revision | Notes                                      | Date  |

|----------|--------------------------------------------|-------|

| Α        | Code A release.                            | 10/19 |

| В        | Updated UL and CSA regulatory information. | 11/19 |

#### For the latest updates, visit our website: www.power.com

Power Integrations reserves the right to make changes to its products at any time to improve reliability or manufacturability. Power Integrations does not assume any liability arising from the use of any device or circuit described herein. POWER INTEGRATIONS MAKES NO WARRANTY HEREIN AND SPECIFICALLY DISCLAIMS ALL WARRANTIES INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF THIRD PARTY RIGHTS.

#### **Patent Information**

The products and applications illustrated herein (including transformer construction and circuits external to the products) may be covered by one or more U.S. and foreign patents, or potentially by pending U.S. and foreign patent applications assigned to Power Integrations. A complete list of Power Integrations patents may be found at www.power.com. Power Integrations grants its customers a license under certain patent rights as set forth at www.power.com/ip.htm.

#### **Life Support Policy**

POWER INTEGRATIONS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF POWER INTEGRATIONS. As used herein:

- 1. A Life support device or system is one which, (i) is intended for surgical implant into the body, or (ii) supports or sustains life, and (iii) whose failure to perform, when properly used in accordance with instructions for use, can be reasonably expected to result in significant injury or death to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Power Integrations, the Power Integrations logo, CAPZero, ChiPhy, CHY, DPA-Switch, EcoSmart, E-Shield, eSIP, eSOP, HiperPLC, HiperPFS, HiperTFS, InnoSwitch, Innovation in Power Conversion, InSOP, LinkSwitch, LinkZero, LYTSwitch, SENZero, TinySwitch, TOPSwitch, PI, PI Expert, PowiGaN, SCALE, SCALE-1, SCALE-2, SCALE-3 and SCALE-iDriver, are trademarks of Power Integrations, Inc. Other trademarks are property of their respective companies. ©2019, Power Integrations, Inc.

#### **Power Integrations Worldwide Sales Support Locations**

#### **World Headquarters**

5245 Hellyer Avenue San Jose, CA 95138, USA Main: +1-408-414-9200 Customer Service:

Worldwide: +1-65-635-64480 Americas: +1-408-414-9621 e-mail: usasales@power.com

#### China (Shanghai)

Rm 2410, Charity Plaza, No. 88 North Caoxi Road Shanghai, PRC 200030 Phone: +86-21-6354-6323 e-mail: chinasales@power.com

#### China (Shenzhen)

17/F, Hivac Building, No. 2, Keji Nan Bangalore-560052 India 8th Road, Nanshan District, Shenzhen, China, 518057 Phone: +86-755-8672-8689 e-mail: chinasales@power.com

**Germany** (AC-DC/LED Sales)

Einsteinring 24

85609 Dornach/Aschheim Germany

Tel: +49-89-5527-39100 e-mail: eurosales@power.com

**Germany** (Gate Driver Sales) HellwegForum 1 59469 Ense

Germany

Tel: +49-2938-64-39990

#1, 14th Main Road Vasanthanagar Phone: +91-80-4113-8020 e-mail: indiasales@power.com

#### Italy

Via Milanese 20, 3rd. Fl. 20099 Sesto San Giovanni (MI) Italy Phone: +39-024-550-8701 e-mail: eurosales@power.com

Yusen Shin-Yokohama 1-chome Bldg. Taiwan 1-7-9, Shin-Yokohama, Kohoku-ku Yokohama-shi. Kanagawa 222-0033 Japan

Phone: +81-45-471-1021 e-mail: igbt-driver.sales@power.com e-mail: japansales@power.com

#### Korea

RM 602, 6FL Korea City Air Terminal B/D, 159-6 Samsung-Dong, Kangnam-Gu, Seoul, 135-728, Korea Phone: +82-2-2016-6610

e-mail: koreasales@power.com

#### **Singapore**

51 Newton Road #19-01/05 Goldhill Plaza Singapore, 308900 Phone: +65-6358-2160

e-mail: singaporesales@power.com

5F, No. 318, Nei Hu Rd., Sec. 1 Nei Hu Dist.

Taipei 11493, Taiwan R.O.C. Phone: +886-2-2659-4570 e-mail: taiwansales@power.com

Building 5, Suite 21 The Westbrook Centre Milton Road Cambridge CB4 1YG

Phone: +44 (0) 7823-557484 e-mail: eurosales@power.com

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Power Integrations:

SIC1182KQ SIC1182KQ-TL