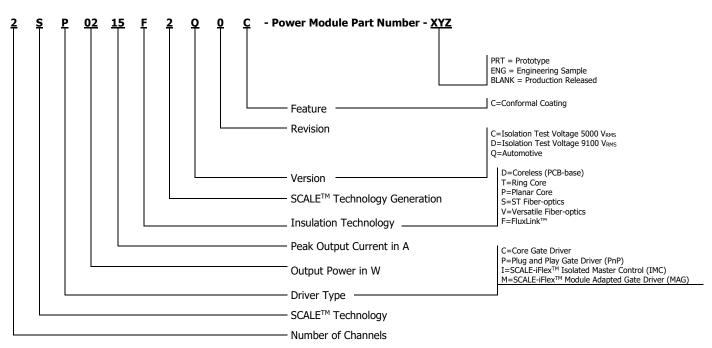

# 2SP0215F2Q0C SCALE EV Family

Automotive Dual Channel Plug and Play Gate Driver for 17 mm IGBT Modules

## **PRELIMINARY**

## **Product Highlights**

- Ready-to-use dual channel gate driver solution with reinforced isolation for 17 mm IGBT power modules up to 1200 V

- Up to 20 kHz switching frequency

- · Digital Bitstream diagnostic output

- Single 5 V Supply

- Integrated Dual 2 W DC/DC converters

- Rail-to-Rail stabilized secondary side output voltage

- -40 °C to +85°C operating ambient temperature

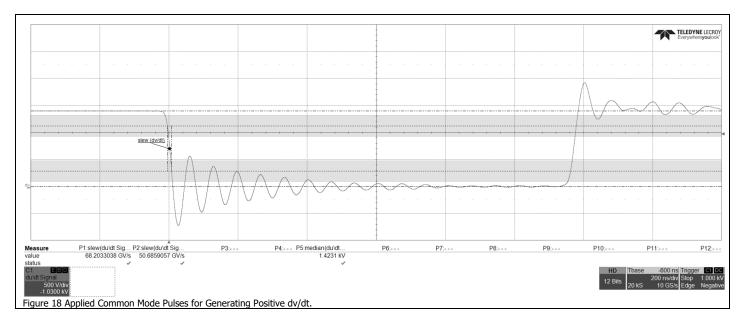

- ± 50 kV / µs common-mode transient immunity

- Operation up to 5500 m altitude

- 5 V Input-Logic

#### **Advanced Protection, Safety and Diagnostic Features**

- DC-link Active-Discharge (AD) function

- · Active Short-Circuit (ASC) function

- Galvanically isolated IGBT module NTC temperature measurement

- Galvanically isolated PCB NTC temperature measurement

- Advanced Resistive Overvoltage Control (AROC)

- Undervoltage monitoring (UVLO) for primary- and Undervoltage warning (UVW) for secondary side

- Secondary side overvoltage monitoring (OVW)

- Gate monitoring

- Input Interlock

- DC/DC controller overcurrent monitoring

- Two stage primary- and secondary side IC temperature monitoring

- Power-Semiconductor short circuit detection (DESAT)

- FluxLink™ signal transfer monitoring

- Active Miller clamp

- Conformally coated

- · Technical cleanliness up to 1 mm

#### **Functional Safety Compliance**

- Enables up to ASIL D in automotive traction systems

- SEooC according to ISO 26262

#### **Full Safety and Regulatory Compliance**

- AEC-Q 100/101/200 components

- IATF 16949 production facilities

- Clearance and creepage distances between primary and secondary sides meet requirements for reinforced isolation (IEC 60664-1, IEC 60664-3)

- 100% production partial discharge test

- 100% production HIPOT testing at 3395  $V_{\text{RMS}}$  for 1 s

#### **Applications**

- e-Bus and e-Truck traction inverter

- BEV automotive traction inverter

- Diesel electric traction inverter

- Fuel cell inverter

- Agricultural and construction vehicles and equipment

- Other automotive and industrial applications

- General purpose drives

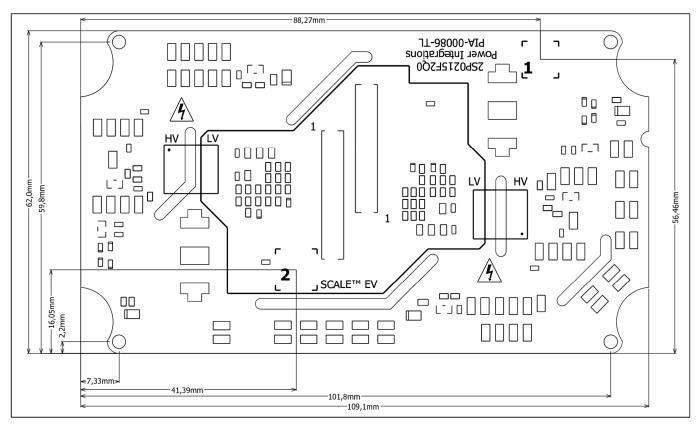

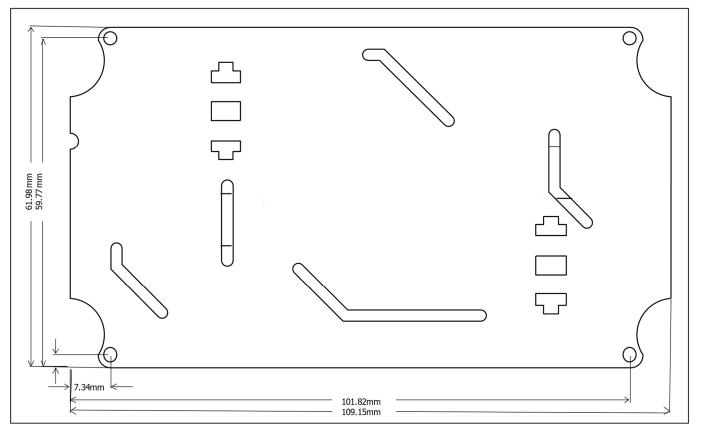

Figure 1. 2SP0215F2Q0C Mounted on Target Power Semiconductor Module.

## **Product Portfolio**

| Order Code                    | Module<br>Technology      | Voltage Class | Current Class | Package   | IGBT Module<br>Supplier |

|-------------------------------|---------------------------|---------------|---------------|-----------|-------------------------|

| 2SP0215F2Q0C-FF900R12ME7W_B11 | Si-IGBT Gen7,<br>Si-Diode | 1200 V        | 900 A         | EconoDUAL | Infineon                |

Table 1 2SP0215F2Q0C Portfolio

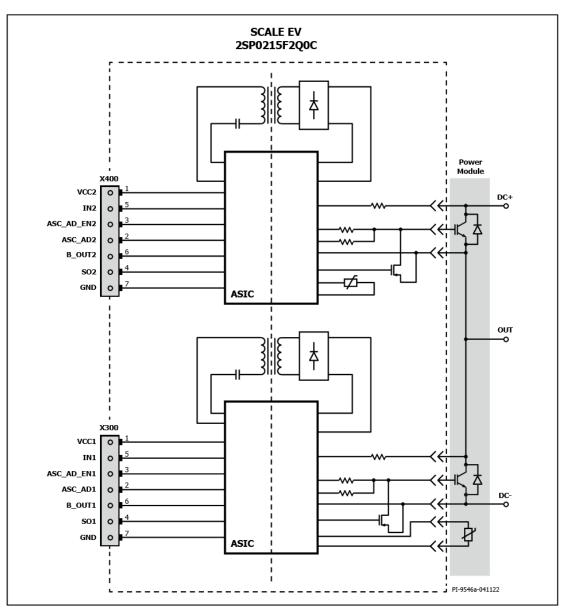

## **Functional Block Diagram**

Figure 2. Block Diagram 2SP0215F2Q0C.

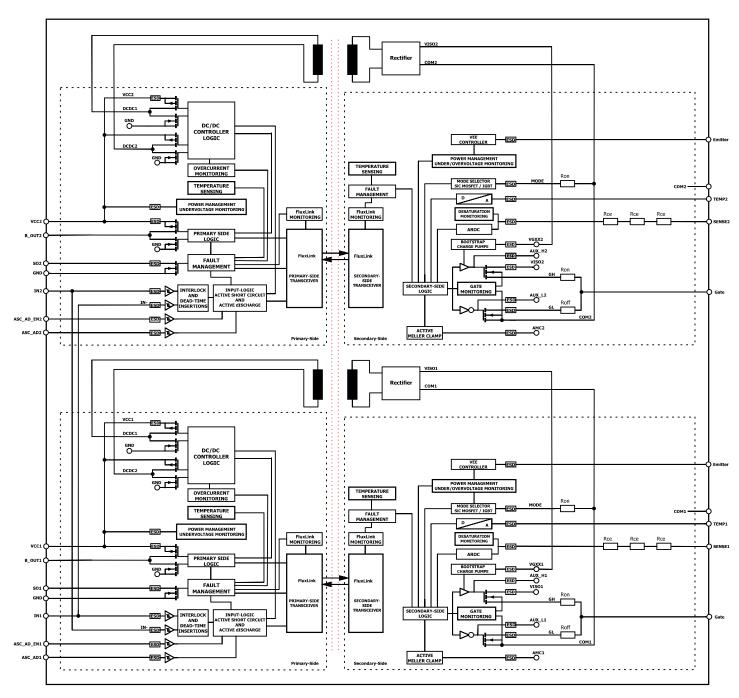

Figure 3. Functional Block Diagram 2SP0215F2Q0C.

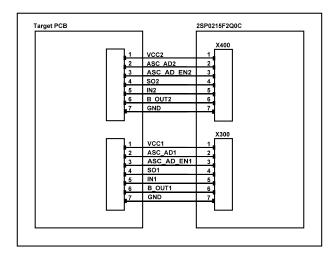

## **Interface Description**

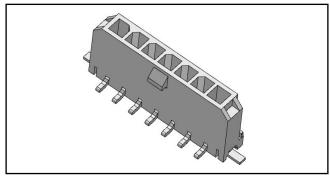

#### Connector X300 (BOT-Channel)

Connection to external system controller from bottom domain (Molex Micro-Fit 3.0 connector).

#### <VCC1 (Pin 1)>

Primary side 5 V supply voltage.

#### <ASC\_AD1> (Pin 2)

This pin determines together with <ASC\_AD\_EN> the Active Short Circuit (ASC) and Active Discharge (AD) operating mode.

#### <ASC\_AD\_EN1> (Pin 3)

This pin determines together with <ASC\_AD> the Active Short Circuit (ASC) and Active Discharge (AD) operating mode.

#### <S01> (Pin 4)

Open drain output fault signal active Low.

#### <IN1> (Pin 5)

Primary side control input signal.

#### <B\_OUT1> (Pin 6)

Bitstream output for diagnostics and NTC temperature value.

#### <GND> (Pin 7)

Primary side <GND> connection with reference to < VCC1>.

#### Connector X400 (TOP-Channel)

Connection to external system controller from top domain (Molex Micro-Fit 3.0 connector).

#### <VCC2> (Pin 1)

Primary side 5 V supply voltage.

#### <ASC\_AD2> (Pin 2)

This pin determines together with <ASC\_AD\_EN> the Active Short Circuit (ASC) and Active Discharge (AD) operating mode.

#### <ASC\_AD\_EN2> (Pin 3)

This pin determines together with <ASC\_AD> the Active Short Circuit (ASC) and Active Discharge (AD) operating mode.

#### <SO2> (Pin 4)

Open drain output fault signal active Low.

#### <IN2> (Pin 5)

Primary side input logic signal.

#### <B\_OUT2> (Pin 6)

Bitstream output for diagnostics and NTC temperature value.

### <GND> (Pin 7)

Primary side <GND> connection with reference to <VCC2>.

## **Quick Start Guide**

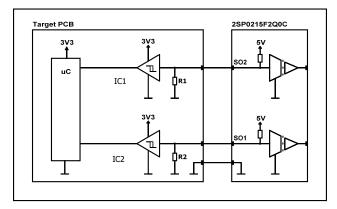

Figure 4. Interface Target System PCB to 2SP0215F2Q0C.

#### Connector X300

Connection to external system controller from bottom domain (Molex Micro-Fit 3.0 connector).

#### **Connector X400**

Connection to external system controller from top domain (Molex Micro-Fit 3.0 connector).

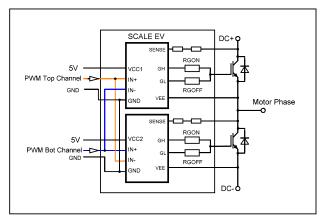

The 2SP0215F2Q0C can be commissioned easily to evaluate the performance in various applications. For this, follow the procedure below:

- With all power off, connect the target system to Connector X300 and Connector X400.

- 2. Turn on the power supplies for  $V_{VCC1}$  and  $V_{VCC2}$ .

- Apply PWM voltages signals according to Table 2 at the logic input pin <IN1> and <IN2>.

| Input<br>Signal | Waveform    | <b>V</b> <sub>LOW</sub> | <b>V</b> <sub>HIGH</sub> | f <sub>sw</sub> | Phase |

|-----------------|-------------|-------------------------|--------------------------|-----------------|-------|

| IN1             | Rectangular | 0 V                     | 5 V                      | 10 kHz          | 0°    |

| IN2             | Rectangular | 0 V                     | 5 V                      | 10 kHz          | 180°  |

Table 2: Example PWM Signal Conditions

Note 1: The minimum gate driver integrated hardware dead time of >465 ns must be inserted into the PWM signals to avoid dead-time warning.

4. The ASC Mode (Active-Short-Circuit) can be activated by applying logic High to <ASC\_AD\_EN> either on each BOT- or on each TOP-Channels of an assumed two level 3-Phase inverter. ASC\_AD\_EN will override the IN1/IN2 signal states.

The following Table 3 shows the possible modes:

| ASC_AD_EN | ASC_AD | Mode                               |

|-----------|--------|------------------------------------|

| 0 V       | 0 V    | Normal Mode                        |

| 5 V       | 0 V    | ASC Mode<br>Gate Output turned-off |

| 5 V       | 5 V    | ASC Mode<br>Gate Output turned-on  |

Table 3 Active Short-Circuit Mode.

The AD (Active Discharge) can be activated by applying logic High to <ASC\_AD> while keeping <ASC\_AD\_EN> at logic Low.

The following Table 4 shows the possible modes:

| ASC_AD_EN | ASC_AD | Mode        |

|-----------|--------|-------------|

| 0 V       | 0 V    | Normal Mode |

| 0 V       | 5 V    | AD Mode     |

Table 4 Active Discharge Mode.

6. A logic Low signal on <SOx> indicates a major fault. Therefore, the target system must set all IN signals to logic Low to avoid a damage of the power semiconductor chips. <B\_OUTx> continuously sends a serial stream of data with detailed information about the actual status, temperature, errors & warnings.

## Recommendations

To achieve the optimum performance of the 2SP0215F2Q0C gate driver consider the following in the design of the target system controller PCB..

#### **Inputs VCC1 and VCC2**

- <VCC1> and <VCC2> must be supplied from independent power supplies to be compliant with functional safety.

- TOP- and BOT-Channel must have a common GND.

- <VCC1> and <VCC2> must be capable of providing a variable output current of up to 500 mA. Actual value depends on the power semiconductor gate charge and switching frequency.

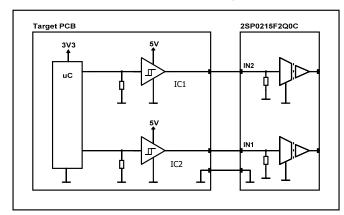

### Inputs ASC\_ADx, ASC\_AD\_ENx and INx

For 3.3 V microcontroller applications, it is recommended to use a level shifter from 3.3 V to 5 V on the target PCB for the inputs <ASC\_ADx>, <ASC\_AD\_ENx> and <INx>. It is recommended to consider the level shifter behavior during power up, power down sequences to avoid unexpected results.

An example for the logic inputs <IN1> and <IN2> is given in Figure 5. The same circuit should be used for all other inputs.

Figure 5. Recommended <INx> Level-Shifter for 3.3 V Microcontroller-Applications.

The following requirements must be considered:

## Schmitt Trigger IC1 and IC2

- Use a Schmitt-Trigger with a supply voltage of 5 V

- The Schmitt-Trigger must be compatible with 3.3 V input signals

- The Schmitt-Trigger output must remain logic Low during power up/down conditions

#### Outputs B\_OUTx and SOx

For 3.3 V microcontroller applications, it is recommended to use a level shifter from 5 V to 3.3 V on the target PCB for the output signals <B\_OUTx> and <SOx>.

An example for the output SO1 and SO2 is given in Figure 6. The same circuit must be used for all other digital output pins.

Figure 6. Recommended Level-Shifter for 3.3 V Microcontroller-Applications for <SOx> outputs.

The following requirements must be considered:

#### **Pull-Down Resistors R1 and R2**

• Use a weak  $100~\text{k}\Omega$  pull-down resistor in the target design for detecting interrupted wiring conditions.

#### Schmitt Trigger IC1 and IC2

- Use a Schmitt-Trigger with a supply voltage of 3.3 V

- The Schmitt-Trigger must be compatible with 5 V input signals

- The Schmitt-Trigger output must remain logic Low during power up/down conditions

## **General Description**

The 2SP0215F2Q0C is an automotive dual channel gate driver for 17 mm EconoDUAL™3 IGBT modules. The plug and play gate driver board is designed for applications which requires automotive qualification like e-Bus, e-Truck, battery electrical vehicles, hybrid electrical vehicles, or fuel cell inverters operating with system voltages up to 1000 V.. Additionally, the plug and play gate driver can control industrial IGBT modules in industrial applications. The 2SP0215F2Q0C is offered in different variants, optimized to meet the requirements of a specific IGBT module.

#### **Primary Side**

- Integrated LLC DC/DC power supply

- Interlocking

- Active-Short-Circuit (ASC) function

- DC Link Active-Discharge (AD) function

- Failure output (low latency)

- Digital Bitstream diagnostic output

- IGBT module and PCB temperature output

#### **Secondary Side**

- Regulated secondary side power supply

- Galvanically isolated IGBT module NTC readout

- Galvanically isolated PCB NTC readout

- Active Miller clamping

#### **Diagnostic and Monitoring**

- · Under- and over-voltage monitoring and warning

- Gate monitoring

- FluxLink™ communication monitoring

- Communication parity check

- Primary side DC/DC overcurrent monitoring

- Primary side DC/DC two level over-temperature monitoring

- Gate driver output stage overtemperature monitoring

- Short pulse diagnostic

#### **Protection**

- Minimum dead time

- PWM input signal interlocking

- Advanced resistive overvoltage control (AROC)

- Short-Circuit

In the following section, all functions and features are briefly described. A more detailed description can be found in in chapter Functional Description .

## **Primary Side Power Supply**

Two individual supply voltages  $V_{VCC2}$  to GND (TOP-Channel) and  $V_{VCC2}$  to GND (BOT-Channel) respectively are necessary to operate the 2SP0215F2QOC.

#### Safe Power-Up and Power-Down

It is required that during the power-up and the power-down events, <INx> pins remains logic Low. Any supply voltage related to  $V_{VCC}$  and GND must be stabilized by capacitors. After the supply voltages reach their recommended nominal values, the gate driver will start to operate after a time delay  $t_{START}$ .

#### **Integrated DC/DC Converter**

Each gate driver channel offers a galvanically isolated DC/DC controller, power stage, transformer and rectifier which supplies the secondary side.

#### **Input Gate Control Signals**

The input <IN1> (BOT-Channel) and <IN2> (TOP-Channel) logic is designed to operate with controllers using 5 V CMOS logic. The gate control signals will be transferred, via galvanic isolation, to the secondary side, defining the on/off state of the power semiconductor chips.

### **Input Logic Interlocking**

The input logic signals IN1 and IN2 are interlocked to each other. This feature prevents an accidently turn-on for both channels at the same time.

Note: This function is deliberately disabled if Active Discharge (AD) is enabled

#### **Active-Short-Circuit (ASC) Function**

For functional safety requirements and overvoltage protection of the high voltage system, the 2SP0215F2Q0C provides an Active-Short-Circuit (ASC) mode, which by system request enables a short circuit to be created across the motor terminals.

#### DC Link Active Discharge (AD) Function

For functional safety requirements the 2SP0215F2QOC provides an Active Discharge (AD) mode. Once activated, this mode will discharge the DC-Link capacitor by using the IGBT module. This provides cost and board area savings compared to a discrete external circuit.

#### **Temperature Measurement**

The 2SP0215F2QOC provides two galvanically isolated NTC readouts for the BOT/TOP-Channel. One for the power semiconductor and one for the PCB.

#### **Active Miller Clamp**

Active Miller clamp can prevent unexpected turn on situations due to unwanted switching of the complementary power semiconductor in a half bridge configuration. The 2SP0215F2Q0C active Miller clamp function is turned on after the corresponding power semiconductor chip is turned off and the gate voltage is below a certain threshold.

#### **Gate Driver Output Stage**

The 2SP0215F2Q0C contains a high current n-channel push-pull driver stage, compatible with the the large gate charges of high current IGBT modules.

## **Under and Overvoltage Monitoring and Warning**

Each gate driver channel continuously monitors the supply voltage  $V_{\text{VCC}}$ . If the supply voltage drops below a specific value, the affected channel will enter the UVLO-Mode and indicates the condition with a static logic Low on <SOx> and logic High on <B\_OUTx>.

Additionally, each channel continuously monitors the secondary side supply voltage. In case of over- and undervoltage conditions, the corresponding warning Bits in the Bitstream output are asserted.

#### **Gate Failure Monitoring**

The 2SP0215F2Q0C compares continuously the gate voltage of each channel with the desired state given by <IN1>/<IN2>. In case of an unexpected condition, the corresponding warning Bit in the Bitstream output is asserted.

#### FluxLink™ Communication Monitoring

The 2SP0215F2Q0C continuously monitors the status of the communication (FluxLink $^{\text{TM}}$ ) between the primary side and secondary side for both channels. In case of an unexpected condition, the corresponding warning Bit in the Bitstream output is asserted.

#### **Communication Parity Check**

The secondary side sends continuously status information to the primary side. For safety reasons the secondary side inserts a parity Bit in each data frame to provide a way to detect corrupted data by the target system.

Note: The parity Bit covers secondary side data only.

#### **Secondary Side Overtemperature Monitoring**

The gate driver 2SP0215F2Q0C monitors continuously the secondary side power semiconductor temperature for each channel. In case of an overtemperature, the corresponding warning Bit in the Bitstream output is asserted.

#### **Hardware Dead Time**

To prevent half bridge shoot through events, the 2SP0215F2Q0C ensures a minimum dead time, if the target system dead time is below a specific value then a minimum deadtime is inserted and a warning bit in the bitstream output is asserted..

#### Advanced Resistive Overvoltage Control (AROC)

If the gate driver is in a turn-off transition or in off-state, the AROC overvoltage limitation algorithm is activated. This provides a deterministic maximum collector voltage regardless of collector current including turn-off after a short circuit event.

#### **Short-Circuit Protection**

When the gate driver is in a turn-on transition or in the on-state, the short-circuit detection algorithm is activated after the delay time  $t_{SENSE(BL)}$  has elapsed.

## FluxLink™ Technology

The FluxLink<sup>™</sup> technology allows signals to be transmitted across a reinforced isolation barrier without the need for magnetic materials. By providing >0.4 mm spacing through solid insulation the reinforced isolation barrier is physically rugged. FluxLink<sup>™</sup> provides bidirectional communication between primary- and secondary side.

#### **Short Pulse Protection**

The 2SP0215F2Q0C continuously monitors <IN1>/<IN2>. Pulse durations lower than a specified value will be extended and the corresponding warning Bit in the Bitstream output is asserted.

Note: A minimum turn-on time for IGBTs and diodes is necessary to avoid diode snappiness especially at low temperatures. Therefore, it is recommended that PWM software include a minimum on time larger than the gate driver minimum hardware on time.

## **Functional Description**

A detailed explanation of function and features is provided below.

#### **Primary Side Power Supply**

Note 1: For greater functional safety, it is recommended to use two independent power supplies for  $V_{VCCI}$  and  $V_{VCCZ}$  The primary GND is common for  $V_{VCCI}$  and  $V_{VCCZ}$ .

Note 2: The gate driver does not provide reverse voltage protection

Note 3: The wiring between the target system and X400 and X300 connectors must be as short as possible. Touching or crossing high voltage potentials is not permitted.

### **Integrated DC/DC Converter**

To generate isolated voltages to drive the gates of the power devices the 2SP0215F2Q0C contains an integrated DC/DC controller, power stage MOSFETs and transformer for each channel.

The 2SP0215F2Q0C monitors the die temperatures related to the DC/DC converter output stage and current on the primary side for each channel.

An overview of the different sensor signals and the corresponding reactions is provided in Table 1 below. A distinction is made between the following sensor signals:

- The temperature threshold OT1<sub>DCDC</sub> (overtemperature warning level 1)

- The temperature threshold OT2<sub>DCDC</sub> (overtemperature warning level 2)

- Over current  $I_{DCDC1}$  and/or  $I_{DCDC2}$

Table 5 gives an overview of the behavior of the DC/DC controllers during the start-up phase and in normal operation . An "X" indicates that the respective threshold value of the sensor signal has been reached. The "B\_OUT" column lists the Bits that are set to logic Low in the presence of an error/warning. For example: during startup, detection of over current will cause the DC/DC controller to stop. However once in stable operation the controller will continue to operate but in both cases B\_OUT[25] bit will be asserted to indicate a warning condition.

| Die<br>Temperature<br>Threshold<br><i>OT1<sub>DCDC</sub></i> | Die<br>Temperature<br>Threshold<br><i>OT2<sub>DCDC</sub></i> | Over Current IDCDC1 and/or IDCDC2 | <b_outx></b_outx>                   | DC/DC<br>Controller<br>Operation<br>Start-up<br>Phase | DC/DC<br>Controller<br>Operation<br>Stable<br>Operation |

|--------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------|-------------------------------------|-------------------------------------------------------|---------------------------------------------------------|

| _                                                            | -                                                            | -                                 | -                                   | Normal<br>Operation                                   | Normal<br>Operation                                     |

| Х                                                            | -                                                            | -                                 | B_OUT[23]                           | Normal<br>Operation                                   | Normal<br>Operation                                     |

| -                                                            | Х                                                            | -                                 | B_OUT[23]<br>B_OUT[24]              | Turned-<br>Off                                        | Turned-<br>Off                                          |

| _                                                            | -                                                            | Х                                 | B_OUT[25]                           | Turned-<br>Off                                        | Normal<br>Operation                                     |

| Х                                                            | -                                                            | Х                                 | B_OUT[23]<br>B_OUT[25]              | Turned-<br>Off                                        | Normal<br>Operation                                     |

| -                                                            | Х                                                            | X                                 | B_OUT[23]<br>B_OUT[24]<br>B_OUT[25] | Turned-<br>Off                                        | Turned-<br>Off                                          |

Table 5 DC/DC Controller States at Different Conditions for Each Channel

#### Safe Power-Up and Power-Down

It is required that during the power-up and the power-down events, <INx> as well as <ASC\_ADx> and <ASC\_AD\_ENx> inputs remains at logic Low. Any supply voltage related to  $V_{VCCx}$  and GND must be well stabilized. If the supply voltages reach their nominal values, the gate driver will start to operate after a delay time  $t_{START}$ .

#### **Input Logic Interlocking**

The input logic signals <IN1> and <IN2> are interlocked from each other. This feature prevents turn-on of both channels at the same time.

An IGBT half-bridge short-circuit is safely prevented in standard operation conditions. If an interlock event occurs, B\_OUT [28] of both channels will be set to logic Low and both gate driver output stages will be turned-off.

Figure 7. Interlocking Function in Half-Bridge Configuration.

Note 1: If the Active Discharge Function is enabled for a channel, the Interlocking-Function of the same channel is disabled.

#### Motor Active Short-Circuit Mode (ASC)

For functional safety and protection of the inverter from excessive voltage, the 2SP0215F2Q0C provides an Active-Short-Circuit (ASC) mode which, by system request, applies a short circuit across the motor terminals.

ASC mode allows the system to keep the gate driver output stage in a defined state either permanently turned-on or permanently turned-off, regardless of <INx> state. This feature makes it possible to short the motor terminals to create a negative torque, decelerating the vehicle in a controlled manner.

The ASC Mode can be activated according the following Table 6

| ASC_AD_EN | ASC_AD | Mode                               |

|-----------|--------|------------------------------------|

| 0 V       | 0 V    | Normal Mode                        |

| 5 V       | 0 V    | ASC Mode<br>Gate Output turned-off |

| 5 V       | 5 V    | ASC Mode<br>Gate Output turned-on  |

Table 6 Active Short-Circuit Mode.

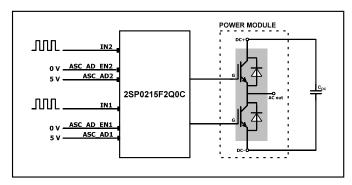

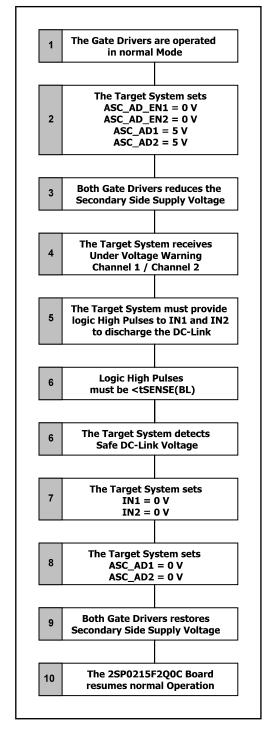

#### DC Link Active Discharge (AD) Function

To avoid the need for additional components for discharging the DC-Link capacitance, the 2SP0215F2Q0C provides an Active Discharge (AD) mode. The principle of the AD mode is to discharge the DC-Link energy through the IGBT module of one or more half-bridges. The IGBT modules are operated in their linear region (reduced gate voltage) and pulsed at a low duty cycle. Linear operation allows the IGBT module acts as a current limiting device.

The AD mode is initiated by applying logic High at pin <ASC\_AD> while keeping <ASC\_AD\_EN> at logic Low.

| ASC_AD_EN | ASC_AD | Mode        |

|-----------|--------|-------------|

| 0 V       | 0 V    | Normal Mode |

| 0 V       | 5 V    | AD Mode     |

Table 7 Active Discharge Mode

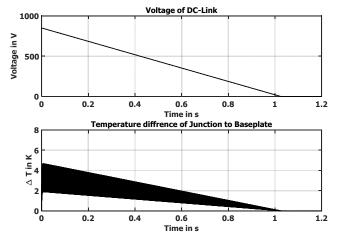

To discharge a DC-Link capacitor the scheme of Figure 9 must be followed. In Figure 8 an implementation example of the AD function in a target system is shown.

Note 1: First the gate drivers from both channels must be operating in normal mode; the secondary side voltages have reached steady state

Note 2: In AD mode, the input logic interlocking is ignored.

#### **Timing & Details**

After setting the <ASC\_AD\_EN> and <ASC\_AD> signals the gate drivers reduce the secondary side supply voltages and the 2SP0215F2Q sends an undervoltage warning on both channels. Subsequently the target system must provide logic High pulses with limited duration  $\leq t_{SENSE(BL)}$  to <IN1> and <IN2> simultaneously.

After discharging the DC-Link, the normal mode can be restored by setting the <ASC\_AD> to logic Low. The gate drivers restore the secondary side supply voltages, and the gate drivers resume normal operation.

Note 2: If tsense(BL) is exceeded the short circuit protection can be activated unexpectedly. This also functions as a safety mechanism, preventing excessive power device dissipation should the system uC command a high duty cycle.

Figure 8. Active Discharge Implementation.

Figure 9. Active Discharge Scheme.

#### **Example:**

The simulation results in 8 and Figure 10 show that the discharge of an 1100 uFmF capacitor, charged at 850 V can be achieved in < 1s by using pulses of 2  $\mu$ s length and 1 kHz repetition rate. The temperature rise of the IGBT devices of <5 Kelvin provides a suitable margin even at 125°C baseplate temperature.

Figure 10. Thermal Simulation of active discharge using FF900R12ME7W\_B11 with 1100  $\mu$ F Cap at 850 V, 2  $\mu$ s, 1 kHz.

| Capacitance             | 1100 μF |

|-------------------------|---------|

| DC-Link Voltage         | 850 V   |

| PWM Switching Frequency | 1 kHz   |

| Pulse width             | 2 μs    |

| Discharge Time          | < 2 s   |

| ΔT in K                 | 5 K     |

Table 8 Simulation Results Active Discharge Mode.

Note: It is highly recommended to evaluate the real thermal behavior in the final application which might differ from the example. In case of thermal overstressing, the pulse repetition rate can be reduced.

## **Secondary Side Power Supply**

The secondary side supply voltage ( $V_{VISO}$  vs. COM) is a unipolar voltage generated from the primary side via a galvanically isolated DC/DC transformer. The positive gate-emitter voltage is provided by  $V_{VISO}$  with respect to  $V_{VEE}$  and the negative gate-emitter voltage by COM with respect to  $V_{VEE}$ . An integrated regulator keeps  $V_{VISO}$  to  $V_{VEE}$  stable.

#### **NTC Temperature Measurement**

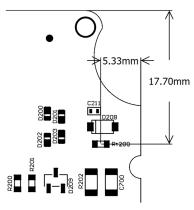

The 2SP0215F2Q0C provides a galvanically isolated NTC readout. The bottom channel is designed to read the IGBT module integrated NTC resistor. The TOP-Channel is designed to read the SMD NTC placed on the PCB, position is shown in Figure 11.

Figure 11. SMD Thermistor for TOP Channel Mounted on PCB

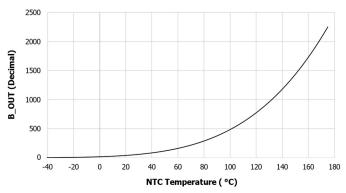

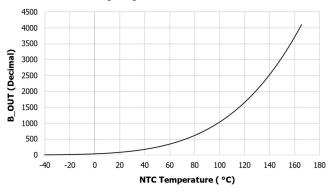

The NTC resistance is digitized by a 12-Bit analog to digital converter (ADC) before it is transferred to B\_OUT.

Equation 1 describes the function R(B\_OUT[ $2_{MSB}$ :13 $_{LSB}$ ]) by applying the following formula:

$$R_{B\_OUT} = 32 \times \frac{V_{TEMP}}{I_{TEMP} \times B_{OUT}[2:13]}$$

Eq. 1

#### **Example:**

For  $B\_OUT$  [2:13] =  $0110111100010_2$  the following resistance value can be calculated:

$$R_{B\_out} = 32 \times \frac{0.3 V}{20 \,\mu A \times 1762} = 272 \,\Omega$$

The following Figure 12 shows the PCB temperature in accordance to  $B\_OUT[2:13]$ :

Figure 12. B\_OUT Decimal Temperature Value as a function of Board NTC Temperature

The following Figure 13 shows the IGBT NTC temperature in accordance to B\_OUT[2:13]:

Figure 13. B\_OUT Decimal Temperature Value as a function of IGBT Module NTC Temperature

#### **Integrated Active Miller Clamp**

To avoid parasitic turn-on effects in half-bridge topologies and during switching events of other power semiconductor chips, the active Miller clamp provides a low impedance connection between the gate of the power semiconductor and the negative supply voltage. Charge injected by switching dv/dt via the Miller capacitance is shorted to the negative gate voltage, keeping the gate safely below the device threshold voltage.

#### **Hardware Dead Time**

To prevent half-bridge short circuits, the 2SP0215F2Q0C ensures a minimum dead time, if the target system dead time insertion is below a specific value.

In case that the dead-time between <IN1> and <IN2> is smaller than  $t_{DT}$ , the gate driver will insert a minimum dead time of  $t_{DT}$  and set B\_OUT [28] to logic low for indication.

Note 1: It is recommended to ensure a suitable dead time in the target system.

Note 2: It is recommended to set up the PWM software with a minimum on time for IGBTs. Short duration pulses can damage the IGBT or diode because of high di/dt and dv/dt.

#### <SOx> and <B\_OUTx> Failure and Diagnostics

The gate driver uses two logic output pins <SOx> and <B\_OUTx> per channel to support failure management and diagnostics.

<SOx> is an open drain fast-responding fault indicator. A logic low indicates a fault state, and the corresponding power semiconductor will be turned off by the gate driver. The gate driver will remain in this state until the next logic low-high transition of the corresponding channel input INx occurs. If SO is recognized as logic Low, it is recommended to switch off all channels immediately.

Note 2: A primary side UVLO-Failure generates a continuously logic low SO if the upper threshold of the UVLO is not exceeded. While this fault condition remains, the power semiconductor will be kept switched off. The gate driver will remain in this state until the UVLO is exceeded and the next logic low-high transition of the corresponding channel input INx occurs.

Note 3: Whenever a SO is asserted (active Low) the next BitStream data packet contains just zeroes. The subsequent data packet will reflect valid information including the cause for the fault to be asserted.

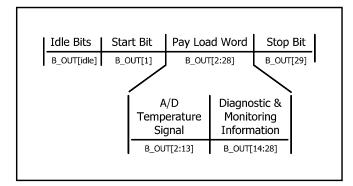

$B\_OUT$  is a digital Bitstream output (Figure 14 ). Multiple different status conditions can be determined by using <SO> and<  $B\_OUT>$  together.

Details are shown in Table 9:

| SOx  | B_OUTx[]              | Fault / Warning                                                       |

|------|-----------------------|-----------------------------------------------------------------------|

| Low  | High                  | V <sub>vccx</sub> undervoltage fault                                  |

| High | [14] = Low            | V <sub>VISO</sub> undervoltage warning<br>UVW <sub>VISO</sub>         |

| High | [15] = Low            | V <sub>VISO</sub> overvoltage warning <i>OVW<sub>VISO</sub></i>       |

| High | [16] = Low            | Gate monitoring warning                                               |

| High | [17] = Low            | Overtemperature warning <i>OT2<sub>GD</sub></i>                       |

| High | [18] = Low            | Overtemperature warning <i>OT1<sub>GD</sub></i>                       |

| High | [19] = Low            | Secondary side FluxLink™ out of service warning                       |

| Low  | [19] = Low            | Secondary side FluxLink™ out of service fault                         |

| Low  | [20] = Low            | Short-Circuit detection                                               |

| High | [21] = Low or<br>High | Parity Bit, set in a way that the sum of B_OUT[2:21] high Bits is odd |

| High | [22] = High           | Primary side FluxLink™ out of service warning                         |

| High | [23] = High           | Overtemperature warning OT1 <sub>DCDC</sub>                           |

| High | [24] = High           | Overtemperature warning OT2 <sub>DCDC</sub>                           |

| High | [25] = High           | Primary side DC/DC Controller overcurrent warning during startup      |

| High | [25] = High           | Primary side DC/DC Controller overcurrent warning after startup       |

| High | [27] = High           | Dead-Time insertion warning                                           |

| High | [28] = High           | Interlock warning                                                     |

Table 9 Combined Fault and Status Feedback of SO and B\_OUT.

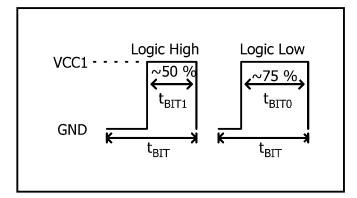

Note: The definition of a logic Low or high condition of <B\_OUTx> Bits are determined by the pulse width as defined in Figure 14.

Figure 14. Definition of Logic Low and Logic High Levels at B\_OUT

The information of the digital Bitstream B\_OUT consists of a start Bit logic High, 27 payload Bits and 1 stop Bit. Prior the start Bit a series of logic Low Bits (B\_OUT [idle]) are sent. The number of idle Bits is not fixed. It is defined by the asynchronous frame time  $t_{\mathcal{B} \, OUT}$  minus the time required for the transmission of the start Bit, Pay Load Bit and the stop Bit.

Figure 15. B\_OUT Bit Assignment.

The individual faults, warnings and feedbacks listed in Table 9 will be explained below.

#### **Under and Overvoltage Monitoring and Warning**

The supply voltages are monitored. In case of an under voltage lock out (UVLO) or over voltage Warning (OVW) a failure or a warning signal is generated.

The undervoltage monitoring function can detect:

- If V<sub>VCC</sub>(primary side) reaches the undervoltage lockout level UVLO<sub>VCCV</sub> / UVLO<sub>VCC2</sub> the related gate driver channel turns-off. <SOx> signal will be set to logic low and <B\_OUTx> will remain logic High.

- If V<sub>VISO</sub> (secondary side) reaches the undervoltage warning level UVW<sub>VISO1</sub> / UVW<sub>VISO2</sub> , the related gate driver channel remains active, only a warning is displayed at B\_OUT[14] (logic Low).

- If V<sub>ISO</sub> (secondary side) reaches the overvoltage warning level OVW<sub>ISO1</sub> OVW<sub>ISO2</sub>, the related gate driver channel remains active, only a warning is displayed at B\_OUT[15] (logic Low)

#### **Gate Monitoring Failure Diagnostic**

The 2SP0215F2Q0C monitors the gate output on the secondary side of each gate driver channel, comparing the expected level with the control input <IN1/2>.

If logic High is applied at <IN1> or <IN2>, the corresponding gate output will turn-on. The output voltage of the gate is measured after the time  $t_{GM(ON)}$  has elapsed. The  $V_{GE}$  voltage level must be larger than the internal reference value  $V_{GM(ON)}$ . If not, a gate monitoring warning will be generated by activating the warning Bit B\_OUT[16].

Similarly, if logic Low is applied at <IN1/2>, the gate output will turn-off the gate of the power semiconductor chip. The output voltage of the gate is measured after the internal time  $t_{GM(OFF)}$  has elapsed. If the voltage level is still higher than the internal reference voltage  $V_{GM(OFF)}$ , a gate monitoring warning will be generated by activating the warning Bit B\_OUT[16].

The gate monitoring function can detect following failures:

- A high resistive gate resistor

- A gate driver communication failure.

- Failed booster stage

- Gate-emitter shorts of the driven power semiconductor chip

Note 1: The digital Bitstream might have a different frequency than the applied command signals at <IN1> or <IN2>. Nevertheless, all switching events will be monitored and any faulty signal reported i.e., a fault condition is latched and reported at the next Bitstream transmission.

#### FluxLink™ Communication Monitoring

The 2SP0215F2Q0C constantly monitors the status of the internal communication channel (FluxLink $^{\text{TM}}$ ) between the primary and secondary sides for both channels.

The FluxLink™ Communication monitoring function can detect:

- If the communication on the primary side is disturbed for typically 10 µs and no valid message is detected, the gate driver triggers a primary side FluxLink™ out-of-service warning and sets Bit B\_OUT [22] to logic Low.

- If the communication on the secondary side is disturbed for typically 10 µs and no valid message is detected, the gate driver triggers a secondary side FluxLink™ out-of-service warning and sets the Bit B\_OUT [19] to logic Low.

If the communication fault on the secondary side lasts longer than typically 20  $\mu$ s, a secondary side FluxLink<sup>TM</sup>-out-of-service fault is triggered, and the SO is set to logic Low for t<sub>SO</sub> after a delay of tSO(DL) has been elapsed. The related gate driver channel turns-off and remains in a latched condition as long as FluxLink returns to normal operation followed by a transition from logic Low to High on INx.

#### **Communication Parity Check**

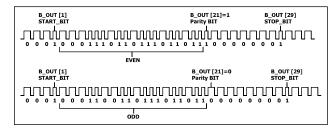

An additional parity Bit is added to the data which send from secondary side to the primary side. The parity Bit is set at position B\_OUT [21] as shown in Figure 16.

Figure 16. Example for the appended Parity Bit.

The parity Bit is calculated in a way that the sum of logical high Bits [2:21] will be odd.

#### **Gate Driver Output Stage Over-Temperature Monitoring**

The temperature of each gate driver channel is monitored on the primary- and secondary side. On the primary side the DC/DC converter output stage and on the secondary side the temperature of the gate driver output stage are monitored.

The overtemperature monitoring function can detect:

- If the temperature on the secondary side exceeds the OT1<sub>GD</sub> threshold level a warning is issued. The related gate driver channel remains on, only a warning is displayed at B\_OUT [18] (logic Low).

- If the temperature further increases reaching OT2<sub>GD</sub>, a second warning is issued. The related gate driver channel also remains on, only a warning is displayed at B\_OUT [17] (logic Low).

- If the temperature on the primary side reaches the OT1DCCC threshold level a warning is issued. The related gate driver channel remains on, only a warning is displayed at B\_OUT [23] (logic High).

- If the temperature further increases and reaches OT2DCDC, a second warning is issued. The related gate driver channel also remains on, only a warning is displayed at B\_OUT [24] (Logic High).

Note: The gate driver will not stop its operation. Therefore, to prevent any thermal damage to the gate driver, the target system must initiate suitable action to keep the gate driver operating conditions within its recommended levels.

#### Advanced Resistive Overvoltage Control (AROC)

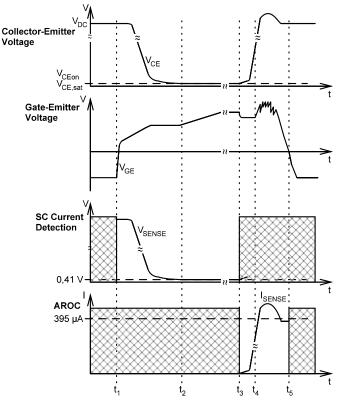

AROC is an advanced circuit to limit the  $V_{CE}$  overvoltage during IGBT turn-off. If the gate driver is in a turn-off transition or in off-state, the overvoltage limitation algorithm is activated. Control is triggered by a current  $I_{SENSE}$  which is derived from the Collector-Emitter-Voltage limited by a resistor and fed into the gate driver IC. If the AROC function is triggered (seen in Figure 17). The gate driver will regulate the gate current to limit the turn-off di/dt and therefore the collector emitter voltage.

Figure 17. AROC and Short-Circuit Detection on SENSE Potential.

## **Short-Circuit Protection**

When the gate driver is in a turn-on transition or in the on-state, the short-circuit detection is activated after an internal response time  $t_{SENSE(BL)}$  has elapsed. A short-circuit condition is detected when the  $V_{CE}$  voltage across the collector-emitter of connected power semiconductor chip reaches its set threshold value  $V_{SC(TH)}$  and the gate driver responds by turning-off the related gate driver channel. In case of a short circuit event, <SOx> signal transits to logic Low for  $t_{SO}$  after a delay of  $t_{SO(DL)}$  has been elapsed. Additionally B\_OUT[20] is set to logic Low.

## **Functional Safety**

The 2SP0215F2Q0C is designed according to the ISO 26262. The gate driver is intended for the usage in automotive safety applications up to ASIL D. The functional safety aspects are described in the 2SP0215F2Q0C functional safety manual.

The 2SP0215F2Q0C contains two gate driver ICs from Power Integrations.

2SP0215F2Q0C is equipped with various warning and fault functions:

- Warnings are defined such, that the 2SP0215F2Q0C will report the event to the system through the Bitstream but will not activate the <SOx> failure output.

- Faults are defined such, that the 2SP0215F2Q0C will report the event to the system through the Bitstream and in addition <SOx> will be activated.

The warnings and faults can further be subdivided into selfdiagnostics and support-to-system diagnostics. The system diagnostics are designed to enhance the system's diagnostic features and thus support the system designer to reach the required level of functional safety.

To satisfy the requirements of a safety related system, 2SP0215F2Q0C offers a variety of safety related features. These features can be integrated into a safety concept from the perspective of a **safety element out of context (SEooC)**:

- Gate Monitoring

- Active Discharge

- Active Short-Circuit

- Galvanically isolated temperature measurement of the IGBT Module NTC

- Galvanically isolated temperature measurement of PCB NTC

- FluxLink control

- Short-circuit detection

- Active Miller Clamp

- DC/DC Die-temperature-measurement

- Undervoltage-Lockout (UVLO) on low voltage side and UVW on high voltage side

- Overvoltage-Warning on high voltage side (OVW)

- Deadtime and Interlock

- Reinforced Insulation

- Diagnostic output (Bitstream), two separate channels

| Primary Side Faults       |                                                                                                                                |  |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| Under voltage per channel | The <sox> output is activated, and a turn-off command is sent to the secondary side (high voltage side) of 2SP0215F2Q0C.</sox> |  |

| 1/2                       | For as long as the condition persists B_OUTx is disabled and the 2SP0215F2Q0C does not accept any further commands.            |  |

Table 10 Primary Side Fault Diagnostic.

| Secondary Side Faults                                              |                                                                                                                                             |  |

|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                    | Detects if the driven IGBT module goes into short-circuit during turn-on.                                                                   |  |

| Short-circuit monitoring per channel 1/2                           | This is a half-bridge relevant diagnostic and detects if the power switch of the other half of the bridge is turned on or in short-circuit. |  |

| Secondary side FluxLink™ out<br>ofservice fault per channel<br>1/2 | Triggered on a timeout if no message is detected after 20 $\mu$ s.                                                                          |  |

|                                                                    | Sends SO command to primary-<br>side and a turn-off command to<br>gate driver output stage.                                                 |  |

|                                                                    |                                                                                                                                             |  |

Table 11 Secondary Side Fault Diagnostic

| Primary Side Warnings                             |                                                                                                                                                   |  |  |

|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| DC/DC over current per channel 1 and 2            | Detects DC/DC converter current on the 2SP0215F2Q0C.                                                                                              |  |  |

|                                                   | Activated if current load of DC/DC converter rises over internal threshold <i>I<sub>DCDC1,th</sub></i> and/or <i>I<sub>DCDC2,th</sub></i> .       |  |  |

| Violation of IN1/IN2<br>Interlock                 | Detects the condition that both<br><in1> and <in2> are high at the<br/>same time</in2></in1>                                                      |  |  |

| Violation of IN1/IN2<br>dead time                 | This is a half-bridge relevant warning. An adequate dead-time is also added to avoid that the half-bridge is short circuited.                     |  |  |

|                                                   | Detects if the dead-time between switching a gate driver respects or not a delay with respect to the gate driver on the other half of the bridge. |  |  |

| Primary side FluxLink™-<br>out-of-service warning | Triggered on a timeout if no valid message is detected after 10 $\mu s$ .                                                                         |  |  |

| DC/DC over-temperature level 1                    | Activated if temperature of DC/DC converter rises over <i>OT1</i> <sub>DCDC</sub> .                                                               |  |  |

| DC/DC over-temperature level 2                    | Activated if temperature of DC/DC converter rises over <i>OT2<sub>DCDC</sub></i> .                                                                |  |  |

|                                                   | The DC/DC converter also turns off as long as the condition persists.                                                                             |  |  |

Table 12 Primary Side Diagnostic Warnings.

| Secondary                                                                  | Side Warnings                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Undervoltage warningper channel 1 and 2                                    | Activated if secondary side supply voltage goes below internal threshold <i>UVWviso</i> .                                                                                                                                                                                                                                                             |

| Overvoltage warning per channel 1 and 2                                    | Activated if secondary side supply voltage goes above internal threshold <i>OVWviso</i> .                                                                                                                                                                                                                                                             |

| Secondary side FluxLink™-out-<br>of-service warning per<br>channel 1 and 2 | Triggered on a timeout if no valid message is detected after 10 $\mu s$ .                                                                                                                                                                                                                                                                             |

| Gate monitoring per channel 1 and 2                                        | Reads back gate status and compares to command received on secondary side. If the value is not correct then it latches a warning which will be sent to the primary.  Although the warning update is f <sub>SW</sub> -times slower than the 2SP0215F2Q0C switching frequency f <sub>SW</sub> , any error is latched and transmitted in the next frame. |

| Gate driver output stage temperature level 1 per channel 1 and 2           | Activated if temperature of gate driver output stage rises over <i>OT1<sub>GD</sub></i>                                                                                                                                                                                                                                                               |

| Gate driver output stage<br>temperature level 2 per<br>channel 1 and 2     | Activated if temperature of gate driver output stage rises over <i>OT2<sub>GD</sub></i>                                                                                                                                                                                                                                                               |

| CRC parity Bit per channel 1 and 2                                         | An even parity Bit is added to digital Bit stream from secondary- to primary side. It is added to <b_outx.></b_outx.>                                                                                                                                                                                                                                 |

Table 13 Secondary Side Diagnostic Warnings

## **Minimum/Maximum Ratings**

| Parameter                                                                                           | Symbol               | <b>Conditions</b> $T_A = -40^{\circ}\text{C to } 85^{\circ}\text{C}$ | Min  | Max                    | Units           |

|-----------------------------------------------------------------------------------------------------|----------------------|----------------------------------------------------------------------|------|------------------------|-----------------|

| Absolute Minimum/Maximum Ratings <sup>1</sup>                                                       |                      | ^                                                                    |      |                        |                 |

| Primary Side Supply Voltage                                                                         | $V_{\text{VCC}_x}$   | Referenced to GND                                                    | -0.5 | 6                      | V               |

| Logic Input Voltage (Command Signal) <sup>2</sup>                                                   | $V_{\text{INx}}$     | Referenced to GND                                                    | -0.5 | V <sub>VCCx</sub> +0.5 | V               |

| Logic Input Voltage ASC_AD_ENx and ASC_ADx                                                          | $V_{ASCx}$           | Referenced to GND                                                    | -0.5 | V <sub>vccx</sub> +0.5 | V               |

| Logic Output Voltage SOx (Status<br>Signal)                                                         | V <sub>SOx</sub>     | Referenced to GND                                                    | -0.5 | V <sub>VCCx</sub> +0.5 | V               |

| Logic Output Voltage B_OUTx<br>(Bitstream Signal)                                                   | $V_{B\_OUTx}$        | Referenced to GND                                                    | -0.5 | V <sub>VCCx</sub> +0.5 | V               |

| Output Current SOx (Status<br>Signal)                                                               | $I_{\text{SOx}}$     | Open drain sink, 1.5 kOhm<br>internal pull up                        |      | 3.5                    | mA              |

| Logic output Current B_OUTx<br>(Bitstream Signal)                                                   | $I_{\text{B\_OUTx}}$ |                                                                      |      | ± 20                   | mA              |

| Gate Output Power Per Channel                                                                       | $P_{gx}$             |                                                                      |      | 2                      | W               |

| Switching Frequency                                                                                 | F <sub>SW</sub>      |                                                                      |      | 20                     | kHz             |

| Test Impulse Withstand<br>Voltage Primary Side to<br>Secondary Side (1.2 / 50 μs) <sup>6-8</sup>    | V <sub>IMP(PS)</sub> | acc. to IEC 60664-1:2020                                             | 4000 |                        | V <sub>PK</sub> |

| Test Impulse Withstand Voltage<br>Secondary Side to Secondary-<br>Side (1.2 / 50 μs) <sup>6-8</sup> | $V_{\text{IMP(SS)}}$ | acc. to IEC 60664-1:2020                                             | 2500 |                        | $V_{PK}$        |

| Operating Voltage Primary Side to<br>Secondary Side                                                 | $V_{OP}$             | Transient only                                                       |      | 1200                   | $V_{PK}$        |

| Operating Voltage Primary Side to                                                                   |                      | Permanently applied                                                  |      | 1000                   | VDC             |

| Secondary Side<br>DC-Link Voltage                                                                   | $V_{\text{DC-Link}}$ | Switching operation                                                  |      | 950                    | VDC             |

| Common Mode Transient Immunity                                                                      | dv/dt                |                                                                      | 50   |                        | kV/μs           |

| Storage Temperature <sup>3</sup>                                                                    | T <sub>st</sub>      |                                                                      | -40  | 50                     | °C              |

| Operating Ambient Temperature                                                                       | T <sub>A</sub>       |                                                                      | -40  | 85                     | °C              |

| Surface Temperature⁴                                                                                | $T_{SF}$             |                                                                      |      | 85                     | °C              |

| Operating Relative Humidity                                                                         | H <sub>R</sub>       | No condensation                                                      |      | 85                     | %               |

| Altitude of Operation <sup>5</sup>                                                                  | A <sub>OP</sub>      |                                                                      |      | 5500                   | m               |

## NOTES:

- 1. Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device.

- 2. INx signals must statically be within the given limits. The transition from low-state to high-state and vice-versa must happen within 50 ns

- 3. The storage temperature inside the original package or in case the coating material of coated products may touch external parts must be limited to the given value. Otherwise, it is limited to 85 °C.

- 4. The component surface temperature, which may strongly vary depending on the actual operating conditions, must be limited to the given value for coated gate driver versions to ensure long-term reliability of the coating material.

- 5. Operation above this level requires a voltage derating to ensure proper isolation coordination.

- 6. The on-board assembled gate driver IC SIC2192FQ is measured according to its datasheet.

- 7. All insulating subsystems are tested separately. The product insulation is not end of line tested.

- 8. The customer is requested to perform a high voltage test according to his product standard.

## **Recommended Operating Conditions**

| Parameter                                     | Symbol                                                                  | Conditions $T_A = -40 \text{ °C to } +85 \text{ °C}$ (Unless Otherwise Specified)   | Min  | Тур   | Мах  | Units |

|-----------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------|-------|------|-------|

| <b>Recommended Operation</b>                  | Conditions                                                              |                                                                                     |      |       |      |       |

| Primary Side<br>Supply Voltage                | V <sub>vccx</sub>                                                       | Referenced to GND                                                                   | 4.75 | 5     | 5.25 | V     |

| Gate Turn-On Voltage                          | $V_{\rm GE,ON}$                                                         | Referenced to VEE                                                                   |      | 15    |      | V     |

| Gate Turn-Off Voltage                         | V <sub>GE,OFF</sub>                                                     | Referenced to VEE                                                                   |      | -5    |      | V     |

| Logic Low Input Voltage<br>(Command Signals)  | V <sub>INx(L)</sub> V <sub>ASC_AD_ENx(L)</sub> V <sub>ASC_AD_X(L)</sub> | Referenced to GND                                                                   |      |       | 0.7  | V     |

| Logic High Input Voltage<br>(Command Signals) | V <sub>INx(H)</sub> V <sub>ASC_AD_ENx(H)</sub> V <sub>ASC_ADX(H)</sub>  | Referenced to GND                                                                   | 4.2  |       |      | V     |

| Logic Output Current<br>SOx (fault signal)    | $I_{\text{SOx}}$                                                        | $V_{VCCx} = 5 \text{ V}, \text{ R}_{SOx} = 1.5 \text{ k}\Omega, \text{ open drain}$ |      | - 3.3 |      | mA    |

| Switching Frequency                           | f <sub>sw</sub>                                                         | 2SP0215F2Q0C-FF900R12ME7W_B11                                                       |      |       | 10   | kHz   |

|                                                                              |                             | Cond                                                                            |                                    |      | _     |      |       |

|------------------------------------------------------------------------------|-----------------------------|---------------------------------------------------------------------------------|------------------------------------|------|-------|------|-------|

| Parameter                                                                    | Symbol                      | $T_{A} = -40  ^{\circ}$ C (Unless Other)                                        | C to +85 °C<br>wise Specified)     | Min  | Тур   | Max  | Units |

| <b>Electrical Characteristics</b>                                            |                             |                                                                                 |                                    | ,    | ,     |      |       |

| Logic Low Input                                                              | $V_{_{\mathrm{INx(HL)}}}$   | $V_{VCCx} = 5 \text{ V, } T_A =$                                                | = 25 °C, f <sub>sw</sub> = 210 kHz |      | 1.3   |      | ٧     |

| Threshold Voltage<br>(Command Signals)                                       | V <sub>ASC_AD_ENx(HL)</sub> | V <sub>VCCx</sub> = 5 V, T <sub>A</sub> = 25 °C                                 |                                    |      | 1.3   |      | V     |

|                                                                              | V <sub>ASC_ADx(HL)</sub>    | VVCCx - 3                                                                       | 5 V, 1A – 25 C                     |      | 1.5   |      | V     |

| Logic High Input<br>Threshold Voltage                                        | $V_{\text{INx-(LH)}}$       | $V_{VCCx} = 5 V, T_A$                                                           | = 25 °C, f <sub>sw</sub> = 10 kHz  |      | 3.5   |      | V     |

| Command Signals)                                                             | V <sub>ASC_AD_ENx(LH)</sub> | V _ E                                                                           | 5 V. T <sub>A</sub> = 25 °C        |      | 2.5   |      | V     |

|                                                                              | V <sub>ASC_ADx(LH)</sub>    | $\mathbf{v}_{\text{VCCx}} = \mathbf{S}$                                         | V, IA = 25 °C                      |      | 3.5   |      | V     |

|                                                                              | $\mathbf{I}_{INx}$          | $V_{VCCx} = 5 V, R$                                                             | <sub>INx+</sub> = 1.53 kΩ          |      | 3.3   |      |       |

| Input Bias Current                                                           | $I_{ASC\_AD\_ENx}$          | $V_{\text{VCCx}} = 5 \text{ V, R}_{\text{ASC\_AD\_ENx}} = 1.53 \text{ k}\Omega$ |                                    |      | 3.3   |      | mA    |

|                                                                              | I <sub>ASC_ADx</sub>        | $V_{VCCx} = 5 \text{ V}, R_{ASC\_ADx} = 1.53 \text{ k}\Omega$                   |                                    |      | 3.3   |      |       |

| Supply Current                                                               |                             | $V_{VCCx} = 5 V$                                                                | , $V_{INx} = 0 V$                  | TBD  | TBD   | TBD  |       |

| (Primary Side)                                                               | $I_{vccx}$                  | $V_{VCCx} = 5 \text{ V}, V_{INx} = 0/5 \text{ V}, f_{SW} = 10 \text{ kHz}$      |                                    | TBD  | TBD   | TBD  | mA    |

| Undervoltage Power<br>Supply Monitoring                                      |                             | Resume Operation Suspend Operation                                              |                                    | 4.30 | 4.35  | 4.45 |       |

| Threshold<br>(Primary Side)                                                  | UVLO <sub>VCCx</sub>        |                                                                                 |                                    | 3.85 | 4.12  | 4.20 | V     |

| Undervoltage Power<br>Supply Monitoring<br>Blanking Time<br>(Primary Side)   | UVLO <sub>VCCx(BL)</sub>    | V <sub>vccx</sub> Voltage Dro                                                   | o from tbd to tbd                  | TBD  | TBD   | TBD  | ns    |

| Undervoltage Power                                                           |                             | Measured between                                                                | Clear Warning                      | 12.3 | 12.85 | 13.5 |       |

| Supply Monitoring Threshold                                                  | UVW <sub>VISOx</sub>        | V <sub>VISO</sub> and V <sub>VEE</sub>                                          | Set Warning                        | 11.6 | 12.3  | 13   | V     |

| (Secondary Side)                                                             |                             | Hyste                                                                           | eresis                             | 0.35 | 0.60  | 0.85 |       |

| Undervoltage Power<br>Supply Monitoring<br>Blanking Time<br>(Secondary Side) | UVWvisox(BL)                | V <sub>viso</sub> Voltage Drop                                                  | o from tbd to tbd                  | TBD  | TBD   | TBD  | ns    |

| Parameter                               | Symbol                 | T <sub>0</sub> = -40 °C                                                              | itions<br>C to +85 °C<br>wise Specified)                                                                              | Min  | Тур  | Max  | Units |

|-----------------------------------------|------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| <b>Electrical Characteristics</b>       | (cont.)                |                                                                                      |                                                                                                                       |      |      |      |       |

| Overvoltage Power                       |                        | Measured between                                                                     | Clear Warning                                                                                                         | 17.3 | 18.5 | 19.8 |       |

| Supply Monitoring<br>Threshold          | OVWvisox               | V <sub>VISO</sub> and V <sub>VEE</sub>                                               | Set Warning                                                                                                           | 18   | 19.1 | 20.4 | V     |

| (Secondary Side)                        |                        | Hyste                                                                                | eresis                                                                                                                | 0.3  | 0.6  | 0.84 |       |

| Power On Startup Time                   | t <sub>start</sub>     | secondary side supply required level for                                             | e after primary and<br>voltages reach minimal<br>gate driver proper<br>ation.                                         |      |      | TBD  | ms    |

| SENSE Fault Monitoring<br>Blanking Time | t <sub>SENSE(BL)</sub> |                                                                                      |                                                                                                                       | 2.4  |      | 3.1  | μS    |

| Minimum Turn-On and -Off Pulses         | $t_{\text{GE(MIN)}}$   | _                                                                                    | $t_{\text{GE}(\text{min})}$ will be extended $t_{\text{GE}(\text{min})}$                                              | 33   |      | 1000 | ns    |

| Turn-On Propagation<br>Delay            |                        | 10 ns. Delay is measu increase on <inx> increase or <math>T_{\rm J} =</math></inx>   | from 0 V to 5 V within ured from 50% voltage pin to 10% voltage on GH pin 25°C e dependent <sup>1</sup>               | TBD  | TBD  | TBD  | ns    |

|                                         | $t_{_{P(LH)}}$         | $V_{\text{INx}}$ potential changes 10 ns. Delay is measu increase on INx pin to on G | from 0 V to 5 V within ured from 50% voltage o 10% voltage increase H pin 85°C                                        | TBD  | TBD  | TBD  |       |

| Turn-Off                                |                        | within 10 ns. Delay is voltage decrease on I decrease $T_{\rm J} =$                  | ges from 5 V to 0 V s measured from 50% Nx pin to 10% voltage on GL pin 25°C e dependent <sup>1</sup>                 | TBD  | TBD  | TBD  |       |

| Propagation Delay                       | $t_{P(HL)}$            | within 10 ns. Delay is voltage decrease on I decrease $T_{\rm J} =$                  | ges from 5 V to 0 V<br>measured from 50%<br>Nx pin to 10% voltage<br>on GL pin<br>85°C<br>e dependent <sup>1</sup>    | TBD  | TBD  | TBD  | ns    |

| Gate Monitoring Turn-On<br>Threshold    | $V_{\text{GM(ON)}}$    | $V_{GM(ON)} = V_{VISO} - V_{GL}$                                                     | $V_{IN1} = 5 \text{ V}, V_{IN2} = 0 \text{ V}$                                                                        | 2.8  | 3.1  | 3.4  | .,    |

| Gate Monitoring<br>Turn-Off Threshold   | $V_{\text{GM(OFF)}}$   | $V_{GM(OFF)} = V_{GH} - V_{COM}$                                                     | $V_{IN1} = 0 \text{ V}, V_{IN2} = 0 \text{ V}$                                                                        | 2.3  | 2.7  | 3.4  | V     |

| Gate Monitoring<br>Turn-On Delay        | t <sub>GM(ON)</sub>    | signal in the secondar<br>50% rising time of G                                       | en receiving a turn-on<br>y side (corresponds to<br>iH signal) and (V <sub>VISO</sub> -<br>ning V <sub>GM(ON)</sub>   | TBD  | TBD  | TBD  | μS    |

| Gate Monitoring<br>Turn-Off Delay       | t <sub>GM(OFF)</sub>   | signal in the Secondar<br>50% falling time of C                                      | en receiving a turn-off<br>ry-side (corresponds to<br>GH signal) and (V <sub>VGH</sub> -<br>hing V <sub>GM(OFF)</sub> | TBD  | TBD  | TBD  | μs    |

| Output Stage<br>Overtemperature 1 | OT1 <sub>GD</sub> | Setting Bit B_OUTx[18] | 135 | 150 | 165 | °C |

|-----------------------------------|-------------------|------------------------|-----|-----|-----|----|

| Output Stage<br>Overtemperature 2 | OT2 <sub>GD</sub> | Setting Bit B_OUTx[17] | 160 | 175 | 190 | °C |

| Half-Bridge Dead-Time             | t <sub>dt</sub>   |                        | 465 | 660 | 870 | ns |

## NOTES:

1. Measured with typical modules. Time can be different (different module loads).

| Parameter                                | Symbol                           | Conditions $T_A = -40 \text{ °C to } +85 \text{ °C}$ (Unless Otherwise Specified)                                           | Min  | Тур | Max  | Units |

|------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------|-----|------|-------|

| <b>Electrical Characteristics</b>        | (cont.)                          |                                                                                                                             |      | ,   | ,    |       |

| DC/DC Controller Over                    | I <sub>DCDC1(TH)</sub>           | Setting Bit B_OUTx[25]                                                                                                      | TBD  | TBD | TBD  | Α     |

| Current Threshold                        | I <sub>DCDC2(TH)</sub>           | Setting Bit B_OUTx[25]                                                                                                      | TBD  | TBD | TBD  | A     |

|                                          | OT1 <sub>DCDC</sub>              | Setting Bit B_OUTx[23]                                                                                                      | 135  | 150 | 165  |       |

| DC/DC Controller Over-Temperature        | OT2 <sub>DCDC</sub>              | Setting Bit B_OUTx[24],<br>Shutdown of DC/DC Controller<br>Operation                                                        | 160  | 175 | 190  | °C    |

| Internal TEMP<br>Reference Voltage       | V <sub>TEMP</sub>                | Internal reference current trimmed with an external resistor R <sub>TEMP</sub> =400 Ohms connected between TEMP and COM pin | 0.29 | 0.3 | 0.33 | V     |

| Internal TEMP<br>Reference Current       | $\mathbf{I}_{TEMP}$              |                                                                                                                             | 18.5 | 20  | 21   | μА    |

| TEMP Sampling Time                       | t <sub>B_OUT_TEMP_SAMPLING</sub> | The temperature output bit stream at B_OUTx is updated with a new temperature sampling within this period (8 x tB_OUT)      | TBD  | TBD | TBD  | ms    |

| SOx Output Voltage<br>Logic Low          | V <sub>SO(0)</sub>               | $V_{\text{VCCx}} \ge 3.9 \text{ V, } I_{\text{Sox}} = 3.4 \text{ mA,}$ Referenced to GND                                    | 80   | 144 | 278  | mV    |

| SOx Fault Signalization<br>Duration Time | t <sub>so</sub>                  | Duration of SO signal at low level during fault event                                                                       | TBD  | 10  | TBD  | μS    |

| SO Fault Signalization<br>Delay Time     | t <sub>so(dl)</sub>              | Delay time to transfer faults from secondary-<br>side to SO pin                                                             | TBD  | 165 | TBD  | ns    |

|                                  |                       |                                                                                      | Conditions                                                                 |      |      |      |      |

|----------------------------------|-----------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------|------|------|------|

| Parameter                        | Symbol                |                                                                                      | = -40 °C to 85°C<br>s Otherwise Specified)                                 | Min  | Тур  | Max  | Unit |

| B_OUT Characteris                | tics Channel 1 and    | d 2                                                                                  |                                                                            | ļ    |      | 1    | 1    |

| Bit Length                       | t <sub>BIT</sub>      |                                                                                      | e beginning of one Bit to the<br>e next Bit of the B_OUT signal            | 2.25 | 2.35 | 2.49 | μs   |

| Bit Pulse Width                  | t <sub>BITO</sub>     | Percentage                                                                           | of B_OUT >Bit length t <sub>RIT</sub>                                      | 72   | 73   | 74   | - %  |

| bit Puise Widtii                 | t <sub>BIT1</sub>     | rerectinge                                                                           | of b_oot > bit length t <sub>BIT</sub>                                     | 45   | 47   | 50   | 70   |

| Bit Frame<br>Transmission Rate   | t <sub>B_OUT</sub>    | The transmission time from one data frame start Bit to the next data frame start Bit |                                                                            |      | 615  | 631  | μS   |

|                                  | B_OUT[idle]           | Alway                                                                                | ys Logic Low, Note 1                                                       | 28   |      |      |      |

|                                  |                       | B_OUT[1]                                                                             | Start Bit, Logic High                                                      |      | 1    |      |      |

|                                  |                       | B_OUT[2:13]                                                                          | Digitized TEMP Signal,<br>B_OUT[2] = MSB,<br>B_OUT[13] = LSB               |      | 12   |      |      |

|                                  |                       | B_OUT[14]                                                                            | V <sub>VISO</sub> Undervoltage Warning,<br>Active Low                      |      | 1    |      |      |

|                                  |                       | B_OUT[15]                                                                            | V <sub>VISO</sub> Overvoltage Warning,<br>Active Low                       |      | 1    |      |      |