www.parallax.com/P2 - sales@parallax.com - support@parallax.com - +1 888-512-1024

# Parallax Propeller 2 (P2X8C4M64P) Datasheet

The Propeller 2 is a multicore microcontroller for embedded systems that delivers high-speed parallel processing with low current consumption in a small package. The Propeller's multiple processors enjoy full command of I/O pins, the flexibility to change clock speed, the power to start and stop at will, and the ability to perform simultaneous tasks in an independent or cooperative manner.

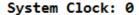

The Propeller 2 P2X8C4M64P microcontroller consists of 8 identical 32-bit processors (called cogs), each with their own RAM, which connect to a common hub. The hub provides 512 KB of shared RAM, a CORDIC math solver, and housekeeping facilities. The architecture supports 64 smart I/O pins, each capable of many autonomous analog and digital functions. The Propeller 2's assembly language (PASM2) features per-instruction conditional execution, special looping mechanisms, and pattern-based instruction skipping to encourage fast, compact code.

| Part Number Legend |                     |                          |                   |  |

|--------------------|---------------------|--------------------------|-------------------|--|

| P2X 8C 4M 64P      |                     |                          |                   |  |

| Propeller 2        | 8 cogs (processors) | 4 Mbit Main RAM (512 KB) | 64 smart I/O pins |  |

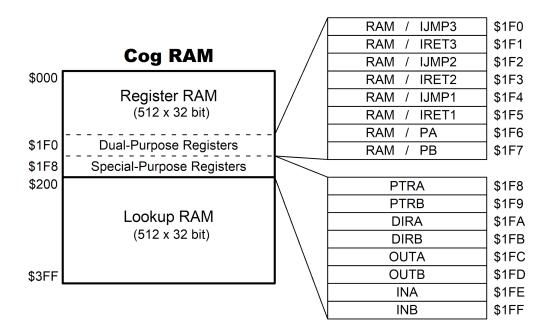

There are three memory regions: Register RAM, Lookup RAM, and Hub RAM. Each cog has its own Register RAM and Lookup RAM (collectively called Cog RAM), while the Hub RAM is shared by all cogs.

| Propeller 2 (P2X8C4M64P) RAM Memory Configuration |         |         |                                        |                                             |

|---------------------------------------------------|---------|---------|----------------------------------------|---------------------------------------------|

| Region                                            | Depth   | Width   | Program Counter<br>Address Range (Hex) | PASM Instruction D/S<br>Address Range (Hex) |

| Cog "Register" RAM                                | 512     | 32 bits | \$00000\$001FF                         | \$000\$1FF                                  |

| Cog "Lookup" RAM                                  | 512     | 32 bits | \$00200\$003FF                         | \$000\$1FF                                  |

| Hub RAM                                           | 524,288 | 8 bits  | \$00400\$7FFFF                         | \$00000\$7FFFF                              |

### **FEATURES**

### Eight powerful 32-bit processors, each with:

- Access to all I/O pins, plus four fast DAC output channels and four fast ADC input channels

- 512 longs of dual-port Register RAM for code and fast variables

- 512 longs of dual-port Lookup RAM for code, streamer lookup, and variables

- Ability to execute code directly from Register RAM, Lookup RAM, and Hub RAM

- ~350 unique instructions for math, logic, timing, and control operations

- 2-clock execution for all math and logic instructions, including 16 x 16 multiply

- 6-clock custom-bytecode executor for interpreted languages

- Ability to stream Hub RAM and/or Lookup RAM to DACs and pins or HDMI modulator

- Ability to stream pins and/or ADCs to Hub RAM

- Live colorspace conversion using a 3 x 3 matrix with 8-bit signed/unsigned coefficients

- Pixel blending instructions for 8:8:8:8 data

- 16 unique event trackers that can be polled and waited upon

- 3 prioritized interrupts that trigger on selectable events

- Cog-to-cog attention signals for swift coordination

- Hidden debug interrupt for single-stepping, breakpoint, and polling

- 8-level hardware stack for fastest subroutine calls/returns and push/pop operations

- Carry and Zero flag

### Central hub serving the processors with:

- 512 KB of contiguous RAM in a 20-bit address space

- o 32-bits-per-clock sequential read/write for all cogs, simultaneously

- o readable and writable as bytes, words, or longs in little-endian format

- o last 16 KB of RAM is write-protectable

- 32-bit, pipelined CORDIC solver with scale-factor correction

- o 32-bit x 32-bit unsigned multiply with 64-bit result

- o 64-bit / 32-bit unsigned divide with 32-bit quotient and 32-bit remainder

- $\circ$  64-bit  $\rightarrow$  32-bit square root

- o Rotate (X32, Y32) by Theta32  $\rightarrow$  (X32, Y32)

- $\circ$  (Rho32, Theta32)  $\rightarrow$  (X32, Y32) polar-to-cartesian

- $\circ$  (X32, Y32)  $\rightarrow$  (Rho32, Theta32) cartesian-to-polar

- $\circ$  32  $\rightarrow$  5.27 unsigned-to-logarithm

- $\circ$  5.27  $\rightarrow$  32 logarithm-to-unsigned

- Cogs can start CORDIC operations every 8 clocks and get results 55 clocks later

- 16 semaphore bits with atomic read-modify-write operations

- 64-bit free-running counter which increments every clock, cleared on reset

- High-quality pseudo-random number generator (Xoroshiro128\*\*), true-random seeded at start-up, updates every clock, provides unique data to each cog and pin

- Mechanisms for starting, polling, and stopping cogs

- 16KB boot ROM

- Loads into last 16 KB of Hub RAM on boot-up

- o SPI loader for automatic startup from 8-pin flash or SD card

- Serial loader for startup from host

- Hex and Base64 download protocols

- Interactive terminal P2 Monitor

- Interactive terminal TAQOZ Forth

### 64 Smart I/O pins, each with:

- 8-bit, 120-ohm (3ns) and 1k-ohm DACs with 16-bit oversampling, noise, and high/low digital modes

- Delta-sigma ADC with 5 ranges, 2 sources, and VIO/GIO calibration

- Several ADC sampling modes: automatic 2n SINC2, adjustable SINC2/SINC3, oscilloscope

- Logic, Schmitt, pin-to-pin-comparator, and 8-bit-level-comparator input modes

- 2/3/5/8-bit-unanimous input filtering with selectable sample rate

- Incorporation of inputs from relative pins, -3 to +3

- Negative or positive local feedback, with or without clocking

- Externally powered in blocks of 4 for clean analog Vdd reference

- Separate drive modes for high and low output: logic / 1.5 k / 15 k / 150 k / 1 mA / 100 μA / 10 μA / float

- Programmable 32-bit clock output, transition output, NCO/duty output

- Triangle/sawtooth/SMPS PWM output, 16-bit frame with 16-bit prescaler

- Quadrature decoding with 32-bit counter, both position and velocity modes

- 16 different 32-bit measurements involving one or two signals

- USB full-speed and low-speed (via odd/even pin pairs)

- Synchronous serial transmit and receive, 1 to 32 bits, up to clock/2 baud rate

- Asynchronous serial transmit and receive, 1 to 32 bits, up to clock/3 baud rate

### Six clock modes, all under software control with glitch-free switching between sources:

- Internal 20M Hz+ RC oscillator, nominally 25 MHz, used as initial clock source

- Crystal oscillator with internal loading caps for 7.5 pF/15 pF crystals, can feed PLL

- Clock input, can feed PLL

- Fractional PLL with 1..64 crystal divider --> 1..1024 VCO multiplier --> optional (1..15)\*2 VCO post-divider

- Internal ~20 kHz RC oscillator for low-power operation (130 μA)

- Clock can be stopped for lowest power until reset (100 μA, due to leakage)

### Power requirements:

- Core: 1.8 VDC, powered via VDD pins

- Smart I/O pins: 3.3 VDC, powered in groups of 4 via VIO pins

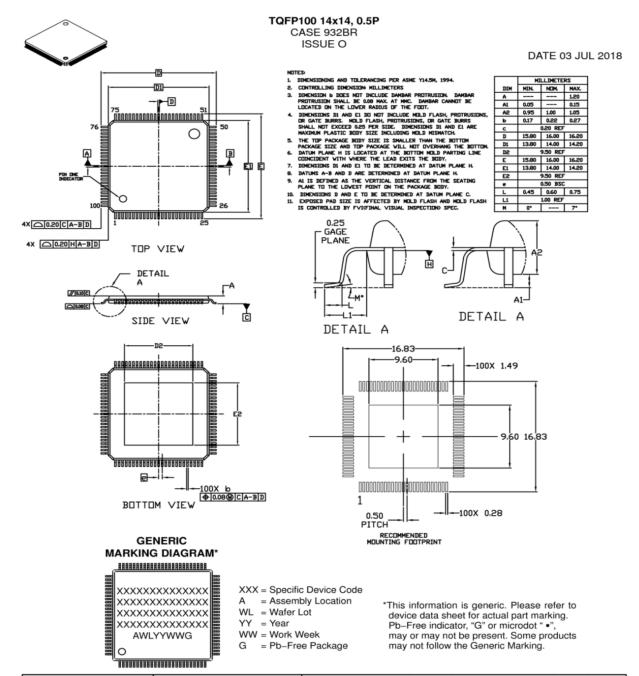

### **Physical characteristics:**

- Package type: Exposed-pad TQFP-100

- Dimensions: 14 x 14 mm

- Operating temperature range: AEC-Q100 Level 2 (-40 to +221 °F, -40 to +105 °C)

- Moisture Sensitivity Level (MSL) 3 (168 hours)

### **Table of Contents**

**OPERATION**

| FEATURES              | 1  |

|-----------------------|----|

| PREFACE               | 5  |

| HARDWARE              | 5  |

| Pin Descriptions      | 5  |

| Hardware Connections  | 7  |

| Minimal Connections   | 7  |

| External Crystal      | 8  |

| Reset Switch          | 8  |

| SPI Flash Boot Memory | 8  |

| MicroSD Boot Memory   | 9  |

| Dual Boot Memory      | 10 |

|                       |    |

11

| HOST COMMUNICATION                                          | 11 |

|-------------------------------------------------------------|----|

| P2 Monitor                                                  | 11 |

| TAQOZ                                                       | 12 |

| SYSTEM ORGANIZATION                                         | 12 |

| Cogs                                                        | 12 |

| Cog RAM                                                     | 13 |

| Register RAM                                                | 13 |

| Lookup RAM                                                  | 14 |

| Execution                                                   | 14 |

| Starting and Stopping Cogs                                  | 15 |

| Cog Attention                                               | 16 |

| Hub                                                         | 16 |

| Hub RAM                                                     | 16 |

| Cog-to-Hub RAM Interface                                    | 16 |

| System Clock                                                | 18 |

| Locks                                                       | 19 |

| CORDIC Solver                                               | 20 |

| Smart I/O Pins                                              | 21 |

| Direction and State                                         | 21 |

| I/O Pin Timing                                              | 22 |

| Pin Modes                                                   | 23 |

| I/O Pin Circuit                                             | 26 |

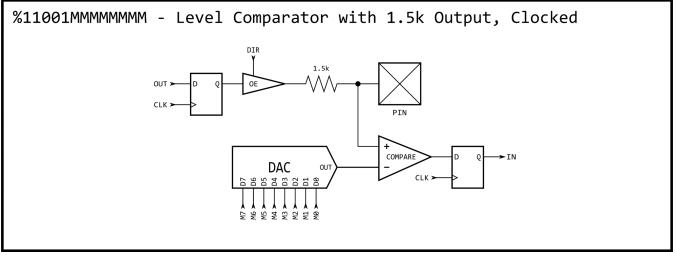

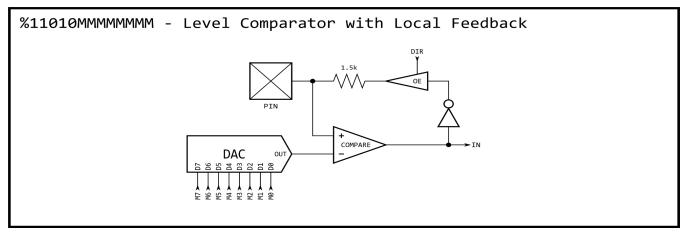

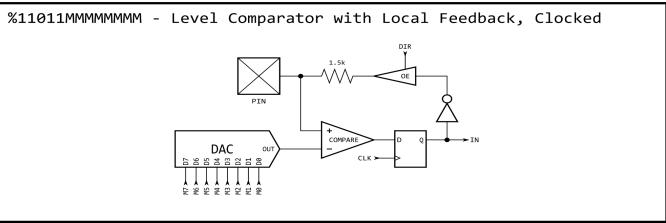

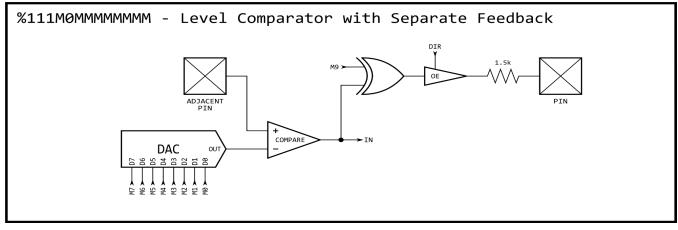

| Equivalent Schematics for Each Unique I/O Pin Configuration | 27 |

| Smart Modes                                                 | 33 |

| Rebooting                                                   | 35 |

| PROPELLER 2 ASSEMBLY LANGUAGE (PASM2) IN BRIEF              | 36 |

| Math and Logic Instructions                                 | 36 |

| Pin & Smart Pin Instructions                                | 39 |

| Branch Instructions                                         | 40 |

| Hub Control, FIFO, & RAM Instructions                       | 41 |

| Event Instructions                                          | 42 |

| PAF | RALLAX INCORPORATED                                | 50 |

|-----|----------------------------------------------------|----|

| CH  | ANGE LOG                                           | 50 |

| PAC | CKAGING                                            | 49 |

|     | AC Characteristics                                 | 48 |

|     | DC Characteristics                                 | 48 |

|     | Absolute Maximum Electrical Ratings                | 47 |

| SYS | STEM CHARACTERISTICS                               | 47 |

|     | Lookup Table, Streamer, and Misc Instructions      | 46 |

|     | Color Space Converter and Pixel Mixer Instructions | 45 |

|     | CORDIC Solver Instructions                         | 45 |

|     | Register Indirection Instructions                  | 44 |

|     | Interrupt Instructions                             | 44 |

### **PREFACE**

This datasheet provides a condensed description of the concepts, features, and hardware of the Propeller 2 multicore microcontroller. It serves as a feature reference beyond that of the single-page spec sheet.

For additional documentation and resources, including programming tools, visit <a href="www.parallax.com/P2">www.parallax.com/P2</a>. The latest version of this datasheet, along with links to a commentable Google Doc version, are available from the Documentation section. In addition, there are links to more in-depth references for the Propeller 2 and its Spin2 and PASM2 languages, which may include commentable Google Docs.

### **HARDWARE**

The Propeller 2 microcontroller's pin layout and simplified connections are described here for conceptual reference. For most prototyping uses, Parallax recommends a pre-made Propeller 2 circuit, like the P2 Edge Module (#P2-EC) or Propeller 2 Evaluation Board (#64000) that includes all the recommended connections and layout design rules. Visit the Propeller 2 section of the Parallax online store for chips, evaluation boards, accessories, and developer starter kit bundles.

### **Pin Descriptions**

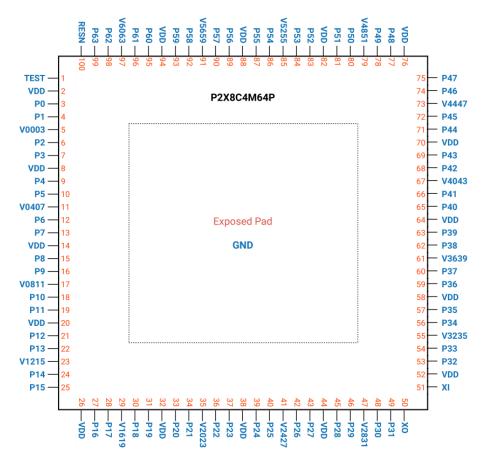

The Propeller 2 (P2X8C4M64P) features notable power and thermal considerations in its pinout:

- A large exposed under-side pad serves both as a ground reference (GND) for the core and I/O pins as well as a heatsink to cool the silicon

- Multiple power pins (VDD) spaced regularly around the chip allow clean core power references across the entire chip

- Multiple I/O power pins (Vxxyy) spaced regularly around the chip provide flexibility for the isolated, ultra-stable power references required for clean DAC and ADC I/O operations

|          | Pin Descriptions |                           |                                                                                                                                                                                                                                                                                   |  |

|----------|------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin Name | Direction        | etion V (typ) Description |                                                                                                                                                                                                                                                                                   |  |

| GND      | -                | 0                         | Exposed Pad (underside of chip); ground for core and smart pins – internally connected to exposed pad. Connect to ground plane for thermal dissipation.                                                                                                                           |  |

| TEST     | I                | 0                         | Tied to ground                                                                                                                                                                                                                                                                    |  |

| VDD      | -                | 1.8                       | Core power                                                                                                                                                                                                                                                                        |  |

| P0-63    | I/O              | 0 to 3.3                  | Smart pins. P58-P63 serve in the boot process, then general purpose after.                                                                                                                                                                                                        |  |

| Vxxyy    | -                | 3.3                       | Power for smart pins in groups of 4: Pxx through Pyy                                                                                                                                                                                                                              |  |

| хо       | 0                | -                         | Crystal Output. Provides feedback for an external crystal, or may be left disconnected depending on CLK Register settings. No external resistors or capacitors are required.                                                                                                      |  |

| XI       | I                | -                         | Crystal Input. Can be connected to the output of crystal/oscillator pack (with XO left disconnected), or to one leg of crystal (with XO connected to the other leg of crystal or resonator) depending on CLK Register settings. No external resistors or capacitors are required. |  |

| RESN     | I                | 0                         | Reset (active low). When low, resets the Propeller: all cogs disabled and I/O pins floating. Propeller restarts 3 ms after RESn transitions from low to high. Connect to a resistor to pull up to 3.3 V.                                                                          |  |

### **Hardware Connections**

### **Minimal Connections**

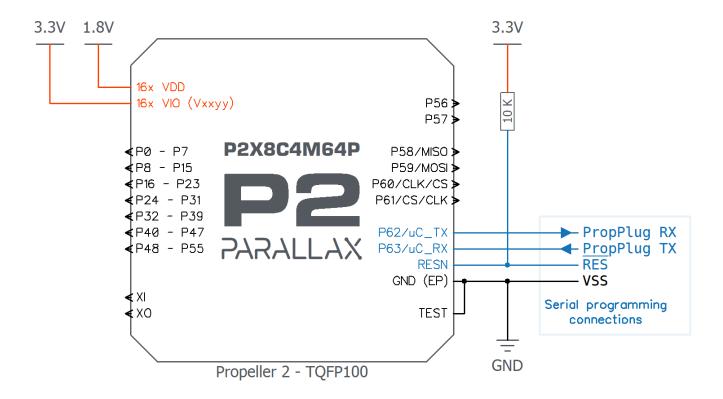

The Propeller 2 is programmed via four wires and may optionally include an external crystal, reset switch, SPI Flash and/or microSD memory.

### Minimal Propeller 2 Connections

- All VDD pins must be connected to a single 1.8 V supply.

- All Vxxyy pins must be connected to 3.3 V. The Vxxyy pins can share a common 3.3 V supply, or be split

across multiple supplies. Typically those Vxxyy pins powering analog and digital functions would have

different supplies.

- All VDD and all Vxxyy pins must have closely-located bypass caps to GND (not shown).

- The common GND (EP) pad under the chip is also used for thermal dissipation. It is recommended to connect the GND pad to a solid ground plane with multiple vias.

- TEST pin must always be connected to GND.

- RESN (reset) pin must always have a pullup resistor to 3.3 V (typically 10 K $\Omega$ ).

- Programming and debugging is achieved with a serial interface, such as the Parallax PropPlug #32201.

- Minimal connections assume no external clock source connected to XI/XO- the internal clock must be used (*adjust source code to match*). Refer to the <u>AC Characteristics</u> table for further information.

### **External Crystal**

The internal clock reference is good for very low power applications, but is also fairly low accuracy.

For applications that require higher accuracy (ex: handling high speed data) an external clock source is connected to XI/XO.

Typically a crystal would be connected between XI and XO, but an external clock source could also be connected to XI only, with common options including a clock source generator, oscillator, or MEMS resonator.

Refer to the AC Characteristics table for further information.

# Crystal $\overset{XI}{\underset{XO}{\longleftarrow}}$

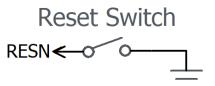

### Reset Switch

Reset Switch can be optionally included and is a convenient way to restart the Propeller 2 during development or in a final product.

The switch drives the Propeller 2 reset pin (RESN) to ground, and while held low, the Propeller 2 remains in a dormant, low-power state.

Note that the RESN pin must always be pulled high (to 3.3 V) with an external resistor, which is shown in the Minimal Connections diagram.

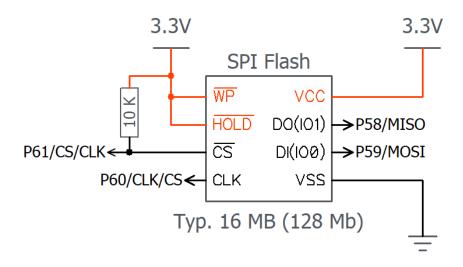

### **SPI Flash Boot Memory**

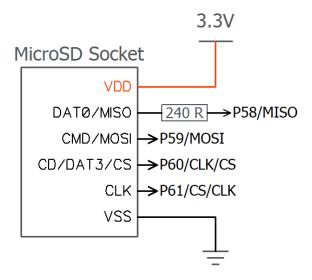

SPI Flash Boot Memory Connections

- Refer to all requirements and recommendations for Minimal Connections

- When the Propeller 2 starts up (or is reset) with this circuit, there will be a serial programming window of 100 ms, then automatic boot from SPI flash. If SPI flash boot fails, then a further serial window of 60 seconds will be followed by shutdown.

- Each Propeller 2 firmware image requires up to 512 KB. A single SPI Flash chip could hold multiple firmware images or code snippets, and/or be used for user data. The SPI Flash chip is fully available to the user program as a general memory area.

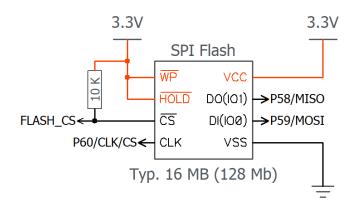

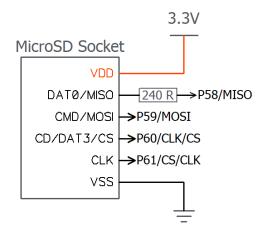

### MicroSD Boot Memory

### MicroSD Boot Memory Connections

- Refer to all requirements and recommendations for Minimal Connections

- When the Propeller 2 starts up (or is reset) with this circuit, it will automatically boot from firmware saved on the microSD card. If microSD boot fails, a further serial window of 60 seconds will be followed by shutdown.

- The microSD card must be formatted as FAT32, and the boot firmware file must be saved in the root of the microSD card with the special filename: P2 BOOT.BIX

- Each Propeller 2 firmware image requires up to 512 KB. A single microSD card could hold multiple firmware images or code snippets, and/or be used for user data. The microSD card is fully available to the user program as a general memory area.

### **Dual Boot Memory**

# Boot Mode Selection FLASH\_CS←○ ○→P61/CS/CLK

### **Dual Boot Memory Connections**

- Refer to all requirements and recommendations for <u>Minimal Connections</u>

- The Boot Mode Selection switch determines the active boot device; either SPI Flash or microSD.

- Switch closed (on) = SPI Flash boot mode: When the Propeller 2 starts up (or is reset) with this circuit, there will be a serial programming window of 100 ms, then automatic boot from firmware stored in the SPI flash memory. If SPI flash boot fails, a further serial window of 60 seconds will be followed by shutdown.

- Switch open (off) = microSD boot mode: When the Propeller 2 starts up (or is reset) with this circuit, it will automatically boot from firmware saved on the microSD card. If microSD boot fails then a further serial window of 60 seconds will be followed by shutdown.

### OPERATION

Assuming a stable power supply and "high" RESn pin, the Propeller 2 boots up using the following procedure:

- 1. Within 5 ms, the Propeller 2 loads its Bootloader into cog 0.

- 2. The Bootloader checks the Boot Pattern (configuration) on pins P59-P61 and either communicates with a host over serial, or loads (boots) an application from a connected flash chip or SD card.

- 3. All further activity is defined by the application itself. The application, and thus the developer, has complete control over modifying internal clock speed, I/O pin usage and behavior, what cogs are running at any given time, and more.

- 4. The Propeller continues running until all cogs shut each other (or themselves) down, the RESn pin goes low, or the application requests a reboot.

### HOST COMMUNICATION

In typical operation (above), the Propeller 2 will boot up with a user's pre-written Propeller application; however, the same process also allows for loading new applications or interacting with the built-in systems. Most boot patterns (pins P59-P61) trigger a serial communication window in which a host computer can talk with the Propeller 2 serially over pins P62 and P63.

To enter interactive mode from a host computer:

- Run serial terminal software (like Parallax Serial Terminal, TeraTerm, or RealTerm)

- Disable character echo ("Echo On" in Parallax Serial Terminal)

- Set to any baud rate from 9600 Bd to 2 MBd (recommended), 8 data bits, 1 stop bit, no parity

- Press and release the Propeller 2 development board's Reset button

- Type "> " (greater than followed by a space), then either Ctrl+D or the ESC key to enter P2 Monitor or TAQOZ mode, respectively

### P2 Monitor

The P2 Monitor is a built-in interactive system that allows for viewing and manipulating memory and running code. Use the P2 Monitor to explore and change current RAM contents or load and run code from microSD memory. After power-up or reset (and while preventing autorun of a flash/microSD-resident application), invoke the P2 Monitor from a terminal by typing: "> " (greater than followed by a space), then Ctrl+D.

Here is an example of listing the first 16 longs of Register RAM (in long format), by typing "000-010L":

```

*000-010L

000: FF800800 FC0C003F F606C832 FCDC041F '.....?...2....'

004: FD747E40 F0A6CA01 F426CA1F FD62CA00 '.t~@....&..b..'

008: FB6EC9FA FC0C003F FD64C428 FF0007E0 '.n....?.d.(....'

00C: FB06012C FD655229 FF0007E1 FB0420B8 '..., eR)......'

```

Here is a list of the first 16 bytes of Hub RAM (in long format), typing "0000-0010L":

```

*0000-0010L

00000: FFFFFFF FFFFFFF FFFFFFF '.....'

```

For more information, see the P2 Monitor link on the Propeller 2 Documentation Page at www.parallax.com/p2.

To switch to TAQOZ while in P2 Monitor, type ESC followed by the Enter key.

### **TAQOZ**

TAQOZ is a built-in interactive Forth language engine, based on Tachyon Forth. Use TAQOZ to explore "what ifs" and quickly exercise P2 hardware for testing or debugging. After power-up or reset (and while preventing autorun of a flash/microSD-resident application), invoke TAQOZ from a terminal by typing: "> " ESC (greater than followed by a space), then the Escape key.

Toggle pin 56 (ex: blink an LED on P56) by typing:

56 blink

(type "56 mute" to stop toggling)

...or by typing:

begin 56 high 250 ms 56 low 250 ms key until (press any key to stop toggling)

For more information, see the TAQOZ links on the Propeller 2 Documentation Page at www.parallax.com/p2.

To switch to P2 Monitor while in TAQOZ, type Ctrl+D.

### SYSTEM ORGANIZATION

The Propeller 2 includes the following subsystems.

- Cogs (processors) independent 32-bit processing units

- Register RAM private memory for cog to execute code and swiftly manipulate data

- o Lookup RAM semi-private memory for cog to execute code and manipulate data tables/streams

- Hub access manager for exclusive shared resources

- o Hub RAM shared memory for all cogs to execute code and manipulate data

- System Clock clock source for all internal components

- Locks 16 semaphore bits to coordinate exclusive access of shared resources

- o CORDIC Solver pipelined calculator for math functions

- Smart I/O Pins I/O pins with optional Smart circuit for autonomous functions

### Cogs

The Propeller contains multiple processors, called cogs. Each cog has its own RAM and can start, stop, and execute instructions independently of one another. All active cogs share the same System Clock, Hub RAM, and I/O pins.

### Cog RAM

Each cog's RAM is made of two blocks of 512 longs (512 x 32), called Register RAM and Lookup RAM, organized as shown here.

### **Register RAM**

Each cog's primary 512 x 32-bit dual-port Register RAM (Reg RAM for short) provides for code execution, fast direct register access, and special use. It is read and written as longs (4 bytes) and contains general purpose, dual-purpose, and special-purpose registers.

### **General Purpose Registers**

RAM registers \$000 through \$1EF are general-purpose registers for code and data usage.

### **Dual-purpose Registers**

RAM registers \$1F0 through \$1F7 may either be used as general-purpose registers, or may be used as special-purpose registers if their associated functions are enabled.

| Address                                   | Name                                                                    | Purpose                                                                                                                                                             |

|-------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| \$1F0<br>\$1F1<br>\$1F2<br>\$1F3<br>\$1F4 | RAM / IJMP3<br>RAM / IRET3<br>RAM / IJMP2<br>RAM / IRET2<br>RAM / IJMP1 | Interrupt call address for INT3 Interrupt return address for INT3 Interrupt call address for INT2 Interrupt return address for INT2 Interrupt call address for INT1 |

| \$1F5<br>\$1F6<br>\$1F7                   | RAM / IRET1<br>RAM / PA<br>RAM / PB                                     | Interrupt return address for INT1 CALLD-imm return, CALLPA parameter, or LOC address CALLD-imm return, CALLPB parameter, or LOC address                             |

### **Special-purpose Registers**

RAM registers \$1F8 through \$1FF give mapped access to eight special-purpose functions. In general, when specifying an address between \$1F8 and \$1FF, the PASM instruction accesses a special-purpose register, *not* just the underlying RAM.

| Address                                                     | Name                                                             | Purpose                                                                                                                                                              |

|-------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| \$1F8<br>\$1F9<br>\$1FA<br>\$1FB<br>\$1FC<br>\$1FD<br>\$1FE | PTRA<br>PTRB<br>DIRA<br>DIRB<br>OUTA<br>OUTB<br>INA <sup>1</sup> | Pointer A to Hub RAM Pointer B to Hub RAM Output enables for P31P0 Output enables for P63P32 Output states for P31P0 Output states for P63P32 Input states for P31P0 |

| \$1FF                                                       | INB <sup>2</sup>                                                 | Input states for P63P32                                                                                                                                              |

<sup>&</sup>lt;sup>1</sup> Also debug interrupt call address

### Lookup RAM

Each cog's secondary 512 x 32-bit dual-port Lookup RAM (LUT RAM for short) is read and written as longs (4 bytes). It is useful for:

- Scratch space

- Streamer access

- Bytecode execution lookup table

- Smart pin data source

- Paired-Cog communication mechanism

- Code execution

### **Scratch Space**

In contrast to Register RAM, the cog cannot directly reference Lookup RAM locations in the majority of its PASM instructions. Instead, the desired location(s) must be read or written between Lookup RAM and Register RAM using the RDLUT and WRLUT instructions, respectively. This is synonymous with other hardware architecture's scratch storage using "LOAD" and "STORE" instructions. When using the RDLUT and WRLUT instructions, the Lookup RAM's locations \$200..\$3FF are addressable as \$000..\$1FF.

### **Paired-Cog Communication Mechanism**

Adjacent cogs whose ID numbers differ by only the LSB (cogs 0 and 1, 2 and 3, etc.) can allow their Lookup RAMs to be written by the other cog via its local Lookup RAM writes. This allows adjacent cogs to share data quickly through their Lookup RAMs. Use the SETLUTS instruction to enable/disable this feature and SETSE1..4 to facilitate handshaking if necessary. Note that this adjacent cog access is implemented on the Lookup RAM's 2nd port, which is also used by the streamer in DDS/LUT modes; these are not intended to be used simultaneously.

### **Execution**

Cogs employ a five-stage pipelined execution architecture. When the execution pipeline is full, each PASM2 instruction effectively takes as little as two clock cycles to execute. If an instruction stalls for additional clock cycles, all following instructions in the pipeline are also stalled. Any instruction that is conditionally cancelled will still move through the pipeline without stalling or executing. Branch instructions cause the pipeline to be flushed, so the first instruction following the branch will take at least five clock cycles.

<sup>&</sup>lt;sup>2</sup> Also debug interrupt return address

Cogs use 20-bit addresses for their program counters (PC); the upper bit is a "don't care" bit - this affords an execution space of up to 512 KB. Depending on the value of a cog's PC, an instruction will be fetched from either its Register RAM, its Lookup RAM, or the Hub RAM.

| PASM2 Execution Regions                              |                  |         |   |  |  |

|------------------------------------------------------|------------------|---------|---|--|--|

| PC Address Instruction Source Memory Width PC Incren |                  |         |   |  |  |

| \$00000\$001FF                                       | Cog Register RAM | 32 bits | 1 |  |  |

| \$00200\$003FF                                       | Cog Lookup RAM   | 32 bits | 1 |  |  |

| \$00400\$7FFFF                                       | Hub RAM          | 8 bits  | 4 |  |  |

### **Register Execution**

When the PC is in the range of \$00000 to \$001FF, the cog fetches instructions from Cog Register RAM. This is referred to as "cog execution." There are no special considerations when branching to a cog register address.

### **Lookup Execution**

When the PC is in the range of \$00200 to \$003FF, the cog fetches instructions from Cog Lookup RAM. This is referred to as "lut execution." There are no special considerations when branching to a cog lookup address.

### **Hub Execution**

When the PC is in the range of \$00400 to \$7FFFF, the cog fetches instructions from Hub RAM. This is referred to as "hub execution mode." Special considerations are involved with hub execution.

- 1. The PC rolling beyond \$003FF <u>will not</u> initiate hub execution (it will just wrap back to \$00000); <u>a branch must occur</u> to get from register or lookup execution to hub execution.

- 2. Branching to a hub address takes a minimum of 13 clock cycles. If the instruction being branched to is not long-aligned, one additional clock cycle is required.

- 3. When executing from Hub RAM, the cog employs the FIFO hardware to spool up instructions so that a stream of instructions will be available for continuous execution. This means the FIFO cannot be used for anything else. So, during hub execution these instructions cannot be used:

RDFAST / WRFAST / FBLOCK

RFBYTE / RFWORD / RFLONG / RFVAR / RFVARS

WFBYTE / WFWORD / WFLONG

XINIT / XZERO / XCONT - when the streamer mode engages the FIFO

It is not possible to execute code from hub addresses \$00000 through \$003FF, as the cog will instead read instructions from the cog's Register RAM or Lookup RAM as indicated above.

### **Starting and Stopping Cogs**

Any cog can start or stop any other cog, or restart or stop itself. Each cog has a unique ID which can be used to start or stop it. It's also possible to start free (stopped or never started) cogs, without needing to know their IDs. This way, applications can simply start free cogs, as needed, and as those cogs retire by stopping themselves or getting stopped by others, they return to the pool of free cogs to become available again for restarting.

PASM2 code can ID its own cog (or get the running status of other cogs) with the COGID instruction, can start a cog with COGINIT, and can stop a cog with COGSTOP. Using a SETQ instruction before a COGINIT instruction sets the target cog's PTRA register to a 32-bit value; useful for pointing the new cog to runtime data or delivering a single startup value.

### **Cog Attention**

Each cog can request the attention of other cogs by using the COGATN instruction. One or more of the D operand's lower 8 bits may be set high (1) to signal the corresponding cog or cogs. For each high bit, the matching cog sees an 'attention' event for POLLATN / WAITATN / JATN / JNATN and interrupt use. The attention strobe outputs from all cogs are OR'd together to form a composite set of 8 strobes from which each cog receives its particular strobe.

In the intended use case, the cog receiving an attention request knows which other cog is strobing it and how to respond. In cases where multiple cogs may request the attention of a single cog, some messaging structure may need to be implemented in Hub RAM to differentiate requests.

### Hub

### **Hub RAM**

The globally-accessible Hub RAM can be read and written as bytes, words, and longs, in little-endian format. Hub addresses are always byte-oriented. There are no special alignment rules for words and longs in Hub RAM. Cogs can read and write bytes, words, and longs starting at any hub address, as well as execute PASM2 instructions (longs) from any hub address starting at \$400.

The last 16 KB of Hub RAM is normally addressable at both its normal address range, as well as at \$FC000..\$FFFFF. This provides a stable address space (regardless of future Propeller 2 variations) for the 16 KB of internal ROM which gets cached into the last 16 KB of Hub RAM on startup. This upper 16 KB mapping is also used by the cog debugging scheme.

The last 16 KB of RAM can be hidden from its normal address range and made read-only at \$FC000..\$FFFFF. This is useful for making the last 16 KB of RAM persistent, like ROM. It is also how debugging is realized, as the RAM mapped to \$FC000..\$FFFFF can still be written to while executing code from within debug interrupt service routines, permitting the otherwise-protected RAM to be used as debugger-application space and cog-register swap buffers for debug interrupts.

### **Cog-to-Hub RAM Interface**

Hub RAM consists of 32-bit-wide single-port RAMs with byte-level write controls. This RAM is split into slices (one per cog) that are multiplexed among all cogs. On the Propeller 2 (P2X8C4M64P), each RAM slice holds every 8th long in the composite Hub RAM. Upon every clock cycle, each cog can access the "next" RAM slice, allowing for continuous bidirectional streaming of sequential Hub RAM longs. The Hub RAM Interface diagram illustrates this process conceptually as the collective of RAM slices rotates around, each facing a new cog every clock cycle.

When a cog wants to read or write the Hub RAM, it must wait up to #cogs-1 clocks to access the initial RAM slice of interest. Once that occurs, subsequent locations (slices) can be accessed on every clock, thereafter, for continuous reading or writing of 32-bit longs.

Normally, if the cog chooses not to access the next available location upon the next clock, it must once again wait up to 7 clocks to re-align with the desired slice. However, each cog has an optional hub FIFO interface that smooths out data flow for less than 32-bits-per-clock access. This hub FIFO interface can be set for hub-RAM-read or hub-RAM-write operation to allow Hub RAM to be either sequentially read or sequentially written in any combination of bytes, words, or longs, at any rate, up to one long per clock. Regardless of the transfer frequency or the word size, the FIFO will ensure that the cog's reads or writes are all properly conducted from/to the composite Hub RAM.

### P2 Hub RAM Interface

Every cog can read/write 32 bits per clock

Cogs can access Hub RAM either via the sequential FIFO interface, or by waiting for RAM slices of interest, while yielding to the FIFO. If the FIFO is not busy (which is soon the case if data is not being read from or written to it) random accesses will have full opportunity to access the composite Hub RAM.

There are three ways the hub FIFO interface can be used, and it can only be used for one of these at a time:

- Hub execution (when the PC is \$00400..\$FFFFF)

- Streamer usage (background transfers from Hub RAM → pins/DACs, or from pins/ADCs → Hub RAM)

- Software usage (fast sequential-reading or sequential-writing instructions)

For streamer or software usage, FIFO operation must be established by a RDFAST or WRFAST instruction executed from Cog RAM (Register/Lookup, \$00000..\$003FF). After that, and while remaining in Cog RAM, the streamer can be enabled to begin moving data in the background, or the two-clock RFxxxx/WFxxxx instructions can be used to manually read and write sequential data.

The FIFO contains (#cogs+11) stages. When in read mode, the FIFO loads continuously whenever less than (#cogs+7) stages are filled, after which point, up to 5 more longs may stream in, potentially filling all stages. These metrics ensure that the FIFO never underflows, under all potential reading scenarios.

### **System Clock**

The system clock is the time base for all internal components and can be configured in several ways.

- Direct from internal slow clock (RCSLOW); a ~20 kHz oscillator is intended for low-power operation

- Direct from internal fast clock (RCFAST); a 20 MHz+ oscillator designed for minimum 20 MHz operation

- Direct from XI pin; driven externally via a clock oscillator or a crystal oscillator

- PLL-modified XI pin; driven externally via a clock oscillator or a crystal oscillator and the signal internally modified by the PLL (phase-locked loop), usually to multiple to a much higher frequency

The system clock is configured by the running Propeller 2 application using the HUBSET instruction in this format:

HUBSET ##%0000\_000E\_DDDD\_DDMM\_MMMM\_PPPP\_CCSS 'set clock mode

The bit fields (E, D, M, P, C, and S) are described in the following tables.

| PLL Setting | Value                                                                              | Effect                                                                                                                                                                                  | Notes                                                                                                                                                                                                                                                                  |

|-------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| %E          | 0/1                                                                                | PLL off/on                                                                                                                                                                              | XI input must be enabled by %CC. Allow 10ms for crystal+PLL to stabilize before switching over to PLL clock source.                                                                                                                                                    |

| %DDDDDD     | 063                                                                                | 164 division of XI pin frequency                                                                                                                                                        | This divided XI frequency feeds into the phase-frequency comparator's 'reference' input.                                                                                                                                                                               |

| %МММММММММ  | 01023                                                                              | 11024 division of<br>VCO frequency                                                                                                                                                      | This divided VCO frequency feeds into the phase-frequency comparator's 'feedback' input. This frequency division has the effect of <i>multiplying</i> the divided XI frequency (per %DDDDDD) inside the VCO. The VCO frequency should be kept within 100MHz to 350MHz. |

| %PPPP       | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15 | VCO / 2<br>VCO / 4<br>VCO / 6<br>VCO / 8<br>VCO / 10<br>VCO / 12<br>VCO / 14<br>VCO / 16<br>VCO / 18<br>VCO / 20<br>VCO / 22<br>VCO / 24<br>VCO / 26<br>VCO / 28<br>VCO / 30<br>VCO / 1 | This divided VCO frequency is selectable as the system clock when SS = %11.                                                                                                                                                                                            |

| %CC | XI status | XO status     | XI / XO impedance | XI / XO loading caps |

|-----|-----------|---------------|-------------------|----------------------|

| %00 | ignored   | float         | Hi-Z              | OFF                  |

| %01 | input     | 600-ohm drive | 1M-ohm            | OFF                  |

| %10 | input     | 600-ohm drive | 1M-ohm            | 15pF per pin         |

| %11 | input     | 600-ohm drive | 1M-ohm            | 30pF per pin         |

| %SS | Clock Source | Notes                                                                              |

|-----|--------------|------------------------------------------------------------------------------------|

| %11 | PLL          | CC != %00 and E=1, allow 10ms for crystal+PLL to stabilize before switching to PLL |

| %10 | ΧI           | CC != %00, allow 5ms for crystal to stabilize before switching to XI pin           |

| %01 | RCSLOW       | ~20 kHz, can be switched to at any time, low-power                                 |

| %00 | RCFAST       | 20 MHz+, can be switched to at any time, used on boot-up.                          |

**WARNING**: Incorrectly switching away from the PLL setting (%SS = %11) can cause a glitch which will hang the clock circuit. In order to safely switch, always start by switching to an internal oscillator using either HUBSET #\$F0 (for RCFAST) or HUBSET #\$F1 (for RCSLOW).

### **PLL Example**

The PLL divides the XI pin frequency from 1 to 64, then multiplies the resulting frequency from 1 to 1024 in the VCO. The VCO frequency can be used directly, or divided by 2, 4, 6, ...30, to get the final PLL clock frequency which can be used as the system clock.

The PLL's VCO is designed to run between 100 MHz and 200 MHz and should be kept within that range.

$$VCO = \frac{Freq(XI) \times (\%MMMMMMMMMM + 1)}{(\%DDDDDD + 1)}$$

$$PLL = if(\%PPPP = 15) \Rightarrow VCO$$

$$PLL = if(\%PPPP \neq 15) \Rightarrow \frac{VCO}{(\%PPPP + 1) \times 2}$$

Let's say you have a 20 MHz crystal attached to XI and XO and you want to run the Prop2 at 148.5 MHz. You could divide the crystal by 40 (%DDDDDD = 39) to get a 500 kHz reference, then multiply that by 297 (%MMMMMMMMM = 296) in the VCO to get 148.5 MHz. You would set %PPPP to %1111 to use the VCO output directly. The configuration value would be %1\_100111\_0100101000\_1111\_10\_11. The last two 2-bit fields select 15 pf crystal mode and the PLL. In order to realize this clock setting, though, it must be done over a few steps:

```

HUBSET #$F0 'set 20 MHz+ (RCFAST) mode

HUBSET ##%1_100111_0100101000_1111_10_00 'enable crystal+PLL, stay in RCFAST mode

WAITX ##20_000_000/100 'wait ~10ms for crystal+PLL to stabilize

HUBSET ##%1_100111_0100101000_1111_10_11 'now switch to PLL running at 148.5 MHz

```

The clock selector controlled by the %SS bits has a deglitching circuit which waits for a positive edge on the old clock source before disengaging, holding its output high, and then waiting for a positive edge on the new clock source before switching over to it. It is necessary to select mode %00 or %01 while waiting for the crystal and/or PLL to settle into operation, before switching over to either.

### Locks

For application-defined cog coordination, the hub provides a pool of 16 semaphore bits, called locks. Cogs may use locks, for example, to manage exclusive access of a resource or to represent an exclusive state, shared among multiple cogs. What a lock represents is completely up to the application using it; they are a means of allowing one cog at a time the exclusive status of 'owner' of a particular lock ID. In order to be useful, all participant cogs must agree on a lock's ID and what purpose it serves.

The LOCK instructions are:

```

LOCKNEW D {WC}

LOCKRET {#}D

LOCKTRY {#}D {WC}

LOCKREL {#}D {WC}

```

### Lock Usage

In order to use a lock, one cog must first allocate a lock with LOCKNEW and communicate that lock's ID with other cooperative cogs. Cooperative cogs then use LOCKTRY and LOCKREL to respectively take or release ownership of the state which that lock represents. If the lock is no longer needed by the application, it may be returned to the unallocated lock pool by executing LOCKRET. A cog may allocate more than one lock.

At any time, a cog may attempt to own a lock (ie: the state that lock represents) by using LOCKTRY. The Hub grants or denies ownership in response, ensuring that, at most, one cog owns the lock at any time. If a cog is granted ownership, it can perform the task defined for that lock and then use LOCKRET to release ownership, allowing any other cog to attempt ownership. Only the cog that has taken ownership of the lock can release it; however, a lock will also be implicitly released if the owner cog is stopped (COGSTOP) or restarted (COGINIT).

### **CORDIC Solver**

The Hub contains a 54-stage pipelined CORDIC solver (Coordinate Rotation Digital Computer) that can compute the following functions for all cogs:

- 32 x 32 unsigned multiply with 64-bit product

- 64 / 32 unsigned divide with 32-bit quotient and 32-bit remainder

- Square root of 64-bit unsigned value with 32-bit result

- 32-bit signed (X, Y) rotation around (0, 0) by a 32-bit angle with 32-bit signed (X, Y) results

- 32-bit signed (X, Y) to 32-bit (length, angle) cartesian to polar operation

- 32-bit (length, angle) to 32-bit signed (X, Y) polar to cartesian operation

- 32-bit unsigned integer to 5:27-bit logarithm

- 5:27-bit logarithm to 32-bit unsigned integer

Each cog can issue one CORDIC instruction per its hub access window (which occurs once every eight clocks) and retrieve the result 55 clocks later via the GETQX and GETQY instructions. For faster throughput, cogs can take advantage of the hub access window and CORDIC pipeline relationship to issue a stream of CORDIC instructions interleaved with retrieving corresponding results, achieving up to one CORDIC result every eight clocks. Each cog's active CORDIC instructions and forthcoming results are completely isolated from each other, as well as from other cogs; however, each result must be retrieved on time else it will be overwritten by the following result, if any.

### Multiply

Use the QMUL instruction to multiply two unsigned 32-bit numbers together and retrieve the CORDIC result with the GETQX and GETQY instructions (for lower and upper long, respectively).

### Divide

Use the QDIV or QFRAC instruction (either with optional preceding SETQ instruction) to divide a 64-bit numerator by a 32-bit denominator, then retrieve the CORDIC results with the GETQX and GETQY instructions (for quotient and remainder, respectively).

### **Square Root**

Use the QSQRT instruction on a 64-bit number and retrieve the square root CORDIC result with the GETQX instruction.

### (X, Y) Rotation

Use the SETQ instruction followed by the QROTATE instruction to rotate a 32-bit signed Y and X point pair by an unsigned 32-bit angle and retrieve the CORDIC results with the GETQX and GETQY instructions for X and Y, respectively.

### (X, Y) to (length, angle)

Use the QVECTOR instruction to convert a (X, Y) cartesian coordinate into (length, angle) polar coordinate and retrieve the CORDIC results with the GETQX and GETQY instructions (for length and angle, respectively).

### (length, angle) to (X, Y)

Use the QROTATE instruction to convert a (length, angle) polar coordinate into (X, Y) cartesian coordinate and retrieve the CORDIC results with the GETQX and GETQY instructions (for X and Y, respectively).

### Logarithm

Use the QLOG instruction on an unsigned 32-bit integer and retrieve the 5:27-bit logarithm CORDIC result (5-bit exponent and 27-bit mantissa) with the GETQX instruction.

### **Exponent**

Use the QEXP instruction on a 5:27-bit logarithm and retrieve the unsigned 32-bit integer CORDIC result with the GETOX instruction.

### **Smart I/O Pins**

Every I/O pin features versatile digital and analog capabilities as well as autonomous state machine functions that would otherwise require processor time to perform. The combination of *pin* modes and *smart* modes provides adept functionality for application design, increasing the Propeller 2 potential beyond what multicore architecture alone provides. There are 24 low-level pin modes and 34 high-level smart modes.

Each I/O pin's behavior is described by the combination of four settings: 1) direction (input/output), 2) state (output drive / input sense), 3) pin mode, and 4) smart mode (optional).

### **Direction and State**

In simplest form, I/O pins are controlled via dedicated cog registers and the instructions that affect them.

| I/O Pin Registers |             |                                                                                     |  |  |

|-------------------|-------------|-------------------------------------------------------------------------------------|--|--|

| Register          | Cog Address | Purpose                                                                             |  |  |

| DIRA              | \$1FA       | Output enable bits for P0P31 (active high)                                          |  |  |

| DIRB              | \$1FB       | Output enable bits for P32P63 (active high)                                         |  |  |

| OUTA              | \$1FC       | Output state bits for P0P31 (corresponding DIRA bit must be high to enable output)  |  |  |

| OUTB              | \$1FD       | Output state bits for P32P63 (corresponding DIRB bit must be high to enable output) |  |  |

| INA               | \$1FE       | Input state bits for P0P31                                                          |  |  |

| INB               | \$1FF       | Input state bits for P32P63                                                         |  |  |

General-purpose and special pin instructions can write to **DIRA / DIRB / OUTA / OUTB** to affect pin input/output behavior and can read from **INA / INB** to retrieve pin states. General-purpose instructions operate on the entire 32-bit register (all pins) while the special pin instructions operate on a single bit (pin) within them.

| Special Pin Instructions                           |                                             |  |  |  |

|----------------------------------------------------|---------------------------------------------|--|--|--|

| Instructions                                       | Purpose                                     |  |  |  |

| DIRL/DIRH/DIRC/DIRNC/DIRZ/DIRNZ/DIRRND/DIRNOT {#}D | Affect pin D bit in DIRx                    |  |  |  |

| OUTL/OUTH/OUTC/OUTNC/OUTZ/OUTNZ/OUTRND/OUTNOT {#}D | Affect pin D bit in OUTx                    |  |  |  |

| FLTL/FLTH/FLTC/FLTNC/FLTZ/FLTNZ/FLTRND/FLTNOT {#}D | Affect pin D bit in OUTx, clear bit in DIRx |  |  |  |

| DRVL/DRVH/DRVC/DRVNC/DRVZ/DRVNZ/DRVRND/DRVNOT {#}D | Affect pin D bit in OUTx, set bit in DIRx   |  |  |  |

| TESTP {#}D WC/WZ/ANDC/ANDZ/ORC/ORZ/XORC/XORZ       | Read pin D bit in INx and affect C or Z     |  |  |  |

| TESTPN {#}D WC/WZ/ANDC/ANDZ/ORC/ORZ/XORC/XORZ      | Read pin D bit in !INx and affect C or Z    |  |  |  |

The selected pin mode and smart mode (if other than the default) may override some of the above, as described in their respective sections, later.

### I/O Pin Timing

Between each physical I/O pin and the cog(s) controlling them, there is a chain of three single-bit registers (reg). The live signal (input or output) traverses through this chain on the way to its destination as described below.

When a DIRx/OUTx bit is changed by any instruction, it takes *three* additional clocks after the instruction before the pin starts transitioning to the new state. Here this delay is demonstrated using DRVH:

When an **IN**x register is read by an instruction, it will reflect the state of the pins registered *three* clocks before the start of the instruction. Here this delay is demonstrated using **TESTB**:

When a TESTP/TESTPN instruction is used to read a pin, the value read will reflect the state of the pin registered *two* clocks before the start of the instruction. Effectively, TESTP/TESTPN get fresher INx data than is available via the INx registers:

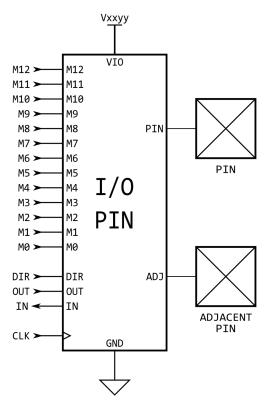

### Pin Modes

Each I/O pin has 13 low-level pin mode configuration bits which determine the mode of operation (1 of 24) for its 3.3 V circuit. The pin mode is set using the WRPIN instruction, where the 13 'M' bits within the instruction's D operand specifies the pin mode configuration. Note that in some smart pin modes, the configuration bits are partially overwritten to set things like DAC values.

The format of the WRPIN's D operand value is:

### %AAAA\_BBBB\_FFF\_MMMMMMMMMMMMMTT\_SSSSS\_0

- A = PIN input selector

- B = ADJ input selector

- F = PIN and ADJ input logic/filtering (applied to result of PIN and ADJ input selectors)

- M = pin mode

- T = pin DIR/OUT control (default = %00)

- S = smart mode

| (A) PIN or (B) ADJ Input Selector |                                 |  |  |  |

|-----------------------------------|---------------------------------|--|--|--|

| %AAAA<br>%BBBB                    | Selection                       |  |  |  |

| 0xxx                              | true (default)                  |  |  |  |

| 1xxx                              | inverted                        |  |  |  |

| x000                              | this pin's read state (default) |  |  |  |

| x001                              | relative +1 pin's read state    |  |  |  |

| x010                              | relative +2 pin's read state    |  |  |  |

| x011                              | relative +3 pin's read state    |  |  |  |

| x100                              | this pin's OUT bit from cogs    |  |  |  |

| x101                              | relative -3 pin's read state    |  |  |  |

| x110                              | relative -2 pin's read state    |  |  |  |

| x111                              | relative -1 pin's read state    |  |  |  |

| (F) PIN and ADJ Logic/Filtering |                                                 |  |  |  |

|---------------------------------|-------------------------------------------------|--|--|--|

| %FFF                            | Logic/Filter                                    |  |  |  |

| 000                             | A, B (default)                                  |  |  |  |

| 001                             | A AND B, B                                      |  |  |  |

| 010                             | A OR B, B                                       |  |  |  |

| 011                             | A XOR B, B                                      |  |  |  |

| 100                             | A, B, both filtered using global filt0 settings |  |  |  |

| 101                             | A, B, both filtered using global filt1 settings |  |  |  |

| 110                             | A, B, both filtered using global filt2 settings |  |  |  |

| 111                             | A, B, both filtered using global filt3 settings |  |  |  |

The resultant 'A' will drive the IN signal in non-smart-pin modes.

### WRPIN D[20:8] Configuration M[12:0] Input Pin Output1 0000\_CIOHHHLLL Pin Logic OUT 0001\_CIOHHHLLL Pin Logic Input 0010\_CIOHHHLLL Adi Logic Input 0011\_CIOHHHLLL Pin Schmitt OUT 0100\_CIOHHHLLL Pin Schmitt Input 0101\_CIOHHHLLL Adj Schmitt Input 0110\_CIOHHHLLL Pin > Adj OUT 0111\_CIOHHHLLL Pin > Adj Input 100000\_OHHHLLL ADC, GND OUT 100001\_0HHLLL ADC, Vxxyy OUT 100010\_0HHHLLL ADC, float OUT 100011\_0HHLLL ADC, Pin 1x OUT 100100\_OHHHLLL ADC, Pin 3.16x OUT 100101\_0HHHLLL ADC, Pin 10x OUT 100110\_0HHHLLL ADC, Pin 31.6x OUT 100111\_0HHHLLL ADC, Pin 100x OUT

ADC, Pin 1x<sup>3</sup>

ADC, Pin 1x  $^{3}$

ADC, Pin 1x  $^{3}$

ADC, Pin 1x<sup>3</sup>

Pin > D

Pin > D

Adj > D

Adj > D

| Resulting Internal Configuration |                 |     |     |          |            |

|----------------------------------|-----------------|-----|-----|----------|------------|

| CIOHHHLLL                        | OE <sup>2</sup> | DAC | ADC | ADC Mode | Comparator |

| CIOHHHLLL                        | DIR             | 0   | 0   |          | 0          |

| CIOHHHLLL                        | DIR             | 0   | 0   |          | 0          |

| CIOHHHLLL                        | DIR             | 0   | 0   |          | 0          |

| CIOHHHLLL                        | DIR             | 0   | 0   |          | 0          |

| CIOHHHLLL                        | DIR             | 0   | 0   |          | 0          |

| CIOHHHLLL                        | DIR             | 0   | 0   |          | 0          |

| CIOHHHLLL                        | DIR             | 0   | 0   |          | Pin > Adj  |

| CIOHHHLLL                        | DIR             | 0   | 0   |          | Pin > Adj  |

| 100HHHLLL                        | DIR             | 0   | 1   | 000      | 0          |

| 100HHHLLL                        | DIR             | 0   | 1   | 001      | 0          |

| 100HHHLLL                        | DIR             | 0   | 1   | 010      | 0          |

| 100HHHLLL                        | DIR             | 0   | 1   | 011      | 0          |

| 100HHHLLL                        | DIR             | 0   | 1   | 100      | 0          |

| 100HHHLLL                        | DIR             | 0   | 1   | 101      | 0          |

| 100HHHLLL                        | DIR             | 0   | 1   | 110      | 0          |

| 100HHHLLL                        | DIR             | 0   | 1   | 111      | 0          |

| 10xxxxxxx                        | 0               | DIR | OUT | 011      | 0          |

| 10xxxxxxx                        | 0               | DIR | OUT | 011      | 0          |

| 10xxxxxxx                        | 0               | DIR | OUT | 011      | 0          |

| 10xxxxxxx                        | 0               | DIR | OUT | 011      | 0          |

| C00001001                        | DIR             | 0   | 0   |          | Pin > D    |

| C01001001                        | DIR             | 0   | 0   |          | Pin > D    |

| C00001001                        | DIR             | 0   | 0   |          | Adj > D    |

| C01001001                        | DIR             | 0   | 0   |          | Adj > D    |

<sup>&</sup>lt;sup>1</sup> OUT means output latch bit drives output; Input means the 'Input' column's item drives output

DAC 990 Ω, 3.3 V

DAC 600 Ω, 2.0 V

DAC 123.75 Ω, 3.3 V

DAC 75 Ω, 2.0 V

OUT,  $1.5 \text{ k}\Omega$

!Input,  $1.5 k\Omega$

Input, 1.5 kΩ

!Input, 1.5 kΩ

10100\_DDDDDDDD

10101\_DDDDDDDD

10110\_DDDDDDDD

10111\_DDDDDDDDD

1100\_CDDDDDDDD

1101\_CDDDDDDDD

1110\_CDDDDDDDD

1111\_CDDDDDDDD

| IN/OUT                 | ННН        | Drive          | OE = digital output enable (when DIR bit high)                                                  |        |        |           |                                                                                                                 |

|------------------------|------------|----------------|-------------------------------------------------------------------------------------------------|--------|--------|-----------|-----------------------------------------------------------------------------------------------------------------|

| Live 1                 | LLL        |                | DAC = digital to analog converter enable (when DIR bit high)                                    |        |        |           |                                                                                                                 |

| Clocked <sup>2</sup>   | 000<br>001 | Fast<br>1.5 kΩ | ADC = analog to digital converter enable (fixed, or when <b>0UT</b> bit high)                   |        |        |           |                                                                                                                 |

| IN                     | 010<br>011 | 010   15 kΩ    | OUT = output latch bit; 0: low, 1: high. Exception: DAC modes use OUT as 0: disable, 1: enable. |        |        |           |                                                                                                                 |

| True<br>Not (inverted) | 101        |                | 100 µA                                                                                          | 100 μΑ | 100 µA | 01 100 μA | DIR = direction bit; 0: input (float), 1: output (drive) Exception: DAC modes use DIR as 0: disable, 1: enable. |

| Output                 |            |                | DDDDDDD and D = DAC Level                                                                       |        |        |           |                                                                                                                 |

| True<br>Not (inverted) |            |                |                                                                                                 |        |        |           |                                                                                                                 |

(M) Pin Mode

<sup>&</sup>lt;sup>2</sup>OE is digital logic output enable only; analog output is indicated in the DAC column

$<sup>^{3}</sup>$  if **OUT** bit = 1

<sup>&</sup>lt;sup>1</sup> used for feedback operations; provides continuous (non-clocked) signal

<sup>&</sup>lt;sup>2</sup> signal updates on clock edge only

|                 | (T) Pin DIR/OUT Control                                         |  |  |  |  |  |

|-----------------|-----------------------------------------------------------------|--|--|--|--|--|

| Default (%TT =  | Default (%TT = 00)                                              |  |  |  |  |  |

| for odd pins    | OTHER' = even pin's NOT (inverted) output state (diff source)   |  |  |  |  |  |

| for even pins   | 'OTHER' = unique pseudo-random bit (noise source)               |  |  |  |  |  |

| for all pins    | 'SMART' = smart pin output which overrides <b>0UT</b> /OTHER    |  |  |  |  |  |

| 'DAC_MODE' is   | enabled when M[12:10] = %101                                    |  |  |  |  |  |

| 'BIT_DAC' outp  | uts {2{M[7:4]}} for 'high' or {2{M[3:0]}} for 'low' in DAC_MODE |  |  |  |  |  |

| for smart pin r | node "off" (%SSSSS = %00000)                                    |  |  |  |  |  |

| DIR ena         | bles output                                                     |  |  |  |  |  |

| for non-        | DAC_MODE                                                        |  |  |  |  |  |

| 0x              | OUT drives output                                               |  |  |  |  |  |

| 1x              | OTHER drives output                                             |  |  |  |  |  |

| for DAC         | MODE                                                            |  |  |  |  |  |

| 00              | DIR enables DAC, M[7:0] sets DAC level                          |  |  |  |  |  |

| 01              | OUT enables ADC, M[3:0] selects cog DAC channel                 |  |  |  |  |  |

| 10              | OUT drives BIT_DAC                                              |  |  |  |  |  |

| 11              | OTHER drives BIT_DAC                                            |  |  |  |  |  |

| for smart pin r | node "on" (%SSSSS > %00000)                                     |  |  |  |  |  |

| х0              | output disabled, regardless of DIR                              |  |  |  |  |  |

| x1              | output enabled, regardless of DIR                               |  |  |  |  |  |

| for DAC smart   | pin modes (%SSSSS = %00001%00011)                               |  |  |  |  |  |

| 0x              | OUT enables DAC in DAC_MODE, M[7:0] overridden                  |  |  |  |  |  |

| 1x              | OTHER enables DAC in DAC_MODE, M[7:0] overridden                |  |  |  |  |  |

| for non-DAC s   | mart pin modes (%SSSSS = %00100%11111)                          |  |  |  |  |  |

| 0x              | SMART/OUT drives output, or BIT_DAC if DAC_MODE                 |  |  |  |  |  |

| 1x              | SMART/OTHER drives output, or BIT_DAC if DAC_MODE               |  |  |  |  |  |

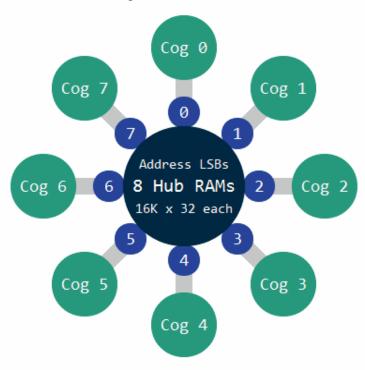

### I/O Pin Circuit

Below is a diagram of a single I/O pin circuit which is powered from its local 3.3V supply pin (Vxxyy). It connects to its own physical pin (PIN), as well as its adjacent odd or even pin (ADJ). I/O Pins P0 and P1 see each other as adjacent pins, as do P2 and P3, etc.

P0..P63

(64 Instances)

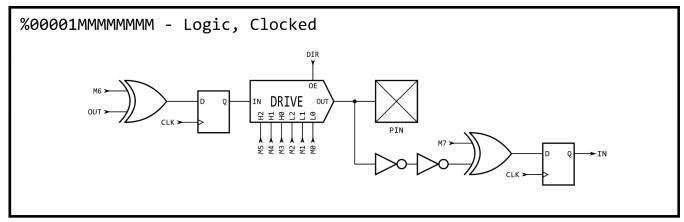

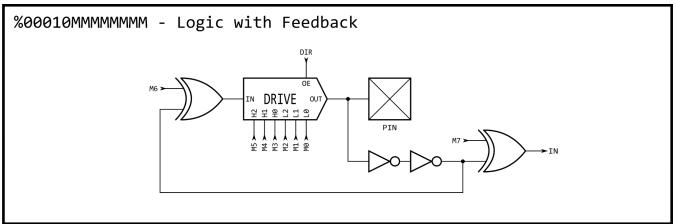

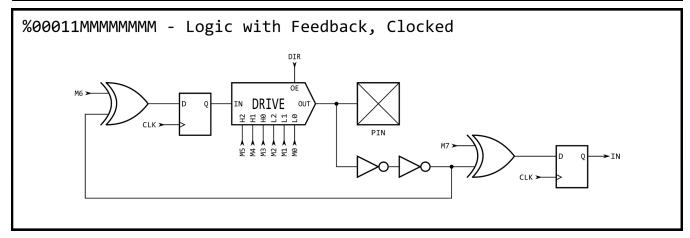

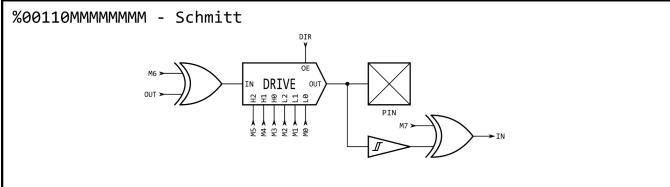

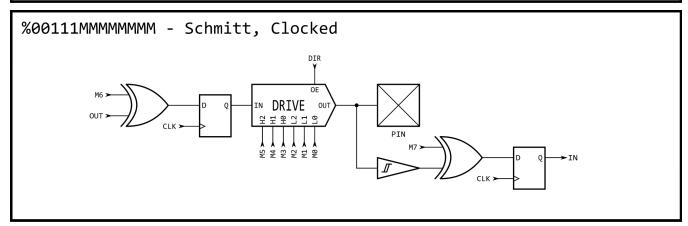

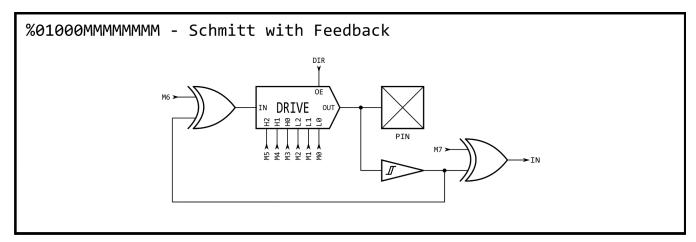

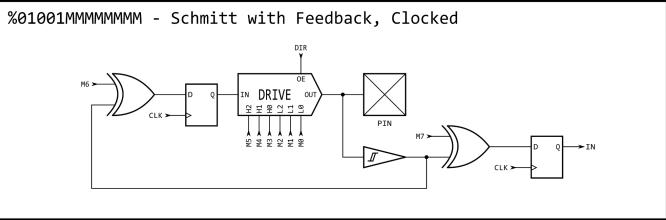

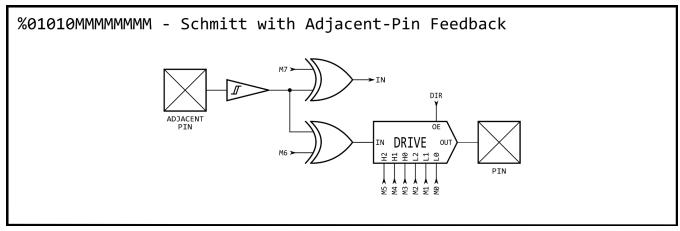

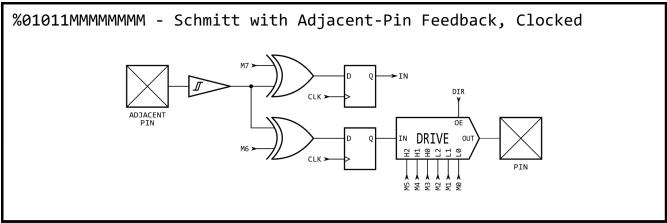

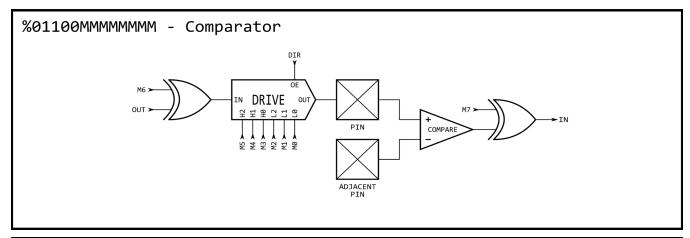

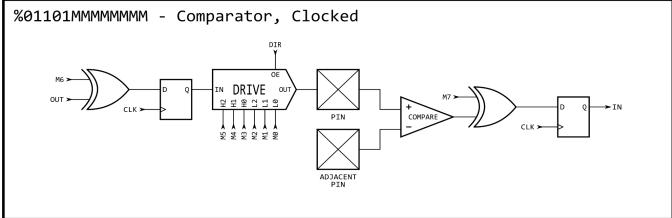

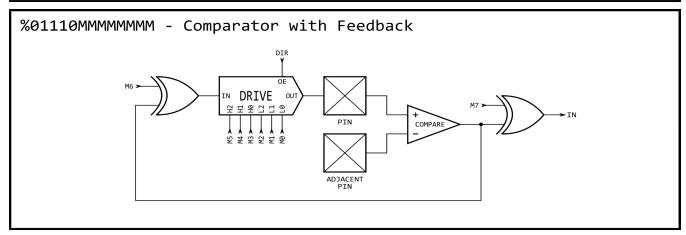

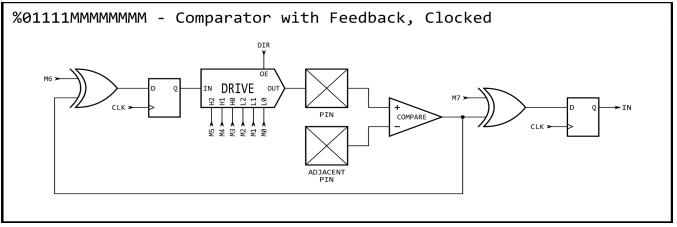

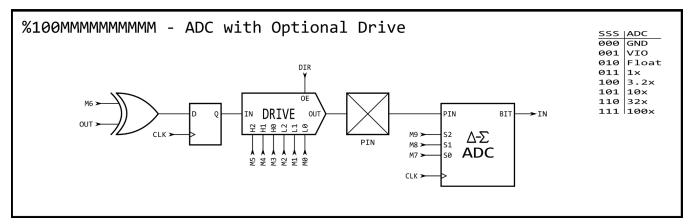

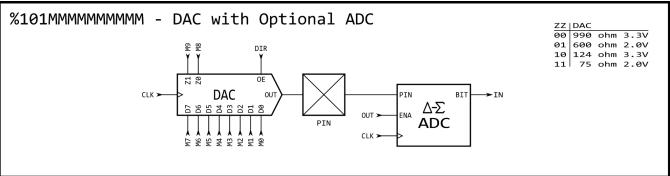

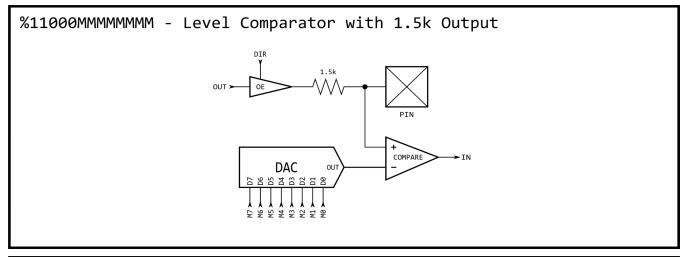

### **Equivalent Schematics for Each Unique I/O Pin Configuration**

#

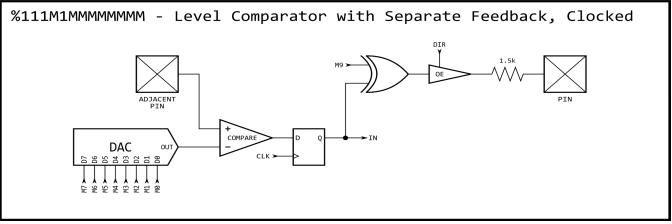

# %00101MMMMMMMM - Logic with Adjacent-Pin Feedback, Clocked

### **Smart Modes**

Each I/O pin has built-in 'smart pin' circuitry which (when enabled) performs one of 34 different autonomous functions on the pin. Smart pins free the cogs from the need to micromanage many I/O operations by providing high-bandwidth concurrent hardware functions that cogs could otherwise not perform as well through I/O pin manipulating instructions.

In normal operation, an I/O pin's output enable is controlled by its **DIR** bit, its output state is controlled by its **OUT** bit, and its **IN** bit returns the pin's read state. With smart pin mode enabled, its **DIR** bit is used as an active-low reset signal to the smart pin circuitry, while the output enable state is controlled by a configuration bit. In some modes, the smart pin circuit takes over driving the output state, in which case the **OUT** bit gets ignored. Its **IN** bit serves as a flag to indicate to the cog(s) that the smart pin has completed some function or an event has occurred, and acknowledgment is perhaps needed.

To configure a smart pin, first set its **DIR** bit to low (holding it in reset) then use **WRPIN**, **WXPIN**, and **WYPIN** to establish the mode and related parameters. Once configured, **DIR** can be raised high and the smart pin will begin operating. After that, depending on the mode, you may feed it new data via **WXPIN/WYPIN** or retrieve results using **RDPIN/RQPIN**. These activities are usually coordinated with the IN signal going high; explained later.

Note that while a smart pin is configured, the %TT bits (of the WRPIN instruction's D operand) will govern the pin's output enable, regardless of the DIR state.

Smart pins have four 32-bit registers inside of them:

| Smart Pin Registers |                                                                |  |  |

|---------------------|----------------------------------------------------------------|--|--|

| 32-bit Register     | Purpose                                                        |  |  |

| Mode                | smart pin mode, as well as low-level I/O pin mode (write-only) |  |  |

| Х                   | mode-specific parameter (write-only)                           |  |  |

| Υ                   | mode-specific parameter (write-only)                           |  |  |

| Z                   | mode-specific result (read-only)                               |  |  |

These four registers are written and read via the following 2-clock instructions, in which S/# is used to select the pin number (0..63) and D/# is the 32-bit data conduit:

```

WRPIN

D/#,S/#

- Set smart pin S/# mode to D/#, ack pin

WXPIN

- Set smart pin S/# parameter X to D/#, ack pin

D/#,S/#

WYPIN

D/#,S/#

- Set smart pin S/# parameter Y to D/#, ack pin

RDPIN

D,S/# {WC}

- Get smart pin S/# result Z into D, flag into C, ack pin

RQPIN

- Get smart pin S/# result Z into D, flag into C, don't ack pin

D,S/# {WC}

AKPIN

S/#

- Acknowledge pin S/#

```

Each smart pin has a 34-bit input bus and a 33-bit output bus that connect it to the cogs.

To configure and control smart pins, each cog writes data and acknowledgement signals to the smart pin input bus. Each smart pin OR's all incoming 34-bit buses from the collective of cogs in the same way **DIR** and **OUT** bits are OR'd before going to the pins. Therefore, if you intend to have multiple cogs execute **WRPIN / WXPIN / WYPIN / RDPIN / AKPIN** instructions on the same smart pin, you must be sure that they do so at different times, in order to avoid clobbering each other's bus data. Reading a smart pin with **RDPIN** can cause the same conflict; however,

any number of cogs can read a smart pin simultaneously without bus conflict by using RQPIN ('read quiet'), since it does not utilize the smart pin input bus for acknowledgement signalling (like RDPIN does).

Each smart pin writes to it's output bus to convey its Z result and a special flag. The RDPIN and RQPIN multiplex and read these buses, so that a pin's Z result is read into D and its special flag can be read into C. C will be either a mode-related flag or the MSB of the Z result.

When a mode-related event occurs in a smart pin, it raises its IN signal to alert the cog(s) that new data is ready, new data can be loaded, or some process has finished. A cog can test for this signal via the TESTP instruction and can acknowledge a smart pin by executing a WRPIN, WYPIN, WYPIN, RDPIN, or AKPIN instruction for it. This acknowledgement causes the smart pin to lower its IN signal so that it can be raised again on the next event. After a WRPIN / WYPIN / RDPIN / AKPIN, it takes two clocks for IN to drop, before it can be polled again.

A smart pin can be reset at any time, without the need to reconfigure it, by clearing and then setting its DIR bit.

To return a pin to normal mode, do a 'WRPIN #0, pin'.

|                    | (S) Smart Pin Modes                                                 |                                 |  |  |  |

|--------------------|---------------------------------------------------------------------|---------------------------------|--|--|--|

| %SSSSS             | Mode                                                                | Note                            |  |  |  |

| 00000              | smart pin off (default)                                             |                                 |  |  |  |

| 00001              | long repository                                                     | M[12:10] != %101 (not DAC_MODE) |  |  |  |

| 00010              | long repository                                                     | M[12:10] != %101 (not DAC_MODE) |  |  |  |

| 00011              | long repository                                                     | M[12:10] != %101 (not DAC_MODE) |  |  |  |

| 00001              | DAC noise                                                           | M[12:10] = %101 (DAC_MODE)      |  |  |  |

| 00010              | DAC 16-bit dither, noise                                            | M[12:10] = %101 (DAC_MODE)      |  |  |  |

| 00011              | DAC 16-bit dither, PWM                                              | M[12:10] = %101 (DAC_MODE)      |  |  |  |

| 00100¹             | pulse/cycle output                                                  |                                 |  |  |  |

| 00101 <sup>1</sup> | transition output                                                   |                                 |  |  |  |

| 00110 <sup>1</sup> | NCO frequency                                                       |                                 |  |  |  |

| 00111 <sup>1</sup> | NCO duty                                                            |                                 |  |  |  |

| 01000¹             | PWM triangle                                                        |                                 |  |  |  |

| 01001 <sup>1</sup> | PWM sawtooth                                                        |                                 |  |  |  |

| 01010 <sup>1</sup> | PWM switch-mode power supply, V and I feedback                      |                                 |  |  |  |

| 01011              | periodic/continuous: A-B quadrature encoder                         |                                 |  |  |  |

| 01100              | periodic/continuous: inc on A-rise & B-high                         |                                 |  |  |  |

| 01101              | periodic/continuous: inc on A-rise & B-high / dec on A-rise & B-low |                                 |  |  |  |

| 01110              | periodic/continuous: inc on A-rise {/ dec on B-rise}                |                                 |  |  |  |

| 01111              | periodic/continuous: inc on A-high {/ dec on B-high}                |                                 |  |  |  |

| 10000              | time A-states                                                       |                                 |  |  |  |

| 10001              | time A-highs                                                        |                                 |  |  |  |

| 10010              | time X A-highs/rises/edges -or- timeout on X A-high/rise/edge       |                                 |  |  |  |

| 10011              | for X periods, count time                     |                           |