#### Is Now Part of

# ON Semiconductor®

# To learn more about ON Semiconductor, please visit our website at www.onsemi.com

Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to Fairchild <a href="guestions@onsemi.com">guestions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officer

October 2014

# FAN6208 Secondary-Side Synchronous Rectifier Controller for LLC Topology

#### **Features**

- Specialized SR Controller for LLC or LC Resonant Converters

- Secondary-Side Timing Detection with Timing Estimator

- Gate-Shrink Function to Prevent Shoot-Through During Load and Line Transient

- Green-Mode Function for Higher Efficiency at Light-Load Condition

- Programmable Dead Time between Primary-Side Gate Drive Signal and SR Drive Signal

- Advanced Output-Short / Overload Protection Based on the Feedback Information

- Internal Over-Temperature Protection (OTP)

- V<sub>DD</sub> Pin Over-Voltage Protection (OVP)

# **Applications**

- LCD TV

- PC Power

- Open-Frame SMPS

### **Description**

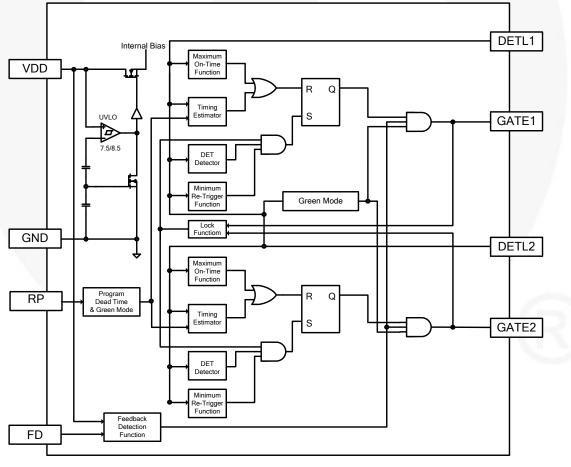

FAN6208 is a synchronous rectification (SR) controller for isolated LLC or LC resonant converters that can drive two individual SR MOSFETs emulating the behavior of rectifier diodes. FAN6208 measures the SR conduction time of each switching cycle by monitoring the drain-to-source voltage of each SR and determines the optimal timing of the SR gate drive. FAN6208 uses the change of opto-coupler diode current to adaptively shrink the duration of SR gate drive signals during load transients to prevent shoot-through. To improve lightload efficiency, Green-Mode operation is employed, which disables the SR drive signals, minimizing gate drive power consumption at light-load condition.

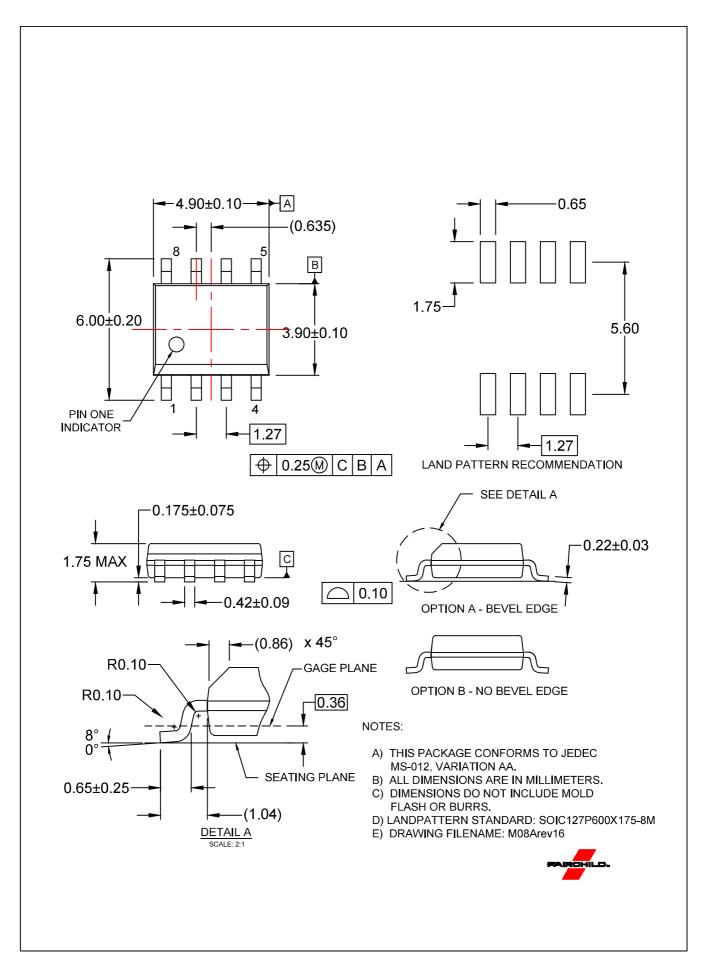

Optimal timing circuits and protection functions are integrated in an 8-pin SOP package, which allows high-efficiency power supply design with fewer components.

#### **Related Resources**

FAN6208 Product Folder

# **Ordering Information**

| Part Number | <b>Operating Temperature Range</b> | Package                           | Packing Method |  |

|-------------|------------------------------------|-----------------------------------|----------------|--|

| FAN6208MY   | -40°C to +105°C                    | 8-Pin Small Outline Package (SOP) | Tape & Reel    |  |

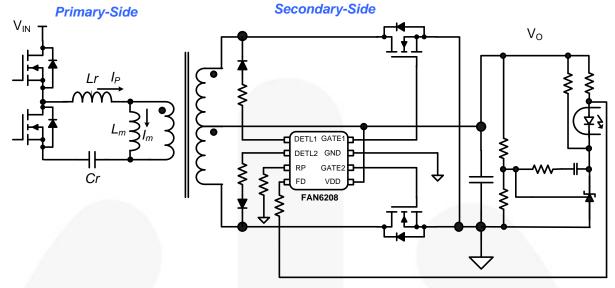

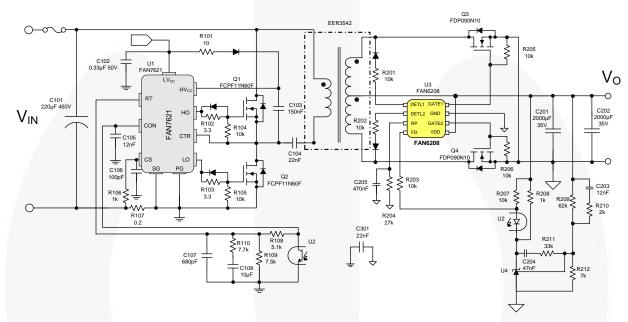

# **Application Diagram**

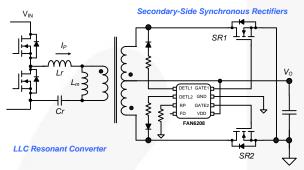

Figure 1. Typical Application

# **Block Diagram**

Figure 2. Block Diagram

# **Marking Information**

F- Fairchild Logo

Z- Plant Code

X- Year Code

Y- Week Code

TT: Die Run Code

T - Package Type (M = SOP)

P - Y: Green Package

M - Manufacture Flow Code

Figure 3. Top Mark

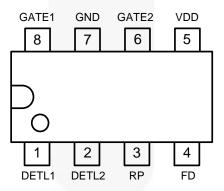

# **Pin Configuration**

Figure 4. Pin Assignments

#### **Pin Definitions**

| Pin# | Name  | Description                                                                  |  |  |  |

|------|-------|------------------------------------------------------------------------------|--|--|--|

| 1    | DETL1 | w Detect provides low-voltage detection of V <sub>DS</sub> of SR MOSFET1.    |  |  |  |

| 2    | DETL2 | Low Detect provides low-voltage detection of V <sub>DS</sub> of SR MOSFET2.  |  |  |  |

| 3    | RP    | Dead Time Programming Resistor programs H/L frequency version and dead time. |  |  |  |

| 4    | FD    | Feedback Detection is used for short-circuit protection and gate shrink.     |  |  |  |

| 5    | VDD   | Power Supply                                                                 |  |  |  |

| 6    | GATE2 | Driver Output. The totem-pole output driver for driving the SR MOSFET2.      |  |  |  |

| 7    | GND   | Ground                                                                       |  |  |  |

| 8    | GATE1 | Driver Output. The totem-pole output driver for driving the SR MOSFET1.      |  |  |  |

## **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           | Parameter                                           | Min.                              | Max.                               | Unit |

|------------------|-----------------------------------------------------|-----------------------------------|------------------------------------|------|

| $V_{DD}$         | Supply Voltage                                      |                                   | 30                                 | V    |

| V <sub>FD</sub>  | Voltage on FD Pin                                   |                                   | 30                                 | V    |

| V <sub>LV</sub>  | Voltage on DETL1, DETL2, RP Pins                    | -0.3                              | 7.0                                | V    |

| P <sub>D</sub>   | Power Dissipation                                   | 350 mW<br>at T <sub>A</sub> =90°C | 1000 mW<br>at T <sub>A</sub> =25°C |      |

| Θ <sub>JA</sub>  | Junction-to-Ambient Thermal Resistance              |                                   | 130                                | °C/W |

| $\Psi_{JT}$      | Junction-to-Top Thermal Characteristics             |                                   | 45                                 | °C/W |

| TJ               | Operating Junction Temperature                      |                                   | Internally Limited                 |      |

| T <sub>STG</sub> | Storage Temperature Range                           | -55                               | +150                               | °C   |

| TL               | Lead Temperature (Wave Soldering or IR, 10 Seconds) | 1                                 | +260                               | °C   |

| FOD              | Human Body Model, JESD22-A114                       |                                   | 6                                  | 1.37 |

| ESD              | Charged Device Model, JESD22-C101                   |                                   | 2                                  | kV   |

### **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol         | Parameter                     | Min. | Max. | Unit |

|----------------|-------------------------------|------|------|------|

| T <sub>A</sub> | Operating Ambient Temperature | -40  | +105 | °C   |

#### **Electrical Characteristics**

V<sub>DD</sub>=20 V, T<sub>A</sub>=25°C, unless otherwise specified. All voltages are with respect to GND unless otherwise noted.

| Symbol                                                          | Parameter                                                                   | Condition                                                                               | Min.                | Тур. | Max. | Unit |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------|------|------|------|

| VDD Section                                                     | 1                                                                           | 1                                                                                       | <u>l</u>            |      |      |      |

| $V_{DD}$                                                        | DC Supply Voltage                                                           |                                                                                         | V <sub>TH-OFF</sub> |      | 28   | V    |

| I <sub>DD-OP1</sub>                                             | Operating Current                                                           | $V_{DD}$ =12 V,<br>DETL=50 KHz, C <sub>L</sub> =6 nF,<br>R <sub>RP</sub> =24 K $\Omega$ | 7.0                 | 8.5  | 10.0 | mA   |

| I <sub>DD-OP2</sub>                                             | Operating Current                                                           | V <sub>DD</sub> =12 V,<br>DETL=100 KHz                                                  | 2.4                 | 3.2  | 4.0  | mA   |

| I <sub>DD-ST</sub>                                              | Startup Current                                                             | V <sub>DD</sub> =8 V                                                                    | 180                 | 300  | 500  | μA   |

| V <sub>TH-ON1</sub> V <sub>TH-ON2</sub>                         | On Threshold Voltage                                                        |                                                                                         | 9.3                 | 9.7  | 10.1 | V    |

| V <sub>TH-OFF1</sub>                                            | Off Threshold Voltage                                                       |                                                                                         | 8.3                 | 8.8  | 9.3  | V    |

| V <sub>DD-OVP1</sub><br>V <sub>DD-OVP2</sub>                    | V <sub>CC</sub> Over-Voltage<br>Protection                                  |                                                                                         | 26                  | 27   | 28   | V    |

| V <sub>DD-OVP-HYS1</sub><br>V <sub>DD-OVP-HYS2</sub>            | V <sub>CC</sub> Over-Voltage<br>Protection Hysteresis                       |                                                                                         | 1.3                 | 1.8  | 2.3  | V    |

| $t_{\text{OVP1}}, t_{\text{OVP2}}$                              | V <sub>CC</sub> Over-Voltage-<br>Protection Debounce                        |                                                                                         | 30                  | 60   | 100  | μs   |

| DETL Section                                                    |                                                                             |                                                                                         |                     |      | ı    |      |

| V <sub>DETL1</sub><br>V <sub>DETL2</sub>                        | Threshold Voltage for LOW Detection of DETL                                 | $V_{DD}$ =12 V,<br>DETL=50 KHz, C <sub>L</sub> =6 nF,<br>R <sub>RP</sub> =24 K $\Omega$ | 1.7                 | 2.0  | 2.3  | V    |

| tsr-on-detl1                                                    | Delay from DETL LOW to<br>SR Gate Turn-On                                   | t <sub>DB</sub> + t <sub>PD</sub> + t <sub>R</sub>                                      | 300                 | 350  | 400  | ns   |

| VDETL-FLOATING1<br>VDETL-FLOATING2                              | DETL Floating Voltage                                                       | V <sub>DD</sub> =12 V, DETL Pin<br>Floating                                             | 4.5                 | 1    |      | V    |

| DETL-SOURCE1                                                    | DETL Source Current                                                         | V <sub>DETL1</sub> =0 V                                                                 | 40                  | 50   | 60   | μΑ   |

| tDETL_Green_LF1 tDETL_Green_LF2                                 | DETL LOW Time Threshold for Green Mode at Low-Frequency Operation           | V <sub>RP</sub> < 1.5 V                                                                 | 3.50                | 3.75 | 4.00 | μs   |

| $t_{\text{DET(L)\_Green\_HF1}}$ $t_{\text{DET(L)\_Green\_HF2}}$ | DETL LOW Time<br>Threshold for Green Mode<br>at High-Frequency<br>Operation | V <sub>RP</sub> > 1.5 V                                                                 | 1.75                | 1.90 | 2.05 | μs   |

| Thermal Shutd                                                   | own                                                                         |                                                                                         |                     |      |      |      |

| T <sub>SHUTDOWN</sub>                                           | Shutdown Temperature                                                        | Temperature Rising, V <sub>DD</sub> =15 V                                               |                     | 140  |      | ••   |

|                                                                 | Hysteresis                                                                  |                                                                                         |                     | 20   |      | °C   |

| T <sub>STARTUP</sub>                                            | Startup Temperature                                                         | Before Startup                                                                          |                     | 120  |      |      |

Continued on the following page...

### **Electrical Characteristics**

V<sub>DD</sub>=20 V, T<sub>A</sub>=25°C, unless otherwise specified. All voltages are with respect to GND unless otherwise noted.

| Symbol                                               | Parameter                                                                              | Condition                                                                     | Min. | Тур. | Max. | Unit |

|------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------|------|------|------|

| Gate Section                                         | 1                                                                                      |                                                                               |      |      |      | l .  |

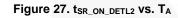

| V <sub>Z1</sub> V <sub>Z2</sub>                      | Gate Output Voltage<br>Maximum (Clamping)                                              | V <sub>DD</sub> =20 V                                                         | 10   | 12   | 14   | V    |

| V <sub>OL1</sub> V <sub>OL2</sub>                    | Gate Output Voltage LOW                                                                | V <sub>DD</sub> =12 V; I <sub>O</sub> =100 mA                                 |      |      | 0.5  | V    |

| $V_{OH1}V_{OH2}$                                     | Gate Output Voltage HIGH                                                               | V <sub>DD</sub> =12 V; I <sub>O</sub> =100 mA                                 | 9    |      |      | V    |

| t <sub>R1</sub> t <sub>R2</sub>                      | Rising Time                                                                            | V <sub>DD</sub> =12 V; C <sub>L</sub> =6 nF;<br>V <sub>GATE</sub> =2 V to 9 V | 30   | 70   | 120  | ns   |

| t <sub>F1</sub> t <sub>F2</sub>                      | Falling Time                                                                           | V <sub>DD</sub> =12 V; C <sub>L</sub> =6 nF;<br>V <sub>GATE</sub> =9 V to 2 V | 30   | 50   | 70   | ns   |

| t <sub>PD_HIGH_DETL1</sub>                           | Propagation Delay to Gate<br>Output HIGH (DETL<br>Trigger)                             | t <sub>R</sub> : 0 V~2 V, V <sub>DD</sub> =12 V<br>(DET Floating)             | - 1  | 120  |      | ns   |

| t <sub>PD_LOW_DETL1</sub> t <sub>PD_LOW_DETL2</sub>  | Propagation Delay to Gate<br>Output LOW (DETL<br>Trigger)                              | t <sub>F</sub> : 100%~90%, V <sub>DD</sub> =12 V<br>(DET Floating)            |      | 120  |      | ns   |

| t <sub>ON_MAX1</sub><br>t <sub>ON_MAX2</sub>         | Maximum On-Time                                                                        | Trim Maximum On-Time                                                          | 9.0  | 10.5 | 12.0 | μs   |

| t <sub>INHIBIT_LF1</sub><br>t <sub>INHIBIT_LF2</sub> | Gate Inhibit Time (from Turn-Off to Next Turn-On)                                      | V <sub>RP</sub> < 1.5 V                                                       | 1.8  | 2.1  | 2.5  | μs   |

| t <sub>INHIBIT_HF1</sub><br>t <sub>INHIBIT_HF2</sub> | Gate Inhibit Time (from Turn-Off to Next Turn-On)                                      | V <sub>RP</sub> > 1.5 V                                                       | 1.25 | 1.45 | 1.70 | μs   |

| t <sub>BLANKING1</sub><br>t <sub>BLANKING2</sub>     | Blanking Time for SR Turn-<br>Off Triggered by DETL<br>High (Minimum On-Time)          |                                                                               |      | 300  |      | ns   |

| K <sub>R</sub>                                       | Gate ON-Time Increase<br>Rate Between Two<br>Consecutive Cycles                        | t <sub>ON</sub> (n) / t <sub>ON</sub> (n-1) %                                 |      | 140  |      | %    |

| Timing Estimat                                       | or Section                                                                             |                                                                               |      |      |      | 7    |

| t <sub>DW</sub>                                      | Detection Window for<br>Insufficient Dead Time<br>(from Gate Turn-Off to<br>DETL HIGH) |                                                                               | 80   | 125  | 150  | ns   |

| tshrink-dt                                           | Gate Shrink Time by<br>Insufficienct Dead Time                                         | $R_{RP}$ =20 KΩ, $t_{DETL}$ =5 μs                                             | 1.00 | 1.25 | 1.50 | μs   |

|                                                      | Dead Time by Timing                                                                    | t <sub>DETL</sub> =4 μs, R <sub>RP</sub> =20 KΩ                               | 210  | 300  | 390  |      |

|                                                      | Estimator (70 kHz ~ 140 kHz, V <sub>RP</sub> < 1.5 V)                                  | t <sub>DETL</sub> =6 μs, R <sub>RP</sub> =20 KΩ                               | 570  | 720  | 870  |      |

| t <sub>DEAD</sub>                                    | Dead Time by Timing                                                                    | t <sub>DETL</sub> =2.5 μs, R <sub>RP</sub> =43 ΚΩ                             | 220  | 320  | 420  | ns   |

|                                                      | Estimator (160kHz ~ 240 kHz, V <sub>RP</sub> > 1.5V)                                   | t <sub>DETL</sub> =3.8 μs, R <sub>RP</sub> =43 ΚΩ                             | 560  | 670  | 780  | K    |

| t <sub>DB</sub>                                      | DETL HIGH-to-LOW Debounce Time for Gate Turn-on Trigger                                |                                                                               |      | 150  |      | ns   |

| t <sub>SHRINK-RNG</sub>                              | Gate Shrink by DETL<br>Ringing around Zero                                             |                                                                               |      | 1.2  |      | μs   |

| t <sub>Green_DH</sub>                                | DETL Pull-HIGH Time<br>Threshold for Green Mode                                        |                                                                               | 18   | 24   | 30   | μs   |

Continued on the following page...

#### **Electrical Characteristics**

$V_{DD}$ =20 V,  $T_A$ =25°C, unless otherwise specified. All voltages are with respect to GND unless otherwise noted.

| Symbol                               | Parameter                                                            | Conditions                                                | Min. | Тур. | Max. | Units |

|--------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------|------|------|------|-------|

| Feedback Dete                        | ection (FD) Section                                                  |                                                           |      | •    | •    | •     |

| ΔV1% ΔV2%                            | Feedback Increase<br>Threshold for Gate Shrink                       | $[(V_{DD}\text{-}V_{FD})_{n+1}/(V_{DD}\text{-}V_{FD})_n]$ |      | 120  |      | %     |

| t <sub>SHRINK-FD</sub>               | Gate Shrink by Feedback Detection                                    |                                                           |      | 1.4  |      | μs    |

| t <sub>D-SHRINK-FD</sub>             | Gate-Shrink Duration by Feedback Detection                           |                                                           | 60   | 90   | 120  | μs    |

| V <sub>DD</sub> -V <sub>FD.SCP</sub> | Short-Circuit Protection<br>(SCP) Threshold by<br>Feedback Detection |                                                           | 200  | 270  | 340  | mV    |

| t <sub>DB-SCP</sub>                  | Debounce Time for Short-Circuit Protection (SCP)                     |                                                           | 12   | 16   | 20   | μs    |

| RP Section                           |                                                                      |                                                           |      |      |      |       |

| I <sub>RP</sub>                      | RP Source Current                                                    |                                                           | 38.5 | 41.5 | 44.5 | μA    |

| $V_{RPO}$                            | RP Open Protect                                                      |                                                           | 3.40 | 3.65 | 3.90 | V     |

| $V_{RPS}$                            | RP Short Protect                                                     |                                                           | 0.25 | 0.30 | 0.35 | V     |

| t <sub>RPOS</sub>                    | RP Open/Short Debounce                                               |                                                           | 1.6  | 2.0  | 2.4  | μs    |

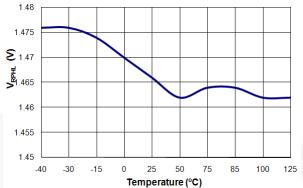

| $V_{RPHL}$                           | H/L Frequency Threshold                                              |                                                           | 1.40 | 1.46 | 1.52 | V     |

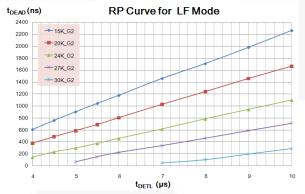

Figure 5. t<sub>DEAD</sub> vs. t<sub>DETL</sub> RP Curve for LF Mode

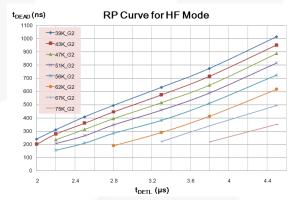

Figure 6. t<sub>DEAD</sub> vs. t<sub>DETL</sub> RP Curve for HF Mode

#### **Function Description**

#### **Operation Principle**

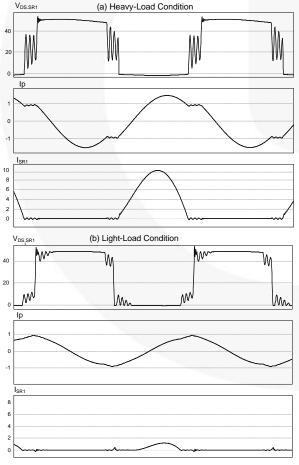

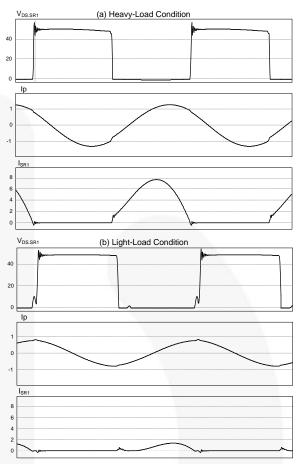

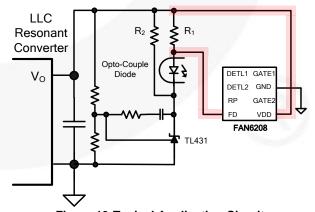

FAN6208 is a secondary-side synchronous rectifier controller for LLC or LC resonant converters that drive two synchronous rectifier MOSFETs. Figure 7 is the simplified circuit diagram of an LLC converter. The FAN6208 determines SR MOSFET turn-on/off timing by detecting the drain-to-source voltage of each SR MOSFET. The key waveforms for LLC resonant converter for below resonance and above resonance are shown in Figure 8 and Figure 9, respectively.

Figure 7. Simplified Schematic of LLC Converter

Figure 8. Key Waveforms of LLC Resonant Converter for Below Resonance Operation

Figure 9. Key Waveforms of LLC Resonant Converter for Above Resonance Operation

#### **Timing Estimator**

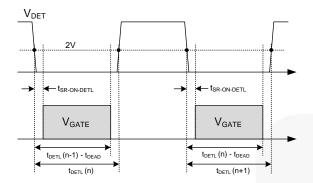

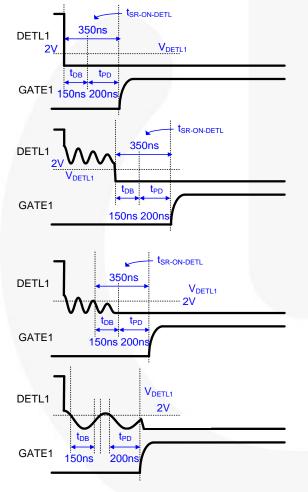

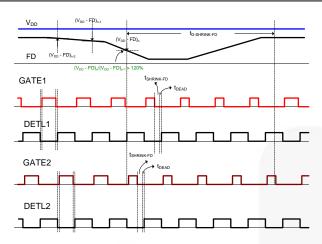

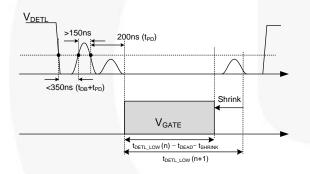

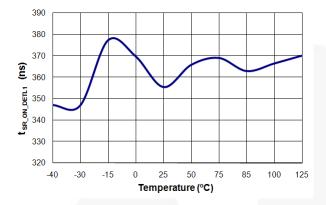

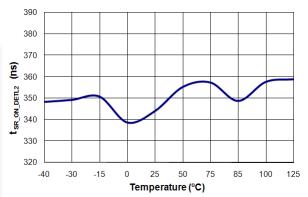

Figure 10 shows the timing diagram for FAN6208. Once the body diode of SR begins conducting, the drain-to-source voltage drops to zero, which causes DETL pin voltage to drop to zero. FAN6208 turns on the MOSFET after  $t_{\text{ON-ON-DETL}}$  (about 350 ns), when voltage on DETL drops below 2 V. As depicted in Figure 11, the turn-on delay (after  $t_{\text{SR-ON-DETL}}$ ) is the sum of debounce time (150 ns) and propagation delay (200 ns).

FAN6208 measures the SR conduction duration ( $t_{DETL}$ ), during which DETL stays lower than 2 V, and uses this information to determine the turn-off instant of SR gates of the next switching cycle. The turn-off timing is obtained by subtracting a dead time ( $t_{DEAD}$ ) from the measured SR conduction duration of the previous switching cycle. The dead time can be programmed using a resistor on the RP pin and the relationship between the dead time and SR conduction duration ( $t_{DETL}$ ) for different resistor values on RP pin is given in Figure 5.

Figure 10.SR Gate Timing Diagram

Figure 11. DETL Debounce (Blanking) Time

#### **Gate-Shrink Functions**

In normal operation, the turn-off instant is determined by subtracting a dead time ( $t_{DEAD}$ ) from the measured SR conduction duration of the previous switching cycle, as shown in Figure 10. This allows proper driving timing for SR MOSFETS when the converter is in steady state and the switching frequency does not change much. However, this control method may cause shoot-through of SR MOSFETs when the switching frequency

increases fast and switching transition of the primaryside MOSFETs takes place before the turn-off command of SR is given. To prevent the shoot-through, FAN6208 has gate-shrink functions. Gate shrink occurs under three conditions:

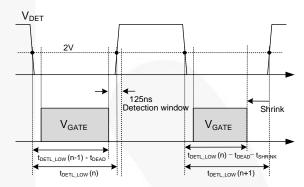

(a) When insufficient dead time is detected in the previous switching cycle. When the DETL goes HIGH within 125 ns of detection window after SR gate is turned off, the SR gate drive signal in the next switching cycle is reduced by t<sub>SHRINK-DT</sub> (about 1.25 μs) to increase the dead time, as shown in Figure 12.

Figure 12.Gate Shrink by Minimum Dead Time Detection Window

(b) When the feedback information changes fast. FAN6208 monitors the current through the opto-coupler diode by measuring the voltage across the resistor in series with the opto-coupler diode, as depicted in Figure 13. If the feedback current through the opto-coupler diode increases by more than 20% of the feedback current of the previous switching cycle, the SR gate signal is shrunk by t<sub>SHRINK-FD</sub> (about 1.4 µs) for t<sub>D-SHRINK-FD</sub> (about 90 µs), as shown in Figure 14.

Figure 13. Typical Application Circuit

Figure 14. Gate Shrink by Feedback Detection

(c) When the DETL voltage has ringing around zero. As depicted in Figure 8, the drain voltage of SR has ringing around zero at light-load condition after the switching transition of the primary-side switches. When DETL voltage rises above 2 V within 350 ns after DETL voltage drops to zero and stays above 2 V longer than 150 ns, the gate is shrunk by 1.2 μs (t<sub>SHRINK-RNG</sub>), as shown in Figure 15.

Figure 15. Gate Shrink by DETL Voltage Ringing Around Zero

#### **RP Pin Function**

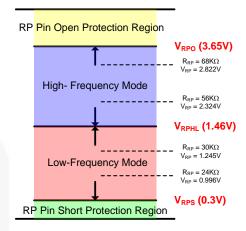

The RP pin programs the level of green mode and  $t_{DEAD}$ . Figure 16 shows how the mode is selected by the voltage on the RP pin (open protection, short protection, and HF/LF mode). When  $R_{RP}$  is less than 36 K $\Omega$ , FAN6208 operates in low-frequency mode. Green mode is enabled when  $t_{DETL}$  is smaller than 3.75  $\mu$ s. When  $R_{RP}$  is larger than 36 K $\Omega$ , high-frequency mode is selected and green mode is enabled for  $t_{DETL}$  < 1.90  $\mu$ s.  $t_{DEAD}$  can be also adjusted by a resistor on the RP pin. Figure 5 shows the relationship between  $t_{DEAD}$  and  $t_{DETL}$  for different RP resistors.

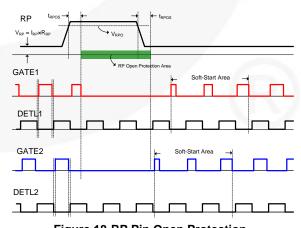

Figure 16. RP Pin Operation

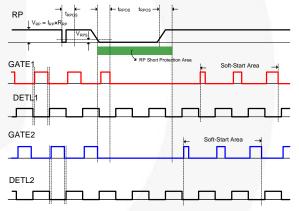

To handle abnormal conditions for IC pins, the RP pin also provides open/short protection. When  $V_{RP}$  is less than  $V_{RPS}$  (0.3 V) or  $V_{RP}$  is higher than  $V_{RPO}$  (3.65 V), the protection is triggered. Figure 17 shows the RP pin short protection timing sequence. If  $V_{RP} < V_{RPS}$  (0.3 V) for longer than  $t_{RPOS}$  (2  $\mu s$ ), FAN6208 is disabled. Figure 18 shows the RP pin open protection timing sequence. If  $V_{RP} > V_{RPO}$  (3.65 V) for longer than  $t_{RPOS}$  (2  $\mu s$ ), FAN6208 is disabled.

Figure 17. RP Pin Short Protection

Figure 18.RP Pin Open Protection

#### **Green Mode**

Switching frequency increases in LLC topology at light-load condition, which increases the power consumption for the SR gate drive. Green mode reduces power loss at light load. FAN6208 has two ways to enable green mode. Green mode is triggered when DETL voltage is pulled LOW for less than 3.75 µs (LF mode) or 1.90 µs (HF mode) for seven switching cycles. FAN6208 resumes normal SR gate driving when DETL voltage is pulled LOW for longer than 3.75 µs (LF mode) or 1.90 µs (HF mode) for seven switching cycles.

When DETL voltage is pulled HIGH for longer than  $24 \,\mu s$ . This occurs when the LLC resonant converter operates in burst mode (skipping mode).

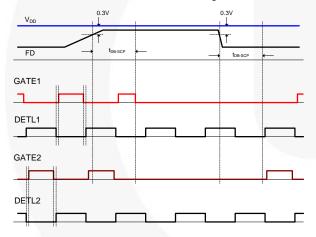

#### **Short-Circuit Protection**

As depicted in Figure 13, FAN6208 monitors the current through the opto-coupler diode by measuring the voltage across the resistor in series with the opto-coupler diode. When the output of the power supply is short circuited, the output voltage drops and the cathode of the shunt regulator (KA431) is saturated to HIGH. No current flows through the opto coupler diode. The output short protection is triggered when the voltage between  $V_{\text{DD}}$  and FD is smaller than 0.3 V, as shown in Figure 19.

Figure 19. Output Short Protection by Feedback Detection

#### **V<sub>DD</sub> Pin Over-Voltage Protection**

Over-voltage conditions are usually caused by an open feedback loop.  $V_{DD}$  over-voltage protection prevents damage of SR MOSFET. When the voltage on the  $V_{DD}$  pin exceeds 27 V, FAN6208 disables gate output.

#### **Internal Over-Temperature Protection**

Internal over-temperature protection prevents the SR gate from fault triggering in high temperatures. If the temperature is over 140°C, the SR gate is disabled until the temperature drops below 120°C.

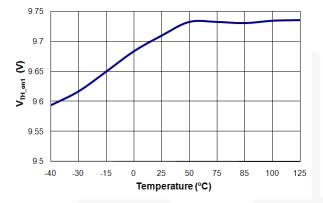

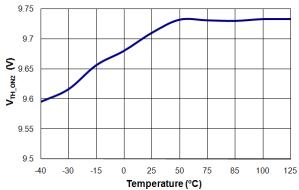

# **Typical Performance Characteristics**

Figure 20. V<sub>TH\_ON1</sub> vs. T<sub>A</sub>

Figure 21. V<sub>TH\_ON2</sub> vs. T<sub>A</sub>

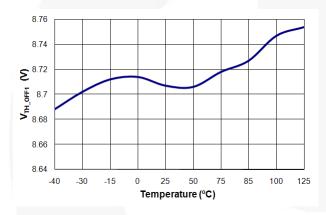

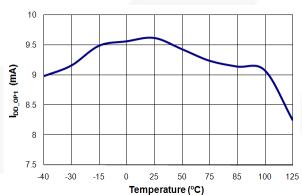

Figure 22. V<sub>TH OFF1</sub> vs. T<sub>A</sub>

Figure 23. V<sub>TH OFF2</sub> vs. T<sub>A</sub>

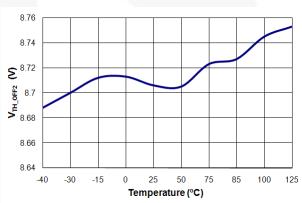

Figure 24. IDD\_ST vs. TA

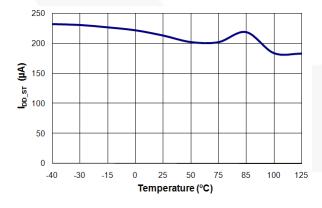

Figure 25. I<sub>DD\_OP1</sub> vs. T<sub>A</sub>

# **Typical Performance Characteristics** (Continued)

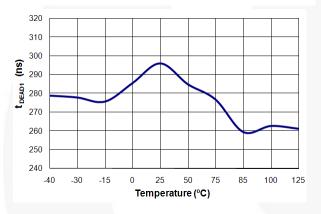

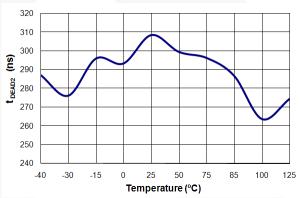

Figure 26.  $t_{\text{SR\_ON\_DETL1}}$  vs.  $T_{\text{A}}$

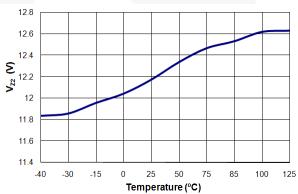

Figure 28. Vz1 vs. TA

Figure 29. Vz2 vs. TA

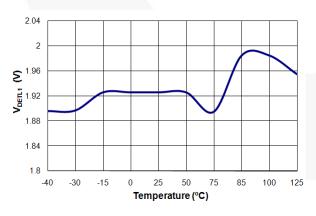

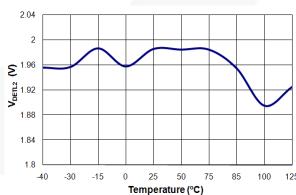

Figure 30. V<sub>DETL1</sub> vs. T<sub>A</sub>

Figure 31. V<sub>DETL2</sub> vs. T<sub>A</sub>

# **Typical Performance Characteristics** (Continued)

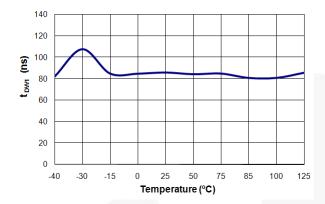

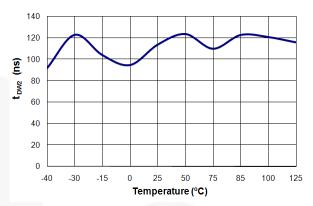

Figure 32.  $t_{\text{DW1}}$  vs.  $T_{\text{A}}$

Figure 33. t<sub>DW2</sub> vs. T<sub>A</sub>

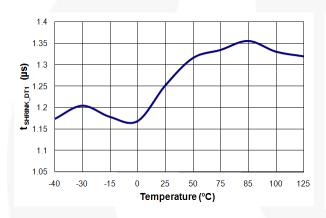

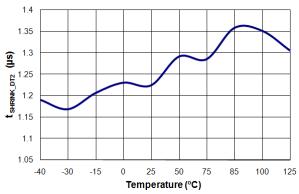

Figure 34. V<sub>SHRINK\_DT1</sub> vs. T<sub>A</sub>

Figure 35. V<sub>SHRINK\_DT2</sub> vs. T<sub>A</sub>

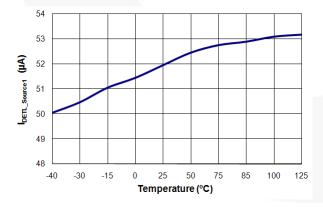

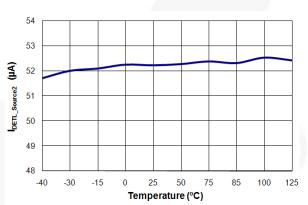

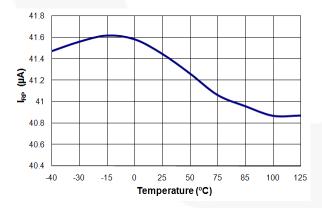

Figure 36.  $I_{DETL\_Source1}$  vs.  $T_A$

Figure 37.  $I_{DETL\_Source2}$  vs.  $T_A$

# **Typical Performance Characteristics** (Continued)

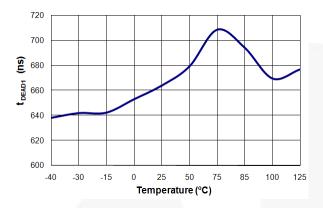

Figure 38.  $t_{DEAD1}$  (R<sub>RP</sub>=20 k, 6  $\mu$ s) vs. T<sub>A</sub>

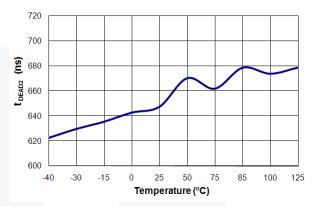

Figure 40. t<sub>DEAD1</sub> (R<sub>RP</sub>=43 k, 2.5 μs) vs. T<sub>A</sub>

Figure 41.  $t_{DEAD2}$  (R<sub>RP</sub>=43 k, 2.5  $\mu$ s) vs. T<sub>A</sub>

Figure 42. I<sub>RP</sub> vs. T<sub>A</sub>

Figure 43. V<sub>RPHL</sub> vs. T<sub>A</sub>

# **Typical Application Circuit (LLC Converter with SR)**

| Application | Fairchild Devices  | Input Voltage Range     | Output     |

|-------------|--------------------|-------------------------|------------|

| TV Power    | FAN7621<br>FAN6208 | 350~400 V <sub>DC</sub> | 24 V / 8 A |

Figure 44. Application Circuit

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdt/Patent-Marking.pdf">www.onsemi.com/site/pdt/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and exp

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# onsemi:

FEBFAN6208\_CP433V1 FEBFAN6208-CP433V1-GEVB