June 2017

# FAN54110 USB-Compatible Single-Cell Li-Ion Linear Charger with DBP

### **Features**

Fully Integrated, High-Efficiency Charger for Single-Cell Li-Ion and Li-Polymer Battery Packs

Charge Voltage Accuracy: ±0.5% at 25°C

±1% from -30 to 85°C

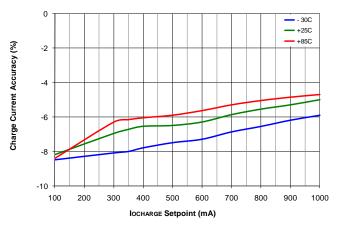

+0/-10% Charge Current Regulation Accuracy

28 V Absolute Maximum Input Voltage

1 A Maximum Charge Current

Support for Dead Battery Provision (DBP) of USB Battery Charging Specification 1.2

Programmable through I<sup>2</sup>C Interface with Fast Mode (400 kHz) Compatibility

- Input Current

- Fast-Charge / Termination Current

- Charger Voltage

Safety Timer with Reset Control

Weak Input Sources Accommodated by Reducing Charging Current to Maintain Minimum V<sub>BUS</sub> Voltage

Low Reverse Leakage to Prevent Battery Drain to VBUS

# **Applications**

**Smart Phones**

**Tablets**

Portable Media Players

Li Ion Powered Devices

# **Description**

The FAN54110 is a USB-compatible single-cell, linear Li-lon charger with support for Dead Battery Provision (DBP).

The device employs Over-Voltage Protection (OVP) circuitry to protect the device, load, and battery. The maximum charge current is rated at 1 A and can be programmed from 100 mA to 1 A through the I<sup>2</sup>C interface, optimizing charging for various battery sizes.

Dynamic Input Voltage Control ensures weak power sources can be used to power the FAN54110 without collapsing to an unusable input voltage for charging.

Open-drain status pins, STAT and POK\_B, provide a status of charging and input power. The STAT pin also notifies the system processor when an I<sup>2</sup>C interrupt occurs so the processor can take action based on the interrupt.

The FAN54110 conforms to the constraints of the Dead Battery Provision within the BC1.2 specification, including a 30-minute timer that cannot exceed 45 minutes.

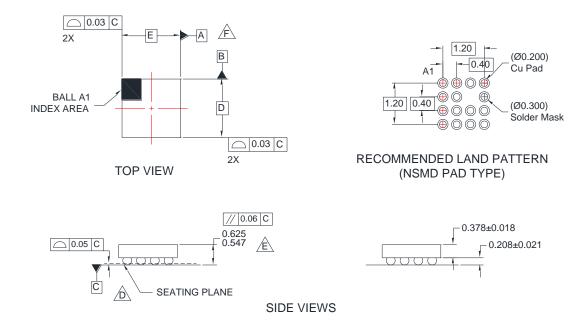

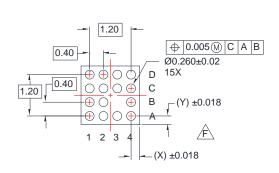

The FAN54110 is designed to be stable with space-saving ceramic capacitors. The FAN54110 is available in a 15-bump, 0.4 mm pitch, WLCSP package.

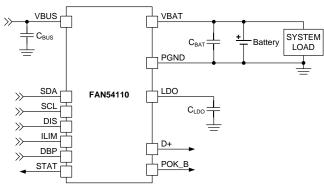

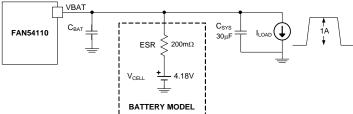

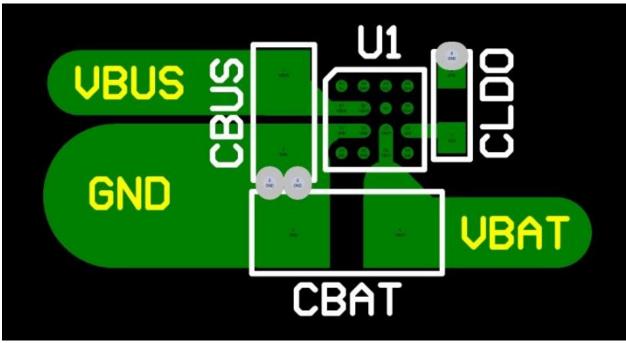

Figure 1. Typical Application

# **Ordering Information**

| Part Number | PN Reg00h[4:3] | Temperature Range | Package                                               | Packing<br>Method |

|-------------|----------------|-------------------|-------------------------------------------------------|-------------------|

| FAN54110UCX | 00             | -40°C to 85°C     | 15-Bump, Wafer-Level Chip-Scale (WLCSP), 0.4 mm Pitch | Tape and Reel     |

#### **Recommended External Components**

| Component                       | Description                   | Vendor                                      | Parameter | Min. | Typ.(1) | Unit |

|---------------------------------|-------------------------------|---------------------------------------------|-----------|------|---------|------|

| C <sub>BUS</sub>                | 1.0 μF, 10%, 25 V, X5R, 0603  | Murata GRM188R61E105K<br>TDK C1608X5R1E105M | С         | 0.5  | 1.0     | μF   |

| C <sub>BAT</sub> <sup>(2)</sup> | 4.7 μF, 10%, 6.3 V, X5R, 0603 | Murata GRM188R60J475K<br>TDK C1608X5R0J475K | С         | 2.0  | 4.7     | μF   |

| C <sub>LDO</sub>                | 1.0 μF, 10%, 6.3 V, X5R, 0402 | Murata GRM155R60J105M                       | С         | 0.4  | 1.0     | μF   |

#### Notes:

- 1. Does not reflect effects of bias, tolerance, and temperature.

- C<sub>BAT</sub> is placed as close to the charger IC as possible. A minimum requirement of 30 μF distributed system capacitance (C<sub>SYS</sub>) is parallel with C<sub>BAT</sub>, but can be located further from the IC.

# **Block Diagram**

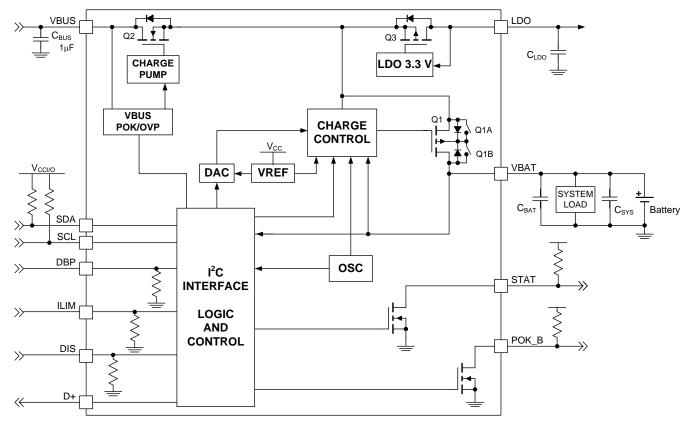

Figure 2. IC and System Block Diagram

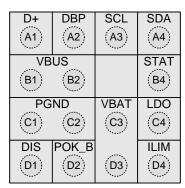

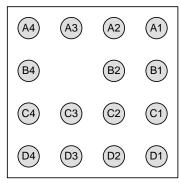

**Bottom View**

# **Pin Definitions**

| Pin#   | Name   | Description                                                                                                                                                                                                                                                                          |

|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1     | D+     | Connect to the USB connector D+ pin                                                                                                                                                                                                                                                  |

| AI     | DŦ     | Charger IC sources 0.6 V in CHARGE state when DBP is LOW. Otherwise, this pin is 3-state.                                                                                                                                                                                            |

| A2     | DBP    | Dead Battery Provision Disable                                                                                                                                                                                                                                                       |

| AZ     | - DDI  | Pull HIGH to disable charger D+ output. Internal pull-down resistor.                                                                                                                                                                                                                 |

| А3     | SCL    | I <sup>2</sup> C Interface Serial Clock                                                                                                                                                                                                                                              |

| A4     | SDA    | I <sup>2</sup> C Interface Serial Data                                                                                                                                                                                                                                               |

| B1, B2 | VBUS   | Charger Input Voltage                                                                                                                                                                                                                                                                |

| D1, D2 | VBUS   | Bypass with a 1 μF capacitor directly to PGND.                                                                                                                                                                                                                                       |

|        |        | Status / Interrupt                                                                                                                                                                                                                                                                   |

| B4     | STAT   | Open-drain output indicating charge status. The IC pulls this pin LOW when charge is in process. High impedance when charging is done or charger is disabled. Also used as system interrupt. 128 $\mu s$ pulse and then high impedance indicates to the system a fault has occurred. |

| C1, C2 | PGND   | Power Ground                                                                                                                                                                                                                                                                         |

| 01, 02 | I GND  | Power return for gate drive and power transistors.                                                                                                                                                                                                                                   |

| C4     | LDO    | 3.3 V LDO                                                                                                                                                                                                                                                                            |

| 04     | LDO    | 3.3 V regulator output.                                                                                                                                                                                                                                                              |

| D1     | DIS    | Active-High Disable                                                                                                                                                                                                                                                                  |

|        | DIO    | When pulled HIGH, the charger is disabled. Internal pull-down resistor.                                                                                                                                                                                                              |

|        |        | VBUS Power-OK Monitor                                                                                                                                                                                                                                                                |

| D2     | POK_B  | Open-drain output that is pulled LOW when $V_{BUS}$ is greater than the $V_{BUS}$ validation threshold and lower than $V_{BUS}$ OVP. High impedance when outside this range.                                                                                                         |

|        |        | Battery Voltage                                                                                                                                                                                                                                                                      |

| C3, D3 | VBAT   | Connect to the positive (+) terminal of the battery pack. Bypass locally with a 4.7 $\mu\text{F}$ capacitor to PGND.                                                                                                                                                                 |

| D4     | ILIM   | Input Current Limit                                                                                                                                                                                                                                                                  |

| D4     | ILIIVI | This pin sets the input current limit for t <sub>30MIN</sub> charging. Internal pull-down resistor.                                                                                                                                                                                  |

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           |                         | Parameter                                                   | Min. | Max. | Unit |  |

|------------------|-------------------------|-------------------------------------------------------------|------|------|------|--|

| V <sub>BUS</sub> | Voltage on VBUS         | Continuous                                                  | -1.2 | 28.0 | V    |  |

| V <sub>BAT</sub> | Voltage on VBAT         |                                                             | -0.3 | 6.5  | V    |  |

| Vo               | Voltage on Other Pins   | Voltage on Other Pins                                       |      | (3)  | V    |  |

|                  | Electrostatic Discharge | Human Body Model per ANSI/ESDA/JEDEC JS-001-2012 (All Pins) | 20   | 00   | .,   |  |

| ESD              | Protection Level        | Charged Device Model per JESD22-C101 (All Pins)             | 15   | 00   | V    |  |

|                  |                         | IEC 61000-4-2 System (VBUS and D+ Pins)                     | 8000 |      |      |  |

| LU               | Latch Up                | JESD78 - Class 1, 25°C                                      | ±1   | 00   | mA   |  |

| TJ               | Junction Temperature    |                                                             | -40  | +150 | °C   |  |

| T <sub>STG</sub> | Storage Temperature     |                                                             | -65  | +150 | °C   |  |

| TL               | Lead Soldering Temper   | ature, 10 Seconds                                           |      | +260 | °C   |  |

#### Note:

Lesser of 6.5 V or V<sub>BAT</sub> + 0.3 V.

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. ON Semiconductor does not recommend exceeding them or designing to absolute maximum ratings.

| Symbol         | Parameter            | Min. | Max. | Unit |

|----------------|----------------------|------|------|------|

| VIN            | Supply Voltage       | 4    | 6    | V    |

| T <sub>A</sub> | Ambient Temperature  | -30  | +85  | °C   |

| TJ             | Junction Temperature | -30  | +125 | °C   |

# **Thermal Properties**

Junction-to-ambient thermal resistance is a function of application and board layout. This data is measured with four-layer 2s2p boards in accordance to JEDEC standard JESD51. Special attention must be paid not to exceed junction temperature  $T_{J(max)}$  at a given ambient temperature  $T_{A}$ . For measured data, see the Evaluation Board Measured  $\theta JA$  table.

| Symbol | Parameter Typical                         |    | Unit |

|--------|-------------------------------------------|----|------|

| θја    | Junction-to-Ambient Thermal Resistance 60 |    | °C/W |

| θЈВ    | Junction-to-PCB Thermal Resistance        | 20 | °C/W |

# **Electrical Specifications**

Unless otherwise specified: circuit of Figure 2, recommended operating temperature range for  $T_J$  and  $T_A$ ,  $V_{BUS}$ =5.0 V, DIS=0 (Charger Mode operation), SCL, SDA=0 or 1.8 V; typical values are for  $T_J$ =25°C.

| Symbol                | Parameter                                                                   | Conditions                                                                   |                                    | Min. | Тур. | Max.  | Unit |

|-----------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------|------|------|-------|------|

| Power Su              | pplies                                                                      |                                                                              |                                    | 1    |      |       |      |

| V <sub>IN(MIN)1</sub> | V <sub>BUS</sub> Input Voltage Rising                                       | To Initiate and Pass VBUS Validation                                         |                                    | 4.18 | 4.40 | 4.65  | V    |

| V <sub>IN(MIN)2</sub> | Minimum V <sub>BUS</sub> during Charge                                      | VBUS Regulation Loop is                                                      | s Off                              | 2.95 | 3.10 | 3.35  | V    |

| tvbus_valid           | V <sub>BUS</sub> Validation Time                                            |                                                                              |                                    |      | 32   |       | ms   |

| V <sub>BUS_REF</sub>  | V <sub>BUS</sub> Regulation Loop Threshold                                  | Relative to VBUS_REF S                                                       | Setting                            | -5   |      | +5    | %    |

| I <sub>VBUS</sub>     | V <sub>BUS</sub> Current                                                    | DIS=1                                                                        |                                    |      | 890  | 1,000 | μА   |

| I <sub>DIS</sub>      | V <sub>BUS</sub> Discharge Current                                          | VBUS Removal or Valida                                                       | ation                              | 40   | 63   | 90    | mΑ   |

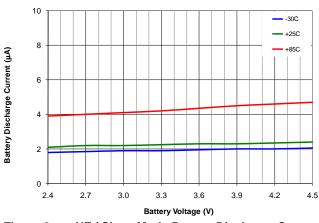

|                       | Battery Discharge Current during                                            | V <sub>BAT</sub> =4. 2 V, VBUS=Ope<br>No I <sup>2</sup> C Traffic, -30°C < T |                                    |      | 5    | 10    |      |

| I <sub>BAT</sub>      | SLEEP State                                                                 | V <sub>BAT</sub> =4. 2 V, VBUS=Ope<br>-30°C < T <sub>J</sub> < 85°C          | n, SDA=SCL=0 V,                    |      | 3    | 8     | μА   |

| I <sub>BUS_LKG</sub>  | S_LKG VBAT to VBUS Leakage Current VBAT=4. 2 V, VBUS=0 V, -30°C < TJ < 85°C |                                                                              |                                    | <1   | 2    | μΑ    |      |

| Charger \             | /oltage Regulation                                                          |                                                                              |                                    | •    | •    |       |      |

|                       | Charge Voltage Range                                                        |                                                                              |                                    | 3.38 |      | 4.44  | V    |

|                       |                                                                             | Voreg=4. 2 V                                                                 | T <sub>J</sub> =25°C               | -0.5 |      | +0.5  | - %  |

|                       | Observe Mallana Assurance                                                   |                                                                              | -30°C < T <sub>J</sub> < 85°C      | -1   |      | +1    |      |

| $V_{OREG}$            | Charge Voltage Accuracy                                                     | 13 38 V < Vores < 4 44 V -                                                   | T <sub>J</sub> =25°C               | -1   |      | +1    |      |

|                       |                                                                             |                                                                              | -30°C < T <sub>J</sub> < 85°C      | -1.5 |      | -1.5  |      |

|                       | V <sub>BAT</sub> Overshoot Pulsed Load <sup>(4)</sup>                       | See V <sub>BAT</sub> Overshoot Tes                                           | t                                  |      | 2    | 10    | mV   |

| Fast Chai             | rging Current Regulation                                                    |                                                                              |                                    |      |      |       |      |

|                       | Output Charge Current Range                                                 |                                                                              |                                    | 100  |      | 1,000 | mA   |

| I <sub>OCHRG</sub>    | Charge Current Accuracy                                                     | I <sub>OCHRG</sub> ≥ 350 mA                                                  |                                    | -10  | -5   | 0     | 0/   |

|                       | (measured at $V_{BUS}$ , includes $I_{CHRG} + I_{REG}$ )                    | Iochrg < 350 mA                                                              |                                    | -15  | -7   | 0     | %    |

| Logic Lev             | vels: DIS, SDA, SCL, ILIM, DBP                                              |                                                                              |                                    |      |      |       |      |

| ViH                   | High-Level Input Voltage                                                    |                                                                              |                                    | 1.05 |      |       | V    |

| $V_{IL}$              | Low-Level Input Voltage                                                     |                                                                              |                                    |      |      | 0.4   | V    |

| I <sub>IN</sub>       | Input Bias Current                                                          | Input Tied to GND or Gre                                                     | eater of V <sub>BAT</sub> or Valid |      | 0.01 | 1.00  | μА   |

| R <sub>PD</sub>       | ILIM, DBP, DIS Pull-Down<br>Resistance                                      |                                                                              |                                    | 0.6  | 0.9  | 1.4   | МΩ   |

### **VBAT Overshoot Test**

In the figure below, Iocharge=1 A (1111), Voreg=4.2 V. ILOAD tr=tr=1  $\mu$ s. Charge current prior to load transient=  $\frac{20mV}{200m\Omega}$  = 100mA

Overshoot is measured as the peak voltage above  $V_{BAT}$  level prior to the load transient application.  $C_{SYS}$  represents the distributed system capacitance across the VBAT terminals and is assumed to be a minimum of 30  $\mu$ F.

Figure 3. VBAT Overshoot Test Condition

# **Electrical Specifications**

Unless otherwise specified: circuit of Figure 2, recommended operating temperature range for  $T_J$  and  $T_A$ ,  $V_{BUS}$ =5.0 V, DIS=0 (Charger Mode operation), SCL, SDA=0 or 1.8 V; typical values are for  $T_J$ =25°C.

| Symbol                 | Parameter                                                   | Conditions                                                                     | Min. | Тур.            | Max. | Unit |

|------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------|------|-----------------|------|------|

| Charge Te              | rmination Detection                                         |                                                                                |      |                 |      |      |

|                        | Termination Current Range                                   | VBAT > VOREG - VRCH, VBUS > VBUS_REF                                           | 20   |                 | 170  | mA   |

| I <sub>TERM</sub>      | T : // O //                                                 | I <sub>TERM</sub> > 80 mA                                                      | -10  |                 | +10  | 0/   |

|                        | Termination Current Accuracy                                | I <sub>TERM</sub> ≤ 80 mA                                                      | -20  |                 | +20  | %    |

| Battery Re             | charge Threshold                                            |                                                                                | •    |                 |      |      |

| $V_{RCH}$              | Recharge Threshold                                          | V <sub>BAT</sub> Falling by V <sub>RCH</sub> below V <sub>OREG</sub> Threshold |      | 100             |      | mV   |

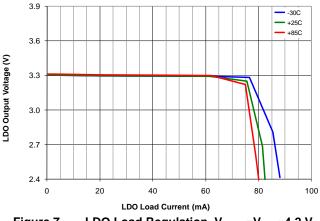

| 3. 3 V Line            | ar Regulator                                                |                                                                                | •    |                 |      |      |

| $V_{REG}$              | 3.3 V Regulator Output                                      | I <sub>REG</sub> from 0 to 40 mA                                               | 3.10 | 3.30            | 3.50 | V    |

| DBP Outpu              | ut                                                          |                                                                                | -    | •               | •    |      |

| V <sub>DBP_SRC</sub>   | Voltage on D+ pin                                           | DBP=0, I <sub>LOAD</sub> on D+ from 0 to 250 μA                                | 0.51 | 0.60            | 0.69 | V    |

| I <sub>DBP_OFF</sub>   | Leakage Current                                             | DBP=1, V <sub>D+</sub> from 0 to 3. 6 V                                        | -1   |                 | +1   | μΑ   |

| STAT / PO              | K_B Output                                                  |                                                                                | •    |                 |      |      |

| V <sub>OL</sub>        | STAT / POK_B Output Low                                     | I=10 mA                                                                        |      |                 | 0.4  | V    |

| Іон                    | STAT / POK_B Leakage Current                                | V=5 V                                                                          |      |                 | 1    | μΑ   |

| Battery De             | tection                                                     |                                                                                | •    |                 |      |      |

| IDETECT                | Battery Detection Current before Charge Done (Sink Current) | Begins after Termination Detected                                              |      | -1              |      | mA   |

| t <sub>DETECT</sub>    | Battery Detection Time                                      |                                                                                |      | 262             |      | ms   |

| Power Swi              | tches (see Error! Reference source                          | e not found.)                                                                  |      | I               | I    |      |

| Q1 R <sub>DS(ON)</sub> | Q1 On Resistance                                            |                                                                                |      | 175             | 260  | mΩ   |

| Q2 R <sub>DS(ON)</sub> | Q2 On Resistance                                            |                                                                                |      | 110             | 170  | mΩ   |

| Protection             | and Timers                                                  |                                                                                | I .  | I               | I    |      |

| \ (D110                | V <sub>BUS</sub> OVP Accuracy                               | V <sub>BUS</sub> Rising                                                        | -7   |                 | +7   | %    |

| VBUS <sub>OVP</sub>    | Hysteresis                                                  | V <sub>BUS</sub> Falling                                                       |      | 100             |      | mV   |

|                        | Battery Short-Circuit Threshold                             | V <sub>BAT</sub> Rising                                                        | 2.10 | 2.27            | 2.40 | V    |

| VSHORT                 | Hysteresis                                                  | V <sub>BAT</sub> Falling                                                       |      | 120             |      | mV   |

| I <sub>SHORT</sub>     | Linear Charging Current                                     | V <sub>BAT</sub> < V <sub>SHORT</sub>                                          | 85   | 93              | 100  | mA   |

| I <sub>LIM(PTM)</sub>  | Production Test Mode Current<br>Limit                       |                                                                                | 2.2  |                 |      | Α    |

| _                      | Thermal Shutdown Threshold <sup>(4)</sup>                   | T <sub>J</sub> Rising                                                          | 130  | 145             | 160  | 9    |

| T <sub>SHUTDWN</sub>   | Re-Enable Threshold <sup>(4)</sup>                          | T <sub>J</sub> Falling                                                         |      | T <sub>CF</sub> |      | °C   |

| T <sub>CF</sub>        | Thermal Regulation Accuracy <sup>(4)</sup>                  | Relative to T <sub>CF</sub> Setting                                            | -10  |                 | +10  | °C   |

| t <sub>32S</sub>       | 32-Second Timer                                             |                                                                                | 20.5 | 24.3            | 28.0 | S    |

| tзомім                 | 30-Minute Timer                                             |                                                                                | 30   | 38              | 45   | min  |

| tosc                   | 125 kHz Oscillator Tolerance                                | Timing in all Sequencing Diagrams                                              | -15  |                 | 15   | %    |

# Note:

4. Guaranteed by design; not tested in production.

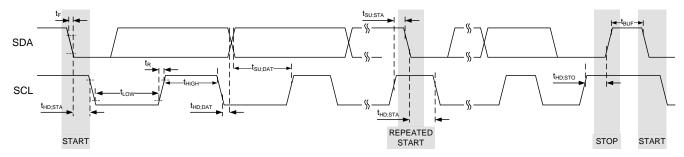

# I<sup>2</sup>C Timing Specifications

Guaranteed by design.

| Symbol                            | Parameter                                 | Conditions                               | Min. | Тур.              | Max. | Unit  |  |

|-----------------------------------|-------------------------------------------|------------------------------------------|------|-------------------|------|-------|--|

|                                   |                                           | Standard Mode                            |      |                   | 100  |       |  |

|                                   | SCL Clock Frequency                       | Fast Mode                                |      |                   | 400  | 1.11= |  |

| fscL                              |                                           | High-Speed Mode, C <sub>B</sub> ≤ 100 pF |      |                   | 3400 | kHz   |  |

|                                   |                                           | High-Speed Mode, C <sub>B</sub> ≤ 400 pF |      |                   | 1700 |       |  |

|                                   | Bus-Free Time between STOP                | Standard Mode                            |      | 4.7               |      |       |  |

| t <sub>BUF</sub>                  | and START Conditions                      | Fast Mode                                |      | 1.3               |      | μS    |  |

|                                   | START or Repeated START Hold Time         | Standard Mode                            |      | 4                 |      | μS    |  |

| thd;sta                           |                                           | Fast Mode                                |      | 600               |      |       |  |

|                                   | Tiold Time                                | High-Speed Mode                          |      | 160               |      | ns    |  |

|                                   |                                           | Standard Mode                            |      | 4.7               |      |       |  |

|                                   | SCL LOW Boried                            | Fast Mode                                |      | 1.3               |      | μS    |  |

| tLow SCL LOW Period               | High-Speed Mode, C <sub>B</sub> ≤ 100 pF  |                                          | 160  |                   |      |       |  |

|                                   |                                           | High-Speed Mode, C <sub>B</sub> ≤ 400 pF |      | 320               |      | ns    |  |

|                                   |                                           | Standard Mode                            |      | 4                 |      | μS    |  |

|                                   |                                           | Fast Mode                                |      | 600               |      |       |  |

| thigh                             | thigh SCL HIGH Period                     | High-Speed Mode, C <sub>B</sub> ≤ 100 pF |      | 60                |      | ns    |  |

|                                   |                                           | High-Speed Mode, C <sub>B</sub> ≤ 400 pF |      | 120               |      |       |  |

|                                   |                                           | Standard Mode                            |      | 4.7               |      | μ     |  |

| tsu;sta Repeated START Setup Time | Fast Mode                                 |                                          | 600  |                   |      |       |  |

|                                   |                                           | High-Speed Mode                          |      | 160               |      | ns    |  |

|                                   |                                           | Standard Mode                            |      | 250               |      |       |  |

| tsu;dat                           | Data Setup Time                           | Fast Mode                                |      | 100               |      | ns    |  |

|                                   |                                           | High-Speed Mode                          |      | 10                |      |       |  |

|                                   |                                           | Standard Mode                            | 0    |                   | 3.45 | μ     |  |

|                                   |                                           | Fast Mode                                | 0    |                   | 900  |       |  |

| t <sub>HD;DAT</sub>               | Data Hold Time                            | High-Speed Mode, C <sub>B</sub> ≤ 100 pF | 0    |                   | 70   | ns    |  |

|                                   |                                           | High-Speed Mode, C <sub>B</sub> ≤ 400 pF | 0    |                   | 150  |       |  |

|                                   |                                           | Standard Mode                            | 20+0 | ).1C <sub>B</sub> | 1000 |       |  |

|                                   |                                           | Fast Mode                                | 20+0 | ).1Св             | 300  |       |  |

| trcl                              | SCL Rise Time                             | High-Speed Mode, C <sub>B</sub> ≤ 100 pF |      | 10                | 80   | ns    |  |

|                                   |                                           | High-Speed Mode, C <sub>B</sub> ≤ 400 pF |      | 20                | 160  |       |  |

|                                   |                                           | Standard Mode                            | 20+0 | ).1C <sub>B</sub> | 300  |       |  |

|                                   |                                           | Fast Mode                                | 20+0 | ).1C <sub>B</sub> | 300  |       |  |

| t <sub>FCL</sub>                  | SCL Fall Time                             | High-Speed Mode, C <sub>B</sub> ≤ 100 pF |      | 10                | 40   | ns    |  |

|                                   |                                           | High-Speed Mode, C <sub>B</sub> ≤ 400 pF |      | 20                | 80   |       |  |

|                                   | 00 A D: T:                                | Standard Mode                            | 20+0 | ).1C <sub>B</sub> | 1000 |       |  |

| t <sub>RDA</sub>                  | SDA Rise Time<br>Rise Time of SCL after a | Fast Mode                                |      | ).1Св             | 300  |       |  |

| t <sub>RCL1</sub>                 | Repeated START Condition                  | High-Speed Mode, C <sub>B</sub> ≤ 100 pF |      | 10                | 80   | ns    |  |

|                                   | and after ACK Bit                         | High-Speed Mode, C <sub>B</sub> ≤ 400 pF |      | 20                | 160  | İ     |  |

Continued on the following page...

# I<sup>2</sup>C Timing Specifications

Guaranteed by design.

| Symbol       | Parameter                      | Conditions                               | Min.                 | Тур. | Max. | Unit |

|--------------|--------------------------------|------------------------------------------|----------------------|------|------|------|

|              |                                | Standard Mode                            | 20+0.1C              |      | 300  |      |

|              | Fast Mode                      | 20+0                                     | 20+0.1C <sub>B</sub> |      | 1    |      |

| <b>I</b> FDA | t <sub>FDA</sub> SDA Fall Time | High-Speed Mode, C <sub>B</sub> ≤ 100 pF |                      | 10   | 80   | ns   |

|              |                                | High-Speed Mode, C <sub>B</sub> ≤ 400 pF |                      | 20   | 160  |      |

|              |                                | Standard Mode                            |                      | 4    |      | μS   |

| tsu;sto      | Stop Condition Setup Time      | Fast Mode                                |                      | 600  |      |      |

|              |                                | High-Speed Mode                          |                      | 160  |      | ns   |

| Св           | Capacitive Load for SDA, SCL   |                                          |                      |      | 400  | pF   |

# **Timing Diagram**

Figure 4. I<sup>2</sup>C Interface Timing for Fast and Slow Modes

# **Typical Characteristics**

Unless otherwise specified; circuit of Figure 2, Voreg=4.2 V, Vbus=5.0 V, and TA=25°C.

- +25C --- +55C OREG Float Voltage Accuracy (%) +85C 0.5 0.0 -0.5 -1.0 3.63 3.72 3.81 3.90 3.99 4.08 4.17 4.26 4.35 4.44 OREG Setpoint (V)

Figure 5. lochrg Accuracy Over-Temperature, 3.7 VBAT

Figure 6. OREG Accuracy Over-Temperature, I<sub>BAT</sub>=100 mA

Figure 7. LDO Load Regulation, V<sub>OREG</sub>=V<sub>BAT</sub>=4.2 V

Figure 8. HZ / Sleep Mode Battery Discharge Current, VBUS Open, DIS=SDA=SCL=0 V

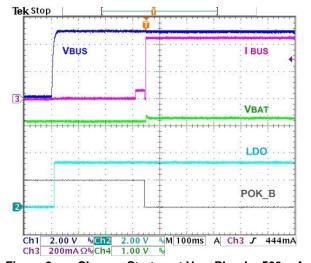

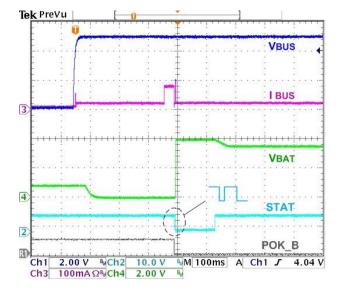

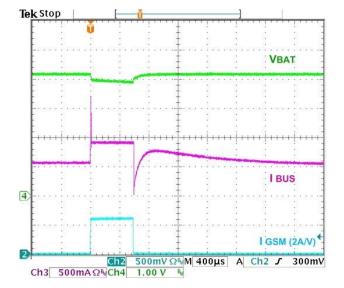

Figure 9. Charger Startup at V<sub>BUS</sub> Plug-In, 500 mA  $I_{OCHRG}$ , 3.2 V<sub>BAT</sub>, 1 k $\Omega$  LDO Load, ILIM=DBP=1.8 V

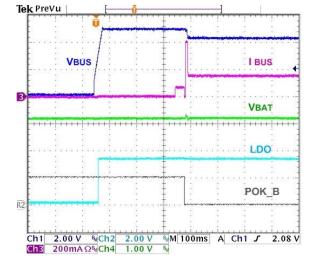

Figure 10. Charger Startup at VBUS Plug-In Using 150 mA Current Limited Source, 3.2 V<sub>BAT</sub>, 500 mA I<sub>OCHRG</sub>, 1 kΩ LDO Load, ILIM=DBP=1.8 V

# **Typical Characteristics**

Unless otherwise specified; circuit of Figure 2, Voreg=4.2 V, Vbus=5.0 V, and Ta=25°C.

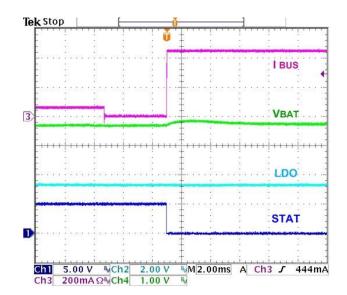

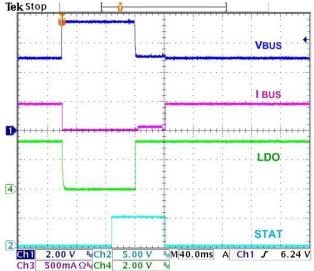

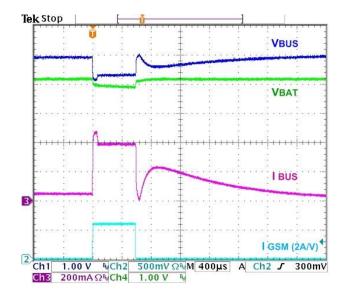

Figure 11. Charger Startup Using HZ Bit Reset, 3.7  $V_{BAT}$ , 500 mA  $I_{OCHRG}$ , 1  $k\Omega$  LDO Load, ILIM=DBP=1.8 V

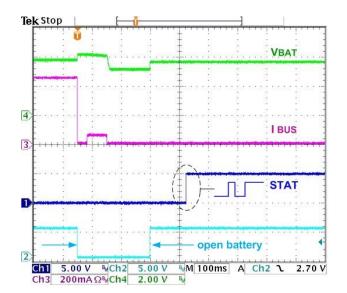

Figure 12. Charger Startup at V<sub>BUS</sub> Plug-In with Dead Battery (Protection Switch Open), 1 kΩ LDO Load, ILIM=DBP=0 V

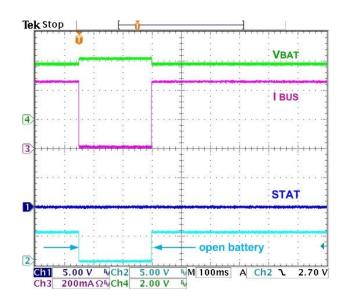

Figure 13. Charger Startup at  $V_{BUS}$  Plug-In with No Battery, 300  $\Omega$  LDO Load, ILIM=DBP=0 V

Figure 14. VBUS OVP Response while Charging, 3.7 V<sub>BAT</sub>, 500 mA  $I_{OCHRG}$ , 1 k $\Omega$  LDO Load, ILIM=DBP=1.8 V

# **Typical Characteristics**

Unless otherwise specified; circuit of Figure 2, Voreg=4.2 V, Vbus=5.0 V, and TA=25°C.

Figure 15. Battery Removal/Insertion while Charging, 3.7 VBAT, 500 mA IOCHRG, ILIM=DBP=1.8 V, ITERM\_DIS=0

Figure 16. Battery Removal/Insertion while Charging, 3.7 VBAT, 500 mA IOCHRG, ILIM=DBP=1.8 V, ITERM\_DIS=1

Figure 17. 1.2 A Load Pulse, t<sub>R</sub>=t<sub>F</sub>=5 μs, 4.19 V<sub>BAT</sub>, 1.0 A lochrg

Figure 18. 1.2 A Load Pulse, t<sub>R</sub>=t<sub>F</sub>=5 μs, 500 mA Current Limited Source, 4.2 VBAT, 1.0 AIOCHRG, 4.32 VBUS\_REF

# **Basic Operation**

The FAN54110 is a USB-compatible single-cell Li-lon charger with support for Dead Battery Provision (DBP) and a maximum charge current rated at 1 A.

The FAN54110 conforms to all the requirements for the DBP within the BC1. 2 specifications, including a 30-minute timer that cannot exceed 45 minutes.

The FAN54110 is designed to be stable with space-saving ceramic capacitors and is available in a 15-bump, 0.4 mm pitch, WLCSP.

### **Charger Circuit Details**

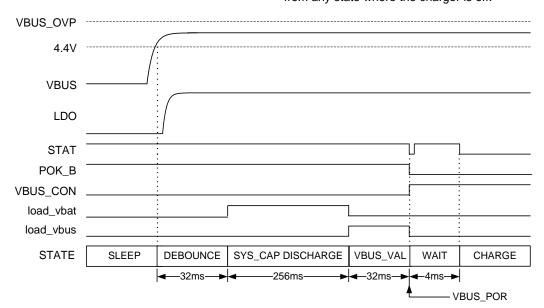

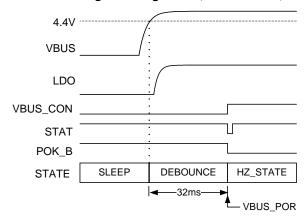

#### **VBUS Insertion**

When the IC detects that  $V_{BUS}$  has risen above  $V_{IN(MIN)1}$ , adapter validation and battery voltage detection will occur before charging begins. To pass validation,  $V_{BUS}$  must remain above  $V_{IN(MIN)1}$  and below  $V_{BUSOVP}$  for  $t_{VBUS\_VALID}$  before the IC initiates charging. Refer to Figure 20 and Figure 21 for details.

If  $V_{BUS}$  is validated, the POK\_B pin pulls LOW and an interrupt is issued to indicate to the system that VBUS is connected. This point is considered to be VBUS\_POR.

If VBUS fails validation, the POK\_B pin remains HIGH and an interrupt is issued. Re-validation is attempted every two seconds.

Setting the HZ\_MODE bit or DIS pin prevents validation from occurring after VBUS rises above V<sub>IN(MIN)1</sub>, but, VBUS validation will be performed prior to entering Charge State from any state where the charger is off.

Figure 19. VBUS Plug-In Timing: DIS=0, HZ\_MODE=0, DBP=1

Figure 20. VBUS Plug-In Timing: DIS=1 or (DBP=1 and HZ\_MODE=1)

#### **VBUS POR and DBP Charging**

If the DBP pin is HIGH at VBUS\_POR, the IC operates in accordance with its  $I^2C$  register settings and starts the  $t_{32s}$  timer when charging begins. This is the normal operating mode for the FAN54110.

If the DBP pin is LOW at VBUS\_POR or the DBP pin transitions from HIGH to LOW when VBUS is valid, the FAN54110:

- Resets its registers to default values

- Charges with its charge current limit set by the state of the ILIM pin:

- ILIM= LOW, I<sub>OCHRG</sub>=100 mA

- ILIM= HIGH, I<sub>OCHRG</sub>=350 mA

- Starts the t<sub>30MIN</sub> timer

- Sources 0.6 V to the D+ pin

BC1.2 and USB 2.0 allow a portable device (defined as a device with a battery) with a dead battery to take a maximum of 100 mA from the USB VBUS line for a maximum of 45 minutes as long as the portable device forces the D+ line to 0.6 V typical.

Once DBP transitions from LOW to HIGH, D+ is three-stated and charge parameters may be programmed by the host. Charge current remains controlled by the state of the ILIM pin and the  $t_{30\text{MIN}}$  timer continues running until the first I<sup>2</sup>C write occurs; at which time, charge current is controlled by the Iocharge (Reg03h[7:4]) bits and the timer changes to  $t_{325}$ .

The ILIM and DBP pins are internally pulled down and there is typically nothing to force them HIGH at this point due to the processor / system not yet being awake. When the t<sub>30MIN</sub> timer expires, the FAN54110 removes the 0.6 V from D+ and stops charging. The D+ pin is three-stated when DBP is HIGH.

### **Battery Absent at VBUS Insertion**

Before charging begins, if  $V_{\text{BAT}}$  is below  $V_{\text{SHORT}}$ , the FAN54110 will determine whether the battery is absent or present.

To accomplish this, the IC temporarily raises  $V_{OREG}$  to 4.0 V after  $V_{BAT}$  has risen above  $V_{SHORT}$ . If  $V_{BAT}$  remains below 3.7 V for more than 128 ms, the battery is present. If  $V_{BAT}$  is above 3.7 V after 128 ms, the battery is assumed absent.

If battery absence is detected, all registers are reset to their default values, the NOBAT bit is set, and an interrupt is generated. Also, it is assumed the DBP pin is LOW since the system was without a power source prior to plug in. The FAN54110 will provide power to the system with STAT HIGH in DBP Mode until otherwise instructed through I<sup>2</sup>C commands. This allows the host processor an opportunity to detect charger type and negotiate with the USB host for higher current.

The IC continues to provide current, provided that:

- a timer (t<sub>30MIN</sub> or t<sub>32S</sub>) is running

- HZ\_MODE (Reg=01h[6])=0 and DIS=LOW.

The current drawn from VBUS is determined by either the state of ILIM pin or the  $I_{\text{OCHARGE}}$  programming.

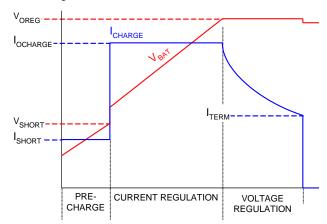

#### **Charging Stages**

Figure 21 shows the different charging stages when a battery is present and discharged below 2.25 V.

PRE-CHARGE is when the battery voltage is below V<sub>SHORT</sub> and a current of I<sub>SHORT</sub> is used to charge the battery above VSHORT. This stage is typically used to recover a deeply discharge battery with its protection switch open.

CURRENT REGULATION increases charging current considerably above I<sub>SHORT</sub> to a programmable I<sub>OCHARGE</sub> (Reg 03h[7:4]) level.

VOLTAGE REGULATION occurs during charging when VBAT reaches VOREG (Reg4[5:0]). The current charging the battery is reduced, limited by the battery's ESR and its internal cell voltage.

- If ITERM\_DIS (Reg03h[0])=0, charging current decreases to ITERM (Reg03h[3:0]), where Charge Termination occurs.

- If ITERM\_DIS=1 (default configuration), charging will continue past I<sub>TERM</sub> until current decreases to 0A, where the part will remain in Charge Mode with the t<sub>32S</sub> timer running.

Figure 21. Typical Charge Profile

### **Charge Termination**

During Voltage Regulation, charging continues until the  $I_{BAT} \leq I_{TERM}$ . If ITERM\_DIS=0, charging stops and the  $t_{32S}$  timer continues counting. The STAT pin remains LOW until the IC determines whether the  $I_{BAT} < I_{TERM}$  condition was caused by VBUS removal, Battery Removal, or by the battery being fully charged (Charge Termination).

During Charge Termination, the  $t_{32S}$  timer will continue running, but, if it expires will not reset all registers until Recharge. Setting the TMR\_RST bit (Reg8[7]) during Charge Termination will reset the  $t_{32S}$  timer. Refer to the Timers section for more details.

#### **Recharge from Charge Termination**

During Charge Termination, if  $V_{BAT}$  falls by  $V_{RCH}$  below  $V_{OREG}$ , charging starts again.

A recharge condition de-bounce time of 60 ms is used to prevent transient battery load currents (such as GSM current pulses) from triggering auto-recharge unnecessarily.

#### **Battery Removal during Charging**

When ITERM\_DIS=0 and the charge current drops below the ITERM setting, a load current (IDETECT) is placed on VBAT in order to determine if the battery was removed during charging. If the battery is determined to be present, the load is removed, and Charge Done State is entered. If the battery is determined to be absent, the IC enters a fault state, which waits with the charger disabled for two seconds, then restarts the charger validation process.

- If the battery is determined to be present, the load is removed, and Charge Termination occurs.

- If the battery is determined to be absent, charging is disabled, all registers except ITERM\_DIS are reset to default values, the NOBAT interrupt bit is set, and the STAT pin rises. After 2s, the charger will restart validation and if the battery is re-inserted, the IC will return to Charge State.

In response to  $V_{BAT}$  collapsing, though, the system electronics have likely lowered the DBP pin which will reset all registers. As a result, the ITERM\_DIS bit will be reset to 1, which will set the unloaded VBAT pin to output 3.54V (the default  $V_{OREG}$  setting) and place the IC in Charge State with the NOBAT bit remaining set until the next VBUS\_POR validation.

#### **VBUS Removal and SLEEP**

When  $V_{BUS}$  falls below either  $V_{IN(MIN)2}$  or  $V_{BAT}$ , the IC ceases charging, the POK\_B pin sets HIGH, and an interrupt occurs to indicate to the system that VBUS has been removed. The IC then enters the Sleep State.

#### LDO

The FAN54110 provides a regulated 3.3 V LDO output when a valid  $V_{BUS}$  condition exists to power the USB PHY. Regulation occurs within 5 ms of valid  $V_{BUS}$  being applied.

LDO load current is derived from  $V_{BUS}$  and is subject to the  $I_{OCHARGE}$  setting / limit. Available battery charging current is reduced by the LDO load current.

# **Charger/Battery/System Protections**

#### **Timers**

There are two timers on the FAN54110; t<sub>328</sub> and the t<sub>30MIN</sub>.

The t<sub>32S</sub> timer is for normal operation where the DBP pin is HIGH. When charging begins after a VBUS\_POR with the DBP pin HIGH, the t<sub>32S</sub> timer is started. If the t<sub>32S</sub> timer is allowed to expire, charging ceases and the part will enter the IDLE State where all registers are reset. A write to any register can return the IC to charging. To avoid a t<sub>32S</sub> timer fault, the host must reset the timer by periodically setting the TMR\_RST (Reg08h[7]) bit before it expires.

The  $t_{30\text{MIN}}$  timer is for unattended charging. If  $V_{\text{BAT}} < V_{\text{SHORT}}$  the device is assumed to be dead and the DBP pin is, therefore, LOW. When charging begins after a VBUS\_POR with  $V_{\text{BAT}} < V_{\text{SHORT}}$  and the DBP pin LOW, the  $t_{30\text{MIN}}$  timer is started. If the  $t_{30\text{MIN}}$  timer is allowed to expire, charging

ceases and the part will enter the IDLE State where all registers are reset. Only a new VBUS\_POR will return the IC to charging.

During unattended charging, if the DBP pin transitions from LOW to HIGH (due to the host waking up and controlling the charger):

- 1- If VBAT<VSHORT, the t<sub>30MIN</sub> timer will continue running.

- 2- If VBAT>VSHORT, the t30MIN timer will continue running until the first I<sup>2</sup>C write. Then the t30MIN will stop and the t32S timer is started.

#### **VBUS Over-Voltage**

The FAN54110 contains programmable Over-Voltage Protection (OVP) on VBUS, ranging from 6.5 V to 8.0 V, as specified in the  $V_{\text{BUSOVP}}$  (Reg01h[2:1) bits with a default setting of 7 V. If OVP is detected, the FAN54110 terminates charging functionality if charging is active when OVP is detected. The FAN54110 interrupts the host when the OVP event occurs and sets the OVP FLAG bit.

#### **Dynamic Input Voltage Control (DIVC)**

V<sub>BUS</sub> is typically 5 V +5% / -10%, depending on the charging current. If the FAN54110 is programmed to a higher current than the charger can support, a regulation control actively regulates the charging current to maintain at least 4.32V (typical) on VBUS. This level is controlled via the VBUS\_REF (Reg02h[3:2]) bits. The FAN54110 reduces the charging current to ensure  $V_{BUS}$  is maintained above the  $V_{BUS_REF}$  setting. The DIVC regulation loop is enabled by default and disabled with the VBUS\_REG (Reg01h[5]) bit.

If DIVC is disabled, the charging cycle stops when  $V_{BUS}$  falls below the  $V_{BUS}$  valid falling threshold ( $V_{INMIN2}$ ) or below  $V_{BAT}$ . Charging remains stopped until  $V_{BUS}$  rises above the rising  $V_{BUS}$  valid threshold ( $V_{INMIN1}$ ) and stays above this threshold.

### Thermal Regulation and Shutdown

The thermal regulation loop is enabled if the junction temperature reaches the threshold defined by the  $T_{CF}$  (Reg02h[5:4]) bits. When  $T_{CF}$  is reached, the FAN54110 reduces the charging current to 90 mA until the junction temperature falls below  $T_{CF}.$  Charge current is then incremented in 1 ms steps until the  $I_{OCHRG}$  level is reached. This algorithm allows for the fastest recovery from a thermal regulation event while averaging a current that keeps the temperature below  $T_{CF}.$

The FAN54110 terminates charging completely if the junction temperature exceeds  $T_{\text{SHUTDWN}}$  (145°C).

In both cases, the temperature event is indicated via the TREG\_FLAG and TSD\_FLAG bits in the FAULT\_INTERRUPT (Reg05h) register. Recovery from either event is indicated via the OT\_RECOV bit in the same register.

Additional  $\theta_{JA}$  data points, measured using the FAN54110 evaluation board, are given in the table below (measured with  $T_A$ =25°C). Note that as power dissipation increases, the effective  $\theta_{JA}$  decreases due to the larger difference between the die temperature and ambient.

Table 1. Evaluation Board Measured θ<sub>JA</sub>

| Power (W) | $\Theta_{JA}$ |

|-----------|---------------|

| 0. 504    | 54°C/W        |

| 0. 844    | 50°C/W        |

| 1. 506    | 46°C/W        |

#### **Production Test Mode**

Production Test Mode (PTM) provides power for the system from the USB port. This eliminates the burden of having an attached battery during production line testing.

PTM is enabled when the PTM\_EN bit is HIGH and when the battery is absent (NOBAT (Reg05h[0])=1). In PTM, Q1 (see Figure 2) is turned on, but it is current limited to about 2.5 A.  $V_{BAT}$  is initially regulated to the default  $V_{OREG}$  setting of 3.54 V in PTM. However, VBAT can be programmed to output any  $V_{OREG}$  from 3.38 V to 4.44 V, as specified in the VOREG (Reg04h[5:0]) bits.

Care should be taken to limit the RMS current in PTM Mode. Thermal regulation ( $T_{CF}$ ) and thermal shutdown are enabled in PTM.

# **Charging Status and Interrupt Reporting**

The STAT and POK\_B pins are used to indicate to the host the presence or absence of a valid charging source, charging status, as well as fault status.

The FAULT\_INTERRUPT (Reg05h[7:0]) and STATUS\_INTERRUPT (Reg07h[7:5]) bits have associated MASK bits and there is a general INTERRUPT (Reg01h[0]) bit. This bit is set when any interrupt occurs, even if the occurring fault is masked. While this bit is set to 1, all subsequent STAT pulses are prevented. Reading this register clears the bit.

The FAULT\_INTERRUPT and STATUS\_INTERRUPT registers and the INTERRUPT (Reg01h[0]) bit should be read and cleared on every STAT pin rising edge and POK\_B pin falling edge to ensure that all faults, masked or otherwise, as well as adapter presence changes are immediately available to the host.

#### POK B Pin

The POK\_B pin is used to indicate the presence or absence of a valid charging source to the host processor.

Table 2. POK\_B Pin State

| POK_B Charging Source |                                                 |

|-----------------------|-------------------------------------------------|

| HIGH                  | absent or not valid                             |

| LOW                   | VINMIN(1) <vbus<vbusovp< td=""></vbus<vbusovp<> |

#### **STAT Pin**

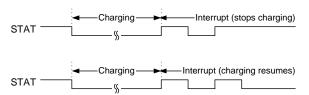

The STAT pin is used to indicate charging status, as well as to signal the host processor of a change in the status of the IC or system.

The static state of the STAT pin is determined by whether the IC is charging a battery:

Table 3. STAT Pin Static State

| CHARGER | NOBAT<br>(Reg05h[0]) | STAT Pin |

|---------|----------------------|----------|

| ON      | 0                    | LOW      |

| OFF     | X                    | HIGH     |

| Х       | 1                    | HIGH     |

The STAT pin emits a 128  $\mu$ s LOW pulse whenever an unmasked interrupt event occurs and the INTERRUPT (Reg01h[0]) bit is reset to "0".

Any interrupt pulse that occurs while STAT is statically LOW is preceded by 128  $\mu s$  of STAT HIGH, as shown below.

Figure 22. STAT Interrupt Pulse Behavior

#### Masking the STAT Pin Interrupt

The FAULT\_INTERRUPT and STATUS\_INTERRUPT register bits have associated MASK bits located in Reg06h[7:0] and Reg07h[3:1] that will mask STAT pin pulses.

When a mask bit is set and an event occurs:

- The associated FAULT\_INTERRUPT or STATUS\_INTERRUPT bit is set

- The INTERRUPT bit is set

- The STAT pin will not pulse

#### INTERRUPT (Reg01h[0]) Bit

When bits in the FAULT\_INTERRUPT and STATUS\_INTERRUPT register are set, the INTERRUPT (Reg01h[0]) bit is set before the falling edge of STAT.

If additional interrupt conditions occur before the host clears the INTERRUPT bit by reading Reg01h, the STAT pin does not pulse.

#### I<sup>2</sup>C Interface

The serial interface is compatible with Standard Mode and Fast Mode I<sup>2</sup>C bus specifications. The SCL line is an input and the SDA line is a bi-directional open-drain output; it can only pull down the bus when active. The SDA line only pulls LOW during data reads and when signaling ACK. All data is shifted in MSB (bit 7) first.

#### Slave Address

Table 4. I<sup>2</sup>C Slave Address Byte

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|---|---|---|---|---|---|---|-----|

| 1 | 1 | 0 | 1 | 0 | 1 | 1 | R/W |

In hex notation, the slave address assumes a 0 LSB. The hex slave address for the FAN54110 is D6.

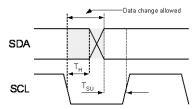

### **Bus Timing**

As shown below, data is normally transferred when SCL is LOW. Data is clocked in on the rising edge of SCL. Typically, data transitions at or shortly after the falling edge of SCL to allow ample time for the data to set up before the next SCL rising edge.

Figure 23. Data Transfer Timing

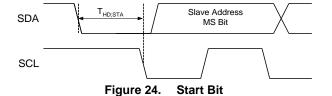

Each bus transaction begins and ends with SDA and SCL HIGH. A transaction begins with a START condition, which is defined as SDA transitioning from 1 to 0 with SCL HIGH, as shown below.

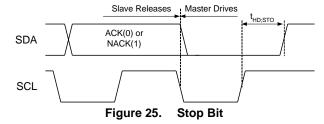

A transaction ends with a STOP condition, which is defined as SDA transitioning from 0 to 1 with SCL HIGH, as shown in Figure 25.

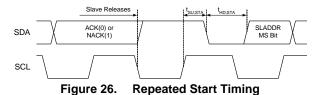

During a read from the FAN54110, the master issues a Repeated Start after sending the register address and before resending the slave address. The Repeated Start is a 1-to-0 transition on SDA while SCL is HIGH, as shown below.

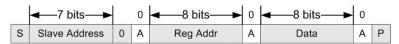

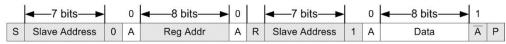

Read and Write Transactions

The figures below outline the sequences for data read and write. Bus control is signified by the shading of the packet,

defined as Master Drives Bus and All addresses and data are MSB first.

Table 5. Bit Definitions for Write and Read Transactions

| Symbol | Definition                                                          |

|--------|---------------------------------------------------------------------|

| S      | START, see Figure 24.                                               |

| А      | ACK. The slave drives SDA to 0 to acknowledge the preceding packet. |

| Ā      | NACK. The slave sends a 1 to NACK the preceding packet.             |

| R      | Repeated START, see Figure 26                                       |

| Р      | STOP, see Figure 25                                                 |

Figure 27. Write Transaction

Figure 28. Read Transaction

# **Register Descriptions**

# Table 6. Register Bit Definitions

Default values are in bold text with VBUS removed and VBAT=3.8V.

| Bit    | Name     | Туре    | Description                                       |                                                                     |  |  |  |  |

|--------|----------|---------|---------------------------------------------------|---------------------------------------------------------------------|--|--|--|--|

| IC_INF | <b>O</b> | Registe | r Address: 00h                                    | Default= 100X XXXX (XXh)                                            |  |  |  |  |

| 7:5    | VENDOR   | R       | 100: Identifies ON Semiconductor as the sup       | pplier                                                              |  |  |  |  |

| 4:3    | PN       | R       | Part number bits, see the Ordering Info on page 2 |                                                                     |  |  |  |  |

| 2:0    | REV      | R       | IC Revision. Revision is 1.X, where X is the o    | C Revision. Revision is 1.X, where X is the decimal of these 3 bits |  |  |  |  |

| CHAR | RGE_CTRL1           | Registe | er Address                                                                                                                                                                                                                                    | s: 01h                                                                                                      | Default=0011 0010 (32h)                                                            |  |  |  |  |

|------|---------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|--|--|--|

| 7    | RESET               | W       | Setting this bit to 1 resets all registers to default values and deactivates t <sub>32S</sub> , causing the part to go to into IDLE State until the next I <sup>2</sup> C write reactivates t <sub>32S</sub> .  This bit returns 0 when read. |                                                                                                             |                                                                                    |  |  |  |  |

| 6    | HZ_MODE             | R/W     |                                                                                                                                                                                                                                               | rging is enabled.<br>rging is disabled.                                                                     |                                                                                    |  |  |  |  |

| 5    | VBUS_REG            | R/W     |                                                                                                                                                                                                                                               | regulation loop disabled.<br>regulation loop enabled.                                                       |                                                                                    |  |  |  |  |

| 4    | VBUS_LOOP           | R       |                                                                                                                                                                                                                                               | (                                                                                                           |                                                                                    |  |  |  |  |

| 3    | Reserved            | R       | This bit re                                                                                                                                                                                                                                   | eturns 0 when read.                                                                                         |                                                                                    |  |  |  |  |

|      |                     |         | disabled u                                                                                                                                                                                                                                    | US is at or above this threshold, a V <sub>BUS</sub> until the fault clears.  V <sub>BUSOVE</sub> Threshold | OVP fault is enunciated and the charger is                                         |  |  |  |  |

|      |                     |         | [2:1]                                                                                                                                                                                                                                         | V <sub>BUSOVP</sub> Threshold                                                                               | ]                                                                                  |  |  |  |  |

| 2:1  | V <sub>BUSOVP</sub> | R/W     | 00                                                                                                                                                                                                                                            | 6.5                                                                                                         |                                                                                    |  |  |  |  |

|      |                     |         | 01                                                                                                                                                                                                                                            | 7.0                                                                                                         |                                                                                    |  |  |  |  |

|      |                     |         | 10                                                                                                                                                                                                                                            | 7.5                                                                                                         |                                                                                    |  |  |  |  |

|      |                     |         | 11                                                                                                                                                                                                                                            | 8.0                                                                                                         |                                                                                    |  |  |  |  |

| 0    | INTERRUPT           | RC      | section fo                                                                                                                                                                                                                                    | or details.<br>s bit is set to 1, all subsequent STAT p                                                     | Charging Status and Interrupt Reporting ulses are prevented. Reading this register |  |  |  |  |

| CHAR | GE_CTRL2         | Registe                                       | r Address   | : 02h         |                                                       | Default=0010 0111 (27h)                                    |    |  |  |  |

|------|------------------|-----------------------------------------------|-------------|---------------|-------------------------------------------------------|------------------------------------------------------------|----|--|--|--|

| 7    | PTM_EN           | SAT (Reg5[0])=1. See the Production Test Mode |             |               |                                                       |                                                            |    |  |  |  |

| 6    | Reserved         | R                                             | This bit re | turns 0 w     | hen read.                                             |                                                            |    |  |  |  |

|      |                  |                                               |             |               | hold at which the current in and Shutdown section for | s reduced to allow the device to cool. See the or details. |    |  |  |  |

|      |                  |                                               | Table 8.    | Temp          | erature Threshold Set                                 | tings                                                      |    |  |  |  |

|      |                  |                                               | DEC         | BIN           | T <sub>CF</sub>                                       |                                                            |    |  |  |  |

| 5:4  | T <sub>C</sub> F | R/W                                           | 0           | 00            | 70                                                    |                                                            |    |  |  |  |

|      |                  |                                               |             |               | 1                                                     | 01                                                         | 85 |  |  |  |

|      |                  |                                               |             |               |                                                       |                                                            |    |  |  |  |

|      |                  |                                               | 3           | 11            | 120                                                   |                                                            |    |  |  |  |

|      |                  |                                               | Sets the \  | BUS_REF t     | hreshold.                                             |                                                            |    |  |  |  |

|      |                  |                                               | Table 9.    | $V_{BUS_{R}}$ | REF Threshold                                         |                                                            |    |  |  |  |

|      |                  |                                               | DEC         | BIN           | $V_{BUS\_REF}$                                        |                                                            |    |  |  |  |

| 3:2  | VBUS_REF         | R/W                                           | 0           | 00            | 4.22                                                  |                                                            |    |  |  |  |

|      |                  |                                               | 1           | 01            | 4.32                                                  |                                                            |    |  |  |  |

|      |                  |                                               | 2           | 10            | 4.37                                                  |                                                            |    |  |  |  |

|      |                  |                                               | 3           | 11            | 4.46                                                  |                                                            |    |  |  |  |

| 1    | VRCH_DIS         | R/W                                           | 1           |               | arts if $V_{BAT} < V_{OREG}$ - $V_{RCH}$ .            | ally if V <sub>BAT</sub> drops.                            |    |  |  |  |

| 0    | ITERM_DIS        | R/W                                           |             |               | inates at the programmed s not terminate at the pr    |                                                            |    |  |  |  |

| BAT |              | Registe | r Address | s: 03h     |                                                                                   | Default=0010 0110 (26h)                                                                     |

|-----|--------------|---------|-----------|------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

|     |              |         | consume   | d by the 3 | CHRG, is the maximum currer<br>3.3 V LDO, therefore, reduce<br>GE <b>Settings</b> | nt drawn from VBUS during charging. Current es the current available to charge the battery. |

|     |              |         | DEC       | BIN        | I <sub>OCHARGE</sub> (mA)                                                         | 7                                                                                           |

|     |              |         | 0         | 0000       | 100                                                                               |                                                                                             |

|     |              |         | 1         | 0001       | 300                                                                               |                                                                                             |

|     |              |         | 2         | 0010       | 350                                                                               |                                                                                             |

|     |              |         | 3         | 0011       | 400                                                                               |                                                                                             |

|     |              |         | 4         | 0100       | 450                                                                               | 7                                                                                           |

|     |              |         | 5         | 0101       | 500                                                                               |                                                                                             |

| 7:4 | IOCHARGE     | R/W     | 6         | 0110       | 550                                                                               | 7                                                                                           |

|     |              |         | 7         | 0111       | 600                                                                               | 7                                                                                           |

|     |              |         | 8         | 1000       | 650                                                                               | 7                                                                                           |

|     |              |         | 9         | 1001       | 700                                                                               | 7                                                                                           |

|     |              |         | 10        | 1010       | 750                                                                               |                                                                                             |

|     |              |         | 11        | 1011       | 800                                                                               |                                                                                             |

|     |              |         | 12        | 1100       | 850                                                                               |                                                                                             |

|     |              |         | 13        | 1101       | 900                                                                               |                                                                                             |

|     |              |         | 14        | 1110       | 950                                                                               |                                                                                             |

|     |              |         | 15        | 1111       | 1000                                                                              | 2                                                                                           |

|     |              |         | Table 1   | I. ITERN   | // Settings                                                                       |                                                                                             |

|     |              |         | DEC       | BIN        | ITERM (mA)                                                                        |                                                                                             |

|     |              |         | 0         | 0000       | 20                                                                                |                                                                                             |

|     |              |         | 1         | 0001       | 30                                                                                |                                                                                             |

|     |              |         | 2         | 0010       | 40                                                                                | 7                                                                                           |

|     |              |         | 3         | 0011       | 50                                                                                | 7                                                                                           |