# **Electronic Fuse**

The NIS5112 is an integrated switch utilizing a high side N-channel FET driven by an internal charge pump. This switch features a MOSFET which allows for current sensing using inexpensive chip resistors instead of expensive, low impedance current shunts.

It is designed to operate in 12 V systems and includes a robust thermal protection circuit.

# Features

- Integrated Power Device

- Power Device Thermally Protected

- No External Current Shunt Required

- Enable/Timer Pin

- Adjustable Slew Rate for Output Voltage

- 9 V to 18 V Input Range

- 30 mΩ Typical

- Internal Charge Pump

- ESD Ratings: Human Body Model (HBM); 4000 V

- These are Pb-Free Devices

### **Typical Applications**

Hard Drives

# **ON Semiconductor®**

www.onsemi.com

### MARKING DIAGRAM

# **ORDERING INFORMATION**

| Device       | Package                                      | Shipping <sup>†</sup> |

|--------------|----------------------------------------------|-----------------------|

| NIS5112D1R2G | 1R2G SOIC-8 2<br>Latch Off Tape<br>(Pb-Free) |                       |

| NIS5112D2R2G | SOIC-8<br>Auto-Retry<br>(Pb-Free)            | 2500 /<br>Tape & Reel |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

8  $V_{CC}$ Charge Voltage Regulator Pump Current Current Limit Limit 4 Overvoltage Clamp Source Thermal 5, 6, 7 Latch Voltage Enable/ Slew Rate Timer Enable/Timer GND dV/dt 3 2 Figure 1. Block Diagram

#### Table 1. FUNCTIONAL PIN DESCRIPTION

| Pin   | Function           | Description                                                                                                                                                                                        |  |

|-------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 3     | Enable/Timer       | er A high level signal on this pin allows the device to begin operation. Connection of a capacitor will delay turn on for timing purposes. A low input signal inhibits the operation.              |  |

| 1     | Ground             | Negative input voltage to the device. This is used as the internal reference for the IC.                                                                                                           |  |

| 4     | I <sub>Limit</sub> | A resistor between this pin and the source pin sets the current limit level.                                                                                                                       |  |

| 5,6,7 | Source             | Source of power FET, which is also the switching node for the load.                                                                                                                                |  |

| 2     | dV/dt              | A capacitor from this pin to ground programs the slew rate of the output at turn on. This capacitor is discharged by an internal discharge circuit when the device is disabled via the enable pin. |  |

| 8     | V <sub>CC</sub>    | Positive input voltage to the device.                                                                                                                                                              |  |

Table 2. MAXIMUM RATINGS (Maximum ratings are those, that, if exceeded, may cause damage to the device. Electrical characteristics are not guaranteed over this range)

| Rating                                                                                          |                                                                |                   | Value                    | Unit         |

|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------|--------------------------|--------------|

| Input Voltage, Operating,                                                                       | Steady-State (Input+ to Input-)<br>Transient (Conditions 1 ms) | V <sub>in</sub>   | -0.3 to 18<br>-0.3 to 25 | V            |

| Drain Voltage, Operating,                                                                       | Steady-State (Drain to Input-)<br>Transient (Conditions 1 ms)  | V <sub>DD</sub>   | -0.3 to 18<br>-0.3 to 25 | V            |

| Drain Current, Peak (Internally Clamped)                                                        |                                                                | I <sub>Dpk</sub>  | 25                       | А            |

| Drain Current, Continuous (T <sub>A</sub> =25°C), (Note 2)                                      |                                                                | I <sub>Davg</sub> | 5.3                      | А            |

| Thermal Resistance, Junction-to-Air<br>0.5 in <sup>2</sup> Copper<br>1.0 in <sup>2</sup> Copper |                                                                | Q <sub>JA</sub>   | 120<br>110               | °C/W<br>°C/W |

| Thermal Resistance, Junction-to-Lead (Pin 8)                                                    |                                                                | Q <sub>JL</sub>   | 27                       | °C/W         |

| Power Dissipation ( $T_A = 25^{\circ}C$ ) (Note 1)                                              |                                                                | P <sub>max</sub>  | 1.0                      | W            |

| Operating Temperature Range (Note 2)                                                            |                                                                | TJ                | -40 to 175               | °C           |

| Nonoperating Temperature Range                                                                  |                                                                | TJ                | -55 to 175               | °C           |

| Lead Temperature, Soldering (10 Sec)                                                            |                                                                | TL                | 260                      | °C           |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Mounted on FR-4 board, 1 in sq pad, 1 oz coverage.

2. Actual maximum junction temperature is limited by an internal protection circuit and will not reach the absolute maximum temperature as specified.

# NIS5112

| Characteristics                                                                                                                                                                                                                 | Symbol              | Min                | Тур                | Max                | Unit     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------|--------------------|--------------------|----------|

| POWER FET                                                                                                                                                                                                                       |                     |                    |                    |                    |          |

| Delay Time (Enabling of Chip to Beginning of Conduction (10% of IPK))                                                                                                                                                           | T <sub>dly</sub>    | _                  | 5.0                | -                  | ms       |

| Charging Time (Beginning of Conduction to 90% of V <sub>out</sub> ) $C_{dV/dt}$ = 1 µF, $C_{load}$ = 1000 µF                                                                                                                    | t <sub>chg</sub>    | -                  | 64                 | -                  | ms       |

| ON Resistance<br>$(I_D = 2 A, T_J = -20^{\circ}C)$ (Note 3)<br>$(I_D = 2 A, T_J = 25^{\circ}C)$<br>$(I_D = 2 A, T_J = 100^{\circ}C)$ (Note 3)                                                                                   | R <sub>DSon</sub>   | -                  | 23.5<br>28<br>37   | 27.5<br>32<br>43.5 | mΩ       |

| Off State Output Voltage<br>$(V_{in} = 12 V_{dc}, Enable Low, V_{dc}, T_J = -20^{\circ}C)$ (Note 3)<br>$(V_{in} = 12 V_{dc}, Enable Low, T_J = 25^{\circ}C)$<br>$(V_{in} = 12 V_{dc}, Enable Low, T_J = 100^{\circ}C)$ (Note 3) | V <sub>off</sub>    | -<br>-<br>-        | -<br>-<br>-        | 120<br>120<br>200  | mV       |

| Output Capacitance (V <sub>DS</sub> = 12 V <sub>dc</sub> , V <sub>GS</sub> = 0 V <sub>dc</sub> , f = 10 kHz)                                                                                                                    |                     | -                  | 396                | -                  | pF       |

| THERMAL LATCH                                                                                                                                                                                                                   |                     |                    |                    |                    |          |

| Shutdown Temperature (Note 3)                                                                                                                                                                                                   | T <sub>SD</sub>     | 125                | 135                | 145                | °C       |

| Thermal Hysteresis (Auto Retry Only) (Note 3)                                                                                                                                                                                   | T <sub>hyst</sub>   | _                  | 40                 | _                  | °C       |

| ENABLE/TIMER                                                                                                                                                                                                                    | · nyst              |                    | 10                 |                    | Ů        |

| Enable Voltage (Turn-on)<br>( $R_{load} = 2 \text{ K}, T_J = -20^{\circ}\text{C}$ ) (Note 3)<br>( $R_{load} = 2 \text{ K}, T_J = 25^{\circ}\text{C}$ )<br>( $R_{load} = 2 \text{ K}, T_J = 100^{\circ}\text{C}$ ) (Note 3)      | V <sub>ENon</sub>   | 2.45<br>2.5<br>2.7 | -<br>-<br>-        |                    | V        |

| Enable Voltage (Turn-off)<br>( $R_{load} = 2 \text{ K}, T_J = -20^{\circ}\text{C}$ ) (Note 3)<br>( $R_{load} = 2 \text{ K}, T_J = 25^{\circ}\text{C}$ )<br>( $R_{load} = 2 \text{ K}, T_J = 100^{\circ}\text{C}$ ) (Note 3)     | V <sub>ENoff</sub>  | -<br>-<br>-        | -<br>-<br>-        | 1.8<br>1.9<br>2.0  | V        |

| Charging Current (Current Sourced into Timing Cap)<br>$(T_J = -20^{\circ}C)$ (Note 3)<br>$(T_J = 25^{\circ}C)$<br>$(T_J = 100^{\circ}C)$ (Note 3)                                                                               | I <sub>Charge</sub> | 67<br>70<br>71     | 80<br>83<br>84     | 90<br>92<br>96     | μΑ       |

| OVERVOLTAGE CLAMP                                                                                                                                                                                                               |                     |                    |                    |                    |          |

| Output Clamping Voltage<br>$(V_{CC} = 18 \text{ V}, T_J = -20^{\circ}\text{C})$ (Note 3)<br>$(V_{CC} = 18 \text{ V}, T_J = 25^{\circ}\text{C})$<br>$(V_{CC} = 18 \text{ V}, T_J = 100^{\circ}\text{C})$ (Note 3)                | V <sub>Clamp</sub>  | 14<br>14<br>13     | 15.5<br>15<br>14.5 | 17<br>16.2<br>16   | V        |

| CURRENT LIMIT                                                                                                                                                                                                                   |                     |                    | •                  |                    |          |

| Short Circuit Current Limit,<br>$(R_{extlLimit} = 56 \Omega, T_J = -20^{\circ}C)$ (Note 3)<br>$(R_{extlLimit} = 56 \Omega, T_J = 25^{\circ}C)$<br>$(R_{extlLimit} = 56 \Omega, T_J = 100^{\circ}C)$ (Note 3)                    | I <sub>Lim-SS</sub> | 2.05<br>2.0<br>1.7 | 2.7<br>2.5<br>2.3  | 3.2<br>3.0<br>2.7  | A        |

| Overload Current Limit, (Note 3)<br>( $R_{extlLimit} = 56 \Omega$ , $T_J = -20^{\circ}C$ )<br>( $R_{extlLimit} = 56 \Omega$ , $T_J = 25^{\circ}C$ )<br>( $R_{extlLimit} = 56 \Omega$ , $T_J = 100^{\circ}C$ )                   | I <sub>Lim–OL</sub> | 3.7<br>3.5<br>3.4  | 4.6<br>4.4<br>4.3  | 5.5<br>5.3<br>5.2  | A        |

| dV/dt CIRCUIT                                                                                                                                                                                                                   |                     |                    |                    |                    |          |

| Slew Rate<br>(C <sub>dV/dt</sub> = 1 μf)                                                                                                                                                                                        | dV/dt               | 0.130              | 0.15               | 0.170              | V/ms     |

| Charging Current (Current Sourced into dV/dt Cap)<br>$(T_J = -20^{\circ}C)$ (Note 3)<br>$(T_J = 25^{\circ}C)$<br>$(T_J = 100^{\circ}C)$ (Note 3)                                                                                | I <sub>dV/dt</sub>  | 67<br>70<br>71     | 80<br>83<br>84     | 90<br>92<br>96     | μΑ       |

| Max Capacitor Voltage                                                                                                                                                                                                           | V <sub>max</sub>    | _                  | -                  | V <sub>CC</sub>    | V        |

| TOTAL DEVICE                                                                                                                                                                                                                    | · · ·               |                    | -                  | -                  | -        |

|                                                                                                                                                                                                                                 |                     |                    | 1                  | 1                  | <b>.</b> |

| Bias Current (Device Operational, Load Open, V <sub>in</sub> = 12 V)                                                                                                                                                            | I <sub>Bias</sub>   | -                  | 1.45               | 2.0                | mA       |

3. Verified by design.

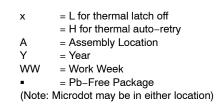

Figure 2. Current Limit Adjustment

Figure 3. Overload vs. Shutdown Time

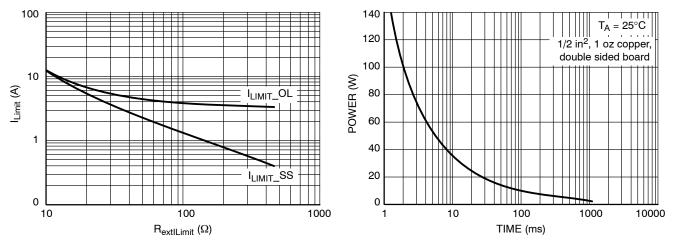

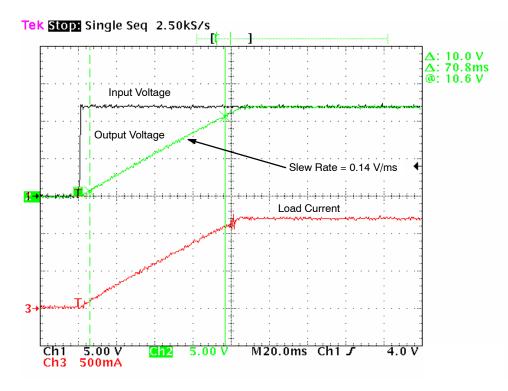

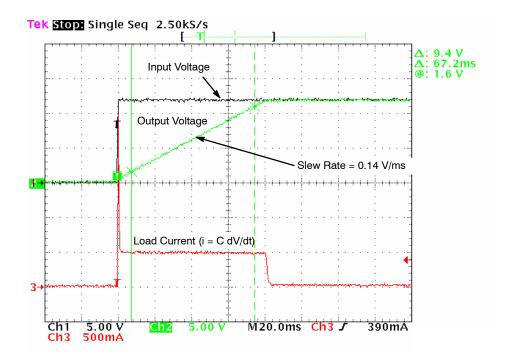

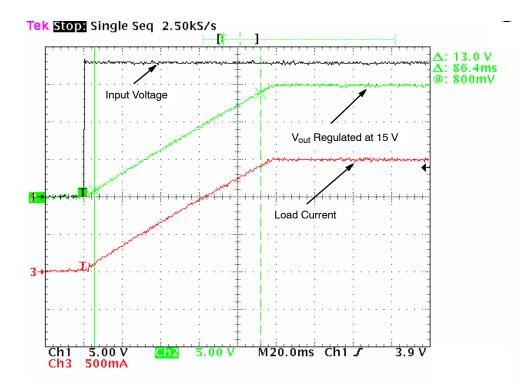

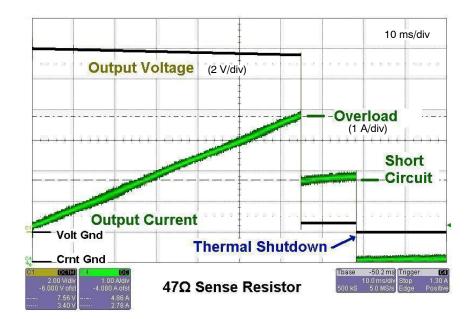

(Typical operating conditions: Vin = 12 V, R\_{ILimit} = 56  $\Omega,$   $C_{dV/dt}$  = 1  $\mu F)$

Figure 4. Typical Application Circuit

Figure 5. Turn–on Waveforms for a Resistive Load of 10  $\Omega$  (C\_{dV/dt} = 1  $\mu f$ )

Figure 6. Turn-on Waveforms for a Load Capacitance of 3,300  $\mu$ f (C<sub>dV/dt</sub> = 1  $\mu$ f)

Figure 7. Turn–on Waveforms for an Overvoltage Condition (10  $\Omega$  Resistive Load)

Figure 8. Current Waveforms for Overload, Short Circuit and Thermal Shutdown

#### DEVICE OPERATION

#### **Basic Operation**

This device is a self-protected, resettable, electronic fuse. It contains circuits to monitor the input voltage, output current, die temperature, turn-on di/dt and turn-on dV/dt, as well as an enable/timer function.

On application of the input voltage, the device will apply the input voltage to the load based on the restrictions of the controlling circuits. The dV/dt of the output voltage can be programmed by the addition of a capacitor to the dV/dt pin, or if left open, the output current will be limited by the internally controlled di/dt.

The device will remain on as long as the temperature does not exceed the  $135^{\circ}$ C limit that is programmed into the chip. The current limit circuit does not shut down the part but will reduce the conductivity of the FET to maintain a constant current as long as it remains at the set level. The input overvoltage clamp also does not shut down the part, but will limit the output voltage to 15 V in the event that the input exceeds that level.

The device can be turned on and off by the enable/timer function, which can also be used to reset the device after a thermal fault if the thermal latch version is chosen.

An internal charge pump provides bias for the gate voltage of the internal N-channel power FET and also for the current limit circuit. The remainder of the control circuitry operates between the input voltage ( $V_{CC}$ ) and ground.

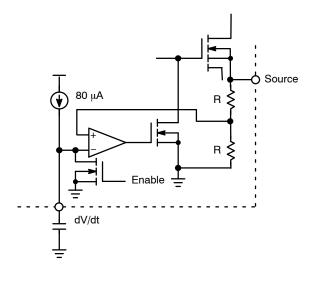

#### dV/dt

This circuit is comprised of an operational amplifier and current source as shown in Figure 9. The enable circuit controls a FET that keeps the slew-rate capacitor discharged any time the device is disabled. When the enable pin is released (low-to-high transition) or when power is applied with the enable pin in a high state, the dV/dt capacitor begins to charge due to the 80  $\mu$ A in the current source. The amplifier controls the output voltage and tracks the voltage on the dV/dt cap scaled by a factor of 2. The output voltage will continue to ramp higher until it reaches the input voltage, or until the 15 V clamp limits it.

The equation for the output slew rate is  $dV/dt = (I/C_{dV/dt}) \times 2$ . Where:

$I - is 80 \ \mu A$  (internal current source)

$C_{dV\!/dt}-is$  the desired dV/dt capacitor value.

The dV/dt ramp begins with a small step of about 200 mV. This step causes a current surge into the output load capacitance which can be seen in Figure 6. The peak level of this surge will be limited to the overload level of the current limit.

Figure 9. dV/dt Circuit

#### **Overvoltage Clamp**

The overvoltage clamp consists of an amplifier and reference. It monitors the output voltage and if the output voltage exceeds 15 V, the gate drive of the main FET is reduced to limit the output. This is intended to allow operation through transients while protecting the load. If an overvoltage condition exists for many seconds, the device may overheat due to the voltage drop across the FET combined with the load current. In this event, the thermal protection circuit would shut down the device.

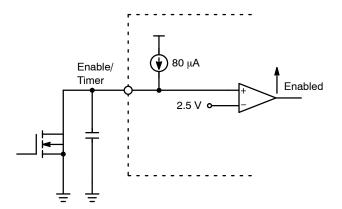

#### Enable/Timer

The enable/timer pin can function either as a direct enable pin, or as a time delay. In the enable mode, an open collector device is connected to this pin. When the device is in its low impedance mode, this pin is low and the operation of the chip is disabled. If a time delay is required, a capacitor is added to this pin.

If a capacitor is added without an open collector device, the turn on will be delayed from the time at which the UVLO voltage is reached. If an open collector device is also used, the delay will start from the time that it goes into its high impedance state. The capacitor is charged by an internal current source of 80  $\mu$ A (typical).

The nominal trip voltage of the comparator is 2.5 V and was designed to be compatible with most logic families. In general, logic gates can be tied directly to this pin, but it is recommended that this be tested.

There is an inherent delay in the turn on of the electronic fuse, due to the method of gate drive used. The gate of the power FET is charged through a high impedance resistor, and from the time that the gate starts charging until the time that it reaches its threshold voltage, there will be no conduction. Once the gate reaches its threshold voltage, the output current will begin a controlled ramp up phase.

This delay will be added to any timing delay due to the enable/timer circuit. Figure 10 shows a simplified diagram of the enable/timer circuit.

Figure 10. Simplified Schematic Diagram of the Enable/Timer Circuit

#### **Thermal Protection Circuit**

The temperature limit circuit senses the temperature of the Power FET and removes the gate drive if the maximum level is exceeded. The NIS5112 device has two different thermal limit versions, auto-retry and latch off.

#### Auto-Retry Version

The device will shut down when the thermal limit threshold is reached ( $T_J = 135^{\circ}C$ , typical) and will not turn back on until the die temperature reduces down to  $95^{\circ}C$  (40°C hysteresis, typical). It will keep auto–retrying until the fault condition is removed or power is turned–off.

#### Latch-Off Version

For the latch–off version, the device will shut down when the thermal limit threshold is reached ( $T_J = 135^{\circ}C$ , typical) and will remain off until power is reset.

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

### STYLES ON PAGE 2

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Document Repository<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SOIC-8 NB   |                                                                                                                                                                                    | PAGE 1 OF 2 |  |  |

| ON Semiconductor and a trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding<br>the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically<br>disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the<br>rights of others. |             |                                                                                                                                                                                    |             |  |  |

© Semiconductor Components Industries, LLC, 2019

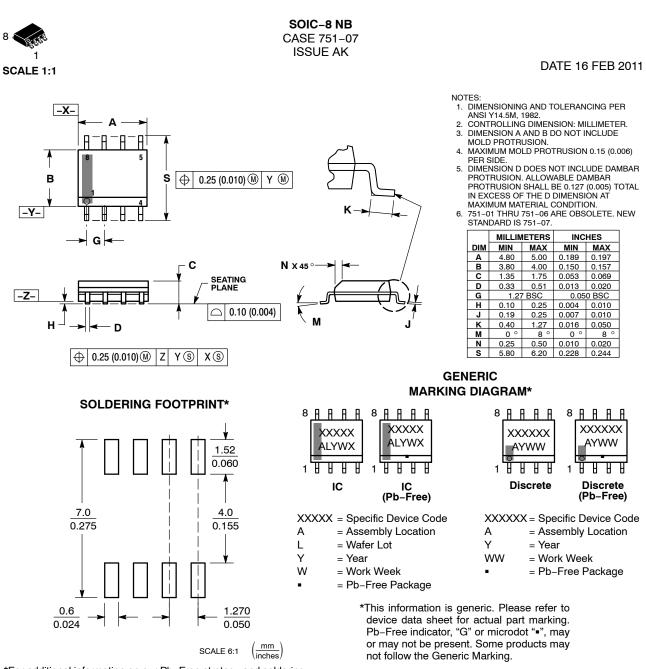

#### SOIC-8 NB CASE 751-07 ISSUE AK

STYLE 1: PIN 1. EMITTER COLLECTOR 2. COLLECTOR 3. 4. EMITTER 5. EMITTER BASE 6. 7 BASE EMITTER 8. STYLE 5: PIN 1. DRAIN 2. DRAIN 3. DRAIN DRAIN 4. GATE 5. 6. GATE SOURCE 7. 8. SOURCE STYLE 9: PIN 1. EMITTER, COMMON COLLECTOR, DIE #1 COLLECTOR, DIE #2 2. З. EMITTER, COMMON 4. 5. EMITTER, COMMON 6 BASE. DIE #2 BASE, DIE #1 7. 8. EMITTER, COMMON STYLE 13: PIN 1. N.C. 2. SOURCE 3 GATE 4. 5. DRAIN 6. DRAIN DRAIN 7. DRAIN 8. STYLE 17: PIN 1. VCC 2. V2OUT V10UT З. TXE 4. 5. RXE 6. VFF 7. GND 8. ACC STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 3 CATHODE 3 CATHODE 4 4. 5. CATHODE 5 6. COMMON ANODE COMMON ANODE 7. 8. CATHODE 6 STYLE 25: PIN 1. VIN 2 N/C REXT З. 4. GND 5. IOUT 6. IOUT IOUT 7. 8. IOUT STYLE 29: BASE, DIE #1 PIN 1. 2 EMITTER, #1 BASE, #2 З. EMITTER, #2 4. 5 COLLECTOR, #2

STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 COLLECTOR, #2 3. 4 COLLECTOR, #2 BASE, #2 5. EMITTER, #2 6. 7 BASE #1 EMITTER, #1 8. STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN SOURCE 4. SOURCE 5. 6. GATE GATE 7. 8. SOURCE STYLE 10: GROUND PIN 1. BIAS 1 OUTPUT 2. З. GROUND 4. 5. GROUND 6 BIAS 2 INPUT 7. 8. GROUND STYLE 14: PIN 1. N-SOURCE 2. N-GATE P-SOURCE 3 P-GATE 4. P-DRAIN 5 6. P-DRAIN N-DRAIN 7. N-DRAIN 8. STYLE 18: PIN 1. ANODE 2. ANODE SOURCE 3. GATE 4. 5. DRAIN 6 DRAIN CATHODE 7. CATHODE 8. STYLE 22 PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC 3 COMMON CATHODE/VCC 4. I/O LINE 3 5. COMMON ANODE/GND 6. I/O LINE 4 7. I/O LINE 5 8. COMMON ANODE/GND STYLE 26: PIN 1. GND 2 dv/dt З. ENABLE 4. ILIMIT 5. SOURCE SOURCE 6. SOURCE 7. 8. VCC STYLE 30: DRAIN 1 PIN 1. DRAIN 1 2 GATE 2 З. SOURCE 2 4. SOURCE 1/DRAIN 2 SOURCE 1/DRAIN 2 5. 6.

STYLE 3: PIN 1. DRAIN, DIE #1 DRAIN, #1 2. DRAIN, #2 З. 4. DRAIN, #2 GATE, #2 5. SOURCE, #2 6. 7 GATE #1 8. SOURCE, #1 STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS THIRD STAGE SOURCE GROUND З. 4. 5. DRAIN 6. GATE 3 SECOND STAGE Vd 7. FIRST STAGE Vd 8. STYLE 11: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. 3. GATE 2 4. 5. DRAIN 2 6. DRAIN 2 DRAIN 1 7. 8. DRAIN 1 STYLE 15: PIN 1. ANODE 1 2. ANODE 1 ANODE 1 3 ANODE 1 4. 5. CATHODE, COMMON CATHODE, COMMON CATHODE, COMMON 6. 7. CATHODE, COMMON 8. STYLE 19: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. 3. GATE 2 4. 5. DRAIN 2 6. MIRROR 2 7. DRAIN 1 8. **MIRROR 1** STYLE 23: PIN 1. LINE 1 IN COMMON ANODE/GND COMMON ANODE/GND 2. 3 LINE 2 IN 4. LINE 2 OUT 5. COMMON ANODE/GND COMMON ANODE/GND 6. 7. LINE 1 OUT 8. STYLE 27: PIN 1. ILIMIT 2 OVI 0 UVLO З. 4. INPUT+ 5. SOURCE SOURCE 6. SOURCE 7. 8 DRAIN

#### DATE 16 FEB 2011

STYLE 4: PIN 1. 2. ANODE ANODE ANODE З. 4. ANODE ANODE 5. 6. ANODE 7 ANODE COMMON CATHODE 8. STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 BASE, #2 З. COLLECTOR, #2 4. COLLECTOR, #2 5. 6. EMITTER, #2 EMITTER, #1 7. 8. COLLECTOR, #1 STYLE 12: PIN 1. SOURCE SOURCE 2. 3. GATE 4. 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 16: PIN 1. EMITTER, DIE #1 2. BASE, DIE #1 EMITTER, DIE #2 3 BASE, DIE #2 4. 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 COLLECTOR, DIE #1 7. COLLECTOR, DIE #1 8. STYLE 20: PIN 1. SOURCE (N) GATE (N) SOURCE (P) 2. 3. 4. GATE (P) 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 24: PIN 1. BASE 2. EMITTER 3 COLLECTOR/ANODE COLLECTOR/ANODE 4. 5. CATHODE 6. CATHODE COLLECTOR/ANODE 7. 8. COLLECTOR/ANODE STYLE 28: PIN 1. SW\_TO\_GND 2. DASIC OFF DASIC\_SW\_DET З. 4. GND 5. 6. V MON VBULK 7. VBULK 8 VIN

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | : SOIC-8 NB |                                                                                                                                                                                     | PAGE 2 OF 2 |  |  |

| ON Semiconductor and ()) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding<br>the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically<br>disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the |             |                                                                                                                                                                                     |             |  |  |

SOURCE 1/DRAIN 2

7.

8. GATE 1

COLLECTOR, #2

COLLECTOR, #1

COLLECTOR, #1

6.

7.

8

rights of others

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and calcular performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

#### TECHNICAL SUPPORT

onsemi Website: www.onsemi.com

Email Requests to: orderlit@onsemi.com

North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Onsemi: NIS5112D1R2G NIS5112D2R2G