# 2.5 V/3.3 V 1:5 LVPECL Fanout Buffer

# NB3L853141

#### Description

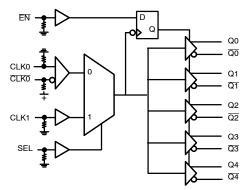

The NB3L853141 is a low skew 1:5 LVPECL Clock fanout buffer designed explicitly for low output skew applications.

The NB3L853141 features a multiplexed input which can be driven by either a differential or single–ended input to allow for the distribution of a lower speed clock along with the high speed system clock.

The SEL pin will select the differential clock inputs, CLK0 &  $\overline{\text{CLK0}}$ , when LOW (or left open and pulled LOW by the internal pull-down resistor). When SEL is HIGH, the single-ended CLK1 input is selected.

The common enable  $(\overline{\text{EN}})$  is synchronous so that the outputs will only be enabled/disabled when they are already in the LOW state. This avoids any chance of generating a runt clock pulse when the device is enabled/disabled as can happen with an asynchronous control. The internal flip flop is clocked on the falling edge of the input clock, therefore, all associated specification limits are referenced to the negative edge of the clock input.

#### Features

- 700 MHz Maximum Clock Output Frequency

- CLK0 and CLK0 can Accept Differential LVPECL, LVDS, HCSL, LVHSTL, SSTL, LVCMOS

- CLK1 can Accept LVCMOS and LVTTL

- Five Differential LVPECL Clock Outputs

- 1.5 ns Maximum Propagation Delay

- Operating Range:  $V_{CC} = 2.375$  V to 3.8 V

- LVCMOS Compatible Control Inputs

- Selectable Differential or LVCMOS Clock Inputs

- Synchronous Clock Enable

- 30 ps Max. Skew Between Outputs

- -40°C to +85°C Ambient Operating Temperature Range

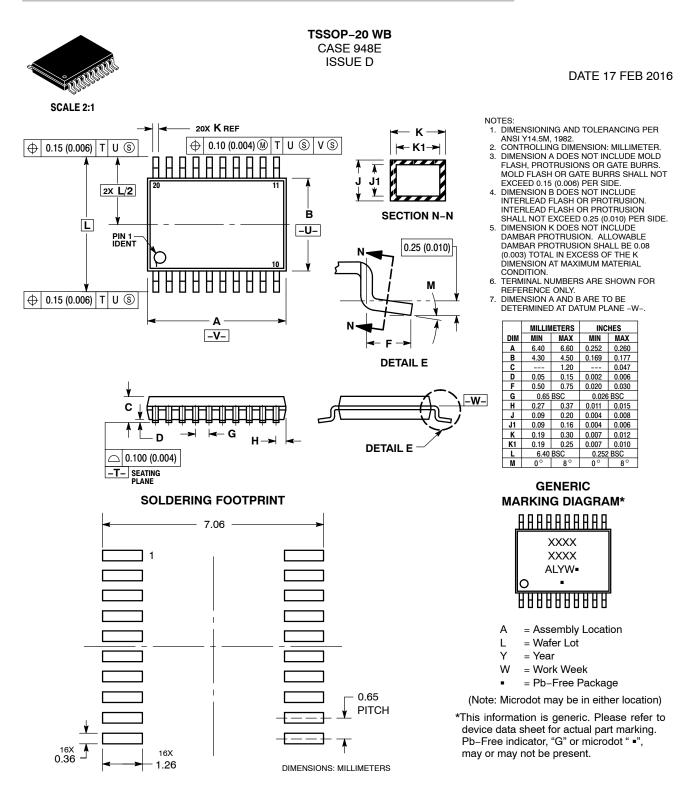

- TSSOP-20 Package

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

#### Applications

- Computing and Telecom

- Routers, Servers and Switches

- Backplanes

## **ON Semiconductor®**

www.onsemi.com

Figure 1. Simplified Logic Diagram of NB3L853141

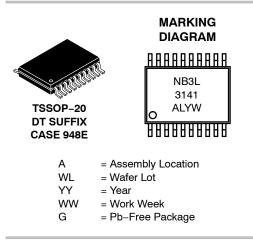

#### **ORDERING INFORMATION**

| Device          | Package               | Shipping <sup>†</sup> |

|-----------------|-----------------------|-----------------------|

| NB3L853141DTR2G | TSSOP-20<br>(Pb-Free) | 2500 / Tape<br>& Reel |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, <u>BRD8011/D</u>.

| V <sub>CC</sub> EN V <sub>CC</sub> NC CLK1 CLK0 CLK0 NC SEL V <sub>EE</sub> |

|-----------------------------------------------------------------------------|

|                                                                             |

|                                                                             |

|                                                                             |

| 1 2 3 4 5 6 7 8 9 10                                                        |

| Q0 <u>Q0</u> Q1 <u>Q1</u> Q2 <u>Q2</u> Q3 <u>Q3</u> Q4 <u>Q4</u>            |

Note: All  $V_{CC}$  and  $V_{EE}$  pins must be externally connected to Power Supply to guarantee proper operation.

#### Figure 1. Pinout (Top View) and Logic Diagram

#### Table 2. PIN DESCRIPTION

### Table 1. FUNCTION TABLE

| CLK0             | CLK1             | SEL             | EN | Q            |

|------------------|------------------|-----------------|----|--------------|

| L<br>H<br>X<br>X | X<br>L<br>H<br>X | L<br>L<br>H H X |    | <b>デェーエー</b> |

\*On next negative transition of CLK0 or CLK1 X = Don't Care

| Pin Number | Name      | I/O                     | Open<br>Default | Description                                                                                                                         |

|------------|-----------|-------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 1          | Q0        | LVPECL Output           |                 | Non-Inverted Differential Clock Output                                                                                              |

| 2          | <u>Q0</u> | LVPECL Output           |                 | Inverted Differential Clock Output                                                                                                  |

| 3          | Q1        | LVPECL Output           |                 | Non-Inverted Differential Clock Output                                                                                              |

| 4          | <u>Q1</u> | LVPECL Output           |                 | Inverted Differential Clock Output                                                                                                  |

| 5          | Q2        | LVPECL Output           |                 | Non-Inverted Differential Clock Output                                                                                              |

| 6          | <u>Q2</u> | LVPECL Output           |                 | Inverted Differential Clock Output                                                                                                  |

| 7          | Q3        | LVPECL Output           |                 | Non-Inverted Differential Clock Output                                                                                              |

| 8          | <u>Q3</u> | LVPECL Output           |                 | Inverted Differential Clock Output                                                                                                  |

| 9          | Q4        | LVPECL Output           |                 | Non-Inverted Differential Clock Output                                                                                              |

| 10         | Q4        | LVPECL Output           |                 | Inverted Differential Clock Output                                                                                                  |

| 11         | VEE       | Power                   |                 | Negative Supply Voltage                                                                                                             |

| 12         | SEL       | LVCMOS / LVTTL<br>Input | Low             | Clock Select Input. When HIGH, selects CLK1 input. When LOW, selects CLK0, CLK0 inputs. Internal Pull-down Resistor.                |

| 13         | NC        |                         |                 | No Connect                                                                                                                          |

| 14         | CLK0      | Multi-Level Input       | High            | Inverted Differential Clock Input. Internal Pull-up Resistor.                                                                       |

| 15         | CLK0      | Multi-Level Input       | Low             | Non-Inverted Differential Clock Input. Internal Pull-down Resistor.                                                                 |

| 16         | CLK1      | LVCMOS/LVTTL<br>Input   | Low             | Single-ended Clock Input. Internal Pull-down Resistor.                                                                              |

| 17         | NC        |                         |                 | No Connect                                                                                                                          |

| 18         | VCC       | Power                   |                 | Positive Supply Voltage                                                                                                             |

| 19         | EN        | LVCMOS/LVTTL<br>Input   | Low             | Synchronous Clock Enable Input. When Low, outputs are enabled.<br>When High, outputs are disabled Low. Internal Pull-down Resistor. |

| 20         | VCC       | Power                   |                 | Positive Supply Voltage                                                                                                             |

All VCC and VEE pins must be externally connected to a power supply to guarantee proper operation. Bypass each supply pin with 0.01  $\mu F$  to GND.

#### Table 3. ATTRIBUTES (Note 1)

| Characteristics                                        | Value                     |

|--------------------------------------------------------|---------------------------|

| ESD Protection<br>Human Body Model<br>Machine Model    | > 2 kV<br>> 200 V         |

| R <sub>PU</sub> – Pull–up Resistor                     | 50 kΩ                     |

| R <sub>PD</sub> – Pull–down Resistor                   | 50 kΩ                     |

| Moisture Sensitivity (Note 1)<br>TSSOP-20              | Level 1                   |

| Flammability Rating<br>Oxygen Index: 28 to 34          | UL*94 code V*0 @ 0.125 in |

| Transistor Count                                       | 300                       |

| Meets or exceeds JEDEC Spec EIA/JESD78 IC Latchup Test | •                         |

1. For additional information, see Application Note AND8003/D.

#### Table 4. MAXIMUM RATINGS

| Symbol               | Parameter                                | Condition 1            | Condition 2          | Rating                        | Unit     |

|----------------------|------------------------------------------|------------------------|----------------------|-------------------------------|----------|

| V <sub>CC</sub>      | LVPECL Mode Power Supply                 | V <sub>EE</sub> = 0 V  |                      | 4.6                           | V        |

| VI                   | LVPECL Mode Input Voltage                | V <sub>EE</sub> = 0 V  | $V_I \leq V_{CC}$    | –0.5 to V <sub>CC</sub> + 0.5 | V        |

| l <sub>out</sub>     | Output Current                           | Continuous<br>Surge    |                      | 50<br>100                     | mA<br>mA |

| T <sub>A</sub>       | Operating Temperature Range              |                        |                      | -40 to +85                    | °C       |

| T <sub>stg</sub>     | Storage Temperature Range                |                        |                      | -65 to +150                   | °C       |

| $\theta_{JA}$        | Thermal Resistance (Junction-to-Ambient) | 0 lfpm<br>500 lfpm     | TSSOP-20<br>TSSOP-20 | 140<br>50                     | °C/W     |

| $\theta_{\text{JC}}$ | Thermal Resistance (Junction-to-Case)    | Standard Board         | TSSOP-20             | 23 to 41                      | °C/W     |

| T <sub>sol</sub>     | Wave Solder                              | <2 to 3 sec @<br>260°C |                      | 265                           | °C       |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

| Symbol             | Characteristic                                          | Min                  | Тур | Max                   | Unit |

|--------------------|---------------------------------------------------------|----------------------|-----|-----------------------|------|

| POWER SI           | JPPLY                                                   |                      |     |                       | -    |

| V <sub>CC</sub>    | Power Supply Voltage                                    | 2.375                |     | 3.8                   | V    |

| I <sub>EE</sub>    | Power Supply Current (Outputs Open)                     |                      | 40  | 55                    | mA   |

| LVPECL O           | UTPUTS (Note 3)                                         |                      |     |                       | -    |

| V <sub>OH</sub>    | Output HIGH Voltage                                     | V <sub>CC</sub> -1.4 |     | V <sub>CC</sub> -0.9  | V    |

| V <sub>OL</sub>    | Output LOW Voltage                                      | V <sub>CC</sub> -2.0 |     | V <sub>CC</sub> -1.7  | V    |

| V <sub>SWING</sub> | Output Voltage Swing, Peak-to-Peak                      | 0.6                  |     | 1.0                   | V    |

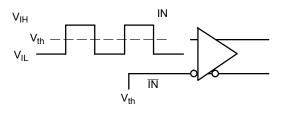

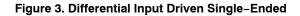

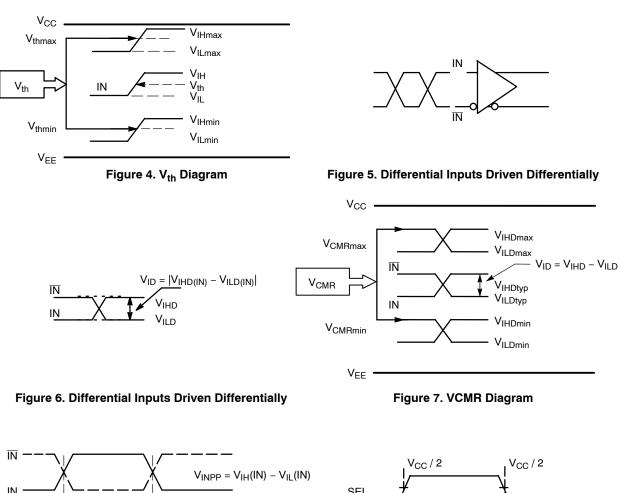

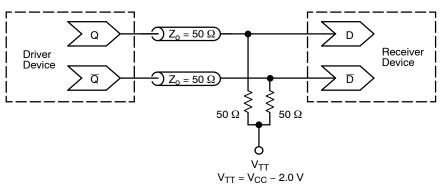

| DIFFEREN           | TIAL INPUTS DRIVEN SINGLE-ENDED (Note 4) (Figures 3 and | 4)                   |     |                       | -    |

| VIH                | Single-ended Input HIGH Voltage                         | 0.5                  |     | V <sub>CC</sub> +0.3  | V    |

| V <sub>IL</sub>    | Single-ended Input LOW Voltage                          | -0.3                 |     | V <sub>CC</sub> -1.0  | V    |

| V <sub>th</sub>    | Input Threshold Reference Voltage Range (Note 5)        | 0.35                 |     | V <sub>CC</sub> -0.85 | V    |

| V <sub>ISE</sub>   | Single-ended Input Voltage (VIH - VIL)                  | 0.3                  |     | V <sub>CC</sub>       | V    |

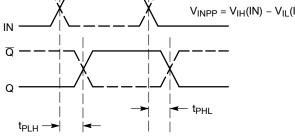

| DIFFEREN           | TIAL INPUTS DRIVEN DIFFERENTIALLY (see Figures 5 and 6) | (Note 6)             |     |                       |      |

| V <sub>IHD</sub>   | Differential Input HIGH Voltage                         | 0.5                  |     | V <sub>CC</sub> -0.85 | mV   |

| VIIID              | Differential Input LOW Voltage                          | 0                    |     | V <sub>IHD</sub> -150 | mV   |

| V <sub>ILD</sub> | Differential Input LOW Voltage                                    |                                                                   | 0          | V <sub>IHD</sub> -150 | mV |

|------------------|-------------------------------------------------------------------|-------------------------------------------------------------------|------------|-----------------------|----|

| V <sub>ID</sub>  | Differential Input Voltage (V <sub>IHD</sub> – V <sub>ILD</sub> ) |                                                                   | 0.15       | 1.3                   | V  |

| V <sub>CMR</sub> | Common Mode Input Voltage; (Note 7)                               |                                                                   | 0.5        | V <sub>CC</sub> -0.85 |    |

| I <sub>IH</sub>  | Input HIGH Current                                                | $V_{CC} = V_{IN} = 3.8 \text{ V} \frac{\text{CLK0}}{\text{CLK0}}$ |            | 150<br>5              | μΑ |

| Ι <sub>ΙL</sub>  | Input LOW Current                                                 | $V_{CC}$ = 3.8V, $V_{IN}$ = 0 V $\frac{CLK0}{CLK0}$               | -5<br>-150 |                       | μΑ |

SINGLE-ENDED INPUTS (SEL, EN, CLK1)

| V <sub>IH</sub> | Input HIGH Voltage                               | SEL, <del>EN</del><br>CLK1 | 2.0<br>2.0   | V <sub>CC</sub> +0.3<br>V <sub>CC</sub> +0.3 | V  |

|-----------------|--------------------------------------------------|----------------------------|--------------|----------------------------------------------|----|

| V <sub>IL</sub> | Input LOW Voltage                                | SEL, <del>EN</del><br>CLK1 | -0.3<br>-0.3 | 0.8<br>V <sub>CC</sub> x0.35                 | V  |

| IIH             | Input HIGH Current VCC = V <sub>IN</sub> = 3.8 V | CLK1, SEL, EN              |              | 150                                          | μΑ |

| ۱ <sub>IL</sub> | CLK1, SEL, EN                                    | CLK1, SEL, EN              | -5           |                                              | μΑ |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm.

2. Input and Output parameters vary 1:1 with V<sub>CC</sub>. 3. LVPECL outputs loaded with 50  $\Omega$  to V<sub>CC</sub> – 2 V for proper operation. 4. V<sub>th</sub>, V<sub>IL</sub>, and V<sub>ISE</sub> parameters must be complied with simultaneously. 5. V<sub>th</sub> is applied to the complementary input when operating in single–ended mode.

6.  $V_{IHD}$ ,  $V_{ILD}$ ,  $V_{ID}$  and  $V_{CMR}$  parameters must be complied with simultaneously. 7. The common mode voltage is defined as  $V_{IH}$ .

| Symbol                                 | Characteristic                                                                                 |                                                                            |                                                                      | Min        | Тур                                                                          | Max        | Unit       |

|----------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------|------------|------------------------------------------------------------------------------|------------|------------|

| f <sub>MAX</sub>                       | Maximum Input Clock Frequency: $V_{OUTpp} \ge 400 \text{ mV}$                                  | 400 mV CLK0/CLK0, V <sub>INPPmin</sub> ≥ 250 mV<br>CLK1                    |                                                                      |            |                                                                              |            | MHz        |

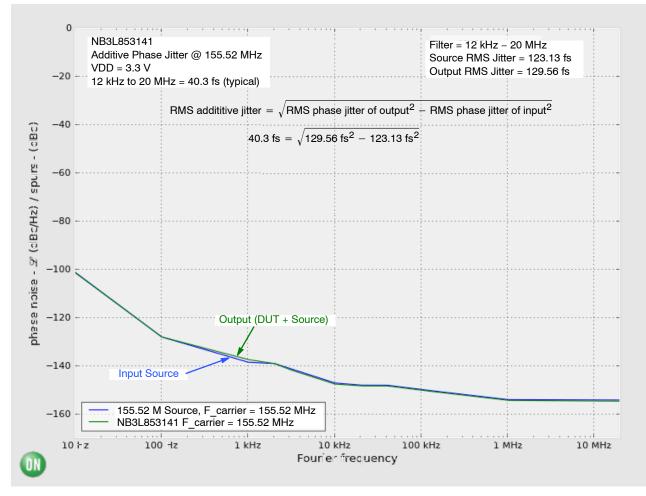

| $\Phi_{\sf N}$                         | Phase Noise, f <sub>C</sub> = 155.52 MHz                                                       | 10 Hz<br>100 Hz<br>1 kHz<br>10 kHz<br>100 kHz<br>1 MHz<br>10 MHz<br>20 MHz | Offset from Carrier                                                  |            | -100.5<br>-128.2<br>-138.6<br>-147.1<br>-149.7<br>-154.2<br>-154.2<br>-154.2 |            | dBc/<br>Hz |

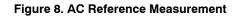

| t <sub>PLH</sub> ,<br>t <sub>PHL</sub> | Propagation Delay to Differential Outputs, @ 50 MHz                                            | Note 9<br>Note 10                                                          | CLK0/CLK0 to Q/Q<br>CLK1 to Q                                        | 0.8<br>0.8 | 1.0<br>1.0                                                                   | 1.5<br>1.5 | ns         |

| t∫⊕N                                   | Additive Phase Jitter, RMS; f <sub>C</sub> = 155.52 MHz,<br>Integration Range: 12 kHz – 20 MHz |                                                                            |                                                                      |            | 0.05                                                                         |            | ps         |

| tsk(o)                                 | Output-to-output skew; (Note 11)                                                               |                                                                            |                                                                      |            |                                                                              | 30         | ps         |

| tsk (pp)                               | Part-to-Part Skew; (Note 12)                                                                   |                                                                            |                                                                      |            |                                                                              | 150        | ps         |

| V <sub>INpp</sub>                      | Input Voltage Swing/Sensitivity (Differential Configuration) (Note 14)                         |                                                                            |                                                                      |            |                                                                              | 1300       | mV         |

| t <sub>r</sub> /t <sub>f</sub>         | Output rise and fall times, 20% to 80%,                                                        |                                                                            | Q, <u>Q</u>                                                          | 200        |                                                                              | 700        | ps         |

| ODC                                    | Output Clock Duty Cycle CLK0/CLK0<br>Input Duty Cycle = 50%                                    | ס, f ≤ 700 MI                                                              | Hz, $V_{INPPmin} \ge 250 \text{ mV}$<br>CLK1, f $\le 250 \text{MHz}$ | 45<br>45   |                                                                              | 55<br>55   | %          |

All parameters measured at  $f_{MAX}$  unless noted otherwise. The cycle–to–cycle jitter on the input will equal the jitter on the

output. The part does not add jitter

8. Measured using a V<sub>INPPmin</sub> source, Reference Duty Cycle = 50% duty cycle clock source. All output loading with external 50  $\Omega$  to V<sub>CC</sub> - 2 V. 9. Measured from the differential input crossing point to the differential output crossing point.

10. Measured from  $V_{CC}$  /2 input crossing point to the differential output crossing point. 11. Defined as skew between outputs at the same supply voltage and with equal load conditions. Measured at the output differential cross points.

12. Defined as skew between outputs on different devices operating at the same supply voltages and with equal load conditions. Using the same type of inputs on each device, the outputs are measured at the differential cross points.13. Output voltage swing is a single–ended measurement operating in differential mode.

14. Input voltage swing is a single-ended measurement operating in differential mode.

Figure 2. Typical Phase Noise Plot at f<sub>carrier</sub> = 155.52 MHz at an Operating Voltage of 3.3 V, Room Temperature

The above phase noise data was captured using Agilent E5052A/B. The data displays the input phase noise and output phase noise used to calculate the additive phase jitter at a specified integration range. The RMS Phase Jitter contributed by the device (integrated between 12 kHz and 20 MHz) is 40.3 fs.

The additive phase jitter performance of the fanout buffer is highly dependent on the phase noise of the input source.

To obtain the most accurate additive phase noise measurement, it is vital that the source phase noise be notably lower than that of the DUT. If the phase noise of the source is greater than the device under test output, the source noise will dominate the additive phase jitter calculation and lead to an artificially low result for the additive phase noise measurement within the integration range. The Figure above is a good example of the NB3L853141 source generator phase noise having a significantly higher floor such that the DUT output results in an additive phase jitter of 40.3 fs.

RMS addititive jitter =

$$\sqrt{\text{RMS phase jitter of output}^2 - \text{RMS phase jitter of input}^2}$$

40.3 fs =  $\sqrt{129.56 \text{ fs}^2 - 123.13 \text{ fs}^2}$

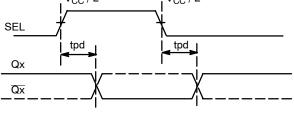

Figure 9. SEL to Qx Timing Diagram

Figure 10. Typical Termination for Output Driver and Device Evaluation (See Application Note <u>AND8020/D</u> – Termination of ECL Logic Devices.)

| DOCUMENT NUMBER: | 98ASH70169A | Electronic versions are uncontrolled except when accessed directly from the Document Repository<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |  |  |  |

|------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| DESCRIPTION:     | TSSOP-20 WB | PAGE 1 OF                                                                                                                                                                          |  |  |  |  |

|                  |             |                                                                                                                                                                                    |  |  |  |  |

ON Semiconductor and use trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the right or others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and calcular performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

#### TECHNICAL SUPPORT

onsemi Website: www.onsemi.com

Email Requests to: orderlit@onsemi.com

North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

onsemi: NB3L853141DTG NB3L853141DTR2G