### Is Now Part of

# ON Semiconductor®

# To learn more about ON Semiconductor, please visit our website at www.onsemi.com

Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to Fairchild <a href="general-regarding-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-numbers-n

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officer

# FUSB300C Programmable USB Type-C Controller

#### **Features**

- Type-C Detection of Attach and Orientation

- Flexible Multi-Platform Support through I<sup>2</sup>C Programmability

- Supports:

- Dual Role Port (DRP)

- Downstream Facing Port (DFP)

- Upstream Facing Port (UFP)

- Accessory Modes

- Alternate Interfaces

### **Applications**

- Smartphones

- Tablets

- Laptops

- Wearables

### **Description**

The FUSB300C is a flexible, thin client solution for USB Type-C control. This product is a generic hardware solution that targets system designers looking to implement a DRP/DFP/UFP USB Type-C connector while providing the software flexibility for multiple platform support.

The FUSB300C performs USB Type-C detection including attach and orientation. TheFUSB300C automates VBUS threshold detection as well as the various charging current levels. The FUSB300C also includes an integrated VCONN power switch.

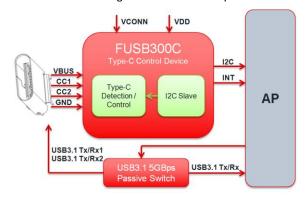

Figure 1. Block Diagram

### **Ordering Information**

| Part Number | Operating<br>Temperature Range | Package                                                                             | Packing<br>Method |

|-------------|--------------------------------|-------------------------------------------------------------------------------------|-------------------|

| FUSB300CUCX | -40 to 85°C                    | 9-Ball Wafer-Level Chip Scale Package (WLCSP), 1.215 x 1.215 x 0.6 mm, 0.4 mm Pitch | Tape and Reel     |

Figure 2. Typical Application

# **Block Diagram**

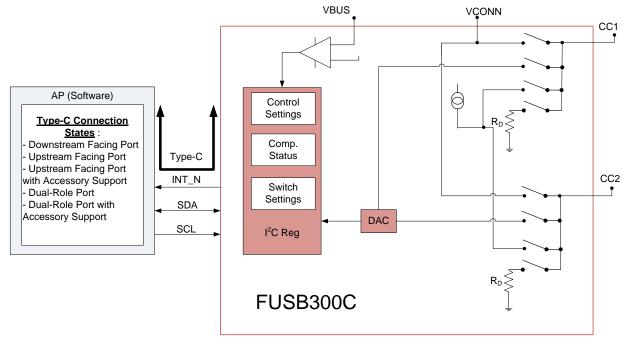

Figure 3. Functional Block Diagram

# **Pin Configuration**

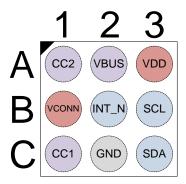

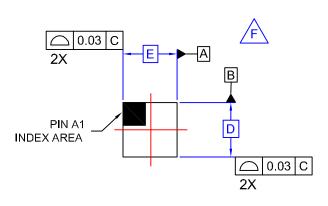

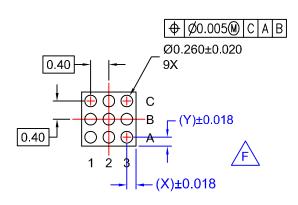

Figure 4. Pin Assignment (Top Through View)

# Pin Map

|       | Column 1 | Column 2 | Column 3 |

|-------|----------|----------|----------|

| Row A | CC2      | VBUS     | VDD      |

| Row B | VCONN    | INT_N    | SCL      |

| Row C | CC1      | GND      | SDA      |

# **Pin Descriptions**

| Name            | Туре                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB Type-C Co   | nnector Interfac     | ce                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CC1/CC2         | I/O                  | Type-C connector Configuration Channel (CC) pins. Initially used to determine when an attach has occurred and what the orientation of the insertion is.  Functionality after attach depends on mode of operation detected.  Operating as a host:  • Sets the allowable charging current for VBUS to be sensed by the attached device  • Used to detect when a detach has occurred  Operating as a device:  • Indicates what the allowable sink current is from the attached host. |

| GND             | Ground               | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| VBUS            | Input                | VBUS input pin for attach and detach detection when operating as an upstream facing port (Device).                                                                                                                                                                                                                                                                                                                                                                                |

| Power Interfac  | e                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VDD             | Power                | Input supply voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VCONN           | Power Switch         | Regulated input to be switched to correct CC pin as VCONN to power USB3.1 full-featured cables and other accessories                                                                                                                                                                                                                                                                                                                                                              |

| Signal Interfac | e                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SCL             | Input                | I <sup>2</sup> C serial clock signal to be connected to the phone-based I <sup>2</sup> C master.                                                                                                                                                                                                                                                                                                                                                                                  |

| SDA             | Open-Drain<br>I/O    | I <sup>2</sup> C serial data signal to be connected to the phone-based I <sup>2</sup> C master                                                                                                                                                                                                                                                                                                                                                                                    |

| INT_N           | Open-Drain<br>Output | Active LOW open drain interrupt output used to prompt the phone baseband processor to read the I <sup>2</sup> C register bits.                                                                                                                                                                                                                                                                                                                                                    |

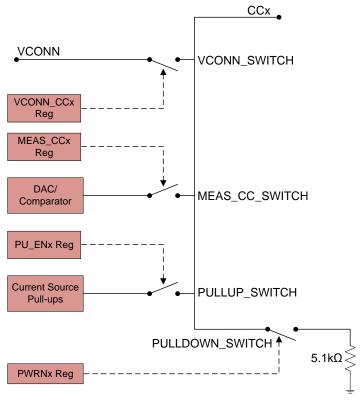

### **Configuration Channel Switch**

The FUSB300C integrates the control and detection functionality required to implement a USB Type-C host, device or dual-role port including:

- Device Port Pull-Down(R<sub>D</sub>)

- Host Port Pull-Up (I<sub>P</sub>)

- VCONN Power Switch for Full-Featured USB3.1 Cables

- Configuration Channel (CC) Threshold Comparators.

Each CC pin contains a flexible switch matrix that allows the host software to control what type of Type-C port is implemented. The switches are shown in Figure 5.

Figure 5. Configuration Channel Switch Functionality

### **Type-C Detection**

The FUSB300C implements multiple comparators and a programmable DAC that can be used by software to determine the state of the CC and VBUS pins. This status information provides the software all the information required to determine attach, detach and charging current capabilities based on the specific Type-C port to which the FUSB300C has been configured.

The FUSB300C has three fixed threshold comparators that match the USB Type-C specification for the three charging current levels that can be detected by a Type-C device. These comparators automatically cause a BC\_LVL interrupt to occur when there is a change of state. In addition to the fixed threshold comparators, the host software can use the 6-bit DAC to determine the state of the CC lines more accurately.

The FUSB300C also has a fixed comparator that monitors if VBUS has reached a valid threshold or not. The DAC can be used to measure VBUS up to 15 V which allows the software to confirm that changes to the VBUS line have occurred as expected based on various communication methods to change the charging level.

### **Initial Attach Detection**

The FUSB300C implements the Type-C Disabled state which removes all termination from the CC pins. In this state, the FUSB300C monitors the CC pins for any activity which indicates that either a host or a device is attempting to attach. When the FUSB300C detects this activity, it interrupts the host software through the WAKE interrupt. The host software can then enable the desired termination based on the required port type and validate the attach per the Type-C specification.

### **Device Detection and Configuration**

A Type-C device must monitor VBUS to determine if it is attached or detached. The FUSB300C provides this information through the VBUSOK interrupt. After the Type-C device knows that a Type-C host has been attached, it needs to determine what type of termination is applied to each CC pin. The software determines if a Ra or Rd termination is present based on the BC\_LVL and COMP interrupt and status bits.

Additionally, for Rd terminations, the software can further determine what charging current is allowed by

the Type-C host by reading the BC\_LVL status bits. This is summarized in Table 1.

Table 1. Device Interrupt Summary

|              |             | Interru | upt Status             |        |                             |

|--------------|-------------|---------|------------------------|--------|-----------------------------|

| Status Type  | BC_LVL[1:0] | СОМР    | COMP Setting           | VBUSOK | Meaning                     |

|              | 2'b00       | NA      | NA                     | 1      | vRA                         |

|              | 2'b01       | NA      | NA                     | 1      | vRd-Connect and vRd-USB     |

|              | 2'b10       | NA      | NA                     | 1      | vRd-Connect and vRd-1.5     |

| CC Detection | 2'b11       | 0       | 6'b11_0000<br>(2.05 V) | 1      | vRd-Connect and vRd-3.0     |

| Attach       | NA          | NA      | NA                     | 1      | Host Attached, VBUS Valid   |

| Detach       | NA          | NA      | NA                     | 0      | Host Detached, VBUS Invalid |

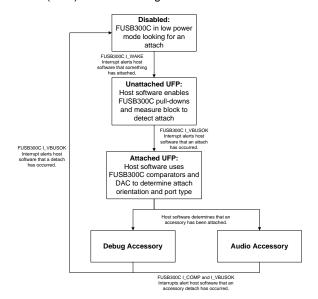

The high level software flow diagram for a Type-C device (UFP) is shown in Figure 6.

Figure 6. UFP Software Flow

### **Host Detection and Configuration**

When the FUSB300C is configured as a Type-C host, the software can use the status of the comparators and DAC to determine when a Type-C device has been attached or detached and what termination type has been attached to each CC pin.

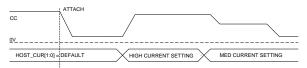

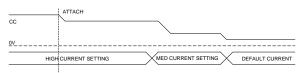

The FUSB300C allows the host software to change the charging current capabilities of the port through the HOST\_CUR control bits. If the HOST\_CUR bits are changed prior to attach, the FUSB300C will automatically indicate the programmed current capability when a device is attached. If the current capabilities are changed after a device is attached, the FUSB300C will immediately change the CC line to the programmed capability.

Figure 7. HOST\_CUR Changed After Attach

Figure 8. HOST\_CUR Changed Prior To Attach

The Type-C specification outlines different attach and detach thresholds for a Type-C host that are based on how much current is supplied to each CC pin. Based on the programmed HOST\_CUR setting, the software adjusts the DAC comparator threshold to match the Type-C specification requirements. The BC\_LVL comparators can also be used as part of the Ra detection flow. This is summarized in Table 2.

Table 2. Host Interrupt Summary

|             |               | Interrupt Status |      |                    |               |

|-------------|---------------|------------------|------|--------------------|---------------|

| Termination | HOST_CUR[1:0] | BC_LVL[1:0]      | COMP | COMP Setting       | Attach/Detach |

|             | 2'b01         | 2'b00            | NA   | NA                 |               |

|             | 2'b10         | 2'b01            | 0    | 6'b00_1000 (0.4 V) |               |

| Ra          | 2'b11         | 2'b10            | 0    | 6'b01_0010 (0.8 V) | NA            |

|             |               | NA               | 0    | 6'b10_0100 (1.6 V) | Attach        |

|             | 2'b01, 2'b10  | NA               | 1    | 6'b10_0100 (1.6 V) | Detach        |

|             |               | NA               | 0    | 6'b11_1101 (2.6 V) | Attach        |

| Rd          | 2'b11         | NA               | 1    | 6'b11_1101 (2.6 V) | Detach        |

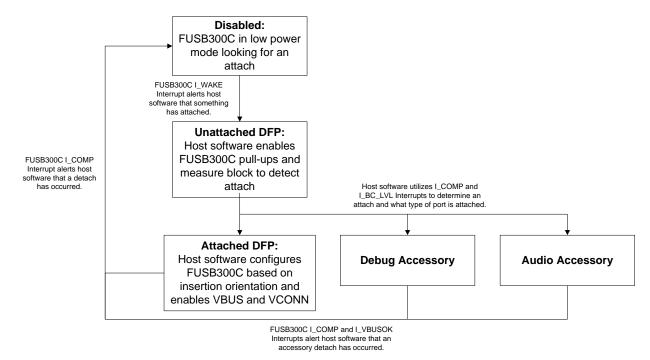

The high level software flow diagram for a Type-C Host (DFP) is shown below in Figure 9.

Figure 9. DFP Software Flow

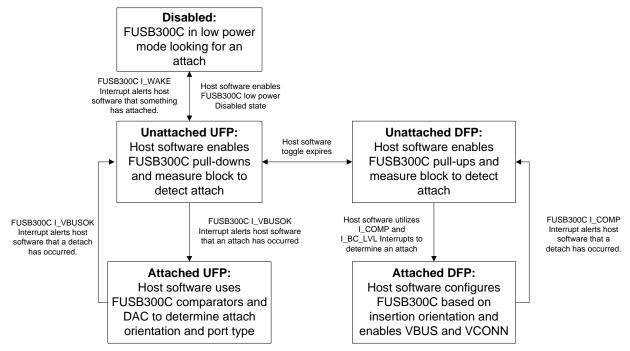

### **Dual-Role Detection and Configuration**

The Type-C specification allows ports to be both a device, or a host depending on what type of port has attached. This functionality is similar to USB OTG ports with the current USB connectors and is called a dual-

role port. The FUSB300C can be used to implement a dual-role port. A Type-C dual role port toggles between presenting as a Type-C device and a Type-C host. The host software controls the toggle time and configuration of the FUSB300C in each state as shown in Figure 10.

Figure 10. DRP Software Flow

### **Power Level Determination**

The Type-C specification outlines the order of precedence for power level determination which covers power levels from basic USB2.0 levels to the highest levels of USB PD. The host software is expected to follow the USB Type-C specification for charging current priority based on feedback from the FUSB300C detection, external BC1.2 detection and any USB Power Delivery communication.

The FUSB300C does not integrate BC1.2 charger detection which is assumed available in the USB transceiver or USB charger in the system.

### Power Up, Initialization and Reset

When power is first applied through VDD, the FUSB300C is reset and registers are initialized to the default values shown in the register map.

The FUSB300C can be reset through software by programming the SW\_RES bit in the RESET register.

To properly configure the device in low power operation, place a  $0.2\mu F$  cap on each CC pin and set the following registers:

| Address 0x03:        | 00 |

|----------------------|----|

| Address 0x05:        | 00 |

| Address 0x06 (bit0): | 0  |

| Address 0x06 (bit1): | 0  |

| Address 0x06 (bit4): | 0  |

| Address 0x07:        | 00 |

| Address 0x0A (bit0)  | 1  |

| Address 0x0A (bit3)  | 1  |

| Address 0x0A (bit4)  | 0  |

| Address 0x0A (bit6)  | 1  |

| Address 0x0B (bit4)  | 0  |

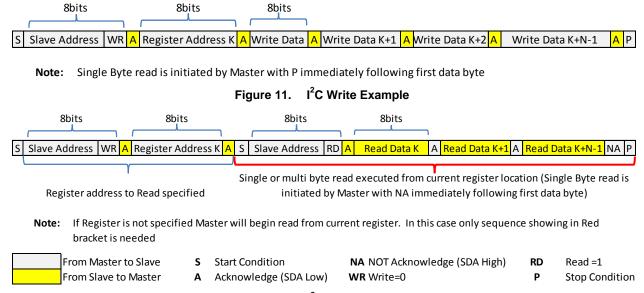

### I<sup>2</sup>C Interface

The FUSB300C includes a full  $I^2C$  slave controller. The  $I^2C$  slave fully complies with the  $I^2C$  specification version 6 requirements.

This block is designed for fast mode. Examples of an  $I^2C$  write and read sequence are shown in Figure 11 and Figure 12 respectively.

Figure 12. I<sup>2</sup>C Read Example

### **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol               | Parameter                                        |                |         |      | Max. | Unit |

|----------------------|--------------------------------------------------|----------------|---------|------|------|------|

| Vv <sub>DD</sub>     | Supply Voltage from V <sub>DD</sub>              |                |         | -0.5 | 6.0  | V    |

| Vcc                  | CC Pin Input Voltage                             |                |         | -0.5 | 6.0  | V    |

| V <sub>VBUS</sub>    | VBUS Supply Voltage                              |                |         | -0.5 | 28.0 | V    |

| T <sub>STORAGE</sub> | Storage Temperature Range                        |                |         | -65  | +150 | °C   |

| TJ                   | Maximum Junction Temperature                     |                |         |      | +150 | °C   |

| TL                   | Lead Temperature (Soldering, 10 Seconds)         |                |         |      | +260 | °C   |

|                      | IFO 04000 4 0 0 materia FOD                      | Connector Pins | Air Gap | 15   |      | kV   |

|                      | IEC 61000-4-2 System ESD                         | (VBUS, CCx)    | Contact | 8    |      | KV   |

| ESD                  | Human Body Model,<br>ANSI/ESDA/JEDEC JS-001-2012 | All Pins       |         | 2    |      | kV   |

|                      | Charged Device Model, JEDEC JESD22-C101          | All Pins       | 1       |      | kV   |      |

### **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol         | Parameter             | Min.               | Тур. | Max. | Unit |

|----------------|-----------------------|--------------------|------|------|------|

| $V_{VBUS}$     | VBUS Supply Voltage   | 4.0                | 5.0  | 21.0 | V    |

| $V_{VDD}$      | VDD Supply Voltage    | 3.0 <sup>(1)</sup> | 3.3  | 3.5  | V    |

| $V_{CONN}$     | VCONN Supply Voltage  | $V_{VDD}$          |      | 5.50 | V    |

| T <sub>A</sub> | Operating Temperature | -40                |      | +85  | °C   |

### Notes:

- 1. I<sup>2</sup>C registers access functions down to 2.8 V

- 2. The external I<sup>2</sup>C pull-up voltage must be 1.8 V (±10%).

# Type-C CC Switches<sup>(3)</sup>

| Symbol               | Parameter                                                                                              |                    |       | -40 to +85°C<br>-40 to +125°C |       | Unit |

|----------------------|--------------------------------------------------------------------------------------------------------|--------------------|-------|-------------------------------|-------|------|

| •                    |                                                                                                        | Min.               | Тур.  | Max.                          | ı     |      |

| R <sub>SW_CCx</sub>  | R <sub>DSON</sub> for SW1_CC1 and SW1_CC2                                                              | VCONN to CC1 & CC2 |       | 0.4                           | 1.5   | Ω    |

| I <sub>TOL_CCX</sub> | Tolerance of CC Current to VDD of 80 µA (default), 180 µA (1.5 A) and 320 µA (3 A)                     |                    | -8    |                               | 8     | %    |

| D                    | Device Pull-down Resistance (VDD>3.0                                                                   | V)                 | 4.59  | 5.10                          | 5.61  | kΩ   |

| R <sub>DEVICE</sub>  | Device Pull-down Resistance (VDD=0 V.                                                                  | CCx=2.18 V)        | 4.08  | 5.10                          | 6.20  | kΩ   |

| zOPEN                | CC Resistance for Disabled State                                                                       |                    | 126   |                               |       | kΩ   |

| WAKElow              | Wake threshold for CC pin DFP or UFP LOW value. Assumes bandgap and wake circuit turned on ie PWR[0]=1 |                    |       | 0.25                          |       | V    |

| WAKE <sub>high</sub> | Wake threshold for CC pin DFP or UFP I bandgap and wake circuit turned on ie P                         |                    | 1.45  |                               | V     |      |

|                      |                                                                                                        | BC=2'b00           | 0.15  | 0.20                          | 0.25  | V    |

| vBC_LVL              | CC Pin Thresholds. Assumes PWR=4'h7                                                                    | BC=2'b01           | 0.61  | 0.66                          | 0.70  | V    |

|                      |                                                                                                        | BC=2'b10           | 1.16  | 1.23                          | 1.31  | V    |

|                      |                                                                                                        | MDAC='h08          | 0.350 |                               | 0.450 | V    |

|                      |                                                                                                        | MDAC='h12          | 0.750 |                               | 0.850 | V    |

| vMDACvt              | Meas_VBUS=0                                                                                            | MDAC='h24          | 1.50  |                               | 1.65  | V    |

|                      |                                                                                                        | MDAC='h30          | 2.04  |                               | 2.16  | V    |

|                      |                                                                                                        | MDAC='h3D          | 2.45  |                               | 2.75  | V    |

| vMDACstep            | Measure block MDAC step size for each register from 0 to 'h3D. MEAS_VBUS=0                             | code in MDAC[5:0]  |       | 42                            |       | mV   |

| viviDACstep          | Measure block MDAC step size for each code in MDAC[5:0] register from 0 to 'h28. MEAS_VBUS=1           |                    |       | 375                           |       | mV   |

| vVBUSthr             | VBUS threshold at which I_VBUSOK inte<br>Assumes measure block on ie; PWR[2]=                          |                    |       | 4.0                           |       | V    |

### Note:

3. For MEAS\_VBUS=0, do not exceed register 'h3D. For MEAS\_VBUS=1, do not exceed register 'h28.

# **Current Consumption**

| Symbol   | Parameter                                       | V <sub>DD</sub> (V) | Conditions                                                                               | T <sub>A</sub> =-40 to +85°C<br>T <sub>J</sub> =-40 to +125°C |      |      | Unit |

|----------|-------------------------------------------------|---------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------|------|------|------|

|          |                                                 |                     |                                                                                          | Min.                                                          | Тур. | Max. |      |

| Idisable | Disabled Current                                | 3.0 to 3.5          | Nothing Attached, No I <sup>2</sup> C<br>Transactions. PWR[2:0]='h0                      |                                                               |      | 5    | μA   |

| Istdby   | Standby Current                                 | 3.0 to 3.5          | Nothing attached, no I2C traffic, PWR[2:0]='h1, Wake block on.                           |                                                               | 20   | 40   | μΑ   |

| ldrp     | Dual Role Port<br>Unattached Current            | 3.0 to 3.5          | Attached and Monitoring VBUS and CC with Terminations Enabled and Toggling. PWR[2:0]='h7 |                                                               | 200  |      | μΑ   |

| Tshut    | Temp. for Vconn<br>Switch Off                   | 3.0 to 3.5          |                                                                                          |                                                               | 145  |      | °C   |

| Thys     | Temp. Hysteresis for<br>Vconn Switch Turn<br>On | 3.0 to 3.5          |                                                                                          |                                                               | 10   |      | °C   |

# IO Specifications<sup>(4)</sup>

| Symbol                                                         | Parameter                             | V <sub>DD</sub> (V) | Conditions                  | T <sub>A</sub> =-40 to +85°C<br>T <sub>J</sub> =-40 to +125°C |      |      | Unit |

|----------------------------------------------------------------|---------------------------------------|---------------------|-----------------------------|---------------------------------------------------------------|------|------|------|

|                                                                |                                       |                     |                             | Min.                                                          | Тур. | Max. |      |

| Host Inter                                                     | face Pins(INT_N)                      |                     |                             | ul                                                            | I.   | l.   |      |

| V <sub>OLINTN</sub>                                            | Output Low Voltage                    | 3.0 to 3.5          | I <sub>OL</sub> =4 mA       |                                                               |      | 0.4  | V    |

| I <sup>2</sup> C Interface Pins – Fast Mode (I2C_SDA, I2C_SCL) |                                       |                     |                             |                                                               |      |      |      |

| V <sub>ILI2C</sub>                                             | Low-Level Input Voltage               | 3.0 to 3.5          |                             |                                                               |      | 0.4  | V    |

| V <sub>IHI2C</sub>                                             | High-Level Input Voltage              | 3.0 to 3.5          |                             | 1.2                                                           |      |      | V    |

| V <sub>HYS</sub>                                               | Hysteresis of Schmitt Trigger Inputs  | 3.0 to 3.5          |                             | 0.09                                                          |      |      | V    |

| I <sub>I2C</sub>                                               | Input Current of SDA and SCL Pins,    | 3.0 to 3.5          | Input Voltage 0.26 V to 2 V | -10                                                           |      | 10   | μΑ   |

| I <sub>CCTI2C</sub>                                            | VDD Current when SDA or SCL is HIGH   | 3.0 to 3.5          | Input Voltage 1.8 V         | -10                                                           |      | 10   | μΑ   |

| V <sub>OLSDA</sub>                                             | Low-Level Output Voltage (Open-Drain) | 3.0 to 3.5          | I <sub>OL</sub> =3 mA       | 0                                                             |      | 0.3  | V    |

| Cı                                                             | Capacitance for Each I/O Pin          | 3.0 to 3.5          |                             |                                                               | 5    |      | pF   |

### Note:

4. The external I<sup>2</sup>C pull-up voltage must be 1.8V (±10%).

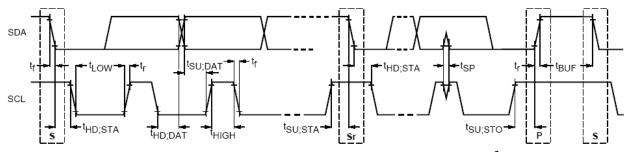

# I<sup>2</sup>C Specifications Fast Mode I<sup>2</sup>C Specification

| Cumbal              | Doromotor                                                         | F                    | Fast Mode |      |  |  |  |

|---------------------|-------------------------------------------------------------------|----------------------|-----------|------|--|--|--|

| Symbol              | Parameter                                                         | Min.                 | Max.      | Unit |  |  |  |

| f <sub>SCL</sub>    | I2C_SCL Clock Frequency                                           | 0                    | 400       | kHz  |  |  |  |

| t <sub>HD;STA</sub> | Hold Time (Repeated) START Condition                              | 0.6                  |           | μs   |  |  |  |

| t <sub>LOW</sub>    | Low Period of I2C_SCL Clock                                       | 1.3                  |           | μs   |  |  |  |

| t <sub>HIGH</sub>   | High Period of I2C_SCL Clock                                      | 0.6                  |           | μs   |  |  |  |

| t <sub>SU;STA</sub> | Set-up Time for Repeated START Condition                          | 0.6                  |           | μs   |  |  |  |

| t <sub>HD;DAT</sub> | Data Hold Time                                                    | 0                    | 0.9       | μs   |  |  |  |

| t <sub>SU;DAT</sub> | Data Set-up Time <sup>(5)</sup>                                   | 100                  |           | ns   |  |  |  |

| t <sub>r</sub>      | Rise Time of I2C_SDA and I2C_SCL Signals <sup>(5)</sup>           | 20+0.1C <sub>b</sub> | 300       | ns   |  |  |  |

| t <sub>f</sub>      | Fall Time of I2C_SDA and I2C_SCL Signals <sup>(5)</sup>           | 20+0.1C <sub>b</sub> | 300       | ns   |  |  |  |

| t <sub>SU;STO</sub> | Set-up Time for STOP Condition                                    | 0.6                  |           | μs   |  |  |  |

| t <sub>BUF</sub>    | Bus-Free Time between STOP and START Conditions                   | 1.3                  |           | μs   |  |  |  |

| t <sub>SP</sub>     | Pulse Width of Spikes that Must Be Suppressed by the Input Filter | 0                    | 50        | ns   |  |  |  |

#### Notes:

- 5. A fast-mode I²C-bus device can be used in a standard-mode I²C-bus system, but the requirement t<sub>SU;DAT</sub> ≥ 250 ns must be met. This is automatically the case if the device does not stretch the LOW period of the I2C\_SCL signal. If such a device does stretch the LOW period of the I2C\_SCL signal, it must output the next data bit to the I2C\_SDA line t<sub>r\_max</sub> + t<sub>SU;DAT</sub> (according to the standard-mode I²C bus specification) before the I2C\_SCL line is released.

- 6. C<sub>b</sub> equals the total capacitance of one BUS line in Pf. If mixed with high-speed devices, faster fall times are allowed according to the I<sup>2</sup>C specification.

Figure 13. Definition of Timing for Full-Speed Mode Devices on the I<sup>2</sup>C Bus

# Table 3. I<sup>2</sup>C<sup>™</sup> Slave Address

| Name          | Size (Bits) | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------------|-------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Slave Address | 8           | 0     | 1     | 0     | 0     | 0     | 1     | 0     | R/W   |

# Register Definitions<sup>(7)</sup>

| Address       | Register<br>Name | Туре | Rst Val | Bit7       | Bit6                        | Bit5        | Bit4                        | Bit3                       | Bit2      | Bit1                        | Bit0     |

|---------------|------------------|------|---------|------------|-----------------------------|-------------|-----------------------------|----------------------------|-----------|-----------------------------|----------|

| 0x01          | Device ID        | RO   | 60      |            | Version                     | ID[3:0]     |                             | Revision ID[3:0]           |           |                             |          |

| 0x02          | Switches0        | R/W  | 03      | PU_EN2     | PU_EN1                      | VCONN _CC2  | VCONN _CC1                  | MEAS_CC2                   | MEAS_CC1  | PDWN2                       | PDWN1    |

| 0x03          | Reserved         |      | _0      | Do Not Use |                             |             |                             |                            |           |                             |          |

| 0x04          | Measure          | R/W  | 00      |            | MEAS_VBUS                   | MDAC5       | MDAC4                       | MDAC3                      | MDAC2     | MDAC1                       | MDAC0    |

| 0x05          | PDDetVT          | R/W  | 20      |            |                             | PDVT5       | PDVT4                       | PDVT3                      | PDVT2     | PDVT1                       | PDVT0    |

| 0x06          | Control0         | R/W  | 20      |            |                             | INT_MASK    | \ \                         | HOST_CUR1                  | HOST_CUR0 |                             |          |

| 0x07          | Reserved         |      |         | Do Not Use |                             |             |                             |                            |           |                             |          |

| 0x08          | Reserved         | 11   | ďi      | Do Not Use |                             |             |                             |                            |           |                             |          |

| 0x09          | Reserved         |      |         | Do Not Use |                             |             |                             |                            |           |                             |          |

| 0x0A          | Mask0            | R/W  | 00      | M_VBUSOK   | M_FCTY_USE3 <sup>(9)</sup>  | M_COMP_CHNG | M_FCTY_USE2 <sup>(9)</sup>  | M_FCTY_USE1 <sup>(9)</sup> | M_WAKE    | M_FCTY_USE0 <sup>(9)</sup>  | M_BC_LVL |

| 0x0B          | Power            | R/W  | 0F      | 7          |                             |             |                             | PWR3 <sup>(8)</sup>        | PWR2      | PWR1                        | PWR0     |

| 0x0C          | SWReset          | W/C  | 00      |            |                             |             |                             |                            | 1/2       |                             | SW_RES   |

| 0x0C-<br>0x1F | Reserved         |      |         | Do Not Use |                             |             |                             |                            |           |                             |          |

| 0x40          | Status0          | RO   | 27      | VBUSOK     | FCTY_USE3 <sup>(10)</sup>   | COMP        | FCTY_USE2 <sup>(10)</sup>   | FCTY_USE1 <sup>(10)</sup>  | WAKE      | BC_LVL1                     | BC_LVL0  |

| 0x41          | Status1          | RO   | 28      |            |                             |             |                             |                            |           | OVRTEMP                     | SHORT    |

| 0x42          | Interrupt        | R/C  | 25      | I_VBUSOK   | I_FCTY_USE3 <sup>(10)</sup> | I_COMP_CHNG | I_FCTY_USE2 <sup>(10)</sup> | FCTY_USE1 <sup>(10)</sup>  | I_WAKE    | I_FCTY_USE0 <sup>(10)</sup> | I_BC_LVL |

| 0x43          | Reserved         |      |         |            |                             |             |                             |                            |           | ·                           |          |

### Notes:

- Do not use registers that are blank.

Registers for M\_FCTY\_USEx must be written to "0"

Registers for M\_FCTY\_USEx must be written to "1"

Values read from undefined register bits are not defined and invalid. Do not write to undefined registers.

### Table 4. Device ID

NOTE: Register descriptions in **BOLD** reflect the default state of the register.

Address: 01h

Reset Value: 0x0110\_0000

Type: Read

| Bit # | Name        | Size (Bits) | Description                                                           |

|-------|-------------|-------------|-----------------------------------------------------------------------|

| 7:3   | Version ID  | 5           | Device version ID B_[Revision ID]: 01100 (e.g. A_revB)                |

| 2:0   | Revision ID | 3           | Revision History of each version [Version ID]_revB: 000 (e.g. A_revB) |

### Table 5. Switches0

Address: 02h

Reset Value: 0x0000\_0011

Type: Read/Write

| Bit # | Name       | Size (Bits) | Description                                                                                                                |

|-------|------------|-------------|----------------------------------------------------------------------------------------------------------------------------|

| 7     | PU_EN2     | 1           | 1: Enable host pull up current to CC2 pin based on Control0 register HOST_CUR[1:0] setting.                                |

| 6     | PU_EN1     | 1           | 1: Enable host pull up current to CC1 pin based on Control0 register HOST_CUR[1:0] setting.                                |

| 5     | VCONN _CC2 | 1           | 1: Enable the VCONN pin to CC2 pin switch.                                                                                 |

| 4     | VCONN _CC1 | 1           | 1: Enable the VCONN pin to CC1 pin switch.                                                                                 |

| 3     | MEAS_CC2   | 1           | 1: Connect the measure block to CC2 pin to monitor or measure the voltage on CC2 pin. Note, PWR=0x07 for proper operation. |

| 2     | MEAS_CC1   | 1           | 1: Connect the measure block to CC2 pin to monitor or measure the voltage on CC2 pin. Note, PWR=0x07 for proper operation. |

| 1     | PDWN2      | 1           | 1: Enable Device pull down on CC2 pin.                                                                                     |

| 0     | PDWN1      | 1           | 1: Enable Device pull down on CC1 pin.                                                                                     |

### Table 6. Measure

Address: 04h

Reset Value: 0x0000\_0000

Type: Read/Write

| Bit # | Name           | Size (Bits) |                                                                                                                                                                                                         |                                                                                                                                                                       | Descript    | ion         |      |  |  |

|-------|----------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|------|--|--|

| 7     | Reserved       | 1           | Do N                                                                                                                                                                                                    | Do Not Use                                                                                                                                                            |             |             |      |  |  |

| 6     | MEAS_VBUS      | 1           | MEA<br>0: <b>M</b> I                                                                                                                                                                                    | Measure VBUS with the MDAC/comparator. This requires     MEAS_CC* bits in Switches0 register to be 0.     MDAC/comparator measurement is controlled by MEAS_CC* bits. |             |             |      |  |  |

|       |                |             | Measure Block DAC data input. The step size is vMDACstep which is dependent on Meas_VBUS register setting. Examples are shown below. Valid values from 00_0000 to 11_1001 for MEAS_VBUS=1.              |                                                                                                                                                                       |             |             |      |  |  |

|       |                | 6           |                                                                                                                                                                                                         | MDAC[5:0]                                                                                                                                                             | MEAS_VBUS=0 | MEAS_VBUS=1 | Unit |  |  |

|       |                |             |                                                                                                                                                                                                         | 00_0000                                                                                                                                                               | 0.042       | 0.420       | V    |  |  |

|       |                |             |                                                                                                                                                                                                         | 00_0001                                                                                                                                                               | 0.084       | 0.840       | V    |  |  |

| 5:0   | MDAC[5:0]      |             |                                                                                                                                                                                                         | 11_0000                                                                                                                                                               | 2.058       | 20.58       | V    |  |  |

| 0.0   | 111.27 (0[0:0] |             |                                                                                                                                                                                                         | 11_0011                                                                                                                                                               | 2.217       | 21.84       | V    |  |  |

|       |                |             |                                                                                                                                                                                                         | 11_1110                                                                                                                                                               | 2.837       | 26.46       | V    |  |  |

|       |                |             |                                                                                                                                                                                                         | 11_1111                                                                                                                                                               | >2.888      | 26.88       | V    |  |  |

|       |                |             | Note which CC pin is currently being measured is controlled by the MEAS_CCx bits in the Switches0 register. For MEAS_VBUS=0, do not exceed register 'h3D. For MEAS_VBUS=1, do not exceed register 'h28. |                                                                                                                                                                       |             |             |      |  |  |

### Table 7. PDDetVT

Address: 05h

Reset Value: 0x0010\_0000

Type: Read/Write

| Bit # | Name      | Size (Bits) | Description                                                                                                                                                                                                                               |

|-------|-----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6   | Reserved  | 2           | Do Not Use                                                                                                                                                                                                                                |

| 5:0   | PDVT[5:0] | 6           | The FUSB300C is capable of alerting the host software if the connected device is attempting PD communication. This feature is enabled by default. To disable PD communication detection, this register must be cleared by writing PDVT=0. |

### Table 8. Control0

Address: 06h

Reset Value: 0x0010\_0000 Type: (See Column Below)

| Bit # | Name          | R/W/C | Size (Bits) | Description                                                                                                                                                                                                                 |

|-------|---------------|-------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6   | Reserved      | N/A   | 2           | Do Not Use                                                                                                                                                                                                                  |

|       |               |       |             |                                                                                                                                                                                                                             |

| 5     | INT_MASK      | R/W   | 1           | <ul><li>1: Mask all interrupts.</li><li>0: Interrupts to host are enabled.</li></ul>                                                                                                                                        |

| 4     | Reserved      | N/A   | 1           | Do Not Use                                                                                                                                                                                                                  |

| 3:2   | HOST_CUR[1:0] | R/W   | 2           | Controls the host pull-up current enabled by PU_EN[2:1] bits in the Switches0 register:  00: Current disabled  01: 80 µA – Default USB power.  10: 180 µA – Medium Current Mode: 1.5 A  11: 330 µA – High Current Mode: 3 A |

| 1:0   | Reserved      | N/A   | 2           | Do Not Use                                                                                                                                                                                                                  |

### Table 9. Mask0

Address: 0Ah

Reset Value: 0x0000\_0000

Type: Read/Write

| Bit # | Name        | Size (Bits) | Description                                         |

|-------|-------------|-------------|-----------------------------------------------------|

| 7     | M_VBUSOK    | 1           | 1: Mask I_VBUSOK interrupt bit.  0: Do not mask.    |

| 6     | M_FCTY_USE3 | 1           | 1: Must be written for this bit.                    |

| 5     | M_COMP_CHNG | 1           | 1: Mask I_COMP_CHNG interrupt bit.  0: Do not mask. |

| 4     | M_FCTY_USE2 | 1           | 1: Must be written for this bit.                    |

| 3     | M_FCTY_USE1 | 1           | 1: Must be written for this bit.                    |

| 2     | M_WAKE      | 1           | 1: Mask I_WAKE interrupt bit.  0: Do not mask.      |

| 1     | M_FCTY_USE0 | 1           | 1: Must be written for this bit.                    |

| 0     | M_BC_LVL    | 1           | 1: Mask I_BC_LVL interrupt bit.  0: Do not mask.    |

### Table 10. Power

Address: 0Bh

Reset Value: 0x0000\_0111

Type: Read/Write

| Bit # | Name     | Size (Bits) | Description                                                                                                                                                                                                                                                                  |  |

|-------|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7:4   | Reserved | 4           | Do Not Use                                                                                                                                                                                                                                                                   |  |

| 3:0   | PWR[3:0] | 4           | Power enables:  PWR[0]: Bandgap and wake circuit.  PWR[1]: Current references for measure block.  PWR[2]: Measure block powered.  PWR[3]: Must be written to 0.  It is expected that PWR=4'h1 is used for low power WAKE detection. PWR=4'h7 is used for all other detection |  |

### Table 11. SWReset

Address: 0Ch

Reset Value: 0x0000\_0000

Type: Write/Clear

| Bit # | Name     | Size (Bits) | Description                                                          |

|-------|----------|-------------|----------------------------------------------------------------------|

| 7:6   | Reserved | 4           | Do Not Use                                                           |

| 0     | SW_RES   | 1           | 1: Software reset. Resets the FUSB300C, including all the registers. |

### Table 12. Status0

Address: 40h

Reset Value: 0x0010\_0111

Type: Read

| Bit # | Name        | Size (Bits) | Description                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------|-------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | VBUSOK      | 1           | 1: VBUS is higher than vVBUSthr threshold. 0: VBUS is lower than vVBUSthr threshold.                                                                                                                                                                                                                                                                                                                               |

| 6     | FCTY_USE3   | 1           | Factory use only. Do not use.                                                                                                                                                                                                                                                                                                                                                                                      |

| 5     | COMP        | 1           | 1: Measured CC* input is higher than reference level driven from the MDAC.  0: Measured CC* input is lower than reference level driven from the MDAC.                                                                                                                                                                                                                                                              |

| 4     | FCTY_USE2   | 1           | Factory use only. Do not use.                                                                                                                                                                                                                                                                                                                                                                                      |

| 3     | FCTY_USE1   | 1           | Factory use only. Do not use.                                                                                                                                                                                                                                                                                                                                                                                      |

| 2     | WAKE        | 1           | 1: Voltage on CCx indicated that either a device, host or dual-role port is attempting to attach.                                                                                                                                                                                                                                                                                                                  |

| 1:0   | BC_LVL[1:0] | 2           | Current voltage status of the measured CC pin interpreted as host current levels as follows:  00: < 200 mV (vRA)  01: >200 mV, <660 mV (vRd-USB)  10: >660 mV, <1.23 V (vRd-1.5)  11:>1.23 V (vRd-3.0*)  Note the software must measure these at an appropriate time, while there is no signaling activity on the selected CC line.  *require use of properly set DAC and COMP interrupt for detection of vRD-3.0. |

### Table 13. Status1

Address: 41h

Reset Value: 0x0010\_1000

Type: Read

| Bit # | Name     | Size (Bits) | Description                                                                                                                  |

|-------|----------|-------------|------------------------------------------------------------------------------------------------------------------------------|

| 7:2   | Reserved | 6           | Do not use.                                                                                                                  |

| 1     | OVRTEMP  | 1           | 1: Temperature of the device has exceeded Tshut temperature.                                                                 |

| 0     | SHORT    | 1           | 1: Indicates an over-current or short condition has occurred on the VCONN switch. This feature is guaranteed for VCONN=3.0V. |

### Table 14. Interrupt

Address: 42h

Reset Value: 0x0010\_0101

Type: Write/Clear

| Bit # | Name        | Size (Bits) | Description                                                                                                                                                                                                                                                                                                                          |  |  |

|-------|-------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7     | I_VBUSOK    | 1           | 1: A change in the value of VBUSOK has occurred. This bit typically is used to recognize a port partner attach or detach when configured as a device/upstream facing port.                                                                                                                                                           |  |  |

| 6     | I_FCTY_USE3 | 1           | Factory use only. Do not use.                                                                                                                                                                                                                                                                                                        |  |  |

| 5     | I_COMP_CHNG | 1           | : A change in the value of COMP has occurred.  Indicates selected CC line has tripped a threshold programmed into the MDAC. This bit is typically used as an attach/detach threshold when configured as a host/downstream facing port or as part of the sharging current detection when configured as a device/upstream facing port. |  |  |

| 4     | I_FCTY_USE2 | 1           | Factory use only. Do not use.                                                                                                                                                                                                                                                                                                        |  |  |

| 3     | I_FCTY_USE1 | 1           | Factory use only. Do not use.                                                                                                                                                                                                                                                                                                        |  |  |

| 2     | I_WAKE      | 1           | 1: A change in the value of WAKE has occurred.  This bit is typically used to detect that something is trying to attach to the FUSB300C and starts the software to determine what type of device is attached and the orientation of the attach.                                                                                      |  |  |

| 1     | I_FCTY_USE0 | 1           | Factory use only. Do not use.                                                                                                                                                                                                                                                                                                        |  |  |

| 0     | I_BC_LVL    | 1           | A change in BC_LVL has occurred.  This bit is typically used to indicate that the host has changed the allowed charging current level on the connected CC pin.                                                                                                                                                                       |  |  |

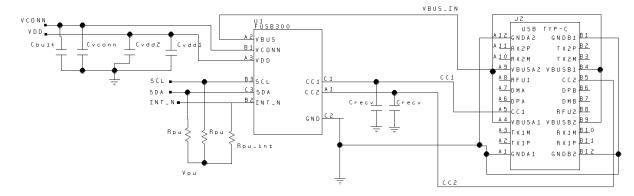

### **Reference Schematic**

Figure 14. Reference Schematic Diagram

**Table 15. Recommended Component Values for Reference Schematic**

| Symbol                     | Parameter                              | Recommended<br>Value |      |      | Unit | Notes                                                   |  |

|----------------------------|----------------------------------------|----------------------|------|------|------|---------------------------------------------------------|--|

| <b>- - - - - - - - - -</b> |                                        | Min.                 | Тур. | Max. |      |                                                         |  |

| C <sub>RECV</sub>          | CC <sub>X</sub> Receiver Capacitance   | 0.2                  |      | 2.2  | μF   |                                                         |  |

| C <sub>BULK</sub>          | VCONN Source Bulk<br>Capacitance       | 10                   |      | 220  | μF   | Section 4.4.3, USB Type-C<br>Specification Revision 1.0 |  |

| C <sub>VCONN</sub>         | VCONN Decoupling Capacitance           |                      | 0.1  |      | μF   |                                                         |  |

| C <sub>VDD1</sub>          | V <sub>DD</sub> Decoupling Capacitance |                      | 0.1  |      | μF   |                                                         |  |

| $C_{VDD2}$                 | V <sub>DD</sub> Decoupling Capacitance |                      | 1.0  |      | μF   |                                                         |  |

| R <sub>PU</sub>            | I2C Pull-up Resistors                  |                      | 4.7  |      | kΩ   | These values are application specific                   |  |

| R <sub>PU_INT</sub>        | INT_N pull-up Resistor                 | 1                    | 4.7  |      | kΩ   |                                                         |  |

| V <sub>PU</sub>            | I2C Pull-up Voltage                    | 1.62                 | 1.8  | 1.98 | ٧    |                                                         |  |

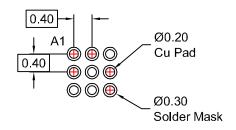

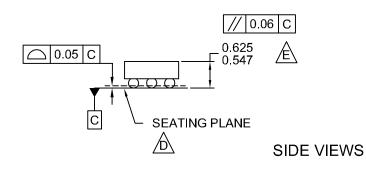

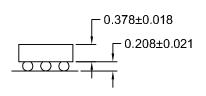

### **Product-Specific Dimensions**

| Product     | Product D |          | X        | Y        |  |

|-------------|-----------|----------|----------|----------|--|

| FUSB300CUCX | 1.215 mm  | 1.215 mm | 0.208 mm | 0.208 mm |  |

|   |     | REVISIONS                                                                                                                     |           |                 |  |  |  |

|---|-----|-------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------|--|--|--|

|   | REV | DESCRIPTION                                                                                                                   | DATE      | BY/SITE         |  |  |  |

|   | 1   | INITIAL DRAWING RELEASE.                                                                                                      | 2-15-2008 | L. ENGLAND/FSME |  |  |  |

| 2 |     | Updated land pattem to individual solder mask openings.<br>Removed solder alloy note. Other misc updates for standardization. | 4-9-2010  | L. ENGLAND/FSME |  |  |  |

**TOP VIEW**

LAND PATTERN RECOMMENDATION (NSMD PAD TYPE)

**BOTTOM VIEW**

### NOTES:

- A. NO JEDEC REGISTRATION APPLIES.

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS AND TOLERANCE PER ASMEY14.5M, 1994.

DATUM C IS DEFINED BY THE SPHERICAL CROWNS OF THE BALLS.

EN PACKAGE NOMINAL HEIGHT IS 586 MICRONS ±39 MICRONS (547-625 MICRONS).

FOR DIMENSIONS D, E, X, AND Y SEE PRODUCT DATASHEET.

G. DRAWING FILNAME: MKT-UC009ABrev2

| APPROVALS              | DATE   | FAIR                                               |      | <u> </u>       |            |     |

|------------------------|--------|----------------------------------------------------|------|----------------|------------|-----|

| L. England             | 4-9-10 | SEMICO                                             |      |                |            |     |

| DFTG. CHK.<br>H. Allen | 4-9-10 | 9 BALL WLCSP, 3X3 ARRAY<br>0.4MM PITCH, 250UM BALL |      |                |            |     |

| ENGR. CHK.             |        |                                                    |      |                |            |     |

|                        |        | - 0.4WW FITCH, 2000W BAL                           |      |                |            |     |

| PROJECTION INCH [MM]   |        | SCALE                                              | SIZE | DRAWING NUMBER |            | REV |

|                        |        | N/A                                                | N/A  | MKT-U          | JC009AB    | 2   |

|                        |        | DO NOT SCALE DRAWING                               |      |                | SHEET 1 of | 1   |

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdt/Patent-Marking.pdf">www.onsemi.com/site/pdt/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and exp

### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative