Product data sheet

## 1 General description

The WLAN8101C is a 5 GHz 2 x 2 MIMO RFFE for Wi-Fi 6 applications in a 3 mm x 4 mm package.

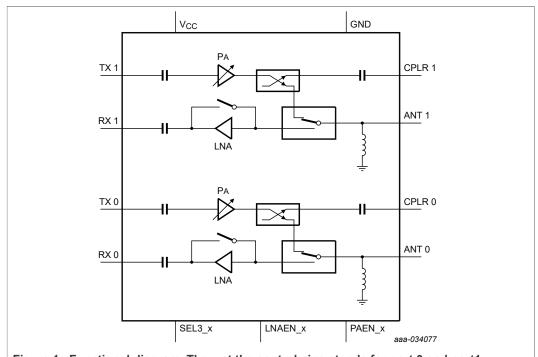

The WLAN8101C includes two monolithic front-end ICs. Each front-end IC has an integrated power amplifier, a low noise amplifier with bypass functionality, and a single pole double throw (SPDT) switch.

WLAN8101C also includes coexistence filters for both transmit and receive channels.

The device is matched to 50  $\Omega$  and integrates harmonic and out of band filtering which minimizes the layout area in the application.

### 2 Features and benefits

- Small-size 2 x 2 MIMO RFFE module for WiFi 6 applications

- Integrated power amplifiers with multiple operation modes for dynamic power efficiency and linearity control

- Full high band 5.150 GHz to 5.925 GHz

- 3 TX operation modes enabling flexibility for power efficiency adaptation

- · Integrated low-noise amplifiers supporting high gain and bypass modes

- Integrated SPDT switches for single antenna RX and TX operation

- · Integrated directional couplers for precise transmit power control

- Requires no external matching components, DC free input/output ports

- Integrated RF decoupling capacitors for all V<sub>CC</sub> and control pins

- Low profile, small-size 3 mm x 4 mm package

- · Integrated ESD protection on all pins

- Human Body Model (HBM) according to ANSI/ESDA/JEDEC standard JS-001 exceeds 2 kV

- Charged Device Model (CDM) according to ANSI/ESDA/JEDEC standard JS-002 exceeds 500 V

## 3 Applications

- · Wi-Fi 6 support

- · Smartphones, tablets, netbooks, and other portable computing devices

- · Module applications for embedded systems

## 4 Quick reference data

### Table 1. Quick reference data

$T_{amb}$  = 25 °C;  $V_{CC}$  = 3.85 V;  $V_{IH}$  = 1.8 V;  $V_{IL}$  = 0 V;  $Z_s$  =  $Z_L$  = 50  $\Omega$ ;  $P_i$  = -30 dBm for RX,  $P_i$  = -10 dBm for TX, f = 5.150 GHz to 5.925 GHz, single channel performance. Unless otherwise specified. All values are measured at product input/output as reference plane. Measurements are done using the application schematic. (See application note AN12711)

| Symbol                  | Parameter                                  | Conditions                                                                  | Min | Тур     | Max | Unit |

|-------------------------|--------------------------------------------|-----------------------------------------------------------------------------|-----|---------|-----|------|

| RF perform              | nance from ANT to RX                       |                                                                             |     | '       |     | _    |

| I <sub>CC</sub>         | supply current                             | RX_gain                                                                     | -   | 11.6    | -   | mA   |

|                         |                                            | RX_bypass mode                                                              | -   | 7.5     | -   | μA   |

| G <sub>p</sub>          | power gain                                 | RX_gain                                                                     | -   | 16      | -   | dB   |

|                         |                                            | RX_bypass mode                                                              | -   | -5.5    | -   | dB   |

| NF                      | noise figure                               | RX_gain                                                                     | -   | 2.5     | -   | dB   |

| P <sub>i(1dB)</sub>     | input power at 1 dB gain compression point | RX_gain                                                                     | -   | -9      | -   | dBm  |

| RLi                     | input return loss                          | RX_gain mode, looking into ANT pin                                          | -   | 10      | -   | dB   |

|                         |                                            | RX_bypass mode, looking into ANT pin                                        | -   | 9       | -   | dB   |

| $RL_o$                  | output return loss                         | RX_gain mode, looking into RX pin                                           | -   | 10      | -   | dB   |

|                         |                                            | RX_bypass mode, looking into RX pin                                         | -   | 10      | -   | dB   |

| RF perform              | nance from TX to ANT                       |                                                                             |     |         |     |      |

| I <sub>CC</sub>         | supply current                             | TX_gain1a (11ax compliant mode), 22dBm_11a, 6 Mbp/s spectral mask compliant | -   | 325     | -   | mA   |

| G <sub>p</sub>          | power gain                                 | TX_gain1a (11ax compliant, high-power mode)                                 | -   | 30      | -   | dB   |

|                         |                                            | TX_gain2a (11ax compliant, 3 dB back-off mode)                              | -   | 27.5    | -   | dB   |

|                         |                                            | TX_gain3 (11ax compliant, low-power mode)                                   | -   | 16      | -   | dB   |

| G <sub>flat</sub>       | gain flatness                              | all TX modes, for any 80 MHz bandwidth                                      | -   | +/-0.25 | -   | dB   |

|                         |                                            | all TX modes, for entire frequency range                                    | -   | +/-0.75 | -   | dB   |

| EVM <sub>dyn</sub>      | dynamic error vector magnitude             | 11ax MCS10/11, TX_gain1a, 14 dBm,<br>180 µs burst, 50 % duty cycle, HE80    | -   | -44.5   | -   | dB   |

| RLi                     | input return loss                          | looking into TX pin                                                         | -   | 10      | -   | dB   |

| $RL_o$                  | output return loss                         | looking into ANT pin                                                        | -   | 8       | -   | dB   |

| High Isola              | tion performance from A                    | NT to RX                                                                    |     |         |     |      |

| I <sub>CC</sub>         | supply current                             | high isolation (default), dual channel                                      | -   | 15      | -   | μA   |

| ISL <sub>(ANT-RX)</sub> | ANT-RX isolation                           | high isolation (default)                                                    | 35  | -       | -   | dB   |

## 5 Ordering information

Table 2. Ordering information

| Туре      | Orderable part  | Package   |                                                       |           |

|-----------|-----------------|-----------|-------------------------------------------------------|-----------|

| number    | number          | Name      | Description                                           | Version   |

| WLAN8101C | WLAN8101C<br>MP | HFCPLGA38 | 3 mm x 4 mm x 0.65 mm package, 0.35 mm pitch, 38 pins | SOT2022-1 |

## 6 Marking

#### Table 3. Marking

| Type number | Marking code |

|-------------|--------------|

| WLAN8101C   | 8101C        |

## 7 Functional diagram

Figure 1. Functional diagram. The  $\boldsymbol{x}$  at the control pins stands for port 0 and port1.

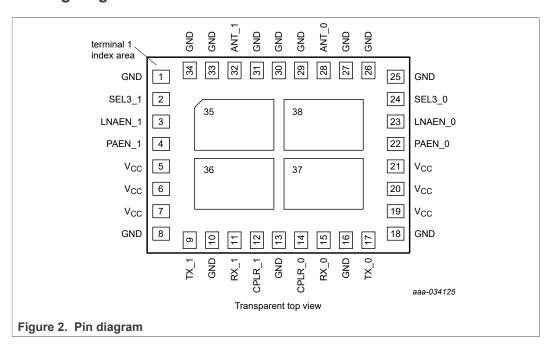

## 8 Pinning information

### 8.1 Pinning diagram

### 8.2 Pin description

Table 4. Pin description

| Pin                                                                      | Symbol          | Description    |

|--------------------------------------------------------------------------|-----------------|----------------|

| 1, 8, 10, 13, 16, 18, 25, 26, 27, 29, 30, 31, 33, 34, 35, 36, 37, and 38 | GND             | Ground         |

| 2                                                                        | SEL3_1          | select control |

| 24                                                                       | SEL3_0          | select control |

| 3                                                                        | LNAEN_1         | LNA enable     |

| 23                                                                       | LNAEN_0         | LNA enable     |

| 4                                                                        | PAEN_1          | PA enable      |

| 22                                                                       | PAEN_0          | PA enable      |

| 5, 6, 7, 19, 20 and 21                                                   | V <sub>CC</sub> | supply voltage |

| 9                                                                        | TX_1            | TX port        |

| 17                                                                       | TX_0            | TX port        |

| 11                                                                       | RX_1            | RX port        |

| 15                                                                       | RX_0            | RX port        |

| 12                                                                       | CPLR_1          | coupler port   |

| 14                                                                       | CPLR_0          | coupler port   |

| 28                                                                       | ANT_0           | antenna port   |

| 32                                                                       | ANT_1           | antenna port   |

## 9 Functional description

### 9.1 Parallel interface control states per MIMO channel

Table 5. Parallel interface control states per MIMO channel

Control pin SEL3\_x, LNAEN\_x, and PAEN\_x contain internal pull-down resistors. The parallel interface table applies to both \_0 and \_1 control pins. [1]

| SEL3_x | LNAEN_x | PAEN_x | Signal path | Operating mode | Mode description                                         | LNA bias | PA bias |

|--------|---------|--------|-------------|----------------|----------------------------------------------------------|----------|---------|

| 0      | 0       | 0      | -           | -              | high isolation (default)                                 | off      | off     |

| 0      | 0       | 1      | TX to ANT   | TX_gain1a      | high gain, high linearity, 11ax compliant                | off      | on      |

| 1      | 0       | 1      | TX to ANT   | TX_gain2a      | high gain, high linearity, 3 dB back off, 11ax compliant | off      | on      |

| 1      | 1       | 1      | TX to ANT   | TX_gain3       | low gain, low power, 11ax compliant                      | off      | on      |

| 1      | 1       | 0      | -           | _              | reserved                                                 | -        | -       |

| 1      | 0       | 0      | -           | -              | reserved                                                 | -        | -       |

| 0      | 1       | 0      | ANT to RX   | RX_gain        | normal gain                                              | on       | off     |

| 0      | 1       | 1      | ANT to RX   | RX_bypass      | bypass                                                   | off      | off     |

<sup>[1]</sup> Binary represented logic levels, where 0 denotes a logic low  $(V_i \le V_{IL})$  and 1 denotes a logic high  $(V_i \ge V_{IH})$

## 10 Limiting values

Table 6. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol           | Parameter                                          | Conditions                                                                                                                                                                             | Min  | Тур | Max  | Unit |

|------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| V <sub>CC</sub>  | supply<br>voltage                                  | [1]                                                                                                                                                                                    | -0.3 | -   | 6    | V    |

| Vi               | input voltage                                      | applied to control pins SEL3_x, LNAEN_x, and PAEN_x, digital control signals for RX, TX, and isolation modes                                                                           | -0.3 | -   | 4.2  | V    |

| Pi               | input power                                        | on ANT pin, RX LNA mode, MCS0 signal applied                                                                                                                                           | -    | -   | 10   | dBm  |

|                  |                                                    | on ANT pin, RX Bypass mode, MCS0 signal applied                                                                                                                                        | -    | -   | 18   | dBm  |

|                  |                                                    | on TX pin, MCS0 signal applied                                                                                                                                                         | -    | -   | 10   | dBm  |

| TX_RUG           | TX<br>ruggedness<br>(no<br>irreversible<br>damage) | $V_{CC}$ = 4.75 V, applied to TX_gain1a modes, $P_o$ = 24 dBm_MCS0 under 50 $\Omega$ load condition. The required $P_i$ level is kept constant during ruggedness test, VSWR all phases | -    | -   | 10:1 | -    |

| T <sub>stg</sub> | storage<br>temperature                             |                                                                                                                                                                                        | -55  | -   | 125  | °C   |

| Tj               | junction<br>temperature                            |                                                                                                                                                                                        | -    | -   | 175  | °C   |

| T <sub>mb</sub>  | mounting<br>base<br>temperature                    |                                                                                                                                                                                        | -    | -   | 100  | °C   |

| $V_{ESD}$        | Electrostatic<br>Discharge                         | Human Body Model (HBM) according to ANSI/ESDA/JEDEC standard JS-001                                                                                                                    | -    | -   | 2    | kV   |

|                  | Voltage                                            | Charged Device Model (CDM) according to ANSI/ESDA/JEDEC standard JS-002                                                                                                                | -    | -   | 500  | V    |

<sup>[1]</sup> Product withstands 30000 charger insert and pull-out events with a duration of 100 ms and a maximum supply voltage of 6 V

## 11 Recommended operating conditions

Table 7. Recommended operating conditions

| Symbol            | Parameter                | Conditions                 | Min   | Тур  | Max   | Unit |

|-------------------|--------------------------|----------------------------|-------|------|-------|------|

| f <sub>oper</sub> | operating frequency      |                            | 5.150 | -    | 5.925 | GHz  |

| V <sub>CC</sub>   | supply voltage           | on pin V <sub>CC</sub> [1] | 2.70  | 3.85 | 4.75  | V    |

| V <sub>IH</sub>   | HIGH-level input voltage |                            | 1.6   | 1.8  | 3.6   | V    |

| V <sub>IL</sub>   | LOW-level input voltage  |                            | 0.0   | -    | 0.4   | V    |

| T <sub>amb</sub>  | ambient temperature      |                            | -40   | 25   | 85    | °C   |

<sup>[1]</sup> Product is functional with reduced performance at supply voltages from 2.5 V to 2.7 V.

**WLAN8101C**

5 GHz Wi-Fi 6 Front-End Module

## 12 Thermal characteristics

#### Table 8. Thermal characteristics

| Symbol         | Parameter                                    | Conditions | Min | Тур | Max | Unit |

|----------------|----------------------------------------------|------------|-----|-----|-----|------|

| $R_{th(j-mb)}$ | junction to mounting base thermal resistance |            | -   | 25  | -   | K/W  |

### 13 Characteristics

### 13.1 Switching time performance

Table 9. Switching time performance

$T_{amb}$  = 25 °C;  $V_{CC}$  = 3.85 V: All ports are terminated with 50  $\Omega$ , single channel performance. Unless otherwise specified

| Symbol                | Parameter         | Conditions                                                   | Min | Тур | Max | Unit |

|-----------------------|-------------------|--------------------------------------------------------------|-----|-----|-----|------|

| t <sub>on(LNA)</sub>  | LNA turn-on time  | from 10 % to 90 % of LNA output level, bypass/LNA transition | -   | 170 | -   | ns   |

| t <sub>off(LNA)</sub> | LNA turn-off time | from 90 % to 10 % of LNA output level, bypass/LNA transition | -   | 230 | -   | ns   |

| t <sub>on(PA)</sub>   | PA turn-on time   | from 10 % to 90 % of PA output level, LNA/TX transition      | -   | 250 | -   | ns   |

| t <sub>off(PA)</sub>  | PA turn-off time  | from 90 % to 10 % of PA output level, LNA/TX transition      | -   | 250 | -   | ns   |

### 13.2 RF performance from ANT to RX

#### Table 10. RF performance from ANT to RX

$T_{amb}$  = 25 °C;  $V_{CC}$  = 3.85 V;  $V_{IH}$  = 1.8 V;  $V_{IL}$  = 0 V; All ports are terminated with 50  $\Omega$ ;  $P_i$  = -30 dBm, f = 5.150 GHz to 5.925 GHz, single channel performance. Unless otherwise specified. All values are measured at product input/output as reference plane. Measurements are done using the application schematic. (See application note AN12711)

| Symbol              | Parameter                      | Conditions                                   | Min | Тур     | Max | Unit |

|---------------------|--------------------------------|----------------------------------------------|-----|---------|-----|------|

| I <sub>CC</sub>     | supply current                 | RX_gain                                      | -   | 11.6    | -   | mA   |

|                     |                                | RX_bypass                                    | -   | 7.5     | -   | μΑ   |

| G <sub>p</sub>      | power gain                     | RX_gain                                      | -   | 16      | -   | dB   |

|                     |                                | RX_bypass                                    | -   | -5.5    | -   | dB   |

| G <sub>flat</sub>   | power gain                     | RX_gain, peak-to-peak over any 80 MHz band   | -   | +/-0.25 | -   | dB   |

|                     | flatness                       | RX_gain, over full RF bandwidth              | -   | +/-0.75 | -   | dB   |

|                     |                                | RX_bypass, peak-to-peak over any 80 MHz band | -   | +/-0.25 | -   | dB   |

|                     |                                | RX_bypass, over full RF bandwidth            | -   | +/-0.75 | -   | dB   |

| NF                  | noise figure                   | RX_gain                                      | -   | 2.5     | -   | dB   |

| RLi                 | input return loss              | RX_gain , looking into ANT pin               | -   | 10      | -   | dB   |

|                     |                                | RX_bypass , looking into ANT pin             | -   | 9       | -   | dB   |

| $RL_o$              | output return loss             | RX_gain , looking into RX pin                | -   | 10      | -   | dB   |

|                     |                                | RX_bypass , looking into RX pin              | -   | 10      | -   | dB   |

| IP3 <sub>i</sub>    | input third order              | RX_gain [1]                                  | -   | 1.5     | -   | dBm  |

|                     | intercept point                | RX_bypass [2]                                | -   | 27      | -   | dBm  |

| P <sub>i(1dB)</sub> | input power                    | RX_gain                                      | -   | -9      | -   | dBm  |

|                     | at 1 dB gain compression point | RX_bypass                                    | -   | 14.0    | -   | dBm  |

<sup>[1]</sup> P<sub>i = -20 dBm/tone, (20 MHz tone spacing)</sub>

<sup>[2]</sup> P<sub>i = -3 dBm/tone</sub>, (20 MHz tone spacing)

## 13.3 RF performance from TX to ANT

Table 11. RF performance from TX to ANT

$T_{amb}$  = 25 °C;  $V_{CC}$  = 3.85 V;  $V_{IH}$  = 1.8 V;  $V_{IL}$  = 0 V; All ports are terminated with 50  $\Omega$ ;  $P_i$  = -30 dBm, f = 5.150 GHz to 5.925 GHz, single channel performance. Unless otherwise specified. All values are measured at product input/output as reference plane. Measurements are done using the application schematic. (See application note AN12711)

| Symbol                  | Parameter                 | Conditions                                                                    | Min   | Тур     | Max | Unit |

|-------------------------|---------------------------|-------------------------------------------------------------------------------|-------|---------|-----|------|

| I <sub>CC</sub>         | supply current            | TX_gain1a, no RF                                                              | -     | 190     | -   | mA   |

|                         |                           | TX_gain2a, no RF                                                              | -     | 145     | -   | mA   |

|                         |                           | TX_gain3, no RF                                                               | -     | 60      | -   | mA   |

|                         |                           | TX_gain1a, P <sub>o</sub> = 17.5 dBm VHT80                                    | -     | 245     | -   | mA   |

|                         |                           | TX_gain1a, P <sub>o</sub> = 19 dBm 11n MCS7 HT20                              | -     | 265     | -   | mA   |

|                         |                           | TX_gain1a, P <sub>o</sub> = 22 dBm 11a OFDM6, 20 MHz                          | -     | 325     | -   | mA   |

|                         |                           | TX_gain2a, P <sub>o</sub> = 14.5 dBm, VHT80                                   | -     | 190     | -   | mA   |

|                         |                           | TX_gain2a, P <sub>o</sub> = 16 dBm, 11n MCS7 HT20                             | -     | 205     | -   | mA   |

|                         |                           | TX_gain2a, P <sub>o</sub> = 19 dBm, 11a OFDM6, 20 MHz                         | -     | 245     | -   | mA   |

|                         |                           | TX_gain3, P <sub>o</sub> = 4 dBm, 11ax MCS10/11 HE80                          | -     | 65      | -   | mA   |

| G <sub>p</sub>          | power gain                | TX_gain1a mode                                                                | -     | 30      | -   | dB   |

|                         |                           | TX_gain2a mode                                                                | -     | 27.5    | -   | dB   |

|                         |                           | TX_gain3 mode                                                                 | -     | 16      | -   | dB   |

| G <sub>flat</sub>       | gain flatness             | all TX modes, for any 80 MHz bandwidth                                        | -     | +/-0.25 | -   | dB   |

|                         |                           | all TX modes, for entire frequency range                                      | -     | +/-0.75 | -   | dB   |

| RLi                     | input return loss         | all TX modes, looking into TX pin                                             | -     | 10      | -   | dB   |

| $RL_o$                  | output return loss        | all TX modes, looking into ANT pin                                            | -     | 8       | -   | dB   |

| ISL <sub>(ANT-RX)</sub> | ANT-RX isolation          | all TX modes, measured between ANT, and RX pins, measured on the same channel | 33    | -       | -   | dB   |

| SEM margin              | margin to                 | 11a, OFDM6, 20 MHz                                                            | '     | '       |     |      |

|                         | spectrum<br>emission mask | TX_gain1a, P <sub>o</sub> = 22 dBm                                            | -     | 3.5     | -   | dB   |

|                         |                           | 11n, MCS0, 20 MHz                                                             | 1     | '       |     |      |

|                         |                           | TX_gain1a, P <sub>o</sub> = 21 dBm                                            | -     | 3       | -   | dB   |

| EVM <sub>dyn</sub>      | dynamic error             | 11a, OFDM6, 20 MHz, 180 μs burst, 50 % duty c                                 | ycle  | '       |     |      |

|                         | vector magnitude          | TX_gain1a, P <sub>o</sub> = 22 dBm                                            | -     | -20     | -   | dB   |

|                         |                           | TX_gain2a, P <sub>o</sub> = 19 dBm                                            | -     | -20     | -   | dB   |

|                         |                           | 11n, MCS0, 20 MHz, 180 µs burst, 50 % duty cyc                                | le    |         |     |      |

|                         |                           | TX_gain1a, P <sub>o</sub> = 20.5 dBm                                          | -     | -26     | -   | dB   |

|                         |                           | TX_gain2a, P <sub>o</sub> = 17.5 dBm                                          | -     | -26     | -   | dB   |

|                         |                           | 11a, OFDM54, 20 MHz, 180 µs burst, 50 % duty                                  | cycle | ,       |     | ,    |

|                         |                           | TX_gain1a, P <sub>o</sub> = 19.5 dBm                                          | -     | -32     | -   | dB   |

|                         |                           | TX_gain2a, P <sub>o</sub> = 16.5 dBm                                          | -     | -32     | -   | dB   |

Table 11. RF performance from TX to ANT...continued

$T_{amb}$  = 25 °C;  $V_{CC}$  = 3.85 V;  $V_{IH}$  = 1.8 V;  $V_{IL}$  = 0 V; All ports are terminated with 50  $\Omega$ ;  $P_i$  = -30 dBm, f = 5.150 GHz to 5.925 GHz, single channel performance. Unless otherwise specified. All values are measured at product input/output as reference plane. Measurements are done using the application schematic. (See application note AN12711)

| Symbol | Parameter                                        | Conditions                                      | Min   | Тур   | Max | Unit    |  |  |

|--------|--------------------------------------------------|-------------------------------------------------|-------|-------|-----|---------|--|--|

|        |                                                  | 11n, MCS7, HT20, 180 µs burst, 50 % duty cycle  |       |       |     |         |  |  |

|        |                                                  | TX_gain1a, P <sub>o</sub> = 18.5 dBm            | -     | -34   | -   | dB      |  |  |

|        |                                                  | TX_gain2a, P <sub>o</sub> = 15.5 dBm            | -     | -34   | -   | dB      |  |  |

|        | 11ac, MCS9, VHT80, 180 µs burst, 50 % duty cycle |                                                 |       |       |     |         |  |  |

|        |                                                  | TX_gain1a, P <sub>o</sub> = 17 dBm              | -     | -40   | -   | dB      |  |  |

|        |                                                  | TX_gain2a, P <sub>o</sub> = 14 dBm              | -     | -40   | -   | dB      |  |  |

|        |                                                  | 11ax, MCS10/11, HE80,180 µs burst, 50 % duty of | cycle |       |     |         |  |  |

|        |                                                  | TX_gain1a, P <sub>o</sub> = 16 dBm              | -     | -43   | -   | dB      |  |  |

|        |                                                  | TX_gain1a, P <sub>o</sub> = 14 dBm              | -     | -44.5 | -   | dB      |  |  |

|        |                                                  | TX_gain2a, P <sub>o</sub> = 13 dBm              | -     | -43.5 | -   | dB      |  |  |

|        |                                                  | TX_gain2a, P <sub>o</sub> = 11 dBm              | -     | -44.5 | -   | dB      |  |  |

|        |                                                  | TX_gain3, P <sub>o</sub> = 4.0 dBm              | -     | -44   | -   | dB      |  |  |

| a2H    | second harmonic                                  | 11a, OFDM6                                      | ,     |       |     |         |  |  |

|        | emission level                                   | TX_gain1a, P <sub>o</sub> = 22 dBm              | -     | -23   | -   | dBm/MHz |  |  |

| аЗН    | third harmonic                                   | ,                                               |       |       |     |         |  |  |

|        | emission level                                   | TX_gain1a, P <sub>o</sub> = 22 dBm              | -     | -21   | -   | dBm/MHz |  |  |

### 13.4 High isolation performance from ANT to RX

#### Table 12. High isolation performance from ANT to RX

$T_{amb}$  = 25 °C;  $V_{CC}$  = 3.85 V;  $V_{IH}$  = 1.8 V;  $V_{IL}$  = 0 V; All ports are terminated with 50  $\Omega$ ;  $P_i$  = -30 dBm, f = 5.150 GHz to 5.925 GHz. Unless otherwise specified. All values are measured at product input/output as reference plane. Measurements are done using the application schematic. (See application note AN12711)

| Symbol                  | Parameter        | Conditions                             | Min | Тур | Max | Unit |

|-------------------------|------------------|----------------------------------------|-----|-----|-----|------|

| I <sub>CC</sub>         | supply current   | high isolation (default), dual channel | -   | 15  | -   | μΑ   |

| ISL <sub>(ANT-RX)</sub> | ANT-RX isolation | high isolation (default)               | 35  | -   | -   | dB   |

### 13.5 Directional coupler

#### Table 13. Power coupler RF Performance

$T_{amb}$  = 25 °C;  $V_{CC}$  = 3.85 V;  $V_{IH}$  = 1.8 V;  $V_{IL}$  = 0 V; All ports are terminated with 50  $\Omega$ ;  $P_i$  = -30 dBm, f = 5.150 GHz to 5.925 GHz, single channel performance. Unless otherwise specified. All values are measured at product input/output as reference plane.

| Symbol                | Parameter                                  | Conditions                                                     | Min | Тур    | Max | Unit |

|-----------------------|--------------------------------------------|----------------------------------------------------------------|-----|--------|-----|------|

| R <sub>cpl</sub>      | coupling ratio                             | measured in Ch-0,TX_gain1a, and TX_gain2a modes, f = 5.540 GHz | -   | 23.5   | -   | dB   |

|                       |                                            | measured in Ch-1,TX_gain1a, and TX_gain2a modes, f = 5.540 GHz | -   | 24.5   | -   | dB   |

| $\Delta R_{cpl(f)}$   | variation of coupling ratio over frequency | positive slope versus frequency,<br>f = 5.150 GHz to 5.925 GHz | -   | +/-0.7 | -   | dB   |

| D                     | directivity                                | measured in all TX modes                                       | -   | 14     | -   | dB   |

| RL <sub>i(CPLR)</sub> | coupler input return loss                  | looking into CPLR pin                                          | -   | 10     | -   | dB   |

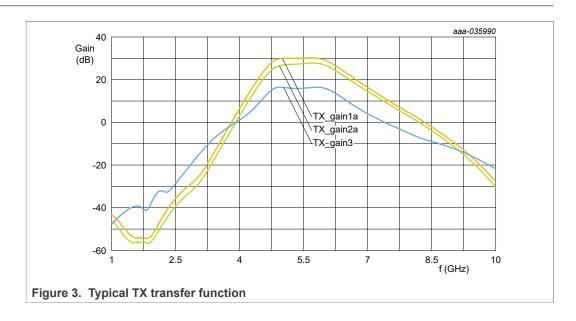

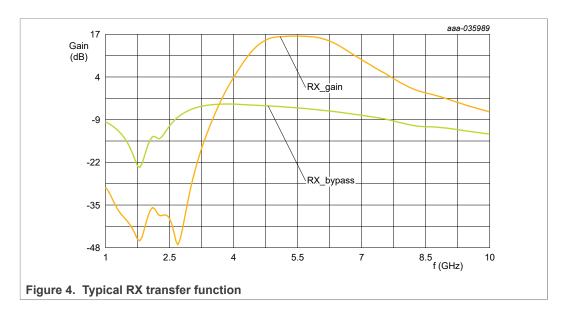

## 14 Graphics

## 15 Application information

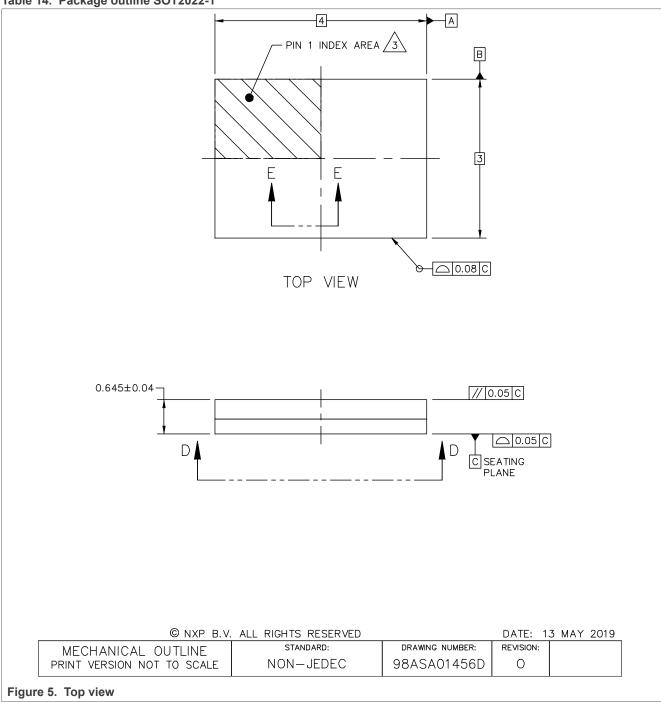

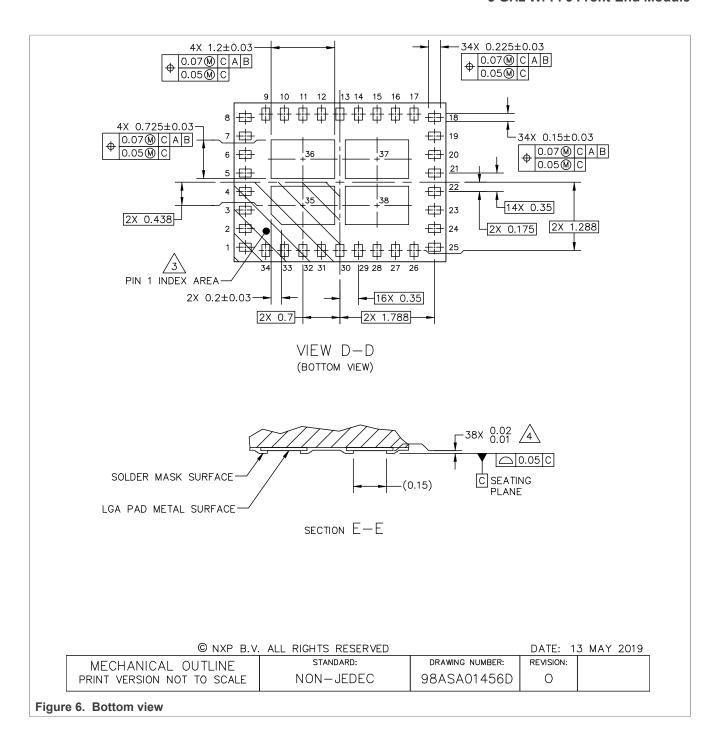

## 16 Package outline

Table 14. Package outline SOT2022-1

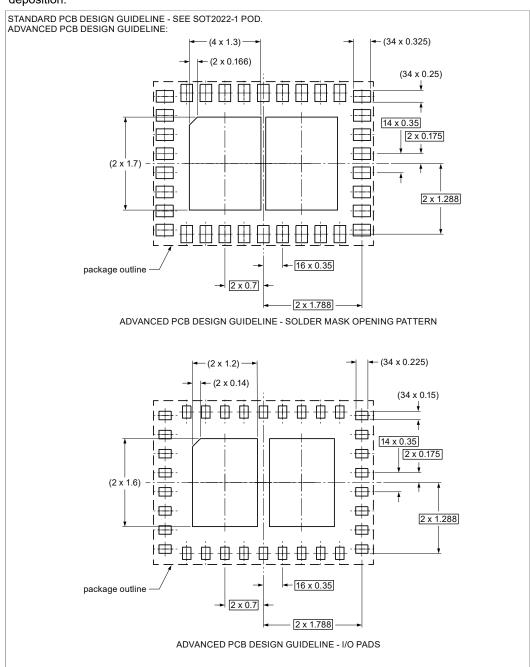

### 16.1 Advanced solder footprint

NXP recommends by default to apply the soldering and footprint guidelines as are released in POD SOT2022-1.

Advanced PCB design guideline may be used when SOT2022-1 is applied with a non wet-able flank design. However, care should be taken in the design of the stencil to ensure optimal solder deposition.

THIS SHEET SERVES ONLY AS A GUIDELINE TO HELP DEVELOP A USER SPECIFIC SOLUTION.

DEVELOPMENT EFFORT WILL STILL BE REQUIRED BY END USERS TO OPTIMIZE PCB MOUNTING PROCESSES AND BOARD DESIGN IN ORDER TO MEET INDIVIDUAL//SPECIFIC REQUIREMENTS

STENCIL TECHNOLOGY SHOULD BE OPTIMIZED FOR OPTIMUM SOLDER DEPOSITION.

aaa-035752

Figure 7. Advanced solder footprint

## 17 Handling information

#### **CAUTION**

This device is sensitive to ElectroStatic Discharge (ESD). Observe precautions for handling electrostatic sensitive devices. Such precautions are described in the ANSI/ESD S20.20, IEC/ST 61340-5, JESD625-A or equivalent standards.

### 18 Abbreviations

Table 15. Abbreviations

| Acronym | Description                               |

|---------|-------------------------------------------|

| ANT     | antenna                                   |

| CDM     | charge device model                       |

| CPLR    | coupler                                   |

| DC      | direct current                            |

| ESD     | electrostatic discharge                   |

| EVM     | error vector magnitude                    |

| НВМ     | human body model                          |

| HFCPLGA | heat sink flip chip power land grid array |

| ISM     | industrial scientific medical             |

| ISL     | isolation                                 |

| LNA     | low noise amplifier                       |

| LNAEN   | low noise amplifier enable                |

| MCS     | modulation code scheme                    |

| MIMO    | multiple in multiple out                  |

| MSL     | moisture sensitivity level                |

| NF      | noise figure                              |

| PA      | power amplifier                           |

| PAEN    | power amplifier enable                    |

| RF      | radio frequency                           |

| RFFE    | radio frequency front end                 |

| RoHS    | restriction of hazardous substances       |

| SEL     | select                                    |

| SPDT    | single pole double throw                  |

| VSWR    | voltage standing wave ratio               |

| WLAN    | wireless local area network               |

# 19 Revision history

#### Table 16. Revision history

| Document ID   | Release date    | Data sheet status      | Change notice | Supersedes                                               |

|---------------|-----------------|------------------------|---------------|----------------------------------------------------------|

| WLAN8101C v.3 | 20200811        | Product data sheet     | -             | WLAN8101C v.2                                            |

| modification  | changed status  | from Company confident | ial to Public |                                                          |

| WLAN8101C v.2 | 20200724        | Product data sheet     | -             | WLAN8101C v.1                                            |

| modification  | adapted the foo |                        | •             | tion of the used ESD standard<br>anged -20 dBm to -3 dBm |

| WLAN8101C v.1 | 20191219        | Preliminary data sheet | -             | -                                                        |

## 20 Legal information

#### 20.1 Data sheet status

| Document status <sup>[1][2]</sup> | Product status <sup>[3]</sup> | Definition                                                                            |

|-----------------------------------|-------------------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet      | Development                   | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet    | Qualification                 | This document contains data from the preliminary specification.                       |

| Product [short] data sheet        | Production                    | This document contains the product specification.                                     |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions".

- The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL <a href="http://www.nxp.com">http://www.nxp.com</a>.

#### 20.2 Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

Product specification — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

#### 20.3 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors. In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without

notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Applications — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products. NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

WLAN8101C

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved

No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Non-automotive qualified products — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications. In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified or documented vulnerabilities. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. NXP has a Product Security Incident Response Team (PSIRT) (reachable at PSIRT@nxp.com) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

#### 20.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

### **Contents**

| 1    | General description                        | 1  |

|------|--------------------------------------------|----|

| 2    | Features and benefits                      | 1  |

| 3    | Applications                               | 1  |

| 4    | Quick reference data                       | 2  |

| 5    | Ordering information                       | 3  |

| 6    | Marking                                    | 3  |

| 7    | Functional diagram                         | 3  |

| 8    | Pinning information                        | 4  |

| 8.1  | Pinning diagram                            |    |

| 8.2  | Pin description                            | 4  |

| 9    | Functional description                     | 5  |

| 9.1  | Parallel interface control states per MIMO |    |

|      | channel                                    | 5  |

| 10   | Limiting values                            | 6  |

| 11   | Recommended operating conditions           | 6  |

| 12   | Thermal characteristics                    | 7  |

| 13   | Characteristics                            |    |

| 13.1 | Switching time performance                 | 8  |

| 13.2 | RF performance from ANT to RX              | 8  |

| 13.3 | RF performance from TX to ANT              | g  |

| 13.4 | High isolation performance from ANT to RX. | 11 |

| 13.5 | Directional coupler                        | 11 |

| 14   | Graphics                                   |    |

| 15   | Application information                    | 13 |

| 16   | Package outline                            | 13 |

| 16.1 | Advanced solder footprint                  |    |

| 17   | Handling information                       | 16 |

| 18   | Abbreviations                              |    |

| 19   | Revision history                           | 17 |

| 20   | Legal information                          | 19 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

NXP:

WLAN8101CMP