**User manual**

### **Document information**

| Information | Content                                                                                                   |

|-------------|-----------------------------------------------------------------------------------------------------------|

| Keywords    | NHS3100, NHS3152, ARM Cortex-M0+, NFC, Temperature, Cold chain, Monitoring, Therapy compliance, Adherence |

| Abstract    | HW user manual for the NHS31xx family of wireless sensor node ICs                                         |

NHS31xx User manual

Table 1. Revision history

| Rev            | Date           | Description                                                 |  |

|----------------|----------------|-------------------------------------------------------------|--|

| v2.3           | 20210913       | Jpdated temperature accuracy numbers.                       |  |

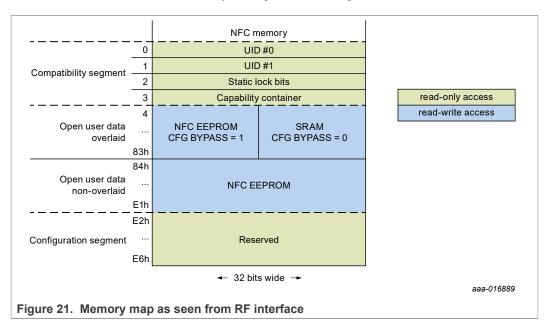

| v2.2           | 20200910       | pdated description of memory map as seen from RF interface. |  |

| v2.1           | 20200420       | Added soldering guidelines for HVQFN24 and WLCSP25 ICs.     |  |

| v2             | 20180330       | Updated issue                                               |  |

| Modifications: | Text and graph | phics have been updated throughout the document.            |  |

| v1             | 20161130       | Initial version                                             |  |

NHS31xx User manual

# 1 Introductory information

#### 1.1 Introduction

The NHS31xx are a family of ICs optimized for monitoring and logging. With their embedded NFC interface, internal temperature sensor and direct battery connection, they support effective system solutions with a minimal number of external components.

The embedded ARM Cortex-M0+ offers flexibility to the users of these ICs to implement their own dedicated solution. The NHS31xx family contains multiple features, like a selectable CPU frequency of up to 8 MHz and various power-down modes for ultra-low-power consumption.

Users can program this NHS31xx family with the industry-wide standard solutions for ARM Cortex-M0+ processors.

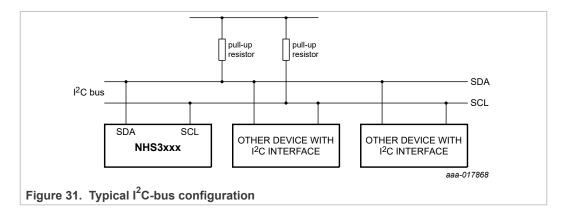

Peripheral components include an ultra-low-power RTC, I<sup>2</sup>C-bus interface, SPI interface with SSP features, NFC wireless interface and up to 12 general-purpose I/O pins.

Depending on the chip variant, other features include a temperature sensor, specific interfaces for capacitive, resistive and current measurements, and a 12-bit ADC/DAC. There are also specific analog interfaces for interfacing with photodiodes and LEDs.

#### 1.2 Attributes

Note: Not all features are available in all family members.

- System:

- ARM Cortex-M0+ processor, running at frequencies of up to 8 MHz

- ARM Cortex-M0+ built-in Nested Vectored Interrupt Controller (NVIC)

- ARM Serial Wire Debug (SWD)

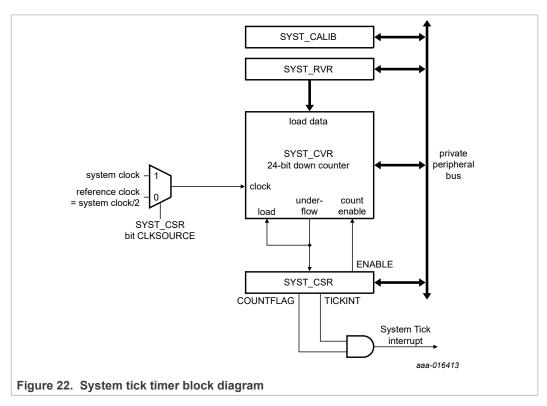

- System tick timer

- Fast (single-cycle) multiplier

- Support for wake-up interrupt controller

- Vector Table remapping possible

- IC reset input

- · Debug options:

- Serial Wire Debug with two watchpoint comparators and four breakpoint comparators

- Halting debug

- Memory:

- 32 kB on-chip flash programming memory

- 4 kB on-chip EEPROM of which 256 bytes can be write protected

- 8 kB SRAM

- Analog peripherals available, depending on variant:

- Temperature sensor with:

- ±0.5 °C absolute temperature accuracy between −40 °C and 0 °C

- ±0.3 °C absolute temperature accuracy between 0 °C and +45 °C

- ±0.5 °C absolute temperature accuracy between +45 °C and +85 °C

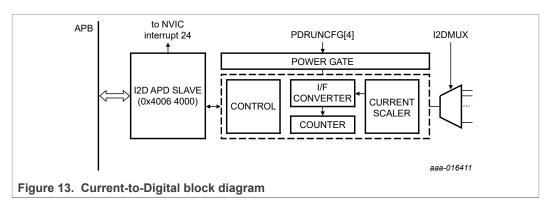

- Current-to-digital converter

- SAR ADC

- DAC for generating external biasing voltages

- 8-bit 20 mA current DAC on 4 pins

UM10876

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved

NHS31xx User manual

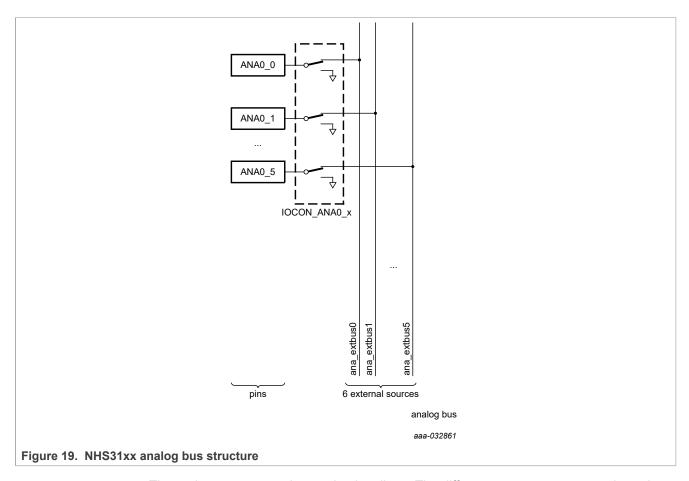

- Flexible analog on-chip switch:

- Each of the 6 analog I/O pins can be dynamically connected to the on-chip converters.

- Measuring 6 voltages connected to the 6 analog pins is possible using time-division multiplexing

- Digital peripherals:

- Up to 12 General-Purpose Input Output (GPIO) pins with configurable pull-up/pulldown resistors

- GPIO pins that can be used as edge and level sensitive interrupt sources

- High-current drivers/sinks (20 mA) on four pins

- High-current drivers/sinks (20 mA) on two I<sup>2</sup>C-bus pins

- Programmable watchdog timer (WDT)

- · Communication interfaces:

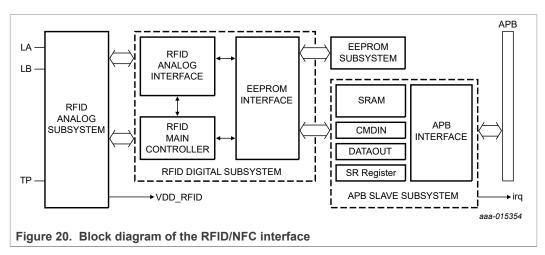

- NFC/RFID ISO 14443 type A interface

- SPI controller with SSP features and with FIFO and multi-protocol capabilities

- I<sup>2</sup>C-bus interface supporting full I<sup>2</sup>C-bus specification and Fast-mode with a data rate of 400 kbit/s with multiple address recognition and monitor mode

- · Clock generation:

- 8 MHz internal RC oscillator trimmed to 2 % accuracy that is used as the system clock

- Timer oscillator operating at 32 kHz linked to On/Off Timer unit, driving the real-time clock timer

- · Power control:

- Supply voltage range: 1.72 V to 3.6 V

- Passive powering via NFC field possible

- Integrated Power Management Unit (PMU) for fine-grained control of power consumption

- Four reduced power modes: Sleep, Deep-sleep, Deep power-down and Battery-off

- Power gating for each analog peripheral for ultra-low-power operation

- < 50 nA current consumption with battery power switch open</p>

- Power-On Reset (POR)

- Unique device serial number for identification

- · Wide operating temperature range

- Available in HVQFN24, WLCSP25 packages and as gold plated bumped die.

NHS31xx User manual

# 1.3 Device-dependent features

The following features are available, depending on the chip variant:

Table 2. Feature overview

| Variant | Function                              | ADC /<br>DAC | RTC | NFC | Temp. | I2D | SPI |

|---------|---------------------------------------|--------------|-----|-----|-------|-----|-----|

| NHS3100 | temperature Logger                    | -            | yes | yes | yes   | -   | yes |

| NHS3152 | therapy adherence monitor - resistive | yes          | yes | yes | yes   | yes | yes |

# 1.4 Ordering information

**Table 3. Ordering Information**

| Type number | Package    |                                                                                               |           |  |  |  |  |  |

|-------------|------------|-----------------------------------------------------------------------------------------------|-----------|--|--|--|--|--|

|             | Name       | Description                                                                                   | Version   |  |  |  |  |  |

| NHS3100     | HVQFN24    | plastic thermal enhanced very thin quad flat package; no leads; 24 terminals; 4 × 4 × 0.85 mm | SOT616-3  |  |  |  |  |  |

| NHS3100UK   | WLCSP25    | wafer level chip scale package; 25 balls; 2.51 × 2.51 × 0.5 mm                                | SOT1401-1 |  |  |  |  |  |

| NHS3100W8   | bumped die | bumped die with 8 functional bumps;<br>2.51 × 2.51 × 0.16 mm                                  | SOT1870-1 |  |  |  |  |  |

| NHS3152     | HVQFN24    | plastic thermal enhanced very thin quad flat package; no leads; 24 terminals; 4 × 4 × 0.85 mm | SOT616-3  |  |  |  |  |  |

| NHS3152UK   | WLCSP25    | wafer level chip scale package; 25 balls; 2.51 × 2.51 × 0.5 mm                                | SOT1401-1 |  |  |  |  |  |

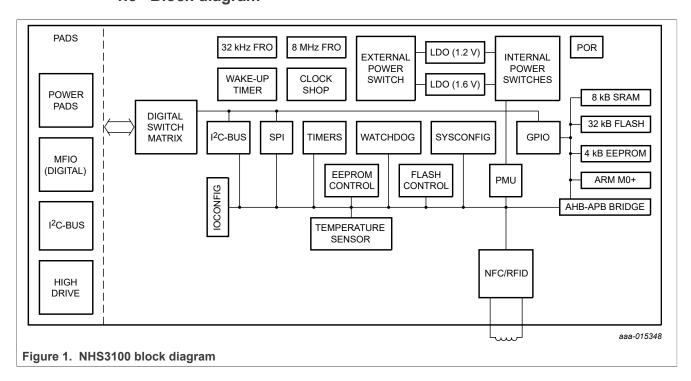

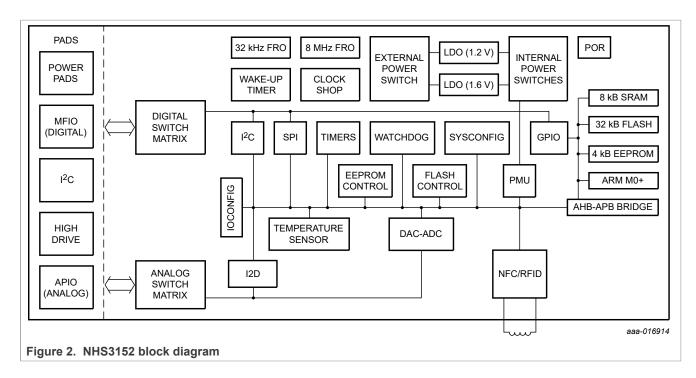

# 1.5 Block diagram

UM10876

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved.

NHS31xx User manual

# 1.6 Arm Cortex-M0+ core configuration

The Arm Cortex-M0+ core operates at frequencies up to 8 MHz. Integrated in the core are the NVIC and serial wire debug with four breakpoints and two watch points. It supports a single-cycle I/O enabled port (IOP) for fast GPIO access.

The specific firmware loaded on the non-volatile memory of the device determines its behavior.

The Arm Cortex-M0+ processor is described in detail in Ref. 3. For the NHS31xx family, the Arm Cortex-M0+ core is configured as follows:

- · System options:

- Nested vectored interrupt controller (NVIC) which is included and supports up to 32 interrupts

- Fast (single-cycle) multiplier

- System tick timer

- Support for wake-up interrupt controller

- Vector table remapping register

- Reset all registers present

- No memory protection unit

- No single-cycle I/O port

- Instruction fetch width, mostly 32-bit wide

- Data endianness: little endian

- · Debug options

- Serial wire debug is included with two watchpoint comparators and four breakpoint comparators

- Halting debug is supported

NHS31xx User manual

# 1.7 Memory map

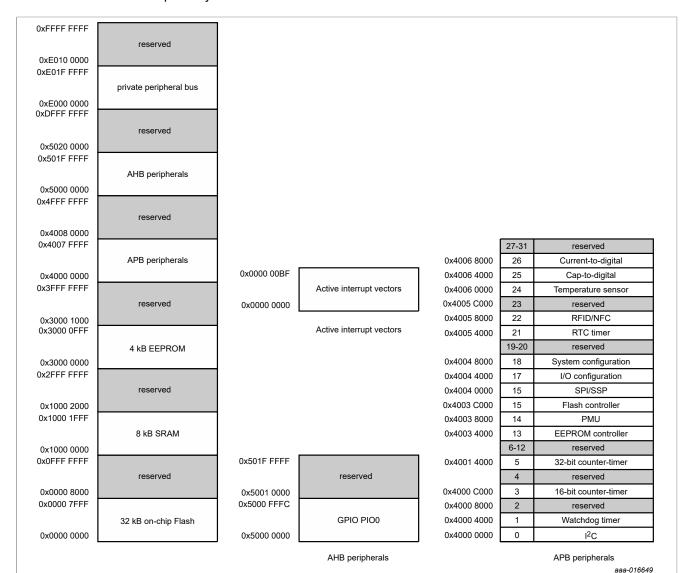

Figure 3 shows the memory and peripheral address space.

Peripheral accesses can only be done as 32-bit accesses on addresses divisible by 4. An implication of this is that word and halfword registers must be accessed at the same time. For example, it is not possible to read or write the upper bytes of a word register separately.

**Note:** Not all registers on the APB block are present on all the chip variants.

Figure 3. NHS31xx family memory map

NHS31xx User manual

### 1.7.1 Memories

### 1.7.1.1 SRAM (0x1000 0000 to 0x1000 1FFF)

The NHS31xx contains a total of 8 kB on-chip static RAM memory configured as  $256 \times 2 \times 4 \times 32$  bit. The SRAM supports byte-level access (BWE = 8).

# 1.7.1.2 Flash (0x0000 0000 to 0x0000 7FFF)

The NHS31xx contains a 32 kB Flash memory of which 30 kB can be used as program and data memory.

The flash is organized in 32 sectors of 1 kB. Each sector consists of 16 rows of  $16 \times 32$ -bit words.

## 1.7.1.3 EEPROM (0x3000 0000 to 0x3000 0FFF)

The NHS31xx contains a 4 kB EEPROM. This EEPROM is organized in 64 rows of  $32 \times 16$ -bit words. Of these rows, the last five contain calibration and test data and are locked. This data is either used by the boot loader after reset, or made accessible to the application via firmware API.

NHS31xx User manual

# 2 Product feature overview

#### 2.1 About this section

To suit different applications, the NHS31xx is available in several different variants. This section gives an overview of the principle components of each variant.

### 2.2 General description

All ICs share flexibility, standard adherence and ultra-low-power features:

- The embedded ARM Cortex-M0+ offers flexibility and processing power to the users of this IC. It enables them to implement their own dedicated solution, including decision making on the IC itself. The ICs contain multiple features including various power-down modes and a selectable CPU frequency up to 8 MHz for ultra-low-power consumption.

- Users can program this IC via SWD using industry-wide standard solutions for ARM Cortex-M0+ processors, or via NFC and the freely provided NFC program downloader. Programming via NFC can only be done once.

### 2.2.1 NHS3100 for cold chain monitoring and therapy adherence

The NHS3100 is an IC optimized for temperature monitoring and logging. The embedded NFC interface, allows fully NFC-forum standards-compliant communication, internal temperature sensing and direct battery connection. It supports an effective system solution with a minimal of external components.

The NHS3100 works either battery-powered or NFC-powered.

### 2.2.2 NHS3152 for therapy adherence using resistive sensing

The NHS3152 is an IC optimized for realizing therapy adherence monitoring and logging solutions. The embedded NFC interface fully allows NFC-forum standards-compliant communication, a resistive network sensing interface, an internal temperature sensor and direct battery connection. The NHS3152 enables the making of an effective system solution, supporting a single layer foil implementation, for pill usage monitoring.

The NHS3152 works either battery-powered or NFC-powered.

NHS31xx User manual

# 3 Pinning

#### 3.1 About this section

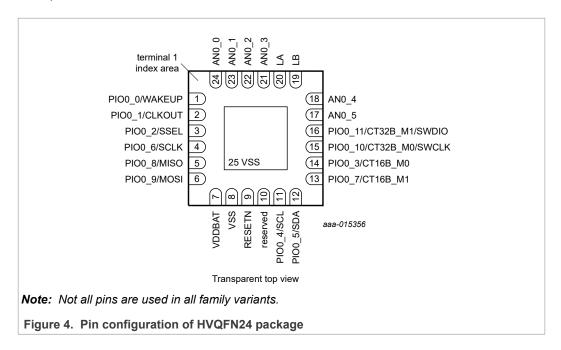

This section describes the pin layout and functions of the NHS31xx family in the HVQFN24 and WLCSP25 packages.

The pin functionality depends on the particular configuration of the chip and is customer or application dependent. Pin functions are software-assigned through the IOCON configuration registers (see <u>Section 23</u>). The pinning of the packages is shown below.

### 3.2 HVQFN24

Table 4. Pad allocation table of the HVQFN24 package

| Pad | Symbol        | Pad               | Symbol                 |

|-----|---------------|-------------------|------------------------|

| 1   | PIO0_0/WAKEUP | 13 <sup>[1]</sup> | PIO0_7/CT16B_M1        |

| 2   | PIO0_1/CLKOUT | 14 <sup>[1]</sup> | PIO0_3/CT16B_M0        |

| 3   | PIO0_2/SSEL   | 15 <sup>[1]</sup> | PIO0_10/CT32B_M0/SWCLK |

| 4   | PIO0_6/SCLK   | 16 <sup>[1]</sup> | PIO0_11/CT32B_M1/SWDIO |

| 5   | PIO0_8/MISO   | 17 <sup>[2]</sup> | AN0_5                  |

| 6   | PIO0_9/MOSI   | 18 <sup>[2]</sup> | AN0_4                  |

| 7   | VDDBAT        | 19                | LB                     |

| 8   | VSS           | 20                | LA                     |

| 9   | RESETN        | 21 <sup>[2]</sup> | AN0_3                  |

| 10  | reserved      | 22 <sup>[2]</sup> | AN0_2                  |

NHS31xx User manual

Table 4. Pad allocation table of the HVQFN24 package...continued

| Pad | Symbol     | Pad               | Symbol |

|-----|------------|-------------------|--------|

| 11  | PIO0_4/SCL | 23 <sup>[2]</sup> | AN0_1  |

| 12  | PIO0_5/SDA | 24 <sup>[2]</sup> | AN0_0  |

Table 5. Pad description of the HVQFN24 package

| Pad                       | Symbol   | Туре   | Description                                     |  |  |

|---------------------------|----------|--------|-------------------------------------------------|--|--|

| Supply                    | Supply   |        |                                                 |  |  |

| 7                         | VDDBAT   | supply | positive supply voltage                         |  |  |

| 8                         | VSS      | supply | ground                                          |  |  |

| GPIO <sup>[1]</sup>       |          |        | ,                                               |  |  |

| 1                         | PIO0_0   | I/O    | GPIO                                            |  |  |

|                           | WAKEUP   | I      | deep power-down mode wake-up pin <sup>[2]</sup> |  |  |

| 2                         | PIO0_1   | I/O    | GPIO                                            |  |  |

|                           | CLKOUT   | 0      | clock output                                    |  |  |

| 3                         | PIO0_2   | I/O    | GPIO                                            |  |  |

|                           | SSEL     | I      | SPI/SSP serial select line                      |  |  |

| 14                        | PIO0_3   | I/O    | GPIO                                            |  |  |

|                           | CT16B_M0 | 0      | 16-bit timer match output 0                     |  |  |

| 11                        | PIO0_4   | I/O    | GPIO <sup>[3]</sup>                             |  |  |

|                           | SCL      | I/O    | I <sup>2</sup> C-bus SCL clock line             |  |  |

| 12                        | PIO0_5   | I/O    | GPIO <sup>[3]</sup>                             |  |  |

| SDA I/O I <sup>2</sup> C- |          | I/O    | I <sup>2</sup> C-bus SDA data line              |  |  |

| 4                         | PIO0_6   | I/O    | GPIO                                            |  |  |

|                           | SCLK     | I/O    | SPI/SSP serial clock line                       |  |  |

| 13                        | PIO0_7   | I/O    | GPIO                                            |  |  |

|                           | CT16B_M1 | 0      | 16-bit timer match output 1                     |  |  |

| 5                         | PIO0_8   | I/O    | GPIO                                            |  |  |

|                           | MISO     | 0      | SPI/SSP master-in slave-out line                |  |  |

| 6                         | PIO0_9   | I/O    | GPIO                                            |  |  |

|                           | MOSI     | I      | SPI/SSP master-out slave-in line                |  |  |

| 15                        | PIO0_10  | I/O    | GPIO                                            |  |  |

|                           | CT32B_M0 | 0      | 32-bit timer match output 0                     |  |  |

|                           | SWCLK    | I      | ARM SWD clock                                   |  |  |

<sup>[1]</sup> High source current pads. See <u>Section 23.2.4</u>.

[2] Only used in variants with analog I/O. In other variants, they must be tied to ground.

NHS31xx User manual

Table 5. Pad description of the HVQFN24 package...continued

| Pad    | Symbol                | Type | Description                         |

|--------|-----------------------|------|-------------------------------------|

| 16     | PIO0_11               | I/O  | GPIO                                |

|        | CT32B_M1              | 0    | 32-bit timer match output 1         |

|        | SWDIO                 | I/O  | ARM SWD I/O                         |

| Analog | I/O <sup>[4][5]</sup> |      | ,                                   |

| 24     | AN0_0                 | Α    | to AN0_BUS0                         |

| 23     | AN0_1                 | Α    | to AN0_BUS1                         |

| 22     | AN0_2                 | Α    | to AN0_BUS2                         |

| 21     | AN0_3                 | Α    | to AN0_BUS3                         |

| 18     | AN0_4                 | Α    | to AN0_BUS4                         |

| 17     | AN0_5                 | Α    | to AN0_BUS5                         |

| Radio  |                       | '    | ,                                   |

| 20     | LA                    | Α    | NFC antenna/coil terminal A         |

| 19     | LB                    | Α    | NFC antenna/coil terminal B         |

| Reset  |                       |      | ,                                   |

| 9      | RESETN                | I    | external reset input <sup>[6]</sup> |

- The GPIO port is a 12-bit I/O port with individual direction and function controls for each bit. The operation of port 0 pads [1] depends on the function selected through the IOCONFIG register block.

- If external wake-up is enabled on this pad, it must be pulled HIGH before entering Deep power-down mode and pulled [2] LOW for a minimum of 100 µs to exit Deep power-down mode.

Open drain, no pull-up or pull down.

- The analog port is a 6-input analog I/O port with enable control for each pad.

- [5] Only used in variants with Analog I/O. In other variants, they must be tied to ground.

- A LOW on this pad resets the device. This reset causes I/O ports and peripherals to take on their default states, and processor execution to begin at address 0. It has weak pull-up to V<sub>BAT</sub> or internal NFC voltage (whichever is highest).

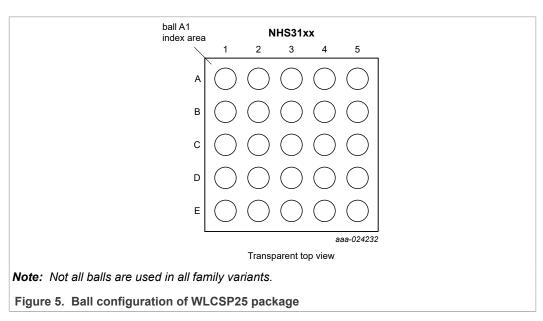

## 3.3 WLCSP25

NHS31xx User manual

Table 6. Ball allocation table of the WLCSP25 package

| Ball              | Symbol                 | Ball              | Symbol                 |

|-------------------|------------------------|-------------------|------------------------|

| A1                | VDDBAT                 | C4 <sup>[1]</sup> | PIO0_7/CT16B_M1        |

| A2                | VSS                    | C5 <sup>[1]</sup> | PIO0_11/CT32B_M1/SWDIO |

| А3                | RESETN                 | D1                | PIO0_0/WAKEUP          |

| A4                | PIO0_4/SCL             | D2                | PIO0_1/CLKOUT          |

| A5                | PIO0_5/SDA             | D3 <sup>[2]</sup> | AN0_2                  |

| B1                | PIO0_8/MISO            | D4 <sup>[2]</sup> | AN0_4                  |

| B2                | PIO0_9/MOSI            | D5 <sup>[2]</sup> | AN0_5                  |

| ВЗ                | reserved               | E1 <sup>[2]</sup> | AN0_0                  |

| B4 <sup>[1]</sup> | PIO0_3/CT16B_M0        | E2 <sup>[2]</sup> | AN0_1                  |

| B5 <sup>[1]</sup> | PIO0_10/CT32B_M0/SWCLK | E3 <sup>[2]</sup> | AN0_3                  |

| C1                | PIO0_2/SSEL            | E4                | LA                     |

| C2                | PIO0_6/SCLK            | E5                | LB                     |

| C3                | VSS                    | -                 | -                      |

Table 7. Ball description of the WLCSP25 package

| Ball                | Symbol   | Type   | Description                                      |  |

|---------------------|----------|--------|--------------------------------------------------|--|

| Supply              |          |        |                                                  |  |

| A1                  | VDDBAT   | supply | positive supply voltage                          |  |

| A2, C3              | VSS      | supply | ground                                           |  |

| GPIO <sup>[1]</sup> |          |        |                                                  |  |

| D1                  | PIO0_0   | I/O    | GPIO                                             |  |

|                     | WAKEUP   | I      | Deep power-down mode wake-up ball <sup>[2]</sup> |  |

| D2                  | PIO0_1   | I/O    | GPIO                                             |  |

|                     | CLKOUT   | 0      | clock output                                     |  |

| C1                  | PIO0_2   | I/O    | GPIO                                             |  |

|                     | SSEL     | I      | SPI/SSP serial select line                       |  |

| B4                  | PIO0_3   | I/O    | GPIO                                             |  |

|                     | CT16B_M0 | 0      | 16-bit timer match output 0                      |  |

| A4                  | PIO0_4   | I/O    | GPIO <sup>[3]</sup>                              |  |

|                     | SCL      | I/O    | I <sup>2</sup> C SCL clock line                  |  |

| A5                  | PIO0_5   | I/O    | GPIO <sup>[3]</sup>                              |  |

|                     | SDA      | I/O    | I <sup>2</sup> C-bus SDA data line               |  |

| C2                  | PIO0_6   | I/O    | GPIO                                             |  |

|                     | SCLK     | I/O    | SPI/SSP serial clock line                        |  |

<sup>[1]</sup> High source current balls. See <u>Section 23.2.4</u>.

[2] Only used in variants with Analog I/O. In other variants, they must be tied to ground.

NHS31xx User manual

Table 7. Ball description of the WLCSP25 package...continued

The GPIO port is a 12-bit I/O port with individual direction and function controls for each bit. The operation of port 0 pads [1] depends on the function selected through the IOCONFIG register block.

If external wake-up is enabled on this pad, it must be pulled HIGH before entering Deep power-down mode and pulled LOW for a minimum of 100 µs to exit Deep power-down mode.

Open drain, no pull-up or pull down.

<sup>[4]</sup> [5]

The analog port is a 6-input analog I/O port with enable control for each pad.

Only used in variants with Analog I/O. In other variants, they must be tied to ground.

A LOW on this pad resets the device. This reset causes I/O ports and peripherals to take on their default states, and processor execution to begin at address 0. It has weak pull-up to V<sub>BAT</sub> or internal NFC voltage (whichever is highest).

NHS31xx User manual

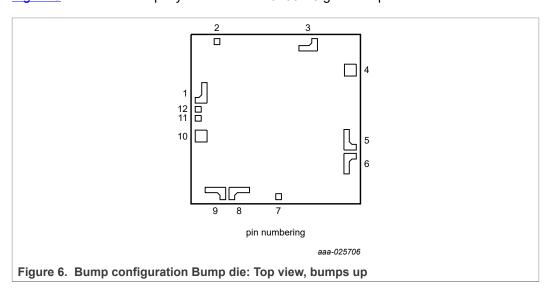

# 3.4 NHS3100W8

Figure 6 shows the bump layout of the NHS3100W8 gold bump version.

Table 8. Bump allocation table of the NHS3100W8 package

| Bump | Symbol                 | Bump | Symbol |

|------|------------------------|------|--------|

| 1    | PIO0_0/WAKEUP          | 7    | TP1    |

| 2    | TP0                    | 8    | VSS    |

| 3    | LA                     | 9    | VDDBAT |

| 4    | LB                     | 10   | PIO0_6 |

| 5    | PIO0_11/CT32B_M1/SWDIO | 11   | TP2    |

| 6    | PIO0_10/CT32B_M0/SWCLK | 12   | TP3    |

Table 9. Bump description of the NHS3100W8 package

| Bump                | Symbol   | Туре   | Description                                     |  |  |

|---------------------|----------|--------|-------------------------------------------------|--|--|

| Supply              |          |        |                                                 |  |  |

| 9                   | VDDBAT   | supply | positive supply voltage                         |  |  |

| 8                   | VSS      | supply | ground                                          |  |  |

| GPIO <sup>[1]</sup> |          |        |                                                 |  |  |

| 1                   | PIO0_0   | I/O    | GPIO                                            |  |  |

|                     | WAKEUP   | I      | Deep power-down mode wake-up pin <sup>[2]</sup> |  |  |

| 10                  | PIO0_6   | I/O    | GPIO                                            |  |  |

| 6                   | PIO0_10  | I/O    | GPIO                                            |  |  |

|                     | CT32B_M0 | 0      | 32-bit timer match output 0                     |  |  |

|                     | SWCLK    | I      | ARM SWD clock                                   |  |  |

NHS31xx User manual

Table 9. Bump description of the NHS3100W8 package...continued

| Bump     | Symbol   | Туре | Description                                     |  |

|----------|----------|------|-------------------------------------------------|--|

| 5        | PIO0_11  | I/O  | GPIO                                            |  |

|          | CT32B_M1 | 0    | 32-bit timer match output 1                     |  |

|          | SWDIO    | I/O  | ARM SWD I/O                                     |  |

| Radio    |          |      |                                                 |  |

| 3        | LA       | Α    | NFC antenna/coil terminal A                     |  |

| 4        | LB       | Α    | NFC antenna/coil terminal B                     |  |

| Test pin | is       |      |                                                 |  |

| 2        | TP0      | -    | test pin - do not connect                       |  |

| 7        | TP1      | -    | test pin - do not connect, or connect to ground |  |

| 11       | TP2      | -    | test pin - do not connect                       |  |

| 12       | TP3      | -    | test pin - do not connect                       |  |

<sup>[1]</sup> The GPIO port is a 12-bit I/O port with individual direction and function controls for each bit. The operation of port 0 balls depends on the function selected through the IOCONFIG register block.

[2] If external wake-up is enabled on this ball, it must be pulled HIGH before entering Deep power-down mode and pulled

LOW for a minimum of 100 µs to exit Deep power-down mode.

NHS31xx User manual

# 4 System configuration (SYSCON)

### 4.1 General description

The system configuration block is at APB 0x4004 8000. It controls oscillators, start logic, and clock generation of the NHS31xx. It contains registers controlling power on/off of the peripherals and a register to remap the ARM vector table to a selectable location in Flash or SRAM.

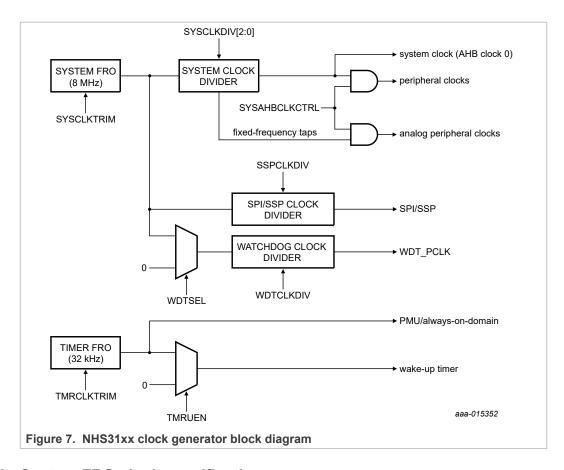

# 4.2 Clock generation

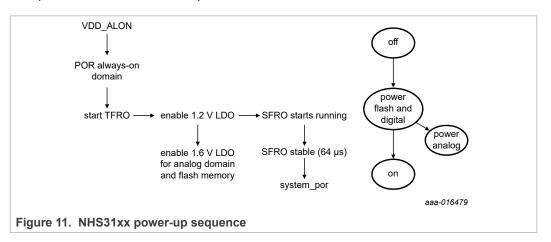

The NHS31xx clock generator unit (CGU) includes two independent RC oscillators. These oscillators are the System Free-Running Oscillator (SFRO) and the Timer Free-Running Oscillator (TFRO).

The SFRO is a current-controlled oscillator and runs at 8 MHz. The system clock is derived from it. The system clock can be set to 8 MHz, 4 MHz, 2 MHz, 1 MHz, 500 kHz, 250 kHz, 125 kHz, or 62.5 kHz with the SYSCLKCTRL system configuration register (see <u>Table 13</u>). The default system clock operating frequency is 500 kHz to minimize dynamic current consumption during the boot cycle.

Note: When the lower clock speeds are used, some features are not available.

The TFRO runs at 32.768 kHz and is the clock source for the Real-Time Clock (RTC) unit and the power management unit. The TMRCLKCTRL configuration register similarly controls it.

Following reset, the NHS31xx starts operating from the SFRO at the default 500 kHz clock frequency. The user can change the system clock frequency by setting the SYSCLKSEL. The SFRO cannot be disabled.

The SYSAHBCLKCTRL register gates the system clock to the various peripherals and memories. The SPI unit has an individual clock divider to derive the serial clock from the SFRO. The watchdog timer unit also has an individual clock divider.

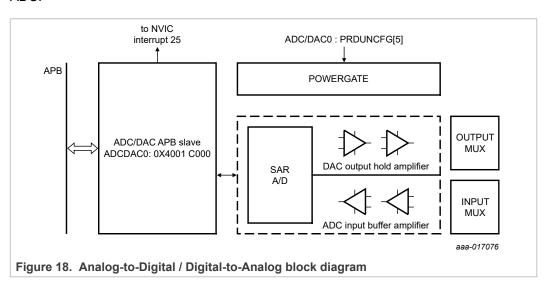

The analog parts of the analog-to-digital converters receive a fixed clock frequency, irrespective of the system clock divider settings. The digital part uses the APB clock. The analog part of the temperature sensor receives 2 MHz, the ADC/DAC receives 8 MHz, and the other peripherals 1 MHz.

NHS31xx User manual

## 4.3 System FRO clock specifications

The SFRO provides the main system clock for the NHS31xx. The system clock is enabled by default and cannot be disabled.

# 4.3.1 SFRO trimming

The 8 MHz SFRO is trimmed by setting the SYSCLKTRIM bits in the SYSCLKCTRL register. Trimming changes the internal biasing current regulating the oscillation frequency. 1 LSB of SYSCLKTRIM corresponds to approximately ±0.65 % change in oscillation frequency.

### 4.4 Timer FRO clock specifications

The TFRO provides a 32.768 kHz signal to the Real Time Clock (RTC) unit.

### 4.5 Register descriptions

All registers, regardless of size, are on addresses divisible by 4. Details of the registers appear in the description of each function.

See Section 18.5 for the flash access timing register. This register can be reconfigured as part of the system setup. Also see Section 17.4 for the EEPROM.

NHS31xx User manual

Table 10. Register overview system configuration control block - SYSCON (base address 0x4004 8000)

| Name          | Access | Address offset   | Description                                              | Reset values | Reference |

|---------------|--------|------------------|----------------------------------------------------------|--------------|-----------|

| SYSMEMREMAP   | R/W    | 0x000            | system memory remap                                      | 0x0000 0000  | Table 11  |

| PRESETCTRL    | R/W    | 0x004            | peripheral reset control                                 | 0x0000 0000  | Table 12  |

| -             | -      | 0x008 -<br>0x01C | reserved                                                 | -            | -         |

| SYSCLKCTRL    | R/W    | 0x020            | system clock control register                            | 0x0002 0008  | Table 13  |

| SYSCLKUEN     | R/W    | 0x024            | system clock update enable                               | 0x0000 0000  | Table 15  |

| -             | -      | 0x028 -<br>0x02C | reserved                                                 | -            | -         |

| SYSRSTSTAT    | R/W    | 0x030            | system reset status register                             | 0x0000 0000  | Table 16  |

| -             | -      | 0x034 -<br>0x078 | reserved                                                 | -            | -         |

| SYSAHBCLKCTRL | R/W    | 0x080            | AHB clock control                                        | 0x0001 C007  | Table 17  |

| -             | -      | 0x084 -<br>0x090 | reserved                                                 | -            | -         |

| SSPCLKDIV     | R/W    | 0x094            | SPI/SSP clock divider                                    | 0x0000 0000  | Table 18  |

| -             | -      | 0x098 -<br>0x0CC | reserved                                                 | -            | -         |

| WDTCLKSEL     | R/W    | 0x0D0            | watchdog timer clock selector                            | 0x0000 0000  | Table 19  |

| WDTCLKUEN     | R/W    | 0x0D4            | watchdog timer clock update enable                       | 0x0000 00000 | Table 20  |

| WDTCLKDIV     | R/W    | 0x0D8            | watchdog timer clock divider                             | 0x0000 0000  | Table 21  |

| -             | -      | 0x0DC -<br>0x0E4 | reserved                                                 | -            | -         |

| CLKOUTEN      | R/W    | 0x0E8            | CLKOUT enable                                            | 0x0000 0000  | Table 22  |

| -             | -      | 0x0EC -<br>0x150 | reserved                                                 | -            | -         |

| SYSTCKCAL     | R/W    | 0x154            | system tick counter calibration                          | 0x0000 0004  | Table 23  |

| -             | -      | 0x210 -<br>0X230 | reserved                                                 | -            | -         |

| STARTAPRP0    | R/W    | 0x200            | start logic edge control register 0                      | 0x0000 0000  | Table 24  |

| STARTERP0     | R/W    | 0x204            | start logic signal enable register 0                     | 0x0000 0000  | Table 25  |

| STARTRSRP0CLR | R/W    | 0x204            | start logic reset register 0                             | 0x0000 0000  | Table 26  |

| STARTSRP0     | R      | 0x20C            | start logic status register 0                            | 0x0000 0000  | Table 27  |

| -             | -      | 0x210 -<br>0X230 | reserved                                                 | -            | -         |

| PDAWAKECFG    | R/W    | 0x234            | Flash address mapping after wake-up from Deep-sleep mode | 0x0000 0000  | Table 28  |

| PDRUNCFG      | R/W    | 0x238            | power-down configuration register                        | 0x0000 003E  | Table 29  |

| -             | -      | 0x23C -<br>0x3EC | reserved                                                 | -            | -         |

NHS31xx User manual

Table 10. Register overview system configuration control block - SYSCON (base address 0x4004 8000)...continued

|           |        | •              | <u> </u>    | ,            |           |

|-----------|--------|----------------|-------------|--------------|-----------|

| Name      | Access | Address offset | Description | Reset values | Reference |

| DEVICE_ID | R      | 0x3F4          | -           | -            | Table 30  |

### 4.5.1 System memory remap register (SYSMEMREMAP)

The system memory remap register contains the addresses of the ARM interrupt vectors. Valid addresses are on 1024-byte boundaries in Flash or SRAM. The first 192 addresses (0 to 191) are remapped to the locations indicated below.

Table 11. SYSMEMREMAP register (address 0x4004 8000) bit description

| Bit        | Symbol | Description                                                   | Description                                                   |        |

|------------|--------|---------------------------------------------------------------|---------------------------------------------------------------|--------|

| 0 map      |        | interrupt v                                                   | ector remap                                                   | 0      |

|            |        | 0                                                             | interrupt vectors reside in Flash                             |        |

|            |        | 1                                                             | interrupt vectors reside in SRAM                              |        |

| 5:1 offset |        | system me                                                     | emory remap offset                                            | 00000b |

|            | 00000b | interrupt vectors in flash or remapped to SRAM but not offset |                                                               |        |

|            |        | 00001b -<br>00111b                                            | interrupt vectors offset in flash or SRAM to 1 K word segment |        |

|            |        | 01000b -<br>11111b                                            | interrupt vectors offset in flash to 1 K word segment 8 to 31 |        |

| 31:6       | -      | reserved                                                      |                                                               | 0      |

### 4.5.2 Peripheral reset control register (PRESETCTRL)

This register allows software to reset some peripherals. Writing a logic 0 to the bits resets the corresponding peripheral. Writing a logic 1 de-asserts the reset.

**Note:** Before accessing the SPI and  $I^2$ C peripherals, write a logic 1 to this register. This action ensures that the reset signals to the SPI and  $I^2$ C are de-asserted.

Table 12. PRESETCTRL register (address 0x4004 8004) bit description

| Bit | Symbol    | Descrip              | tion                                       | After boot |

|-----|-----------|----------------------|--------------------------------------------|------------|

| 0   | SSP_RST_N | SPI/SSF              | reset control                              | 0          |

|     |           | 0                    | resets the SPI peripheral                  |            |

|     |           | 1                    | SPI reset de-asserted                      |            |

| 1   | I2C_RST_N | I <sup>2</sup> C-bus | reset control                              | 0          |

|     |           | 0                    | resets the I <sup>2</sup> C-bus peripheral |            |

|     |           | 1                    | I <sup>2</sup> C-bus reset de-asserted     |            |

| 2   | EE_RST_N  | EEPRO                | M NVMC reset control                       | 1          |

|     |           | 0                    | resets the EEPROM NVMC controller          |            |

|     |           | 1                    | reset de-asserted                          |            |

NHS31xx User manual

Table 12. PRESETCTRL register (address 0x4004 8004) bit description...continued

| Bit  | Symbol    | Descri  | escription                     |  |  |

|------|-----------|---------|--------------------------------|--|--|

| 3    | NFC_RST_N | NFC sh  | FC shared memory reset control |  |  |

|      |           | 0       | resets the NFC shared memory   |  |  |

|      |           | 1       | reset de-asserted              |  |  |

| 31:4 | -         | reserve | eserved                        |  |  |

# 4.5.3 System clock control register (SYSCLKCTRL)

The system clock control register controls the analog part of the internal 8 MHz oscillator as well as the system clock divider.

For changes to the system clock divider to take effect, first write a logic 0 to the SYSCLKUEN register, then write a logic 1 to SYSCLKUEN.

Table 13. SYSCLKCTRL register (address 0x4004 8020) bit description

| Bit           | Symbol     | Descri                                       | Description                                  |   |

|---------------|------------|----------------------------------------------|----------------------------------------------|---|

| 0             | -          | reserve                                      | reserved. Do not write to this bit.          |   |

| 3:1 SYSCLKDIV | system     | ı clock divider                              | 100b                                         |   |

|               |            | 000b                                         | no division (system clock set to 8 MHz)      |   |

|               |            | 001b divide-by-2 (system clock set to 4 MHz) |                                              |   |

|               |            | 010b                                         | divide-by-4 (system clock set to 2 MHz)      |   |

|               |            | 011b                                         | divide-by-8 (system clock set to 1 MHz)      |   |

|               |            | 100b                                         | divide-by-16 (system clock set to 500 kHz)   |   |

|               |            | 101b                                         | divide-by-32 (system clock set to 250 kHz)   |   |

|               |            | 110b                                         | divide-by-64 (system clock set to 125 kHz)   |   |

|               |            | 111b                                         | divide-by-128 (system clock set to 62.5 kHz) |   |

| 15:4          | -          | reserve                                      | ed                                           | - |

| 21:16         | SYSCLKTRIM | SFRO                                         | SFRO trim value (6-bit)                      |   |

| 31:22         | -          | reserve                                      | ed                                           | - |

<u>Table 14</u> shows the impact on the system of the clock frequency choices.

NHS31xx User manual

Table 14. Impact of different clock frequency settings

| Setting | Frequency | Impact on sy         | ystem behavior                                                                |

|---------|-----------|----------------------|-------------------------------------------------------------------------------|

| 000b    | 8 MHz     | I <sup>2</sup> C-bus | Standard and Fast mode possible                                               |

|         |           | flash                | LPM requires 1 additional wait state, no wait state needed in High-power mode |

|         |           | EEPROM               | EECLKDIV = 21                                                                 |

| 001b    | 4 MHz     | I <sup>2</sup> C-bus | Standard mode only                                                            |

|         |           | flash                | no wait-states needed                                                         |

|         |           | EEPROM               | EECLKDIV = 10                                                                 |

| 010b    | 2 MHz     | I <sup>2</sup> C-bus | Standard mode only                                                            |

|         |           | flash                | no wait-states needed                                                         |

|         |           | EEPROM               | EECLKDIV = 5                                                                  |

| 011b    | 1 MHz     | I <sup>2</sup> C-bus | Standard mode only                                                            |

|         |           | flash                | no wait-states needed                                                         |

|         |           | EEPROM               | EECLKDIV = 2                                                                  |

| 100b    | 500 kHz   | I <sup>2</sup> C-bus | not supported                                                                 |

|         |           | flash                | no wait-states needed                                                         |

|         |           | EEPROM               | EECLKDIV = 1                                                                  |

| 101b    | 250 kHz   | I <sup>2</sup> C-bus | not supported                                                                 |

|         |           | flash                | no wait-states needed                                                         |

|         |           | EEPROM               | program/erase not supported                                                   |

| 110b    | 125 kHz   | I <sup>2</sup> C-bus | not supported                                                                 |

|         |           | flash                | no wait-states needed                                                         |

|         |           | EEPROM               | program/erase not supported                                                   |

| 111b    | 62.5 kHz  | I <sup>2</sup> C-bus | not supported                                                                 |

|         |           | flash                | no wait-states needed                                                         |

|         |           | EEPROM               | program/erase not supported                                                   |

# 4.5.4 System clock update enable register (SYSCLKUEN)

This register updates the clock source of the system with the new input clock after the SYSCLKCTRL register has been written to. For the update to take effect, first write a logic 0 to the SYSCLKUEN register and then write a logic 1 to SYSCLKUEN.

Table 15. SYSCLKUEN register (address 0x4004 8024) bit description

| Bit  | Symbol | Description                       |                                       | Reset value |

|------|--------|-----------------------------------|---------------------------------------|-------------|

| 0    | ENA    | enable system clock source update |                                       | 0           |

|      |        | 0                                 | no update                             |             |

|      |        | 1                                 | update clock source and clock divisor |             |

| 31:1 | -      | reserved                          |                                       | 0           |

UM10876

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved.

NHS31xx User manual

# 4.5.5 System reset status register (SYSRSTSTAT)

The SYSRSTSTAT register shows the source of the latest reset event. The bits are cleared by writing a value to the register. The POR event clears all other bits in this register. However, if another reset signal - for example EXTRST - remains asserted after the POR signal is negated, then its bit is set to detected.

Table 16. SYSRSTSTAT register (address 0x4004 8030) bit description

| Bit  | Symbol             | Description                                                                  |                            | Reset value |

|------|--------------------|------------------------------------------------------------------------------|----------------------------|-------------|

| 0    | POR [1]            | POR reset statu                                                              | s                          | 0           |

|      |                    | 0                                                                            | no POR detected            |             |

|      |                    | 1                                                                            | POR detected               |             |

| 1    | EXTRST [1]         | status of externa                                                            | al RESETN pin              | 0           |

|      |                    | 0                                                                            | no RESETN event detected   |             |

|      |                    | 1                                                                            | external reset detected    |             |

| 2    | WDT <sup>[2]</sup> | status of the Watchdog reset                                                 |                            | 0           |

|      |                    | 0                                                                            | no WDT reset detected      |             |

|      |                    | 1                                                                            | WDT reset detected         |             |

| 3    | SYSRST [3]         | status of software system reset (ARM AIRCR register SYSRESETREQ bit was set) |                            | 0           |

|      |                    | 0                                                                            | no software reset detected |             |

|      |                    | 1                                                                            | software reset detected    |             |

| 31:4 | -                  | reserved                                                                     |                            | -           |

POR and EXTRST trigger full system reset.

If the debugger is not active, then WDT triggers full system reset.

SYSRST triggers a reset of the ARM core (the peripheral registers are not reset).

NHS31xx User manual

# 4.5.6 AHB clock control register

The SYSAHBCLKCTRL register enables the clocks to individual system and peripheral blocks. The system clock provides the clock for the AHB to APB bridge, the AHB matrix, the ARM Cortex-M0+, the SYSCON block, and the PMU. This clock cannot be disabled.

Table 17. SYSAHBCLKCTRL register (address 0x4004 8080) bit description

| Bit | Symbol                   | Description                                                                             | Reset value         |

|-----|--------------------------|-----------------------------------------------------------------------------------------|---------------------|

| 0   | -                        | reserved                                                                                | 1                   |

| 1   | -                        | reserved                                                                                | -                   |

| 2   | RAM                      | enable clock for RAM                                                                    | 1                   |

|     |                          | 0 disable                                                                               |                     |

|     |                          | 1 enable                                                                                |                     |

| 4:3 | FLASHREG /<br>FLASHARRAY | enable clock for Flash register interface and ar                                        | rray access 0b11    |

|     |                          | 0b00 disable                                                                            |                     |

|     |                          | 0b01 enable                                                                             |                     |

|     |                          | 0b10 enable                                                                             |                     |

|     |                          | 0b11 enable                                                                             |                     |

| 5   | I2C                      | enable clock for I <sup>2</sup> C-bus                                                   | 0                   |

|     |                          | 0 disable                                                                               |                     |

|     | 1 enable                 |                                                                                         |                     |

| 6   | GPIO                     | enable clock for GPIO                                                                   | 0                   |

|     |                          | 0 disable                                                                               |                     |

|     |                          | 1 enable                                                                                |                     |

| 7   | SPISSP                   | enable clock for SPI/SSP                                                                | 0                   |

|     |                          | 0 disable                                                                               |                     |

|     |                          | 1 enable                                                                                |                     |

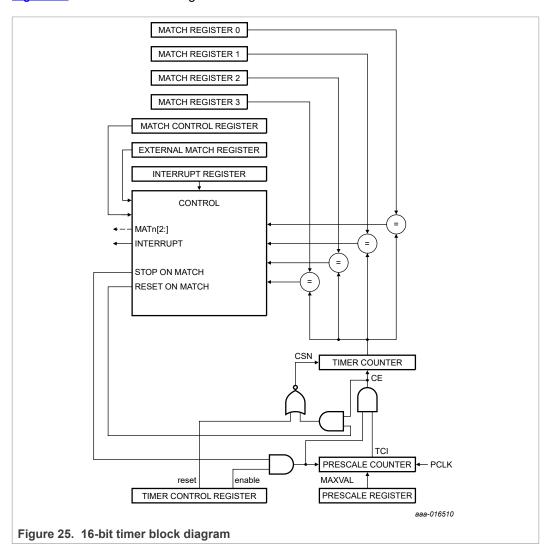

| 8   | CT16B                    | enable clock for 16-bit timer                                                           | 0                   |

|     |                          | 0 disable                                                                               |                     |

|     |                          | 1 enable                                                                                |                     |

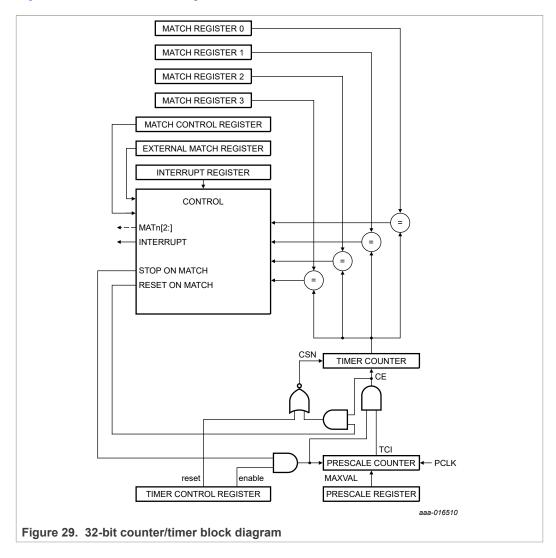

| 9   | CT32B                    | enable clock for 32-bit timer                                                           | 0                   |

|     |                          | 0 disable                                                                               |                     |

|     |                          | 1 enable                                                                                |                     |

| 10  | RTC                      | enable clock for RTC (APB side only, TFRO ditimer unit, as set by TMRCLKCTRL register). | rectly clocks the 0 |

|     |                          | 0 disable                                                                               |                     |

|     |                          | 1 enable                                                                                |                     |

| 11  | WDT                      | enable clock for watchdog timer                                                         | 0                   |

|     |                          | 0 disable                                                                               |                     |

|     |                          | 1 enable                                                                                |                     |

NHS31xx User manual

Table 17. SYSAHBCLKCTRL register (address 0x4004 8080) bit description ...continued

| Bit   | Symbol  | Descrip                                  | Description                                          |      |

|-------|---------|------------------------------------------|------------------------------------------------------|------|

| 12    | TSEN    | enable clock for temperature sensor      |                                                      | 0    |

|       |         | 0                                        | disable                                              |      |

|       |         | 1                                        | enable                                               |      |

| 13    | -       | reserved                                 | d                                                    |      |

| 14    | -       | reserved                                 | d                                                    |      |

| 15    | I2D     | enable o                                 | clock for Current-to-Digital converter               | 0    |

|       |         | 0                                        | disable                                              | 0    |

|       |         | 1                                        | enable                                               |      |

| 16    | ADC/DAC | enable clock for ADC/DAC converter       |                                                      | 0    |

|       |         | 0                                        | disable                                              |      |

|       |         | 1                                        | enable                                               |      |

| 17    | -       | reserved                                 | d                                                    |      |

| 18    | IOCON   | enable clock for I/O configuration block |                                                      | 1    |

|       |         | 0                                        | disable                                              |      |

|       |         | 1                                        | enable                                               |      |

| 20:19 |         | enable o                                 | clock for EEPROM register interface and array access | 0b11 |

|       | EEARRAY | 0b00                                     | disable                                              |      |

|       |         | 0b01                                     | enable                                               |      |

|       |         | 0b10                                     | enable                                               |      |

|       |         | 0b11                                     | enable                                               |      |

| 31:21 | -       | reserved                                 | t                                                    | 0    |

### 4.5.7 SPI/SSP clock divider control register (SSPCLKDIV)

This register configures the SPI peripheral clock SPI\_PCLK. The SPI\_PCLK can be shut down by setting the DIV bits to logic 0.

Table 18. SSPCLKDIV register (address 0x4004 8094) bit description

| Bit  | Symbol | Value | Description                                                                                       | Reset value |

|------|--------|-------|---------------------------------------------------------------------------------------------------|-------------|

| 7:0  | DIV    | -     | SPI_CLK clock divider values: (0) disable, (1) equal to SFRO frequency (even 2-254) divide-by-DIV | 0           |

| 31:8 | -      | -     | reserved                                                                                          | 0           |

# 4.5.8 Watchdog timer clock source selection register (WDTCLKSEL)

This register selects the clock source for the watchdog timer. The WDTCLKUEN register must be toggled from logic 0 to logic 1 for the update to take effect.

NHS31xx User manual

Table 19. WDTCLKSEL register (address 0x4004 80D0) bit description

| Bit  | Symbol  | Descri  | ption       | Reset value |

|------|---------|---------|-------------|-------------|

| 1:0  | 1:0 SEL | WDT o   | lock source | 0           |

|      |         | 0x0     | system FRO  |             |

|      |         | 0x1     | reserved    |             |

|      |         | 0x2     | disabled    |             |

|      |         | 0x3     | reserved    |             |

| 31:2 | -       | reserve | eserved     |             |

# 4.5.9 Watchdog timer clock update enable register (WDTCLKUEN)

This register updates the clock source of the watchdog timer with the new input source after the WDTCLKSEL register has been written to. For the update to take effect at the input of the watchdog timer, the following procedure must be applied:

- 1. Write a logic 0 to the WDTCLKUEN register

- 2. Write a logic 1 to WDTCLKUEN to preset the value

- 3. Write a logic 0 again to apply the value

The 0-1-0 pulse length should be longer than the period of the actual and selected clock sources.

Table 20. WDTCLKUEN register (address 0x4004 80D4) bit description

| Bit  | Symbol | Desc   | escription                |   |

|------|--------|--------|---------------------------|---|

| 0    | ENA    | enabl  | e WDT clock source update | 0 |

|      |        | 0      | no update                 |   |

|      |        | 1      | update clock source       |   |

| 31:1 | -      | reserv | ved                       | 0 |

# 4.5.10 Watchdog timer clock divider register (WDTCLKDIV)

This register determines the divider values for the watchdog clock wdt\_clk. For the update to take effect at the input of the watchdog timer, a 1-0-1 sequence has to be written to register WDTCLKEN (see <u>Section 4.5.9</u>).

When the division factor is set to 0, the WDT\_CLK is disabled. Apart from 1, only even division factors can be used.

Table 21. WDTCLKDIV register (address 0x4004 80D8) bit description

| Bit  | Symbol | Value | Description                                                                                            | Reset value |  |

|------|--------|-------|--------------------------------------------------------------------------------------------------------|-------------|--|

| 7:0  | DIV    | 1     | WDT clock divider values: (0) disable WDT_PCLK, (1) equal to SFRO frequency (even 2-254) divide-by-DIV | 0           |  |

| 31:8 | -      | -     | reserved                                                                                               | 0           |  |

NHS31xx User manual

# 4.5.11 Clock output enable register (CLKOUTEN)

This register enables output of the different clocks to the CLKOUT pin.

Table 22. CLKOUTEN register (address 0x4004 80E8) bit description

| Bit  | Symbol    | Value | Description                                 | Reset value |

|------|-----------|-------|---------------------------------------------|-------------|

| 0    | CLKOUTEN  | 0     | disable output                              | 0           |

|      |           | 1     | enable output                               |             |

| 2:1  | CLKOUTSRC | 00b   | output SFRO (8 MHz)                         | 0           |

|      |           | 01b   | output system clock (62.5 kHz to 8ηMHz)     |             |

|      |           | 10b   | output TFRO (32 kHz)                        |             |

|      |           | 11b   | output NFC clock (1.695 MHz) <sup>[1]</sup> |             |

| 31:3 | -         | -     | reserved                                    | 0           |

<sup>[1]</sup> The NFC clock is only available if a 13.56 MHz signal is seen at the LA/LB inputs.

### 4.5.12 System tick counter calibration register (SYSTCKCAL)

This register determines the value of the SYST\_CALIB register.

Table 23. SYSTCKCAL register (address 0x4004 8154) bit description

| Bit  | Symbol | Value | Description                         | Reset value |

|------|--------|-------|-------------------------------------|-------------|

| 25:0 | CAL    | 1     | system tick timer calibration value | 26'h0004    |

| 31:8 | -      | -     | reserved                            | 0           |

# 4.5.13 Start logic edge control register 0 (STARTAPRP0)

The STARTAPRP0 register controls the start logic inputs of the digital PIO ports (PIO0\_0 to PIO0\_10). This register selects a falling or rising edge on the corresponding PIO0 input trigger the start logic.

Every bit in the STARTAPRP0 register controls one port input and is connected to one wake-up interrupt in the NVIC. Bit 0 in the STARTAPRP0 register corresponds to interrupt 0, bit 1 to interrupt 1, etc. (see Table 274), up to a total of 11 interrupts.

Table 24. STARTAPRP0 register (address 0x4004 8200) bit description

| Bit   | Symbol   | Descripti | Description                                                  |   |  |  |

|-------|----------|-----------|--------------------------------------------------------------|---|--|--|

| 10:0  | APRPIO_n | edge sele | edge select for start logic input PIO0_n (PIO0_10 to PIO0_0) |   |  |  |

|       |          | 0         | falling edge (per bit)                                       |   |  |  |

|       |          | 1         | rising edge                                                  |   |  |  |

| 31:11 | -        | reserved  |                                                              | 0 |  |  |

NHS31xx User manual

# 4.5.14 Start logic signal enable register 0 (STARTERP0)

The STARTERP0 register enables or disables the start signal bits in the start logic. The bit assignment for bits 10:0 is identical to <u>Table 24</u>. Bit 11 enables start on RFID, bit 12 enables start on wake-up timer.

Table 25. STARTERP0 register (address 0x4004 8204) bit description

| Bit          | Symbol | Desci                                                                | Description                                    |                                           |   |

|--------------|--------|----------------------------------------------------------------------|------------------------------------------------|-------------------------------------------|---|

| 10:0 ERPIO_n |        | enable start signal for start logic input PIO0_n (PIO0_10 to PIO0_0) |                                                |                                           |   |

|              |        | 0                                                                    | disabled                                       |                                           |   |

|              |        | 1                                                                    | enabled                                        |                                           |   |

| 11           | ERRFID | ERRFID                                                               | enable                                         | e start signal for start logic input RFID | 0 |

|              |        | 0                                                                    | disabled                                       |                                           |   |

|              |        | 1                                                                    | enabled                                        |                                           |   |

| 12           | ERTMR  | enable                                                               | e start signal for start logic input RTC timer | 0                                         |   |

|              |        | 0                                                                    | disabled                                       |                                           |   |

|              |        | 1                                                                    | enabled                                        |                                           |   |

| 31:13        | -      | reserv                                                               | ved .                                          | 0                                         |   |

# 4.5.15 Start logic reset register 0 (STARTRSRP0CLR)

Writing a one to a bit in the STARTRSRP0CLR register resets the start logic state. The bit assignment is identical to <u>Table 25</u>. The start-up logic uses the input signals to generate a clock edge for registering a start signal. This clock edge (falling or rising) sets the interrupt for waking up from Deep-sleep mode. Writing a value to the registers clears the conditions. After writing a logic 1 to the register, write a logic 0 to it to clear the list again.

Table 26. STARTRSRP0CLR register (address 0x4004 8208) bit description

| Bit           | Symbol           | Descript                                      | escription                                        |   |

|---------------|------------------|-----------------------------------------------|---------------------------------------------------|---|

| 10:0 RSRPIO_n |                  | start sign<br>PIO0_0)                         | al reset for start logic input PIO0_x (PIO0_10 to | 0 |

|               |                  | 0                                             | do nothing                                        |   |

|               |                  | 1                                             | writing logic 1 resets the start signal           |   |

| 11            | RSRRFID          | start signal reset for start Logic input RFID |                                                   | 0 |

|               |                  | 0                                             | do nothing                                        |   |

|               |                  | 1                                             | writing logic 1 resets the start signal           |   |

| 12            | RSRTMR start sig | start sign                                    | al reset for start logic input wake-up timer      | 0 |

|               |                  | 0 do n                                        | do nothing                                        |   |

|               |                  | 1                                             | writing logic 1 resets the start signal           |   |

| 31:13         | -                | reserved                                      |                                                   | 0 |

NHS31xx User manual

# 4.5.16 Start logic status register 0 (STARTSRP0)

This register reflects the status of the enabled start signal bits. Each bit (if enabled) reflects the state of the start logic, i.e. whether a wake-up signal has been received for a given pin or not.

Table 27. STARTSRP0 register (address 0x4004 820C) bit description

| Bit          | Symbol | Descrip                                        | escription                                          |   |

|--------------|--------|------------------------------------------------|-----------------------------------------------------|---|

| 10:0 SRPIO_n |        | start sigr<br>PIO0_0)                          | nal status for start logic input PIO0_n (PIO0_10 to | 0 |

|              |        | 0                                              | no start signal received                            | _ |

|              |        | 1                                              | start signal received                               |   |

| 11           | SRRFID | start signal status for start logic input RFID |                                                     | 0 |

|              |        | 0                                              | no start signal received                            |   |

|              |        | 1                                              | start signal received                               |   |

| 12           | SRTMR  | start sigr                                     | nal status for start logic input wake-up timer      | 0 |

|              |        | 0                                              | no start signal received                            |   |

|              |        | 1                                              | start signal received                               |   |

| 31:13        | -      | reserved                                       |                                                     | 0 |

### 4.5.17 Wake-up configuration register (PDAWAKECFG)

The FLASH\_PD bit in this register, PDAWAKECFG, enables an address remap of the flash addresses to SRAM addresses after exiting from Deep-sleep mode.

When the bit is set before going in Deep-sleep mode, all the flash addresses are remapped to SRAM addresses, when the chip leaves Deep-sleep mode. All the flash addresses are remapped, not only the interrupt vector table. The remapping is independent of the FLASH\_PD bit in the PDRUNCFG register. In other words, the remapping is active whether the flash is powered down or not.

The remapping becomes only active when the chip goes in Deep-sleep mode. The remapping continues until the FLASH\_PD bit in this register is cleared.

If the user chooses to enable this feature, the interrupt vector table and the program code must be copied to SRAM. The SRAM content is preserved during Deep-sleep mode.

Table 28. PDAWAKECFG register (address 0x4004 8234) bit description

| Bit        | Symbol | Descripti | Description                                                               |   |

|------------|--------|-----------|---------------------------------------------------------------------------|---|

| 0 FLASH_PD |        | Flash add | resses remapped to SRAM after Deep-sleep mode                             | 0 |

|            |        | 0         | no flash address remapping after Deep-sleep mode (Flash must be powered)  |   |

|            |        | 1         | Flash address remapping after Deep-sleep mode (Flash can be powered down) |   |

| 31:1       | -      | reserved  |                                                                           | 0 |

NHS31xx User manual

# 4.5.18 Power-down configuration register (PDRUNCFG)

The bits in the PDRUNCFG register control the power to the various analog blocks. This register can be written to at any time while the chip is powered, and a write takes effect immediately. By default, the Flash memory is running. Before switching off power to Flash memory, the user must ensure the interrupt vector table points to SRAM, and the relevant program code resides in SRAM.

Table 29. PDRUNCFG register (address 0x4004 8238) bit description

| Bit  | Symbol    | Description                             |              | Reset value |  |

|------|-----------|-----------------------------------------|--------------|-------------|--|

| 0    | FLASH_PD  | flash power down                        |              | 0           |  |

|      |           | 0                                       | powered      |             |  |

|      |           | 1                                       | powered down |             |  |

| 1    | TSEN_PD   | temperature sensor power down           |              | 1           |  |

|      |           | 0                                       | powered      |             |  |

|      |           | 1                                       | powered down |             |  |

| 2    | -         | reserved                                |              |             |  |

| 3    | EEPROM_PD | EEPROM power down                       |              | 1           |  |

|      |           | 0                                       | powered      |             |  |

|      |           | 1                                       | powered down |             |  |

| 4    | I2D       | current-to-digital converter power down |              | 1           |  |

|      |           | 0                                       | powered      |             |  |

|      |           | 1                                       | powered down |             |  |

| 5    | ADCDAC    | ADC/DAC converter power down            |              | 1           |  |

|      |           | 0                                       | powered      |             |  |

|      |           | 1                                       | powered down |             |  |

| 31:6 | -         | reserved                                | I            | 0           |  |

NHS31xx User manual

# 4.5.19 Device ID register (DEVICE\_ID)

This device ID register is a read-only register and contains the part ID of the chip (NHS3100, NHS3152...). The value of this register is copied from EEPROM as part of device boot (firmware).

Table 30. DEVICE\_ID register (address 0x4004 83F4) bit description

| Bit  | Symbol   | Value | Description                      | After boot       |

|------|----------|-------|----------------------------------|------------------|

| 31:0 | DEVICEID | -     | part ID number for NHS31xx model | device dependent |

#### Table 31. Device IDs

| Type number  | Device ID  |

|--------------|------------|

| NHS3100/A1   | 0x4E310020 |

| NHS3100UK/A1 |            |

| NHS3100W8/A1 |            |

| NHS3152/A1   | 0x4E315220 |

| NHS3152UK/A1 |            |

NHS31xx User manual

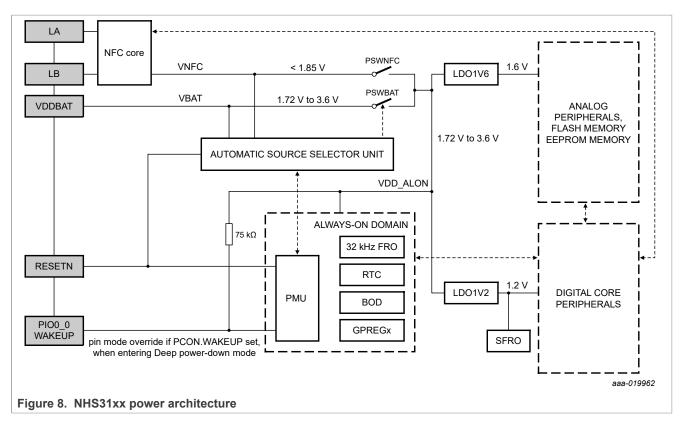

# 5 Power management unit (PMU)

#### 5.1 About this section

This section describes the power management unit (PMU) which controls the switching between available power sources.

### 5.2 General description

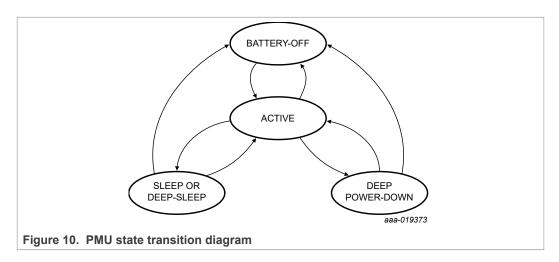

The PMU controls four power modes:

- Active

- Sleep

- Deep-sleep

- · Deep power-down

Additionally, the chip can be put into the Battery-off mode, which reduces current to nA levels. However, this mode can only be left via the RESETN pin or an NFC signal.

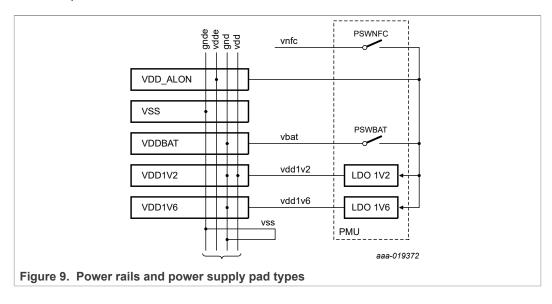

The IC power controller controls power flow from the NFC domain or the external domain to the internal domains; the PMU controls the power regulators.

### 5.3 Functional description

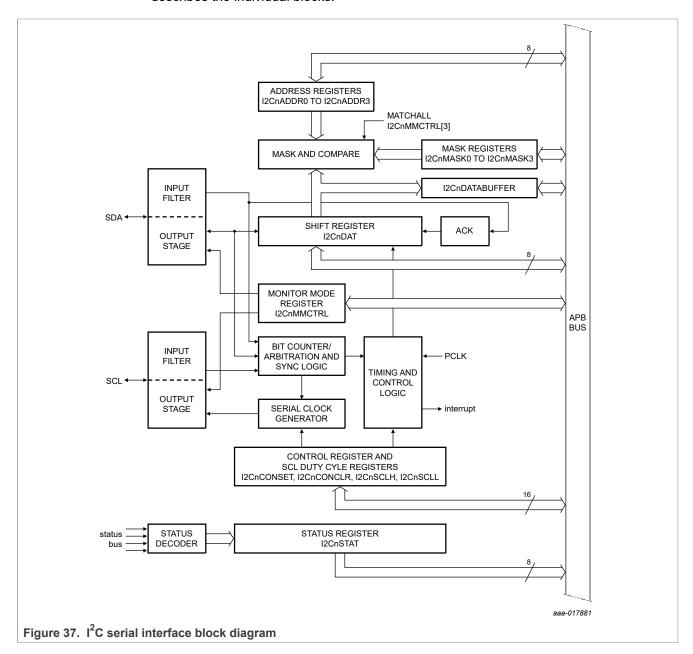

The NHS31xx supports various power control features. In Active mode, when the chip is running, power and clocks to selected peripherals can be optimized for power consumption. In addition, there are three special modes of processor power reduction: Sleep mode, Deep-sleep mode, and Deep power-down mode.