# **SJA1105P/Q/R/S**

# 5-port automotive Ethernet switch

Rev. 2 — 1 March 2024

Product data sheet

# 1 General description

The SJA1105P/Q/R/S safe and secure automotive gigabit Ethernet switch family extends the capabilities of the SJA1105/SJA1105T [1] switches with improved security-related features, extended interface options, and ISO 26262 ASIL-A compliance.

The SJA1105P/Q/R/S is a 5-port automotive Ethernet switch supporting IEEE Audio Video Bridging (AVB) and Time-Sensitive Networking (TSN) standards. Each of the five ports can be individually configured to operate at 10/100/1000 Mbit/s. This feature provides the flexibility to connect any Fast/Gigabit/optical PHY or MCU/MPU to any of the ports. Examples of external PHYs are the TJA1101, TJA1102 and TJA1103/4 100BASE-T1 PHYs and the TJA1120/21 1000BASE-T1 PHYs from NXP Semiconductors ([2] and [3]).

The new frame allow/denylisting, port-reachability and address learning restriction features, available on all SJA1105P/Q/R/S variants, improve switch security by limiting data processing to known frames and data sources and preventing the forwarding of erroneous or malicious data.

The MII/RMII/RGMII interfaces offer extended IO voltages such as 1V8 and 3V3 RGMII. Furthermore, the SGMII interface available on the /R and /S variants extends the connectivity options of the switch. The /P and /Q variants do not feature an SGMII port and remain 100 % pin-compatible with the SJA1105/SJA1105T switches.

The SJA1105P/Q/R/S switch family was developed according to the ISO 26262 standard. ASIL-A compliance reduces the safety-critical ECU design load. Additional documentation, including a safety manual, is available on request.

The switches are compatible with the IEEE AVB standard. The /Q and /S variants support extended TSN features such as 802.1Qbv. NXP-original AUTOSAR drivers and AVB SW stack are available for this series.

#### 2 Features and benefits

#### 2.1 General features

- · 5-port store and forward architecture

- Each port individually configurable for 10/100 Mbit/s when operated as MII/RMII and 10/100/1000 Mbit/s when operated as RGMII or SGMII

- Independent I/O voltage domains: selectable 1.8/2.5/3.3 V operation for MII/RMII/RGMII; selectable 1.8/2.5/3.3 V for host interfacing; 1.2 V core voltage domains

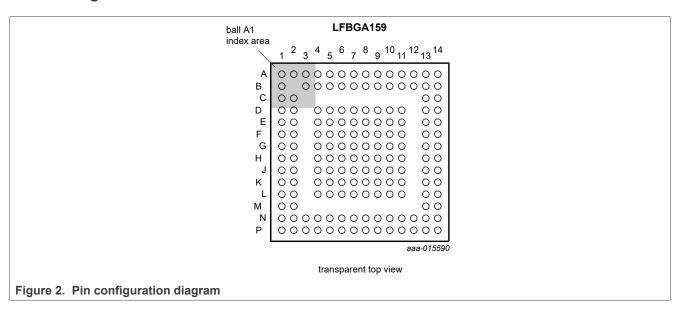

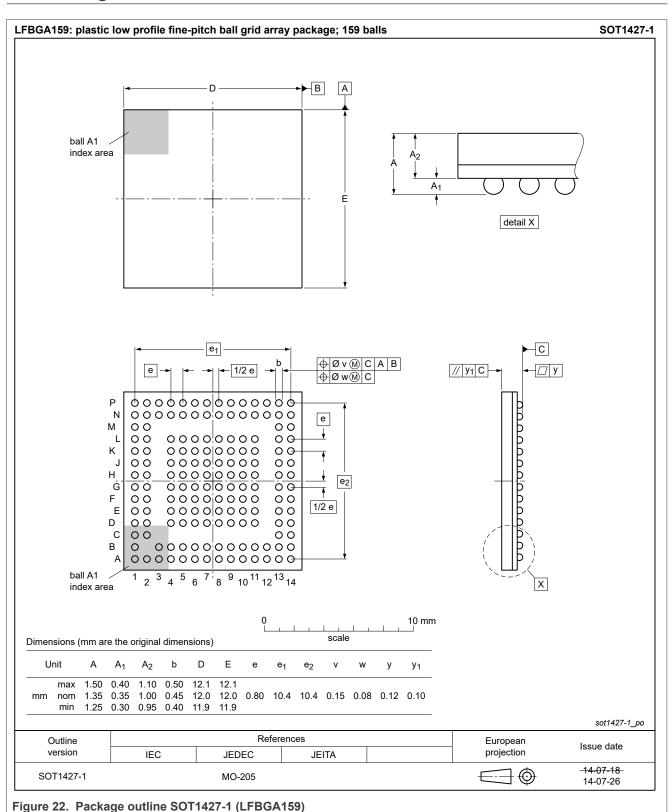

- Small footprint: LFBGA159 (12 mm × 12 mm) package

- Automotive Grade 2 ambient operating temperature: -40 °C to +105 °C

- Automotive product qualification in accordance with AEC-Q100 Rev-H

- ISO-26262, ASIL-A

# 2.2 Ethernet switching and AVB features

- IEEE 802.3 compliant

- · 128 kB frame buffer

- 1024 entry TCAM for collision-free MAC address learning

- · 2 kB frame length handling

- · IEEE 802.1Q defined tag support

- 4096 VLANs supported

- Egress tagging/untagging on a per-VLAN basis per port

- · Priority-based QoS handling as specified in IEEE 802.1Q

- Per-port priority remapping and 8 configurable egress queues per port

- · Optional double-tagging support

- Hardware support for IEEE 802.1AS timestamping and IEEE 802.1Qav AVB traffic shaping

- 16 credit-based shapers available according to IEEE 802.1Qav; shapers can be freely allocated to any priority

queue on a per port basis

- Support for SR Class A, Class B, and Class C traffic

- IEEE 1588v2 one-step sync forwarding in hardware

- · Frame mirroring and retagging for enhanced diagnostics

- · Statistics for dropped frames and buffer load

- RFC2819 support for counters

# 2.3 Ethernet security

- IEEE 802.1X hardware support for EAP filtering, reachability and disabling address learning

- Extensive filtering rules for frame forwarding, retagging, tunneling and double-tagging

- · Address learning space can be configured for static and learned addresses

- · Enhanced support for address learning restrictions for security

- Ingress rate-limiting on a per-port basis for Unicast/Multicast and Broadcast traffic

- · Broadcast storm protection

## 2.4 TT and TSN features (SJA1105/Q/S only)

- IEEE 802.1Qbv time-aware traffic

- IEEE 802.1Qci per-stream policing (pre-standard)

- Support for ring-based redundancy (for time-triggered traffic only)

- 1024 deterministic Ethernet flows with per-flow based:

- Time-triggered traffic transmission

- Ingress policing and reception window check

- Statistics

### 2.5 Interface features

- MII/RMII for interfacing with 10/100 Mbit/s PHYs/host processor (Fast Ethernet)

- RGMII for interfacing with 10/100/1000 Mbit/s PHYs/host processor (with external delay components)

- RGMII-ID (with internal delay) for interfacing with 1000 Mbit/s PHYs/host processor

- SGMII for interfacing with 10/100/1000 Mbit/s PHYs/host processor/cascading

- MAC and PHY modes for interfacing (MII/RMII/RGMII/SGMII) directly with another switch or host processor

- Programmable drive strength for MII/RMII/RGMII interfaces

- SPI for host processor access

SJA1105PQRS

All information provided in this document is subject to legal disclaimers.

## 2.6 Other features

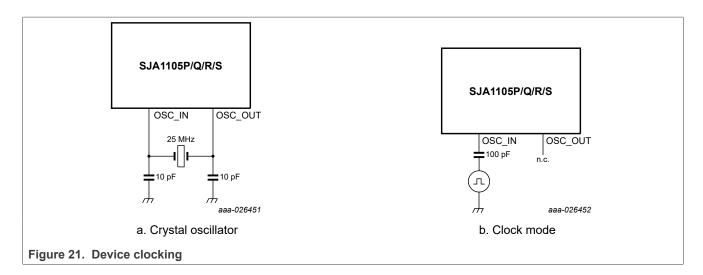

- 25 MHz system clock input from crystal oscillator or AC-coupled single-ended clock

- 25 MHz reference clock output

- · Device reset input from host processor

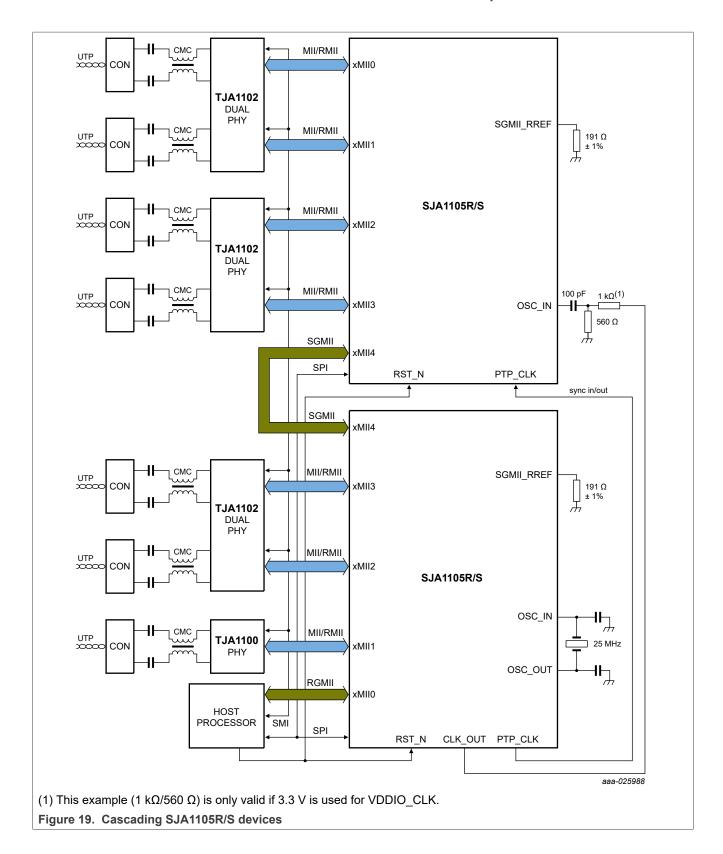

- Synchronization output for cascading devices

- IEEE 1149.1/1149.6 compliant JTAG interface for TAP controller access and BSCAN

# **Ordering information**

Table 1. Ordering information

| Type number <sup>[1]</sup> | Package  |                                                                   |           |  |  |  |

|----------------------------|----------|-------------------------------------------------------------------|-----------|--|--|--|

|                            | Name     | Description                                                       | Version   |  |  |  |

| SJA1105PEL [2]             | LFBGA159 | plastic low profile fine-pitch ball grid array package; 159 balls | SOT1427-1 |  |  |  |

| SJA1105QEL [2]             |          |                                                                   |           |  |  |  |

| SJA1105REL                 |          |                                                                   |           |  |  |  |

| SJA1105SEL                 |          |                                                                   |           |  |  |  |

Table 2. SJA1105PQRS family overview

|                         | MII/RMII/RGMII ports | SGMII ports | TSN/TTEthernet | RGMII-ID | TCAM |

|-------------------------|----------------------|-------------|----------------|----------|------|

| SJA1105P <sup>[1]</sup> | 5                    | 0           | no             | yes      | yes  |

| SJA1105Q <sup>[1]</sup> | 5                    | 0           | yes            | yes      | yes  |

| SJA1105R                | 4                    | 1           | no             | yes      | yes  |

| SJA1105S                | 4                    | 1           | yes            | yes      | yes  |

<sup>[1]</sup> Pin compatible with SJA1105 and SJA1105T.

<sup>&#</sup>x27;EL' is the LFBGA159 package code. Pin compatible with SJA1105 and SJA1105T.

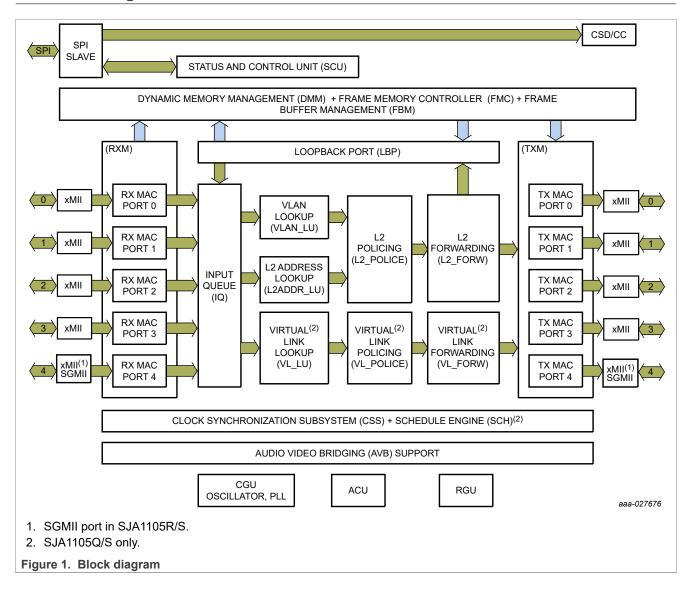

# 4 Block diagram

# 5 Pinning information

# 5.1 Pinning

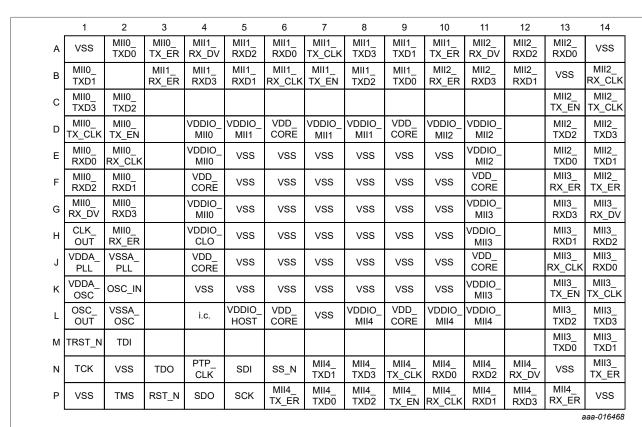

Figure 3. Pin configuration: SJA1105P and SJA1105Q

SJA1105PQRS

All information provided in this document is subject to legal disclaimers.

|   | 1               | 2               | 3              | 4              | 5              | 6               | 7               | 8              | 9             | 10             | 11             | 12             | 13              | 14              |

|---|-----------------|-----------------|----------------|----------------|----------------|-----------------|-----------------|----------------|---------------|----------------|----------------|----------------|-----------------|-----------------|

| А | VSS             | MIIO_<br>TXD0   | MII0_<br>TX_ER | MII1_<br>RX_DV | MII1_<br>RXD2  | MII1_<br>RXD0   | MII1_<br>TX_CLK | MII1_<br>TXD3  | MII1_<br>TXD1 | MII1_<br>TX_ER | MII2_<br>RX_DV | MII2_<br>RXD2  | MII2_<br>RXD0   | VSS             |

| В | MII0_<br>TXD1   |                 | MII1_<br>RX_ER | MII1_<br>RXD3  | MII1_<br>RXD1  | MII1_<br>RX_CLK | MII1_<br>TX_EN  | MII1_<br>TXD2  | MII1_<br>TXD0 | MII2_<br>RX_ER | MII2_<br>RXD3  | MII2_<br>RXD1  | VSS             | MII2_<br>RX_CLK |

| С | MII0_<br>TXD3   | MII0_<br>TXD2   |                |                |                |                 |                 |                |               |                |                |                | MII2_<br>TX_EN  | MII2_<br>TX_CLK |

| D | MII0_<br>TX_CLK | MII0_<br>TX_EN  |                | VDDIO_<br>MII0 | VDDIO_<br>MII1 | VDD_<br>CORE    | VDDIO_<br>MII1  | VDDIO_<br>MII1 | VDD_<br>CORE  | VDDIO_<br>MII2 | VDDIO_<br>MII2 |                | MII2_<br>TXD2   | MII2_<br>TXD3   |

| Е | MII0_<br>RXD0   | MII0_<br>RX_CLK |                | VDDIO_<br>MII0 | VSS            | VSS             | VSS             | VSS            | VSS           | VSS            | VDDIO_<br>MII2 |                | MII2_<br>TXD0   | MII2_<br>TXD1   |

| F | MII0_<br>RXD2   | MII0_<br>RXD1   |                | VDD_<br>CORE   | VSS            | VSS             | VSS             | VSS            | VSS           | VSS            | VDD_<br>CORE   |                | MII3_<br>RX_ER  | MII2_<br>TX_ER  |

| G | MII0_<br>RX_DV  | MII0_<br>RXD3   |                | VDDIO_<br>MII0 | VSS            | VSS             | VSS             | VSS            | VSS           | VSS            | VDDIO_<br>MII3 |                | MII3_<br>RXD3   | MII3_<br>RX_DV  |

| н | CLK_<br>OUT     | MII0_<br>RX_ER  |                | VDDIO_<br>CLO  | VSS            | VSS             | VSS             | VSS            | VSS           | VSS            | VDDIO_<br>MII3 |                | MII3_<br>RXD1   | MII3_<br>RXD2   |

| J | VDDA_<br>PLL    | VSSA_<br>PLL    |                | VDD_<br>CORE   | VSS            | VSS             | VSS             | VSS            | VSS           | VSS            | VDD_<br>CORE   |                | MII3_<br>RX_CLK | MII3_<br>RXD0   |

| K | VDDA_<br>OSC    | OSC_IN          |                | VSS            | VSS            | VSS             | VSS             | VSS            | VSS           | VSS            | VDDIO_<br>MII3 |                | MII3_<br>TX_EN  | MII3_<br>TX_CLK |

| L | OSC_<br>OUT     | VSSA_<br>OSC    |                | i.c.           | VDDIO_<br>HOST | VDD_<br>CORE    | VSS             | VDD_<br>SGMII  | VDD_<br>CORE  | VDD_<br>SGMII  | VDD_<br>SGMII  |                | MII3_<br>TXD2   | MII3_<br>TXD3   |

| М | TRST_N          | TDI             |                |                |                |                 |                 |                |               |                |                |                | MII3_<br>TXD0   | MII3_<br>TXD1   |

| N | TCK             | VSS             | TDO            | PTP_<br>CLK    | SDI            | SS_N            | VSS             | VDDA_<br>SGMII | VSS           | SGMII_<br>RREF | VSS            | VDDA_<br>SGMII | VSS             | MII3_<br>TX_ER  |

| Р | VSS             | TMS             | RST_N          | SDO            | SCK            | VSS             | VSS             | SGMII_<br>TXP  | SGMII_<br>TXN | VSS            | SGMII_<br>RXP  | SGMII_<br>RXN  | VSS             | VSS             |

aaa-025846

Figure 4. Pin configuration: SJA1105R and SJA1105S

# 5.2 Pin description

Table 3. Pin description - xMII interface

| Symbol                      | I Pin          |                |                    |                   |                         | Type <sup>[1]</sup> | Description                                                                                                                                                                                  |

|-----------------------------|----------------|----------------|--------------------|-------------------|-------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             | Ethe           | rnet p         | ort <sup>[2]</sup> |                   |                         | -                   |                                                                                                                                                                                              |

|                             | 0              | 1              | 2                  | 3                 | <b>4</b> <sup>[3]</sup> |                     |                                                                                                                                                                                              |

| VDDIO_<br>MIIx              | D4<br>E4<br>G4 | D5<br>D7<br>D8 | D10<br>D11<br>E11  | G11<br>H11<br>K11 | L8<br>L10<br>L11        | P<br>P<br>P         | 3.3 V/2.5 V/1.8 V I/O supply voltages                                                                                                                                                        |

| TX_CLK/<br>REF_CLK/<br>TXC  | D1             | A7             | C14                | K14               | N9                      | I/O<br>I/O<br>O     | TX_CLK: MII interface transmit clock (also configurable as output) REF_CLK: RMII interface reference clock (also configurable as input) TXC: RGMII interface transmit clock                  |

| TX_EN/<br>TX_CTL            | D2             | В7             | C13                | K13               | P9                      | 0                   | TX_EN: MII/RMII interface transmit enable output (active-HIGH) TX_CTL: RGMII interface transmit control output (active-HIGH)                                                                 |

| TX_ER                       | А3             | A10            | F14                | N14               | P6                      | 0                   | MII/RMII interface transmit coding error output (active-HIGH)                                                                                                                                |

| TXD0                        | A2             | В9             | E13                | M13               | P7                      | 0                   | MII/RMII/RGMII interface transmit data output, bit 0                                                                                                                                         |

| TXD1                        | B1             | A9             | E14                | M14               | N7                      | 0                   | MII/RMII/RGMII interface transmit data output, bit 1                                                                                                                                         |

| TXD2                        | C2             | В8             | D13                | L13               | P8                      | 0                   | MII/RGMII interface transmit data output, bit 2                                                                                                                                              |

| TXD3                        | C1             | A8             | D14                | L14               | N8                      | 0                   | MII/RGMII interface transmit data output, bit 3                                                                                                                                              |

| RX_CLK/<br>RXC              | E2             | В6             | B14                | J13               | P10                     | I/O<br>I            | RX_CLK: MII interface receive clock (also configurable as output); RXC: RGMII interface receive clock                                                                                        |

| RX_ER                       | H2             | ВЗ             | B10                | F13               | P13                     | I                   | MII/RMII interface receive error input (active-HIGH); must be connected to VSS if not used                                                                                                   |

| RX_DV/<br>CRS_DV/<br>RX_CTL | G1             | A4             | A11                | G14               | N12                     | <br>                | RX_DV: MII interface receive data valid input (active-HIGH); CRS_DV: RMII interface carrier sense/data valid input (active-HIGH) RX_CTL: RGMII interface receive control input (active-HIGH) |

| RXD0                        | E1             | A6             | A13                | J14               | N10                     | I                   | MII/RMII/RGMII interface receive data input, bit 0                                                                                                                                           |

| RXD1                        | F2             | B5             | B12                | H13               | P11                     | I                   | MII/RMII/RGMII interface receive data input, bit 1                                                                                                                                           |

| RXD2                        | F1             | A5             | A12                | H14               | N11                     | I                   | MII/RGMII interface receive data input, bit 2                                                                                                                                                |

| RXD3                        | G2             | B4             | B11                | G13               | P12                     | I                   | MII/RGMII interface receive data input, bit 3                                                                                                                                                |

Table 4. Pin description - hardwired SGMII interface: SJA1105R/S

| Symbol     | Pin          | Type <sup>[1]</sup> | Description                                                                        |

|------------|--------------|---------------------|------------------------------------------------------------------------------------|

| VDD_SGMII  | L8, L10, L11 | Р                   | 1.2 V core supply voltage for SGMII PHY (must be derived from the VDD_CORE supply) |

| VDDA_SGMII | N8, N12      | Р                   | 2.5 V analog supply voltage for SGMII PHY                                          |

| SGMII_RXN  | P12          | Al                  | SGMII differential receive negative [2]                                            |

| SGMII_RXP  | P11          | Al                  | SGMII differential receive positive                                                |

SJA1105PQRS

All information provided in this document is subject to legal disclaimers.

I: digital input; O: digital output; P: power supply.

MI/RMII/RGMII I/O pins are floating until the configuration is loaded and the interface is decided; all digital output pins are in "Fast speed mode" after reset unless otherwise indicated.

MII/RMII/RGMII on port 4 available in SJA1105P/Q only. SJA1105R/S features a hardwired SGMII PHY on this port. [3]

Table 4. Pin description - hardwired SGMII interface: SJA1105R/S...continued

| Symbol     | Pin | Type <sup>[1]</sup> | Description                              |  |  |

|------------|-----|---------------------|------------------------------------------|--|--|

| SGMII_TXN  | P9  | AO                  | SGMII differential transmit negative [2] |  |  |

| SGMII_TXP  | P8  | AO                  | SGMII differential transmit positive     |  |  |

| SGMII_RREF | N10 | AO                  | SGMII calibration resistor output        |  |  |

Table 5. Pin description - core supply and ground

| and of the accompanies control capping and ground |                                                                                                                                                                                            |                     |                                 |  |  |  |  |  |

|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------------|--|--|--|--|--|

| Symbol                                            | Pin                                                                                                                                                                                        | Type <sup>[1]</sup> | Description                     |  |  |  |  |  |

| VDD_CORE                                          | D6, D9, F4, F11, J4, J11, L6, L9                                                                                                                                                           | Р                   | 1.2 V core supply voltage       |  |  |  |  |  |

| VSS                                               | A1, A14, B13, E5, E6, E7, E8, E9, E10, F5, F6, F7, F8, F9, F10,G5, G6, G7, G8, G9, G10, H5, H6, H7, H8, H9, H10, J5, J6, J7,J8, J9, J10, K4, K5, K6, K7, K8, K9, K10, L7, N2, N13, P1, P14 | G                   | supply ground (all variants)    |  |  |  |  |  |

|                                                   | N7, N9, N11, P6, P7, P10, P13                                                                                                                                                              | G                   | supply ground (SJA1105R/S only) |  |  |  |  |  |

<sup>[1]</sup> P: power supply; G: ground.

Table 6. Pin description - general

| Symbol               | Pin <sup>[1]</sup> | Type <sup>[2]</sup> | Description                                                                                   |  |  |

|----------------------|--------------------|---------------------|-----------------------------------------------------------------------------------------------|--|--|

| RST_N                | P3                 | I                   | reset input (active-LOW, hysteresis, VDDIO_HOST)                                              |  |  |

| PTP_CLK              | N4                 | I/O                 | sync in/out or PTP clock (if input: active-HIGH, VDDIO_HOST)                                  |  |  |

| VDDIO_HOST           | L5                 | Р                   | host interface supply voltage for SPI, JTAG, CLK_OUT, PTP_CLK and RST_N (1.8 V, 2.5 V, 3.3 V) |  |  |

| i.c.                 | L4                 | G                   | internally connected; must be connected to ground                                             |  |  |

| Clock generation (CC | GU)                |                     |                                                                                               |  |  |

| VDDA_OSC             | K1                 | Р                   | oscillator supply voltage (1.2 V)                                                             |  |  |

| VSSA_OSC             | L2                 | G                   | oscillator supply ground                                                                      |  |  |

| VDDA_PLL             | J1                 | Р                   | PLL supply voltage (1.2 V)                                                                    |  |  |

| VSSA_PLL             | J2                 | G                   | PLL supply ground                                                                             |  |  |

| VDDIO_CLO            | H4                 | Р                   | clock output interface supply voltage (1.8 V, 2.5 V, 3.3 V)                                   |  |  |

| CLK_OUT              | H1                 | 0                   | clock output (VDDIO_CLO)                                                                      |  |  |

| OSC_IN               | K2                 | Al                  | oscillator input                                                                              |  |  |

| OSC_OUT              | L1                 | AO                  | oscillator output                                                                             |  |  |

| SPI interface        |                    |                     |                                                                                               |  |  |

| SCK                  | P5                 | I                   | SPI clock (hysteresis, weak pull-down, VDDIO_HOST)                                            |  |  |

| SDI                  | N5                 | I                   | SPI data input (hysteresis, weak pull-up, VDDIO_HOST)                                         |  |  |

| SDO                  | P4                 | 0                   | SPI data output (VDDIO_HOST)                                                                  |  |  |

I: digital input; O: digital output; AI: analog input; AO: analog output; P: power supply. SGMII positive/negative polarities can be swapped in software to allow for MAC-MAC configurations.

Table 6. Pin description - general...continued

| Symbol         | Pin <sup>[1]</sup> | Type <sup>[2]</sup> | Description                                                   |  |  |

|----------------|--------------------|---------------------|---------------------------------------------------------------|--|--|

| SS_N           | N6                 | I                   | SPI chip select (hysteresis, weak pull-up, VDDIO_HOST)        |  |  |

| JTAG interface |                    |                     |                                                               |  |  |

| TRST_N         | M1                 | I                   | test reset (active LOW, hysteresis, weak pull-up, VDDIO_HOST) |  |  |

| TDI            | M2                 | I                   | test data in (hysteresis, weak pull-up, VDDIO_HOST)           |  |  |

| TCK            | N1                 | I                   | test clock (hysteresis, weak pull-up, VDDIO_HOST)             |  |  |

| TMS            | P2                 | I                   | test mode select (hysteresis, weak pull-up, VDDIO_HOST)       |  |  |

| TDO            | N3                 | 0                   | test data out (VDDIO_HOST)                                    |  |  |

- [1] All digital output pins are in "Fast speed mode" after reset unless otherwise indicated.

- [2] I: digital input; O: digital output; Al: analog input; AO: analog output; P: power supply, G: ground.

# 6 Functional description

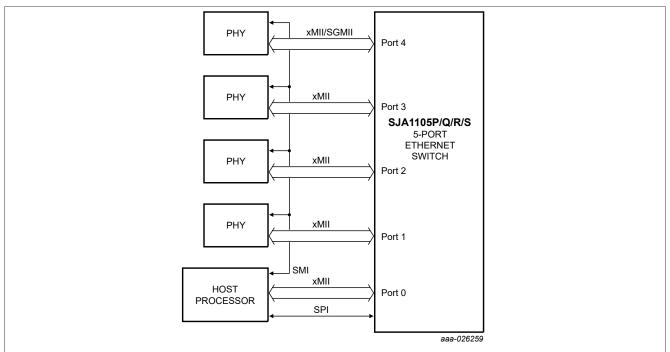

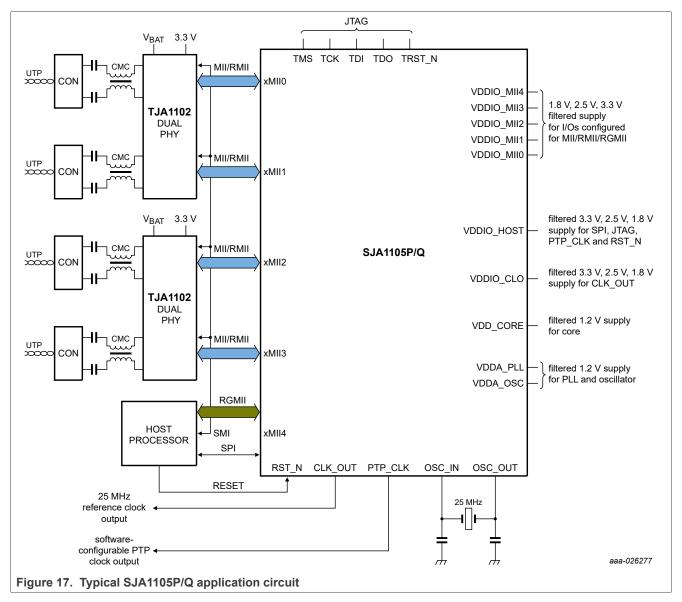

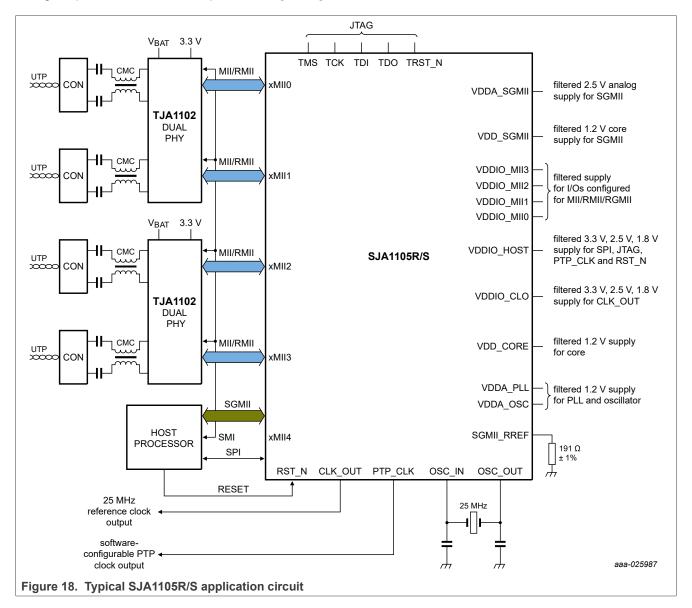

The SJA1105P/Q/R/S is designed to provide a cost-optimized and flexible solution for automotive Ethernet switches. The SJA1105P/Q variants are feature-enhanced, drop-in replacements for the SJA1105/T. In the SJA1105R/S variants, one of the ports provides SGMII capability. These devices can be used in applications requiring SGMII connectivity with a host processor or where multiple devices need to be cascaded.

Each port can be independently configured for 10/100 Mbit/s MII/RMII or 10/100/1000 Mbit/s RGMII operation. The SGMII port on the SJA1105R/S can be configured for 10/100/1000 Mbit/s operation. An SPI-slave interface provides device register access to the host processor. A typical system diagram is shown in Figure 5.

Figure 5. System diagram showing the SJA1105P/Q/R/S Ethernet switch connected to PHYs and a host processor. Port 4 is SGMII on SJA1105R/S

## 6.1 Functional overview

The SJA1105P/Q/R/S contains the following functional modules (see the block diagram in Figure 1):

# **6.1.1 Auxiliary Configuration Unit (ACU)**

This module contains the pin configuration and status registers. The host can configure the I/O pads of the chip (pull-up/pull-down, speed etc.) and monitor the product configuration and temperature sensor status via these registers.

## 6.1.2 Clock Generation Unit (CGU)

This module contains the clock inputs, PLL and clock distribution for all internal blocks.

#### 6.1.3 Reset Generation Unit (RGU)

This block resets all internal configuration registers to a pre-defined state at power-up.

#### 6.1.4 Serial Peripheral Interface (SPI)

The host controller manages the device via the SPI.

#### 6.1.5 Status and Control Unit (SCU)

This block contains the SJA1105PQRS status and configuration registers. The host processor accesses these registers via the SPI.

## 6.1.6 Configuration Stream Decoder/Configuration Controller (CSD/CC)

This block handles the distribution of the configuration stream from the host processor to other modules and performs a CRC check on the configuration blocks.

#### 6.1.7 xMII

This block is a wrapper and multiplexer for the MII interface options. The device supports MII, RMII and RGMII. In the SJA1105R/S, port 4 is hard-wired for SGMII operation.

# 6.1.8 Dynamic Memory Management (DMM)/Frame Memory Controller (FMC)/ Frame Buffer Management (FBM)

These blocks deal with the storage and handling of frames in the memory buffer. The DMM provides memory handles for ingress frames and holds meta information related to the frames. The DMM releases frame handles for frames that are transmitted or dropped. The FMC converts frame handles into virtual memory addresses and the FBM optimizes the use of on-chip frame memory based on frame size.

#### 6.1.9 Receive MAC (RXM)

The RXM loads the data from the xMII interface block and checks the IFG, the preamble, the SOF delimiter, the CRC and the frame length. It provides timestamps for clock synchronization frames, extracts frame metadata such as MAC addresses and VLAN information, and drops runt and oversized frames. The RXM collects memory handles from the DMM and transfers frame data to the FMC block for writing to memory.

SJA1105PQRS

All information provided in this document is subject to legal disclaimers.

# 6.1.10 Input Queue (IQ)

The IQ arranges the frame processing order so that the switching fabric behaves in a deterministic manner. If two ports receive an EOF during the same clock cycle, frames received on the port with the lower port ID are processed first.

The switch has a non-blocking, egress queue architecture. The input queue arbitrates access to the switching fabric and not to the egress ports.

#### 6.1.11 VLAN Lookup (VLAN\_LU)

The forwarding limitations and tagging/untagging options are determined in the VLAN LU block.

### 6.1.12 Address Lookup (L2ADDR\_LU)

The forwarding information for frames based on the destination MAC address in combination with the VLAN ID is determined in this block. The lookup table is addressed using a TCAM-based LUT. The table holds dynamically learned and statically configured entries. Dynamically learned entries can be configured to timeout. The address lookup process can be configured to use shared or independent address learning. The TCAM-based LUT can, additionally, be configured as a filter to determine subsequent action for frame processing.

# 6.1.13 Policing (L2\_POLICE)

Ingress policing rules are enforced in the L2\_POLICE block. The transmission rate can be limited for any of the eight priority levels and for broadcast traffic at each port. Non-compliant traffic is dropped and is indicated by associated flags and counters.

# 6.1.14 Forwarding (L2\_FORW)

The L2\_FORW block forwards frames to the destination ports. It maintains a vector of reachable ports for unicast traffic for each ingress port. In addition, it maintains a vector of destination ports for broadcast traffic and for unknown multicast traffic. This block also maintains a memory partition account for traffic received per port and drops frames if there is insufficient space. This block also handles priority remapping and egress queue priority mapping.

#### 6.1.15 Transmit MAC (TXM)

This block handles frame output via the xMII interface. It supports eight priority queues and implements strict-priority scheduling. The AVB block can interrupt the scheduling from specific priority queues in case shapers are allocated to queues. When a frame is selected for transmission, this block gets the frame data from the FMC using the memory handle of the frame. It passes the free memory handle back to the DMM once the frame has been transmitted. It also inserts VLAN tags into packet headers. It can be configured to perform the IEEE 1588v2 transparent clock update for sync frames.

# 6.1.16 Audio Video Bridging (AVB)

This block implements credit-based traffic shaping according to IEEE802.1Qav and interrupts transmission from priority queues in the TXM when necessary, to ensure that shaping occurs. It also captures high-resolution timestamps for IEEE 802.1AS and IEEE 1588v2 operation. The host processor can adjust the IEEE 1588v2 hardware clock via this block.

SJA1105PQRS

All information provided in this document is subject to legal disclaimers.

# 6.1.17 Loopback Port (LBP)

This block uses an internal port to replicate a frame internally and change the VLAN tag to support ingress and egress retagging of traffic. The replicated frame-handling information is fed back to the IQ which processes the frame in the same way as a frame from a regular traffic port.

# 6.1.18 Virtual Link Lookup (VL\_LU); SJA1105Q/S only

The VL\_LU block performs a lookup of time-triggered and rate-constrained traffic based on the configured Virtual Link Multicast addresses, the VLAN ID and the VLAN priority identifying time-triggered or rate-constrained traffic.

# 6.1.19 Virtual Link Policing (VL\_POLICE); SJA1105Q/S only

The VL\_POLICE block executes policing functions based on the time-triggered Ethernet or rate-constrained traffic rule set. Policing mechanisms can be configured individually per flow (i.e. per virtual link). Time-triggered Ethernet policing verifies that a frame received by the switch was sent at the correct point in time by the neighboring node. Non-compliant frames are dropped and are indicated by associated flags and counters.

### 6.1.20 Virtual Link Forwarding (VL\_FORW); SJA1105Q/S only

The VL\_FORW block forwards time-triggered or rate-constrained traffic to the destination ports. Time-triggered traffic is stored in this module until the running traffic schedule fires a transmit trigger for the respective Virtual Link. Rate-constrained traffic is immediately routed to the destination ports. All time-triggered frames are dropped if synchronization is lost.

#### 6.1.21 Clock Synchronization Subsystem (CSS) and Schedule Engine (SCH); SJA1105Q/S only

This block implements the clock synchronization protocol and executes the message schedules.

# 6.2 Media Independent Interfaces (xMII)

The xMII interfaces can be configured to support a wide variety of PHYs and host controllers. Each port can be configured for MAC-to-PHY or MAC-to-MAC communication. The following configurations are supported:

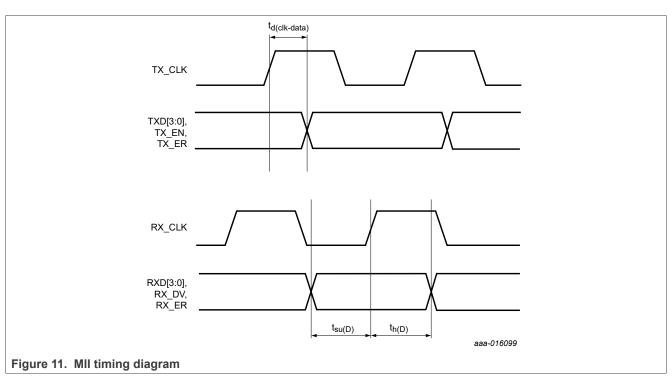

MII: 25 MHz clock for 100 Mbit/s or 2.5 MHz for 10 Mbit/s operation, 14 interface signals, full duplex only [4]

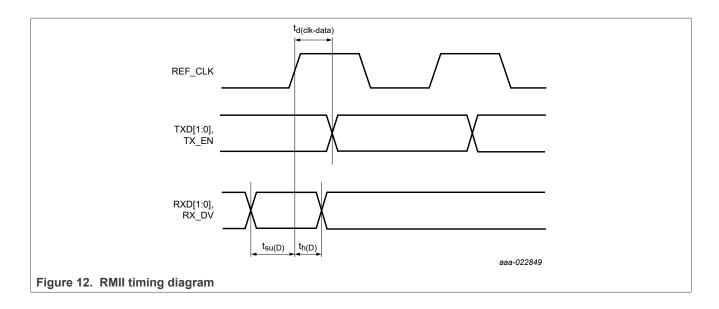

RMII: 50 MHz clock for 100 Mbit/s and 10 Mbit/s operation, 8 interface signals (reference clock can be an input to both devices or may be driven from MAC to PHY), full duplex only [5]

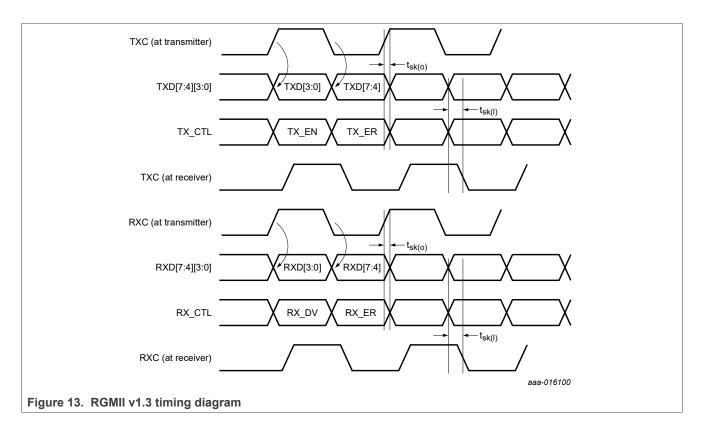

RGMII: 125 MHz clock (both edges) for 1000 Mbit/s, 25 MHz for 100 Mbit/s or 2.5 MHz for 10 Mbit/s operation, 12 interface signals; full duplex only [6] [7]

SGMII: 1.25 Gbit/s LVDS for 10/100/1000 Mbit/s data transmission, 4 interface signals [8]

The interfaces can operate under the following conditions:

Table 7. Supported xMII interface operating conditions

| Interface | Interface I/O Voltage |       |       |               | I/O Slew Rate |                 |               |  |  |

|-----------|-----------------------|-------|-------|---------------|---------------|-----------------|---------------|--|--|

|           | 1.8 V                 | 2.5 V | 3.3 V | High<br>Speed | Fast<br>Speed | Medium<br>Speed | Slow<br>Speed |  |  |

| MII       | •                     | •     | •     | -             | •             | •               | •             |  |  |

| RMII      | -                     | •     | •     | -             | •             | •               | •             |  |  |

| RGMII     | •                     | •     | •     | •             | •             | -               | -             |  |  |

SJA1105PQRS

All information provided in this document is subject to legal disclaimers.

Table 7. Supported xMII interface operating conditions...continued

| Interface | I/O Voltage    |       |       | I/O Slew Rate |               |                 |               |

|-----------|----------------|-------|-------|---------------|---------------|-----------------|---------------|

|           | 1.8 V          | 2.5 V | 3.3 V | High<br>Speed | Fast<br>Speed | Medium<br>Speed | Slow<br>Speed |

| SGMII     | not applicable |       |       |               |               |                 |               |

Depending on how the switch is configured, the following interface signals are available at each of the five ports (SGMII signals on SJA1105R/S port 4 are fixed and are not multiplexed):

Table 8. xMII pin multiplexing

| MII (14 interface signals) | RMII (8 interface signals) | RGMII (12 interface signals) |

|----------------------------|----------------------------|------------------------------|

| TX_CLK                     | REF_CLK                    | TXC                          |

| TX_EN                      | TX_EN                      | TX_CTL                       |

| TX_ER [1]                  | TX_ER [1]                  | -                            |

| TXD0                       | TXD0                       | TXD0                         |

| TXD1                       | TXD1                       | TXD1                         |

| TXD2                       | -                          | TXD2                         |

| TXD3                       | -                          | TXD3                         |

| RX_CLK                     | -                          | RXC                          |

| RX_ER [1]                  | RX_ER [1]                  | -                            |

| RX_DV                      | CRS_DV                     | RX_CTL                       |

| RXD0                       | RXD0                       | RXD0                         |

| RXD1                       | RXD1                       | RXD1                         |

| RXD2                       | -                          | RXD2                         |

| RXD3                       | -                          | RXD3                         |

<sup>[1]</sup> TX\_ER and RX\_ER are optional; unused inputs must be connected to VSS.

## 6.2.1 MII signaling

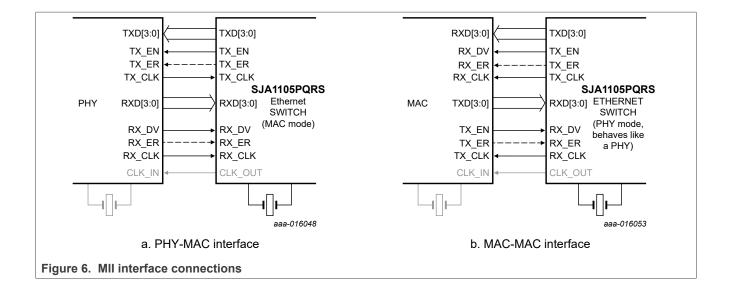

<u>Figure 6</u> shows the PHY-MAC (i.e. PHY to switch) and MAC-MAC (i.e. processor to switch) connections in an MII interface. Data is exchanged in 4-bit wide data nibbles TXD[3:0] and RXD[3:0]. Data transmission is synchronous with the transmit (TX\_CLK) and receive (RX\_CLK) clocks. For the PHY-MAC interface, both clock signals are provided by the PHY and are typically derived from an external crystal running at a nominal 25 MHz (±100 ppm) or from the CLK\_OUT signal on the switch. When the Ethernet Switch is configured for MAC-MAC communication, the switch provides the clocks and acts like a PHY.

Note that RX\_ER must be connected to VSS when not used.

# 6.2.2 RMII signaling

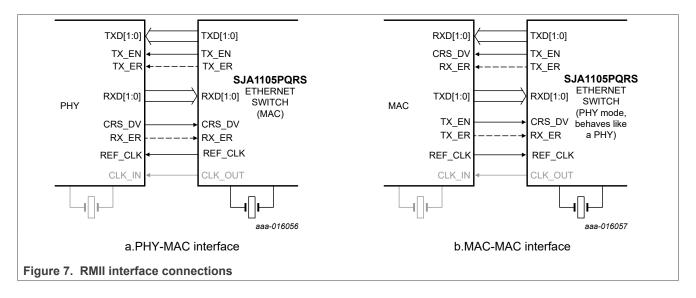

RMII data is exchanged via 2-bit data signals TXD[1:0] and RXD[1:0] as shown in <u>Figure 7</u>. Transmit and receive signals are synchronized with the shared reference clock, REF\_CLK.

In the PHY-MAC (i.e. PHY to switch) configuration, the shared reference clock is output by the switch on pin REF\_CLK. In MAC-MAC mode (i.e. processor to switch; switch port configured as a PHY), the reference clock is provided by the MAC.

To achieve the same data rate as MII, the interface is clocked at a nominal 50 MHz (±50 ppm) for 100 Mbit/s and 10 Mbit/s operation.

Note that RX ER must be connected to VSS when not used.

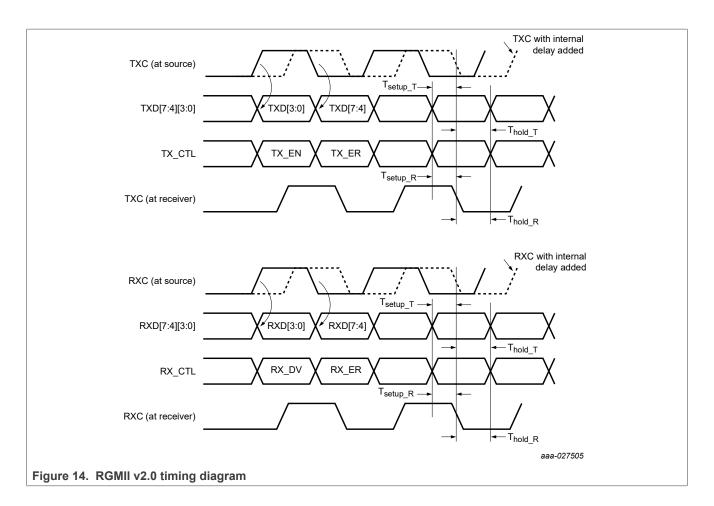

### 6.2.3 RGMII signaling

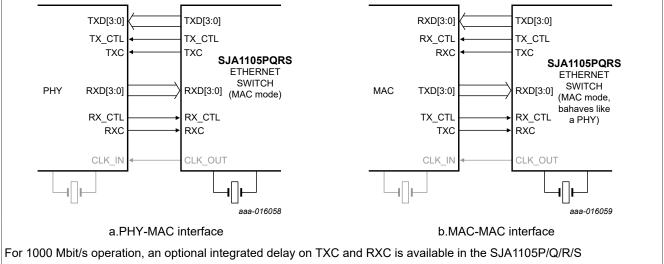

The PHY-MAC (i.e. PHY to switch) and MAC-MAC (i.e. processor to switch) connections in an RGMIIconfigured interface are shown in Figure 8. The RGMII protocol is intended to be an alternative to the IEEE 802.3z GMII standard (not supported on the SJA1105P/Q/R/S). The objective is to reduce the number of pins needed to connect the MAC and PHY in a cost-effective and technology-independent way. RGMII has the added advantage over RMII in that it supports Gigabit operation.

In order to achieve a reduced pin count, the number of data signals and associated control signals is reduced. Control signals are multiplexed together and transmitted data is synchronized with both clock edges (double data rate).

RGMII is a symmetrical interface. For 1000 Mbit/s, 100 Mbit/s and 10 Mbit/s operation, the clocks operate at 125 MHz, 25 MHz and 2.5 MHz (±50 ppm) respectively. The TXC signal is always generated by the MAC. The PHY generates the RXC.

Note that RGMII v1.3 [6] requires an external delay of between 1.5 ns and 2 ns on TXC and RXC. The SJA1105P/Q/R/S provides support for delay timing as defined in the updated RGMII v2.0 specification for 1000 Mbit/s [7].

The maximum interconnect delay is limited to 1 ns. Therefore, the maximum supported trace length is approximately 15 cm.

### 6.2.4 SGMII signaling

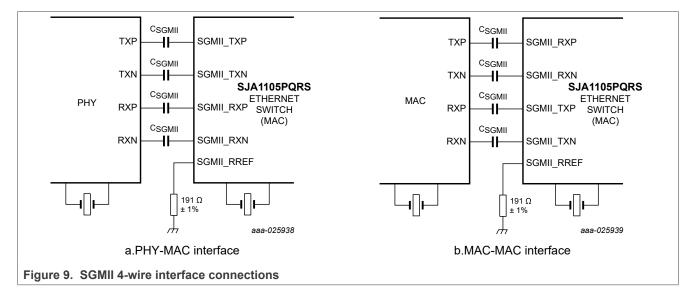

The PHY-MAC (i.e. PHY to switch) and MAC-MAC (i.e. processor to switch) connections on an SGMII-configured interface are shown in <u>Figure 9</u>. The SGMII protocol [8] is intended as an alternative to the RGMII standard. It uses fewer interface signals and provides better EMC performance. Port 4 on SJA1105R/S is an SGMII 4-wire interface. It implements clock data recovery so no additional clock pairs are needed (6-wire interface is not supported). SGMII must always be AC coupled with a capacitor ( $C_{SGMII}$ , 100 nF). The SJA1105R/S is AC-compliant with the SGMII specification. For SGMII operation, an external calibration resistor (191  $\Omega$  ±1 %) must be connected to SGMII\_RREF.

The SGMII interface implements (optional) Auto-Negotation. In this mode, PHY and MAC handshake the supported interface capabilities to determine optimal operating conditions. SGMII Auto-Negotiation can be disabled to force the interface into the desired operating mode to improve the start-up time.

## 6.3 SPI interface

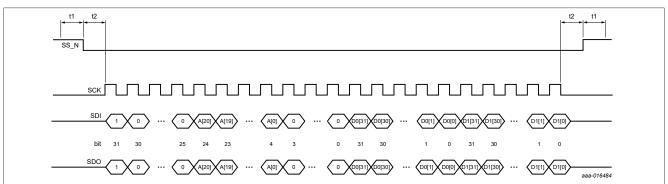

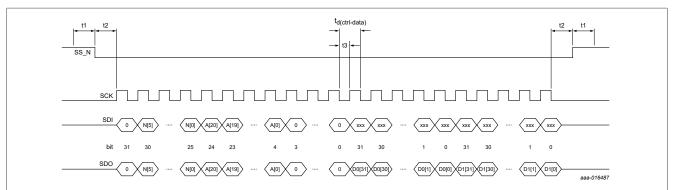

The SJA1105P/Q/R/S provides an SPI bus slave as the host control interface. The host can control/configure the SJA1105P/Q/R/S by accessing the configuration address space and the programming address space.

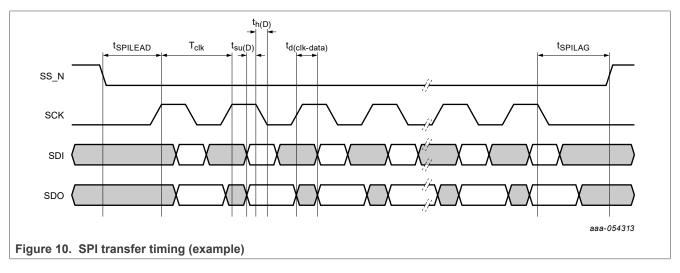

This interface acts as a slave in a synchronous serial data link that conforms with the SPI standard as defined in the SPI Block Guide from Motorola [9]. The interface operates in SPI Transfer mode 1 (CPOL = 0, CPHA = 1).

An example SPI timing diagram is shown in <u>Figure 10</u>. Data is captured on the falling edge of the clock and transmitted on the rising edge. Both master and slave must operate in the same mode.

After the SS\_N signal has been asserted, the SPI clock signal (SCK) must be stable for at least  $t_{SPILEAD}$  before being asserted. At the end of the SPI transaction, the SPI clock signal (SCK) must be stable for at least  $t_{SPILAG}$  before the SS\_N signal is de-asserted.

The SPI clock signal (SCK) must be stable for at least half a clock period between the reception of on the SDI input and the transmission on the SDO output.

When CGU registers are read, a 64 ns delay must be inserted between the control and data phases to allow the device to retrieve the data. Alternatively, the access can be performed at a frequency below 17.8 MHz. In addition, a read-after-write time of  $t_{d(W-R)}$  between an SPI write and read transaction to the same register must be guaranteed. See the SJA1105P/Q/R/S software user manuals [10] for further details on the data format.

The number of SPI clock cycles must be between 64 and 2080 and be a multiple of 32. In order to ensure support for a wide a range of microcontrollers, the SPI interface can operate at a supply voltage of 3.3 V, 2.5 V or 1.8 V (determined by the voltage connected to VDDIO HOST).

# **Limiting values**

Table 9. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol                  | Parameter                        | Conditions                             |     | Min   | Max   | Unit |

|-------------------------|----------------------------------|----------------------------------------|-----|-------|-------|------|

| V <sub>DDA(osc)</sub>   | oscillator analog supply voltage |                                        |     | -0.5  | +1.6  | V    |

| V <sub>DDA(PLL)</sub>   | PLL analog supply voltage        |                                        |     | -0.5  | +1.6  | V    |

| $V_{DDC}$               | core supply voltage              |                                        |     | -0.5  | +1.6  | V    |

| V <sub>DD(host)</sub>   | host supply voltage              |                                        |     | -0.5  | +5    | V    |

| V <sub>DD(clk)</sub>    | clock supply voltage             |                                        |     | -0.5  | +5    | V    |

| $V_{DD(MII)}$           | MII supply voltage               |                                        |     | -0.5  | +5    | V    |

| V <sub>DDA(SGMII)</sub> | SGMII analog supply voltage      |                                        |     | -0.5  | +5    | V    |

| V <sub>DDD(SGMII)</sub> | SGMII digital supply voltage     |                                        |     | -0.5  | +1.6  | V    |

| V <sub>ESD</sub>        | electrostatic discharge voltage  | Human Body Model (HBM); 100 pF, 1.5 kΩ | [1] | -2000 | +2000 | V    |

|                         |                                  | Charged Device Model (CDM)             | [2] |       |       |      |

|                         |                                  | corner balls                           |     | -750  | +750  | V    |

|                         |                                  | other balls                            |     | -500  | +500  | V    |

| T <sub>j</sub>          | junction temperature             |                                        | [3] | -40   | +125  | °C   |

| T <sub>stg</sub>        | storage temperature              |                                        | [4] | -55   | +150  | °C   |

According to AEC-Q100-002. According to AEC-Q100-011.

## Thermal characteristics

#### Table 10. Thermal characteristics

Value determined for free convection conditions on a JEDEC 2S2P board [1].

| Symbol                | Parameter                                                          | Conditions | Тур | Unit |

|-----------------------|--------------------------------------------------------------------|------------|-----|------|

| R <sub>th(j-a)</sub>  | thermal resistance from junction to ambient                        |            | 26  | K/W  |

| R <sub>th(j-b)</sub>  | thermal resistance from junction to board <sup>[2]</sup>           |            | 9   | K/W  |

| $\Psi_{j\text{-top}}$ | thermal characterization parameter from junction to top of package |            | 12  | K/W  |

According to JEDEC JESD51-2, JESD51-5 and JESD51-7 at natural convection on 2s2p board. Board with two inner copper layers (thickness: 35 µm) and thermal via array under the exposed pad connected to the first inner copper layer (thickness: 70 µm).

In accordance with IEC 60747-1. An alternative definition of virtual junction temperature is:  $T_{vj} = T_{amb} + P \times R_{th(j-a)}$ , where  $R_{th(j-a)}$  is a fixed value used in the calculation of  $T_{vj}$ . The rating for  $T_{vj}$  limits the allowable combinations of power dissipation (P) and ambient temperature ( $T_{amb}$ ).  $T_{stg}$  in application according to IEC61360-4. For component transport and storage conditions, see instead IEC61760-2.

Board temperature refers to all solder pads on the PCB connecing to the BGA balls.

# 9 Static characteristics

Table 11. Static characteristics

$T_j$  = -40 °C to +125 °C; all voltages are defined with respect to ground unless otherwise specified; positive currents flow into the IC.<sup>[1]</sup>

| Symbol                   | Parameter                        | Conditions                                                         | Min  | Тур  | Max      | Unit     |

|--------------------------|----------------------------------|--------------------------------------------------------------------|------|------|----------|----------|

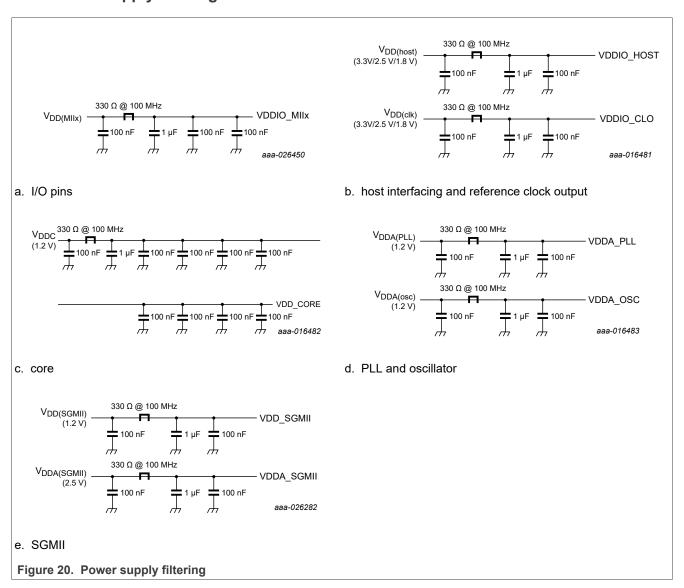

| Supply volta             | ges; see <u>Figure 20</u>        |                                                                    |      | '    | <b>"</b> | <b>'</b> |

| Clock and h              | ost interface supply (pins VDDIC | O_CLO and VDDIO_HOST)                                              |      |      |          |          |

| V <sub>DD(clk)</sub>     | clock supply voltage             | 3.3 V signaling                                                    | 3.00 | 3.30 | 3.60     | V        |

|                          |                                  | 2.5 V signaling                                                    | 2.30 | 2.50 | 2.70     | V        |

|                          |                                  | 1.8 V signaling                                                    | 1.65 | 1.80 | 1.95     | V        |

| V <sub>DD(host)</sub>    | host supply voltage              | 3.3 V signaling                                                    | 3.00 | 3.30 | 3.60     | V        |

|                          |                                  | 2.5 V signaling                                                    | 2.30 | 2.50 | 2.70     | V        |

|                          |                                  | 1.8 V signaling                                                    | 1.65 | 1.80 | 1.95     | V        |

| MII/RMII/RG              | MII interface supply (pins VDDI  | O_MII0 to VDDIO_MII4)                                              |      |      |          |          |

| V <sub>DD(MII)</sub>     | MII supply voltage               | 3.3 V signaling                                                    | 3.00 | 3.30 | 3.60     | V        |

|                          |                                  | 2.5 V signaling                                                    | 2.30 | 2.50 | 2.70     | V        |

|                          |                                  | 1.8 V signaling                                                    | 1.65 | 1.80 | 1.95     | V        |

| SGMII interfa            | ace supply (pins VDD_SGMII ar    | nd VDDA_SGMII)                                                     |      | ·    |          | ·        |

| V <sub>DDA(SGMII)</sub>  | SGMII analog supply voltage      |                                                                    | 2.3  | 2.5  | 2.7      | V        |

| V <sub>DDD(SGMII)</sub>  | SGMII digital supply voltage     |                                                                    | 1.14 | 1.2  | 1.32     | V        |

| Core, oscilla            | tor and PLL supply (pins VDD_0   | CORE, VDDA_OSC and VDDA_PLL)                                       |      |      |          |          |

| $V_{DDC}$                | core supply voltage              | see Figure 20                                                      | 1.14 | 1.2  | 1.32     | V        |

| $V_{\rm DDA(osc)}$       | oscillator analog supply voltage |                                                                    | 1.1  | 1.2  | 1.3      | V        |

| V <sub>DDA(PLL)</sub>    | PLL analog supply voltage        |                                                                    | 1.1  | 1.2  | 1.3      | V        |

| Supply curre             | ents                             |                                                                    |      | ·    | <u>'</u> |          |

| Clock and h              | ost interface supply (pins VDDIC | D_CLO and VDDIO_HOST)                                              |      |      |          |          |

| I <sub>DD(host)RMS</sub> | host supply current (RMS)        | SPI running at 25 MHz; JTAG port at 16 MHz; C <sub>L</sub> = 25 pF |      |      |          |          |

|                          |                                  | V <sub>DD(host)</sub> = 3.30 V                                     | -    | -    | 2.1      | mA       |

|                          |                                  | V <sub>DD(host)</sub> = 2.50 V                                     | -    | -    | 1.6      | mA       |

|                          |                                  | V <sub>DD(host)</sub> = 1.80 V                                     | -    | -    | 1.2      | mA       |

| I <sub>DD(clk)RMS</sub>  | clock supply current (RMS)       | C <sub>L</sub> = 25 pF                                             |      |      |          |          |

|                          |                                  | V <sub>DD(clk)</sub> = 3.30 V                                      | -    | -    | 3.9      | mA       |

|                          |                                  | V <sub>DD(clk)</sub> = 2.50 V                                      | -    | -    | 3.0      | mA       |

|                          |                                  | V <sub>DD(clk)</sub> = 1.80 V                                      | -    | -    | 2.2      | mA       |

Table 11. Static characteristics...continued

$T_j$  = -40 °C to +125 °C; all voltages are defined with respect to ground unless otherwise specified; positive currents flow into the IC.<sup>[1]</sup>

| Symbol                      | Parameter                          | Conditions                                                                                     | Min      | Тур  | Max  | Unit |

|-----------------------------|------------------------------------|------------------------------------------------------------------------------------------------|----------|------|------|------|

| MII interface               | supply (pins VDDIO_MII0 to VI      | DDIO_MII4)                                                                                     | 1        |      |      |      |

| I <sub>DD(MII)</sub> RMS    | MII supply current (RMS)           | MII-PHY mode at 100 Mbit/s;<br>C <sub>L</sub> = 29 pF; worst-case alternating<br>data pattern  |          |      |      |      |

|                             |                                    | 3.3 V operation                                                                                | -        | -    | 15.4 | mA   |

|                             |                                    | 2.5 V operation                                                                                | -        | -    | 11.6 | mA   |

|                             |                                    | 1.8 V operation                                                                                | -        | -    | 8.4  | mA   |

|                             |                                    | RMII-MAC mode at 100 Mbit/s;<br>C <sub>L</sub> = 29 pF; worst-case alternating<br>data pattern |          |      |      |      |

|                             |                                    | 3.3 V operation                                                                                | -        | -    | 15.8 | mA   |

|                             |                                    | 2.5 V operation                                                                                | -        | -    | 11.9 | mA   |

|                             |                                    | RGMII mode at 1 Gbit/s; C <sub>L</sub> = 22 pF; worst-case alternating data pattern            |          |      |      |      |

|                             |                                    | 3.3 V operation                                                                                | -        | -    | 84   | mA   |

|                             |                                    | 2.5 V operation                                                                                | -        | -    | 63.1 | mA   |

|                             |                                    | 1.8 V operation                                                                                | -        | -    | 45.6 | mA   |

| SGMII interfa               | ce supply (pins VDD_SGMII a        | nd VDDA_SGMII)                                                                                 | 1        |      |      |      |

| I <sub>DDA(SGMII)</sub> RMS | SGMII analog supply current (RMS)  |                                                                                                | -        | 20.2 | -    | mA   |

| I <sub>DDD(SGMII)RM</sub>   | SGMII digital supply current (RMS) |                                                                                                | -        | 17.6 | -    | mA   |

| Core, oscillat              | or and PLL supply (pins VDD_       | CORE, VDDA_OSC and VDDA_PLL)                                                                   | 1        |      |      |      |

| I <sub>DDC</sub>            | core supply current                |                                                                                                | -        | -    | 200  | mA   |

| I <sub>DDA(PLL)</sub>       | PLL analog supply current          | single-phase per PLL                                                                           | -        | -    | 1.2  | mA   |

|                             |                                    | multi-phase per PLL                                                                            | -        | -    | 1.6  | mA   |

| I <sub>DDA(osc)</sub>       | oscillator analog supply           | slave mode; 25 MHz input clock                                                                 | -        | 700  | -    | μΑ   |

|                             | current                            | oscillation mode; 25 MHz<br>crystal                                                            | -        | 350  | -    | μΑ   |

| I <sub>startup(osc)</sub>   | oscillator start-up current        |                                                                                                | 0.2      | 1.0  | 2.5  | mA   |

| Power-On Re                 | eset (POR)                         |                                                                                                | <u> </u> |      |      |      |

| $V_{\text{trip(POR)}}$      | power-on reset trip voltage        | HIGH level                                                                                     | 0.65     | 0.76 | 1.01 | V    |

| •                           |                                    | LOW level                                                                                      | 0.60     | 0.72 | 0.91 | V    |

| Oscillator (pir             | ns OSC_IN and OSC_OUT)             |                                                                                                | <u>'</u> |      |      |      |

| Crystal oscilla             | ator mode                          |                                                                                                |          |      |      |      |

| C <sub>shunt</sub>          | shunt capacitance                  |                                                                                                | -        | -    | 7    | pF   |

| C <sub>L(ext)</sub>         | external load capacitance          | per pin [2]                                                                                    | _        | 10   | -    | pF   |

Table 11. Static characteristics...continued

$T_j$  = -40 °C to +125 °C; all voltages are defined with respect to ground unless otherwise specified; positive currents flow into the IC.<sup>[1]</sup>

| Symbol                 | Parameter                               | Conditions                            | Min                                      | Тур | Max                                      | Uni |

|------------------------|-----------------------------------------|---------------------------------------|------------------------------------------|-----|------------------------------------------|-----|

| Clock mode             | ;                                       |                                       |                                          | '   |                                          |     |

| C <sub>cpl(ext)</sub>  | external coupling capacitor             |                                       | -                                        | 100 | -                                        | pF  |

| V <sub>i(OSC_IN)</sub> | input voltage on pin OSC_IN             | peak-to-peak voltage                  | 0.20                                     | -   | V <sub>DDA(OSC)</sub>                    | V   |

| I/O pins               |                                         |                                       |                                          |     | 1                                        |     |

| pins SPI, JT           | TAG, CLK_OUT, PTP_CLK, RST              | _N                                    |                                          |     |                                          |     |

| V <sub>IH</sub>        | HIGH-level input voltage                | 3.3 V signaling                       | 2.0                                      | -   | VDDx<br>+ 0.5 <sup>[3]</sup>             | V   |

|                        |                                         | 2.5 V signaling                       | 1.7                                      | -   | VDDx<br>+ 0.5 <sup>[3]</sup>             | V   |

|                        |                                         | 1.8 V signaling                       | 0.65<br>×V <sub>DDx</sub> <sup>[3]</sup> | -   | V <sub>DDx</sub><br>+0.5 <sup>[3]</sup>  | V   |

| V <sub>IL</sub>        | LOW-level input voltage                 | 3.3 V signaling                       | -0.5                                     | -   | +0.8                                     | V   |

|                        |                                         | 2.5 V signaling                       | -0.5                                     | -   | +0.7                                     | V   |

|                        |                                         | 1.8 V signaling                       | -0.5                                     | -   | 0.35<br>×V <sub>DDx</sub> <sup>[3]</sup> | V   |

| V <sub>OH</sub>        | HIGH-level output voltage               | 3.3 V signaling                       | 2.8                                      | -   | 3.4                                      | V   |

|                        |                                         | 2.5 V signaling                       | 2.1                                      | -   | 2.5                                      | V   |

|                        |                                         | 1.8 V signaling                       | 1.4                                      | -   | 1.8                                      | V   |

| V <sub>OL</sub>        | LOW-level output voltage                | 3.3 V signaling                       | 0.19                                     | -   | 0.25                                     | V   |

|                        |                                         | 2.5 V signaling                       | 0.19                                     | -   | 0.25                                     | V   |

|                        |                                         | 1.8 V signaling                       | 0.19                                     | -   | 0.25                                     | V   |

| V <sub>hys(i)</sub>    | input hysteresis voltage                | CFG_PAD_xxx[yyy_IH] = 1; see [Ref. 8] | 0.1 ×<br>V <sub>DDx</sub> <sup>[3]</sup> | -   | -                                        | V   |

| R <sub>pu(weak)</sub>  | weak pull-up resistance                 |                                       | 40                                       | 50  | 57                                       | kΩ  |

| R <sub>pd(weak)</sub>  | weak pull-down resistance               |                                       | 40                                       | 50  | 57                                       | kΩ  |

| I <sub>OSH</sub>       | HIGH-level short-circuit output current |                                       | -                                        | -   | -111.7                                   | mA  |

| I <sub>OSL</sub>       | LOW-level short-circuit output current  |                                       | -                                        | -   | 110.2                                    | mA  |

| Ci                     | input capacitance                       | 1.8 V signaling                       | -                                        | -   | 5                                        | pF  |

| Z <sub>o</sub>         | output impedance                        |                                       | 40.0                                     | -   | 67.5                                     | Ω   |

| RGMII/RMII             | I/MII interface: pins TX_CLK, TX        | _EN, TX_ER, TXDx, RX_CLK, RX_ER, F    | RX_DV, RXD                               | х   |                                          |     |

| C <sub>i</sub>         | input capacitance                       |                                       | -                                        | -   | 5                                        | pF  |

| Z <sub>o</sub>         | output impedance                        | 1.8 V signaling                       |                                          |     |                                          |     |

|                        |                                         | low/medium/fast speed mode            | 36                                       | -   | 60                                       | Ω   |

|                        |                                         | high-speed mode                       | 26                                       |     | 45                                       | Ω   |

|                        |                                         | 2.5 V signaling                       |                                          |     |                                          |     |

SJA1105PQRS

All information provided in this document is subject to legal disclaimers.

Table 11. Static characteristics...continued

$T_j$  = -40 °C to +125 °C; all voltages are defined with respect to ground unless otherwise specified; positive currents flow into the IC.<sup>[1]</sup>

| Symbol              | Parameter                 | Conditions                               | Min                                            | Тур | Max                                          | Unit |

|---------------------|---------------------------|------------------------------------------|------------------------------------------------|-----|----------------------------------------------|------|

|                     |                           | low/medium/fast speed mode               | 35                                             | -   | 53                                           | Ω    |

|                     |                           | high-speed mode                          | 26                                             | -   | 40                                           | Ω    |

|                     |                           | 3.3 V signaling                          |                                                |     |                                              |      |

|                     |                           | low/medium/fast speed mode               | 34                                             | -   | 50                                           | Ω    |

|                     |                           | high-speed mode                          | 25                                             | -   | 38                                           | Ω    |

| V <sub>IH</sub>     | HIGH-level input voltage  | 3.3 V signaling                          | 2.0                                            | -   | V <sub>DD(MIIx)</sub> + 0.5 <sup>[4]</sup>   | V    |

|                     |                           | 2.5 V signaling                          | 1.7                                            | -   | V <sub>DD(MIIx)</sub> + 0.5 <sup>[4]</sup>   | V    |

|                     |                           | 1.8 V signaling                          | 0.65 ×<br>V <sub>DD(MIIx)</sub> <sup>[4]</sup> | -   | V <sub>DD(MIIx)</sub> + 0.5 <sup>[4]</sup>   | V    |

| V <sub>IL</sub> LOW | LOW-level input voltage   | 3.3 V signaling                          | -0.5                                           | -   | +0.8                                         | V    |

|                     |                           | 2.5 V signaling                          | -0.5                                           | -   | +0.7                                         | V    |

|                     |                           | 1.8 V signaling                          | -0.5                                           | -   | +0.35 × V <sub>DD(MIIX)</sub> <sup>[4]</sup> | V    |

| V <sub>OH</sub> F   | HIGH-level output voltage | I <sub>O</sub> = 4 mA                    |                                                |     |                                              |      |

|                     |                           | 3.3 V signaling                          | 2.8                                            | -   | 3.5                                          | V    |

|                     |                           | 2.5 V signaling                          | 2.1                                            | -   | 2.6                                          | V    |

|                     |                           | 1.8 V signaling                          | 1.4                                            | -   | 1.8                                          | V    |

| V <sub>OL</sub>     | LOW-level output voltage  | I <sub>O</sub> = 4 mA                    |                                                |     |                                              |      |

|                     |                           | 3.3 V signaling                          | 0.1                                            | -   | 0.2                                          | V    |

|                     |                           | 2.5 V signaling                          | 0.1                                            | -   | 0.2                                          | ٧    |

|                     |                           | 1.8 V signaling                          | 0.1                                            | -   | 0.2                                          | V    |

| $V_{hys(i)}$        | input hysteresis voltage  | CFG_PAD_xxx[yyy_IH] = 1;<br>see [Ref. 8] | 0.1 ×<br>V <sub>DD(MIIx)</sub> <sup>[4]</sup>  | -   | -                                            | V    |

| l <sub>osh</sub>    | HIGH-level short-circuit  | 1.8 V signaling                          |                                                |     |                                              |      |

|                     | output current            | low/medium/fast speed mode               | -                                              | -   | -51                                          | mA   |

|                     |                           | high-speed mode                          | -                                              | -   | -68                                          | mA   |

|                     |                           | 2.5 V signaling                          |                                                |     |                                              |      |

|                     |                           | low/medium/fast speed mode               | -                                              | -   | -78                                          | mA   |

|                     |                           | high-speed mode                          | -                                              | -   | -104                                         | mA   |

|                     |                           | 3.3 V signaling                          |                                                |     |                                              |      |

|                     |                           | low/medium/fast speed mode               | -                                              | -   | -118                                         | mA   |

|                     |                           | high-speed mode                          | -                                              | -   | -157                                         | mA   |

| losL                | LOW-level short-circuit   | 1.8 V signaling                          |                                                |     |                                              |      |

|                     | output current            | low/medium/fast speed mode               | -                                              | _   | 54                                           | mA   |

SJA1105PQRS

All information provided in this document is subject to legal disclaimers.

Table 11. Static characteristics...continued

$T_j$  = -40 °C to +125 °C; all voltages are defined with respect to ground unless otherwise specified; positive currents flow into the IC.<sup>[1]</sup>

| Symbol                            | Parameter                             | Conditions                                  | Min        | Тур                 | Max  | Unit |

|-----------------------------------|---------------------------------------|---------------------------------------------|------------|---------------------|------|------|

|                                   |                                       | high-speed mode                             | -          | -                   | 72   | mA   |

|                                   |                                       | 2.5 V signaling                             |            |                     |      |      |

|                                   |                                       | low/medium/fast speed mode                  | -          | -                   | 81   | mA   |

|                                   |                                       | high-speed mode                             | -          |                     | 108  | mA   |

|                                   |                                       | 3.3 V signaling                             |            |                     |      |      |

|                                   |                                       | low/medium/fast speed mode                  | -          | -                   | 118  | mA   |

|                                   |                                       | high-speed mode                             | -          | -                   | 157  | mA   |

| SGMII port; s                     | l<br>symbol and parameter formats i   | n this section are taken from the SGMII spo | ecificatio | n [ <u>Ref. 6</u> ] |      |      |

| C <sub>cpl(ext)</sub>             | external coupling capacitor           |                                             | -          | 100                 | -    | nF   |

| $R_{\text{cal}(\text{SGMII})}$    | SGMII calibration resistor            | 1 % tolerance, 20 mW                        | -          | 191                 | -    | Ω    |

| SGMII transr                      | mitter                                |                                             |            |                     |      |      |

| $V_{ring}$                        | output ringing                        | de-emphasis disabled                        | -          | -                   | 10   | %    |

| $ V_{OD} $                        | output differential voltage           | programmable                                | 250        | 350                 | 500  | mV   |

| $\Delta V_{O(dif)}$               | differential output voltage variation | between 0 and 1                             | -          | -                   | 10   | %    |

| Vos                               | output offset voltage                 | [5]                                         | 400        | 500                 | 600  | mV   |

| R <sub>o</sub>                    | output impedance (single-ended)       |                                             | 40         | 50                  | 60   | Ω    |