# Quick Start Guide S12ZVM32EVB

Highly Integrated Microcontroller Enhanced S12Z Core at 50 MHz Bus Speed Up to 32 KB Flash and 4 KB RAM

TOWER® SYSTEM DEVELOPMENT PLATFORM

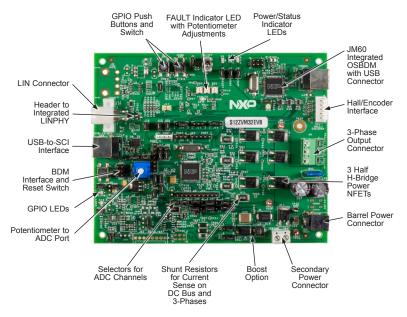

#### GET TO KNOW THE \$12ZVM32EVB BOARD

Front Side of the S12ZVM32EVB Board

#### INTRODUCTION AND DEFAULT SETTINGS

The S12ZVM32EVB features the S12ZVM128 microcontroller, an automotive 16-bit MCU for three-phase BLDC motor control applications. The S12ZVML31 integrates an S12Z CPU, a LIN physical interface, a 5 V regulator system to supply the microcontroller, and a gate driver unit (GDU) to drive up to six external power N-channel MOSFETs.

The board includes an onboard OSBDM, a USB-to-SCI interface, a resolver interface, a hall sensor interface, an external 4 MHz oscillator, current sense resistors, multiple op-amps for signal conditioning of voltage and current measurements, and the option for an external CAN transceiver.

Default jumper positions of the S12ZVM32EVB board are shown in the figure at right.

#### **Quick Start Guide**

#### SOFTWARE TOOLS INSTALLATION

#### 1 Install CodeWarrior® Development Studio

NXP®'s CodeWarrior development studio for MCUs integrates the development tools for several architectures, including the S12Z architecture, into a single product based on the Eclipse open development platform. Eclipse offers an excellent framework for building software development environments and is a standard framework used by many embedded software vendors.

The latest version of CodeWarrior for MCUs (Eclipse IDE) can be downloaded from **www.nxp.com/CodeWarrior**.

### 2 Download Additional Software

Visit **www.nxp.com/S12ZVM** and download our example codes, such as PMSM motor controller, BLDC motor controller, LIN Driver, MSCAN, HVI, etc.

#### JUMPER DEFAULT CONFIGURATION

| JUMPER | SETTING | DESCRIPTION                                              |

|--------|---------|----------------------------------------------------------|

| J4     | 1–2     | RESET LED indicator enabled                              |

| J5     | 1–2     | V <sub>DD</sub> LED indicator enabled                    |

| J6     | 1–2     | V <sub>SUP</sub> LED indicator enabled                   |

| J9     | 1–2     | PT1 "ON/OFF" switch enabled                              |

| J10    | Open    | OSBDM boot loader disabled                               |

| J12    | 1–2     | Resolver (+5 VDC) supplied from V <sub>DDX</sub>         |

| J14    | 2–3     | PP0 connected to supply EVDD to hall sensor interface    |

| J16    | 1–2     | PT2 connected to Hall/encoder Phase B                    |

| J18    | 1–2     | V <sub>DDX</sub> supplies 5 V to the USB-to-SCI isolator |

| J19    | 1–2     | PP1 "UP" push button enabled                             |

| J20    | 1–2     | PP2 "DOWN" push button enabled                           |

| J27    | 2–3     | SCI1 RXD connected to USB-to-SCI                         |

| J28    | 2–3     | SCI1 TXD connected to USB-to-SCI                         |

| J29    | 1–2     | V <sub>DDX</sub> supplies 5 V to BDM header              |

| J30    | 1–2     | V <sub>DDX</sub> supplies 5 V to ADC potentiometer       |

| J33    | 1–2     | MCU V <sub>SUP</sub> connected                           |

| J35    | 1–2     | PAD0 (AMP0) connected to external gain setting resistors |

| J36    | 1–2     | V <sub>REF</sub> generation supplied from VSUP enable    |

| J37    | 1–2     | PS4 "User LED 1" enabled                                 |

| J40    | 1–2     | V <sub>SUP</sub> supply to V <sub>DDX</sub> ballast      |

#### JUMPER DEFAULT CONFIGURATION (CONT.)

| JUMPER  | SETTING | DESCRIPTION                                                                         |

|---------|---------|-------------------------------------------------------------------------------------|

|         |         |                                                                                     |

| J44     | 1–2     | PAD1 (AMPM0) connected to external gain setting resistors                           |

| J45     | 1–2     | PAD2 (AMPP0) connected to external gain setting resistors                           |

| J46     | 1–2     | PAD3 (AN0_3) connected to ADC_IA (Phase A current sense from external op-amp)       |

| J47     | 1–2     | PAD4 (AN0_4) connected to ADC_IB (Phase B current sense from external op-amp)       |

| J48     | 1–2     | PAD5 (AMP1) connected to external gain setting resistors                            |

| J50     | 1–2     | PAD6 (AMPM1) connected to external gain setting resistors                           |

| J51/J42 | 1–2     | PAD7 (AMPP1) connected to external gain setting resistors                           |

| J52     | 2–3     | PAD8 (AN1_3) connected to ADC_IC (Phase C current sense from external op-amp)       |

| J53     | 1–2     | PS5 "User LED 2" enabled                                                            |

| J55     | 1–2     | V <sub>REF</sub> supplied from V <sub>DDX</sub>                                     |

| J57     | 2–3     | Current sense op-amp inverting input connected to Ground (DC Bus current sense)     |

| J60     | 2–3     | Current sense op-amp non-inverting input connected to DC Bus (DC Bus current sense) |

| J63     | 1–2     | V <sub>DDX</sub> supply 5 V to FAULT comparator circuits                            |

#### JUMPER LIST AND DESCRIPTION

| JUMPER | DESCRIPTION                                                                                  |

|--------|----------------------------------------------------------------------------------------------|

| J2     | CAN transceiver 5 V supply option                                                            |

| JZ     | Closing this jumper, the $V_{_{DDC}}$ ballast transistor is supplied from VSUP               |

| J3     | V <sub>DDC</sub> supplied from USB option                                                    |

| 13     | Closing this jumper, the $V_{_{DDC}}$ node is supplied from the USB-to-SCI interface         |

| J4     | RESET LED indicator option                                                                   |

| J4     | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                                        |

| J5     | V <sub>DDX</sub> LED indicator option                                                        |

| 12     | Closing this jumper, the LED indicator for $V_{_{\rm DDX}}$ is connected to $V_{_{\rm DDX}}$ |

| .16    | V <sub>SUP</sub> LED indicator option                                                        |

| JO     | Closing this jumper, the LED indicator for $V_{_{\rm SUP}}$ is connected to $V_{_{\rm SUP}}$ |

| J9     | ON/OFF switch option                                                                         |

| 19     | Closing this jumper connects the "ON/OFF" GPIO switch to port PT1                            |

| J10    | OSBDM boot-loader option                                                                     |

| 510    | Closing this jumper, the OSBDM enters in boot-loader mode                                    |

| J12    | Resolver circuit 5 V supply option                                                           |

| JIZ    | Closing this jumper connects $V_{\text{DDX}}$ to supply 5 V at the Resolver circuit          |

|        | EVDD or FAULT selector                                                                       |

| J14    | Pins 1-2 closed: FAULT input is connected to port PP0                                        |

|        | Pins 2-3 closed: Port PP0 is connected to EVDD at Hall sensor interface                      |

| JUMPER | DESCRIPTION                                                                            |

|--------|----------------------------------------------------------------------------------------|

| J15    | Resolver or Hall/encoder Phase A selector                                              |

|        | Pins 1-2 closed: Phase A from Resolver is connected to port PT1                        |

|        | Pins 2-3 closed: Phase A from Hall/encoder interface is connected to port PT1          |

|        | Resolver or Hall/encoder Phase B selector                                              |

| J16    | Pins 1-2 closed: Phase B from Hall/encoder interface is connected to port PT2          |

|        | Pins 2-3 closed: Phase B from Resolver is connected to port PT2                        |

| 110    | USB-to-SCI interface supply option                                                     |

| J18    | Closing this jumper, $V_{_{DDX}}$ supplies 5 V to the USB-to-SCI isolator              |

| J19    | "UP" push-button option                                                                |

| 119    | Closing this jumper, the "UP" GPIO push button is connected to port PP1                |

| .120   | "DOWN" push-button option                                                              |

| J20    | Closing this jumper, the "DOWN" GPIO push button is connected to port PP2              |

|        | SCI RXD selector                                                                       |

| J27    | Pins 1-2 closed: RXD from OSBDM is connected to port PS2                               |

|        | Pins 2-3 closed: RXD from USB-to-SCI is connected to port PS2                          |

|        | SCI TXD selector                                                                       |

| J28    | Pins 1-2 closed: TXD from OSBDM is connected to port PS3                               |

|        | Pins 2-3 closed: TXD from USB-to-SCI is connected to port PS3                          |

| 100    | BDM interface supply option                                                            |

| J29    | Closing this jumper, the 5 V pin on the BDM interface is connected to $V_{\text{DDX}}$ |

| JUMPER | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J30    | ADC potentiometer pull-up option                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| J30    | Closing this jumper, V <sub>DDX</sub> supplies 5 V to POT 1 (ADC potentiometer)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| J33    | Microcontroller supply option                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 133    | ADC potentiometer pull-up option   Closing this jumper, $V_{oDX}$ supplies 5 V to POT 1 (ADC potentiometer)   Microcontroller supply option   Closing this jumper connects the $V_{SUP}$ pin of the MCU to the supply voltage   ADC mapping – PAD0   Pins 1-2 closed – Connects PAD0 to AMP0 external gain-setting resistors   Pins 2-3 closed – Connects PAD0 to POS_SIN resolver output $V_{REF}$ generation supply option   Closing this jumper connects $V_{SUP}$ to supply a regulated voltage at $V_{REF2}$ USER LED1 option   Closing this jumper, the GPIO LED1 is connected to port PS4   Resolver Phase B selector   Pins 1-2 closed – SINCOS I/O connector Phase B connected to Resolver Phase B input   Pins 2-3 closed – POS_COS connected to Resolver Phase B input   VD <sub>DX</sub> ballast supply option   Closing this jumper, the $V_{DX}$ ballast is connected to $V_{SUP}$ |

|        | ADC mapping – PAD0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| J35    | Pins 1-2 closed – Connects PAD0 to AMP0 external gain-setting resistors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|        | Pins 2-3 closed – Connects PAD0 to POS_SIN resolver output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| J36    | V <sub>REF</sub> generation supply option                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 130    | Closing this jumper connects $V_{SUP}$ to supply a regulated voltage at $V_{REF2}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| J37    | USER LED1 option                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| J37    | Closing this jumper, the GPIO LED1 is connected to port PS4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|        | Resolver Phase B selector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| J39    | Pins 1-2 closed – SINCOS I/O connector Phase B connected to Resolver<br>Phase B input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|        | Pins 2-3 closed – POS_COS connected to Resolver Phase B input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 140    | VD <sub>DX</sub> ballast supply option                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| J40    | Closing this jumper, the V <sub>DDX</sub> ballast is connected to V <sub>SUP</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|        | Resolver circuit 12 V supply option                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| J43    | Closing this jumper, the 12 V supply to the resolver circuit op-amps is supplied from $\rm V_{SUP}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| JUMPER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DESCRIPTION                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ADC mapping—PAD1                                                                        |

| J44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Closing this jumper, PAD1 is connected to the AMPM0 external gain-setting resistors     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ADC mapping—PAD2                                                                        |

| ADC mapping—PAD1<br>Closing this jumper, PAD1 is connected to the A<br>resistors<br>ADC mapping—PAD2<br>Closing this jumper, PAD2 is connected to the A<br>resistors<br>ADC mapping—PAD2<br>Closing this jumper, PAD2 is connected to the A<br>resistors<br>ADC mapping—PAD3<br>Pins 1-2 closed—connects PAD3 to ADC_IA (PI<br>external op-amp)<br>Pins 2-3 closed—connects PAD3 to ADC_IA (PI<br>external op-amp)<br>Pins 2-3 closed—connects PAD3 to ADC_IA (PI<br>external op-amp)<br>Pins 2-3 closed—connects PAD3 to ADC_IB (PI<br>external op-amp)<br>Pins 2-3 closed—connects PAD4 to ADC_IB (PI<br>external op-amp)<br>Pins 2-3 closed—connects PAD4 to ADC potent<br>ADC mapping—PAD5<br>Pins 1-2 closed—connects PAD5 to AMP1 external | Closing this jumper, PAD2 is connected to the AMPP0 external gain-setting resistors     |

| J46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ADC mapping—PAD3                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Pins 1-2 closed—connects PAD3 to ADC_IA (Phase A current sense from external op-amp)    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Pins 2-3 closed—connects PAD3 to POS_SIN resolver output                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ADC mapping—PAD4                                                                        |

| J47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Pins 1-2 closed—connects PAD4 to ADC_IB (Phase B current sense from<br>external op-amp) |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Pins 2-3 closed—connects PAD4 to ADC potentiometer POT1                                 |

| J48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ADC mapping—PAD5                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Pins 1-2 closed—connects PAD5 to AMP1 external gain setting resistors                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Pins 2-3 closed—connects PAD5 to ADC_IB (Phase B current sense from external op-amp)    |

| JUMPER                | DESCRIPTION                                                                          |

|-----------------------|--------------------------------------------------------------------------------------|

|                       | Resolver phase A selector                                                            |

| J49                   | Pins 1-2 closed—resolver Phase A connected to SINCOS I/O connector Phase A input     |

|                       | Pins 2-3 closed—resolver Phase A connected to Resolver POS_SIN Schmitt-<br>Trigger   |

|                       | ADC mapping—PAD6                                                                     |

| J50<br>J51/J42<br>J52 | Pins 1-2 closed—connects PAD6 to AMPM1 external gain-setting resistors               |

|                       | Pins 2-3 closed—connects PAD6 to POS_COS resolver output                             |

| J51/J42               | ADC mapping—PAD7                                                                     |

|                       | J51 pins 1-2 closed—connects PAD7 to AMPP1 external gain-setting resistors           |

|                       | J51 pins 2-3 closed—connects PAD7 to POS_SIN resolver output                         |

|                       | J51 pin 2 to J42 pin 1 closed—connects PAD7 to ADC potentiometer POT1                |

|                       | ADC mapping—PAD8                                                                     |

| J52                   | Pins 1-2 closed—connects PAD8 to ADC_IC (Phase C current sense from external op-amp) |

| J51/J42<br>J52<br>J53 | Pins 2-3 closed—connects PAD8 to POS_COS resolver output                             |

| 150                   | USER LED2 option                                                                     |

| 123                   | Closing this jumper, the GPIO LED2 is connected to port PS5                          |

|                       | V <sub>REF</sub> selector                                                            |

| J55                   | Pins 1-2 closed—V <sub>REF</sub> supplied from V <sub>DDX</sub>                      |

|                       | Pins 2-3 closed—V <sub>REF</sub> supplied from the V <sub>REF2</sub> regulator       |

| JUMPER | DESCRIPTION                                                                                       |

|--------|---------------------------------------------------------------------------------------------------|

|        | Resolver COS reference                                                                            |

| J56    | Pins 1-2 closed: Input to POS_COS circuit is from OFFSET1                                         |

|        | Pins 2-3 closed: Input to POS_COS circuit is from RES_COS_REF                                     |

|        | Internal AMP0 input selector (inverting)                                                          |

| J57    | Pins 1-2 closed—connects DC Bus to the internal AMP0 inverting input (Phase A current sense)      |

|        | Pins 2-3 closed—connects Ground to the internal AMP0 inverting input (DC Bus current sense)       |

|        | Resolver SIN reference                                                                            |

| J59    | Pins 1-2 closed: Input to POS_SIN circuit is from RES_SIN_REF                                     |

|        | Pins 2-3 closed: Input to POS_SIN circuit is from OFFSET1                                         |

|        | Internal AMP0 input selector (non-inverting)                                                      |

| J60    | Pins 1-2 closed—connects Phase A to the internal AMP0 non-inverting input (Phase A Current sense) |

|        | Pins 2-3 closed—connects DC Bus as non-inverting input for internal AMP0 (DC Bus current sense)   |

| 100    | FAULT comparators 5 V supply option                                                               |

| J63    | Closing this jumper connects V <sub>DDX</sub> to supply 5 V at the FAULT circuit                  |

#### HEADERS AND CONNECTORS LIST

| HEADER/CONNECTOR | DESCRIPTION                                                            |

|------------------|------------------------------------------------------------------------|

| .11              | External BDM connector for OSBDM                                       |

| JI               | (1. BKGD, 2. Ground, 3. PDO, 4. RESET, 5. PDOCLK, 6. V <sub>DD</sub> ) |

| J7               | OSBDM USB connector                                                    |

| J8               | CAN connector                                                          |

| <b>JO</b>        | (1. MSCAN_H, 2. MSCAN_L, 3. Open, 4. Open)                             |

| J11              | Hall sensor/encoder interface                                          |

| JII              | (1. EVDD, 2. GND, 3. Ph-A, 4. Ph-B, 5. Ph-C)                           |

| J13              | LIN connector                                                          |

| 112              | (1. GND, 2. GND, 3. +12 V [HD], 4. LIN)                                |

| J17              | LINPHY interface                                                       |

| 517              | (1. LPRXD, 2. LPTXD)                                                   |

| .121             | Port P Header                                                          |

| JZT              | (1. PP0, 2. PP1, 3. PP2, 4. GND)                                       |

| J22              | Port E Header                                                          |

| JZZ              | (1. PE0, 2. PE1, 3. GND)                                               |

| J23              | Port T Header                                                          |

| JZJ              | (1. PT3, 2. PT2, 3. PT1, 4. PT0, 5. GND)                               |

| J24              | Three-Phase Motor power output connector                               |

| J25              | USB-to-SCI USB connector                                               |

#### HEADERS AND CONNECTORS LIST (CONT.)

| HEADER/CONNECTOR | DESCRIPTION                                                                       |

|------------------|-----------------------------------------------------------------------------------|

| J31              | Port S Header                                                                     |

| J21              | (1. PS0, 2. PS1, 3. PS2, 4. PS3, 5. PS4, 6. PS5, 7. GND)                          |

| J34              | External BDM connector for S12ZVM MCU                                             |

| J38              | Header for extended debug interface                                               |

| 120              | (1. PDOCLK, 2. PDO)                                                               |

|                  | Port AD Header                                                                    |

| J41              | (1. AN0, 2. AN1, 3. AN2, 4. AN3, 5. AN4, 6. AN5, 7. AN6, 8. AN7, 9. AN8, 10. GND) |

| J54              | DC connector for wall power supply                                                |

| J58              | Alternative power supply connector                                                |

| J61              | SINCOS I/O Connector                                                              |

| 101              | (1. Phase A, 2. SIN, 3. Phase B, 4. COS, 5. GND, 6. +5VA)                         |

|                  | Resolver I/O Connector                                                            |

| J62              | (1. GEN_P, 2. GEN_M, 3. SIN, 4. SIN_REF, 5. COS, 6. COS_<br>REF, 7. GND, 8. +5VA) |

| J64              | Alternative connector (blade) for power supply (+12 V) input                      |

| J65              | Alternative connector (blade) for ground                                          |

#### POTENTIOMETERS

| POTENTIOMETER | DESCRIPTION                                            |

|---------------|--------------------------------------------------------|

| R59           | POT1, routable to ADC input AN8                        |

| R78           | Resolver generator gain setting potentiometer          |

| R77           | Resolver interface offset adjustment                   |

| R20           | Phase current threshold setting for FAULT5 generation  |

| R123          | DC Bus voltage threshold setting for FAULT5 generation |

#### LEDS

| - |

|---|

#### SUPPORT

Visit **www.nxp.com/support** for a list of phone numbers within your region.

#### WARRANTY

Visit **www.nxp.com/warranty** for complete warranty information.

#### www.nxp.com

NXP, the NXP logo and CodeWarrior are trademarks of NXP B.V. All other product or service names are the property of their respective owners. © 2015–2016 NXP B.V.

Doc Number: S12ZVM32EVBQS REV 1 Agile Number: 926-28636 REV B

## **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

NXP: S12ZVM32EVB