# PTN38003A

### Multi-protocol USB3.2 and DisplayPort linear redriver

Rev. 2.1 — 8 December 2021

Product data sheet

### 1 General description

PTN38003A is a high-performance USB3.2/DisplayPort multi-protocol linear redriver that is optimized for USB3.2 and DisplayPort applications on either the downstream facing port (DFP) or upstream facing port (UFP) application.

PTN38003A addresses high-speed signal quality enhancement requirements for implementation of USB Type-C interface in a platform that supports the USB Type-C, VESA DisplayPort Alternate Mode standards. This device also implements the snooping monitor of the sideband signals from DP mode (AUX) to optimize the configuration, power saving mode and performance.

The device provides programmable linear equalization, output swing linearity control by pin strapping or I<sup>2</sup>C control to improve signal integrity and enable channel extension by reducing inter-symbol interference (ISI). DisplayPort AUX snooping is performed to follow relevant DisplayPort source-sink AUX transactions and configure the redriver to meet link requirements.

For USB operation, PTN38003A has built-in advanced power management capability that enables significant power saving under USB3.2 low power modes (U2/U3). It detects LFPS (Low Frequency Periodic Signaling)/LBPM (LFPS Based PWM Message) signaling to configure the operation (USB3.2 Gen 1/Gen 2 & x1/x2) and link electrical conditions and it activates/deactivates internal circuitry and logic dynamically. The device performs these actions without host software intervention and conserves power. The host processor keeps PTN38003A in deep power saving or USB mode until Alternate Mode has been entered.

The device is tailored to support USB3.2 electrical idle, receiver detection and power saving modes. It maintains two separate input signal detectors – loss of high-speed signal (LOS) and USB LFPS detectors with built-in hysteresis.

For DisplayPort (DP) operation, PTN38003A monitors the AUX transactions and adjusts the DisplayPort channel setting during DP Link initialization and training.

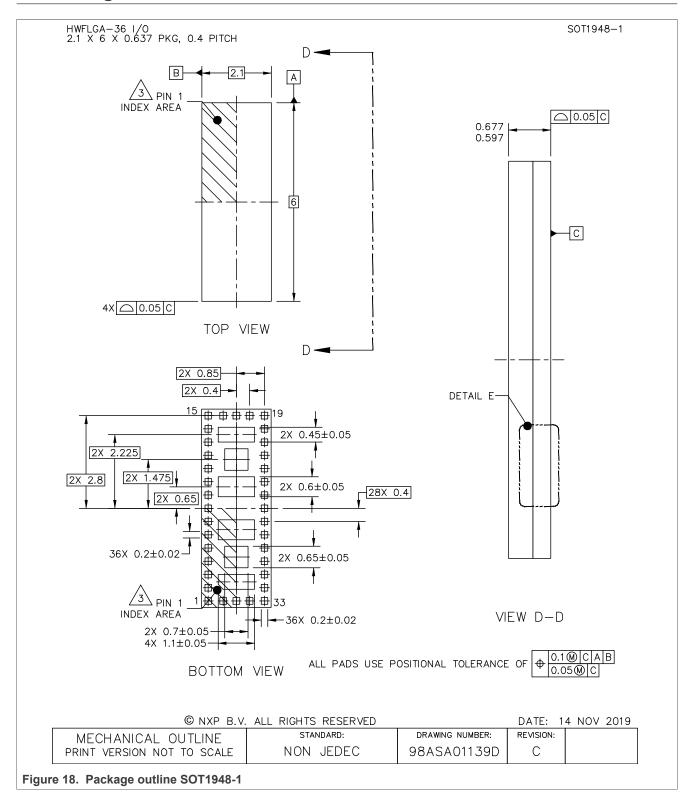

PTN38003A is powered from a 1.8 V supply. It is available in a small high performance HWFLGA36 package.

Multi-protocol USB3.2 and DisplayPort linear redriver

### 2 Features and benefits

- Flexible multi-protocol linear redriver supports three signaling combinations specified in USB Type-C and VESA specifications

- Mode 0: Deep Power saving

- Mode 1: USB3.2 Gen1x1/Gen1x2/Gen2x1/Gen2x2

- Mode 2: USB3.2 + DP 2-Lane + AUX snooping

- Mode 3: DP 4-Lane + AUX snooping

- Supports USB 3.2 Gen1x1, Gen 1x2, Gen2x1, Gen2x2 (5 Gbps and 10 Gbps)

- I<sup>2</sup>C register based Flat gain control

- Peaking gain of +12.1 dB at 5 GHz

- Output linearity control: 500 mVppd to 950 mVppd

- Support DP2.0 link rates at 1.62 Gbps (RBR), 2.7 Gbps (HBR), 5.4 Gbps (HBR2), 8.1 Gbps (HBR3),10 Gbps (UHBR10), 13.5 Gbps (UHBR13.5), 20 Gbps (UHBR20)

- DP AUX monitoring during DP link training to control DP channel

- I<sup>2</sup>C register based Flat gain control

- Peaking gain of 10.2 dB at 4.05 GHz, 20 dB at 10 GHz

- Output linearity control: 500 mVppd to 950 mVppd

- Compliant to DisplayPort, USB3.2 standard and USB Type-C Alternate Mode interoperability testing

- Implements USB Type-C Safe state conditions on all connector facing pins

- Configurable via I<sup>2</sup>C interface with a configurable address pin

- Integrated termination resistors provide impedance matching on both transmit and receive sides

- Supports maximum voltage limit (V<sub>voltage\_jump</sub>) to align to the latest USB3 specification and computing platform capabilities

- Autonomous Orientation detection of USB Type-C device connection

- RX equalizers on all high-speed inputs to compensate for signal attenuation

- Automatic receiver termination detection in USB mode

- Good linearity over the frequency band (50 MHz to 10.3 GHz) and voltage dynamic range

- Excellent Differential return loss performance: < -16 dB up to 10.3 GHz

- Flow-through pin-out to ease PCB layout and minimize crosstalk effects

- Very low crosstalk: DDNEXT < -50 dB up to 10.3 GHz

- Low active current consumption for output swing linearity control of 950 mVppd

- USB3.2 Gen2x2 or Gen1x2 (Mode 1) active power: 250 mA (typ)

- USB3.2 Gen2x1 or Gen1x1 (Mode 1) active power: 125 mA (typ)

- 1-lane DP HBR3/UHBR10/UHBR13.5/UHBR20 (Mode 2 or 3): 62 mA (typ)

- 2-lane DP HBR3/UHBR10/UHBR13.5/UHBR20 (Mode 2 or 3): 125 mA (typ)

- 4-lane DP only HBR3/UHBR10/UHBR13.5/UHBR20 (Mode 3): 250 mA (typ)

- · Power-saving states:

- USB3.2 (Mode 1)

- 0.22 mA (typ) when 2 lanes are enabled in USB3 U2/U3 states

- 0.11 mA (typ) when 1 lane is enabled in USB3 U2/U3 states

- 0.11 mA (typ) only Rx detection is enabled on 1 lane when no connection detected (USB Rx detection enabled)

- DisplayPort sleep D3 mode (Mode 3): 3.2 mA (typ)

- 10 µA (typ) when in deep power saving state

PTN38003A

### Multi-protocol USB3.2 and DisplayPort linear redriver

- · Hot Plug capable:

- Support Type-C plug connection through PD controller

- Power Supply 1.7 V to 1.9 V

- Small high performance HWFLGA36 package

- ESD HBM 1.5 kV, CDM 1 kV

- Operating temperature range -20 °C to +85 °C

### 3 Applications

- For USB Type-C host/source application

- Smartphones and tablets

- Notebooks, AIO and desktop computers

- Hub or dock devices

- For USB Type-C device/sink application

- Docking stations

- Display units

### 4 Ordering information

#### Table 1. Ordering information

| Type number | Topside | Package  |                                                                            |           |  |  |  |  |

|-------------|---------|----------|----------------------------------------------------------------------------|-----------|--|--|--|--|

| marking     |         | Name     | Description                                                                | Version   |  |  |  |  |

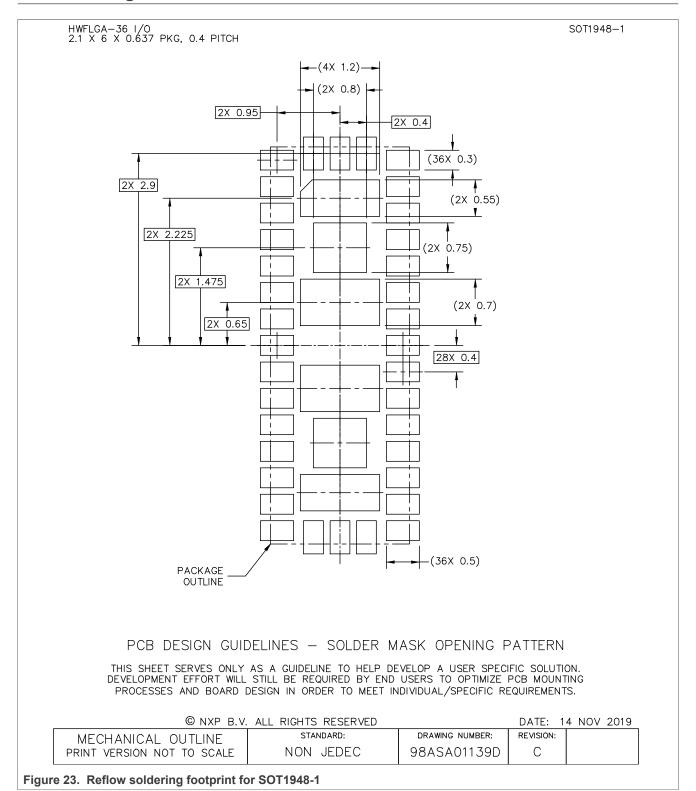

| PTN38003AEW | 3A      | HWFLGA36 | plastic thermal enhanced very very thin fine-pitch land grid array package | SOT1948-1 |  |  |  |  |

### 4.1 Ordering options

#### Table 2. Ordering options

| Type number | Orderable part number | Package  | J                             | Minimum order quantity | Temperature                        |

|-------------|-----------------------|----------|-------------------------------|------------------------|------------------------------------|

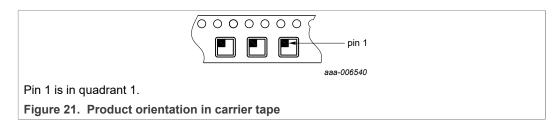

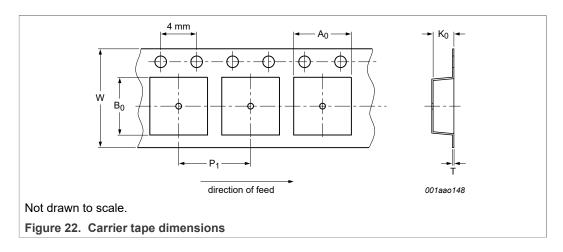

| PTN38003AEW | PTN38003AEWY          | HWFLGA36 | reel dry pack, SMD,<br>13" Q1 | 7000                   | T <sub>amb</sub> = -20 °C to 85 °C |

Multi-protocol USB3.2 and DisplayPort linear redriver

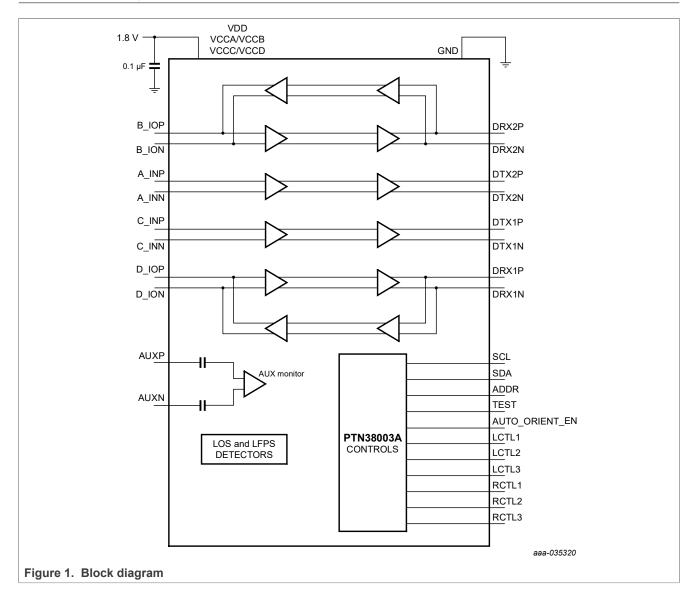

# 5 Block diagram

Multi-protocol USB3.2 and DisplayPort linear redriver

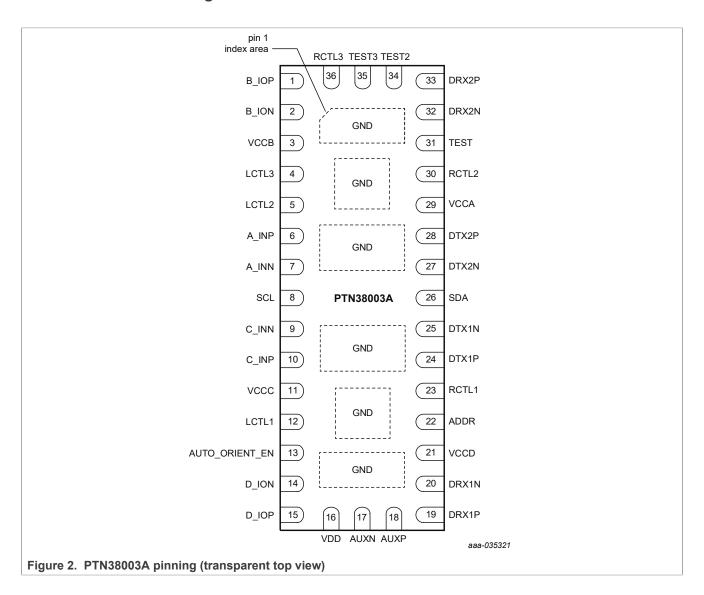

### 6 Pinning information

### 6.1 Pinning

### 6.2 Pin description

Table 3. Pin description

| Symbol | Pin   | Туре                         | Description                                                                                                                               |

|--------|-------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | B_IOP | Self-biasing                 | Differential signal high-speed input/output. B_IOP makes                                                                                  |

| 2      | B_ION | differential<br>input/output | a differential pair with B_ION. The associated output/ input pair is DRX2P and DRX2N. The I/O configuration is controlled by mode setting |

Table 3. Pin description...continued

| Symbol | Pin                | Туре                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|--------|--------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 3      | VCCB               | Power pins                   | These dedicated power pins for high-speed differential                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| 11     | VCCC               | for high-<br>speed paths     | pairs provide good signal integrity and isolation                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 21     | VCCD               |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| 29     | VCCA               |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

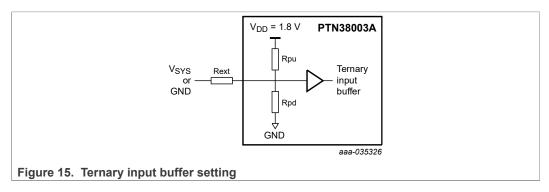

| 4      | LCTL3              | Ternary Input                | Ternary Input for controlling Output Swing Linearity on the downstream side of the redriver. Please refer to Table 10 for details                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 12     | LCTL1              | Ternary input                | LCTL1 and LCTL2 are EQ Peaking Gain setting pins for                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 5      | LCTL2              |                              | inputs on upstream side of the redriver. Please refer to<br><u>Table 8</u> for details                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| 6      | A_INP              | Self-biasing                 | Differential signal from high-speed RX path. A_INP makes                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 7      | A_INN              | differential input           | a differential pair with A_INN. The associated TX output pair is DTX2P and DTX2N                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

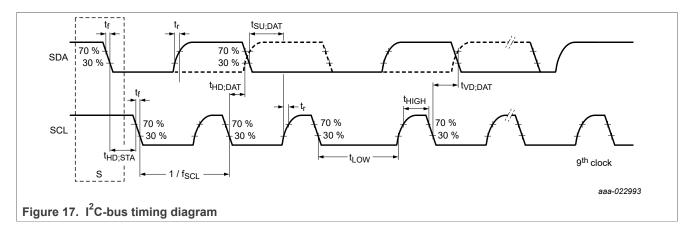

| 8      | SCL                | Open Drain input             | When operating in I <sup>2</sup> C mode, this pin is slave I <sup>2</sup> C clock pin, and external pull-up resistor to I <sup>2</sup> C supply (1.8 V or 3.3 V) is required                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 9      | C_INN              | Self-biasing                 | Differential signal from high-speed RX path. C_INP                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| 10     | C_INP              | differential input           | makes a differential pair with C_INN. The associated TX output pair is DTX1P and DTX1N                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| 13     | AUTO_<br>ORIENT_EN | Binary input                 | <ul> <li>Input for Auto Orientation Detection Enable:</li> <li>If the pin input is HIGH, Autonomous orientation detection of USB-C connection is enabled</li> <li>If this pin is LOW, Autonomous orientation detection of USB-C connection is disabled</li> <li>The pin can be either strapped in the application or connected to host processor. The pin is sampled at POR for initiating orientation detection process. This pin has a weak internal pulldown resistor (2 MΩ typ) to GND.</li> </ul> |  |  |  |  |  |

| 14     | D_ION              | Self-biasing                 | Differential signal high-speed input/output. D_IOP makes                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 15     | D_IOP              | differential<br>input/output | a differential pair with D_ION. The associated output/ input pair is DRX1P and DRX1N. The I/O configuration is controlled by mode setting                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| 16     | VDD                | Power                        | 1.8 V Supply for I <sup>2</sup> C, AUX snooping and digital blocks                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| 17     | AUXN               | Input                        | DP AUX channel snooping input                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 18     | AUXP               |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| 19     | DRX1P              | Self-biasing                 | Differential signal high-speed input/output. DRX1P makes                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 20     | DRX1N              | differential<br>input/output | a differential pair with DRX1N. The associated output/input pair is D_IOP and D_ION. The I/O configuration is controlled by mode setting                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

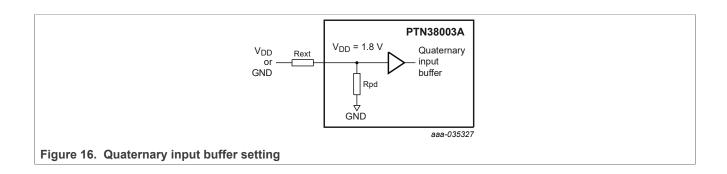

| 22     | ADDR               | Quaternary<br>Input          | I <sup>2</sup> C slave address selection pin in I <sup>2</sup> C mode                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 23     | RCTL1              | Ternary input                | RCTL1 and RCTL2 are EQ Peaking Gain setting pins for                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 30     | RCTL2              |                              | inputs on downstream side of the redriver. Please refer to Table 8 for details                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

Table 3. Pin description...continued

| Symbol      | Pin   | Туре                                  | Description                                                                                                                                                                                       |  |  |  |  |

|-------------|-------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 24          | DTX1P | Self-biasing                          | Differential signal of high-speed TX path. DTX1P makes a                                                                                                                                          |  |  |  |  |

| 25          | DTX1N | differential output                   | differential pair with DTX1N. The associated RX input pair is C_INP and C_INN                                                                                                                     |  |  |  |  |

| 26          | SDA   | Binary open<br>drain input/<br>output | When PTN38003A is operating in I <sup>2</sup> C mode, this pin is slave I <sup>2</sup> C Data pin, and external pull-up resistor to I <sup>2</sup> C supply (1.8 V or 3.3 V) is required          |  |  |  |  |

| 27          | DTX2N | Self-biasing                          | Differential signal of high-speed TX path. DTX2P makes a                                                                                                                                          |  |  |  |  |

| 28          | DTX2P | differential<br>output                | differential pair with DTX2N. The associated RX input p is A_INP and A_INN                                                                                                                        |  |  |  |  |

| 31          | TEST  | Reserved<br>Test pin                  | Reserved for test purpose only. Must be connected to GND in the system application                                                                                                                |  |  |  |  |

| 32          | DRX2N | Self-biasing                          | Differential signal high-speed input/output. DRX2P makes a differential pair with DRX2N. The associated output/input pair is B_IOP and B_ION. The I/O configuration is controlled by mode setting |  |  |  |  |

| 33          | DRX2P | differential input/output             |                                                                                                                                                                                                   |  |  |  |  |

| 34          | TEST2 | Reserved                              | These pins are left open/unconnected                                                                                                                                                              |  |  |  |  |

| 35          | TEST3 |                                       |                                                                                                                                                                                                   |  |  |  |  |

| 36          | RCTL3 | Ternary input                         | Ternary input for controlling Output Swing Linearity on the upstream side of the redriver. Please refer to Table 10 for details                                                                   |  |  |  |  |

| Center pads | GND   |                                       | These 6 center pads must be connected to GND plane for both electrical grounding and thermal relief                                                                                               |  |  |  |  |

Multi-protocol USB3.2 and DisplayPort linear redriver

### 7 Functional description

#### 7.1 USB3.2 operation

PTN38003A supports USB3.2 Redriver operation at Gen1 (5 Gbps) and Gen2 (10 Gbps) data rates. The receive equalization – peaking gain and output linearity control are configured either via I<sup>2</sup>C register settings or pin strapping.

PTN38003A has implemented an advanced power management scheme that operates in tune with USB Bus electrical condition. Though the device does not decode USB power management commands (related to USB3 U1/U2/U3 transitions) exchanged between USB Host and Peripheral/Device, it relies on bus electrical conditions and control pins/ register settings to decide to be in one of the following states:

- Active state wherein device is fully operational. In this state, USB connection exists and the Receive Termination remains active.

- Power-saving state wherein some portions of the TX and RX channels are kept enabled. In this state, LOS detector, LFPS/LBPM detection and/or Receive termination detection circuitry are active. Based on USB connection, there are two possibilities,

- No USB connection (also called Rx-detect state)

- Receive Termination detection circuitry keeps polling periodically

- RX and TX signal paths (including LOS detector) are not enabled

- Receive Termination is not active

- When USB connection exists and when the link is in USB U2/U3 mode,

- Receive Termination detection circuitry keeps polling periodically

- RX and TX signal paths are not enabled; LOS detector is disabled, and LFPS detector is enabled.

- Receive Termination is active

#### 7.2 DisplayPort operation

PTN38003A supports DisplayPort v1.4/2.0 operation seamlessly at 1.62 Gbps, 2.7 Gbps, 5.4 Gbps, 8.1 Gbps, 10 Gbps, 13.5 Gbps, and 20 Gbps with receiver equalization and linearity control.

The DisplayPort mode is selected only when DP alternate mode has been entered by the host controller. The DisplayPort source can activate power down via AUX command. DP spec supports two modes – D0/active or D3/Low power mode. In D0 mode, the linear redriver data path is active depending on the state of the DP link. In D3 mode, the AUX snooping logic is active while high-speed path is disabled resulting in lower current consumption.

The DisplayPort lane count is configured during DisplayPort link training phase based on AUX communication exchanges between source and sink.

PTN38003A performs equalization control for DP signals, and can be configured by LCTL[3:1] and RCTL[3:1] settings through either I<sup>2</sup>C or pin strapping.

PTN38003A uses lane count information for configuring the transmitters and receivers. It is possible that only a subset of lanes gets selected during DP Link training and remaining lanes are not active. Depending on the number of lanes selected, PTN38003A is configured to operate with the selected lane count thereby saving power consumption on unused lanes.

Multi-protocol USB3.2 and DisplayPort linear redriver

### 7.2.1 AUX monitoring and configuration

PTN38003A monitors DP AUX communication exchanges that occur between DP source and DP sink. It detects AUX communication involving DPCD register controls – Lane count, sleep, wake and configures its operation suitably. AUX monitor function is enabled when operating mode is set to Mode 2 (USB+DP 2-Lane) or 3 (DP 4-Lane), and is disabled in other mode settings.

The list of DPCD registers (with only the relevant bit fields) supported are as follows:

- LANE COUNT SET

- SET POWER

- Other DPCD registers and I<sup>2</sup>C over AUX transactions are not decoded

Input receive equalization is determined by LCTL[2:1] pins, and output linearity is controlled by LCTL3.

All lanes of DP redriver can be configured separately on a per lane basis using  $I^2C$ . When the Lane-Count is set via AUX, then the legal values are 1,2,4. If AUX tries to set it to 0, PTN38003A ignores it, and continues with the last known legal value. When the Lane-Count is set via  $I^2C$ , then the legal values are 0,1,2,4. If  $I^2C$  sets it to 0, PTN38003A disables all the lanes.

- Operational Mode = 0/1, DP Lane count = 0

- Operational Mode = 2, DP Lane count = 1 or 2

- Operational Mode = 3, DP lane count = 1, 2 or 4

### 7.3 Signal detectors

PTN38003A implements two types of signal detectors:

- LFPS detector: This is used in detect LFPS signaling on high speed data path. This is implemented only on lanes wherein USB data flows.

- Loss of (High-speed) Signal detector (LOS detector): This is meant for detecting both

presence and absence of high-speed signal at the input pins over all protocols USB

and DP. The LOS detection is used to enter and exit from low power states.

Based on LOS detector output, PTN38003A turns off certain portions of the internal circuitry and optimizes current consumption under various modes: USB (U2/U3), DP (D3 mode), and especially under electrical idle conditions.

### 7.4 Linear redriver controls

PTN38003A allows for programming of linear redriver functions – equalizer and linearity on a per channel basis. Since the USB3.2 and DisplayPort input channels support different maximum data rates, the corresponding input equalization on those paths need to be tuned accordingly.

Each linear redriver channel path has individual control of

- Flat gain can be controlled via I<sup>2</sup>C register for all the high speed data paths

- Peaking gain referenced to the maximum data rate (or Nyquist channel) in that channel

- Output Linear Swing is set up based on selected input source signal amplitude and preemphasis and considering channel attenuation

PTN38003A

Multi-protocol USB3.2 and DisplayPort linear redriver

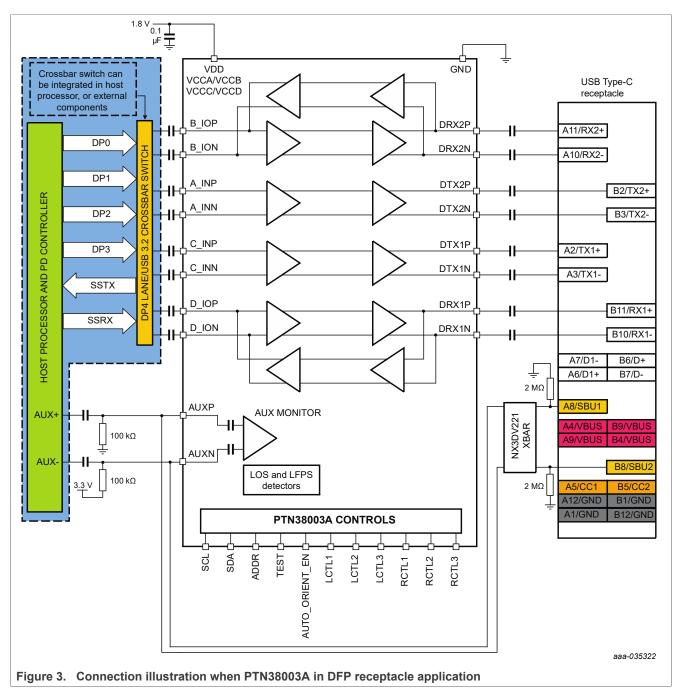

### 7.5 USB Type-C DFP receptacle application

Refer to <u>Figure 3</u> for using PTN38003A in USB Type-C DFP receptacle application. In this configuration, upstream side of PTN38003A is connected to host processor and downstream side is connected to Type-C receptacle.

Each pin on the downstream side of PTN38003A connecting to the Type-C connector has specific input/output configuration, and must match the signal assignments on the upstream side accordingly. Table 4 shows the downstream pin connection facing the Type-C receptacle.

PTN38003A

### Multi-protocol USB3.2 and DisplayPort linear redriver

Table 4. Downstream pin connection to Type-C receptacle in DFP application

| PTN38003A pins |          | USB Type-C receptacle pins |                   |  |  |  |

|----------------|----------|----------------------------|-------------------|--|--|--|

| Symbol         | Pin name | Symbol                     | Pin name          |  |  |  |

| 33             | DRX2P    | A11                        | RX2+              |  |  |  |

| 32             | DRX2N    | A10                        | RX2-              |  |  |  |

| 27             | DTX2N    | В3                         | TX2-              |  |  |  |

| 28             | DTX2P    | B2                         | TX2+              |  |  |  |

| 24             | DTX1P    | A2                         | TX1+              |  |  |  |

| 25             | DTX1N    | A3                         | TX1-              |  |  |  |

| 20             | DRX1N    | B10                        | RX1-              |  |  |  |

| 19             | DRX1P    | B11                        | RX1+              |  |  |  |

| 18             | AUXP     |                            | Input of SBU XBAR |  |  |  |

| 17             | AUXN     |                            | Input of SBU XBAR |  |  |  |

The upstream pins of PTN38003A are connected to the host processor, with specific functions assigned to each differential signal. For each pin assignment configuration below, PTN38003A controls which transmitters or receivers to turn on or turn off, and operating in USB3.2 or DP mode according to the mode setting.

Table 5. Upstream pin connection to host processor in DFP receptacle application

| PTN3800 | 3A pins     | Host proc | Host processor signal names |                                 |                     |        |                  |        |           |  |  |  |  |

|---------|-------------|-----------|-----------------------------|---------------------------------|---------------------|--------|------------------|--------|-----------|--|--|--|--|

| Symbol  | Pin<br>name | USB3.2    |                             | USB3.2<br>Gen1/2 x <sup>2</sup> | USB3.2<br>Gen1/2 x1 |        | USB3 + 2-Lane DP |        | 4-Lane DP |  |  |  |  |

|         |             | Normal    | Reversed                    | Normal                          | Reversed            | Normal | Reversed         | Normal | Reversed  |  |  |  |  |

| 14      | D_ION       | SSRX1-    | SSRX2-                      | SSRX-                           |                     | SSRX-  | ML0-             | ML3-   | ML0-      |  |  |  |  |

| 15      | D_IOP       | SSRX1+    | SSRX2+                      | SSRX+                           |                     | SSRX+  | ML0+             | ML3+   | ML0+      |  |  |  |  |

| 10      | C_INP       | SSTX1+    | SSTX2+                      | SSTX+                           |                     | SSTX+  | ML1+             | ML2-   | ML1+      |  |  |  |  |

| 9       | C_INN       | SSTX1-    | SSTX2-                      | SSTX-                           |                     | SSTX-  | ML1-             | ML2+   | ML1-      |  |  |  |  |

| 6       | A_INP       | SSTX2+    | SSTX1+                      |                                 | SSTX+               | ML1+   | SSTX+            | ML1+   | ML2+      |  |  |  |  |

| 7       | A_INN       | SSTX2-    | SSTX1-                      |                                 | SSTX-               | ML1-   | SSTX-            | ML1-   | ML2-      |  |  |  |  |

| 1       | B_IOP       | SSRX2+    | SSRX1+                      |                                 | SSRX+               | ML0+   | SSRX+            | ML0+   | ML3+      |  |  |  |  |

| 2       | B_ION       | SSRX2-    | SSRX1-                      |                                 | SSRX-               | ML0-   | SSRX-            | ML0-   | ML3-      |  |  |  |  |

Multi-protocol USB3.2 and DisplayPort linear redriver

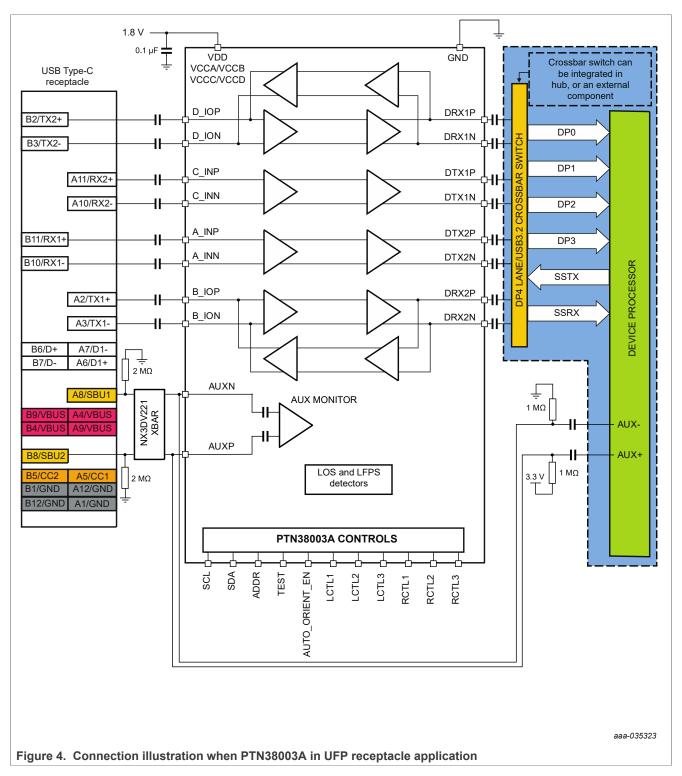

### 7.6 USB Type-C UFP receptacle application

Refer to Figure 4 for using PTN38003A in USB Type-C UFP receptacle application. In this configuration, downstream side of PTN38003A is connected to device processor while the upstream side is connected to Type-C receptacle.

PTN38003A

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved.

Multi-protocol USB3.2 and DisplayPort linear redriver

Each pin on the upstream side of PTN38003A connecting to the Type-C connector has specific input/output configuration, and must match the signal assignments on the downstream side accordingly. <u>Table 6</u> shows the upstream pin connection facing the Type-C receptacle.

Table 6. Upstream pin connection to Type-C receptacle in UFP application

| PTN38003A pins |          | USB Type-C re | USB Type-C receptacle pins |  |  |  |  |

|----------------|----------|---------------|----------------------------|--|--|--|--|

| Symbol         | Pin name | Symbol        | Pin name                   |  |  |  |  |

| 14             | D_IOP    | B2            | TX2+                       |  |  |  |  |

| 15             | D_ION    | В3            | TX2-                       |  |  |  |  |

| 9              | C_INN    | A10           | RX2-                       |  |  |  |  |

| 10             | C_INP    | A11           | RX2+                       |  |  |  |  |

| 6              | A_INP    | B11           | RX1+                       |  |  |  |  |

| 7              | A_INN    | B10           | RX1-                       |  |  |  |  |

| 1              | B_IOP    | A2            | TX1+                       |  |  |  |  |

| 2              | B_ION    | A3            | TX1-                       |  |  |  |  |

| 18             | AUXP     |               | Output of SBU XBAR         |  |  |  |  |

| 17             | AUXN     |               | Output of SBU XBAR         |  |  |  |  |

The downstream pins of PTN38003A are connected to the device processor, with specific functions assigned to each differential signal. For each pin assignment configuration below, PTN38003A controls which transmitters or receivers to turn on or turn off, and operating in USB3.2 or DisplayPort mode according to the mode setting.

Table 7. Downstream pin connection to device processor in UFP receptacle application

| PTN3800         | 3A pins | Device pro | ocessor signa | I names             |                      |        |                  |        |           |  |

|-----------------|---------|------------|---------------|---------------------|----------------------|--------|------------------|--------|-----------|--|

| Symbol Pin name |         |            |               | USB3.2<br>Gen 1/2 X | USB3.2<br>Gen 1/2 X1 |        | USB3 & DP 2-Lane |        | DP 4-Lane |  |

|                 |         | Normal     | Reversed      | Normal              | Reversed             | Normal | Reversed         | Normal | Reversed  |  |

| 20              | DRX1N   | SSTX2-     | SSTX1-        |                     | SSTX-                | ML0-   | SSTX-            | ML0-   | ML3-      |  |

| 19              | DRX1P   | SSTX2+     | SSTX1+        |                     | SSTX+                | ML0+   | SSTX+            | ML0+   | ML3+      |  |

| 24              | DTX1P   | SSRX2+     | SSRX1+        |                     | SSRX+                | ML1+   | SSRX+            | ML1+   | ML2+      |  |

| 25              | DTX1N   | SSRX2-     | SSRX1-        |                     | SSRX-                | ML1-   | SSRX-            | ML1-   | ML2-      |  |

| 28              | DTX2P   | SSRX1+     | SSRX2+        | SSRX+               |                      | SSRX+  | ML1+             | ML2+   | ML1+      |  |

| 27              | DTX2N   | SSRX1-     | SSRX2-        | SSRX-               |                      | SSRX-  | ML1-             | ML2-   | ML1-      |  |

| 33              | DRX2P   | SSTX1+     | SSTX2+        | SSTX+               |                      | SSTX+  | ML0+             | ML3+   | ML0+      |  |

| 32              | DRX2N   | SSTX1-     | SSTX2-        | SSTX-               |                      | SSTX-  | ML0-             | ML3-   | ML0-      |  |

Multi-protocol USB3.2 and DisplayPort linear redriver

#### 7.7 Control and programmability

#### 7.7.1 Power-on operational mode

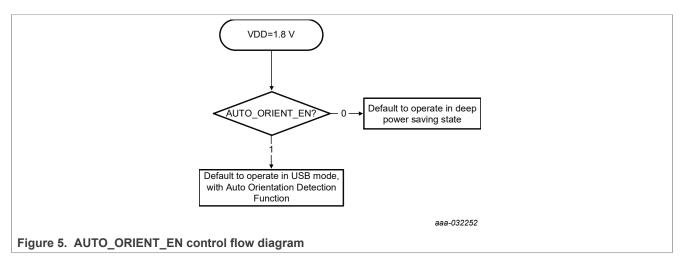

After POR initialization, if AUTO\_ORIENT\_EN pin is LOW, the chip is put into deep power saving state. In the deep power saving state, PTN38003A line drivers and input receive paths are terminated to ground with hi-ohmic resistors. If AUTO\_ORIENT\_EN pin is HIGH, then the device goes into USB mode of operation.

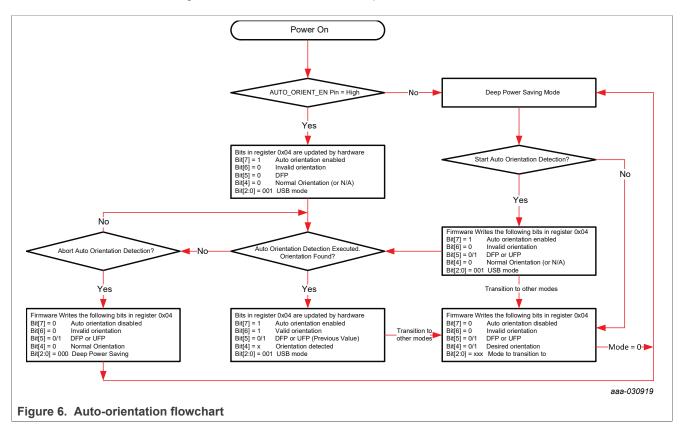

### 7.7.2 Auto Orientation Detection feature

PTN38003A is designed to detect the plug-in orientation autonomously based on SuperSpeed USB characteristics. This function may not work properly if SuperSpeed USB interface is not enabled in the host's or device's operation mode. Refer to <a href="Figure 6">Figure 6</a> for overall operating settings, and details are explained below.

Auto orientation detection feature is enabled through either setting AUTO\_ORIENT\_EN pin to high at power on reset, or through setting I<sup>2</sup>C register 0x04 bit 7 to 1. When auto orientation detection is enabled through AUTO\_ORIENT\_EN pin at power on reset, PTN38003A transitions to USB mode by default, and the auto orientation detection process is executed without any firmware intervention. After the orientation is determined, "orientation" bit (register 0x04 bit 4) is updated, with "orientation done" bit (register 0x04 bit 6) set to 1. Since there is no way to indicate DFP or UFP application mode at power up reset when the detection process is executed, reporting of orientation is based on DFP application use case. At the same time, LCTLx and RCTLx pin values are used to configure USB upstream and downstream channel conditions.

If this feature is not enabled at power on reset, it can be enabled separately through  $I^2C$  register 0x04 bit 7 when the device is programmed to operate in USB only mode (register 0x04 bit [2:0] = 001). In addition, DFP or UFP application mode can be programmed in register 0x04 bit 5. When auto orientation detection process is completed, valid orientation will be reported in register 0x04 bit 4, based on the DFP or UFP application programmed information, with "orientation done" bit (register 0x04 bit 6) set to 1. USB's upstream and downstream channel conditions are also applied based on LCTLx and RCTLx values in register 0x10 through 0x13.

The auto orientation detection process is executed only once using either one of two methods mentioned above. After the orientation is found (register 0x04 bit 6 is set to 1),

PTN38003A

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved.

Multi-protocol USB3.2 and DisplayPort linear redriver

setting register 0x04 bit 7 to 1 will not re-initiate the auto orientation detection procedure, as long as the mode bits (register 0x04 bit [2:0]) are not set to Deep Power Saving mode (000). I<sup>2</sup>C controller may further configure PTN38003A to other operating modes (DP 2-Lane+USB, DP 4-Lane) with a different orientation if necessary, and correct pin configuration will be adjusted accordingly. Setting the mode bits (register 0x04 bit [2:0]) to Deep Power Saving mode (000) before the orientation done bit is set to 1 will result in aborting the auto orientation detection process.

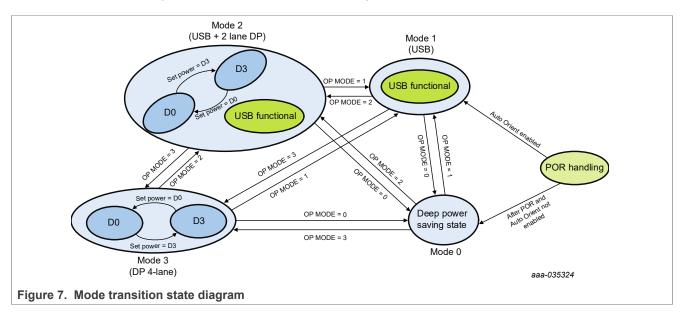

#### 7.7.3 Mode transitions

The mode transitions follow USB safe state transition requirements of USB Type-C cable and connection specification, USB Power Delivery and Alternate Mode specifications.

<u>Figure 7</u> illustrates the various functional modes and deep power saving state transitions.

In Deep Power Saving mode, all high-speed pins are put in USB Safe state. The AUX snooping function is disabled. When a valid Type-C cable is connected, the host PD controller could place PTN38003A in USB3 mode (mode 1). Once DP Alternate Mode is negotiated, PTN38003A adheres the USB safe state requirements before making the mode transition.

The user can configure the device to transition between different modes at any time. When transitioning from Mode 1 to Mode 2, the USB3 connectivity is left undisturbed and DP 2-Lane + AUX functionality is included and when transitioning from Mode 2 to Mode 1, USB3 connectivity is left undisturbed while disabling the DP redriver functionality. While in Mode 1, USB's non-config lane is held in USB safe state. It is possible to transition from DP 4-Lane to USB only without entering Deep Power Saving, or vice versa. PTN38003A takes care of transition to USB Safe state internally.

#### Multi-protocol USB3.2 and DisplayPort linear redriver

The orientation is assumed to be fixed in <u>Figure 7</u>, because a change in orientation requires a disconnect event which requires a return to USB Safe state.

### 7.7.4 Channel settings for USB3.2 and DP Modes

The ternary channel condition inputs LCTL1, LCTL2, LCTL3, RCTL1, RCTL2, RCTL3 are enabled and sampled at POR. The detected values from these ternary inputs are used to initialize the  $I^2C$  registers. After entering via  $I^2C$  interface, changes to the ternary channel conditions are ignored and subsequent writes of  $I^2C$  values overwrite the sampled ternary inputs. Once the ternary inputs have been sampled during mode detection, there will be no mechanism to re-initialize the  $I^2C$  registers to the sampled values except via an  $I^2C$  write. When a software reset is issued,  $I^2C$  register values get reset to the stored value of the ternary inputs sampled at power-up.

<u>Table 8</u> will be expanded to cover gain values at different link rates for each of the protocols - USB and DP.

Table 8. LCTL[2:1] and RCTL[2:1] Channel configurations: Flat gain = 0

Peaking Gain is the equalization gain at specific frequency relative to gain at 100 MHz and for Flat Gain (FG) = 0

| I <sup>2</sup> C<br>register<br>value<br><3:0> | LCTL2/<br>RCTL2 | LCTL1/<br>RCTL1 | Unit | Gain at<br>100 MHz<br>(as<br>reference) | 0.81 GHz | 1.35 GHz | 2.5 GHz | 2.7 GHz | 4.05 GHz | 5.0 GHz | 6.75 GHz | 10 GHz |

|------------------------------------------------|-----------------|-----------------|------|-----------------------------------------|----------|----------|---------|---------|----------|---------|----------|--------|

| 0000                                           | LOW             | OPEN            | dB   | 0.5                                     | -0.2     | -0.4     | -0.1    | -0.1    | 0.1      | 0.5     | 1.0      | 2.0    |

| 0001                                           | OPEN            | LOW             | dB   | 0.5                                     | -0.1     | -0.3     | 0.0     | 0.1     | 0.4      | 0.8     | 1.5      | 2.8    |

| 0010                                           |                 |                 | dB   | 0.5                                     | 0.0      | -0.2     | 0.2     | 0.3     | 0.7      | 1.2     | 2.0      | 3.8    |

| 0011                                           | HIGH            | HIGH            | dB   | 0.5                                     | 0.1      | 0.0      | 0.6     | 0.7     | 1.3      | 1.9     | 3.0      | 5.4    |

| 0100                                           |                 |                 | dB   | 0.5                                     | 0.3      | 0.1      | 0.9     | 0.9     | 1.6      | 2.4     | 3.6      | 6.4    |

| 0101                                           | HIGH            | OPEN            | dB   | 0.5                                     | 0.6      | 0.5      | 1.5     | 1.6     | 2.6      | 3.5     | 5.1      | 8.4    |

| 0110                                           |                 |                 | dB   | 0.6                                     | 0.7      | 0.8      | 1.8     | 2.0     | 3.1      | 4.1     | 5.9      | 9.5    |

| 0111                                           | HIGH            | LOW             | dB   | 0.6                                     | 1.1      | 1.3      | 2.6     | 2.8     | 4.2      | 5.4     | 7.5      | 11.6   |

| 1000                                           |                 |                 | dB   | 0.6                                     | 1.5      | 1.8      | 3.4     | 3.6     | 5.3      | 6.6     | 9.0      | 13.4   |

| 1001                                           | OPEN            | HIGH            | dB   | 0.6                                     | 1.7      | 2.0      | 3.7     | 4.0     | 5.7      | 7.2     | 9.7      | 14.2   |

| 1010                                           |                 |                 | dB   | 0.6                                     | 2.0      | 2.4      | 4.4     | 4.7     | 6.7      | 8.2     | 10.9     | 15.6   |

| 1011                                           | LOW             | HIGH            | dB   | 0.6                                     | 2.4      | 2.8      | 5.0     | 5.3     | 7.4      | 9.1     | 11.9     | 16.8   |

| 1100                                           |                 |                 | dB   | 0.6                                     | 2.6      | 3.2      | 5.4     | 5.7     | 8.0      | 9.7     | 12.7     | 17.5   |

| 1101                                           | OPEN            | OPEN            | dB   | 0.7                                     | 2.9      | 3.7      | 5.9     | 6.2     | 8.6      | 10.4    | 13.6     | 18.4   |

| 1110                                           |                 |                 | dB   | 0.7                                     | 2.9      | 3.7      | 5.9     | 6.2     | 8.6      | 10.5    | 13.6     | 18.4   |

| 1111                                           | LOW             | LOW             | dB   | 0.7                                     | 2.9      | 3.7      | 5.9     | 6.2     | 8.6      | 10.5    | 13.6     | 18.4   |

### Multi-protocol USB3.2 and DisplayPort linear redriver

Table 9. LCTL[2:1] and RCTL[2:1] Channel configurations: Flat gain = 1

Peaking Gain is the equalization gain at specific frequency relative to gain at 100 MHz and for Flat Gain (FG) = 1

| I <sup>2</sup> C<br>register<br>value<br><3:0> | LCTL2/<br>RCTL2 | LCTL1/<br>RCTL1 | Unit | Gain at<br>100 MHz<br>(as<br>reference) | 0.81 GHz | 1.35 GHz | 2.5 GHz | 2.7 GHz | 4.05 GHz | 5.0 GHz | 6.75 GHz | 10 GHz |

|------------------------------------------------|-----------------|-----------------|------|-----------------------------------------|----------|----------|---------|---------|----------|---------|----------|--------|

| 0000                                           | LOW             | OPEN            | dB   | -1.1                                    | -0.1     | -0.2     | 0.5     | 0.6     | 1.3      | 1.9     | 2.6      | 3.8    |

| 0001                                           | OPEN            | LOW             | dB   | -1.1                                    | 0.0      | -0.1     | 0.7     | 0.8     | 1.6      | 2.2     | 3.1      | 4.6    |

| 0010                                           |                 |                 | dB   | -1.1                                    | 0.1      | 0.0      | 1.0     | 1.1     | 1.9      | 2.7     | 3.7      | 5.6    |

| 0011                                           | HIGH            | HIGH            | dB   | -1.1                                    | 0.3      | 0.2      | 1.4     | 1.6     | 2.6      | 3.4     | 4.7      | 7.2    |

| 0100                                           |                 |                 | dB   | -1.1                                    | 0.5      | 0.4      | 1.7     | 1.9     | 3.0      | 4.0     | 5.4      | 8.1    |

| 0101                                           | HIGH            | OPEN            | dB   | -1.1                                    | 0.9      | 1.0      | 2.5     | 2.7     | 4.0      | 5.1     | 6.9      | 10.2   |

| 0110                                           |                 |                 | dB   | -1.0                                    | 1.1      | 1.3      | 2.9     | 3.1     | 4.6      | 5.8     | 7.7      | 11.3   |

| 0111                                           | HIGH            | LOW             | dB   | -1.0                                    | 1.6      | 2.0      | 3.8     | 4.0     | 5.8      | 7.1     | 9.3      | 13.3   |

| 1000                                           |                 |                 | dB   | -1.0                                    | 2.0      | 2.5      | 4.6     | 4.9     | 6.9      | 8.3     | 10.7     | 15.1   |

| 1001                                           | OPEN            | HIGH            | dB   | -1.0                                    | 2.3      | 2.8      | 5.0     | 5.3     | 7.4      | 8.9     | 11.4     | 15.9   |

| 1010                                           |                 |                 | dB   | -1.0                                    | 2.7      | 3.3      | 5.8     | 6.1     | 8.3      | 9.9     | 12.6     | 17.3   |

| 1011                                           | LOW             | HIGH            | dB   | -1.0                                    | 3.1      | 3.8      | 6.4     | 6.7     | 9.1      | 10.8    | 13.6     | 18.4   |

| 1100                                           |                 |                 | dB   | -0.9                                    | 3.3      | 4.2      | 6.8     | 7.1     | 9.6      | 11.4    | 14.3     | 19.1   |

| 1101                                           | OPEN            | OPEN            | dB   | -0.9                                    | 3.7      | 4.7      | 7.3     | 7.7     | 10.2     | 12.1    | 15.2     | 20     |

| 1110                                           |                 |                 | dB   | -0.9                                    | 3.7      | 4.7      | 7.3     | 7.7     | 10.2     | 12.1    | 15.2     | 20     |

| 1111                                           | LOW             | LOW             | dB   | -0.9                                    | 3.7      | 4.7      | 7.3     | 7.7     | 10.2     | 12.1    | 15.2     | 20     |

Table 10. LCTL3/RCTL3 channel configuration

| iable to: Lottestto thamber comigaration |       |       |                        |  |  |  |  |  |

|------------------------------------------|-------|-------|------------------------|--|--|--|--|--|

| I <sup>2</sup> C Register<br>Value       | LCTL3 | RCTL3 | Output Swing Linearity |  |  |  |  |  |

| 0                                        |       |       | 500 mV <sub>ppd</sub>  |  |  |  |  |  |

| 1                                        | OPEN  | OPEN  | 650 mV <sub>ppd</sub>  |  |  |  |  |  |

| 2                                        | LOW   | LOW   | 800 mV <sub>ppd</sub>  |  |  |  |  |  |

| 3                                        | HIGH  | HIGH  | 950 mV <sub>ppd</sub>  |  |  |  |  |  |

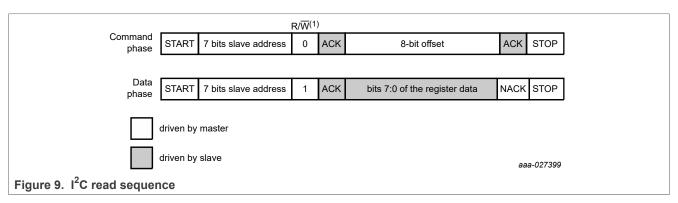

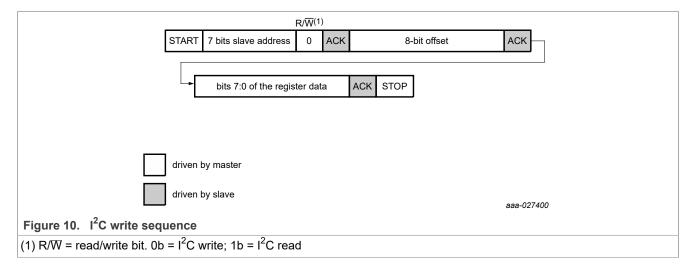

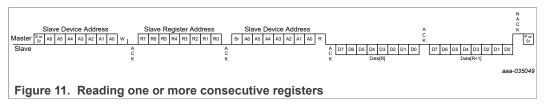

# 7.7.5 I<sup>2</sup>C configurability

PTN38003A has an I<sup>2</sup>C register interface that enables system integrator to program register settings suitable as per application needs. After power on reset, the device reads the ADDR pin for determining the I<sup>2</sup>C Slave Address. PTN38003A provides up to four I<sup>2</sup>C Slave address combinations based on quaternary pin (ADDR) setting, and they are summarized in Table 11.

Table 11. I<sup>2</sup>C slave address options

| table 11. 1 9 diave address options                            |                                      |                                |   |   |   |   |   |   |     |

|----------------------------------------------------------------|--------------------------------------|--------------------------------|---|---|---|---|---|---|-----|

| ADDR pin state                                                 | 7-bit I <sup>2</sup> C slave address | 8-bit I <sup>2</sup> C address |   |   |   |   |   |   |     |

| Connected to 1.8 V supply directly                             | 011-0011 (0x33)                      | 0                              | 1 | 1 | 0 | 0 | 1 | 1 | R/W |

| Connected to 1.8 V with 56 k $\Omega$ (±10 %) pull-up resistor | 011-0010 (0x32)                      | 0                              | 1 | 1 | 0 | 0 | 1 | 0 | R/W |

| Connect to 1.8 V with 200 kΩ (±10 %) pull-up resistor          | 011-0001 (0x31)                      | 0                              | 1 | 1 | 0 | 0 | 0 | 1 | R/W |

| Connected to GND directly                                      | 011-0000 (0x30)                      | 0                              | 1 | 1 | 0 | 0 | 0 | 0 | R/W |

PTN38003A

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved.

Multi-protocol USB3.2 and DisplayPort linear redriver

# 7.7.6 I<sup>2</sup>C registers

The system integrator must program the registers of the device for proper operation. Further, it is expected that the system integrator performs I<sup>2</sup>C configuration after power-up and before data transport is initiated over the link. If such an operation is attempted during normal operation, the device may not behave as specified.

Table 12. I<sup>2</sup>C registers and description

| Register offset   | Register name     | Bits | POR default value | Description                                                                                    |

|-------------------|-------------------|------|-------------------|------------------------------------------------------------------------------------------------|

| 0x00<br>Read Only | Chip ID           | 7:0  | b'00001011        | Chip ID Number                                                                                 |

| 0x01              | Chip Revision     | 7:4  | b'1010            | Chip base layer version                                                                        |

| Read Only         |                   | 3:0  | b'0001            | Chip metal layer version                                                                       |

| 0x02              | Reserved          | 7:0  | p,0000 0000       |                                                                                                |

| 0x03              | Flat gain control |      |                   | Flat gain control setting for each high speed data path. The gain is specified at 100 MHz      |

|                   |                   | 7:6  | b'00              | Write '0' only. Read is don't care                                                             |

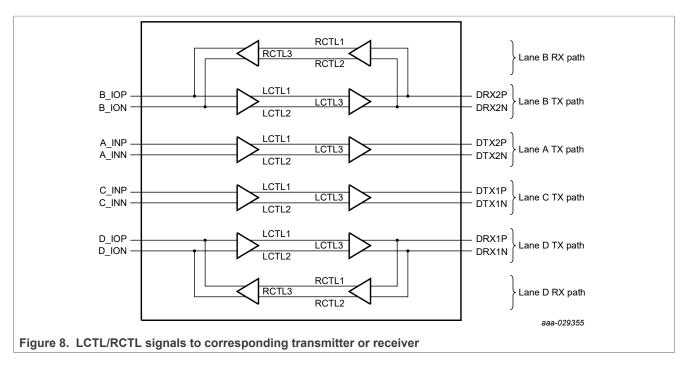

|                   |                   | 5    | b'0               | Lane B Rx path (Figure 8) flat gain control 0 = flat gain of +0.7 dB, 1 = flat gain of -0.7 dB |

|                   |                   | 4    | b'0               | Lane D Rx path flat gain control 0 = flat gain of +0.7 dB, 1 = flat gain of -0.7 dB            |

|                   |                   | 3    | b'0               | Lane B Tx path (Figure 8) flat gain control 0 = flat gain of +0.7 dB, 1 = flat gain of -0.7 dB |

|                   |                   | 2    | b'0               | Lane A Tx path flat gain control 0 = flat gain of +0.7 dB, 1 = flat gain of -0.7 dB            |

|                   |                   | 1    | b'0               | Lane C Tx path flat gain control 0 = flat gain of +0.7 dB, 1 = flat gain of -0.7 dB            |

|                   |                   | 0    | b'0               | Lane D Tx path downstream flat gain control 0 = flat gain of +0.7 dB, 1 = flat gain of -0.7 dB |

Table 12. I<sup>2</sup>C registers and description...continued

| Register offset    | Register name | Bits | POR default value               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------|---------------|------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x04<br>Read/Write | Mode control  | 7    | AUTO_<br>ORIENT_EN<br>pin value | <ul> <li>Auto orientation enable bit is used to select Auto orientation option</li> <li>1 = Enable</li> <li>0 = Disable or abort an ongoing auto orientation detection process</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                             |

|                    |               | 6    | p,0                             | <ul> <li>Orientation done bit</li> <li>When 0, 'Plug orientation control' bit (bit 4) is not valid</li> <li>When 1, then it conveys 'Plug orientation control' bit (bit 4) is valid.</li> <li>This bit is cleared when Auto orientation enable (bit 7) is cleared by host, and it is not valid wher bit 7 is '0'. Writes to this bit do not have any effect.</li> </ul>                                                                                                                                                                                                                               |

|                    |               | 5    | p,0                             | DFP or UFP configuration  • 0: DFP configuration  • 1: UFP configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                    |               | 4    | p,0                             | Plug orientation control. This orientation condition applies to high-speed TX/RX configuration  • 0: normal plug orientation of Type-C connection  • 1: reverse plug orientation of Type-C connection This bit is to be written/read by the host or it can get updated automatically whenever 'Auto orientation enable' option is selected by setting bit 7 to '1'.  If bit 7 is '1', then the bit value is valid only when 'Orientation done' bit (bit 6) is '1'.  The host shall not write this bit while bit[7] = 1.  Overriding the orientation selection is possible only when bit 7 is cleared. |

|                    |               | 3    | p,0                             | <ul> <li>AUX snooping polarity control bit</li> <li>When 0, AUXP/AUXN signal polarities follow pin naming: <ul> <li>Pin 18 = AUXP</li> <li>Pin 17 = AUXN</li> </ul> </li> <li>When 1, AUXP/AUXN signal polarities are reverse of the pin naming: <ul> <li>Pin 17 = AUXP</li> <li>Pin 18 = AUXN</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                 |

|                    |               | 2:0  | p,000                           | Operational mode of the device. Refer to Section 7.7.3 for mode transition requirement  0: Deep power saving state 1: USB3.2 2: USB3.2 and 2-lane DP 3: 4-lane DP 4-7 Reserved                                                                                                                                                                                                                                                                                                                                                                                                                        |

Table 12. I<sup>2</sup>C registers and description...continued

| Register offset | Register name              | Bits | POR default value | Description                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|-----------------|----------------------------|------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0x05            | Device control             | 7:1  | b'0001010         | Reserved                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| Read/Write      |                            | 0    | b'0               | <ul> <li>Device Reset bit. This is a self-clearing bit, and reading this register will always return 0.</li> <li>Writing a '1' to this register will soft reset the device including I<sup>2</sup>C register contents and internal digital logic states, while the chip continuing to operate under I<sup>2</sup>C mode.</li> <li>Writing a '0' does not have any effect.</li> </ul> |  |  |

| 0x06            | DP link control and status | 7:5  | p,000             | Write '0' only. Read is don't care                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Read/Write      |                            | 4    | b'0               | DisplayPort Power saving mode selection on all DP lanes.  • 0: Normal/Active mode  • 1: D3 Power saving mode  This field may be modified thru I <sup>2</sup> C write or AUX monitor function. When corresponding DPCD register changes are detected via AUX monitor, this field will be updated.                                                                                     |  |  |

|                 |                            | 3:2  | p.00              | DisplayPort operating lane count  • 0: 0 DP Lane  • 1: 1 DP Lane  • 2: 2 DP lanes  • 3: 4 DP lanes  This field may be modified thru I <sup>2</sup> C write or AUX monitor function. When corresponding DPCD register changes are detected via AUX monitor, this field will be updated.                                                                                               |  |  |

|                 |                            | 1:0  | p,00              | DP Link rate  • 0: 1.62 Gbps (RBR)  • 1: 2.7 Gbps (HBR)  • 2: 5.4 Gbps (HBR2)  • 3: 8.1 Gbps (HBR3)  The field may be modified through I <sup>2</sup> C write or AUX monitor function. When corresponding DPCD register changes are detected via AUX monitor, this field will be updated.                                                                                            |  |  |

| 0x07            | DP Lane 0 Control_1        | 7:4  | b'00              | Write '0' only. Read is don't care                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Read/Write      | Register                   | 3:0  | LCTL1, LCTL2      | DP Lane 0 link Equalization gain. Refer to Peaking gain tables - <u>Table 8</u> and <u>Table 9</u> in <u>Section 7.7.4</u> for more details.                                                                                                                                                                                                                                         |  |  |

| 0x08            | DP Lane 0 Control_2        | 7:2  | p,0000 00         | Write '0' only. Read is don't care                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Read/Write      | Register                   | 1:0  | LCTL3             | DP Lane 0 output signal swing linearity  • 0: 500 mVppd  • 1: 650 mVppd  • 2: 800 mVppd  • 3: 950 mVppd                                                                                                                                                                                                                                                                              |  |  |

Table 12. I<sup>2</sup>C registers and description...continued

| Register offset    | Register name          | Bits | POR default value | Description                                                                                                                                                                                                                                                               |

|--------------------|------------------------|------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x09               | DP Lane 1 Control_1    | 7:4  | b'0000            | Write '0' only. Read is don't care                                                                                                                                                                                                                                        |

| Read/Write         | Register               | 3:0  | LCTL1, LCTL2      | DP Lane 1 link Equalization gain. Refer to Peaking gain tables - <u>Table 8</u> and <u>Table 9</u> in <u>Section 7.7.4</u> for more details.                                                                                                                              |

| 0x0A               | DP Lane 1 Control_2    | 7:2  | b'0000 00         | Write '0' only. Read is don't care                                                                                                                                                                                                                                        |

| Read/Write         | Register               |      | LCTL3             | DP Lane 1 output signal swing linearity  • 0: 500 mVppd  • 1: 650 mVppd  • 2: 800 mVppd  • 3: 950 mVppd                                                                                                                                                                   |

| 0x0B               | DP Lane 2 Control_1    | 7:4  | b'0000            | Write '0' only. Read is don't care                                                                                                                                                                                                                                        |

| Read/Write         | Register               | 3:0  | LCTL1, LCTL2      | DP Lane 2 link Equalization gain. Refer to Peaking gain tables - <u>Table 8</u> and <u>Table 9</u> in <u>Section 7.7.4</u> for more details.                                                                                                                              |

| 0x0C               | DP Lane 2 Control_2    | 7:2  | b'0000 00         | Write '0' only. Read is don't care                                                                                                                                                                                                                                        |

| Read/Write         | Register               | 1:0  | LCTL3             | DP Lane 2 output signal swing linearity • 0: 500 mVppd • 1: 650 mVppd • 2: 800 mVppd • 3: 950 mVppd                                                                                                                                                                       |

| 0x0D               | DP Lane 3 Control_1    | 7:4  | b'0000            | Write '0' only. Read is don't care                                                                                                                                                                                                                                        |

| Read/Write         | Register               | 3:0  | LCTL1, LCTL2      | DP Lane 3 link Equalization gain. Refer to Peaking gain tables - <u>Table 8</u> and <u>Table 9</u> in <u>Section 7.7.4</u> for more details.                                                                                                                              |

| 0x0E               | DP Lane 3 Control_2    | 7:2  | b'0000 00         | Write '0' only. Read is don't care                                                                                                                                                                                                                                        |

| Read/Write         | Register               | 1:0  | LCTL3             | DP Lane 3 output signal swing linearity  • 0: 500 mVppd  • 1: 650 mVppd  • 2: 800 mVppd  • 3: 950 mVppd                                                                                                                                                                   |

| 0x0F<br>Read/Write | LOS detector threshold | 7    | 0                 | LFPS detection disable in U2/U3 state in USB3 operation. This bit can be set/changed only during Deep Power saving mode.  0: LFPS detector is used in U2/U3 state to transition back to U0 state  1: LFPS detector is not used to transition from U2/U3 state to U0 state |

|                    |                        | 6    | 0                 | LOS detector disable in USB3 operation. This bit can be set/changed only during Deep Power saving mode.  0: LOS detector is enabled  1: LOS detector is disabled                                                                                                          |

Table 12. I<sup>2</sup>C registers and description...continued

| Register offset | Register name      | Bits | POR default value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------|--------------------|------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 |                    | 5:4  | b'00              | Chip upstream (B_IO, A_IN, C_IN, and D_IO) side LOS detector threshold setting  • 0: 45 mV (default/POR)  • 1: 60 mV  • 2: 70 mV  • 3: 80 mV  • Other values are reserved The setting is applicable for operational modes (USB3.2 and DP). It is used as a signal threshold reference for low power state management                                                                                                                                                                                                                         |