# **M**•CORE<sup>™</sup>

# MMC2001 Reference Manual Revision 1.1

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. The Motorola name and logotype are trademarks of Motorola, Inc.

The M•CORE name and logotype and the OnCE name are trademarks of Motorola, Inc.

© Motorola, Inc. 1998

# Conventions

This document uses the following notational conventions:

| mnemonics | Instruction mnemonics are shown in lowercase bold |

|-----------|---------------------------------------------------|

| 0x0F      | Hexadecimal numbers                               |

| 0b0011    | Binary numbers                                    |

# Nomenclature

Logic level one is the voltage that corresponds to a Boolean true (1) state.

Logic level zero is the voltage that corresponds to a Boolean false (0) state.

To set a bit or bits means to establish logic level one on the bit or bits.

To **clear** a bit or bits means to establish logic level zero on the bit or bits.

**LSB** means least significant bit or bits. **MSB** means most significant bit or bits. References to low and high bytes are spelled out.

A signal is **asserted** when it is in its active or true state, regardless of whether that state is represented by a high or low voltage. A signal is **negated** when it is in its inactive or false state.

# **TABLE OF CONTENTS**

Paragraph

Title

Page

SECTION 1 INTRODUCTION

# SECTION 2 INTEGER CPU

| 2.1   | M•CORE Overview                      | 2-1  |

|-------|--------------------------------------|------|

| 2.2   | Features                             | 2-2  |

| 2.3   | Microarchitecture Summary            | 2-2  |

| 2.4   | Programming Model                    | 2-3  |

| 2.5   | Data Format Summary                  | 2-5  |

| 2.6   | Operand Addressing Capabilities      |      |

| 2.7   | Instruction Set Overview             | 2-6  |

| 2.8   | M•CORE Bus Interface                 | 2-8  |

| 2.8.1 | Bus Characteristics                  | 2-8  |

| 2.8.2 | Bus Signals                          | 2-9  |

| 2.8.3 | Signal Descriptions                  | 2-10 |

| 2.8.4 | Bus Operation                        | 2-11 |

| 2.8.5 | Processor Instruction/Data Transfers | 2-13 |

| 2.8.6 | Bus Exception Cycles                 | 2-14 |

|       |                                      |      |

# SECTION 3 SYSTEM MEMORY MAP

| 3.1 | Overview                              | 3-1 |

|-----|---------------------------------------|-----|

|     | Peripheral Module Address Allocation  |     |

|     | Peripheral Module Interface Operation |     |

| 3.4 | Peripheral Module Address Assignment  | 3-2 |

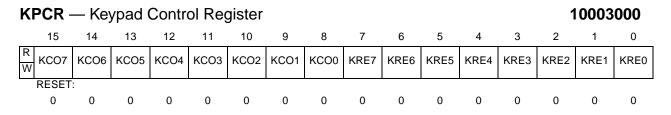

# SECTION 4 SIGNAL DESCRIPTIONS

| 4.1   | Overview                    |     |

|-------|-----------------------------|-----|

| 4.2   | Signal Index                | 4-2 |

| 4.3   | Bus Signals                 |     |

| 4.3.1 | Address Bus (ADDR[19:0])    | 4-4 |

| 4.3.2 | Data Bus (DATA[15:0])       | 4-4 |

| 4.3.3 | Output Enable (OE)          |     |

| 4.3.4 | Read/Write Enable (R/W)     |     |

| 4.3.5 | Enable Byte 1 (EB1)         | 4-4 |

| 4.3.6 | Enable Byte 0 (EB0)         |     |

| 4.3.7 | Chip Selects (CS3, CS[2:0]) | 4-4 |

| 4.3.8 | Internal ROM Disable (MOD)  |     |

| 4.4   | Exception Control Signals   | 4-4 |

| 4.4.1 | Reset (RSTIN)               | 4-4 |

| 4.4.2 | Low Voltage Reset (LVRSTIN) |     |

| 4.4.3 | Reset Out (RSTOUT)          |     |

|       |                             |     |

MMC2001 REFERENCE MANUAL MOTOROLA

# TABLE OF CONTENTS

| Parag         | raph                             | Title                                 | Page |

|---------------|----------------------------------|---------------------------------------|------|

| 4.5           | Clock Signals                    |                                       | 4-5  |

| 4.5.1         | Crystal Oscillator (XOSC, EXOSC  |                                       | 4-5  |

| 4.5.2         | Clock Input (CLKIN)              | · · · · · · · · · · · · · · · · · · · | 4-5  |

| 4.5.3         | Clock Output (CLKOUT)            |                                       | 4-5  |

| 4.6           | Debug and Emulation Support Sign | als                                   | 4-5  |

| 4.6.1         | Test Clock (TCK)                 |                                       | 4-5  |

| 4.6.2         | Test Data Input (TDI)            |                                       | 4-5  |

| 4.6.3         |                                  |                                       |      |

| 4.6.4         | Test Mode Select (TMS)           |                                       | 4-6  |

| 4.6.5         |                                  |                                       |      |

| 4.6.6         | <b>č</b> ( ,                     |                                       |      |

| 4.6.7         |                                  |                                       |      |

| 4.7           |                                  |                                       |      |

| 4.7.1         |                                  | )                                     |      |

| 4.8           |                                  |                                       |      |

| 4.8.1         | Column Strobes (COL[7:0])        |                                       | 4-7  |

| 4.8.2         |                                  |                                       |      |

| 4.9           |                                  |                                       |      |

| 4.9.1         |                                  |                                       |      |

| 4.9.2         |                                  |                                       |      |

| 4.9.3         | ·                                |                                       |      |

| 4.9.4         |                                  |                                       |      |

| 4.10          |                                  | Signals                               |      |

| 4.10.1        |                                  | PI_MOSI)                              |      |

| 4.10.2        |                                  | PI_MISO)                              |      |

| 4.10.3        |                                  |                                       |      |

| 4.10.4        |                                  |                                       |      |

| 4.10.5        |                                  | I _GP)                                |      |

| 4.11          |                                  |                                       |      |

| 4.11.1        | L J                              |                                       |      |

| 4.12          |                                  |                                       |      |

| 4.12.1        |                                  |                                       |      |

| 4.12.2        |                                  |                                       |      |

| 4.12.3 4.12.4 |                                  |                                       |      |

| 4.12.4        | Stanuby Fower Filter (VSTBY)     |                                       | 4-9  |

# SECTION 5 ROM MODULE

| 5.1 | Overview                  |

|-----|---------------------------|

| 5.2 | Functional Description5-1 |

| 5.3 | Applications5-2           |

# **TABLE OF CONTENTS**

Paragraph

Title

Page

# SECTION 6 STATIC RAM MODULE

| 6.1 | Overview               | 6-1 |  |

|-----|------------------------|-----|--|

|     | Functional Description |     |  |

# SECTION 7 EXTERNAL INTERFACE MODULE

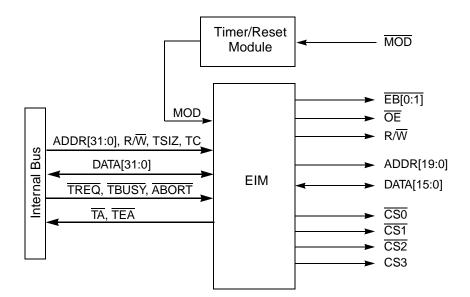

| 7.1   | Overview                       | 7-1  |

|-------|--------------------------------|------|

| 7.2   | Signals                        | 7-1  |

| 7.2.1 | Address Bus                    |      |

| 7.2.2 | Data Bus                       | 7-2  |

| 7.2.3 | Read/Write                     | 7-2  |

| 7.2.4 | Control Signals                |      |

| 7.2.5 | Boot Mode                      |      |

| 7.2.6 | Chip Select Outputs            | 7-2  |

| 7.3   | Chip-Select Address Range      |      |

| 7.4   | EIM Interface Example          |      |

| 7.5   | EIM Functionality              | 7-4  |

| 7.5.1 | Configurable Bus Sizing        | 7-4  |

| 7.5.2 | External Boot ROM Control      |      |

| 7.5.3 | Programmable Output Generation | 7-6  |

| 7.5.4 | Bus Watchdog Operation         | 7-6  |

| 7.5.5 | Error Conditions               | 7-6  |

| 7.5.6 | Show Cycles                    |      |

| 7.6   | EIM Programming Model          | 7-7  |

| 7.6.1 | Chip-Select Control Registers  |      |

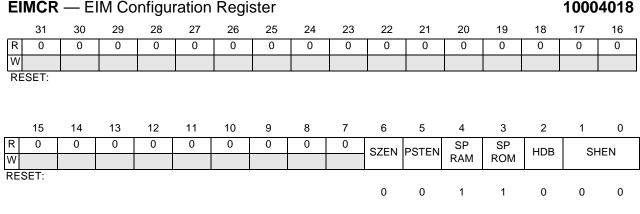

| 7.7   | EIM Configuration Register     | 7-11 |

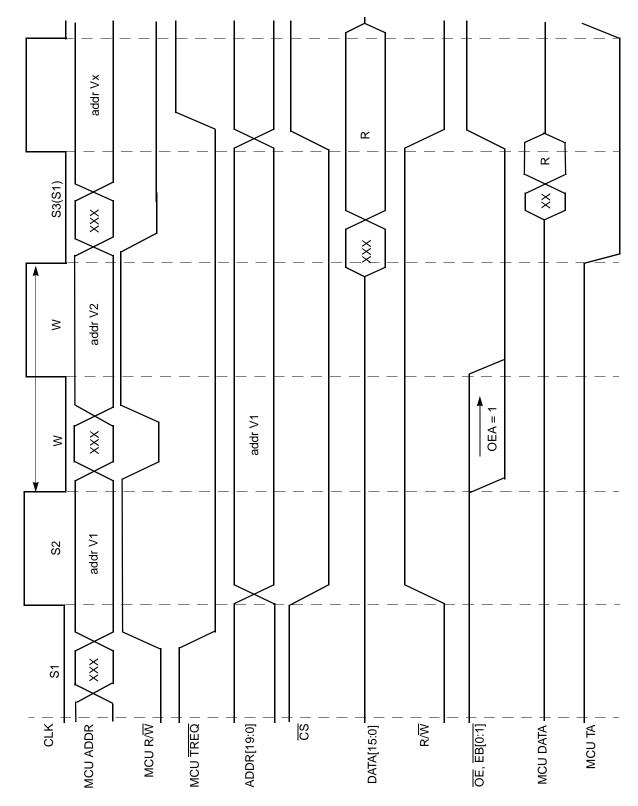

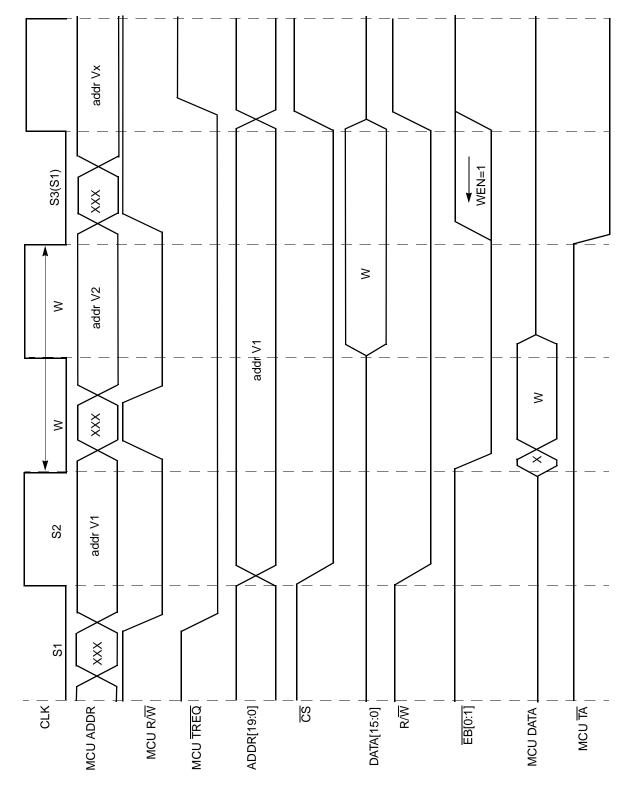

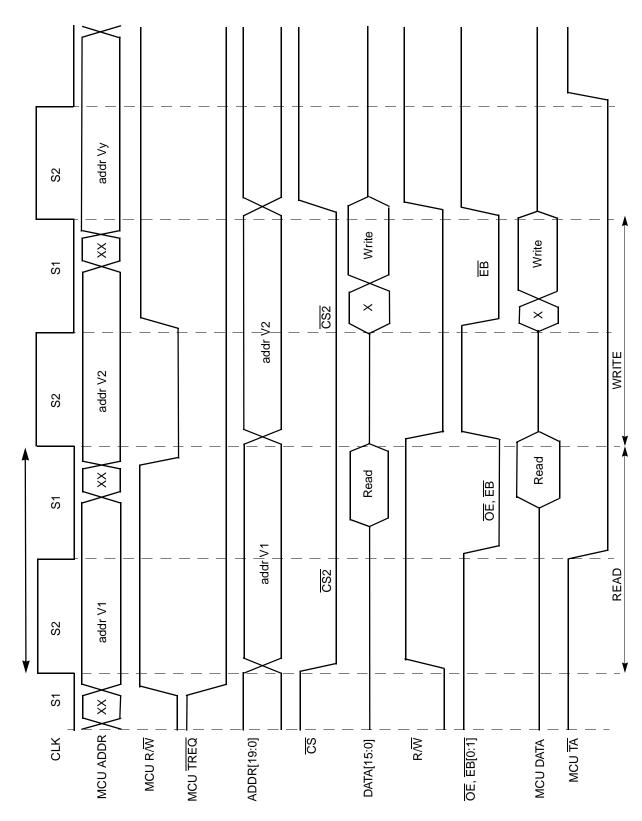

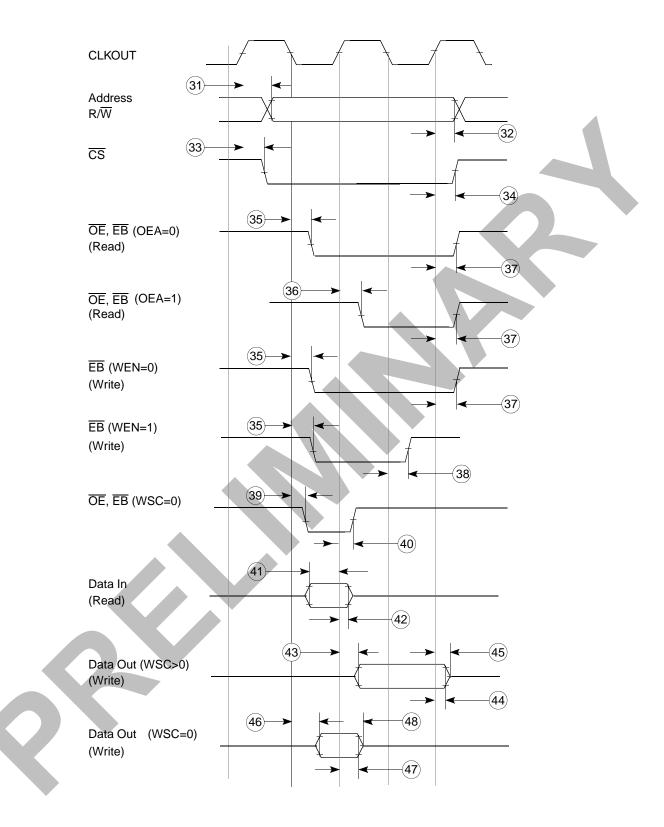

| 7.8   | External Bus Timing Diagrams   |      |

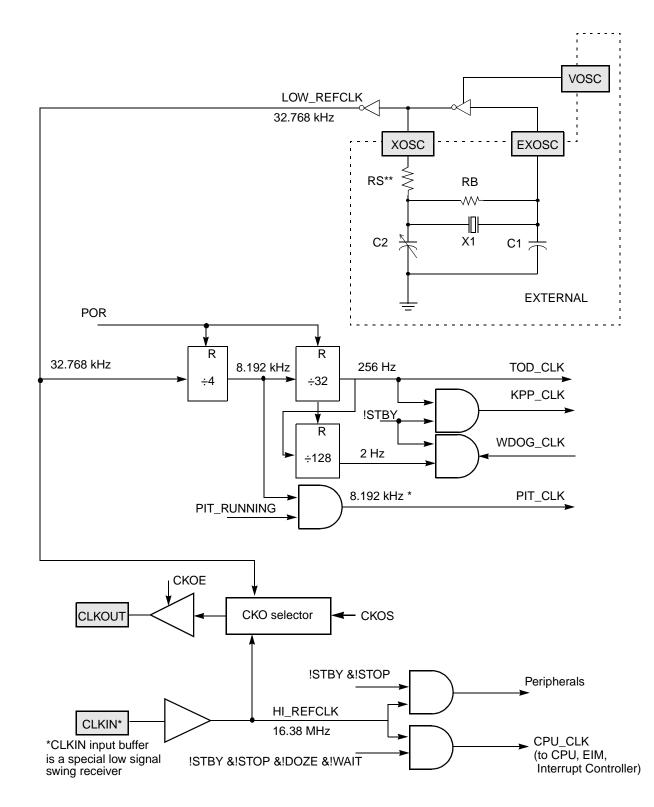

# SECTION 8 CLOCK MODULE AND LOW-POWER MODES

| 8.1   | Overview                               | 8-1 |

|-------|----------------------------------------|-----|

| 8.2   | Low-Power Modes                        | 8-4 |

| 8.2.1 | CPU Core Low-Power Modes               | 8-4 |

| 8.2.2 | Peripheral Behavior in Low-Power Modes | 8-5 |

|       | General Low-Power Features             |     |

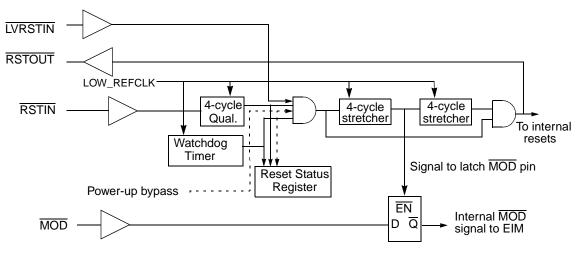

# SECTION 9 TIMER/RESET MODULE

| 9.1   | Overview                      | 9-1 |

|-------|-------------------------------|-----|

| 9.2   | Timer/Reset Programming Model | 9-1 |

| 9.3   | Reset Operation               | 9-2 |

| 9.3.1 | Reset Pins                    | 9-2 |

MMC2001 REFERENCE MANUAL MOTOROLA

vii

# TABLE OF CONTENTS

| Paragraph |                                   | le Page           |

|-----------|-----------------------------------|-------------------|

| 9.3.2     | Reset Sources                     |                   |

| 9.3.3     |                                   |                   |

| 9.3.4     | Reset Source/Chip Configuration R | egister (RSCR)9-3 |

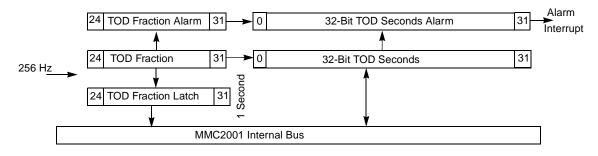

| 9.4       | Time-of-Day Timer                 |                   |

| 9.4.1     |                                   |                   |

| 9.4.2     |                                   |                   |

| 9.4.3     |                                   | r (TODCSR)        |

| 9.4.4     | <b>J</b>                          |                   |

| 9.4.5     |                                   |                   |

| 9.4.6     | <b>-</b>                          | SAR)              |

| 9.4.7     |                                   | FAR)              |

| 9.5       |                                   |                   |

| 9.5.1     |                                   |                   |

| 9.5.2     | 0                                 |                   |

| 9.5.3     |                                   |                   |

| 9.5.4     |                                   |                   |

| 9.5.5     | 0                                 |                   |

| 9.5.6     |                                   |                   |

| 9.5.7     |                                   |                   |

| 9.5.8     |                                   | el9-10            |

| 9.6       |                                   |                   |

| 9.6.1     |                                   |                   |

| 9.6.2     | 0                                 |                   |

| 9.6.3     | •                                 |                   |

| 9.6.4     | Interval Timer Registers          |                   |

| 9.6.5     |                                   | )                 |

| 9.6.6     | <b>č</b> ( <i>,</i>               |                   |

| 9.6.7     |                                   | )                 |

| 9.6.8     |                                   |                   |

| 9.6.9     | PIT in Debug Mode                 |                   |

# SECTION 10 INTERRUPT CONTROLLER

| 10.1   | Overview                                  |      |

|--------|-------------------------------------------|------|

| 10.2   | Interrupt Controller Programming Model    |      |

| 10.2.1 | Interrupt Source Register (INTSRC)        |      |

| 10.2.2 | Normal Interrupt Enable Register (NIER)   |      |

| 10.2.3 | Fast Interrupt Enable Register (FIER)     |      |

| 10.2.4 | Normal Interrupt Pending Register (NIPND) |      |

| 10.2.5 | Fast Interrupt Pending Register (FIPND)   |      |

| 10.2.6 | Interrupt Request Input Assignments       | 10-5 |

# **TABLE OF CONTENTS**

Paragraph

Title

Page

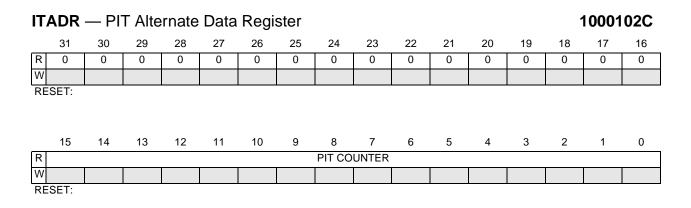

# SECTION 11 UNIVERSAL ASYNCHRONOUS RECEIVER/TRANSMITTER MODULE

| 11.1 ( | Overview                                 | 11-1  |

|--------|------------------------------------------|-------|

| 11.2   | U <u>ART</u> Signals                     |       |

| 11.2.1 | RTS — Request to Send (UART0)            | 11-2  |

| 11.2.2 | CTS — Clear to Send (UART0)              | 11-2  |

| 11.2.3 | TXD — UART Transmit                      | 11-3  |

| 11.2.4 | RXD — UART Receive                       | 11-3  |

| 11.3   | Sub-Block Description                    | 11-3  |

| 11.3.1 | Transmitter                              | 11-3  |

| 11.3.2 | Receiver                                 | 11-3  |

| 11.3.3 | Infrared Interface                       | 11-4  |

| 11.3.4 | 16x Bit Clock Generator                  | 11-4  |

| 11.3.5 | General UART Definitions                 | 11-4  |

| 11.4   | UART Programming Model                   |       |

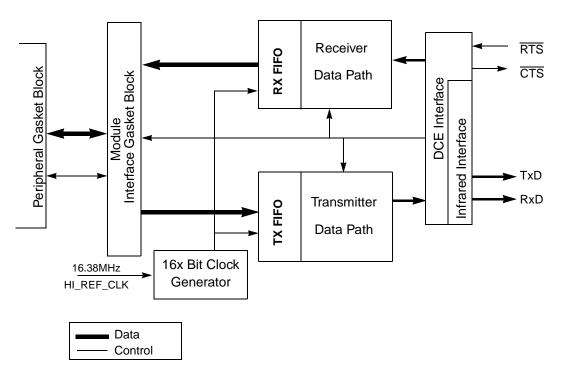

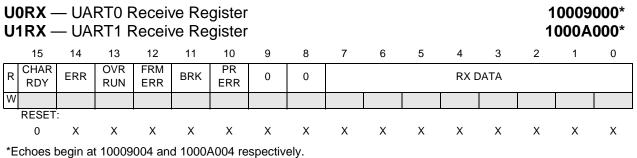

| 11.4.1 | UART Receive Register (URX)              | 11-7  |

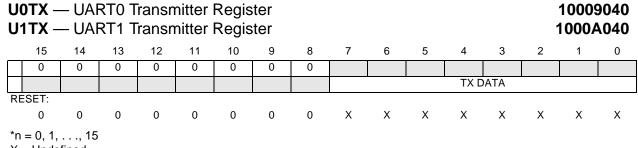

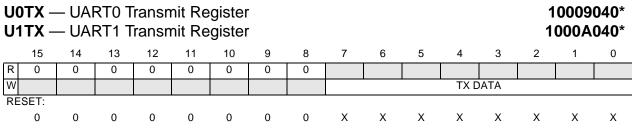

| 11.4.2 | UART Transmitter Register (UTX)          | 11-8  |

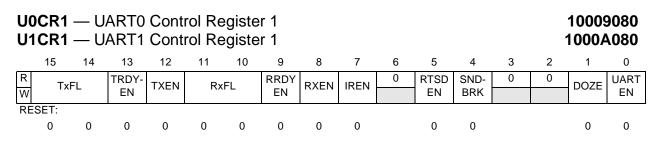

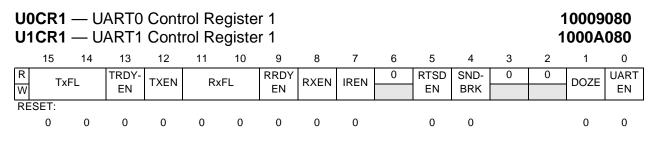

| 11.4.3 | UART Control Register 1 (UCR1)           | 11-9  |

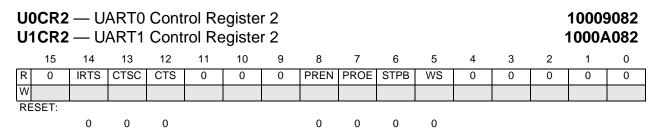

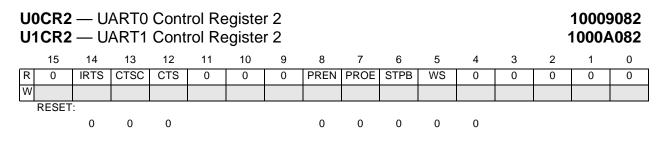

| 11.4.4 | UART Control Register 2 (UCR2)           | 11-11 |

| 11.4.5 | UART BRG Register (UBRGR)                | 11-13 |

| 11.4.6 | UART Status Register (USR)               |       |

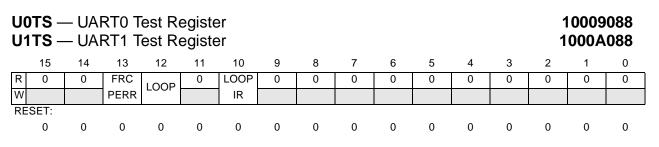

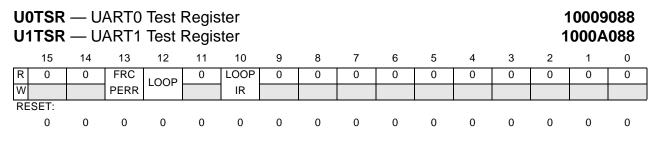

| 11.4.7 | UART Test Register (UTS)                 | 11-15 |

| 11.5   | GPIO Pins and Registers                  | 11-16 |

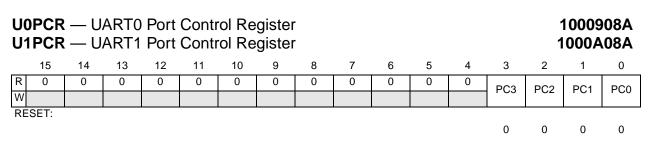

| 11.5.1 | UART Port Control Register (UPCR)        | 11-16 |

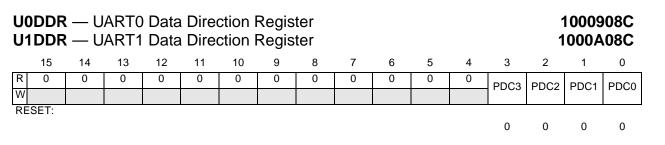

| 11.5.2 | UART Data Direction Register (UDDR)      | 11-16 |

| 11.5.3 | UART Port Data Register (UPDR)           | 11-17 |

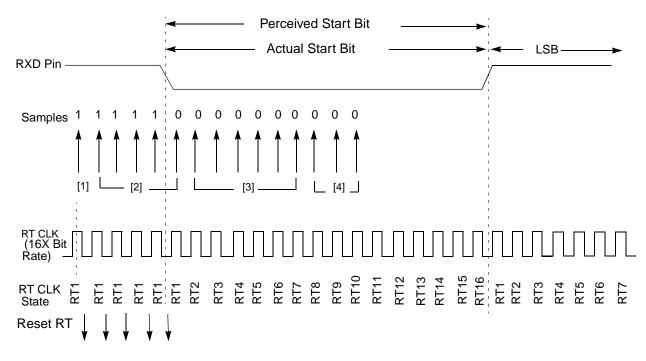

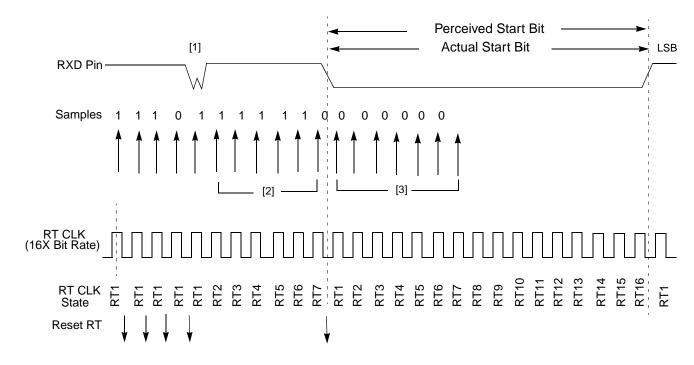

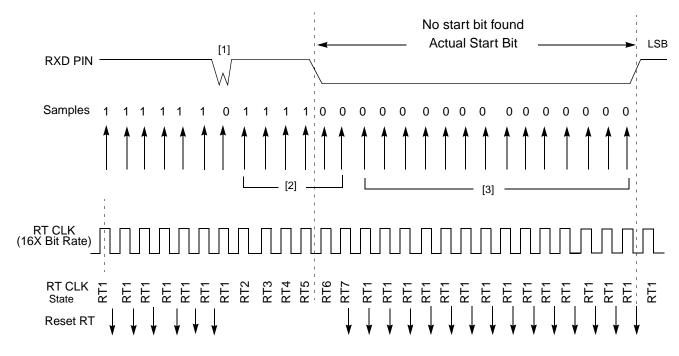

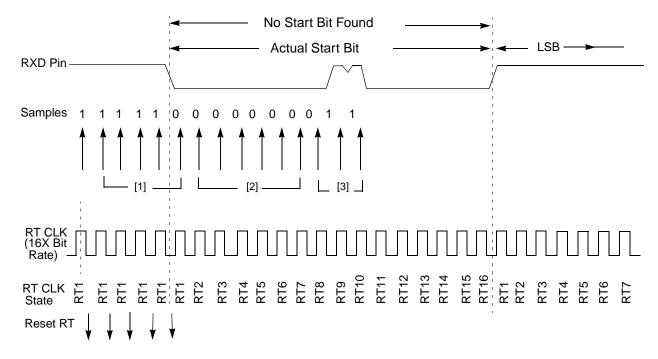

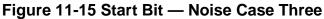

| 11.6 I | Data Sampling Technique on the Receiver  | 11-17 |

| 11.7   | UART Operation in Low-Power System Modes | 11-23 |

| 11.8   | UART Operation in System Debug Mode      | 11-24 |

# SECTION 12 INTERVAL MODE SERIAL PERIPHERAL INTERFACE

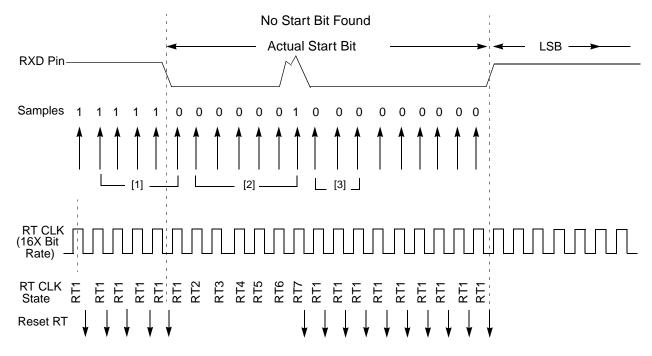

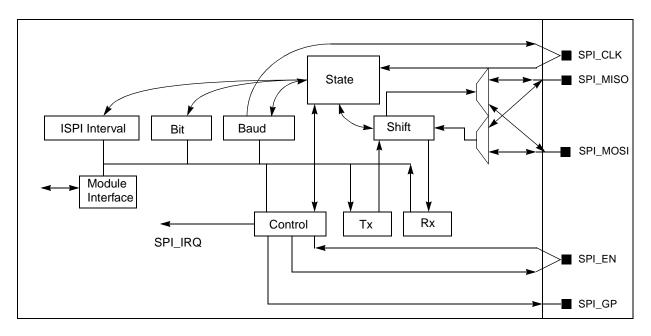

| 12.1   | Overview                        | 12-1 |

|--------|---------------------------------|------|

| 12.2   | Operation                       | 12-1 |

| 12.2.1 | Manual (Master) Mode            | 12-2 |

| 12.2.2 | Interval (Master) Mode          | 12-3 |

| 12.2.3 | Slave Mode                      | 12-3 |

| 12.3   | Signal Descriptions             | 12-3 |

| 12.3.1 | SPI_MISO (Master In, Slave Out) | 12-3 |

| 12.3.2 | SPI_MOSI (Master Out, Slave In) | 12-4 |

| 12.3.3 | SPI_EN                          | 12-4 |

| 12.3.4 | SPI_CLK                         | 12-4 |

| 12.3.5 | SPI_GP                          | 12-4 |

|        |                                 |      |

MMC2001 REFERENCE MANUAL MOTOROLA

# **Freescale Semiconductor, Inc.**

# **TABLE OF CONTENTS**

Title

# Page

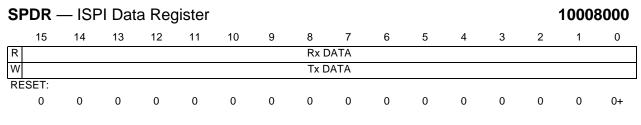

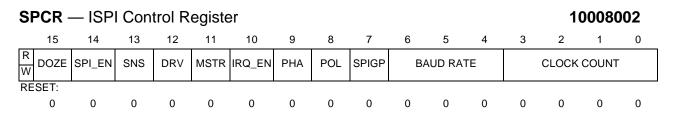

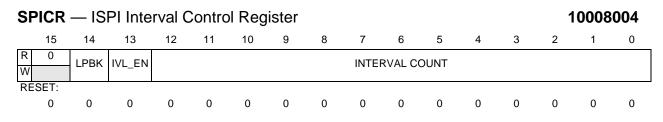

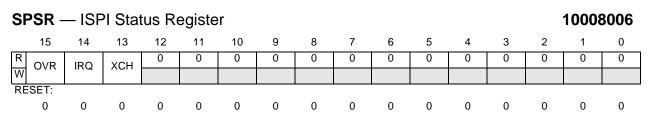

| 12.4 ISPI Programming Model                   | 12-/ |

|-----------------------------------------------|------|

| 12.4.1 ISPI Data Register                     |      |

|                                               |      |

| 12.4.2 ISPI Control Register                  |      |

| 12.4.3 ISPI Interval Control Register         |      |

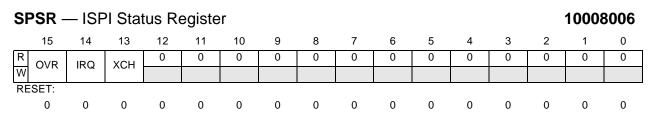

| 12.4.4 ISPI Status Register                   | 12-8 |

| 12.5 ISPI Programming Examples                | 12-9 |

| 12.5.1 Manual Mode Example                    |      |

| 12.5.2 Slave Mode Example                     |      |

| 12.5.3 Interval Model Example                 |      |

| 12.6 ISPI Operation in Low-Power System Modes |      |

| 12.7 ISPI Operation in System Debug Mode      |      |

|                                               |      |

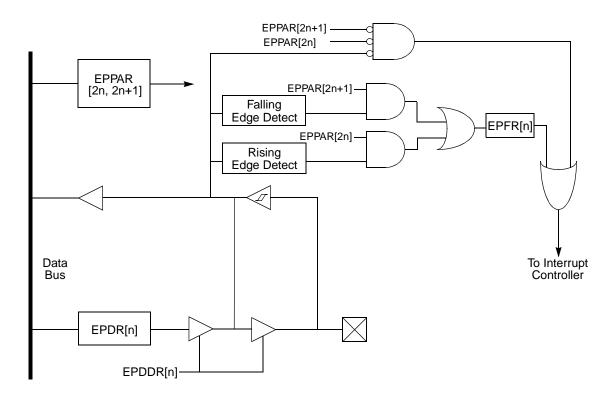

# SECTION 13 EXTERNAL INTERRUPTS/GPIO (EDGE PORT)

| 13.1   | Overview                                                  |  |

|--------|-----------------------------------------------------------|--|

| 13.2   | Interrupt/General-Purpose I/O Pin Descriptions (INT[0:7]) |  |

| 13.3   | Edge Port Programming Model                               |  |

| 13.3.1 | Edge Port Pin Assignment Register (EPPAR)                 |  |

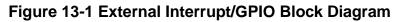

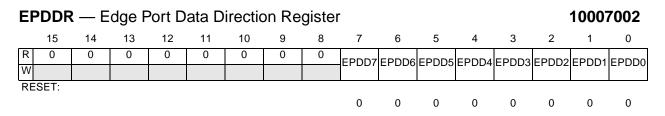

| 13.3.2 | Edge Port Data Direction Register (EPDDR)                 |  |

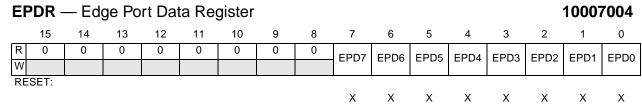

| 13.3.3 | Edge Port Data Register (EPDR)                            |  |

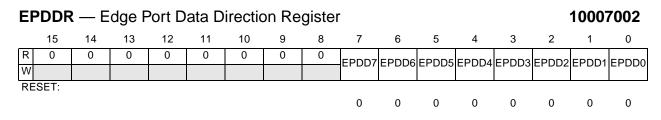

| 13.3.4 | Edge Port Flag Register (EPFR)                            |  |

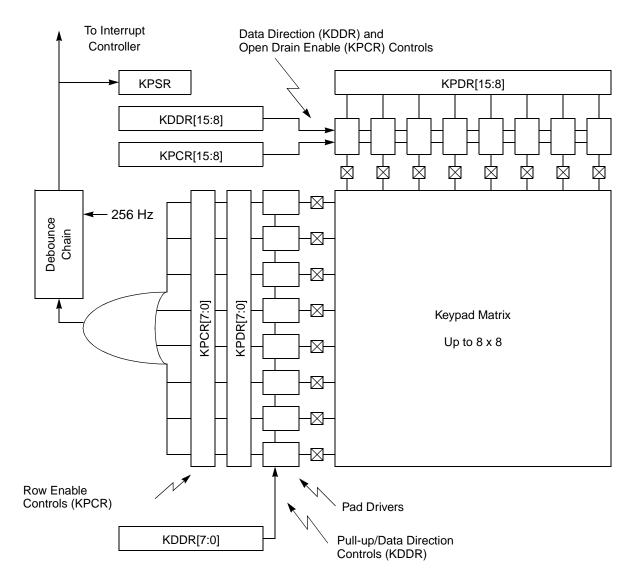

# SECTION 14 KEYPAD PORT

| 14.1 Overview                                             |    |

|-----------------------------------------------------------|----|

| 14.2 KPP Pin Description                                  | -2 |

| 14.2.1 Input Pins                                         | -2 |

| 14.2.2 Output Pins                                        | -2 |

| 14.3 KPP Programming Model14                              | -2 |

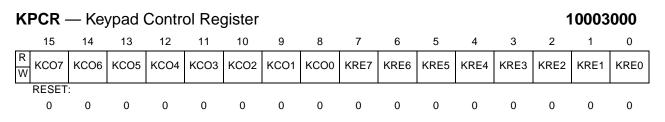

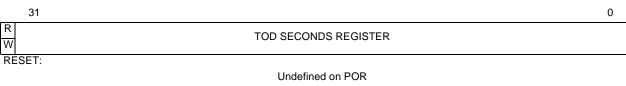

| 14.3.1 Keypad Control Register (KPCR)14                   | -2 |

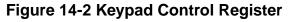

| 14.3.2 Keypad Status Register (KPSR)14                    | -3 |

| 14.3.3 Keypad Data Direction Register (KDDR)14            | -5 |

| 14.3.4 Keypad Data Register (KPDR)14                      | -5 |

| 14.4 Keypad Operation                                     | -6 |

| 14.4.1 Keypad Matrix Construction14                       | -6 |

| 14.4.2 Keypad Port Configuration14                        | -6 |

| 14.4.3 Keypad Matrix Scanning14                           | -6 |

| 14.4.4 Keypad Standby14                                   |    |

| 14.4.5 Glitch Suppression on Keypad Inputs14              |    |

| 14.4.6 Multiple Key Closures14                            | -8 |

| 14.4.7 Typical Keypad Configuration and Scanning Sequence | -9 |

# **TABLE OF CONTENTS**

Paragraph

Title

Page

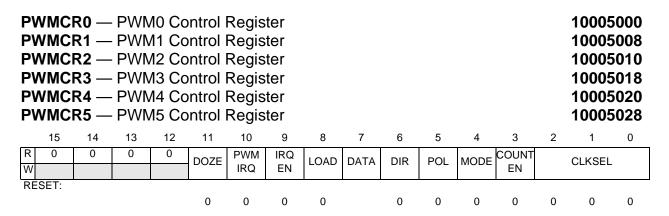

# SECTION 15 PULSE WIDTH MODULATOR

| Overview                                | 15-1                                                                                                                                                                                                                |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PWM Programming Model                   | 15-2                                                                                                                                                                                                                |

| PWM Control Register                    |                                                                                                                                                                                                                     |

| PWM Period Register                     | 15-6                                                                                                                                                                                                                |

| PWM Width Register                      | 15-7                                                                                                                                                                                                                |

| PWM Counter Register                    | 15-7                                                                                                                                                                                                                |

|                                         |                                                                                                                                                                                                                     |

| PWM Operation in Low-Power System Modes | 15-8                                                                                                                                                                                                                |

|                                         | PWM Programming Model       PWM Control Register         PWM Period Register       PWM Width Register         PWM Counter Register       PWM Counter Register         PWM Operating Range       PWM Operating Range |

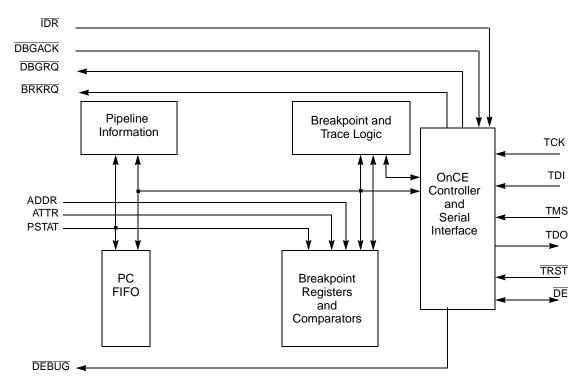

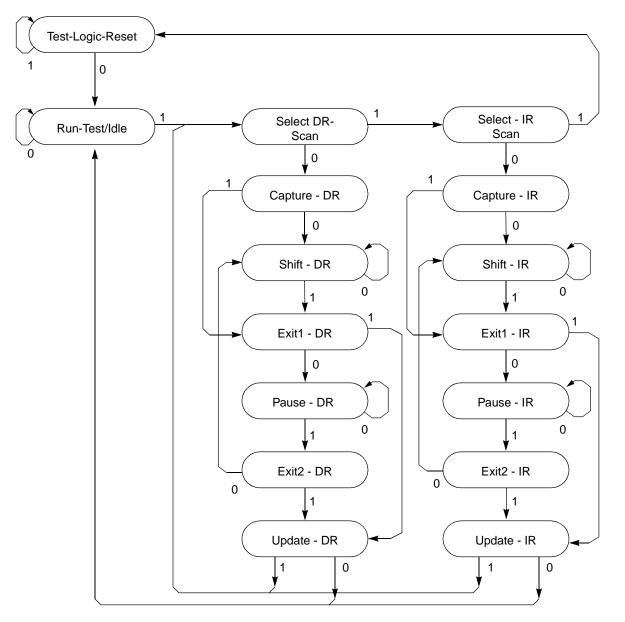

# SECTION 16 OnCE™ DEBUG MODULE

| 16.1 Overview                                         |       |

|-------------------------------------------------------|-------|

| 16.2 Operation                                        | 16-1  |

| 16.3 OnCE Pins                                        |       |

| 16.3.1 Debug Serial Input (TDI)                       | 16-3  |

| 16.3.2 Debug Serial Clock (TCK)                       |       |

| 16.3.3 Debug Serial Output (TDO)                      | 16-3  |

| 16.3.4 Debug Mode Select (TMS)                        | 16-3  |

| 16.3.5 Test Reset (TRST)                              |       |

| 16.3.6 Debug Event (DE)                               | 16-4  |

| 16.4 OnCE Controller and Serial Interface             |       |

| 16.5 OnCE Interface Signals                           | 16-5  |

| 16.5.1 Internal Debug Request Input (IDR)             | 16-5  |

| 16.5.2 CPU Debug Request (DBGRQ)                      | 16-5  |

| 16.5.3 CPU Debug Acknowledge (DBGACK)                 | 16-5  |

| 16.5.4 CPU Breakpoint Request (BRKRQ)                 | 16-5  |

| 16.5.5 CPU Address, Attributes (ADDR, ATTR)           | 16-5  |

| 16.5.6 CPU Status (PSTAT)                             | 16-5  |

| 16.5.7 OnCE Debug Output (DEBUG)                      | 16-6  |

| 16.6 OnCE Controller Registers                        | 16-6  |

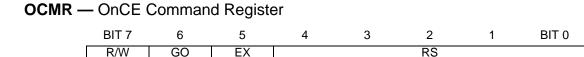

| 16.6.1 OnCE Command Register (OCMR)                   |       |

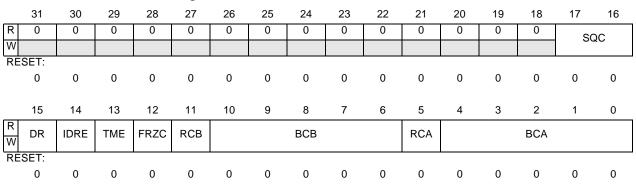

| 16.6.2 OnCE Control Register (OCR)                    | 16-8  |

| 16.6.3 OnCE Status Register (OSR)                     | 16-11 |

| 16.7 OnCE Decoder (ODEC)                              | 16-12 |

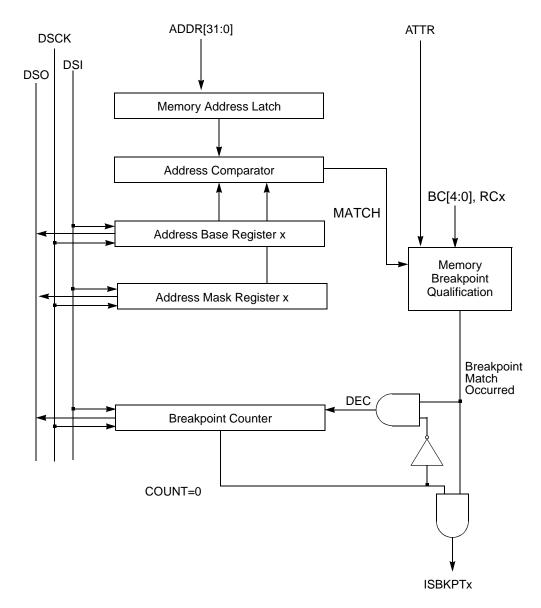

| 16.8 Memory Breakpoint Logic                          |       |

| 16.8.1 Memory Address Latch (MAL)                     |       |

| 16.8.2 Breakpoint Address Base Registers (BABA, BABB) | 16-14 |

| 16.8.3 Breakpoint Address Mask Registers (BAMA, BAMB) |       |

| 16.8.4 Breakpoint Address Comparators                 | 16-14 |

| 16.8.5 Memory Breakpoint Counters (MBCA, MBCB)        | 16-14 |

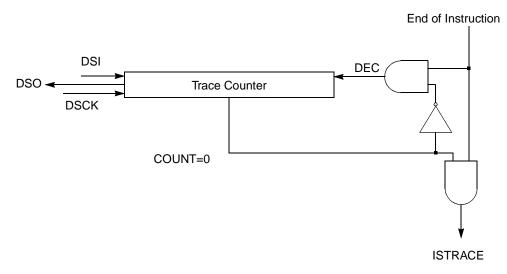

| 16.9 OnCE Trace Logic                                 | 16-14 |

MMC2001 REFERENCE MANUAL MOTOROLA

# **TABLE OF CONTENTS**

## Paragraph Title 16.9.1 16.11.4 Write-Back Bus Register (WBBR) ...... 16-19 16.12.1 Reserved Test Control Registers (Reserved, MEM BIST, FTCR, LSRL) 16-21

# **APPENDIX A** ELECTRICAL CHARACTERISTICS

| A.1   | Maximum Ratings                  | A-1 |

|-------|----------------------------------|-----|

| A.2   | DC Electrical Specifications     | A-1 |

|       | Clock Input Specifications       |     |

|       | AC Electrical Specifications     |     |

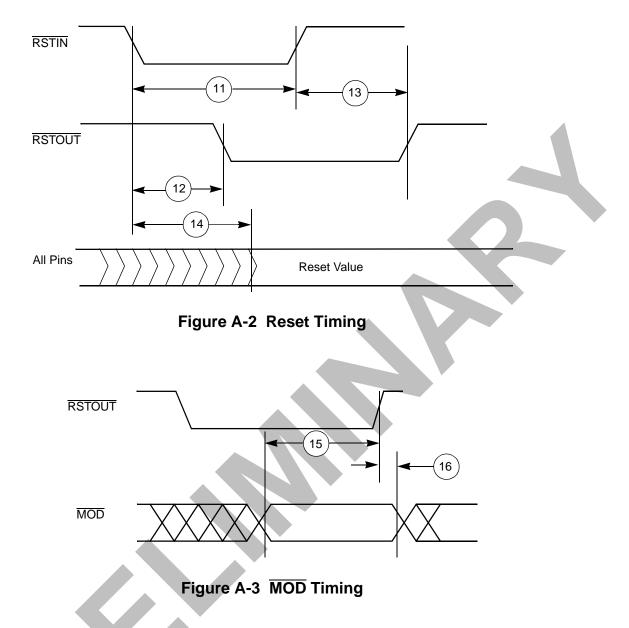

|       | Reset, MOD Timing Specifications |     |

| A.4.2 |                                  |     |

| A.4.3 | EIM Timing Specifications        | A-4 |

| A.4.4 | ISPI Timing Specifications       |     |

| A.4.5 | OnCE Timing Specifications       |     |

|       |                                  |     |

# **APPENDIX B** PACKAGING AND PIN ASSIGNMENTS

**B.1** Overview ......B-1

# APPENDIX C PROGRAMMING REFERENCE

| C.1   | Peripheral Module Address Assignment   | C-1 |

|-------|----------------------------------------|-----|

|       | Interrupt Controller Programming Model |     |

|       | Interrupt Source Register (INTSRC)     |     |

| C.2.2 |                                        |     |

### MOTOROLA

xii

MMC2001 REFERENCE MANUAL

### For More Information On This Product. Go to: www.freescale.com

Page

# **TABLE OF CONTENTS**

### Paragraph Title Page Fast Interrupt Enable Register (FIER) .....C-3 C.2.3Normal Interrupt Pending Register (NIPND).....C-4 C.2.4 Fast Interrupt Pending Register (FIPND).....C-4 C.2.5 C.3 Timer/Reset Programming Model .....C-5 Reset Source/Chip Configuration Register (RSCR) ......C-5 C.3.1 C.3.2 Time-of-Day Control/Status Register (TODCSR) ......C-7 C.3.3 TOD Seconds Register (TODSR).....C-7 C.3.4 TOD Fraction Register (TODFR).....C-8 TOD Seconds Alarm Register (TODSAR) .....C-8 C.3.5 C.3.6 TOD Fraction Alarm Register (TODFAR) .....C-9 C.3.7 Watchdog Control Register (WCR).....C-9 C.3.8 Watchdog Service Register (WSR) .....C-10 C.3.9 PIT Control/Status Register (ITCSR).....C-11 C.3.10 PIT Data Register (ITDR) .....C-12 PIT Alternate Data Register (ITADR).....C-13 C.3.11 KPP Programming Model.....C-13 C.4 C.4.1 Keypad Control Register (KPCR) .....C-14 C.4.2 Keypad Status Register (KPSR).....C-14 C.4.3 Keypad Data Direction Register (KDDR).....C-15 Keypad Data Register (KPDR) ......C-15 C.4.4 EIM Programming Model .....C-16 C.5 C.5.1 Chip-Select Control Registers ......C-16 C.5.2 EIM Configuration Register.....C-20 PWM Module.....C-22 C.6 C.6.1 PWM Control Register .....C-23 C.6.2 PWM Period Register ......C-25 PWM Width Register .....C-26 C.6.3 C.6.4 PWM Counter Register.....C-27 C.7 Edge Port Programming Model.....C-27 Edge Port Pin Assignment Register (EPPAR).....C-27 C.7.1 Edge Port Data Direction Register (EPDDR).....C-28 C.7.2 Edge Port Data Register (EPDR) .....C-29 C.7.3 Edge Port Flag Register (EPFR) .....C-29 C.7.4 C.8 ISPI Programming Model.....C-30 C.8.1 ISPI Send/Receive Data Register.....C-30 C.8.2 ISPI Control Register ......C-31 ISPI Interval Control Register ......C-33 C.8.3 ISPI Status Register .....C-34 C.8.4 UART Programming Model.....C-34 C.9 C.9.1 UART Receive Register (URX).....C-36 C.9.2 UART Transmit Register (UTX) .....C-37 UART Control Register 1 (UCR1).....C-38 C.9.3 C.9.4 UART Control Register 2 (UCR2).....C-40

MMC2001 REFERENCE MANUAL

MOTOROLA

# Freescale Semiconductor, Inc.

# **TABLE OF CONTENTS**

Title

# Page

| C.9.5   | UART BRG Register (UBRGR)C-42                                         |

|---------|-----------------------------------------------------------------------|

| C.9.6   | UART Status Register (USR)C-42                                        |

| C.9.7   | UART Test Register (UTSR)C-43                                         |

| C.9.8   | UART Port Control Register (UPCR)C-44                                 |

| C.9.9   | UART Data Direction Register (UDDR)C-45                               |

| C.9.10  | UART Port Data Register (UPDR)C-45                                    |

| C.10 OI | nCE RegistersC-46                                                     |

| C.10.1  | OnCE Command Register (OCMR)C-46                                      |

| C.10.2  | OnCE Control Register (OCR)C-47                                       |

| C.10.3  | OnCE Status Register (OSR)C-50                                        |

| C.10.4  | Memory Address Latch (MAL)C-51                                        |

| C.10.5  | Breakpoint Address Base Registers (BABA, BABB)C-51                    |

| C.10.6  | Breakpoint Address Mask Registers (BAMA, BAMB)C-51                    |

| C.10.7  | Breakpoint Address ComparatorsC-51                                    |

| C.10.8  | Memory Breakpoint Counters (MBCA, MBCB)C-51                           |

| C.10.9  | Program Counter Register (PC)C-51                                     |

| C.10.10 | Instruction Register (IR)C-52                                         |

| C.10.11 | Control State Register (CTL)C-52                                      |

| C.10.12 | Write-Back Bus Register (WBBR)C-53                                    |

| C.10.13 | Processor Status Register (PSR)C-53                                   |

| C.10.14 | Reserved Test Control Registers (Reserved, MEM_BIST, FTCR, LSRL).C-53 |

# INDEX

# **RECORD OF CHANGES**

# **Freescale Semiconductor, Inc.**

# LIST OF ILLUSTRATIONS

Title

# Freescale Semiconductor, Inc.

| 1-1  | MMC2001 Block Diagram                                         |      |

|------|---------------------------------------------------------------|------|

| 2-1  | Programming Model                                             |      |

| 2-2  | Data Organization in Memory                                   |      |

| 2-3  | Data Organization in Registers                                |      |

| 2-4  | Signal Relationships to Clocks                                |      |

| 2-5  | M•CORE Bus Signals                                            |      |

| 2-6  | External Multiplexer Connections                              |      |

| 4-1  | Functional Signal Groups                                      |      |

| 7-1  | EIM Block Diagram                                             |      |

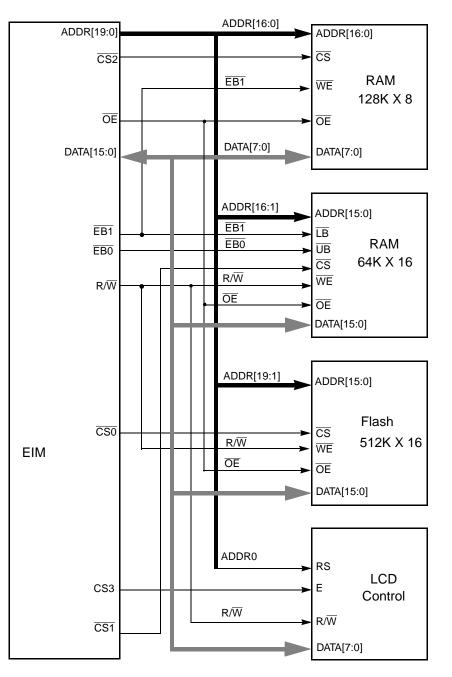

| 7-2  | EIM Interface to Memory and Peripherals                       |      |

| 7-3  | CS0 Control Register                                          |      |

| 7-4  | CS1, CS2, CS3 Control Registers                               |      |

| 7-5  | EIM Configuration Register                                    |      |

| 7-6  | Read Memory Access (CSA = 0, WSC = 1)                         |      |

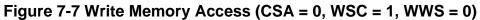

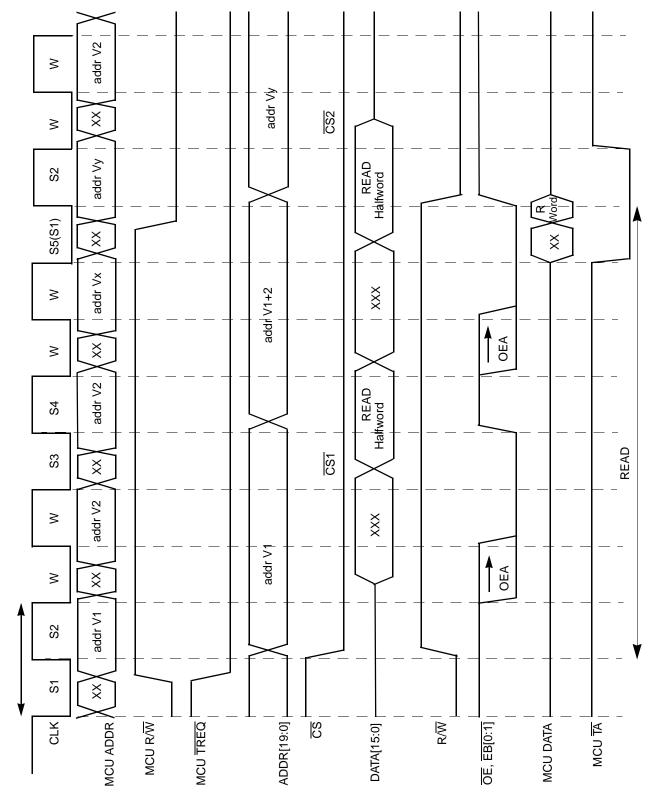

| 7-7  | Write Memory Access (CSA = 0, WSC = 1, WWS = 0)               |      |

| 7-8  | Word Read Access from Halfword Width Memory                   |      |

| 7-9  | Word Write Access to Halfword Width Memory                    |      |

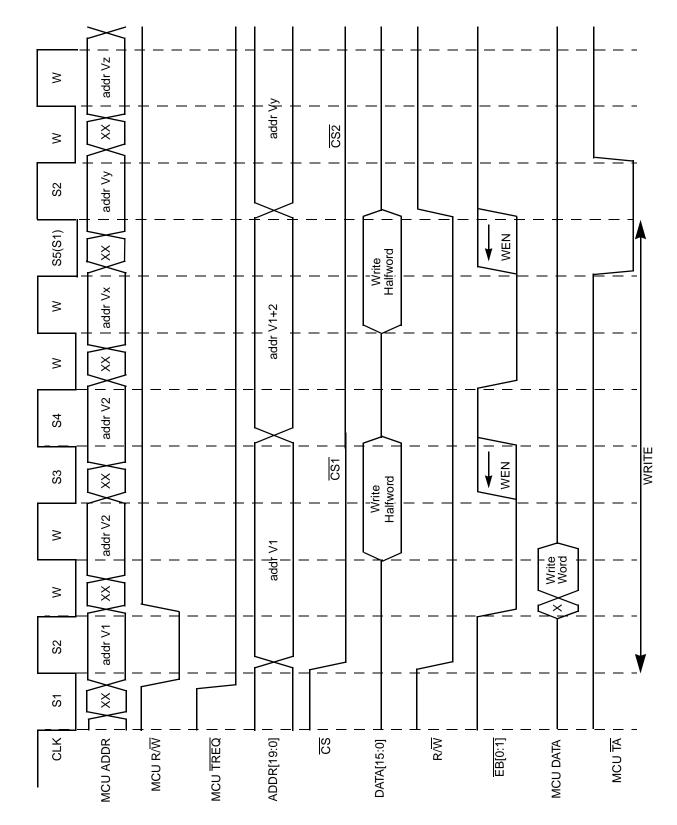

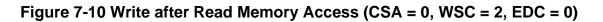

| 7-10 | Write after Read Memory Access (CSA = 0, WSC = 2, EDC = 0)    |      |

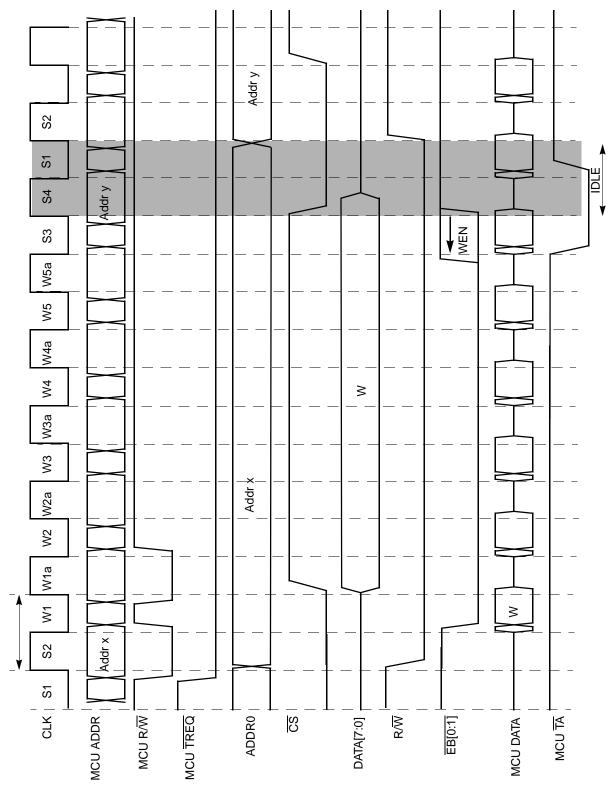

| 7-11 | Write after Read Memory Access (CSA = 0, WSC = 1, EDC = 1)    |      |

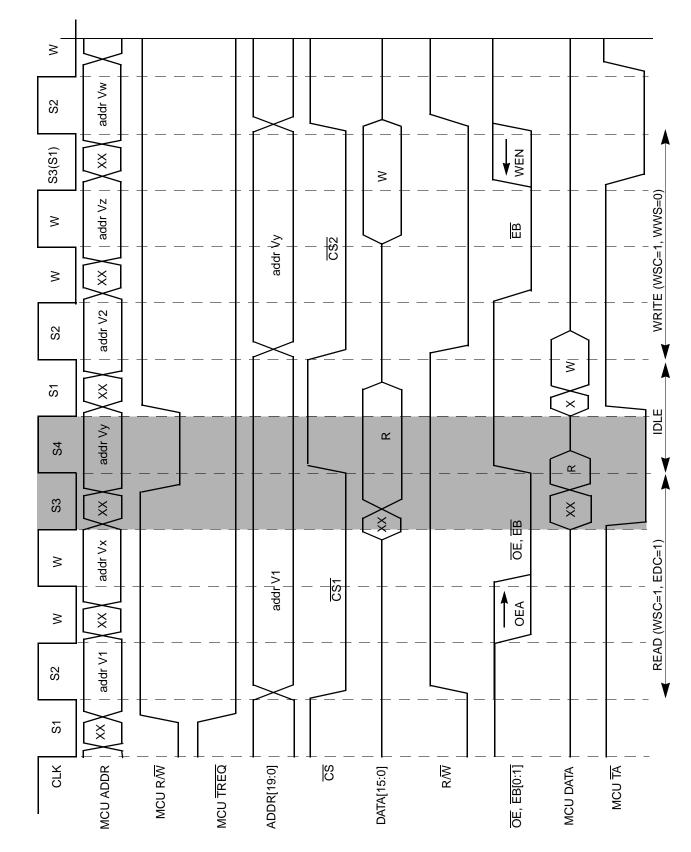

| 7-12 | Peripheral Read Access (CSA = 1, WSC = 5)                     |      |

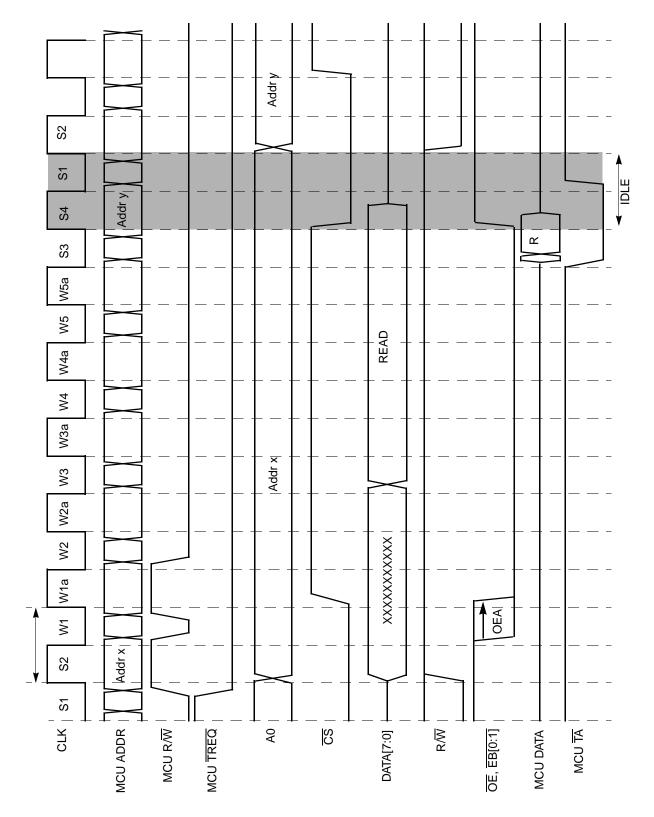

| 7-13 | Peripheral Write Access (CSA = 1, WSC = 5)                    |      |

| 7-14 | Read and Write Fast Memory Access (CSA = 0, WSC = 0, WWS = 0) |      |

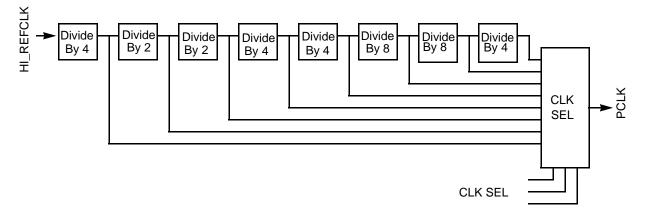

| 8-1  | MMC2001 Clock Module                                          |      |

| 9-1  | Reset Functional Block Diagram                                | 9-2  |

| 9-2  | Reset Source Register                                         |      |

| 9-3  | TOD Block Diagram                                             | 9-4  |

| 9-4  | TOD Control/Status Register                                   | 9-5  |

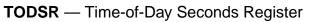

| 9-5  | TOD Seconds Register                                          |      |

| 9-6  | TOD Fraction Register                                         | 9-7  |

| 9-7  | TOD Seconds Alarm Register                                    | 9-7  |

| 9-8  | TOD Fraction Alarm Register                                   | 9-8  |

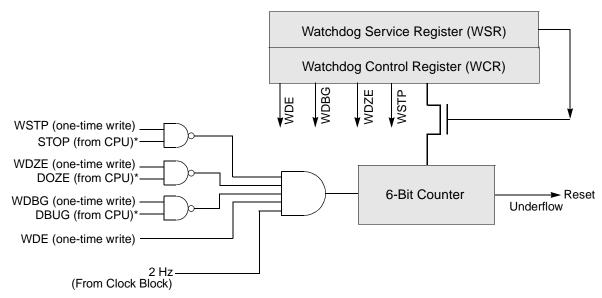

| 9-9  | Watchdog Timer Block Diagram                                  | 9-8  |

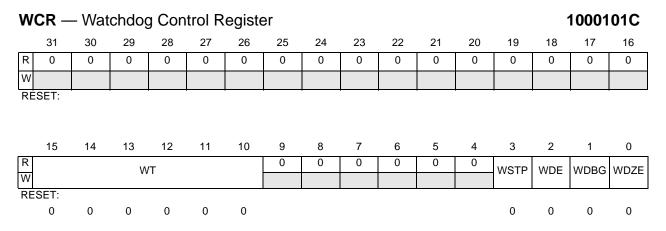

| 9-10 | Watchdog Control Register                                     | 9-10 |

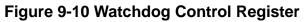

| 9-11 | Watchdog Service Register                                     | 9-11 |

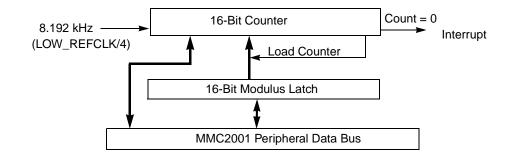

| 9-12 | PIT Block Diagram                                             | 9-12 |

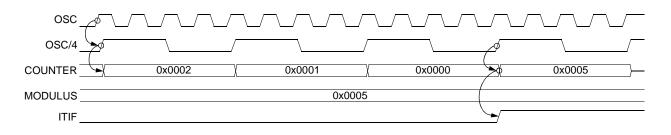

| 9-13 | Starting a Count from an Off State                            | 9-12 |

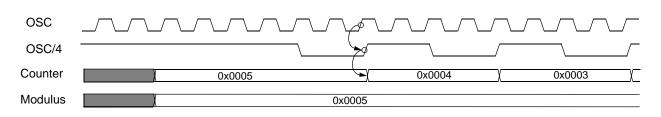

| 9-14 | Counter Reloading from the Modulus Latch                      | 9-13 |

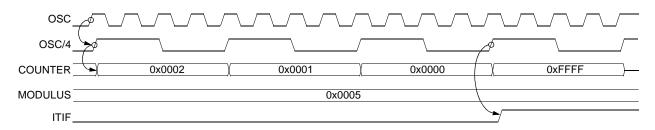

| 9-15 | Counter in Free-Running Mode                                  | 9-13 |

| 9-16 | PIT Control and Status Register                               | 9-14 |

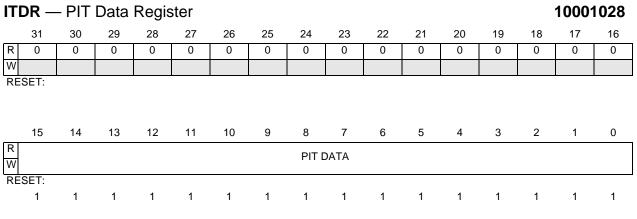

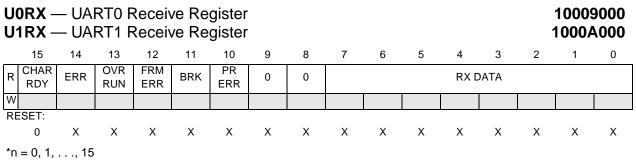

| 9-17 | PIT Data Register                                             | 9-15 |

| 9-18 | PIT Alternate Data Register                                   | 9-16 |

| 10-1 | Interrupt Source Register                                     |      |

| 10-2 | Normal Interrupt Enable Register                              |      |

MOTOROLA

Page

# **Freescale Semiconductor, Inc.**

# LIST OF ILLUSTRATIONS

Title

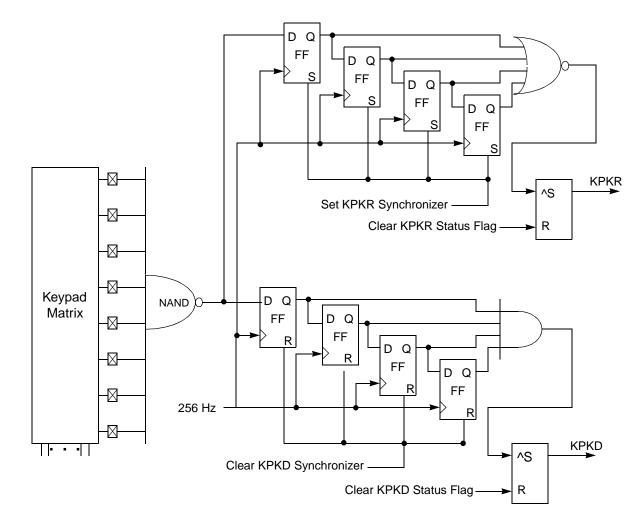

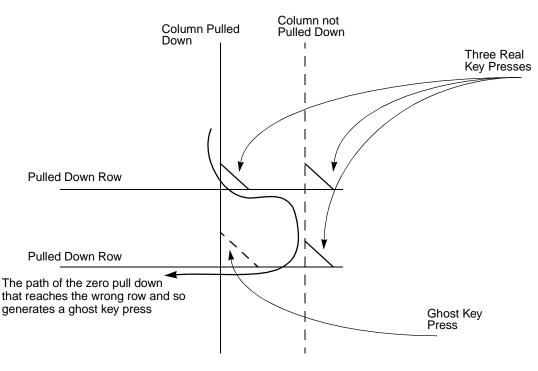

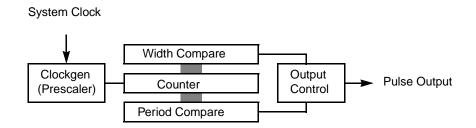

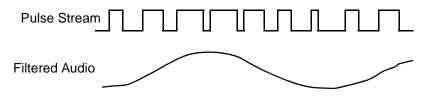

### 10-5 Fast Interrupt Pending Register ...... 10-5 11-1 11-4 UART Control Register 1 ...... 11-9 11-5 UART Control Register 2 ..... 11-12 11-6 UART BRG Register ...... 11-13 11-7 11-15 Start Bit — Noise Case Three...... 11-22 12-1 12-2 12-4 12-5 13-1 13-2 13-3 13-4 13-5 14-1 KPP Block Diagram......14-1 14-2 Keypad Control Register ...... 14-3 Keypad Status Register ...... 14-4 14-3 14-4 14-5 14-6 Keypad Synchronizer Functional Diagram......14-8 14-7 Decoding Wrong Three Key Presses......14-9 15-1 15-2 15-3 15-4 15-5

15-6

xvi

Page

# LIST OF ILLUSTRATIONS

| Parag        | raph Title                                                       | Page |

|--------------|------------------------------------------------------------------|------|

| 15-7         | PWM Count Registers                                              |      |

| 16-1         | OnCE Block Diagram                                               |      |

| 16-2         | OnCE Controller                                                  |      |

| 16-3         | OnCE Controller and Serial Interface                             |      |

| 16-4         | OnCE Command Register                                            |      |

| 16-5         | OnCE Control Register                                            |      |

| 16-6         | OnCE Status Register                                             |      |

| 16-7         | OnCE Memory Breakpoint Logic                                     |      |

| 16-8         | OnCE Trace Logic Block Diagram                                   |      |

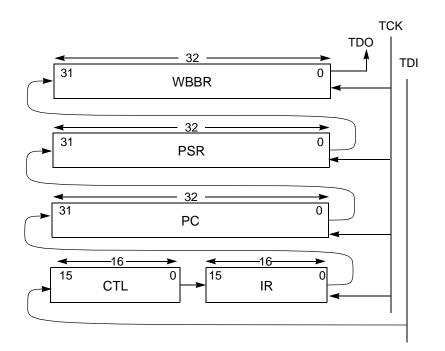

| 16-9         | CPU Scan Chain Register (CPUSCR)                                 |      |

|              | Control State Register                                           |      |

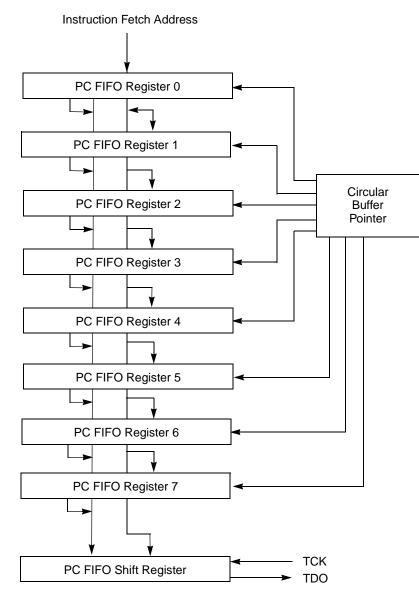

|              | OnCE PC FIFO                                                     |      |

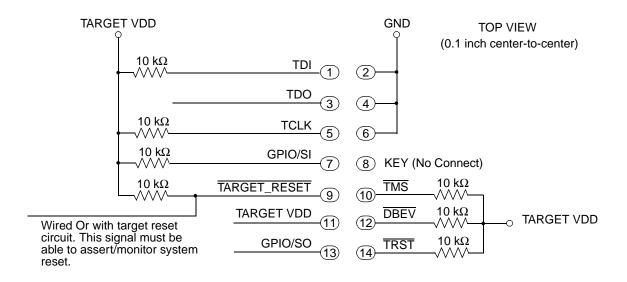

|              | Recommended Connector Interface to JTAG/On                       |      |

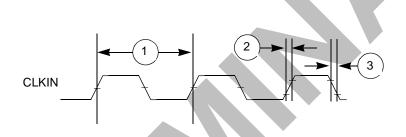

| A-1          | CLKIN Timing (for Square Wave Input)                             |      |

| A-2          | Reset Timing                                                     |      |

| A-3          | MOD Timing                                                       |      |

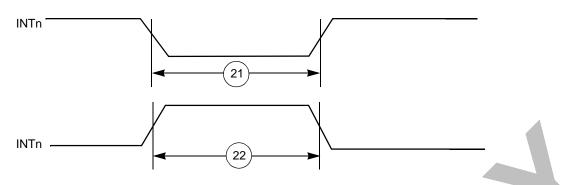

| A-4          | External Interrupt Timing                                        |      |

| A-5          | EIM Read/Write Timing                                            |      |

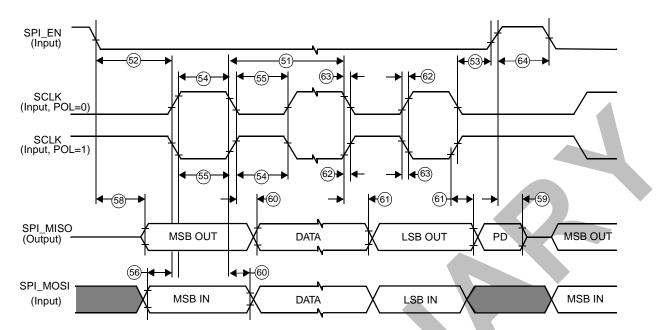

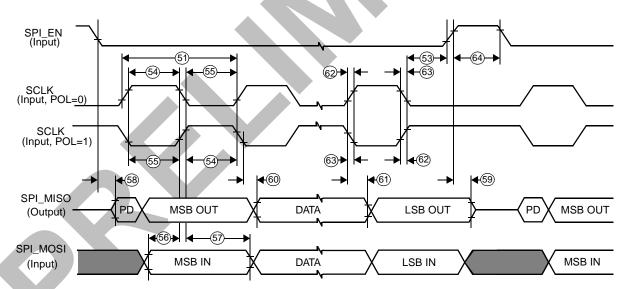

| A-6          | SPI Slave Timing (PHA = 0)                                       |      |

| A-7          | SPI Slave Timing (PHA = 1)                                       |      |

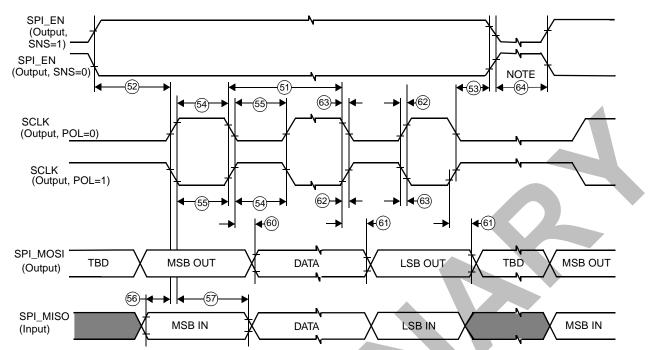

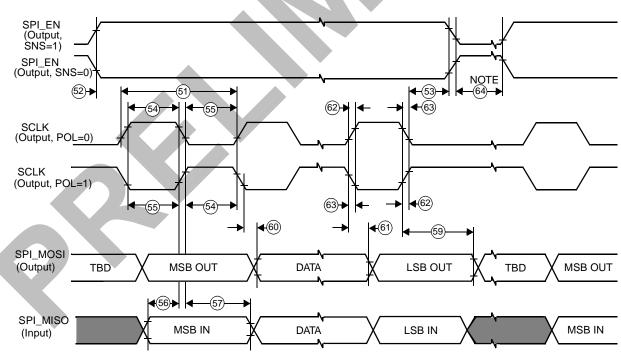

| A-8          | SPI Manual/Interval Mode Timing (PHA = 0)                        |      |

| A-9          | SPI Manual/Interval Mode Timing (PHA = 1)                        |      |

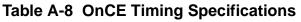

| A-10         | Test Clock Input Timing                                          |      |

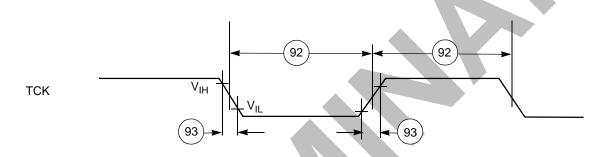

| A-11         | TRST Timing                                                      |      |

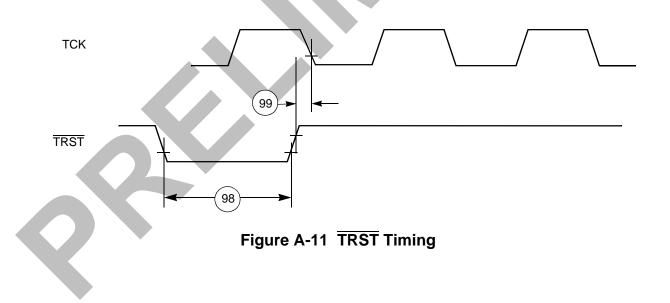

| A-12         | Test Access Port Timing                                          |      |

| B-1          | 144-Lead Plastic Thin Quad Flat Pack Pin Assig                   |      |

| C-1          | Interrupt Source Register                                        |      |

| C-2          | Normal Interrupt Enable Register                                 |      |

| C-3          | Fast Interrupt Enable Register                                   |      |

| C-4          | Normal Interrupt Pending Register                                |      |

| C-5<br>C-6   | Fast Interrupt Pending Register                                  |      |

| C-6<br>C-7   | Reset Source Register                                            |      |

| C-7<br>C-8   | TOD Control/Status Register                                      |      |

| C-8<br>C-9   | TOD Seconds Register                                             |      |

| C-9<br>C-10  | TOD Fraction Register                                            |      |

| C-10<br>C-11 | TOD Seconds Alarm Register<br>TOD Fraction Alarm Register        |      |

| C-12         | 0                                                                |      |

| C-12<br>C-13 | Watchdog Control Register                                        |      |

| C-13<br>C-14 | Watchdog Service Register<br>PIT Control and Status Register     |      |

| C-14<br>C-15 | PIT Data Register                                                |      |

| C-15<br>C-16 | PIT Data Register<br>PIT Alternate Data Register                 |      |

| C-10<br>C-17 | Keypad Control Register                                          |      |

| 0-17         | They part of the they are the the the the the the the the the th |      |

MOTOROLA xvii

# LIST OF ILLUSTRATIONS

| Parag | yraph                          | Title | Page |

|-------|--------------------------------|-------|------|

| C-18  | Keypad Status Register         |       | C-14 |

| C-19  | Keypad Data Direction Register |       |      |

| C-20  | Keypad Data Register           |       | C-16 |

| C-21  | CS0 Control Register           |       | C-17 |

| C-22  | CS1, CS2, CS3 Control Register | ers   | C-17 |

| C-23  | EIM Configuration Register     |       |      |

| C-24  | PWM Control Registers          |       | C-23 |

| C-25  | PWM Period Registers           |       | C-26 |

| C-26  | PWM Width Registers            |       | C-26 |

| C-27  | PWM Count Registers            |       | C-27 |

| C-28  | Edge Port Pin Assignment Reg   | ster  | C-28 |

| C-29  | Edge Port Data Direction Regis |       |      |

| C-30  | Edge Port Data Register        |       | C-29 |

| C-31  | Edge Port Flag Register        |       | C-29 |

| C-32  | ISPI Data Register             |       | C-30 |

| C-33  | ISPI Control Register          |       | C-31 |

| C-34  | ISPI Interval Control Register |       | C-33 |

| C-35  | ISPI Status Register           |       | C-34 |

| C-36  | UART Receive Register          |       | C-36 |

| C-37  | UART Transmit Register         |       | C-37 |

| C-38  | UART Control Register 1        |       | C-38 |

| C-39  | UART Control Register 2        |       | C-40 |

| C-40  | UART BRG Register              |       | C-42 |

| C-41  | UART Status Register           |       | C-42 |

| C-42  | UART Test Register             |       | C-44 |

| C-43  | UART Port Control Register     |       | C-44 |

| C-44  | UART Data Direction Register.  |       | C-45 |

| C-45  | UART Port Data Register        |       | C-45 |

| C-46  | OnCE Command Register          |       | C-46 |

| C-47  | OnCE Control Register          |       | C-47 |

| C-48  | OnCE Status Register           |       | C-50 |

| C-49  | Control State Register         |       | C-52 |

# **Freescale Semiconductor, Inc.**

# LIST OF TABLES

Title

Page

| 2-1        | M•CORE Instruction Set2-6                        |

|------------|--------------------------------------------------|

| 2-1        | M•CORE Bus Signals                               |

| 2-2<br>2-3 | Interface Requirements for Read and Write Cycles |

| 2-3<br>2-4 | Termination Result Summary                       |

| 2-4<br>3-1 | MMC2001 Module Address Map                       |

| 3-2        | MMC2001 Address Map                              |

| 3-2<br>4-1 | Pin Requirements in 144-Pin Package              |

| 4-1<br>5-1 |                                                  |

| 5-1<br>6-1 | ROM Module Address Map                           |

| ו-ט<br>7-1 | Static RAM Module Address Map                    |

|            | Chip Select Address Range                        |

| 7-2        | Interface Requirements for Read and Write Cycles |

| 7-3        | EIM Memory Map                                   |

| 7-4        | Wait State Control Field Settings                |

| 7-5        | Data Port Size Field Settings                    |

| 7-6        | Show Cycle Enable Field Settings                 |

| 8-1        | CPU Core and Peripherals Clock Source            |

| 8-2        | CPU Core and Peripherals in Low-Power Modes      |

| 9-1        | Timer/Reset Module Address Map                   |

| 10-1       | Interrupt Controller Address Map                 |

| 10-2       | Interrupt Source Assignment                      |

| 11-1       | UART Module Address Map                          |

| 11-2       | TxFL Field Settings                              |

| 11-3       | RxFL Field Settings                              |

| 11-4       | UART Pins GPIO Assignment11-16                   |

| 11-5       | UART Low-Power Mode Operation11-23               |

| 12-1       | ISPI Module Address Map 12-4                     |

| 12-2       | BAUD RATE Field Settings12-7                     |

| 12-3       | CLOCK COUNT Field Settings 12-7                  |

| 12-4       | ISPI Low-Power Mode Operation12-11               |

| 13-1       | GPIO Edge Port Address Map13-2                   |

| 13-2       | EPPAx Field Settings                             |

| 14-1       | Keypad Port Column Modes14-2                     |

| 14-2       | Keypad Port Address Map14-2                      |

| 15-1       | PWM Address Map15-3                              |

| 15-2       | CLK SEL Field Settings                           |

| 15-3       | PWM Range at 16 MHz 15-8                         |

| 15-4       | PWM Low-Power Mode Operation15-8                 |

| 16-1       | OnCE Register Addressing                         |

| 16-2       | Sequential Control Field Settings                |

| 16-3       | Memory Breakpoint Control Field Settings         |

| 16-4       | Processor Mode Field Settings                    |

| A-1        | Maximum RatingsA-1                               |

| A-2        | DC Electrical Specifications                     |

MOTOROLA

# Freescale Semiconductor, Inc.

# LIST OF TABLES

Title

### A-3 A-4 A-5 EIM Timing Specifications......A-4 A-6 A-7 A-8 MMC2001 Address Map .....C-1 C-1 C-2 Interrupt Controller Address Map .....C-2 C-3 Timer/Reset Module Address Map .....C-5 C-4 Keypad Port Address Map .....C-13 C-5 EIM Address Map .....C-16 Wait State Control Field Settings ......C-18 C-6 C-7 C-8 Chip-Select Address Range.....C-20 C-9 C-10 PWM Address Map .....C-22 C-11 Clock Select Field Values .....C-25 C-12 GPIO Edge Port Address Map .....C-27 C-13 EPPAx Field Settings.....C-28 C-14 Interval Mode Serial Peripheral Interface Address Map......C-30 C-15 BAUD RATE Values.....C-32 C-16 CLOCK COUNT Values.....C-33 C-17 UART Module Address Map .....C-35 C-19 RxFL Field Settings......C-39 C-20 OnCE Register Addressing......C-47 C-21 Sequential Control Field Definition......C-48 C-22 Memory Breakpoint Control Field Definition.....C-49 C-23 Processor Mode Field Definition ......C-51

Page

# SECTION 1 INTRODUCTION

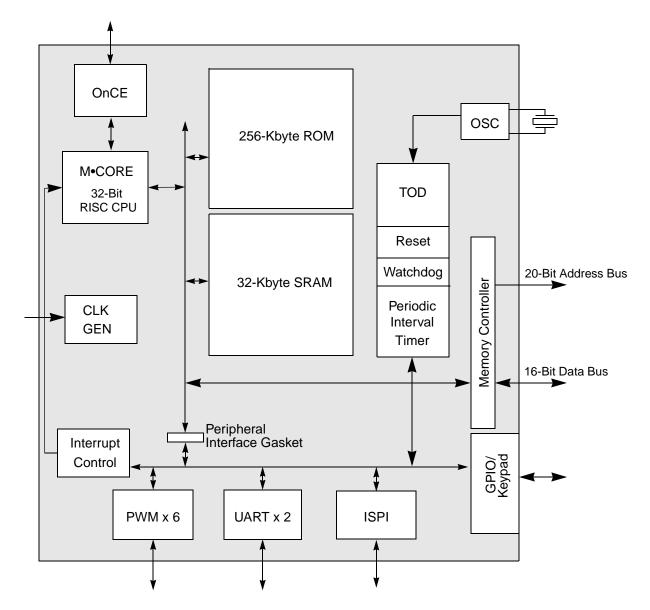

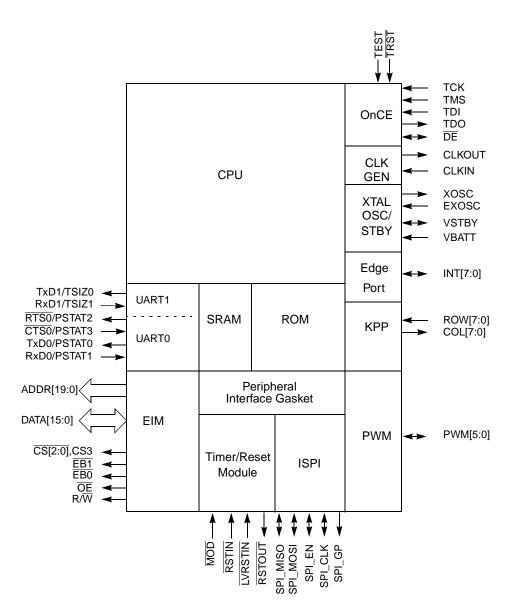

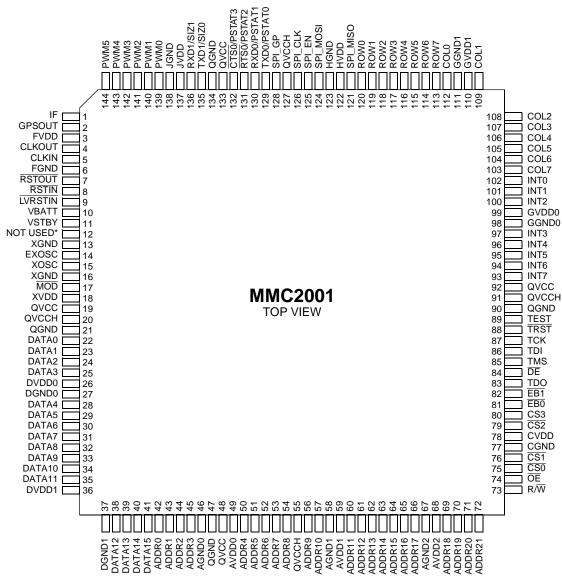

The MMC2001 integrated processor incorporates the following functional units:

- M•CORE<sup>™</sup> Integer Processor

- 32-bit RISC architecture

- Low power, high performance

- On-chip, 256-Kbyte ROM

- On-chip, 32-Kbyte SRAM with battery backup supply support

- Interrupt Controller

- Support for up to 32 interrupt sources

- External Interface Module (EIM)

- Transfers information between the MMC2001 and external memory or peripherals

- 22 address lines

- 16 data lines

- Chip select and wait state generation

- Bus watchdog timer

- Timer/Reset Module

- Crystal oscillator: generates the master clock signal for the time-of-day timer from a 32.768-kHz external crystal

- Time-of-day timer: provides time-of-day information as well as an alarm clock function

- Watchdog timer: resets the chip to recover from system failure

- Reset unit: provides low voltage detection input and backup power switching for SRAM and the time-of-day timer

- Periodic interrupt timer

- Universal Asynchronous Receiver/Transmitter Module (UART)

- Two independent UART channels

- Asynchronous operation

- Baud rate generation

- Infrared (IR) interface support

- 16-bit general-purpose I/O port with support for keyboard scan/encode

- 8-bit general-purpose I/O port with support for edge/level sensitive external interrupts

- Pulse-Width Modulation Module (PWM)

- Six independent PWM channels

- Programmable period

- Programmable duty cycle

- Periodic interrupt capability

- Pins can be configured as general-purpose I/O

- Interval Mode Serial Peripheral Interface (ISPI)

- Efficient communication with slower serial peripherals

MMC2001 REFERENCE MANUAL

### INTRODUCTION

MOTOROLA 1-1

- Designed for master/slave SPI operation

- Interval-mode SPI operation

- OnCE<sup>™</sup> Debug Module

As a low-voltage part, the MMC2001 operates at voltages between 2.0 and 3.3 volts. It is particularly suited for use in battery-powered applications.

The internal logic and external I/O buffers are provided with independent power supply connections to allow 3.3-V I/O levels while operating internal logic at 2.0 V for lower power consumption.

Figure 1-1 MMC2001 Block Diagram

INTRODUCTION

MMC2001 REFERENCE MANUAL

# SECTION 2 INTEGER CPU

This section gives a short description of the M•CORE CPU features and some basic bus interface information.

# 2.1 M•CORE Overview

The 32-bit M•CORE microRISC engine represents a new family of Motorola microprocessor core products. The processor architecture has been designed for high-performance and cost-sensitive embedded control applications, with particular emphasis on reduced system power consumption. This makes the M•CORE suitable for battery-operated, portable products, as well as for highly integrated parts designed for a high temperature environment.

Total system power consumption is dictated by various components in addition to the processor core. In particular, memory power consumption (both on-chip and external) is expected to dominate overall power consumption of the core-plus-memory subsystem. With this factor in mind, the instruction set architecture (ISA) for M•CORE makes the trade-off of absolute performance capability versus total energy consumption in favor of reducing the overall energy consumption, while maintaining an acceptably high level of performance at a given clock frequency.

M•CORE is a streamlined execution engine that provides many of the same performance enhancements as mainstream reduced instruction set computer (RISC) designs. Fixed length instruction encoding and a strict load/store architecture minimize control complexity and overhead. The goal of minimizing the overhead of memory system energy consumption is achieved by adopting a (relatively) short 16-bit instruction encoding. This choice significantly lowers the memory bandwidth needed to sustain a high rate of instruction execution.

Code density statistics for a number of applications show relative code density competitive in comparison to complex instruction set computer (CISC) designs, and implementation statistics show a large reduction in complexity and overhead relative to a CISC approach.

In addition to substantial cost and performance benefits, M•CORE also offers advantages in power consumption and power management. M•CORE minimizes power dissipation by using a fully static design, dynamic power management, and low-voltage operation. The M•CORE automatically powers-down internal functional blocks that are not needed on a clock-by-clock basis. Power conservation modes are also provided for absolute power conservation on a coarser granularity.

# 2.2 Features

The main features of the M•CORE are as follows:

- 32-bit load/store RISC architecture

- Fixed 16-bit instruction length

- 16-entry, 32-bit general-purpose register file

- Efficient 4-stage execution pipeline, hidden from application software

- Single-cycle instruction execution for many instructions

- Two cycles for taken branches and memory access instructions

- Support for byte, halfword, and word memory accesses

- Fast interrupt support with 16-entry dedicated alternate register file

- Vectored and autovectored interrupt support

# 2.3 Microarchitecture Summary

The M•CORE instruction execution pipeline consists of the following stages:

- Instruction fetch

- Instruction decode/register file read

- Execute

- Register writeback

These stages operate in an overlapped fashion, allowing single-clock instruction execution for most instructions.

Sixteen general-purpose registers are provided for source operands and instruction results. Register R15 is used as the link register to hold the return address for sub-routine calls, and register R0 is associated with the current stack pointer value by convention.

The execution unit consists of a 32-bit arithmetic/logic unit (ALU), a 32-bit barrel shifter, a find-first-one unit (FFO), result feed-forward hardware, and miscellaneous support hardware for multiplication and multiple register loads and stores. Arithmetic and logical operations are executed in a single cycle with the exception of the multiply, signed divide, and unsigned divide instructions. The multiply instruction is implemented with a 2-bit per clock, overlapped-scan, modified Booth algorithm with early-out capability to reduce execution time for operations with small multiplier values. The signed divide and unsigned divide instructions also have data-dependent timing. A find-first-one unit operates in a single clock cycle.

The program counter unit has a PC incrementer and a dedicated branch address adder to minimize delays during change of flow operations. Branch target addresses are calculated in parallel with branch instruction decode, with a single pipeline bubble for taken branches and jumps. This results in an execution time of two clocks. Conditional branches that are not taken execute in a single clock.

Memory load and store operations are provided for byte, halfword, and word (32-bit) data with automatic zero extension of byte and halfword load data. These instructions can execute in two clock cycles. Load and store multiple register instructions allow low overhead context save and restore operations. These instructions can execute in (N+1) clock cycles, where N is the numbers of registers to transfer.

MOTOROLA 2-2 INTEGER CPU

MMC2001 REFERENCE MANUAL

A single condition code/carry (C) bit is provided for condition testing and for use in implementing arithmetic and logical operations greater than 32 bits. Typically, the C-bit is set only by explicit test/comparison operations, not as a side-effect of normal instruction operation. Exceptions to this rule occur for specialized operations for which it is desirable to combine condition setting with actual computation.

A 16-entry alternate register file is provided to support low overhead interrupt exception processing. The CPU supports both vectored and autovectored interrupts.

# 2.4 Programming Model

The M•CORE programming model is defined separately for two privilege modes: supervisor and user. Certain operations are not available in user mode.

User programs can only access registers specific to the user mode; system software executing in the supervisor mode can access all registers, using the control registers to perform supervisory functions. User programs are thus restricted from accessing privileged information. The operating system performs management and service tasks for the user programs by coordinating their activities.

Most instructions execute in either mode, but some instructions that have important system effects are privileged and can only execute in the supervisor mode. For instance, user programs cannot execute the **stop**, **doze**, or **wait** instructions. To prevent a user program from entering the supervisor mode except in a controlled manner, instructions that can alter the S bit in the program status register (PSR) are privileged. The **trap #n** instructions provide controlled access to operating system services for user programs. Access to special control registers is also precluded in user mode.

When the S bit in the PSR is set, the processor executes instructions in the supervisor mode. Bus cycles associated with an instruction indicate either supervisor or user access depending on the mode.

The processor uses the user programming model during normal user mode processing. During exception processing, the processor changes from user to supervisor mode. Exception processing saves the current value of the PSR in the EPSR or FPSR shadow control register and then sets the S bit in the PSR, forcing the processor into the supervisor mode. To return to the previous operating mode, a system routine may execute the **rte** (return from exception) or **rfi** (return from fast interrupt) instruction as appropriate, causing the instruction pipeline to be flushed and refilled from the appropriate address space.

The registers depicted in the programming model (see **Figure 2-1**) provide operand storage and control. The registers are partitioned into two levels of privilege: user and supervisor. The user programming model consists of 16 general-purpose 32-bit registers, the 32-bit program counter (PC) and the condition/carry (C) bit. The C bit is implemented as bit 0 of the PSR. This is the only portion of the PSR accessible by the user. The supervisor programming model consists of 16 additional 32-bit general-purpose registers (the alternate file), as well as a set of status/control registers and scratch registers. By convention, register R15 serves as the link register for subroutine calls, and register R0 is typically used as the current stack pointer.

MMC2001 REFERENCE MANUAL **INTEGER CPU**

MOTOROLA 2-3

The alternate file is selected for use via a control bit in the PSR. The status, control, and scratch registers are accessed via the move from control register (**mfcr**) and move to control register (**mtcr**) instructions. When the alternate file is selected via the AF bit in the PSR, general-purpose operands are accessed from it. When the AF bit is cleared, operands are accessed from the normal file. This alternate file is provided to allow very low overhead context switching capability for real-time event handling.

| R13        | R13<br>R14 | GSR CF           |

|------------|------------|------------------|

| R12<br>R13 | R12        | GCR CF           |

| R11        | R11        | SS4 CF           |

| R10        | R10        | SS3 CF           |

| R9         | R9         | SS1 CF<br>SS2 CF |

| R8         | R7<br>R8   | SS0 CF           |

| R7         | R6         | FPC CF           |

| R6         | R5         | EPC CF           |

| R5         | R4         | FPSR CF          |

| R3<br>R4   | R3         | EPSR CF          |

| R2         | R2         | VBR CF           |

| R1         | R0<br>R1   | PSR CF           |

Figure 2-1 Programming Model

The supervisor programming model includes the PSR, which contains operation control and status information. In addition, a set of exception shadow registers is provided to save the state of the PSR and the program counter at the time an exception occurs. A separate set of shadow registers is provided for fast interrupt support to minimize context saving overhead.

Five scratch registers are provided for supervisor software use in handling exception events. A single register is provided to alter the base address of the exception vector table. Two registers are provided for global control and status.

Semiconductor, Inc.

0

eescal

# **Freescale Semiconductor, Inc.**

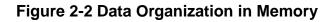

# 2.5 Data Format Summary

The operand data formats supported by the integer unit are standard two's-complement data formats. The operand size for each instruction is either explicitly encoded in the instruction (load/store instructions) or implicitly defined by the instruction operation (index operations, byte extraction). Typically, instructions operate on all 32 bits of the source operand(s) and generate a 32-bit result.

Memory is viewed from a big-endian byte ordering perspective. The most significant byte (byte 0) of word 0 is located at address 0. Bits are numbered within a word starting with bit 31 as the most significant bit.

| 31     |        |        | 0      | _         |

|--------|--------|--------|--------|-----------|

| Byte 0 | Byte 1 | Byte 2 | Byte 3 | Word at 0 |

| Byte 4 | Byte 5 | Byte 6 | Byte 7 | Word at 4 |

| Byte 8 | Byte 9 | Byte A | Byte B | Word at 8 |

| Byte C | Byte D | Byte E | Byte F | Word at C |

Figure 2-3 Data Organization in Registers

# 2.6 Operand Addressing Capabilities

M•CORE accesses all memory operands through load and store instructions, transferring data between the general-purpose registers and memory. Register-plus-fourbit scaled displacement addressing mode is used for the load and store instructions to address byte, halfword, or word (32-bit) data.

Load and store multiple instructions allow a subset of the 16 GPRs to be transferred to or from a base address pointed to by register R0 (the default stack pointer by convention).

Load and store register quadrant instructions use register indirect addressing to transfer a register quadrant to or from memory.

# 2.7 Instruction Set Overview

The instruction set is tailored to support high-level languages and is optimized for those instructions most commonly executed. A standard set of arithmetic and logical instructions is provided, as well as instruction support for bit operations, byte extraction, data movement, control flow modification, and a small set of conditionally executed instructions which can be useful in eliminating short conditional branches.

**Table 2-1** is an alphabetized listing of the M•CORE instruction set. Refer to the M•CORE Reference Manual (MCORERM/AD) for more details on instruction operation.

| Mnemonic Description |                                      |  |  |  |

|----------------------|--------------------------------------|--|--|--|

| ABS                  | Absolute Value                       |  |  |  |

| ADDC                 | Add with C Bit                       |  |  |  |

| ADDI                 | Add Immediate                        |  |  |  |

| ADDU                 | Add Unsigned                         |  |  |  |

| AND                  | Logical AND                          |  |  |  |

| ANDI                 | Logical AND Immediate                |  |  |  |

| ANDN                 | AND NOT                              |  |  |  |

| ASR                  | Arithmetic Shift Right               |  |  |  |

| ASRC                 | Arithmetic Shift Right, Update C Bit |  |  |  |

| BCLRI                | Bit Clear Immediate                  |  |  |  |

| BF                   | Branch on Condition False            |  |  |  |

| BGENI                | Bit Generate Immediate               |  |  |  |

| BGENR                | Bit Generate Register                |  |  |  |

| ВКРТ                 | Breakpoint                           |  |  |  |

| BMASKI               | Bit Mask Immediate                   |  |  |  |

| BR                   | Branch                               |  |  |  |

| BREV                 | Bit Reverse                          |  |  |  |

| BSETI                | Bit Set Immediate                    |  |  |  |

| BSR                  | Branch to Subroutine                 |  |  |  |

| BT                   | Branch on Condition True             |  |  |  |

| BTSTI                | Bit Test Immediate                   |  |  |  |

# Table 2-1 M•CORE Instruction Set

# Table 2-1 M•CORE Instruction Set (Continued)

| Mnemonic   | Description                                                      |

|------------|------------------------------------------------------------------|

| CLRF       | Clear Register on Condition False                                |

| CLRT       | Clear Register on Condition True                                 |

| CMPHS      | Compare Higher or Same                                           |

| CMPLT      | Compare Less Than                                                |

| CMPLTI     | Compare Less Than Immediate                                      |

| CMPNE      | Compare Not Equal                                                |

| CMPNEI     | Compare Not Equal Immediate                                      |

| DECF       | Decrement on Condition False                                     |

| DECGT      | Decrement Register and Set Condition if Result Greater Than Zero |

| DECLT      | Decrement Register and Set Condition if Result Less Than Zero    |

| DECNE      | Decrement Register and Set Condition if Result Not Equal to Zero |

| DECT       | Decrement on Condition True                                      |

| DIVS       | Divide Signed Integer                                            |

| DIVU       | Divide Unsigned Integer                                          |

| DOZE       | Doze                                                             |

| FF1        | Find First One                                                   |

| INCF       | Increment on Condition False                                     |

| INCT       | Increment on Condition True                                      |

| IXH        | Index Halfword                                                   |

| IXW        | Index Word                                                       |

| JMP        | Jump                                                             |

| JMPI       | Jump Indirect                                                    |

| JSR        | Jump to Subroutine                                               |

| JSRI       | Jump to Subroutine Indirect                                      |

| LD.[BHW]   | Load                                                             |

| LDM        | Load Multiple Registers                                          |

| LDQ        | Load Register Quadrant                                           |

| LOOPT      | Decrement with C-Bit Update and Branch if Condition True         |

| LRW        | Load Relative Word                                               |

| LSL, LSR   | Logical Shift Left and Right                                     |

| LSLC, LSRC | Logical Shift Left and Right, Update C Bit                       |

| LSLI, LSRI | Logical Shift Left and Right by Immediate                        |

| MFCR       | Move from Control Register                                       |

| MOV        | Move                                                             |

| MOVI       | Move Immediate                                                   |

| MOVF       | Move on Condition False                                          |

| MOVT       | Move on Condition True                                           |

| MTCR       | Move to Control Register                                         |

| MULT       | Multiply                                                         |

| MVC        | Move C Bit to Register                                           |

| MVCV       | Move Inverted C Bit to Register                                  |

| NOT        | Logical Complement                                               |

| OR         | Logical Inclusive-OR                                             |

| ROTLI      | Rotate Left by Immediate                                         |

| RSUB       | Reverse Subtract                                                 |

| RSUBI      | Reverse Subtract Immediate                                       |

| RTE        | Return from Exception                                            |

| RFI        | Return from Interrupt                                            |

MMC2001 REFERENCE MANUAL

| Mnemonic                                               | Description                                                                                                                                        |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| SEXTB                                                  | Sign-Extend Byte                                                                                                                                   |

| SEXTH                                                  | Sign-Extend Halfword                                                                                                                               |

| ST.[BHW]                                               | Store                                                                                                                                              |

| STM                                                    | Store Multiple Registers                                                                                                                           |

| STQ                                                    | Store Register Quadrant                                                                                                                            |

| STOP                                                   | Stop                                                                                                                                               |

| SUBC                                                   | Subtract with C Bit                                                                                                                                |

| SUBU                                                   | Subtract                                                                                                                                           |

| SUBU                                                   | Subtract                                                                                                                                           |

| SUBI                                                   | Subtract Immediate                                                                                                                                 |

| SYNC                                                   | Synchronize                                                                                                                                        |

| TRAP                                                   | Trap                                                                                                                                               |

| TST                                                    | Test Operands                                                                                                                                      |

| TSTNBZ                                                 | Test for No Byte Equal Zero                                                                                                                        |

| WAIT<br>XOR<br>XSR<br>XTRB0<br>XTRB1<br>XTRB2<br>XTRB3 | Wait         Exclusive OR         Extended Shift Right         Extract Byte 0         Extract Byte 1         Extract Byte 2         Extract Byte 3 |

| ZEXTB                                                  | Zero-Extend Byte                                                                                                                                   |

| ZEXTH                                                  | Zero-Extend Halfword                                                                                                                               |

# Table 2-1 M•CORE Instruction Set (Continued)

# 2.8 M•CORE Bus Interface

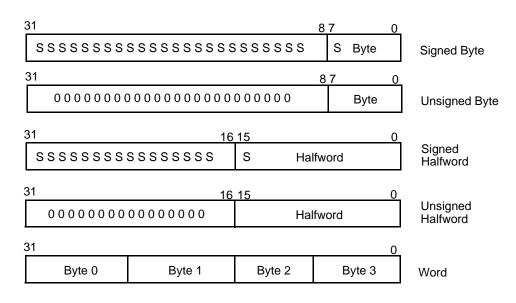

The M•CORE bus is a synchronous pipelined interface. Signals driven on this bus are required to meet the set up and hold time relative to the falling and rising edges of the bus clock.

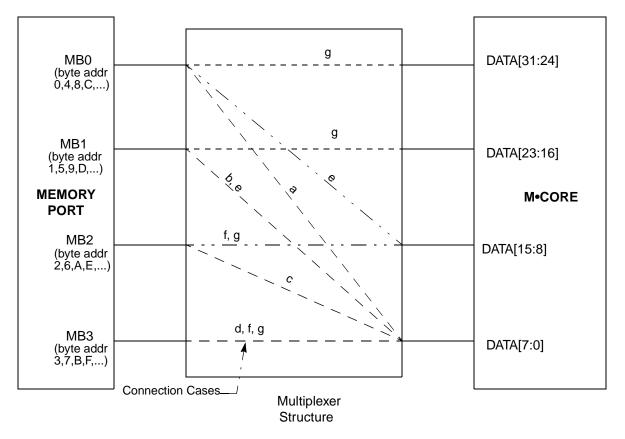

The M•CORE architecture supports byte, half-word, and word operands, allowing access to 8-,16-, and 32-bit data ports through the use of synchronous cycles controlled by the size outputs (TSIZ0, TSIZ1).

M•CORE bus interface features are summarized below.

- 32-bit address bus with transfer size indication

- 32-bit data bus

- Signals referenced to both the rising and falling edges of the bus clock

- Only aligned transfers allowed

- M•CORE is the only bus master; no arbitration support

- 32-bit fixed port size

# 2.8.1 Bus Characteristics

The bus transfers information between the M•CORE and external memory or a peripheral device via the external and internal bus interfaces. The M•CORE port size is fixed at 32 bits. External devices can accept or provide eight or 16 bits in parallel and must follow the handshake protocol described in this section. The number of bits accepted or provided during a bus transfer is defined as the transfer size. The M•CORE uses the address bus to specify the address for the transfer and the data bus to transfer the data. Control and attribute signals indicate the beginning and type

MOTOROLA 2-8 **INTEGER CPU**

MMC2001 REFERENCE MANUAL

of the cycle as well as the address space and size of the transfer. The selected device then controls the length of the cycle with the signal(s) used to terminate the cycle. Access requests are generated in an overlapped fashion in order to support sustained single-cycle transfers.

Inputs to the M•CORE are sampled synchronously and must be stable during the sample windows defined in **Figure 2-4**. If an input makes a transition during the window time period, the level recognized by the M•CORE is not predictable.

Outputs from the M•CORE change on one of the two clock edges, depending on the signal class.

th = time hold

# Figure 2-4 Signal Relationships to Clocks

# 2.8.2 Bus Signals

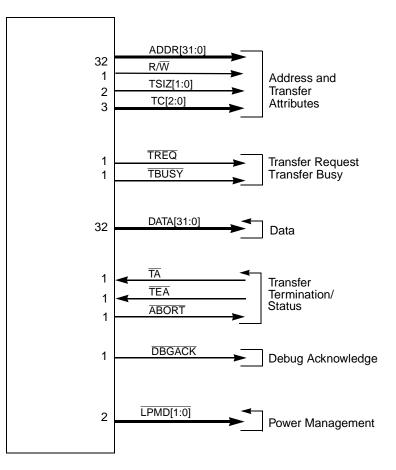

Figure 2-5 shows the M•CORE bus signals arranged by functional group.

Figure 2-5 M•CORE Bus Signals

# 2.8.3 Signal Descriptions

**Table 2-2** lists and describes the bus interface signals. More detailed descriptions can be found in subsequent sections. Signal direction is relative to the M•CORE.

**INTEGER CPU**

MMC2001 REFERENCE MANUAL

| Signal Name                          | Pins        | Active | I/O | Description                                                                                                                                                                                          |

|--------------------------------------|-------------|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address and Transfer A               |             |        |     |                                                                                                                                                                                                      |

| ADDR[31:0]<br>Address Bus            | 32          | High   | 0   | Driven by the M•CORE to specify the physical address of the bus transaction.                                                                                                                         |

| R/W<br>Read/Write 1 High             |             | High   | 0   | Driven by the M•CORE along with the address. Driven<br>high indicates that a read access is in progress. Driven<br>low indicates that a write access is in progress.                                 |

| TSIZ[1:0]<br>Transfer Size           | 2           | High   | 0   | Driven by the M•CORE along with the address. Specifies the data transfer size for the transaction.                                                                                                   |

| TC[2:0]<br>Transfer Code             | 3           | High   | 0   | Driven by the M•CORE along with the address. Indicates the type of access for the current bus cycle.                                                                                                 |

| Transfer Request/Transf              | fer Busy    |        |     |                                                                                                                                                                                                      |

| TREQ<br>Transfer Request             | 1           | Low    | 0   | Driven by the M•CORE along with the address and trans-<br>fer attributes to indicate that a new access has been<br>requested.                                                                        |

| TBUSY<br>Transfer Busy               | 1           | Low    | ο   | Driven by the M•CORE to indicate that an access is in progress. This signal is driven for the duration of a cycle and may be held asserted for multiple transfers.                                   |

| Data                                 |             |        |     |                                                                                                                                                                                                      |

| DATA[31:0]                           | 32          | High   | 0   | Driven by the M•CORE when it "owns" the bus and it initi-<br>ated a write transaction to a slave device. Eight (byte), 16<br>(halfword), or 32 (word) bits of data can be transferred<br>per access. |

| Data Bus                             |             |        | I   | Driven by the slave in a read transaction. Eight (byte), 16 (halfword), or 32 (word) bits of data can be transferred per access.                                                                     |

| Transfer Cycle Terminat              | ion and Sta | atus   |     |                                                                                                                                                                                                      |

| TA<br>Transfer Acknowledge           | 1           | Low    | I   | Driven by the slave device to which the current transac-<br>tion was addressed. Indicates that the slave has received<br>the data on the write cycle or returned data on the read<br>cycle.          |

| TEA<br>Transfer Error<br>Acknowledge | 1           | Low    | I   | Driven by the slave device to which the current transac-<br>tion was addressed. Indicates that an error condition has<br>occurred during the bus cycle.                                              |

| ABORT<br>Abort                       | 1           | Low    | 0   | Driven by the M•CORE to indicate that the transfer is to be aborted immediately.                                                                                                                     |