# **KTFRDMPF1510EVMUG** FRDM-PF1510EVM evaluation board Rev. 1.0 — 18 June 2018

User guide

#### FRDM-PF1510EVM 1

aaa-030722

FRDM-PF1510EVM evaluation board

## 2 Important notice

NXP provides the enclosed product(s) under the following conditions:

This evaluation kit is intended for use of ENGINEERING DEVELOPMENT OR EVALUATION PURPOSES ONLY. It is provided as a sample IC pre-soldered to a printed circuit board to make it easier to access inputs, outputs, and supply terminals. This evaluation board may be used with any development system or other source of I/O signals by simply connecting it to the host MCU or computer board via off-the-shelf cables. This evaluation board is not a Reference Design and is not intended to represent a final design recommendation for any particular application. Final device in an application will be heavily dependent on proper printed circuit board layout and heat sinking design as well as attention to supply filtering, transient suppression, and I/O signal quality.

The goods provided may not be complete in terms of required design, marketing, and or manufacturing related protective considerations, including product safety measures typically found in the end product incorporating the goods. Due to the open construction of the product, it is the user's responsibility to take any and all appropriate precautions with regard to electrostatic discharge. In order to minimize risks associated with the customers applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards. For any safety concerns, contact NXP sales and technical support services.

Should this evaluation kit not meet the specifications indicated in the kit, it may be returned within 30 days from the date of delivery and will be replaced by a new kit.

NXP reserves the right to make changes without further notice to any products herein. NXP makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typical", must be validated for each customer application by customer's technical experts.

NXP does not convey any license under its patent rights nor the rights of others. NXP products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the NXP product could create a situation where personal injury or death may occur.

Should the buyer purchase or use NXP products for any such unintended or unauthorized application, the buyer shall indemnify and hold NXP and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges NXP was negligent regarding the design or manufacture of the part.

NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. © NXP B.V. 2018.

KTFRDMPF1510EVMUG

FRDM-PF1510EVM evaluation board

## 3 Overview of the PF1510 PMIC development environment

NXP offers a combination of boards that support the evaluation of the PF1510 power management integrated circuit (PMIC).

The FRDM-PF1510EVM boards serve as an evaluation platform that allows users to test and demo designs that incorporate the PF1510 PMIC. The evaluation board contains a preconfigured MC32PF1510A4EP device and provides numerous jumpers and test points that allow users to tailor the evaluation to their needs.

The kit comes with a FRDM-KL25Z already mounted and loaded with compatible microcode. The primary function of the FRDM-KL25Z is to control communication between the evaluation board and a PC.

## 4 Getting started

The NXP analog product development boards provide an easy-to-use platform for evaluating NXP products. These development boards support a range of analog, mixed-signal, and power solutions. These boards incorporate monolithic integrated circuits and system-in-package devices that use proven high-volume technology. NXP products offer longer battery life, a smaller form factor, reduced component counts, lower cost, and improved performance in powering state-of-the-art systems.

The tool summary page for FRDM-PF1510EVM is at <u>http://www.nxp.com/FRDM-PF1510EVM</u>. The overview tab on this page provides an overview of the device, a list of device features, a description of the kit contents, links to supported devices and a **Get Started** section.

The **Get Started** section provides information applicable to using the FRDM-PF1510EVM.

- 1. Go to <u>http://www.nxp.com/FRDM-PF1510EVM</u>.

- 2. On the **Overview** tab, locate the **Jump To** navigation feature on the left side of the window.

- 3. Select the Get Started link.

- 4. Review each entry in the Get Started section.

- 5. Download an entry by clicking the linked title.

After reviewing the **Overview** tab, visit the other related tabs for additional information:

- Documentation: Download current documentation.

- Software & Tools: Download current hardware and software tools.

- Buy/Parametrics: Purchase the product and view the product parametrics.

After downloading files, review each file, including the user guide, which includes setup instructions. If applicable, the bill of materials (BOM) and supporting schematics are also available for download in the **Get Started** section of the **Overview** tab.

## 4.1 Kit content/packing list

The FRDM-PF1510EVM content includes:

- Assembled and tested evaluation board in an anti-static bag

- · Cable, USB type A male/type mini B male 3 ft

- Quick start guide

FRDM-PF1510EVM evaluation board

## 4.2 Required equipment

This kit requires the following items:

- 5.0 V DC power supply or USB with enough current capability (3.0 A for maximum performance)

- KITPF1510GUI installed on a Windows PC

- Optional voltmeters to measure regulator outputs

- Optional oscilloscope

#### 4.3 System requirements

The kit requires the following to function properly with the software:

• USB-enabled computer running Windows XP, Vista 7, 8, or 10 (32 bit or 64 bit)

## 5 Getting to know the hardware

#### 5.1 Board overview

The FRDM-PF1510EVM board is an easy-to-use circuit board, allowing the user to exercise all the functions of the PF1510 PMIC.

The FRDM-KL25Z is mounted to the EVB as an integral component and serves as an interface between the KITPF1510GUI and the PF1510 PMIC. The FRDM-KL25Z drives circuitry on the FRDM-PF1510EVM and provides an analog-to-digital converter (ADC) to monitor PF1510 regulator voltages which are displayed in the GUI.

## 5.2 Board features

The board features the following:

- PF1510 PMIC

- Integrated FRDM-KL25Z as a communication link between the EVB and a PC

#### 5.3 Device features

The evaluation board features the following NXP product:

| Table 1. Device features |                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|--------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Device                   | Description                                                                                             | Features                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| PF1510                   | power management integrated circuit<br>(PMIC) for i.MX 7ULP, i.MX 6SL, 6UL,<br>6ULL, and 6SX processors | <ul> <li>Three adjustable high efficiency buck regulators with 1.0 A per regulator current capability</li> <li>Three adjustable general-purpose linear regulators</li> <li>Input voltage range on VIN: 4.1 V to 6.0 V</li> <li>Low dropout (LDO)/switch supply</li> <li>Double data rate (DDR) memory reference voltage</li> <li>One time programmable (OTP) memory for device configuration</li> </ul> |  |  |  |  |

```

KTFRDMPF1510EVMUG

```

FRDM-PF1510EVM evaluation board

#### 5.3.1 Device description

The PF1510 device populated on board features the A4 OTP; see Table 2.

| Table 2. Startup configuration |                                                        |

|--------------------------------|--------------------------------------------------------|

| Register                       | Pre-programmed OTP configuration –<br>A4 configuration |

| OTP_VSNVS_VOLT[2:0]            | 3.0 V                                                  |

| OTP_SW1_VOLT[5:0]              | 1.1 V                                                  |

| OTP_SW1_PWRUP_SEQ[2:0]         | 4                                                      |

| OTP_SW2_VOLT[5:0]              | 1.2 V                                                  |

| OTP_SW2_PWRUP_SEQ[2:0]         | 3                                                      |

| OTP_SW3_VOLT[5:0]              | 1.8 V                                                  |

| OTP_SW3_PWRUP_SEQ[2:0]         | 2                                                      |

| OTP_LDO1_VOLT[4:0]             | 3.3 V                                                  |

| OTP_LDO1_PWRUP_SEQ[2:0]        | 1                                                      |

| OTP_LDO2_VOLT[3:0]             | 3.3 V                                                  |

| OTP_LDO2_PWRUP_SEQ[2:0]        | 2                                                      |

| OTP_LDO3_VOLT[4:0]             | 1.8 V                                                  |

| OTP_LDO3_PWRUP_SEQ[2:0]        | 1                                                      |

| OTP_VREFDDR_PWRUP_SEQ[2:0]     | 3                                                      |

| OTP_SW1_DVS_ENB                | dynamic voltage scaling (DVS) mode                     |

| OTP_SW2_DVS_ENB                | DVS mode                                               |

| OTP_LDO1_LS_EN                 | LDO mode                                               |

| OTP_LDO3_LS_EN                 | LDO mode                                               |

| OTP_SW1_RDIS_ENB               | enabled                                                |

| OTP_SW2_RDIS_ENB               | enabled                                                |

| OTP_SW3_RDIS_ENB               | enabled                                                |

| OTP_SW1_DVSSPEED               | 12.5 mV step each 4.0 µs                               |

| OTP_SW2_DVSSPEED               | 12.5 mV step each 4.0 µs                               |

| OTP_SWx_EN_AND_STBY_EN         | SW1, SW2, SW3 enabled in RUN and STANDBY               |

| OTP_LDOx_EN_AND_STBY_EN        | LDO1, LDO2, LDO3, VREFDDR enabled in RUN and STANDBY   |

| OTP_PWRON_CFG                  | level sensitive                                        |

| OTP_SEQ_CLK_SPEED              | 2 ms time slots                                        |

| OTP_TGRESET[1:0]               | 4 s global reset timer                                 |

| OTP_POR_DLY[2:0]               | 2 ms RESETBMCU power up delay                          |

| OTP_UVDET[1:0]                 | rising 3.0 V; falling 2.9 V                            |

| OTP_I2C_DEGLITCH_EN            | I <sup>2</sup> C-bus deglitch filter disabled          |

| OTP_VSYSMIN[1:0]               | VSYSMIN = 4.3 V                                        |

## FRDM-PF1510EVM evaluation board

| Register          | Pre-programmed OTP configuration –<br>A4 configuration |

|-------------------|--------------------------------------------------------|

| OTP_VIN_ILIM[4:0] | VIN ILIM = 1500 mA                                     |

| OTP_USBPHYLDO     | USBPHY LDO enabled                                     |

| OTP_USBPHY        | USBPHY = 3.3 V                                         |

| OTP_ACTDISPHY     | USBPHY active discharge enabled                        |

## 5.4 Board description

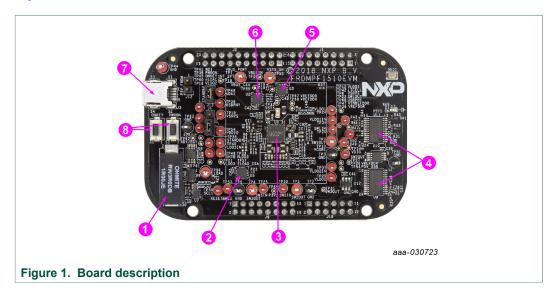

Figure 1 describes the main elements on the FRDM-PF1510EVM.

#### Table 3. Board description

| Number | Name                    | Description                                      |

|--------|-------------------------|--------------------------------------------------|

| 1      | 1A ELOAD                | electronic load 1.0 A                            |

| 2      | ELOAD CSA               | current sense amplifier for the electronic load  |

| 3      | PF1510                  | PF1510 PMIC                                      |

| 4      | analog MUX              | analog multiplexers                              |

| 5      | VSYS CSA                | current sense amplifier for VSYS                 |

| 6      | VIN CSA                 | current sense amplifier for VIN                  |

| 7      | VIN USB input           | USB 5.0 V power supply for the VIN               |

| 8      | ONKEY and PWRON buttons | buttons connected to the ONKEY and PWRON signals |

FRDM-PF1510EVM evaluation board

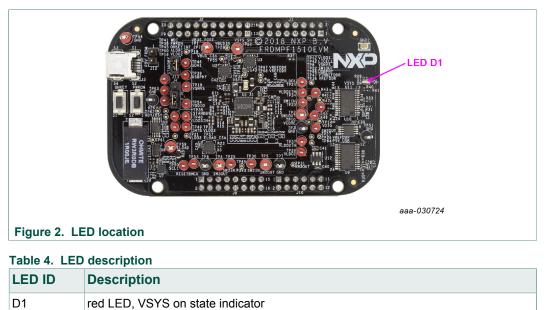

## 5.4.1 LED description

The following LED is provided as visual output device for the board:

#### FRDM-PF1510EVM evaluation board

# Image: space of the space of

#### 5.4.2 Jumper and switch definitions

Figure 3 shows the location of jumpers and switches on the evaluation board.

Table 5 describes the function and settings for each jumper and switch.

| Jumper/switch | Description          | Setting   | Connection/result                                                                             |

|---------------|----------------------|-----------|-----------------------------------------------------------------------------------------------|

| S1            | ONKEY                | open      | connects ONKEY pin to GND when<br>pressed; if configured properly, it causes<br>wake-up event |

| S2            | PWRON                | open      | connects PWRON pin to GND when pressed; resets the PMIC device                                |

| J3            | 5.0 V USB            | -         | power supply for the board (J12 shall be opened)                                              |

| J4            | pullup configuration | [1-2]     | pullup to VSNVS                                                                               |

|               |                      | [2-3]     | pullup to VDDIO which is supplied by<br>P3V3 coming from the FRDM-KL25Z<br>board              |

| J12           | 5 V power supply     | open      | 5.0 V from the J3 (USB) is used                                                               |

|               |                      | [1-2]     | 5.0 V is used from the FRDM-KL25Z board (current is limited)                                  |

| J13           | STANDBY pin          | open      | pull STANDBY pin high                                                                         |

|               | configuration        | connected | pull STANDBY pin low to GND                                                                   |

#### Table 5. Jumper and switch definitions

FRDM-PF1510EVM evaluation board

#### TP24 TP34 TP20 TP2 TP3 TP54 TP40 TP33 TP19 TP1 TP52 TP44 TP46 TP39 TP37 TP29 TP41 TP38 TP45 TP42 TP66 TP47 TP36 TP63 TP35 TP49 TP59 TP51 TP50 TP53 TP6 TP4 TP25 TP30 TP5 TP7 aaa-030726 Figure 4. Test point locations

## 5.4.3 Test point definitions

The following test points provide access to various signals to and from the board.

#### Table 6. Test point definitions

| Test point name | Signal name | Description                                |

|-----------------|-------------|--------------------------------------------|

| TP1             | VIN_PORT    | 5.0 V power supply (from USB connector J3) |

| TP2             | SW1OUT      | SW1 output                                 |

| TP3             | GND         | ground (next to SW1OUT)                    |

| TP4             | SW3OUT      | SW3 output                                 |

| TP5             | SW2OUT      | SW2 output                                 |

| TP6             | GND         | ground (next to SW3OUT)                    |

| TP7             | GND         | ground (next to SW2OUT)                    |

| TP19            | VSNVS       | VSNVS regulator output                     |

| TP20            | SW1IN       | SW1 input                                  |

| TP24            | VLDO1       | VLDO1 regulator output                     |

| TP25            | SW3IN       | SW3 input                                  |

| TP29            | VLDO2       | VLDO2 regulator output                     |

| TP30            | SW2IN       | SW2 input                                  |

| TP33            | VLDO3       | VLDO3 regulator output                     |

| TP34            | VLDO1IN     | VLDO1 regulator input                      |

| TP35            | STANDBY     | STANDBY input                              |

| TP36            | VREFDDR     | VREFDDR regulator output                   |

| TP37            | VLDO2IN     | VLDO2 regulator input                      |

| TP38            | PWRON       | PWRON input                                |

| TP39            | USBPHY      | USBPHY regulator output                    |

#### FRDM-PF1510EVM evaluation board

| Test point name | Signal name | Description                                             |

|-----------------|-------------|---------------------------------------------------------|

| TP40            | VLDO3IN     | VLDO3 regulator input                                   |

| TP41            | WDI         | watchdog input from microcontroller unit (MCU)          |

| TP42            | LICELL      | coin cell input                                         |

| TP44            | GND         | ground                                                  |

| TP45            | ONKEY       | ONKEY push-button input                                 |

| TP46            | SDA1        | data signal of the I <sup>2</sup> C-bus                 |

| TP47            | VINREFDDR   | VREFDDR regulator input                                 |

| TP49            | INTB        | interrupt to the MCU                                    |

| TP50            | SCL1        | clock signal of the I <sup>2</sup> C-bus                |

| TP51            | GND         | ground                                                  |

| TP52            | VSYS_SH     | VSYS of PMIC                                            |

| TP53            | RESETBMCU   | MCU reset signal                                        |

| TP54            | VDDIO       | I/O supply voltage of the PMIC                          |

| TP59            | ELOAD       | electronic load input (connect the tested power supply) |

| TP63            | GND         | ground (next to the electronic load)                    |

| TP66            | USBPHY      | USBPHY regulator output                                 |

## 6 FRDM-KL25Z Freedom development platform

The NXP Freedom development platform is a set of software and hardware tools for evaluation and development. It is ideal for rapid prototyping of microcontroller-based applications. The NXP Freedom KL25Z hardware, FRDM-KL25Z, is a simple, yet sophisticated design featuring a Kinetis L series microcontroller, the first microcontroller of the industry built on the Arm Cortex-M0+ core.

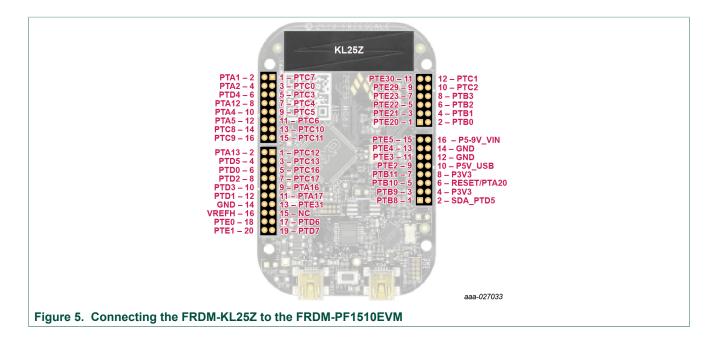

## 6.1 Connecting the FRDM-KL25Z to the board

The FRDM-KL25Z evaluation board was chosen specifically to work with the FRDM-PF1510EVM kit because of its low cost and features. The FRDM-KL25Z board uses the USB, built-in LEDs, and I/O ports available with NXPs Kinetis KL2x family of microcontrollers.

The FRDM-PF1510EVM connects to the FRDM-KL25Z using the four dual row Arduino R3 connectors on the bottom of the board.

KTFRDMPF1510EVMUG

## **NXP Semiconductors**

# **KTFRDMPF1510EVMUG**

#### FRDM-PF1510EVM evaluation board

#### Table 7. FRDM-PF1510EVM to FRDM-KL25Z connections

| FRDM-PF1510EVM FRDM-KL |     | L25Z   | Pin hardware name | Description    |            |                                                               |

|------------------------|-----|--------|-------------------|----------------|------------|---------------------------------------------------------------|

| Header                 | Pin | Header | Pin               | FRDM-PF1510EVM | FRDM-KL25Z | -                                                             |

| J1                     | 1   | J1     | 1                 | n.c.           | PTC7       | not connected                                                 |

| J1                     | 2   | J1     | 2                 | INTB           | PTA1       | interrupt to the MCU                                          |

| J1                     | 3   | J1     | 3                 | n.c.           | PTC0       | not connected                                                 |

| J1                     | 4   | J1     | 4                 | WDI            | PTA2       | watchdog input from MCU                                       |

| J1                     | 5   | J1     | 5                 | n.c.           | PTC3       | not connected                                                 |

| J1                     | 6   | J1     | 6                 | nLDAC          | PTD4       | DAC configuration signal                                      |

| J1                     | 7   | J1     | 7                 | n.c.           | PTC4       | not connected                                                 |

| J1                     | 8   | J1     | 8                 | RDY/BSY        | PTA12      | DAC control signal                                            |

| J1                     | 9   | J1     | 9                 | n.c.           | PTC5       | not connected                                                 |

| J1                     | 10  | J1     | 10                | MUX_RESETB     | PTA4       | multiplexer reset                                             |

| J1                     | 11  | J1     | 11                | n.c.           | PTC6       | not connected                                                 |

| J1                     | 12  | J1     | 12                | VDDIO          | PTA5       | VDDIO power supply                                            |

| J1                     | 13  | J1     | 13                | n.c.           | PTC10      | not connected                                                 |

| J1                     | 14  | J1     | 14                | SCL2           | PTC8       | clock signal of the I <sup>2</sup> C-bus (for additional ICs) |

| J1                     | 15  | J1     | 15                | n.c.           | PTC11      | not connected                                                 |

| J1                     | 16  | J1     | 16                | SDA2           | PTC9       | data signal of the I <sup>2</sup> C-bus (for additional ICs)  |

| J2                     | 1   | J2     | 1                 | n.c.           | PTC12      | not connected                                                 |

| J2                     | 2   | J2     | 2                 | PWRON          | PTA13      | PWRON input                                                   |

KTFRDMPF1510EVMUG

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2018. All rights reserved.

## **NXP Semiconductors**

# **KTFRDMPF1510EVMUG**

## FRDM-PF1510EVM evaluation board

| FRDM-PF1510EVM |                       | FRDM-KL25Z |                | Pin hardware name |          | Description                                          |

|----------------|-----------------------|------------|----------------|-------------------|----------|------------------------------------------------------|

| Header         | Header Pin Header Pin |            | FRDM-PF1510EVM | FRDM-KL25Z        |          |                                                      |

| J2             | 3                     | J2         | 3              | n.c.              | PTC13    | not connected                                        |

| J2             | 4                     | J2         | 4              | STANDBY           | PTD5     | STANDBY input                                        |

| J2             | 5                     | J2         | 5              | n.c.              | PTC16    | not connected                                        |

| J2             | 6                     | J2         | 6              | RESETBMCU         | PTD0     | MCU reset signal                                     |

| J2             | 7                     | J2         | 7              | n.c.              | PTC17    | not connected                                        |

| J2             | 8                     | J2         | 8              | VSYS_CSA_ALERT    | PTD2     | alert signal from the VSYS current shunt             |

| J2             | 9                     | J2         | 9              | ELOAD_CSA_ALERT   | PTA16    | alert signal from the ELOAD current shunt            |

| J2             | 10                    | J2         | 10             | n.c.              | PTD3     | not connected                                        |

| J2             | 11                    | J2         | 11             | n.c.              | PTA17    | not connected                                        |

| J2             | 12                    | J2         | 12             | VBUS_CSA_ALERT    | PTD1     | alert signal from the VBUS current shunt             |

| J2             | 13                    | J2         | 13             | n.c.              | PTE31    | not connected                                        |

| J2             | 14                    | J2         | 14             | GND               | GND      | ground                                               |

| J2             | 15                    | J2         | 15             | n.c.              | n.c.     | not connected                                        |

| J2             | 16                    | J2         | 16             | n.c.              | VREFH    | not connected                                        |

| J2             | 17                    | J2         | 17             | n.c.              | PTD6     | not connected                                        |

| J2             | 18                    | J2         | 18             | SDA1              | PTE0     | data signal of the I <sup>2</sup> C-bus<br>(PF1510)  |

| J2             | 19                    | J2         | 19             | n.c.              | PTD7     | open                                                 |

| J2             | 20                    | J2         | 20             | SCL1              | PTE1     | clock signal of the I <sup>2</sup> C-bus<br>(PF1510) |

| J10            | 1                     | J10        | 1              | n.c.              | PTE20    | not connected                                        |

| J10            | 2                     | J10        | 2              | n.c.              | PTB0     | not connected                                        |

| J10            | 3                     | J10        | 3              | n.c.              | PTE21    | not connected                                        |

| J10            | 4                     | J10        | 4              | n.c.              | PTB1     | not connected                                        |

| J10            | 5                     | J10        | 5              | n.c.              | PTE22    | not connected                                        |

| J10            | 6                     | J10        | 6              | 2V5_ADC           | PTB2     | voltage reference for ADC                            |

| J10            | 7                     | J10        | 7              | n.c.              | PTE23    | not connected                                        |

| J10            | 8                     | J10        | 8              | ADC_1             | PTB3     | analog signal to ADC1                                |

| J10            | 9                     | J10        | 9              | n.c.              | PTE29    | not connected                                        |

| J10            | 10                    | J10        | 10             | ADC_0             | PTC2     | analog signal to ADC0                                |

| J10            | 11                    | J10        | 11             | n.c.              | PTE30    | not connected                                        |

| J10            | 12                    | J10        | 12             | n.c.              | PTC1     | not connected                                        |

| 19             | 1                     | J9         | 1              | n.c.              | PTB8     | not connected                                        |

| J9             | 2                     | J9         | 2              | P3V3              | SDA_PTD5 | 3.3 V coming from the<br>Freedom board               |

## FRDM-PF1510EVM evaluation board

| FRDM-PF1510EVM |     | FRDM-KL25Z |     | Pin hardware name |             | Description                            |

|----------------|-----|------------|-----|-------------------|-------------|----------------------------------------|

| Header         | Pin | Header     | Pin | FRDM-PF1510EVM    | FRDM-KL25Z  | -                                      |

| J9             | 3   | J9         | 3   | n.c.              | PTB9        | not connected                          |

| J9             | 4   | <b>J</b> ð | 4   | P3V3              | 3V3         | 3.3 V coming from the<br>Freedom board |

| J9             | 5   | J9         | 5   | n.c.              | PTB10       | not connected                          |

| J9             | 6   | <b>J</b> ð | 6   | P3V3              | RESET/PTA20 | 3.3 V coming from the<br>Freedom board |

| J9             | 7   | J9         | 7   | n.c.              | PTB11       | not connected                          |

| J9             | 8   | J9         | 8   | P3V3              | 3V3         | 3.3 V coming from the<br>Freedom board |

| J9             | 9   | J9         | 9   | n.c.              | PTE2        | not connected                          |

| J9             | 10  | <b>J</b> ð | 10  | P5V_USB           | 5V          | 5 V coming from the Freedom board      |

| J9             | 11  | J9         | 11  | n.c.              | PTE3        | not connected                          |

| J9             | 12  | J9         | 12  | GND               | GND         | ground                                 |

| J9             | 13  | J9         | 13  | n.c.              | PTE4        | not connected                          |

| J9             | 14  | J9         | 14  | GND               | GND         | ground                                 |

| J9             | 15  | J9         | 15  | n.c.              | PTE5        | not connected                          |

| J9             | 16  | J9         | 16  | n.c.              | P5-9V_VIN   | not connected                          |

## 7 Installing the software and setting up the hardware

## 7.1 Set up PF1510GUI on your computer

- 1. Download **PF1510GUI.zip** from <u>http://www.nxp.com/FRDM-PF1550EVM</u>. Choose the 32-bit or 64-bit version regarding the system installed on your PC.

- 2. Extract all the files to any desired folder on your PC.

- 3. Plug the evaluation board.

- 4. Launch the GUI (no installation is necessary, GUI can be directly launched by clicking the file **PF1510\_x\_Bx.jar**).

FRDM-PF1510EVM evaluation board

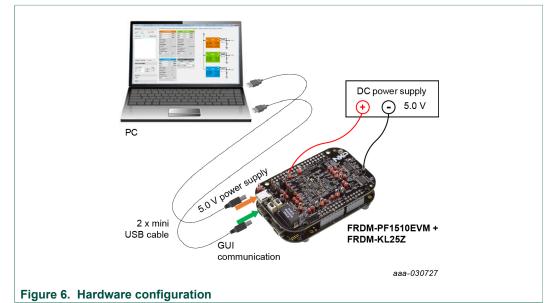

# 7.2 Configuring the hardware and using the GUI for control and monitoring

## 1. Apply input voltage to the board.

- First solution is to use power directly from the FRDM-KL25Z by connecting J12 jumper. Advantage of this configuration is that only one USB port (USB for GUI communication) is needed. This solution may have limited performance because of the current capability of the USB port.

- Second possibility is to use 5.0 V either from USB input (J3) or from DC power supply. In these cases, keep J12 open. The DC power supply connection is recommended for higher currents.

- 2. Connect the mini-USB cable from a PC to the KL25Z USB port on the FRDM-KL25Z board.

- 3. Windows automatically installs the necessary drivers. Wait for this operation to complete.

- 4. Launch the PF1510 GUI.

- 5. In the PF1510 GUI window, click the **Scan For Devices** button in the top-left corner. A confirmation message that a valid device is available is logged.

FRDM-PF1510EVM evaluation board

| USB Connection   |              |              |       |   |

|------------------|--------------|--------------|-------|---|

| Vendor ID: 0x1   | 5A2          | Device: Pl   | F1510 |   |

| Part ID: 0x0     | 000          |              |       |   |

| Target Enabled:  | $\checkmark$ | Scan For Dev | rices |   |

| Device connected |              |              |       | ^ |

|                  |              |              |       |   |

|                  |              |              |       |   |

|                  |              |              |       |   |

|                  |              |              |       |   |

|                  |              |              |       |   |

|                  |              |              |       |   |

|                  |              |              |       |   |

|                  |              |              |       |   |

|                  |              |              |       |   |

|                  |              |              |       |   |

|                  |              |              |       |   |

|                  |              |              |       |   |

|                  |              |              |       |   |

|                  |              |              |       |   |

|                  |              |              |       |   |

|                  |              |              |       |   |

|                  |              |              |       | ~ |

| Save Log C       | lear Log     | I2C Address: | 0x08  | ~ |

|                  |              | aaa-0        | 3072  | 8 |

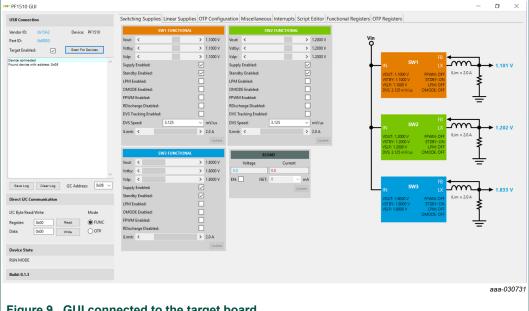

- 6. Enable the communication by clicking the **Target Enabled:** checkbox. The window turns from gray to color.

- 7. The GUI installation and hardware setup now are complete.

FRDM-PF1510EVM evaluation board

## 7.3 Understanding and using the GUI

#### 7.3.1 GUI structure for PF1510

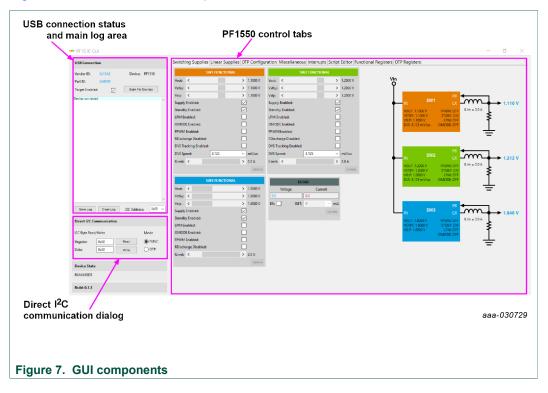

Figure 7 shows the different components of the GUI.

#### 7.3.2 GUI panels

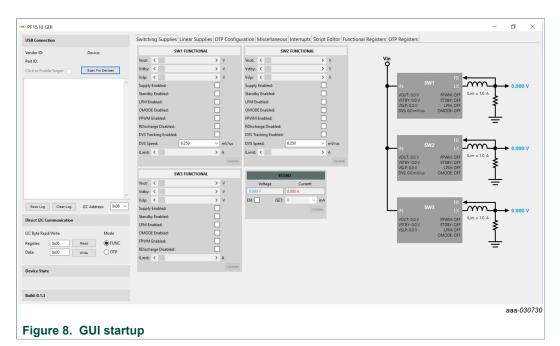

When the GUI is launched, it looks for a PF1510 target board connected via the USB cable. If connected, the USB connection panel displays the vendor ID: 0x15A2, and part ID: 0x00D0.

The main log window displays messages, example, when the board is connected (PF1510 attached) and when the board was removed (PF1510 removed).

FRDM-PF1510EVM evaluation board

Pressing the Scan For Devices button attempts to read from each of the eight permissible I<sup>2</sup>C-bus device addresses. The results are displayed in the main log window. If multiple PMIC devices are detected, the GUI can be configured to communicate with a particular device by selecting the corresponding device address.

Note: The GUI can communicate with only one PMIC device at a time.

FRDM-PF1510EVM evaluation board

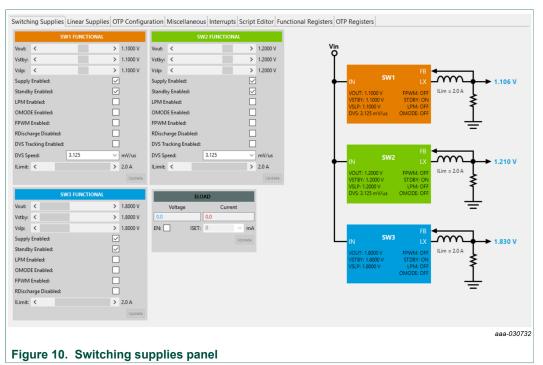

#### 7.3.3 Switching supplies panel

The switching supplies panel allows users to adjust the functional parameters of each supply.

To change supply parameters, click and adjust the desired control. An **Update** button appears whenever a change is made, and pressing the **Update** button writes the change to the PMIC.

*Note:* Multiple changes can be made at a time, and all changes are written when the *Update* button is pressed.

FRDM-PF1510EVM evaluation board

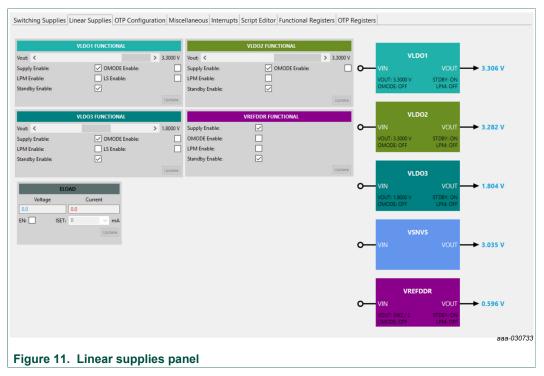

#### 7.3.4 Linear supplies panel

The linear supplies panel allows users to adjust the functional parameters of each linear regulator. To change supply parameters, click and adjust the desired control.

An **Update** button appears whenever a change is made, and pressing the **Update** button writes the change to the PMIC.

**Note:** Multiple changes can be made at a time, and all changes are written when the **Update** button is pressed.

FRDM-PF1510EVM evaluation board

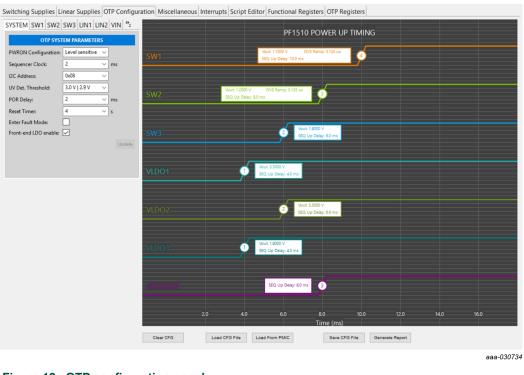

#### 7.3.5 OTP configuration panel

The OTP configuration panel allows access and editing of the PF1510 startup parameters.

#### Figure 12. OTP configuration panel

Initially, the panel display is the OTP configuration read from PMIC PF1510.

The **Load CFG File** button opens the configuration file open dialog, and populates the panel with the parameters contained in this file.

The **Load From PMIC** button loads the OTP configuration data from the PMIC PF1510 of the evaluation board.

FRDM-PF1510EVM evaluation board

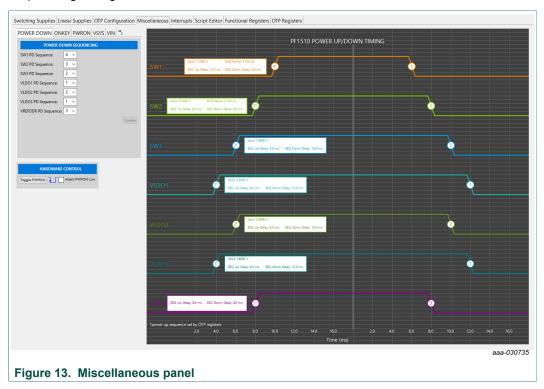

#### 7.3.6 Miscellaneous panel

The miscellaneous panel contains general-purpose commands and power up and down sequencing configuration.

FRDM-PF1510EVM evaluation board

#### 7.3.7 Interrupts panel

The interrupts panel displays the state of all PF1510 interrupts.

| Switching Supplies Linear Supplies OTP Configu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ration Miscellaneous Interrupts Script Editor                                                                                               | unctional Registers OTP Registers                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SW1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ONKEY                                                                                                                                       | MISCELLANEOUS                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| STATUS MASK SENSE<br>SW1 - LS Current Limit<br>SW1 - HS Current Limit<br>SW1 - DVS Complete<br>Clear All Mask All Unmask All<br>SW2 - LS Current Limit<br>SW2 - LS Current Limit<br>SW2 - HS Current Limit<br>SW2 - DVS Complete<br>Clear All Mask All Unmask All Unmask All<br>SW2 - DVS Complete<br>Clear All Mask All Unmask All Unmask All<br>SW2 - DVS Complete<br>Clear All Mask All Unmask All Unmask All<br>SW2 - DVS Complete<br>Clear All Mask All Unmask All<br>SW2 - DVS Complete<br>Clear All Mask All Unmask All<br>SW2 - DVS Complete<br>Clear All Mask All Unmask All<br>SW2 - DVS Complete<br>SW2 - DVS COMPLES<br>SW3 - DVS COMPLES | ONKEY Pressed > 4 sec<br>ONKEY Pressed > 8 sec<br>Clear All<br>Mask All Unmask All                                                          | STATUS     MASK     SENSE       Power UP     Image: Constraint of the sense     Image: Constraint of the sense       Power On     Image: Constraint of the sense     Image: Constraint of the sense       VSYS Overvoltage     Image: Constraint of the sense     Image: Constraint of the sense       VIN     Image: Constraint of the sense     Image: Constraint of the sense       Clear All     Image: Constraint of the sense     Image: Constraint of the sense |

| STATUS MASK SENSE<br>SW3 - LS Current Limit SW3 - HS Current Limit SW3 - HS Current Limit Comment<br>Clear All Mask All Ounmask All                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | LDOs<br>STATUS MASK SENSE<br>VLD01 - Current Limit V<br>VLD02 - Current Limit V<br>VLD03 - Current Limit V<br>Clear All Mask All Unmask All | STATUS - Reports the latched state of the<br>interrunt. Uncheck to CI FAR interrunt.<br>MASK - Controls the assertion of the<br>INTB pin. When Unchecked, INTB will be<br>asserted by interrupt.<br>SENSE - Is the real-time state of the<br>interrupt. READ ONLY.                                                                                                                                                                                                     |

| TEMPERATURE         STATUS       MASK       SENSE         Die Temperature > 110 °C       Image: Colspan="2">Image: Colspan="2">Image: Colspan="2">Image: Colspan="2">Image: Colspan="2">Image: Colspan="2">Image: Colspan="2">Image: Colspan="2"         Die Temperature > 125 °C       Image: Colspan="2">Image: Colspan="2"         Clear All       Mask All       Unmask All         Poll Interrupts       Image: Colspan="2">Image: Colspan="2"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                             | INTB = HIGH                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                             | aaa-0307                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

#### Figure 14. Interrupts panel

The **Interrupts** tab displays status, mask, and sense registers for INT0, INT1, INT3, and INT4. Selecting the **Poll Interrupts** checkbox enables update of this information with period of 500 ms. To activate interrupt, the appropriate mask has to be set. When an interrupt occurs, the appropriate checkbox is selected. Interrupt can be then cleared by unchecking this checkbox.

The state of the PF1510 INTB pin is displayed, and updated asynchronously. Interrupts that are unmasked, cause the INTB pin to go LOW while the interrupt condition exists.

The PF1510 target hardware detects when the INTB pin goes LOW, and sends a message to the GUI to indicate that an interrupt has occurred. The INTB label on the panel is LOW until the interrupt condition is cleared.

KTFRDMPF1510EVMUG

FRDM-PF1510EVM evaluation board

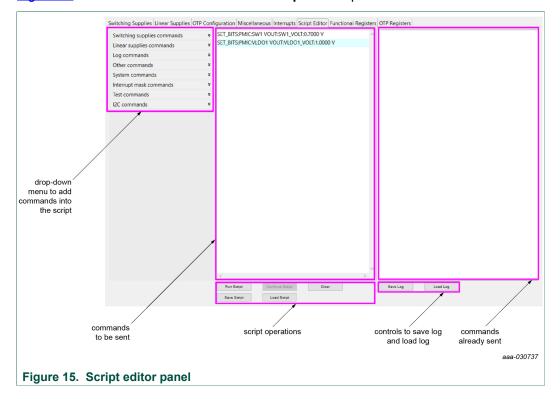

#### 7.3.8 Script editor panel

The script editor panel allows the user to write and execute scripts that exercise various functions on the PF1510 PMIC. These functions include setting voltages on the regulators, reading and writing I<sup>2</sup>C-bus addresses, and clearing interrupts. Script commands can be written directly in an editor window. Alternatively, the user can build the scripts by selecting commands from drop-down menus and entering the appropriate values.

The scripts are executed within the **Files:** section of the panel, and the results are displayed in the **Script Log** section.

Completed scripts can be saved as text files for later use. Commands can be generated easily.

Figure 15 shows the main elements in the Script Editor panel.

FRDM-PF1510EVM evaluation board

#### 7.3.9 Functional registers panel

In the functional registers panel, clicking a checkbox immediately sets or clears the corresponding register bit. Key bit fields in each register are decoded to help displaying the actual state of each parameter.

Registers are grouped within each tab by function.

| Switching | Supplies L | inear Supp | lies OTP C | onfiguratio | on Miscella | aneous Inte | errupts Sci | ript Editor | Function | al Registers OTP Registers                                                                                           |            |

|-----------|------------|------------|------------|-------------|-------------|-------------|-------------|-------------|----------|----------------------------------------------------------------------------------------------------------------------|------------|

| MISC 1    | MISC 2     | MISC 3     | INT 1      | INT 2       | NT 3 IN     | T4 SW1      | SW2         | SW3 L       | N RE     | G PD SEQ                                                                                                             |            |

| ADDRESS   |            |            |            | DEV         | ICE ID      |             |             |             |          | Device ID: PF1510<br>Family: PF1510                                                                                  | Â          |

| 0x00      | B7         | ✓ В6       | ✓ B5       | 🗸 В4        | ✓ ВЗ        | 🗸 В2        | B1          | B0          | 0x7C     |                                                                                                                      |            |

| PAGE 0    | FAM4       | FAM3       | FAM2       | FAM1        | FAM0        | DEVID2      | DEVID1      | DEVID0      |          |                                                                                                                      |            |

| ADDRESS   |            |            |            | OTP F       | LAVOR       |             |             |             |          | OTP flavor: Not burned                                                                                               |            |

| 0x01      | B7         | B6         | B5         | B4          | B3          | B2          | B1          | B0          | 0x00     |                                                                                                                      |            |

| PAGE 0    | OTPFLAV7   | OTPFLAV8   | OTPFLAV5   | OTPFLAV4    | OTPFLAV3    | OTPFLAV2    | OTPFLAV1    | OTPFLAV0    |          |                                                                                                                      |            |

| ADDRESS   |            |            |            | SILICON     | REVISION    |             |             |             |          |                                                                                                                      |            |

| 0x02      | B7         | Bô         | B5         | 🗸 В4        | B3          | B2          | B1          | ✓ B0        | 0x11     |                                                                                                                      |            |

| PAGE 0    | FABFIN1    | FABFIN0    | MLREV2     | MLREV1      | MLREV0      | METLR2      | METLR1      | METLR0      |          |                                                                                                                      |            |

| ADDRESS   |            |            |            | COINCELL    | CONTROL     |             |             |             |          | Coin cell charging vol. 1.8 V<br>Coin cell charger disabled                                                          |            |

| 0x30      | B7         | 86         | B5         | B4          | <b>B</b> 3  | B2          | □ B1        | <b>B</b> 0  | 0x00     |                                                                                                                      |            |

| PAGE 0    |            |            |            | CHEN        | VCOIN3      | VCOIN2      | VCOIN1      | VCOIN0      |          |                                                                                                                      |            |

| ADDRESS   |            |            |            | POWER C     | ONTROL 0    |             |             |             |          | Standby pin delay = 31.25 s<br>Standby pin polarity = high<br>RESETBMCU pin delay = 2 s                              |            |

| 0x58      | <b>B</b> 7 | B6         | B5         | B4          | B3          | B2          | B1          | ✓ B0        | 0x01     | ONKEY low duration = 4 s                                                                                             |            |

| PAGE 0    | TGRST1     | TGRSTO     | PORDLY2    | PORDLY1     | PORDLY0     | STBINV      | STBDLY1     | STBDLY0     |          |                                                                                                                      |            |

| ADDRESS   |            |            |            | POWER C     | ONTROL 1    |             |             |             |          | PWRON debounce = 31.25   31.25 ms<br>ONKEY debounce = 31.25   31.25 ms<br>REGS_DISABLE/Sleep on PWRON low = disabled |            |

| 0x59      | ✓ в7       | <b>B</b> 6 | B5         | B4          | B3          | B2          | B1          | <b>B</b> 0  | 0x80     | System restart on PWRON low = disabled<br>LDO shut down = disabled<br>Turn off via ONKEY = enabled                   |            |

|           |            |            |            |             |             |             |             |             |          |                                                                                                                      | ~          |

|           |            |            |            |             |             |             |             |             |          |                                                                                                                      | aaa-030738 |

| Figure    | 16. F      | unctio     | nal reg    | jisters     | panel       |             |             |             |          |                                                                                                                      |            |

FRDM-PF1510EVM evaluation board

#### Switching Supplies Linear Supplies OTP Configuration Miscellaneous Interrupts Script Editor Functional Registers OTP Registers MISC2 SUP REG PU SEQ MISC1 Power On Configuration = level sensitive SEQ CLK SPEED = 2 ms Enter fault mode = disabled OTP PMIC CONFIGURATION 0 B1 B4 B3 0x04 B B5 🗸 В2 BO PWRGDEN CLK PWRON Reset delay on ONKEY press = 4 s POR delay = 2 s OTP PMIC CONFIGURATION 1 tection threshold = 3.0 V I 2.9 V IV de B4 B7 🗸 ве B5 B3 B2 B1 В0 0x40 UVDET1 UVDETO PORDLY2 PORDLY1 PORDLY0 TGRST1 TGRSTO VREFDDR power up sequence = 3 I2C deglitch = disabled OTP PMIC CONFIGURATION 2 I2C address = 0x08 Ship core off = disabled B7 B6 B5 B4 B3 B2 ✓ B1 🖌 во 0x03 COREOFF I2CA2 I2CA1 I2CA0 I2CDEGL VREFUP2 VREFUP1 VREFUP0 Front end operation = ON OTP CONFIGURATION 0 0x01 B7 B6 B5 B4 B3 B2 B1 🖌 ВО FEOPER1 FEOPER0 Minimum VSYS = 4.30 V OTP CONFIGURATION 2 🖂 В4 0x90 🗸 в7 B3 BO B6 B5 B2 B1 VSYS1 aaa-030739

#### 7.3.10 OTP registers panel

The OTP registers panel provides bit-level access to each register.

#### Figure 17. OTP registers panel

Clicking a checkbox immediately sets or clears the corresponding register bit. Key bit fields in each register are decoded to help displaying the actual state of each parameter.

Registers are grouped within each tab by function.

While in edit configuration (TBB mode), the OTP data import, export, and compare buttons are visible. The buttons function the same as the buttons on the OTP configuration panel.

FRDM-PF1510EVM evaluation board

## 8 Schematics, board layout and bill of materials

Schematics, board layout and bill of materials are available on the tool summary page: <u>http://www.nxp.com/FRDM-PF1510EVM</u>.

## 9 References

Following are URLs where you can obtain information on related NXP products and application solutions:

| Support page   | Description                  | URL                               |

|----------------|------------------------------|-----------------------------------|

| FRDM-PF1510EVM | tool summary page            | http://www.nxp.com/FRDM-PF1510EVM |

| PF1510         | product summary page         | http://www.nxp.com/PF1510         |

| FRDM-KL25Z     | Freedom development platform | http://www.nxp.com/FRDM-KL25Z     |

## **10 Revision history**

| Revision histo | ory      |                 |

|----------------|----------|-----------------|

| Rev            | Date     | Description     |

| v.1.0          | 20180618 | initial version |

#### FRDM-PF1510EVM evaluation board

## **11 Legal information**

## **11.1 Definitions**

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

## 11.2 Disclaimers

Limited warranty and liability - Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors. In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXF Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Applications — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products. NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by

customer's third party customer(s). NXP does not accept any liability in this respect.

Suitability for use in automotive applications — This NXP Semiconductors product has been qualified for use in automotive applications. Unless otherwise agreed in writing, the product is not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Evaluation products — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer. In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages. Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

## 11.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

**I<sup>2</sup>C-bus** — logo is a trademark of NXP B.V. **Kinetis** — is a trademark of NXP B.V.

FRDM-PF1510EVM evaluation board

## Tables

| Tab. 1. | Device features        | Та |

|---------|------------------------|----|

| Tab. 2. | Startup configuration5 | Та |

| Tab. 3. | Board description      | Та |

| Tab. 4. | LED description7       |    |

| ab. 5. | Jumper and switch de   | finitio | ns | 8  |

|--------|------------------------|---------|----|----|

|        | Test point definitions |         |    |    |

|        | FRDM-PF1510EVM         |         |    |    |

|        | connections            |         |    | 11 |

## **Figures**

| Fig. 1. | Board description                      | 6  |

|---------|----------------------------------------|----|

| Fig. 2. | LED location                           | 7  |

| Fig. 3. | Jumper and switch locations            | 8  |

| Fig. 4. | Test point locations                   | 9  |

| Fig. 5. | Connecting the FRDM-KL25Z to the FRDM- |    |

|         | PF1510EVM                              | 11 |

| Fig. 6. | Hardware configuration                 | 14 |

| Fig. 7. | GUI components                         | 16 |

| Fig. 8. | GUI startup                            | 17 |

| Fig. 9.  | GUI connected to the target board | 17 |

|----------|-----------------------------------|----|

| Fig. 10. | Switching supplies panel          |    |

| Fig. 11. | Linear supplies panel             |    |

| Fig. 12. | OTP configuration panel           | 20 |

| Fig. 13. | Miscellaneous panel               | 21 |

| Fig. 14. | Interrupts panel                  | 22 |

| Fig. 15. | Script editor panel               | 23 |

| Fig. 16. | Functional registers panel        | 24 |

| Fig. 17. | OTP registers panel               | 25 |

FRDM-PF1510EVM evaluation board

## Contents

| <b>^</b>                                                                                                          | FRDM-PF1510EVM                                                                                                                                                                                                                                                                                                                        |                                                                             |

|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| 2                                                                                                                 | Important notice                                                                                                                                                                                                                                                                                                                      | 2                                                                           |

| 3                                                                                                                 | Overview of the PF1510 PMIC development                                                                                                                                                                                                                                                                                               | _                                                                           |