# **Reset Timer IC for Mobile Equipments**

NO.EA-280-230523

# OUTLINE

The R3200x is a reset timer IC with two input signals for mobile equipment which require long interval for reset sequence. The long interval prevents unexpected resets caused by accidental key operations. Internally, the R3200x consists of a delay generator circuit and output driver transistors.

The R3200x has two active-low input pins ( $\overline{SR0}$  and  $\overline{SR1}$ ) which generate reset signals after output delay time when both active-low input pins are activated at the same time.

The R3200x has two versions that are different in output delay time settings and output release method.

### R3200x001x:

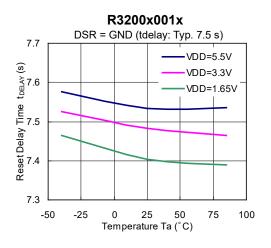

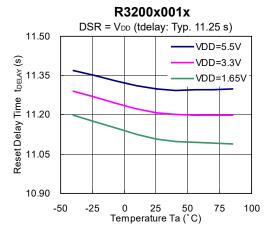

Output delay time is selectable from 7.5 s or 11.25 s typ. by connecting the DSR pin to either GND or  $V_{DD}$ . A reset signal can be released by making one of the active-low input pins high.

R3200xxx2x, R3200L053B or R3200L064A:

Output delay time is fixed. A reset signal will be released automatically after output release time. Or, by making one of the active-low input pins high, a reset signal can be released before output release time.

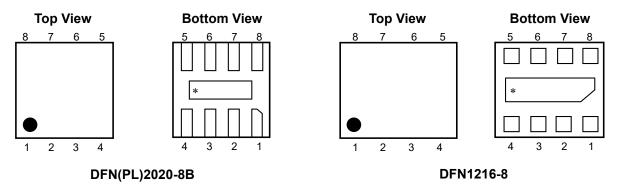

The R3200x provides ultra-low supply current while a reset signal is remaining active or after being sent out. The R3200x is offered in a 8-pin DFN(PL)2020-8B package or a 8-pin DFN1216-8 package.

# FEATURES

| • | Operating Voltage Range (Maximum Rating)                | 1.65 V to 5.5 V (6 V)                             |

|---|---------------------------------------------------------|---------------------------------------------------|

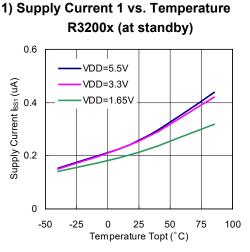

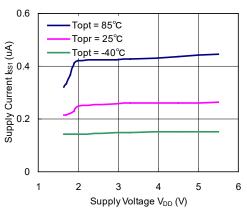

| • | Supply Current 1 (at standby)                           | Typ. 0.28 μA (V <sub>DD</sub> = 5.5 V)            |

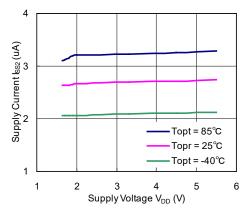

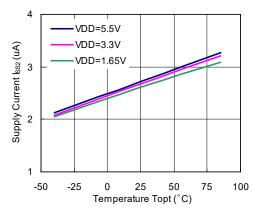

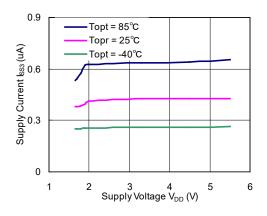

| • | Supply Current 2 (at active before reset signal output) | Typ. 3 μA (V <sub>DD</sub> = 5.5 V) <sup>*1</sup> |

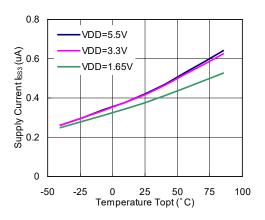

| ٠ | Supply Current 3 (at active after reset signal output)  | Typ. 0.45 μA (V <sub>DD</sub> = 5.5 V)            |

| • | Operating Temperature Range                             | −40 to +85°C                                      |

| • | Output Delay Time (R3200x001x)                          | Typ. 7.5 s or 11.25 s                             |

|   | (R3200x002x)                                            | Typ. 7.5 s                                        |

|   | (R3200L052B)                                            | Typ. 10 s                                         |

|   | (R3200L053B)                                            | Typ. 10 s                                         |

|   | (R3200L064A)                                            | Typ. 3.0 s                                        |

| • | Output Delay Time Accuracy                              | ±10%                                              |

| • | Output Release Time (R3200x002x)                        | Typ. 0.234 s                                      |

|   | (R3200L052B)                                            | Typ. 0.313 s                                      |

|   | (R3200L053B)                                            | Typ. 0.078 s                                      |

|   | (R3200L064A)                                            | Typ. 0.1875 s                                     |

| • | Output Release Time Accuracy                            | ±10%                                              |

| • | Output Type (R3200xxxxA)                                | Nch Open Drain                                    |

|   | (R3200xxxxB)                                            | Nch Open Drain and CMOS                           |

| • | Packages                                                | DFN(PL)2020-8B, DFN1216-8                         |

|   |                                                         |                                                   |

\*1 Guaranteed by design engineering

# **APPLICATIONS**

- Mobile phone, Smartphone

- Tablet devices such as E-book etc.

- Portable Games

- Personal Navigation Devices

NO.EA-280-230523

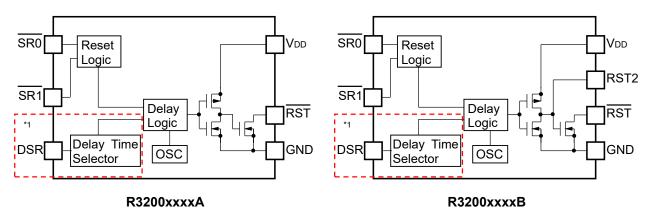

# **BLOCK DIAGRAMS**

<sup>\*1</sup> The parts surrounded by red dotted lines are for the R3200x001x only.

# **SELECTION GUIDE**

The package type, the combination of output delay time and output release time, the output type for the device are user-selectable options.

#### **Selection Guide**

| Product Name                                                                                       | Package                                                                       | Quantity per Reel                                                                                                     | Pb Free                                                                                       | Halogen Fre                          |

|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------|

| R3200Kxxx*-TR                                                                                      | DFN(PL)2020-8B                                                                | 5,000 pcs                                                                                                             | Yes                                                                                           | Yes                                  |

| R3200Lxxx*-E2                                                                                      | DFN1216-8                                                                     | 5,000 pcs                                                                                                             | Yes                                                                                           | Yes                                  |

| · · · ·                                                                                            |                                                                               | om 7.5 s or 11.25 s typ.<br>by making one of the a                                                                    | ctive-low input pins h                                                                        | iah.                                 |

| (xx2) / (053) / (06<br>A reset sig<br>A reset sig<br>pins high.                                    | 64)<br>nal will be released a<br>nal can be released                          | automatically after output<br>before output release ti<br>output delay time and t                                     | ut release time.<br>me by making one of                                                       | the active-low in                    |

| (xx2) / (053) / (06<br>A reset sig<br>A reset sig<br>pins high.                                    | 64)<br>nal will be released a<br>nal can be released                          | automatically after outpu<br>before output release ti<br>output delay time and t                                      | ut release time.<br>me by making one of<br>he output release tim                              | the active-low in the for each devic |

| (xx2) / (053) / (06<br>A reset sig<br>A reset sig<br>pins high.                                    | 64)<br>nal will be released a<br>nal can be released                          | automatically after outpublic before output release ti                                                                | ut release time.<br>me by making one of                                                       | the active-low in the for each devic |

| (xx2) / (053) / (06<br>A reset sig<br>A reset sig<br>pins high.<br>Refer to the<br>002             | 64)<br>nal will be released a<br>nal can be released                          | automatically after outp<br>before output release ti<br>output delay time and t<br>Output Delay Time                  | ut release time.<br>me by making one of<br>he output release tim<br>Output Release            | the active-low in the for each devic |

| (xx2) / (053) / (06<br>A reset sig<br>A reset sig<br>pins high.<br>Refer to the<br>002<br>052 (R32 | 64)<br>nal will be released a<br>nal can be released<br>e table below for the | automatically after outpu<br>before output release ti<br>output delay time and t<br><u>Output Delay Time</u><br>7.5 s | ut release time.<br>me by making one of<br>he output release tim<br>Output Release<br>0.234 s | the active-low in the for each devic |

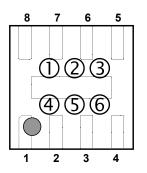

### **PIN DESCRIPTIONS**

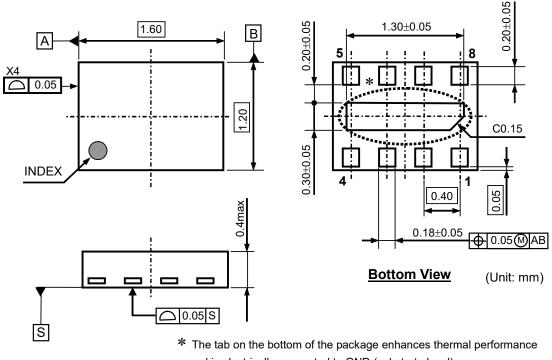

\* The tab on the bottom of the package enhances thermal performance and is electrically connected to GND (substrate level). It is recommended that the tab be connected to the ground plane on the board, or otherwise be left floating.

| Pin No. | Symbol | Description                                                                            |  |

|---------|--------|----------------------------------------------------------------------------------------|--|

| 1       | NC     | No Connection (R3200xxxxA)                                                             |  |

| I       | RST2   | CMOS Output Pin, Active-high (R3200xxxxB)                                              |  |

| 2       | GND    | Ground Pin                                                                             |  |

| 3       | SR1    | Input Pin2, Active-low <sup>*1</sup>                                                   |  |

| 4       | RST    | Nch Open Drain Output Pin, Active-low <sup>*2</sup>                                    |  |

| 5       | DSR    | Output Delay Time Selection Pin (R3200x001x) (GND: 7.5 s, V <sub>DD</sub> : 11.25 s)*3 |  |

| 5       | TEST2  | Test Pin 2*4 (R3200xxx2x/ R3200L053B/ R3200L064A)                                      |  |

| 6       | TEST   | Test Pin <sup>*4</sup>                                                                 |  |

| 7       | SR0    | Input Pin1, Active-low <sup>*1</sup>                                                   |  |

| 8       | Vdd    | Power Supply Input Pin                                                                 |  |

<sup>\*1</sup> When only one active-low input pin is used, connect the unused one to GND.

<sup>\*2</sup> The RST pin must be connected to GND or left floating if it is not used (Ex.R3200xxxxB).

$^{\star3}$  The DSR pin must be connected to GND or  $V_{\text{DD}}.$

<sup>\*4</sup> The TEST pin and the TEST2 pin must be connected to GND when they are used.

# **ABSOLUTE MAXIMUM RATINGS**

### **Absolute Maximum Ratings**

| Symbol          | Item                                                            | Rat                              | Rating        |       |

|-----------------|-----------------------------------------------------------------|----------------------------------|---------------|-------|

| V <sub>DD</sub> | Supply Voltage                                                  | GND -(                           | GND -0.3 to 6 |       |

| Vsr0            | Input Voltage (Input Pin1)                                      | GND -(                           | 0.3 to 6      | V     |

| Vsr1            | Input Voltage (Input Pin2)                                      | GND -(                           | 0.3 to 6      | V     |

| Vrst            | Output Voltage (Reset Signal Output Pin1)                       | GND -(                           | 0.3 to 6      | V     |

| Vrst2           | Output Voltage (Reset Signal Output Pin2)                       | GND -0.3 to V <sub>DD</sub> +0.3 |               | V     |

| Vdsr            | Input Voltage (Output Delay Time Selection Pin)<br>(R3200x001x) | GND -0.3 to 6                    |               | V     |

| Іоит            | Output Current                                                  | 20                               |               | mA    |

| PD              | Power Dissipation (JEDEC STD. 51)*1                             | DFN(PL)2020-8B                   | 1050          | - mW  |

| FD              | Fower Dissipation (JEDEC STD. 51)                               | DFN1216-8                        | 1700          | 11100 |

| Та              | Operating Temperature Range -40 to +85                          |                                  | o +85         | °C    |

| Tstg            | Storage Temperature Range -55 to +125                           |                                  | °C            |       |

<sup>\*1</sup> Refer to PACKAGE INFORMATION for detailed information.

#### ABSOLUTE MAXIMUM RATINGS

Electronic and mechanical stress momentarily exceeded absolute maximum ratings may cause permanent damage and may degrade the life time and safety for both device and system using the device in the field. The functional operation at or over these absolute maximum ratings is not assured.

#### **RECOMMENDED OPERATING CONDITIONS (ELECTRICAL CHARACTERISTICS)**

All of electronic equipment should be designed that the mounted semiconductor devices operate within the recommended operating conditions. The semiconductor devices cannot operate normally over the recommended operating conditions, even if they are used over such conditions by momentary electronic noise or surge. And the semiconductor devices may receive serious damage when they continue to operate over the recommended operating conditions.

NO.EA-280-230523

# **ELECTRICAL CHARACTERISTICS**

The specifications surrounded by  $\Box$  are guaranteed by design engineering at  $-40^{\circ}C \le Ta \le 85^{\circ}C$ .

| Symbol           | ltem                              | Conditions                                                 |                          | Min.                      | Тур.  | Max.   | Unit |

|------------------|-----------------------------------|------------------------------------------------------------|--------------------------|---------------------------|-------|--------|------|

| Vdd              | Supply Voltage                    |                                                            |                          |                           |       | 5.5    | V    |

| Iss1             | Supply Current 1 <sup>*1</sup>    | V <sub>DD</sub> = 5.5 V (at                                | standby)                 |                           | 0.28  | 1.35   | μA   |

| I <sub>SS2</sub> | Supply Current 2*2                | $V_{DD} = 5.5 V$<br>(at active before reset signal output) |                          |                           | 3.0   | 6.5    | μA   |

| lss3             | Supply Current 3*3                | V <sub>DD</sub> = 5.5 V<br>(at active after re             | eset signal output)      |                           | 0.45  | 1.7    | μA   |

|                  |                                   | V <sub>DD</sub> ≥ 4.5 V                                    | I <sub>OL</sub> = 8 mA   |                           |       |        |      |

| Vol              | "L" Output Voltage                | V <sub>DD</sub> ≥ 3.3 V                                    | I <sub>0L</sub> = 5 mA   |                           |       | 0.3    | V    |

|                  |                                   | V <sub>DD</sub> ≥ 1.65 V                                   | I <sub>OL</sub> = 3 mA   |                           |       |        |      |

|                  |                                   | V <sub>DD</sub> ≥ 4.5 V                                    | I <sub>OH</sub> = 5 mA   |                           |       |        |      |

| V <sub>OH</sub>  | "H" Output Voltage <sup>*4</sup>  | V <sub>DD</sub> ≥ 3.3 V                                    | I <sub>OH</sub> = 2.5 mA | V <sub>DD</sub><br>x 0.85 |       |        | V    |

|                  |                                   | V <sub>DD</sub> ≥ 1.65 V                                   | I <sub>он</sub> = 0.8 mA | <u>k 0.05</u>             |       |        |      |

| ILEAKI           | SR0, SR1 Input<br>Leakage Current | V <sub>DD</sub> = 5.5 V                                    |                          |                           |       | 0.1    | μA   |

| ILEAKO           | Output Leakage Current            | V <sub>DD</sub> = 5.5 V                                    |                          |                           |       | 0.1    | μA   |

| tdolov           | Output Dolov Time                 | DSR = GND                                                  |                          | 6.75                      | 7.5   | 8.25   | S    |

| tdelay           | Output Delay Time                 | $DSR = V_{DD}$                                             |                          | 10.125                    | 11.25 | 12.375 | S    |

| VIL              | SR0, SR1 "L" Input Voltaget       |                                                            |                          |                           |       | 0.3    | V    |

| VIH              | SR0, SR1 "H" Input Voltaget       |                                                            |                          | 0.85                      |       |        | V    |

All test items listed under *ELECTRICAL CHARACTERISTICS* are done under the pulse load condition (Tj ≈ Ta = 25°C) except Supply Current 2.

<sup>\*1</sup> Supply current when the device is active and waiting for the reset input.

<sup>\*2</sup> Supply current when both active-low input pins are low and the timer operation is running.

<sup>\*3</sup> Supply current after the completion of timer operation and the output of reset signal.

<sup>\*4</sup> For the R3200xxxxB only (CMOS output).

# **ELECTRICAL CHARACTERISTICS (continued)**

The specifications surrounded by  $\square$  are guaranteed by design engineering at  $-40^{\circ}C \le Ta \le 85^{\circ}C$ .

| Symbol           | ltem                              | Con                                                                  | ditions                  | Min.                      | Тур.     | Max.              | Unit |

|------------------|-----------------------------------|----------------------------------------------------------------------|--------------------------|---------------------------|----------|-------------------|------|

| VDD              | Operating Voltage                 |                                                                      |                          | 1.65                      |          | 5.5               | V    |

| Iss1             | Supply Current 1 <sup>*1</sup>    | V <sub>DD</sub> = 5.5 V (at                                          | standby)                 |                           | 0.28     | 1.35              | μA   |

| I <sub>SS2</sub> | Supply Current 2*2                | V <sub>DD</sub> = 5.5 V<br>(at active before reset signal<br>output) |                          |                           | 3.0      | 6.5               | μA   |

| lss3             | Supply Current 3*3                | V <sub>DD</sub> = 5.5 V<br>(at active after r                        | eset signal output)      |                           | 0.45     | 1.7               | μA   |

|                  |                                   | V <sub>DD</sub> ≥ 4.5 V                                              | I <sub>OL</sub> = 8 mA   |                           |          |                   |      |

| Vol              | "L" Output Voltage                | V <sub>DD</sub> ≥ 3.3 V                                              | l <sub>o∟</sub> = 5 mA   |                           |          | 0.3               | V    |

|                  |                                   | V <sub>DD</sub> ≥ 1.65 V                                             | I <sub>OL</sub> = 3 mA   |                           |          |                   |      |

|                  |                                   | V <sub>DD</sub> ≥ 4.5 V                                              | I <sub>он</sub> = 5 mA   |                           |          |                   |      |

| V <sub>OH</sub>  | "H" Output Voltage <sup>*4</sup>  | V <sub>DD</sub> ≥ 3.3 V                                              | I <sub>OH</sub> = 2.5 mA | V <sub>DD</sub><br>x 0.85 |          |                   | V    |

|                  |                                   | V <sub>DD</sub> ≥ 1.65 V                                             | I <sub>OH</sub> = 0.8 mA | и 0.00                    |          |                   |      |

| ILEAKI           | SR0, SR1 Input<br>Leakage Current | V <sub>DD</sub> = 5.5 V                                              |                          |                           |          | 0.1               | μA   |

| ILEAKO           | Output Leakage Current            | V <sub>DD</sub> = 5.5 V                                              |                          |                           |          | 0.1               | μA   |

| tdelay           | Output Delay Time <sup>*5</sup>   |                                                                      |                          | tdelay_s<br>x 0.9         | tdelay_s | tdelay_s<br>x 1.1 | sec  |

| trec             | Output Release Time*5             |                                                                      |                          | trec_s<br>x 0.9           | trec_s   | trec_s<br>x 1.1   | sec  |

| VIL              | SR0, SR1 "L" Input Voltage        |                                                                      |                          |                           |          | 0.3               | V    |

| VIH              | SR0, SR1 "H" Input Voltage        |                                                                      |                          | 0.85                      |          |                   | V    |

All test items listed under ELECTRICAL CHARACTERISTICS are done under the pulse load condition (Tj ≈ Ta = 25°C) except Supply Current 2.

<sup>\*1</sup> Supply current when the device is active and waiting for the reset input.

<sup>\*2</sup> Supply current when both active-low input pins are low and the timer operation is running.

<sup>\*3</sup> Supply current after the automatic cancellation of reset signal following the completion of timer operation and the output of rest signal.

<sup>\*4</sup> For the R3200xxxxB only (CMOS output).

<sup>\*5</sup> Refer to Output Delay Time and Output Release Time of R3200x.

### Output Delay Time and Output Release Time of R3200x

| Product Name | tdelay_s | trec_s   |

|--------------|----------|----------|

| R3200x002x   | 7.5 s    | 0.234 s  |

| R3200L052B   | 10 s     | 0.313 s  |

| R3200L053B   | 10 s     | 0.078 s  |

| R3200L064A   | 3.0 s    | 0.1875 s |

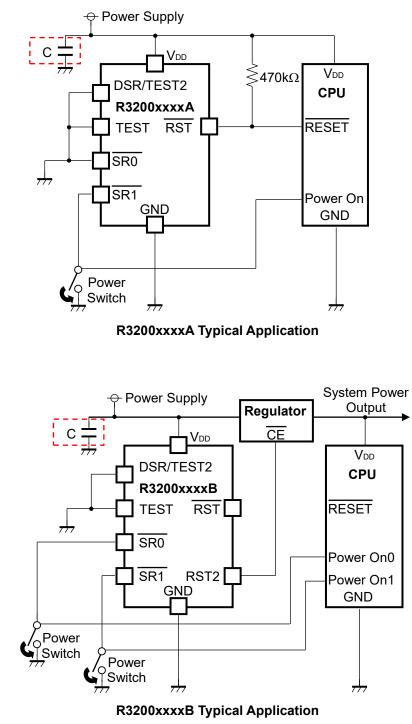

# **TYPICAL APPLICATIONS**

A bypass capacitor between the power supply line and the GND line is not necessarily required. If the device operation is affected by power supply noise, connect an appropriately selected bypass capacitor.

# **TECHNICAL NOTES**

The performance of power source circuits using this device largely depends on the peripheral circuits. When selecting the peripheral components, consider the conditions of use. Do not allow each component, PCB pattern and the device to exceed their respected rated values (voltage, current and power) when designing the peripheral circuits.

- When only one active-low input pins is used (refer to *R3200xxxxA Typical Application*) connect the unused one to GND.

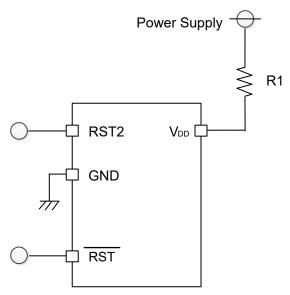

- In the case of applying the following circuit configuration to the R3200x, the supply current of the device itself may cause significant voltage drop on the V<sub>DD</sub> pin if the R1 value is high. As a result, the V<sub>DD</sub> voltage may fall below the minimum operating voltage.

**Circuit Configuration Example**

### THEORY OF OPERATION

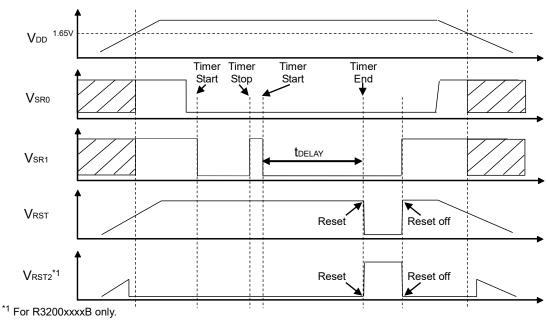

R3200x001x Timing Chart

- When both active-low input pins become the low voltage level, the timer operation starts. After the output delay time (tdelay), a reset signal will be sent out. When one of the active-low input pins becomes the high voltage level, the timer operation stops.

- During tdealy, if one of the active-low input pins becomes the high voltage level, the timer operation stops. If both active-low input pins become the low voltage level again, a reset signal will be sent out after tdelay.

- A reset signal will be released if one of the active-low input pins becomes the high voltage level. Until one of the active-low input pins becomes the high voltage level, a reset signal will be continually sent out.

- tdelay can be selected from 7.5 s or 11.25 s typ. by connecting the DSR pin to either GND or V<sub>DD</sub>. However, if the DSR pin is switched during the operations, the output would become unstable and may cause false operations. Switching of the DSR pin must be done during power-off.

Also, the DSR pin must be connected to either GND or  $V_{DD}$ , otherwise the output would become unstable and may cause false operations.

NO.EA-280-230523

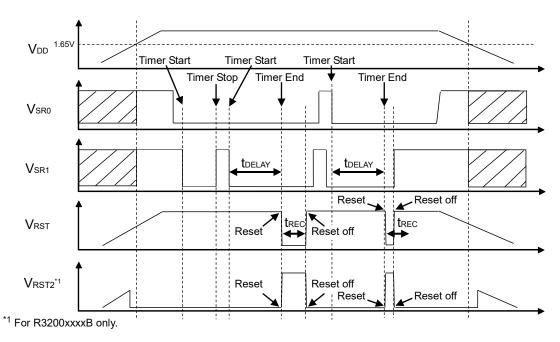

R3200xxx2x, R3200L053B, R3200L064A Timing Chart

- When both active-low input pins become the low voltage level, the timer operation starts. After the output delay time (tdelay), a reset signal will be sent out. If one of the active-low input pins becomes the high voltage level, the timer operation stops.

- During tdelay, if one of the active-low input pins becomes the high voltage level, the timer operation stops. If both active-low input pins become the low voltage level again, a reset signal will be sent out after tdelay.

- A reset signal will be released automatically after the reset delay time (trec), or it will be released if one of the active-low input pins becomes the high voltage level.

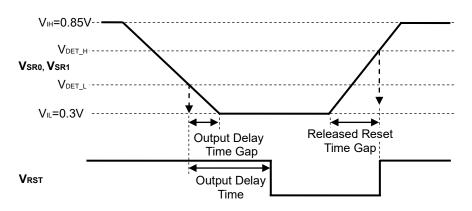

### OUTPUT DELAY TIME GAP

The threshold voltages of the active-low input pins are between  $V_{IL}$  and  $V_{IH}$ . Therefore, if the rising or falling slew rate is very slow, the timer will start at the point of crossing the threshold voltage and may cause errors in the output delay time (tdelay) and the output release time (trec).

Relation between the Rising and Falling Slew Rate and the Time Gap

### **VDD START-UP DURING LOW INPUT**

When starting up  $V_{DD}$  at slow slew rate of 0.001 V/µs or less while the active-low input pins are the low voltage level, the device may start the operation at lower than the minimum operating voltage, thus tdelay may exceed the guaranteed time.

# PACKAGE INFORMATION

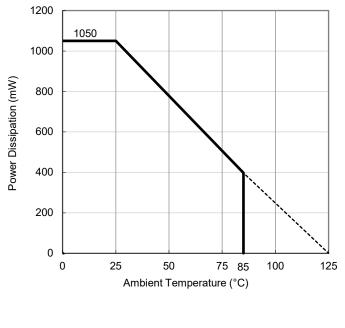

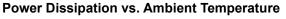

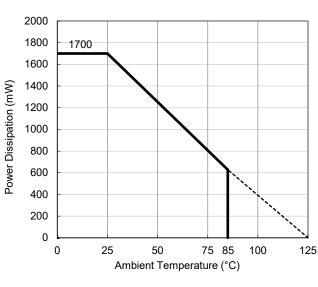

Power Dissipation (DFN(PL)2020-8B)

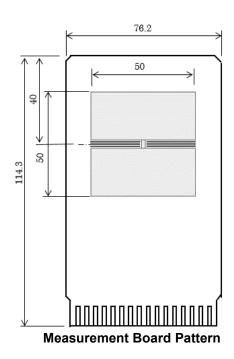

The power dissipation of the package is dependent on PCB material, layout, and environmental conditions. The following measurement conditions are based on JEDEC STD. 51-7.

| Item             | Measurement Conditions                                                                                                                                                                       |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Environment      | Mounting on Board (Wind Velocity = 0 m/s)                                                                                                                                                    |  |

| Board Material   | Glass Cloth Epoxy Plastic (Four-Layer Board)                                                                                                                                                 |  |

| Board Dimensions | 76.2 mm × 114.3 mm × 0.8 mm                                                                                                                                                                  |  |

| Copper Ratio     | Outer Layer (First Layer): Less than 95% of 50 mm Square<br>Inner Layers (Second and Third Layers): Approx. 100% of 50 mm Square<br>Outer Layer (Fourth Layer): Approx. 100% of 50 mm Square |  |

| Through-holes    | φ 0.3 mm × 23 pcs                                                                                                                                                                            |  |

### Measurement Conditions

#### **Measurement Result**

(Ta = 25°C, Tjmax = 125°C)

|                                          | ( , j ,            |  |  |

|------------------------------------------|--------------------|--|--|

| Item                                     | Measurement Result |  |  |

| Power Dissipation                        | 1050 mW            |  |  |

| Thermal Resistance (θja)                 | θja = 92°C/W       |  |  |

| Thermal Characterization Parameter (ψjt) | ψjt = 60°C/W       |  |  |

θja: Junction-to-Ambient Thermal Resistance

#### wjt: Junction-to-Top Thermal Characterization Parameter

NO.EA-280-230523

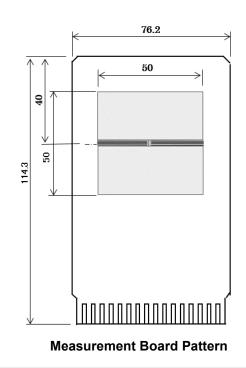

### PACKAGE DIMENSIONS (DFN(PL)2020-8B)

The tab on the bottom of the package enhances thermal performance and is electrically connected to GND (substrate level).

It is recommended that the tab be connected to the ground plane on the board, or otherwise be left floating.

### DFN(PL)2020-8B Package Dimensions

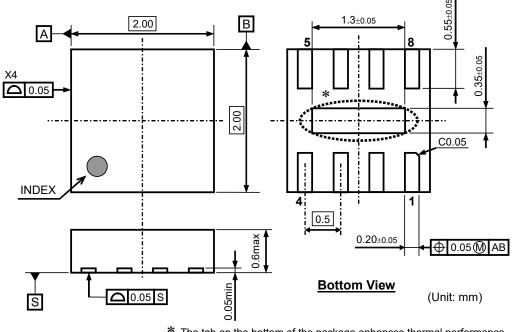

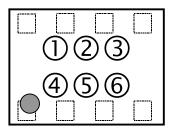

### MARK SPECIFICATION (DFN(PL)2020-8B)

①②③④: Product Code … <u>Refer to MARK SPECIFICATION TABLE (DFN(PL)2020-8B)</u>.

⑤⑥: Lot Number … Alphanumeric Serial Number

DFN(PL)2020-8B Mark Specification

NO.EA-280-230523

### MARK SPECIFICATION TABLE (DFN(PL)2020-8B)

### R3200K Mark Specification Table

| Product Name | 0234    |

|--------------|---------|

| R3200K001A   | D 0 0 1 |

| R3200K001B   | D D 0 2 |

| R3200K002A   | D D 0 3 |

| R3200K002B   | D D 0 4 |

### Power Dissipation (DFN1216-8)

The power dissipation of the package is dependent on PCB material, layout, and environmental conditions. The following conditions are based on JEDEC STD. 51-7.

#### **Measurement Conditions**

| ltem             | Measurement Conditions                                                                                                                                                                       |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Environment      | Mounting on Board (Wind Velocity = 0 m/s)                                                                                                                                                    |  |

| Board Material   | Glass Cloth Epoxy Plastic (Four-Layer Board)                                                                                                                                                 |  |

| Board Dimensions | 76.2 mm × 114.3 mm × 0.8 mm                                                                                                                                                                  |  |

| Copper Ratio     | Outer Layer (First Layer): Less than 95% of 50 mm Square<br>Inner Layers (Second and Third Layers): Approx. 100% of 50 mm Square<br>Outer Layer (Fourth Layer): Approx. 100% of 50 mm Square |  |

| Through-holes    | φ 0.2 mm × 25 pcs                                                                                                                                                                            |  |

#### **Measurement Result**

(Ta = 25°C. Timax = 125°C)

| Item                                     | Measurement Result |

|------------------------------------------|--------------------|

| Power Dissipation                        | 1700 mW            |

| Thermal Resistance (θja)                 | θja = 56°C/W       |

| Thermal Characterization Parameter (ψjt) | ψjt = 18°C/W       |

θja: Junction-to-Ambient Thermal Resistance

wjt: Junction-to-Top Thermal Characterization Parameter

Power Dissipation vs. Ambient Temperature

### PACKAGE DIMENSIONS (DFN1216-8)

and is electrically connected to GND (substrate level). It is recommended that the tab be connected to the ground plane on the board, or otherwise be left floating.

#### **DFN1216-8 Package Dimensions**

### MARK SPECIFICATION (DFN1216-8)

①②③④: Product Code ... <u>Refer to MARK SPECIFICATION TABLE (DFN1216-8).</u>

⑤⑥: Lot Number ... Alphanumeric Serial Number

**DFN1216-8 Mark Specification**

NO.EA-280-230523

### MARK SPECIFICATION TABLE (DFN1216-8)

### R3200L Mark Specification Table

| Product Name | 0234    |

|--------------|---------|

| R3200L001A   | D E 0 1 |

| R3200L001B   | D F 0 2 |

| R3200L002A   | D E 0 3 |

| R3200L002B   | D E 0 4 |

| R3200L052B   | D E 0 5 |

| R3200L053B   | D E 0 6 |

| R3200L064A   | D E 0 7 |

NO.EA-280-230523

# **TEST CIRCUITS**

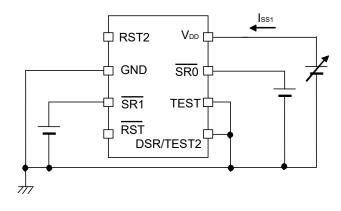

**Supply Current Test Circuit**

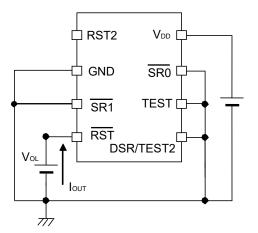

Nch Driver Output Voltage Test Circuit

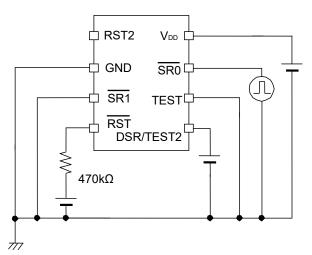

**Output Delay Time Test Circuit**

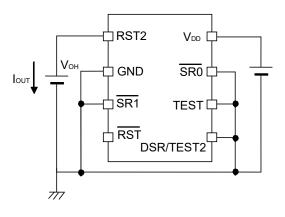

CMOS Driver Output Voltage Test Circuit (For the R3200xxxxB only.)

# **TYPICAL CHARACTERISTICS**

Note: Typical Characteristics are intended to be used as reference data; they are not guaranteed.

3) Supply Current 3 vs. Temperature R3200x (after the reset signal output)

5) Supply Current 2 vs. Supply Voltage R3200x (before the reset signal output)

2) Supply Current 2 vs. Temperature R3200x (before the reset signal output)

4) Supply Current 1 vs. Supply Voltage R3200x (at standby)

6) Supply Current 2 vs. Supply Voltage R3200x (after the reset signal output)

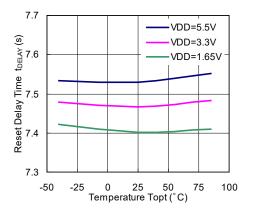

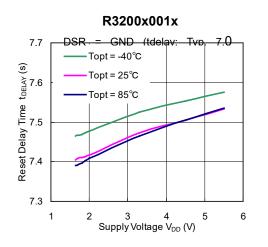

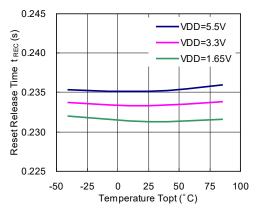

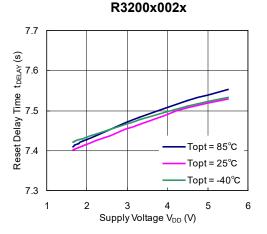

#### 7) Output Delay Time vs. Temperature

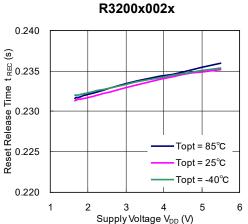

#### 8) Output Release Time vs. Temperature

R3200x002x

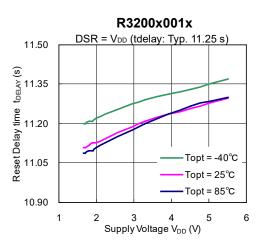

9) Output Delay Time vs. Supply Voltage

R3200x002x

NO.EA-280-230523

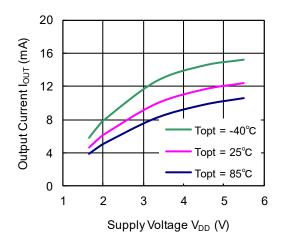

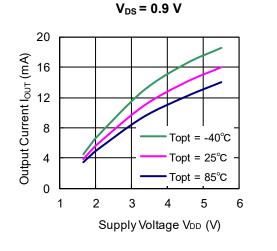

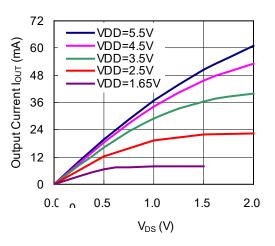

11) Nch Driver Output Current vs. Supply Voltage  $V_{DS} = 0.3 V$

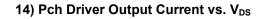

13) Pch Driver Output Current vs. Supply Voltage

10) Output Release Time vs. Supply Voltage

12) Nch Driver Output Current vs. V<sub>DS</sub>

- 1. The products and the product specifications described in this document are subject to change or discontinuation of production without notice for reasons such as improvement. Therefore, before deciding to use the products, please refer to our sales representatives for the latest information thereon.

- 2. The materials in this document may not be copied or otherwise reproduced in whole or in part without the prior written consent of us.

- 3. This product and any technical information relating thereto are subject to complementary export controls (so-called KNOW controls) under the Foreign Exchange and Foreign Trade Law, and related politics ministerial ordinance of the law. (Note that the complementary export controls are inapplicable to any application-specific products, except rockets and pilotless aircraft, that are insusceptible to design or program changes.) Accordingly, when exporting or carrying abroad this product, follow the Foreign Exchange and Foreign Trade Control Law and its related regulations with respect to the complementary export controls.

- 4. The technical information described in this document shows typical characteristics and example application circuits for the products. The release of such information is not to be construed as a warranty of or a grant of license under our or any third party's intellectual property rights or any other rights.

- 5. The products listed in this document are intended and designed for use as general electronic components in standard applications (office equipment, telecommunication equipment, measuring instruments, consumer electronic products, amusement equipment etc.). Those customers intending to use a product in an application requiring extreme quality and reliability, for example, in a highly specific application where the failure or misoperation of the product could result in human injury or death should first contact us.

- Aerospace Equipment

- Equipment Used in the Deep Sea

- Power Generator Control Equipment (nuclear, steam, hydraulic, etc.)

- Life Maintenance Medical Equipment

- Fire Alarms / Intruder Detectors

- Vehicle Control Equipment (automotive, airplane, railroad, ship, etc.)

- Various Safety Devices

- Traffic control system

- Combustion equipment

In case your company desires to use this product for any applications other than general electronic equipment mentioned above, make sure to contact our company in advance. Note that the important requirements mentioned in this section are not applicable to cases where operation requirements such as application conditions are confirmed by our company in writing after consultation with your company.

- 6. We are making our continuous effort to improve the quality and reliability of our products, but semiconductor products are likely to fail with certain probability. In order to prevent any injury to persons or damages to property resulting from such failure, customers should be careful enough to incorporate safety measures in their design, such as redundancy feature, fire containment feature and fail-safe feature. We do not assume any liability or responsibility for any loss or damage arising from misuse or inappropriate use of the products.

- 7. The products have been designed and tested to function within controlled environmental conditions. Do not use products under conditions that deviate from methods or applications specified in this datasheet. Failure to employ the products in the proper applications can lead to deterioration, destruction or failure of the products. We shall not be responsible for any bodily injury, fires or accident, property damage or any consequential damages resulting from misuse or misapplication of the products.

- 8. Quality Warranty

- 8-1. Quality Warranty Period

In the case of a product purchased through an authorized distributor or directly from us, the warranty period for this product shall be one (1) year after delivery to your company. For defective products that occurred during this period, we will take the quality warranty measures described in section 8-2. However, if there is an agreement on the warranty period in the basic transaction agreement, quality assurance agreement, delivery specifications, etc., it shall be followed.

8-2. Quality Warranty Remedies

When it has been proved defective due to manufacturing factors as a result of defect analysis by us, we will either deliver a substitute for the defective product or refund the purchase price of the defective product.

- Note that such delivery or refund is sole and exclusive remedies to your company for the defective product.

- 8-3. Remedies after Quality Warranty Period

With respect to any defect of this product found after the quality warranty period, the defect will be analyzed by us. On the basis of the defect analysis results, the scope and amounts of damage shall be determined by mutual agreement of both parties. Then we will deal with upper limit in Section 8-2. This provision is not intended to limit any legal rights of your company.

- 9. Anti-radiation design is not implemented in the products described in this document.

- 10. The X-ray exposure can influence functions and characteristics of the products. Confirm the product functions and characteristics in the evaluation stage.

- 11. WLCSP products should be used in light shielded environments. The light exposure can influence functions and characteristics of the products under operation or storage.

- 12. Warning for handling Gallium and Arsenic (GaAs) products (Applying to GaAs MMIC, Photo Reflector). These products use Gallium (Ga) and Arsenic (As) which are specified as poisonous chemicals by law. For the prevention of a hazard, do not burn, destroy, or process chemically to make them as gas or power. When the product is disposed of, please follow the related regulation and do not mix this with general industrial waste or household waste.

- 13. Please contact our sales representatives should you have any questions or comments concerning the products or the technical information.

Nisshinbo Micro Devices Inc.

Official website https://www.nisshinbo-microdevices.co.jp/en/ Purchase information https://www.nisshinbo-microdevices.co.jp/en/buy/

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Nisshinbo Micro Devices:

<u>R3200L001A-E2</u> <u>R3200L002A-E2</u> <u>R3200K001B-TR</u> <u>R3200L052B-E2</u> <u>R3200K001A-TR</u> <u>R3200K002B-TR</u> R3200L001B-E2 R3200L064A-E2 R3200L002B-E2 R3200K002A-TR R3200L053B-E2