# M0220MD-202MDAR1-3

# **Dot-matrix Character Vacuum Fluorescent Display Module**

| M-      | VFD Module                       |

|---------|----------------------------------|

| 0220-   | 2 Lines x 20 Characters          |

| M-      | Model                            |

| D-      | Dot-Matrix                       |

| 202MDA- | Character Size = 3.85mm x 8.95mm |

| R-      | RoHS Compliant                   |

| 1-3     | M68 Parallel Interface           |

Newhaven Display International, Inc. 2661 Galvin Ct. Elgin IL, 60124 Ph: 847-844-8795 Fax: 847-844-8796

### **Document Revision History**

| Revision | Date      | Description                                           | Changed by |

|----------|-----------|-------------------------------------------------------|------------|

| 0        | 3/21/2005 | Initial Release                                       | -          |

| 1        | 9/21/2009 | Updated Driver version, modified VF glass pins        | CL         |

| 2        | 12/4/2009 | Reduce pixel size to increase brightness and lifetime | CL         |

| 3        | 1/26/2011 | Storage temperature updated                           | TL         |

| 4        | 7/26/15   | Module redesigned                                     | AK         |

### **Functions and Features**

- 2 lines x 20 characters

- Built-in controller

- Built-in VF AC power supply

- 5.0V power supply

- 5x8 dots with cursor

- Parallel interface (serial interface selectable by onboard jumpers)

- Display color: x = 0.250, y = 0.439 (Green)

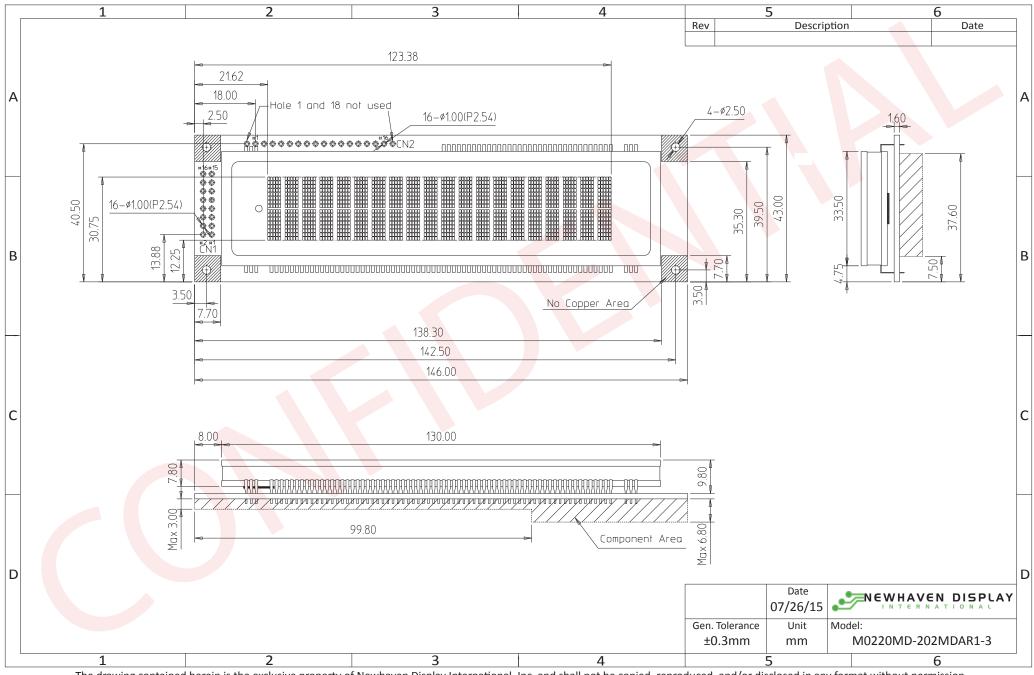

### **Mechanical Drawing**

The drawing contained herein is the exclusive property of Newhaven Display International, Inc. and shall not be copied, reproduced, and/or disclosed in any format without permission.

# Pattern Detail

\*101.75

|          | <br>101.72 | _ |

|----------|------------|---|

|          |            | 1 |

| 1        |            |   |

| 20       |            |   |

| ¶<br>19. |            |   |

# **Pin Description**

#### Parallel Interface (Default):

| Pin No. | Symbol    | External     | Function Description                                         |

|---------|-----------|--------------|--------------------------------------------------------------|

|         |           | Connection   |                                                              |

| 1       | VSS       | Power Supply | Ground                                                       |

| 2       | VDD       | Power Supply | Supply Voltage for logic (+5.0V)                             |

| 3       | NC (/RST) | - (MPU)      | No Connect (if JP2 is short, PIN3 = Active LOW reset signal) |

| 4       | RS        | MPU          | Register Select signal RS=1: DATA RS=0: COMMAND              |

| 5       | R/W       | MPU          | Read/Write select signal R/W=1: Read, R/W=0: Write           |

| 6       | E         | MPU          | Operation Enable signal. Falling Edge Triggered              |

| 7-10    | DB0 – DB3 | MPU          | Four low order bi-directional three-state data bus lines.    |

|         |           |              | These four are not used during 4-bit operation               |

| 11-14   | DB4 – DB7 | MPU          | Four high order bi-directional three-state data bus lines.   |

Recommended LCD connector: 2.54mm pitch pins

#### Serial Interface:

| Pin No. | Symbol | External     | Function Description             |

|---------|--------|--------------|----------------------------------|

|         |        | Connection   |                                  |

| 1       | VSS    | Power Supply | Ground                           |

| 2       | VDD    | Power Supply | Supply Voltage for logic (+5.0V) |

| 3       | SI/SO  | MPU          | Serial Data In/Out signal        |

| 4       | STB    | MPU          | Serial Strobe signal             |

| 5       | NC     | -            | No Connect                       |

| 6       | SCK    | MPU          | Serial Clock signal              |

| 7-16    | NC     | -            | No Connect                       |

# **Jumper Settings**

| Mode                   | JP2  | JP3   | JP4   | JP5   | JP6   | JP7   |

|------------------------|------|-------|-------|-------|-------|-------|

| Serial                 | Open | Short | Open  | Short | Open  | Short |

| Parallel i80           | *1   | Open  | Short | Open  | Open  | Short |

| Parallel M68 (default) | *1   | Open  | Short | Open  | Short | Open  |

\*1: JP2 short enables PIN3 as external reset. JP2 open disables reset.

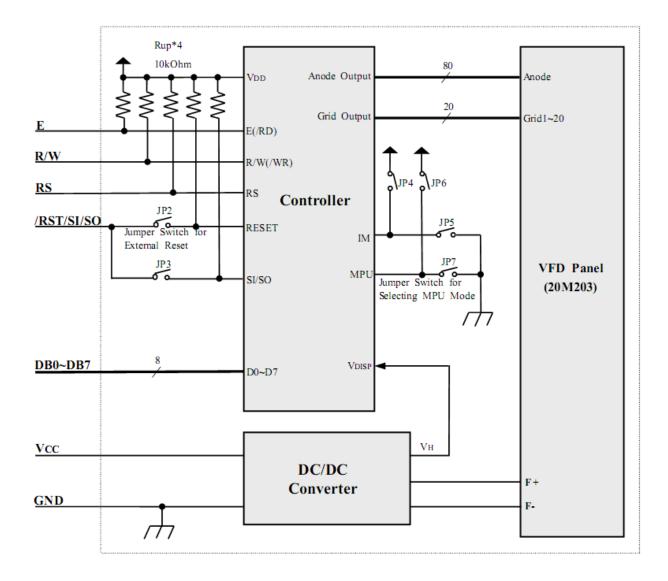

# **Block Diagram**

### **Electrical Characteristics**

| Item                        | Symbol | Condition | Min.    | Тур. | Max.    | Unit              |

|-----------------------------|--------|-----------|---------|------|---------|-------------------|

| Operating Temperature Range | Vop    |           | -40     | -    | +85     | °C                |

| Storage Temperature Range   | Vst    |           | -50     | -    | +95     | °C                |

| Operating Humidity          | Нор    |           | 0       | -    | 85      | %                 |

| Storage Humidity            | Hst    |           | 0       | -    | 90      | %                 |

| Vibration                   | -      | 10~55Hz   | -       | -    | 4       | G                 |

| Shock                       | -      |           | -       | -    | 40      | G                 |

| Supply Voltage              | VDD    |           | 4.5     | 5.0  | 5.5     | V                 |

| Supply Current (*Note 1)    | IDD    | Ta=25⁰C   | -       | 290  | 435     | mA                |

|                             |        | VDD=5.0V  |         |      |         |                   |

| Luminance                   | L      |           | 350     | 500  | -       | cd/m <sup>2</sup> |

|                             |        |           | 102     | 146  | -       | ft-L              |

| "H" Level input (*Note 2)   | Vih    |           | 0.7*VDD | -    | -       | V                 |

| "L" Level input             | Vil    |           | -       | -    | 0.3*VDD | V                 |

| "H" Level output            | Voh    |           | 0.8*VDD | -    | -       | V                 |

| "L" Level output            | Vol    |           | -       | -    | 0.2*VDD | V                 |

#### <u>Note</u>:

1. In-rush current can be approx. 10 times the specified supply current at power up.

2. A 10K ohm pull-up resistor is on each input signal for TTL compatibility.

### **Controller Information**

Built-in PT6314 controller.

Please download specification at <a href="http://www.newhavendisplay.com/app\_notes/PT6314.pdf">http://www.newhavendisplay.com/app\_notes/PT6314.pdf</a>

# **Table of Commands**

| Instructions                                                                                                                  |                                  | ıtrol                                                                                                                                                                                                                   | Instruction Code              |                   |     |        |        |       |       |                          | Descriptions                                                                                                                                                                                                  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------|-----|--------|--------|-------|-------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Instructions                                                                                                                  | RS                               | R/W                                                                                                                                                                                                                     | D7                            | D6                | D5  | D4     | D3     | D2    | D1    | D0                       | Descriptions                                                                                                                                                                                                  |  |  |

| Display Clear                                                                                                                 | 0                                | 0                                                                                                                                                                                                                       | 0 0 0 0 0 0 0                 |                   |     |        |        | 0     | 0     | 1                        | Clears all display and sets DD-RAM address 0 in<br>address counter.                                                                                                                                           |  |  |

| Cursor Home                                                                                                                   | 0                                | 0                                                                                                                                                                                                                       | 0                             | 0 0 0 0 0 1 * the |     |        |        | 0     | 1     | *                        | Sets DD-RAM address 0 in ACC. Also returns<br>the display being shifted to the original position.<br>DD-RAM contents remain unchanged.                                                                        |  |  |

| Entry Mode Set                                                                                                                | 0                                | 0                                                                                                                                                                                                                       | 0                             | 0                 | 0   | 0      | 0      | 1     | I/D   | s                        | Sets the cursor direction and specifies display<br>shift. These operations are performed during<br>writing/reading data.                                                                                      |  |  |

| Display ON/OFF Control                                                                                                        | 0                                | 0                                                                                                                                                                                                                       | 0                             | 0                 | 0   | 0      | 1      | D     | С     | в                        | Sets all display ON/OFF (D), cursor ON/OFF (C),<br>cursor blink of character position (B).                                                                                                                    |  |  |

| Cursor or Display Shift                                                                                                       | 0                                | 0                                                                                                                                                                                                                       | 0                             | 0                 | 0   | 1      | S/C    | R/L   | *     | *                        | Shifts display or cursor, keeping DD-RAM contents.                                                                                                                                                            |  |  |

| Function Set                                                                                                                  | 0                                | 0                                                                                                                                                                                                                       |                               |                   |     |        |        |       |       | BR0                      | Sets data length (IF), number of display lines(N),<br>Set brightness level(BR1,BR0)                                                                                                                           |  |  |

| CG-RAM Address Set                                                                                                            | 0                                | 0                                                                                                                                                                                                                       | 0 1 ACG (CG-RAM Address) Sets |                   |     |        |        |       |       |                          | Sets the CG-RAM address.                                                                                                                                                                                      |  |  |

| DD-RAM Address Set                                                                                                            | 0                                | 0                                                                                                                                                                                                                       | 1                             |                   | ADI | D (DD  | -RAN   | 1 Add | ress) | Sets the DD-RAM address. |                                                                                                                                                                                                               |  |  |

| Busy Flag and Address<br>Counter Reading                                                                                      | 0                                | 1                                                                                                                                                                                                                       | BF                            |                   | AC  | C (Ad  | ldress | Coun  | ter)  |                          | Reads busy flag (BF) and address counter (ACC).                                                                                                                                                               |  |  |

| Data Writing to CG- or<br>DD-RAM                                                                                              | 1                                | 0                                                                                                                                                                                                                       |                               |                   | С   | haract | er Co  | de    |       |                          | Writes data into CG-RAM or DD-RAM.                                                                                                                                                                            |  |  |

| Data Reading from CG-<br>or DD-RAM                                                                                            | 1                                | 1                                                                                                                                                                                                                       |                               |                   | С   | haract | er Co  | de    |       |                          | Reads data from CG-RAM or DD-RAM.                                                                                                                                                                             |  |  |

| REMARKS:<br>* DD-RAM: Display<br>Data RAM<br>* CG-RAM: Character<br>Generator RAM<br>* ACG: CG-RAM<br>Address<br>* ADR DB DAM | * I/D<br>* S =<br>* S =<br>* S/C | <ul> <li>* I/D = 1: Increment</li> <li>* I/D = 0: Decrement</li> <li>* S = 1: Display Shift Enabled</li> <li>* S = 0: Cursor Shift Enabled</li> <li>* S/C = 1: Display Shift</li> <li>* S/C = 0: Cursor Move</li> </ul> |                               |                   |     |        |        |       |       |                          | <ul> <li>* IF = 1: 8-bit Operation</li> <li>* IF = 0: 4-bit Operation</li> <li>* N = 1: 2 Lines Display</li> <li>* N = 0: 1 Line Display</li> <li>* BR1, BR0 = 00: 100%, 01: 75%, 10: 50%, 11: 25%</li> </ul> |  |  |

| * ADD: DD-RAM<br>Address<br>* ACC: Address Counter                                                                            |                                  | L = 1:<br>L = 0:                                                                                                                                                                                                        |                               |                   |     |        |        |       |       |                          | * BF = 1: Busy (Internally operating)<br>* BF = 0: Not busy (Instruction acceptable)                                                                                                                          |  |  |

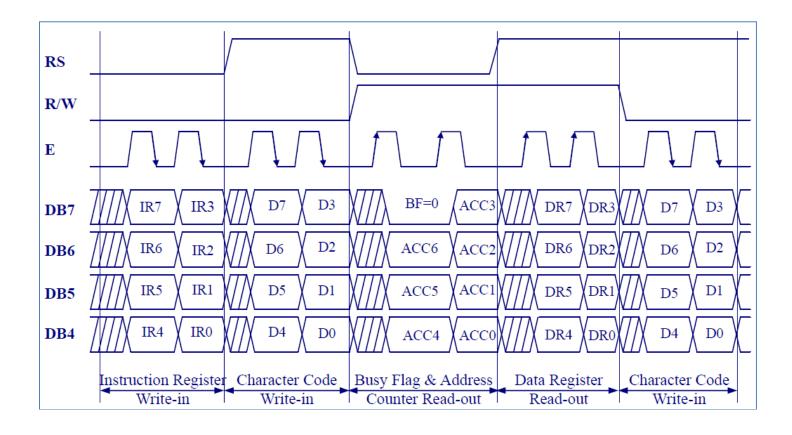

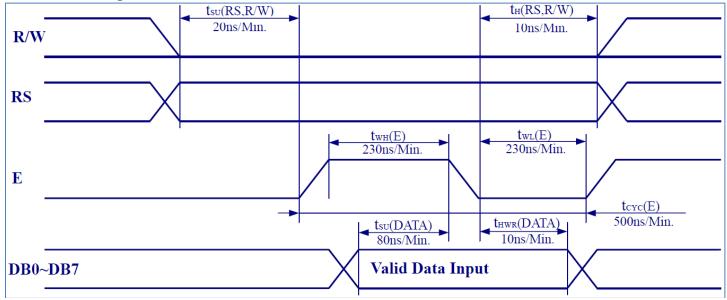

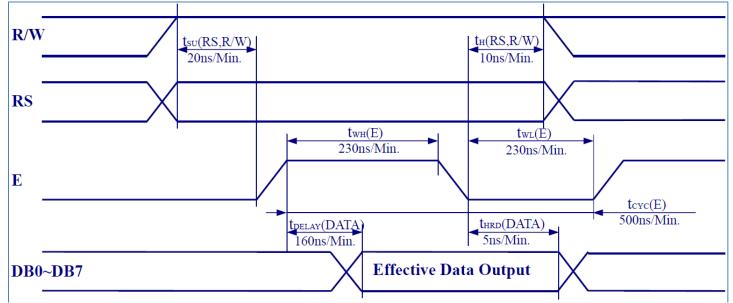

## **Parallel Interface:**

This VFD module can interface in either two 4-bit operations or one 8-bit operation. For 4-bit interface data, only four bus lines (DB4 to DB7) are used for transfer. When to use 4-bit parallel data transfer, DB0 to DB3 keep "H" or "L". The data transfer between the VFD module and the MPU is completed after the 4-bit data has been transferred twice. As for the order of data transfer the four high order bits (for 8-bit operation, DB4 to DB7) are transferred before the four low order bits (for 8-bit operation, DB0 to DB3). The busy flag (BF) are performed before transferring the higher 4 bits. BF checks are not required before transferring the lower 4 bits.

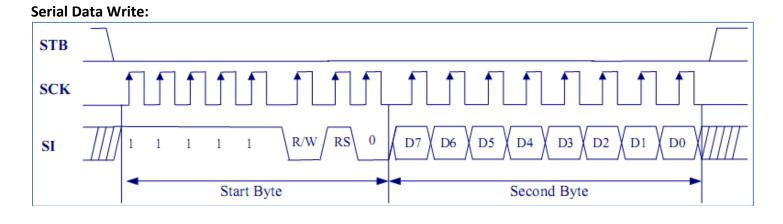

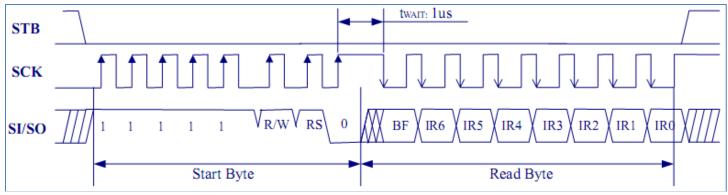

## Serial Interface:

When data is written, it can be inputted when the STB goes to "0". The first byte-Start Byte consists of a total 8 bits including Synchronous bits (bit 1-bit 5), R/W (bit 6), RS (bit 7) and bit 8. The register is selected (IR or DR) by RS(bit 7) while data write or read is selected by R/W (bit 6 = "0"). Next 8-bit instruction byte will follow closely after the defined operation in Start Byte. Data should be keep active in rising edge of clock while it would be output in falling edge in Read operation. Follow the protocol herein:

#### Serial Data Read:

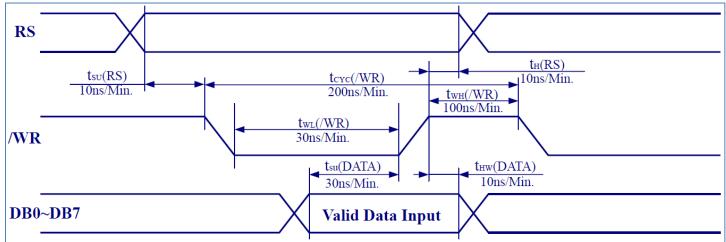

## **Timing Characteristics:**

M68 Write Timing:

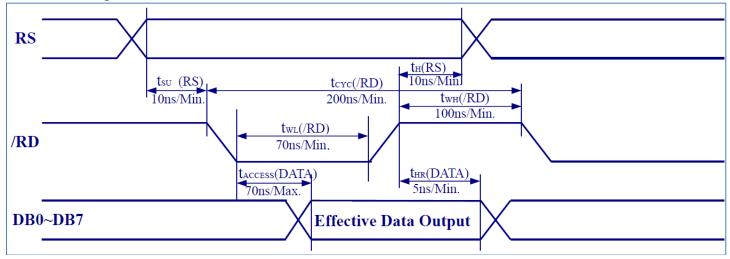

#### M68 Read Timing:

#### i80 Write Timing:

#### i80 Read Timing:

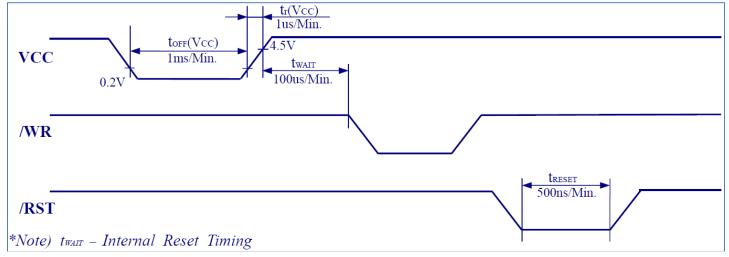

#### **Power ON Timing:**

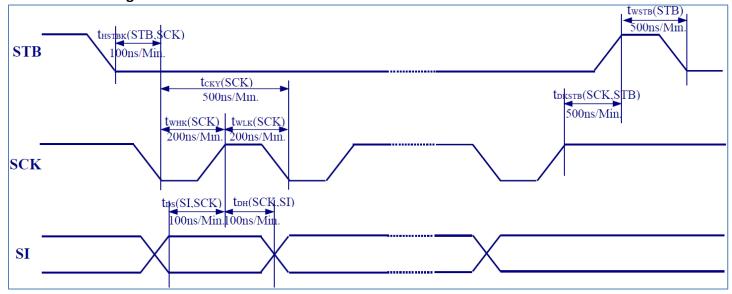

#### **Serial Write Timing:**

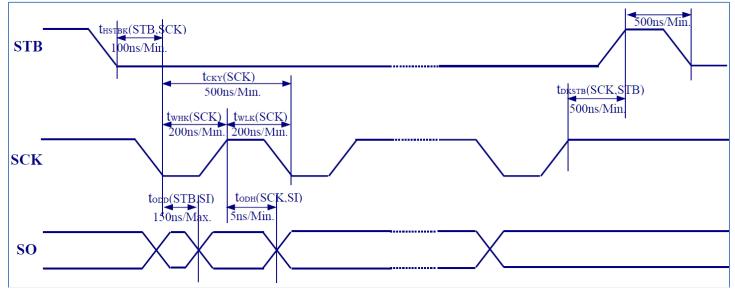

#### **Serial Read Timing:**

# **Built-in Font Table**

|           |     | 1 | Uppe | r D7 | 0              | 0 | 0 | 0   | 0   | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

|-----------|-----|---|------|------|----------------|---|---|-----|-----|---|---|---|---|---|---|---|---|---|---|---|

| $\square$ |     |   | ibbb | _    | 0              | 0 | ő | ő   | 1   | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| Lo        | wei |   |      | D5   | ŏ              | ŏ | ľ | 1 I | ô   | Ô | î | î | ŏ | ŏ | 1 | 1 | ô | ô | î | î |

|           | ble |   | /    | D4   | Ő              | ĩ | Ô | 1   | ů ů | ů | Ô | 1 | ő | 1 | ô | î | ŏ | 1 | Ô | î |

|           | _   | _ | 1 D  | 1    | 0              | 1 | 2 | 3   | 4   | 5 | 6 | 7 | 8 | 9 | Å | B | č | D | Ē | F |

| <b>—</b>  | 0   |   |      |      | CG-RAM         |   |   |     |     |   |   |   |   |   |   |   |   |   |   |   |

| Ľ         | _   |   |      | ľ    | (#1)           |   |   |     |     |   |   |   |   |   |   |   |   |   |   |   |

| 0         | 0   | 0 | ) 1  | 1    | CG-RAM<br>(#2) |   |   |     |     |   |   |   |   |   |   |   |   |   |   |   |

| 0         | 0   | 1 | 0    | 2    | CG-RAM<br>(∦3) |   |   |     |     |   |   |   |   |   |   |   |   |   |   |   |

| 0         | 0   | 1 | 1    | 3    | CG-RAM<br>(∦4) |   |   |     |     |   |   |   |   |   |   |   |   |   |   |   |

| 0         | 1   | 0 | ) () | 4    | CG-RAM<br>(#5) |   |   |     |     |   |   |   |   |   |   |   |   |   |   |   |

| 0         | 1   | 0 | ) 1  | 5    | CG-RAM<br>(∦6) |   |   |     |     |   |   |   |   |   |   |   |   |   |   |   |

| 0         | 1   | 1 | 0    | 6    | CG-RAM<br>(#7) |   |   |     |     |   |   |   |   |   |   |   |   |   |   |   |

| 0         | 1   | 1 | 1    | 7    | CG-RAM<br>(#8) |   |   |     |     |   |   |   |   |   |   |   |   |   |   |   |

| 1         | 0   | 0 | 0    | 8    | CG−RAM<br>(#1) |   |   |     |     |   |   |   |   |   |   |   |   |   |   |   |

| 1         | 0   | 0 | ) 1  | 9    | CG-RAM<br>(#2) |   |   |     |     |   |   |   |   |   |   |   |   |   |   |   |

| 1         | 0   | 1 | 0    | A    | CC-RAM<br>(#3) |   |   |     |     |   |   |   |   |   |   |   |   |   |   |   |

| 1         | 0   | 1 | 1    | в    | CG-RAM<br>(#4) |   |   |     |     |   |   |   |   |   |   |   |   |   |   |   |

| 1         | 1   | 0 | ) () | С    | CG-RAM<br>(#5) |   |   |     |     |   |   |   |   |   |   |   |   |   |   |   |

| 1         | 1   | 0 | ) 1  | D    | CG-RAM<br>(#6) |   |   |     |     |   |   |   |   |   |   |   |   |   |   |   |

| 1         | 1   | 1 | . 0  | E    | CG-RAM<br>(#7) |   |   |     |     |   |   |   |   |   |   |   |   |   |   |   |

| 1         | 1   | 1 | 1    | F    | CG-RAM<br>(#8) |   |   |     |     |   |   |   |   |   |   |   |   |   |   |   |

# **Example Initialization Sequence**

| RS   | R/W    | DB7     | DB6    | DB5  | DB4    | DB3    | DB2    | DB1    | DB0    | Description                                                                                 |  |  |  |  |  |

|------|--------|---------|--------|------|--------|--------|--------|--------|--------|---------------------------------------------------------------------------------------------|--|--|--|--|--|

|      |        |         |        | Powe | er ON  |        |        |        |        | Wait for 100 us                                                                             |  |  |  |  |  |

| 0    | 0      | 0       | 0      | 1    | 1      | 1      | *      | 0      | 0      | Function set:<br>- Data length: 8 bits<br>- Display line No.: 2 lines<br>- Brightness: 100% |  |  |  |  |  |

| 0    | 0      | 0       | 1      | 0    | 0      | 0      | 0      | 0      | 0      | CG-RAM address set to 00H                                                                   |  |  |  |  |  |

| 1    | 0      | *       | *      | *    | D<br>D | D<br>D | D<br>D | D<br>D | D<br>D | Writes data into CG-RAM (the user-definable characters)                                     |  |  |  |  |  |

|      |        |         |        |      |        |        |        |        |        | 64 bytes in total (8 characters)                                                            |  |  |  |  |  |

|      |        | *       | *      | *    | D      | D      | D      | D      | D      |                                                                                             |  |  |  |  |  |

| 0    | 0      | 1       | 0      | 0    | 0      | 0      | 0      | 0      | 0      | DD-RAM address set to 00H (the first column of upper line)                                  |  |  |  |  |  |

|      |        | D       | D      | D    | D      | D      | D      | D      | D      | Writes data into DD DANG (shares the sharester as don to                                    |  |  |  |  |  |

| 1    | 0      | D       | D      | D    | D      | D      | D      | D      | D      | Writes data into DD-RAM (choose the character codes to display in upper line)               |  |  |  |  |  |

| 1    | •      |         |        |      |        |        |        |        |        | Totally 20 bytes in the upper line (20 characters)                                          |  |  |  |  |  |

|      |        | D       | D      | D    | D      | D      | D      | D      | D      |                                                                                             |  |  |  |  |  |

| 0    | 0      | 1       | 1      | 0    | 0      | 0      | 0      | 0      | 0      | DD-RAM address set to 40H (the first column of lower line)                                  |  |  |  |  |  |

|      |        | D       | D      | D    | D      | D      | D      | D      | D      |                                                                                             |  |  |  |  |  |

| 1    | 0      | D       | D      | D    | D      | D      | D      | D      | D      | Writes data into DD-RAM (choose the character codes to                                      |  |  |  |  |  |

| 1    | 0      |         |        |      | -      |        |        |        |        | display in lower line)<br>Totally 20 bytes in the lower line (20 characters)                |  |  |  |  |  |

|      |        | D       | D      | D    | D      | D      | D      | D      | D      | Totany 20 bytes in the lower line (20 characters)                                           |  |  |  |  |  |

| 0    | 0      | 0       | 0      | 0    | 0      | 1      | 1      | 0      | 0      | Display ON, Cursor OFF, Cursor blink OFF                                                    |  |  |  |  |  |

| *Noi | te): L | ) is th | he bii | nary | data   | to be  | writ   | ten-ir | n.     |                                                                                             |  |  |  |  |  |

| Pov  | ver (  | ON      | ⊨⇒`    | > Fu | unctio | n Se   | et⊏    | ⇒      | CG-    | RAM Address Set CG-RAM Data Define                                                          |  |  |  |  |  |

|      |        |         | _      |      |        | _      | _      |        |        |                                                                                             |  |  |  |  |  |

Display ON/OFF Character Code Write-in DD-RAM Address Set

## **Quality Information**

| Test Item                | Content of Test                             | Test Condition                 | Note |

|--------------------------|---------------------------------------------|--------------------------------|------|

| High Temperature storage | Endurance test applying the high            | +80°C , 48hrs                  | 2    |

|                          | storage temperature for a long time.        |                                |      |

| Low Temperature storage  | Endurance test applying the low storage     | -30°C , 48hrs                  | 1,2  |

|                          | temperature for a long time.                |                                |      |

| High Temperature         | Endurance test applying the electric stress | +70°C 48hrs                    | 2    |

| Operation                | (voltage & current) and the high thermal    |                                |      |

|                          | stress for a long time.                     |                                |      |

| Low Temperature          | Endurance test applying the electric stress | -20°C , 48hrs                  | 1,2  |

| Operation                | (voltage & current) and the low thermal     |                                |      |

|                          | stress for a long time.                     |                                |      |

| High Temperature /       | Endurance test applying the electric stress | +40°C , 90% RH , 48hrs         | 1,2  |

| Humidity Operation       | (voltage & current) and the high thermal    |                                |      |

|                          | with high humidity stress for a long time.  |                                |      |

| Thermal Shock resistance | Endurance test applying the electric stress | 0°C,30min -> +25°C,5min ->     |      |

|                          | (voltage & current) during a cycle of low   | +50°C,30min = 1 cycle          |      |

|                          | and high thermal stress.                    | 10 cycles                      |      |

| Vibration test           | Endurance test applying vibration to        | 10-55Hz , 15mm amplitude.      | 3    |

|                          | simulate transportation and use.            | 60 sec in each of 3 directions |      |

|                          |                                             | X,Y,Z                          |      |

|                          |                                             | For 15 minutes                 |      |

| Static electricity test  | Endurance test applying electric static     | VS=800V, RS=1.5kΩ, CS=100pF    |      |

|                          | discharge.                                  | One time                       |      |

Note 1: No condensation to be observed.

Note 2: Conducted after 4 hours of storage at 25°C, 0%RH.

Note 3: Test performed on product itself, not inside a container.

# Precautions for using LCDs/LCMs

See Precautions at <a href="http://www.newhavendisplay.com/specs/precautions.pdf">www.newhavendisplay.com/specs/precautions.pdf</a>

### Warranty Information and Terms & Conditions

http://www.newhavendisplay.com/index.php?main\_page=terms

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Newhaven Display: M0220MD-202MDAR1-3