# **CEL** California Eastern Laboratories

**Evaluation Board Document**

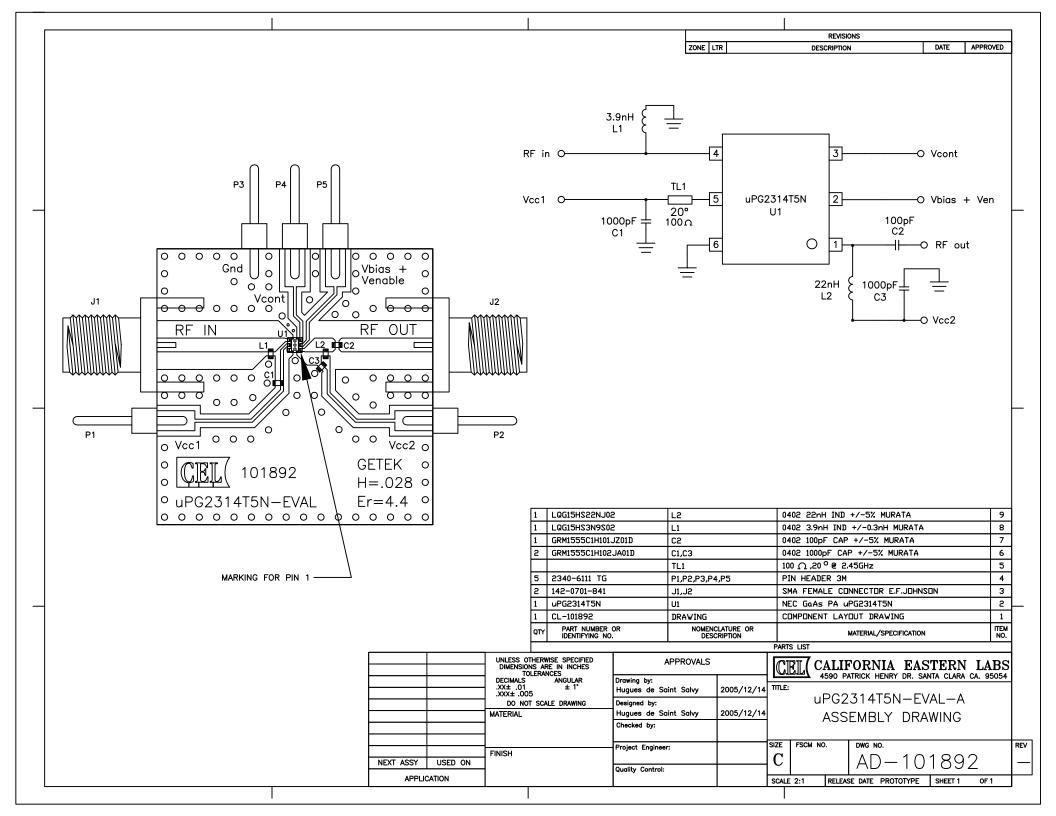

## µPG2314T5N-EVAL-A

## **Evaluation Board**

- Bias and Matching Circuits

- Output Power Control

- PCB Information

- Typical Performance

- o Schematic and Assembly Drawing

#### **Matching and Bias Circuits**

As shown in the circuit schematic on the next page, the uPG2314T5N requires relatively simple matching circuits. The inductor L1 is for input matching and should be placed close to the device. At the output essentially no matching circuit is required. L2 functions as an RF choke and C2 is DC block capacitor.

The uPG2314T5N is a two stage PA. The first stage bias is through Vcc1. A small section of transmission line between the device and the bypass capacitor, C1, is needed to provide enough isolation between RF and DC paths.

#### **Output Power Control**

The output power of uPG2314T5N can be adjusted by the voltage on Vcont pin. The control curve is shown on the data sheet. To turn off the PA, Vbias+Venable pin should be set to 0V.

#### **PCB** Information

The PCB is Getek two layer board. The board thickness is 28mil.

#### **Typical Performance**

Refer to the data sheet for typical performance curves.

### **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

CEL: UPG2314T5N-EVAL-A