### **Product Description**

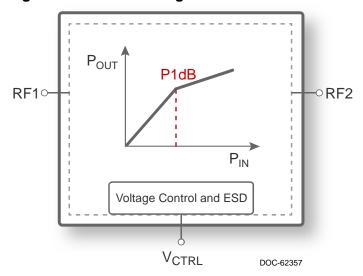

The PE45140 is a HaRP™ technology-enhanced RF power limiter designed for use in tactical and military communications receivers, land mobile radio and other high performance power limiting applications.

Unlike traditional PIN diode solutions the limiting threshold can be adjusted through a low current control voltage (V<sub>CTRL</sub>), eliminating the need for external components such as DC blocking capacitors, RF choke inductors, and bias resistors.

This power limiter has symmetric RF ports that limit incident power up to 50W pulsed in both biased and unbiased conditions. It provides an extremely fast limiting response to undesired high power signals while delivering low insertion loss and high linearity under safe operating power levels.

The PE45140 is manufactured on Peregrine's UltraCMOS® process, a patented variation of silicon-oninsulator (SOI) technology on a sapphire substrate.

Peregrine's HaRP™ technology enhancements deliver high linearity and excellent harmonics performance. It is an innovative feature of the UltraCMOS process, offering the performance of GaAs with the economy and integration of conventional CMOS.

Figure 1. Functional Diagram

# **Product Specification**

# PE45140

# UltraCMOS® Power Limiter 20 MHz-2 GHz

#### **Features**

- Monolithic drop in solution with no external components required

- Adjustable power limiting threshold from +22 dBm to +32 dBm

- Max power handling

- +47 dBm Pulsed (50W)

- +40 dBm CW (10W)

- Superior ESD rating and ESD protection

- 8 kV HBM on RF pins to GND

- 1 kV CDM on all pins

- 200V MM on all pins

- Unbiased power limiting operation

- Fast response and recovery time of 1 ns

- Dual mode operation

- Power limiting mode

- Power reflecting mode

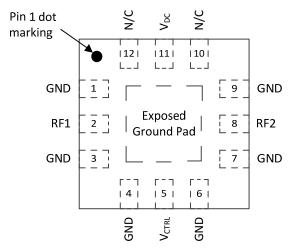

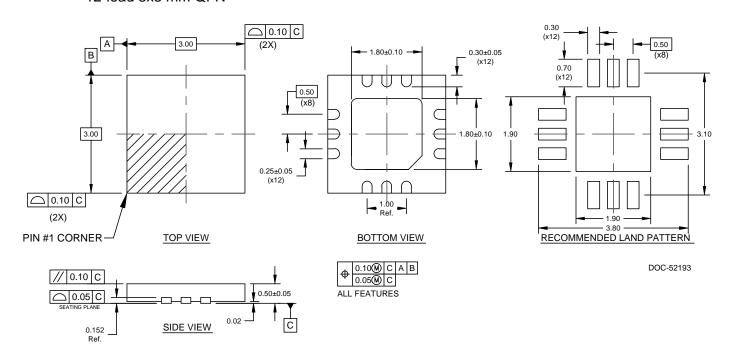

Figure 2. Package Type 12-lead 3x3 mm QFN

# Table 1. Electrical Specifications @ +25°C ( $Z_S = Z_L = 50\Omega$ ), unless otherwise noted

| Parameter                           | Condition                                                                  | Min | Тур          | Max          | Unit       |

|-------------------------------------|----------------------------------------------------------------------------|-----|--------------|--------------|------------|

| Operating frequency                 |                                                                            | 20  |              | 2000         | MHz        |

| Power limiting mode                 | ·                                                                          | ·   |              |              |            |

| Insertion loss                      | 20 MHz–1 GHz<br>1–2 GHz                                                    |     | 0.20<br>0.60 | 0.45<br>1.00 | dB<br>dB   |

| Return loss                         | 20 MHz–1 GHz<br>1–2 GHz                                                    |     | 16<br>10     |              | dB<br>dB   |

| P1dB / limiting threshold           | V <sub>CTRL</sub> = -2.5V @ 915 MHz<br>V <sub>CTRL</sub> = -0.5V @ 915 MHz |     | 32<br>22     |              | dBm<br>dBm |

| Leakage power <sup>1</sup>          | V <sub>CTRL</sub> = -2.5V @ 915 MHz<br>V <sub>CTRL</sub> = -0.5V @ 915 MHz |     | 31.5<br>29   | 34<br>31.5   | dBm<br>dBm |

| Leakage power slope                 | V <sub>CTRL</sub> = -1.0V @ 915 MHz                                        |     | 0.4          |              | dB/dB      |

| Unbiased leakage power <sup>1</sup> | V <sub>CTRL</sub> = 0V                                                     |     | 23.5         | 27           | dBm        |

| Input IP2                           | V <sub>CTRL</sub> = −2.5V @ 915 MHz                                        |     | 104          |              | dBm        |

| Input IP3                           | V <sub>CTRL</sub> = −2.5V @ 915 MHz                                        |     | 64           |              | dBm        |

| Response / recovery time            | 1 GHz                                                                      |     | 1            |              | ns         |

| Power reflecting mode <sup>2</sup>  |                                                                            | ·   |              |              |            |

| Leakage power <sup>1</sup>          | V <sub>CTRL</sub> = +2.5V @ 915 MHz                                        |     | -1           | 4.5          | dBm        |

| Switching time <sup>3</sup>         | State change to 10% RF                                                     |     | 390          |              | μs         |

Notes: 1. Measured with +40 dBm CW applied at input.

<sup>2.</sup> This mode requires the control voltage to toggle between +2.5V and -2.5V. At +2.5V, the limiter equivalent circuit is a low impedance to ground, reflecting most of the incident power back to the source.

3. State change is V<sub>CTRL</sub> toggle from –2.5V to +2.5V.

Figure 3. Pin Configuration (Top View)

Table 2. Pin Descriptions

| Pin No.             | Pin Name          | Description                              |

|---------------------|-------------------|------------------------------------------|

| 1, 3, 4, 6,<br>7, 9 | GND               | Ground                                   |

| 2                   | RF1*              | RF port 1                                |

| 5                   | V <sub>CTRL</sub> | Control                                  |

| 8                   | RF2*              | RF port 2                                |

| 10, 12              | N/C               | No connect                               |

| 11                  | $V_{DC}$          | DC voltage                               |

| Pad                 | GND               | Exposed pad: Ground for proper operation |

RF pins 2 and 8 must be at 0 VDC. The RF pins do not require DC Note: \* blocking capacitors for proper operation if the 0 VDC requirement is

#### Latch-Up Avoidance

Unlike conventional CMOS devices, UltraCMOS devices are immune to latch-up.

#### **Moisture Sensitivity Level**

The Moisture Sensitivity Level rating for the PE45140 in the 12-lead 3x3 mm QFN package is MSL1.

**Table 3. Operating Ranges**

| Parameter                                                 | Symbol                  | Min          | Тур | Max          | Unit   |

|-----------------------------------------------------------|-------------------------|--------------|-----|--------------|--------|

| DC voltage                                                | $V_{DC}$                | 2.5          |     | 3.3          | V      |

| Control voltage Power limiting mode Power reflecting mode | V <sub>CTRL</sub>       | -2.5<br>-2.5 |     | -0.5<br>+2.5 | V<br>V |

| RF input power, CW <sup>1</sup>                           | P <sub>MAX,CW</sub>     |              |     | 40           | dBm    |

| RF input power, pulsed <sup>2</sup>                       | P <sub>MAX,PULSED</sub> |              |     | 47           | dBm    |

| RF input power, unbiased <sup>2,3</sup>                   | P <sub>MAX,UNB</sub>    |              |     | 47           | dBm    |

| Operating temperature range                               | T <sub>OP</sub>         | <b>-</b> 55  | +25 | +85          | °C     |

| Operating junction temperature <sup>1</sup>               | TJ                      |              |     | +270         | °C     |

Notes: 1. CW, 100% duty cycle, in 10 min,  $50\Omega$

2. Pulsed, 0.1% duty cycle of 1  $\mu s$  pulse width in 10 min,  $50\Omega$

3.  $V_{CTRL} = 0V$  or  $V_{CTRL}$  pin left not connected

Table 4. Absolute Maximum Ratings

| Parameter                                                 | Symbol               | Min  | Max          | Unit |

|-----------------------------------------------------------|----------------------|------|--------------|------|

| DC voltage                                                | $V_{DC}$             | -0.3 | 3.6          | V    |

| Control voltage Power limiting mode Power reflecting mode | V <sub>CTRL</sub>    | -3.3 | 3.6          | V    |

| Storage temperature range                                 | T <sub>ST</sub>      | -65  | +150         | °C   |

| ESD voltage HBM <sup>1</sup> All pins RF pins to GND      | V <sub>ESD,HBM</sub> |      | 7000<br>8000 | V    |

| ESD voltage MM <sup>2</sup> , all pins                    | V <sub>ESD,MM</sub>  |      | 200          | V    |

| ESD voltage CDM <sup>3</sup> , all pins                   | $V_{ESD,CDM}$        |      | 1000         | V    |

Notes: 1. Human Body Model (HBM, MIL\_STD 883 Method 3015.7)

2. Machine Model (JEDEC JESD22-A115)

3. Charged Device Model (JEDEC JESD22-C101)

Exceeding absolute maximum ratings may cause permanent damage. Operation should be restricted to the limits in the Operating Ranges table. Operation between operating range maximum and absolute maximum for extended periods may reduce reliability.

#### **Electrostatic Discharge (ESD) Precautions**

When handling this UltraCMOS device, observe the same precautions that you would use with other ESD-sensitive devices. Although this device contains circuitry to protect it from damage due to ESD, precautions should be taken to avoid exceeding the rating specified.

#### **ESD Protection Capability**

The PE45140 has the unique capability of being used as a voltage clamp in the event of an ESD strike. Clamping the output voltage can protect devices that follow from ESD damage and enable overall system ESD ratings to be increased.

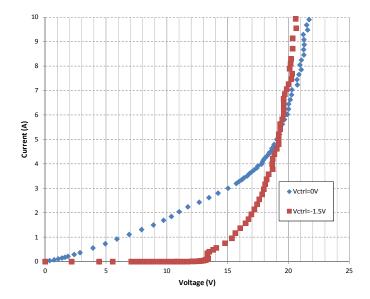

The PE45140's ESD protection capability under biased and unbiased conditions is observed with a Transmission Line Pulse (TLP) measurement characterizing the product as an ESD clamp from each RF port to ground.

Table 5. Transmission Line Pulse Data vs. HBM

| V <sub>CTRL</sub> | HBM (V) | Max Current (A) | Voltage (V) |

|-------------------|---------|-----------------|-------------|

| 0                 | 1000    | 0.7             | 4.5         |

| -1.5              | 1000    | 0.7             | 14.5        |

| 0                 | 2000    | 1.3             | 8           |

| -1.5              | 2000    | 1.3             | 16          |

| 0                 | 3000    | 2.0             | 11          |

| -1.5              | 3000    | 2.0             | 17          |

Figure 4. Transmission Line Pulse Measurement

#### **Dual Mode Operation**

#### Power Limiting Mode

The PE45140 performs as a linear power limiter with adjustable P1dB / limiting threshold. The P1dB / limiting threshold can be adjusted by changing the control voltage between -2.5V and -0.5V. If unbiased, or if  $V_{CTRL} = 0V$ , the PE45140 still offers power limiting protection.

#### Power Reflecting Mode

Power reflecting mode requires a power detector to sample the RF input power and a microcontroller to toggle the limiter control voltage between +2.5V and -2.5V based on the system protection requirements. At +2.5V, the limiter impedance to ground is less than  $1\Omega$  and most of the incident power will be reflected back to the source. At -2.5V, the device operates as in power limiting mode.

#### **Thermal Data**

When limiting high power RF signals, the junction temperature of the power limiter can rise significantly.

Special consideration needs to be made in the design of the PCB to properly dissipate the heat away from the part and maintain the +270°C maximum junction temperature.

It is recommended to use best design practices for high power QFN packages: multi-layer PCBs with thermal vias in a thermal pad soldered to the slug of the package. Special care also needs to be made to alleviate solder voiding under the part.

Table 5. Theta JC

| Parameter | Min | Тур | Max | Unit |

|-----------|-----|-----|-----|------|

| Theta JC  |     | 16  |     | °C/W |

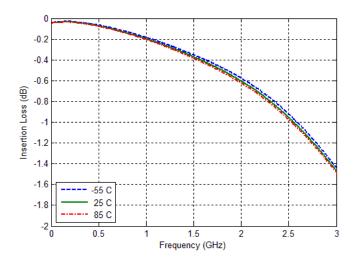

### Typical Performance Data @ +25°C ( $Z_S = Z_L = 50\Omega$ ), unless otherwise noted

## Figure 5. Insertion Loss vs. Temperature

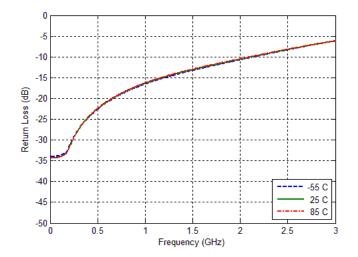

Figure 6. Input Return Loss vs. Temperature

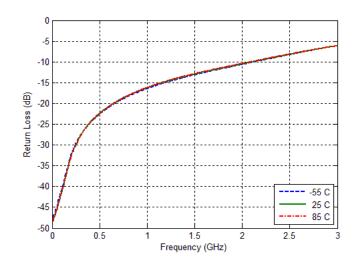

Figure 7. Output Return Loss vs. Temperature

## Typical Performance Data @ +25°C, 915 MHz ( $Z_S = Z_L = 50\Omega$ ), unless otherwise noted

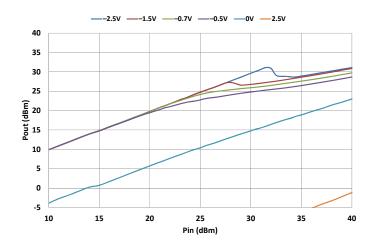

Figure 8. Pout vs. PIN Over VCTRL

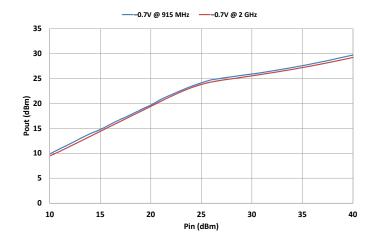

Figure 9.  $P_{OUT}$  vs.  $P_{IN}$  Over Frequency @  $V_{CTRL} = -0.7V$

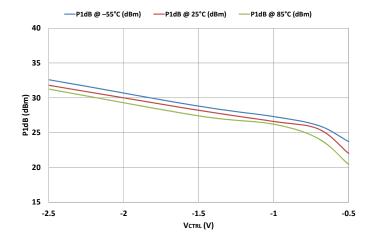

Figure 10. P1dB vs. V<sub>CTRL</sub> Over Temperature

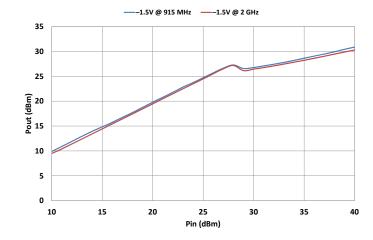

Figure 11. P<sub>OUT</sub> vs. P<sub>IN</sub> Over Frequency @  $V_{CTRL} = -1.5V$

### Typical Performance Data @ +25°C, 915 MHz ( $Z_S = Z_L = 50\Omega$ ), unless otherwise noted

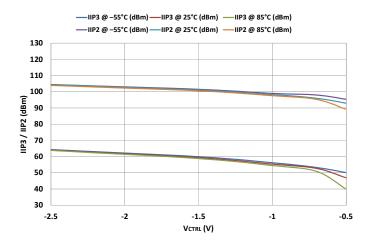

# Figure 12. IIP3 / IIP2 vs. $V_{\text{CTRL}}$ Over Temperature

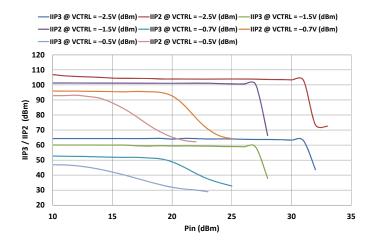

Figure 13. IIP3 / IIP2 vs. PIN Over VCTRL

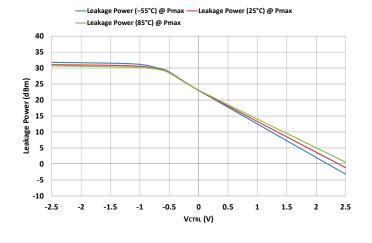

Figure 14. Leakage Power @ P<sub>MAX</sub> vs. V<sub>CTRL</sub>

Over Temperature

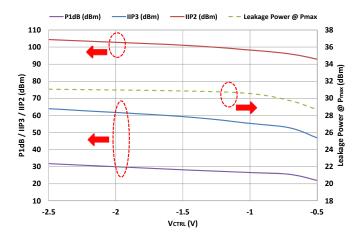

Figure 15. P1dB, IIP3, IIP2, Leakage Power @ P<sub>MAX</sub> vs. V<sub>CTRL</sub>

#### **Evaluation Kit**

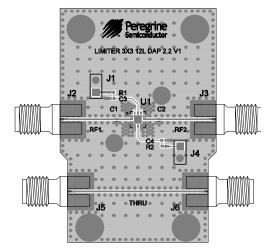

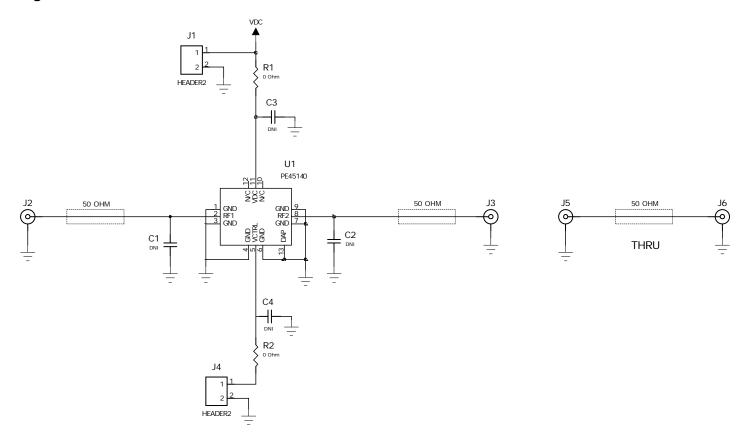

The power limiter EVK board was designed to ease customer evaluation of Peregrine's PE45140. The bi-directional RF input and output are connected to RF1 and RF2 port through a 50Ω transmission line via SMA connectors J2 and J3. A through 50Ω transmission line is available via SMA connectors J5 and J6. This transmission line can be used to estimate the loss of the PCB over the environmental conditions being evaluated. The 2-pin connectors J1 and J4 are connected to the external DC voltage V<sub>DC</sub> and V<sub>CTRL</sub>, respectively.

The board is constructed of a four metal layer material with a total thickness of 62 mils. The top RF layer is Rogers RO4350B material with a 6.6 mil RF core and Er = 3.66. The middle layers provide ground for the transmission lines. The transmission lines were designed using a coplanar waveguide with ground plane model using a trace width of 13.5 mils, trace gaps of 10 mils, and metal thickness of 2.1 mils.

Figure 16. Evaluation Board Layout

PRT-51452

# Figure 17. Evaluation Board Schematic

Caution: Contains parts and assemblies susceptible to damage by electrostatic discharge (ESD)

DOC-44027

#### Figure 18. Package Drawing 12-lead 3x3 mm QFN

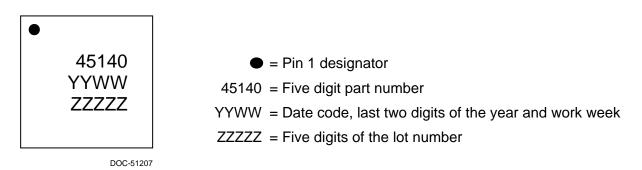

Figure 19. Top Marking Specifications

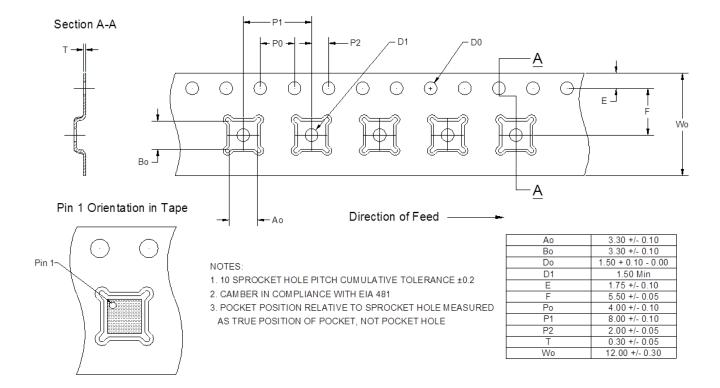

#### Figure 20. Tape and Reel Drawing

**Table 6. Ordering Information**

| Order Code | Description            | Package                  | Shipping Method |  |

|------------|------------------------|--------------------------|-----------------|--|

| PE45140A-X | PE45140 Power limiter  | Green 12-lead 3x3 mm QFN | 500 units / T&R |  |

| EK45140-02 | PE45140 Evaluation kit | Evaluation kit           | 1 / box         |  |

#### **Sales Contact and Information**

For sales and contact information please visit www.psemi.com.

Advance Information: The product is in a formative or design stage. The datasheet contains design target specifications for product development. Specifications and features may change in any manner without notice. Preliminary Specification: The datasheet contains preliminary data. Additional data may be added at a later date. Peregrine reserves the right to change specifications at any time without notice in order to supply the best possible product. Product Specification: The datasheet contains final data. In the event Peregrine decides to change the specifications, Peregrine will notify customers of the intended changes by issuing a CNF (Customer Notification Form).

The information in this datasheet is believed to be reliable. However, Peregrine assumes no liability for the use of this information. Use shall be entirely at the user's own risk.

No patent rights or licenses to any circuits described in this datasheet are implied or granted to any third party. Peregrine's products are not designed or intended for use in devices or systems intended for surgical implant, or in other applications intended to support or sustain life, or in any application in which the failure of the Peregrine product could create a situation in which personal injury or death might occur. Peregrine assumes no liability for damages, including consequential or incidental damages, arising out of the use of its products in such applications.

The Peregrine name, logo, UltraCMOS and UTSi are registered trademarks and HaRP, MultiSwitch and DuNE are trademarks of Peregrine Semiconductor Corp. Peregrine products are protected under one or more of the following U.S. Patents: <a href="http://patents.psemi.com">http://patents.psemi.com</a>.

Document No. DOC-44014-4 | UltraCMOS® RFIC Solutions

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

pSemi:

PE45140A-X EK45140-02