# 900V, Fixed-Frequency, Offline Regulator w/ Ultra-Low Standby Power Consumption

### **DESCRIPTION**

The HF920 is a flyback regulator with a monolithic, 900V MOSFET. The HF920 provides excellent power regulation in AC/DC applications that require high reliability, such as smart meters, large appliances, industrial controls, and products powered by poor AC grids. The HF920 requires a minimal number of external components.

The HF920 uses peak-current-mode control to provide excellent transient response and easy loop compensation. When the output power falls below a given level, the regulator enters burst mode. The IC consumption is also specially optimized. As a result, the HF920 achieves very low power consumption during standby conditions.

MPS's proprietary, 900V, monolithic process enables an over-temperature protection (OTP) that is on the same silicon as the 900V power MOSFET, offering the most precise thermal protection. The HF920 also offers a full suite of protection features such as VCC under-voltage lockout (UVLO), overload protection (OLP), over-voltage protection (OVP), and short-circuit protection (SCP).

The HF920 designed is to minimize electromagnetic interference for power line communications (PLC) in home and building automation applications. The operating frequency is programmed externally with a single resistor, so the power supply's radiated energy can be designed to block interference to the PLC. In addition to the programmable frequency, the HF920 employs frequency jittering that reduces the noise level and EMI filter cost greatly.

Frequency-doubling mode operation can be enabled through a simple external set-up. With this special operation mode, the switching frequency is doubled when the converter runs into an over-power condition. In this way, the converter is able to handle up to a 50% decrease of the transformer inductance caused by external magnetizing interference.

### **FEATURES**

- Monolithic 900V/15Ω MOSFET and High-Voltage Current Source

- Fixed Switching Frequency, Programmable up to 150kHz

- Current-Mode Control Scheme

- Frequency Jittering

- Low Standby Power Consumption via Active Burst Mode

- <30mW No-Load Consumption</li>

- Frequency Doubling Operation Mode

- Internal Leading-Edge Blanking (LEB)

- Built-In Soft-Start (SS) Function

- Internal Slope Compensation

- External Input PRO Pin Protection with Hysteresis and Auto-Restart Recovery

- Over-Temperature Protection (OTP)

- VCC Under-Voltage Lockout (UVLO) with Hysteresis

- Over-Voltage Protection (OVP) on VCC

- Time-Based Overload Protection (OLP)

- Short-Circuit Protection (SCP)

- Available in SOIC8-7A and SOIC14-11 Packages

### **APPLICATIONS**

- E-Meters

- Industrial Controls

- Large Appliances

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems. Inc.

**Table 1: Maximum Output Power**

| Dookogo   | P <sub>MAX</sub> (W) |            |  |  |

|-----------|----------------------|------------|--|--|

| Package   | 85Vac~420Vac         | 230Vac±15% |  |  |

| SOIC8-7A  | 6.5                  | 9.5        |  |  |

| SOIC14-11 | 7                    | 10         |  |  |

### NOTES:

- The maximum output power is limited by junction temperature.

- Test is done under T<sub>A</sub> = 50°C. The test board is placed into a box about 20cm\*15cm\*10cm.

- To reduce V<sub>DS</sub>, the turns ratio is set to 5.

- Single output, V<sub>OUT</sub> = 12.5V.

- GND of the SOIC8-7A package is connected to a 3cm<sup>2</sup> copper area with exposed copper strips. GND of the SOIC14-11 package is connected to a 2.5cm<sup>2</sup> copper area.

- Working condition under minimum input voltage is set to BCM.

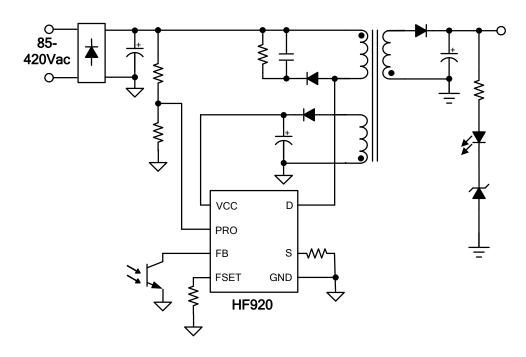

# **TYPICAL APPLICATION**

### ORDERING INFORMATION

| Part Number | Package   | Top Marking |  |

|-------------|-----------|-------------|--|

| HF920GSE*   | SOIC8-7A  | See Below   |  |

| HF920GS**   | SOIC14-11 | See Below   |  |

<sup>\*</sup> For Tape & Reel, add suffix -Z (e.g.: HF920GSE-Z)

# **TOP MARKING (HF920GSE)**

HF920 LLLLLLLL

**MPSYWW**

HF920: Part number LLLLLLL: Lot number MPS: MPS prefix Y: Year code WW: Week code

# **TOP MARKING (HF920GS)**

MP<u>SYYWW</u> HF920 LLLLLLLL

MPS: MPS prefix YY: Year code WW: Week code HF920: Part number LLLLLLLL: Lot number

<sup>\*\*</sup> For Tape & Reel, add suffix –Z (e.g.: HF920GS–Z)

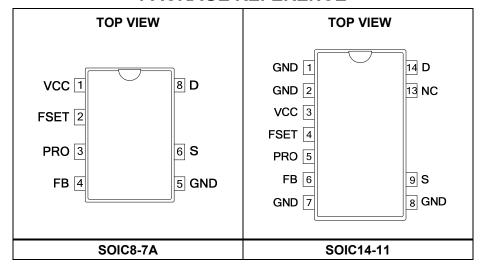

### **PACKAGE REFERENCE**

| Thermal Resistance (4) | $oldsymbol{	heta}_{JA}$ | $oldsymbol{	heta}_{JC}$ |      |

|------------------------|-------------------------|-------------------------|------|

| SOIC8-7A               | 96                      | 45                      | °C/W |

| SOIC14-11              | 70                      | 35                      | °C/W |

### NOTES:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-to-ambient thermal resistance θ<sub>JA</sub>, and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX)-T<sub>A</sub>)/θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

VCC = 12V,  $T_J$  = -40°C to 125°C, min and max values are guaranteed by characterization, typical values are tested under 25°C, unless otherwise noted.

| Parameter                    | Symbol                                              | Conditions                 |                                 | Min  | Тур  | Max  | Unit     |

|------------------------------|-----------------------------------------------------|----------------------------|---------------------------------|------|------|------|----------|

|                              | Start-Up Current Source and Internal MOSFET (D Pin) |                            |                                 |      |      |      |          |

| Supply current from drain    | I <sub>Charge</sub>                                 | VCC = V <sub>CCH</sub> - 0 |                                 | 1    | 2    | 3    | mA       |

| Leakage current from drain   | I <sub>Leak</sub>                                   |                            | = 0V, T <sub>J</sub> = 25°C     |      |      | 1    | μA       |

| Leakage current from drain   | ILeak                                               | $V_D = 400V, V_{GS}$       |                                 |      |      | 10   | μΑ       |

| Breakdown voltage            | V <sub>(BR)DSS</sub>                                | 15 1001, 100               |                                 | 900  |      |      | V        |

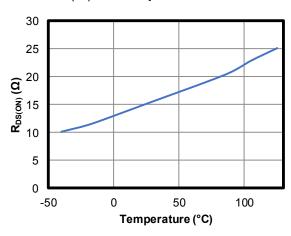

|                              |                                                     | VCC = 10V,                 | T <sub>J</sub> = 25°C           |      | 15   | 18   | Ω        |

| On-state resistance          | R <sub>DS(ON)</sub>                                 | I <sub>D</sub> = 100mA     | T <sub>J</sub> = 125°C          |      | 25   | 29   | Ω        |

| Supply Voltage Management    | nt (VCC Pi                                          | n)                         |                                 |      |      |      |          |

| VCC upper level at which     | V <sub>CCH</sub>                                    |                            |                                 | 12   | 13   | 14   | V        |

| the IC switch turns on       | V CCH                                               |                            |                                 | 12   | 10   | 17   | V        |

| VCC lower level at which     | V <sub>CCL</sub>                                    |                            |                                 | 8.4  | 9    | 9.6  | V        |

| the IC switch turns off      | V CCL                                               |                            |                                 | 0.4  | J    | 0.0  |          |

| VCC hysteresis               | Vcc_hys                                             |                            |                                 | 3    | 4    | 5    | V        |

| VCC OVP level                | V <sub>OVP</sub>                                    |                            |                                 | 24.4 | 25.5 | 26.5 | V        |

| VCC OVP delay time           | tovp                                                |                            |                                 |      | 70   |      | μs       |

| VCC recharge level after     | Vccr                                                |                            |                                 | 4.8  | 5.5  | 6.2  | V        |

| protections                  | V CCR                                               |                            |                                 | 4.0  | 5.5  | 0.2  | V        |

| Quiescent current during     | I <sub>Pro</sub>                                    | VCC = V <sub>CCL</sub>     |                                 |      |      | 300  | μΑ       |

| protections                  | IPro                                                |                            |                                 |      |      |      | μΛ       |

| Quiescent current            | IQ                                                  | VCC = V <sub>CCH</sub> - 0 |                                 |      | 200  | 300  | μA       |

| Operation current            | Icc                                                 | VCC =13V, f <sub>S</sub> = |                                 |      | 510  | 610  | μA       |

| •                            |                                                     | VCC = 13V, FB              | = 0V                            |      | 300  | 400  | μA       |

| Feedback Management (FB      |                                                     |                            |                                 |      |      |      |          |

| Internal pull-up resistor    | $R_{FB}$                                            | Normal operatir            | ng                              |      | 39   |      | kΩ       |

| Internal pull-up voltage     | $V_{UP}$                                            |                            |                                 | 4.1  | 4.4  | 4.7  | <b>V</b> |

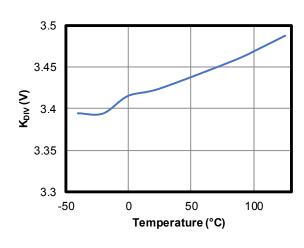

| FB to current-set-point      | K <sub>div</sub>                                    |                            |                                 |      | 3.4  | 3.7  |          |

| division ratio               | rvaiv                                               |                            |                                 |      |      | 3.7  |          |

| Internal soft-start time     | tss                                                 |                            |                                 |      | 6.7  |      | ms       |

| FB decreasing level at       |                                                     |                            |                                 |      |      |      |          |

| which the regulator enters   | $V_{BURL}$                                          |                            |                                 | 0.4  | 0.5  | 0.6  | V        |

| burst mode                   |                                                     |                            |                                 |      |      |      |          |

| FB increasing level at       |                                                     |                            |                                 |      |      |      |          |

| which the regulator leaves   | V <sub>BURH</sub>                                   |                            |                                 | 0.6  | 0.7  | 8.0  | V        |

| burst mode                   |                                                     |                            |                                 |      |      |      |          |

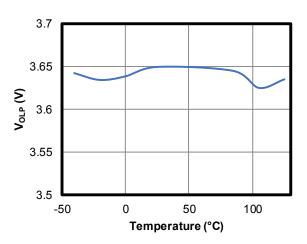

| Overload set point           | Volp                                                |                            |                                 | 3.3  | 3.65 | 4    | V        |

| Overload counter             |                                                     |                            |                                 |      | 8192 |      |          |

| Threshold for frequency to   | $V_{FR}$                                            | C <sub>FSET</sub> = 1nF    |                                 | 2.85 | 3    | 3.15 | V        |

| recover                      | VIIX                                                | OTSET TIME                 |                                 |      |      | 0.10 | •        |

| Frequency doubling entry/    |                                                     | C <sub>FSET</sub> = 1nF    |                                 |      | 31   |      |          |

| recovery counter             |                                                     | OFSET TITE                 |                                 |      | 01   |      |          |

| Frequency Setting (FSET Pin) |                                                     |                            |                                 |      |      |      |          |

| FSET reference voltage       | $V_{FSET}$                                          |                            |                                 | 1.18 | 1.25 | 1.32 | V        |

| Frequency spectrum           |                                                     |                            |                                 |      | _    |      |          |

| jittering range, in          | RJittering                                          |                            |                                 |      | ±3.5 |      | %        |

| percentage of Fs             |                                                     |                            |                                 |      | 4.5  |      |          |

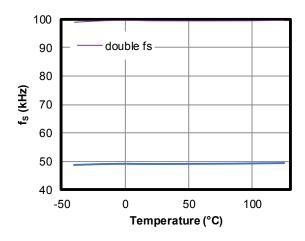

| Typical operating            |                                                     | $R_{FSET} = 200k\Omega$    |                                 | 43   | 49   | 55   |          |

| frequency                    | fs                                                  | $R_{FSET} = 200k\Omega$ ,  | $C_{\text{FSET}} = 1\text{nF},$ | 87   | 99   | 111  | kHz      |

|                              |                                                     | V <sub>FB</sub> = 3.5V     |                                 |      |      |      | 0.1      |

| Maximum switching duty       | D <sub>max</sub>                                    |                            |                                 | 79   | 83   | 87   | %        |

# **ELECTRICAL CHARACTERISTICS** (continued)

VCC = 12V, T<sub>J</sub> = -40°C to 125°C, min and max values are guaranteed by characterization, typical values are tested under 25°C, unless otherwise noted.

| Parameter                                | Symbol                             | Conditions              | Min  | Тур  | Max  | Unit  |  |

|------------------------------------------|------------------------------------|-------------------------|------|------|------|-------|--|

| <b>Current Sensing Manageme</b>          | Current Sensing Management (S Pin) |                         |      |      |      |       |  |

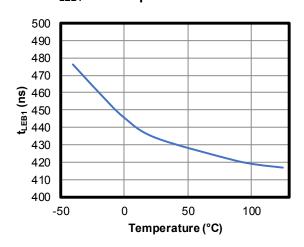

| Leading-edge blanking for current sensor | <b>t</b> LEB1                      |                         |      | 385  |      | ns    |  |

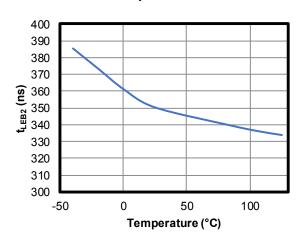

| Leading-edge blanking for SCP            | t <sub>LEB2</sub>                  |                         |      | 350  |      | ns    |  |

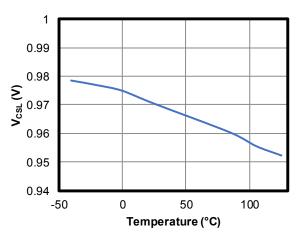

| Maximum current set point                | Vcsl                               |                         | 0.91 | 0.97 | 1.02 | V     |  |

| Short-circuit protection set point       | V <sub>SCP</sub>                   |                         | 1.43 | 1.5  | 1.57 | V     |  |

| Slope compensation ramp                  | S <sub>Ramp</sub>                  | $R_{FSET} = 200k\Omega$ |      | 21   |      | mV/μs |  |

| Protection Management (Pl                | RO Pin)                            |                         |      |      |      |       |  |

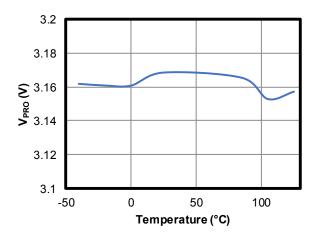

| Protection voltage                       | $V_{PRO}$                          |                         | 2.92 | 3.1  | 3.32 | V     |  |

| Protection hysteresis                    | V <sub>PRO-Hys</sub>               |                         |      | 0.2  |      | V     |  |

| Thermal Shutdown                         |                                    |                         |      |      |      |       |  |

| Thermal shutdown threshold (5)           |                                    |                         |      | 150  |      | °C    |  |

| Thermal shutdown recovery hysteresis (5) |                                    |                         |      | 30   |      | °C    |  |

### NOTE:

<sup>5)</sup> This parameter is guaranteed by design.

# **PIN FUNCTIONS**

| Pin #    |            | N.   | December 2011                                                                                                                                                                                                                                                                           |  |

|----------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SOIC8-7A | SOIC14-11  | Name | Description                                                                                                                                                                                                                                                                             |  |

| 1        | 3          | VCC  | <b>IC power supply.</b> Connect an electrolytic capacitor and a small ceramic decoupling capacitor to VCC.                                                                                                                                                                              |  |

| 2        | 4          | FSET | <b>Switching frequency setting.</b> Connect a resistor from FSET to GND to set the switching frequency, which can be up to 150kHz. FSET is also used for enabling frequency-doubling operation mode by placing a typical 1nF capacitor in parallel with the frequency-setting resistor. |  |

| 3        | 5          | PRO  | <b>External protection.</b> When pulled up, PRO shuts down the IC with a hysteresis.                                                                                                                                                                                                    |  |

| 4        | 6          | FB   | <b>Feedback.</b> The output voltage is regulated according to the feedback signal on FB. OLP detection and burst mode control are also performed on FB.                                                                                                                                 |  |

| 5        | 1, 2, 7, 8 | GND  | IC ground.                                                                                                                                                                                                                                                                              |  |

| 6        | 9          | S    | <b>Source of the internal MOSFET.</b> S is the input for the primary current-sense signal.                                                                                                                                                                                              |  |

| -        | 13         | NC   | No connection.                                                                                                                                                                                                                                                                          |  |

| 8        | 14         | D    | <b>Drain of the internal MOSFET.</b> D is the input for the start-up high voltage current source.                                                                                                                                                                                       |  |

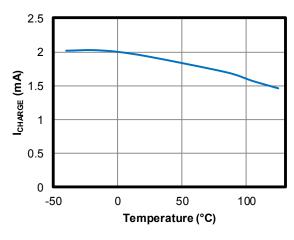

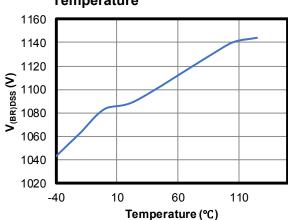

# **TYPICAL CHARACTERISTICS**

I<sub>charge</sub> @ V<sub>D</sub> = 400V vs. Temperature

$V_{(BR)DSS}$  @  $I_{Leak}$  = 100 $\mu$ A vs. Temperature

R<sub>DS(ON)</sub> vs. Temperature

V<sub>CSL</sub> vs. Temperature

K<sub>div</sub> vs. Temperature

V<sub>OLP</sub> vs. Temperature

# TYPICAL CHARACTERISTICS (continued)

fs vs. Temperature

t<sub>LEB1</sub> vs. Temperature

t<sub>LEB2</sub> vs. Temperature

**V<sub>PRO</sub> vs. Temperature**

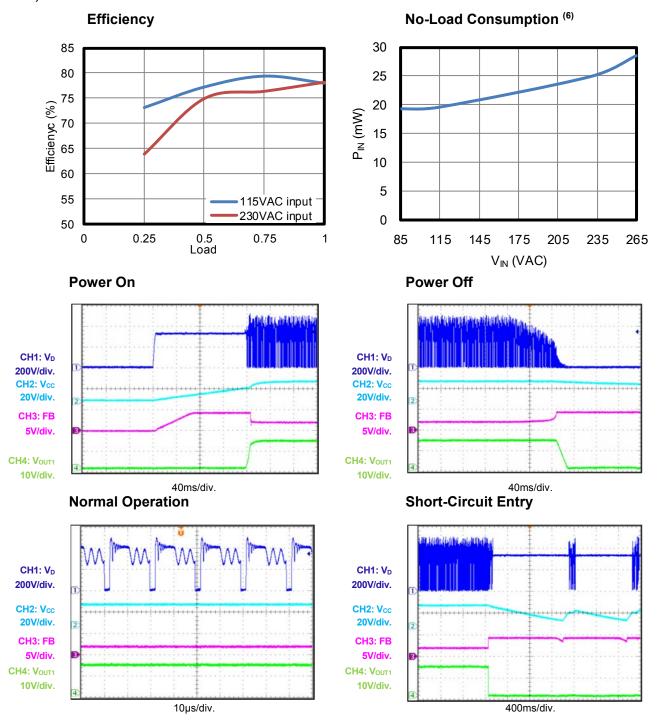

### TYPICAL PERFORMANCE CHARACTERISTICS

Performance waveforms are tested with the evaluation board in the Design Example section.  $V_{IN}$  = 230V,  $V_{OUT1}$  = 13.5V,  $I_{OUT1}$  = 300mA,  $V_{OUT2}$  = 8V,  $I_{OUT2}$  = 50mA,  $V_{OUT3}$  = 8V,  $I_{OUT3}$  = 50mA,  $T_A$  = 25°C, unless otherwise noted.

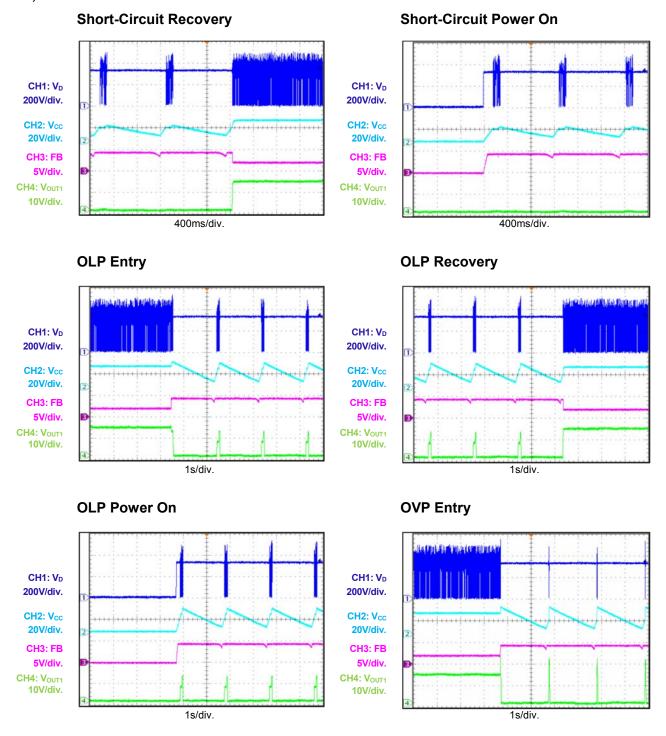

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

Performance waveforms are tested with the evaluation board in the Design Example section.  $V_{IN}$  = 230V,  $V_{OUT1}$  = 13.5V,  $I_{OUT1}$  = 300mA,  $V_{OUT2}$  = 8V,  $I_{OUT2}$  = 50mA,  $V_{OUT3}$  = 8V,  $I_{OUT3}$  = 50mA,  $T_A$  = 25°C, unless otherwise noted.

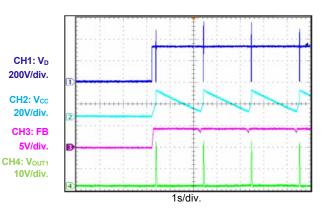

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

Performance waveforms are tested with the evaluation board in the Design Example section.  $V_{IN}$  = 230V,  $V_{OUT1}$  = 13.5V,  $I_{OUT1}$  = 300mA,  $V_{OUT2}$  = 8V,  $I_{OUT2}$  = 50mA,  $V_{OUT3}$  = 8V,  $I_{OUT3}$  = 50mA,  $T_A$  = 25°C, unless otherwise noted.

### **OVP Recovery**

# CH1: V<sub>D</sub> 200V/div. CH2: V<sub>CC</sub> 20V/div. CH3: FB 5V/div. CH4: V<sub>OUT1</sub> 10V/div. Ts/div.

### **OVP Power On**

### NOTE:

6) The no load consumption is tested with OUT2 and OUT3 open.

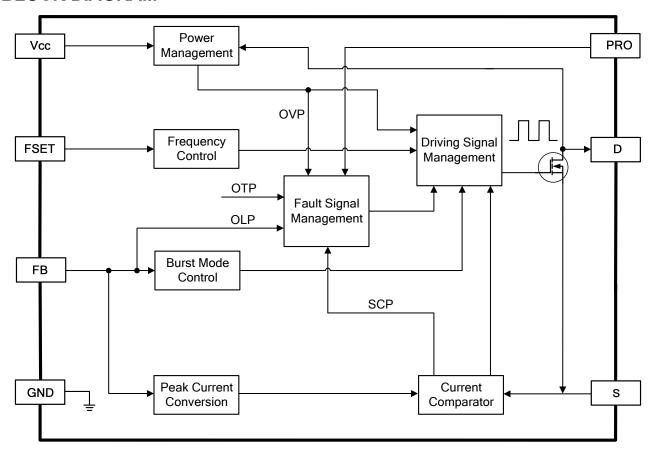

# **BLOCK DIAGRAM**

Figure 1: Internal Functional Block Diagram

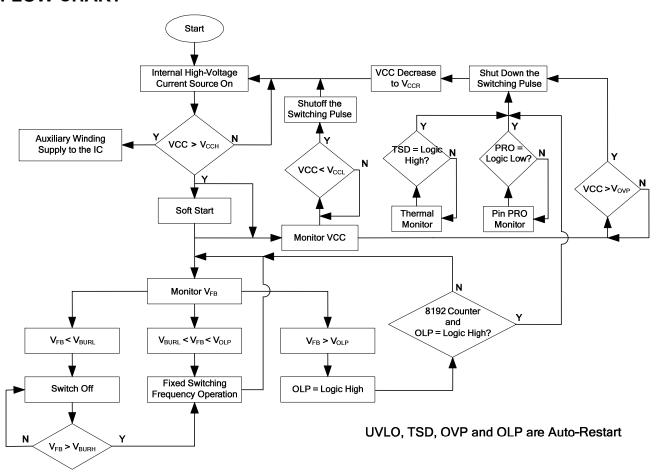

### **OPERATION**

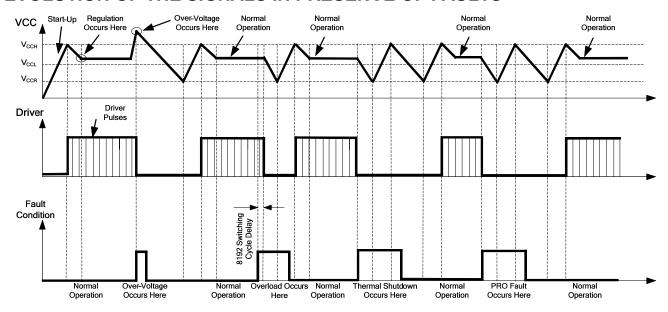

The HF920 incorporates all of the necessary features required by a reliable switch-mode power supply. The proprietary, 900V, monolithic integration enables a highly integrated power supply solution. The HF920 uses burst-mode operation to minimize the stand-by power consumption at light load. Protection features such as auto-recovery for overload protection (OLP), short-circuit protection (SCP), overvoltage protection (OVP), and thermal shutdown for over-temperature protection (OTP) contribute to a safer converter design with minimal external components.

### Pulse-Width Modulation (PWM) Operation

The HF920 employs peak-current-mode control. On the secondary side, the output voltage is regulated by the compensation network, and the compensation output is fed back to the primary side as an input signal to FB through an optical coupler. The FB voltage ( $V_{\text{FB}}$ ) is used to control the peak current on the primary side winding of the flyback transformer based on the current sensing on S. The integrated 900V MOSFET turns on at the beginning of each cycle based on the internal oscillator and turns off based on the peak current control.

### Start-Up and VCC UVLO

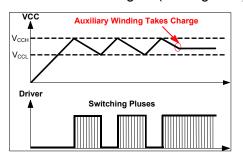

Initially, the IC is driven by the internal current source drawn from the high-voltage D pin. The IC begins switching, and the internal high-voltage current source turns off once the VCC voltage reaches its upper threshold ( $V_{\text{CCH}}$ ). Then, the IC supply is taken over by the auxiliary winding of the transformer. Whenever VCC falls below its lower threshold ( $V_{\text{CCL}}$ ), the regulator stops switching, and the internal high-voltage current source turns on again (see Figure 2).

Figure 2: VCC Start-Up

The lower VCC under-voltage lockout (UVLO) threshold decreases from  $V_{\text{CCL}}$  to  $V_{\text{CCR}}$  when a fault condition (such as SCP, OLP, OVP, or OTP) occurs.

### Soft Start (SS)

The HF920 implements an internal soft-start circuit to reduce stress on the primary-side MOSFET and secondary diode and to smoothly establish the output voltage during start-up. The internal soft-start circuit increases the threshold of the peak-current comparator gradually from the minimal level until the feedback control loop takes over. The maximum soft-start time is  $t_{\rm SS}$ . Within the soft-start duration, the switching frequency is also increased progressively from 20 - 100% of the programmed switching frequency.

### **Switching Frequency**

The switching frequency can be set by a resistor between FSET and GND. The oscillator frequency can be calculated with Equation (1):

$$f_{s} = \frac{1}{523 \times 10^{-9} + 123.4 \times 10^{-12} \times \frac{R_{FSET}}{V_{FST}}} Hz$$

(1)

Where  $V_{\text{FSET}}$  is the internal reference voltage on FSET.

### **Frequency Jittering**

The HF920 provides a frequency jittering function, which simplifies the input EMI filter design and decreases system cost. The HF920 has optimized frequency jittering with a  $\pm 3.5\%$  frequency deviation range and a  $256T_{\rm S}$  carrier cycle that improves EMI effectively by spreading the energy dissipation over the frequency range.

### **Frequency Doubling**

Connect a 1nF capacitor to FSET to enable the frequency doubling. The switching frequency is doubled when the converter enters an overpower condition (FB voltage rises to  $V_{OLP}$ ). This way, the converter is able to handle up to a 50% decrease of the transformer inductance caused by external magnetizing interference.

### **Peak Current Limit**

The primary peak current is sensed by a sensing resistor between S and GND. When the sum of the sense resistor voltage and the slope compensation voltage reaches the peak current limit (Vcs), the MOSFET turns off.

The peak current limit is set by  $V_{FB}$ , as  $V_{CS} = V_{FB}$  /  $K_{div}$ , for all normal operations. The maximum value of peak current limit is limited to  $V_{CSL}$  internally. This way, the output power is always limited to prevent excessive stress on the power supply.

### **Burst Operation**

The HF920 implements burst-mode operation at no-load and light-load conditions. Burst-mode operation enables and disables the switching pulse of the MOSFET alternately to reduce switching loss. This helps minimize the stand-by power consumption and achieve high light-load efficiency.

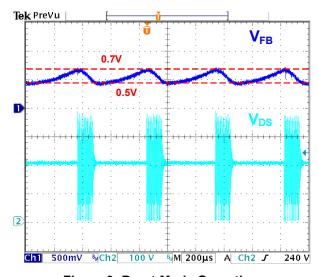

As the load decreases,  $V_{FB}$  decreases. The IC stops switching when  $V_{FB}$  drops below  $V_{BURL}$ . As the converter stops and the output voltage drops,  $V_{FB}$  rises again due to the negative feedback control loop. Once  $V_{FB}$  goes over  $V_{BURH}$ , the switching pulse resumes. If the load condition remains the same,  $V_{FB}$  decreases, and the entire process is repeated.

Figure 3 shows the burst mode operation of the HF920.

Figure 3: Burst-Mode Operation

### **Over-Voltage Protection (OVP)**

The HF920 shuts down via OVP when VCC rises above  $V_{\text{OVP}}$  for  $t_{\text{OVP}}$ . In a flyback application, the auxiliary winding output voltage is proportional to the output voltage, so OVP protects the circuit from overstress during an output over-voltage condition. The HF920 restarts automatically after VCC drops to  $V_{\text{CCR}}$ . The regulator resumes normal operation once the fault disappears.

### Overload Protection (OLP)

The HF920 shuts down when OLP is triggered. The OLP fault occurs when  $V_{\text{FB}}$  is pulled up to  $V_{\text{OLP}}$  for 8192 switching cycles. The HF920 restarts automatically when VCC drops to  $V_{\text{CCR}}$ . When the fault disappears, the power supply resumes operation.

If frequency doubling is enabled, the HF920 doubles the switching frequency when  $V_{\text{FB}}$  rises to the OLP point.

### **Short-Circuit Protection (SCP)**

The HF920 shuts down when the S voltage is higher than  $V_{\text{SCP}}$ , which indicates a short circuit. The HF920 enters short-circuit protection (SCP), which prevents any thermal or stress damage. The HF920 restarts automatically when VCC drops to  $V_{\text{CCR}}$ . Once the fault disappears, the power supply resumes operation.

### Thermal Shutdown (OTP)

When the junction temperature of the IC exceeds 150  $^{\circ}$  C, over-temperature protection (OTP) is activated, and the main power MOSFET stops switching to protect the HF920 from thermal damage. During the protection period, the regulator is latched off. VCC is discharged to V<sub>CCR</sub> and recharged to V<sub>CCH</sub> by the internal high-voltage current source. Once the junction temperature drop exceeds the thermal shutdown recovery hysteresis, the HF920 resumes operation.

### **PRO**

PRO provides external protection. The HF920 is shut down when the PRO voltage exceeds  $V_{\text{PRO}}$  and resumes operation once the fault disappears. PRO protection can be used for input OVP or any other protections (input UVP, OTP for key components, etc.).

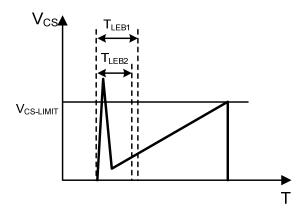

### Leading-Edge Blanking (LEB)

The HF920 implements a leading-edge blanking (LEB) unit to prevent the MOSFET from turning off prematurely due to its high turn-on current spike. During the blanking time, the current sensing signal on S is blocked.

The LEB unit contains two LEB times. The current sensor LEB inhibits the current limitation comparator for  $T_{LEB1}$ , and the SCP LEB inhibits the SCP current comparator for  $T_{LEB2}$ . Figure 4 shows the primary current sense waveform and the LEB.

Figure 4: Leading-Edge Blanking

### APPLICATION INFORMATION

### **Selecting the Input Capacitor**

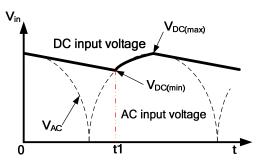

The input bulk capacitor filters the rectified AC input voltage and hold the bus voltage for the converter. Figure 5 shows the typical DC bus voltage waveform of a full-bridge rectifier.

Figure 5: Input Voltage Waveform

When a full-bridge rectifier is used, the input capacitor is set at  $2\mu F/W$  for the universal input condition (85  $\sim$  265V<sub>AC</sub>), typically. For high-voltage input applications (>185V<sub>AC</sub>), cut the capacitor values in half. Very low DC input voltages can cause thermal problems under heavy-load conditions. It is recommended that the minimum DC voltage is higher than 70V. Estimate the minimum DC voltage with the following procedure.

First, estimate the input power  $(P_{in})$  with Equation (2):

$$P_{in} = \frac{V_{o} \times I_{o}}{\eta}$$

(2)

Where  $V_0$  is the output voltage,  $I_0$  is the rated output current, and  $\eta$  is the estimated efficiency. Generally,  $\eta$  is between 0.75 and 0.85 depending on the input range and output application.

Then, the linear part of the DC input voltage ( $V_{DC}$ ) can be expressed with Equation (3):

$$V_{DC}(t) = \sqrt{V_{AC(peak)}^2 - \frac{2 \times P_{in}}{C_{in}} \times t}$$

(3)

At t1, the DC bus voltage reaches its minimum value, and the AC input starts charging the input capacitor. t1 can be calculated with Equation (4):

$$V_{DC}(t1) = V_{AC}(t1) \tag{4}$$

$V_{\text{DC(min)}}$  can then be calculated with t1 and Equation (4). A larger input capacitor should be used if the estimated  $V_{\text{DC(min)}}$  is too low.

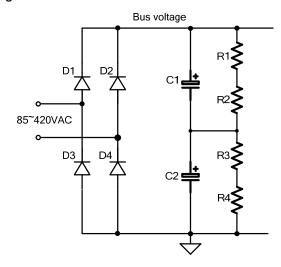

As a 900V offline regulator, the HF920 is ideal for very high-voltage input applications, which means a very high bus voltage is beyond the rated voltage of normal high voltage electrolytic capacitors. To meet the high bus voltage requirement, stack capacitors as shown in Figure 6.

**Figure 6: Input Stacked Capacitor Circuit**

The same type of capacitors should be chosen for C1 and C2 to balance their voltages. Each capacitor endures half of the bus voltage, but due to the capacitance distribution (typically  $\pm$  20% for electrolytic capacitors), their voltage varies in mass production. In this case, R1 to R4 should be used as the voltage balancing resistors.

To balance the voltage on C1 and C2, R1 to R4 should have the same value. R1 to R4 should be a 1206 package size to meet the voltage rating requirement. The R1 to R4 values should also be large enough for energy savings. For example, the total value of R1 to R4 is  $20M\Omega$ , which consumes about 18mW at a  $600V_{DC}$  bus voltage.

### **Voltage Stress on the Primary MOSFET**

Typically, the maximum voltage stress on the primary MOSFET is design to be less than 90% of its breakdown voltage for reliable operation.

© 2018 MPS. All Rights Reserved.HF920

The maximum voltage stress occurs when the primary MOSFET turns off and can be calculated with Equation (5):

$$V_{DS(max)} = V_{BUS(max)} + N(V_O + V_F) + V_{spike}$$

(5)

Where  $V_F$  is the rectifier diode's forward voltage,  $V_O$  is the output voltage, N is the primary-to-secondary turns ratio, and  $V_{spike}$  is the voltage spike caused by the transformer's primary leakage inductance.

According to Equation (5), voltage stress can be reduced either by choosing a small N or  $V_{\text{spike}}$ . However, a small N leads to larger secondary stress, which means there is a trade-off to make. A small  $V_{\text{spike}}$  requires a strong snubber to suppress the voltage spike.

The input circuit should be designed to guarantee a proper  $V_{\text{BUS(max)}}$  (i.e.: using suppression components to protect it from surge).

### Primary-Side Inductor Design (L<sub>m</sub>)

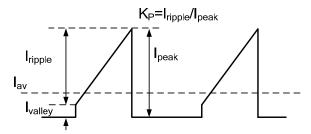

Typically, the converter is designed to operate in continuous conduction mode (CCM) under a low input voltage for universal input applications. With a built-in slope compensation function, the HF920 supports stable CCM control when the duty cycle exceeds 50%. Set the ratio (K<sub>P</sub>) of the primary inductor ripple current amplitude vs. the peak current value to 0 <  $K_P \leqslant 1$ , where a smaller  $K_P$  means a deeper CCM, and  $K_P = 1$ stands for boundary conduction mode (BCM) and discontinuous conduction mode (DCM). Figure 7 shows the relevant waveforms. A larger primary inductance leads to a smaller K<sub>P</sub>, which reduces the RMS current but increases the transformer size. For most HF920 applications, an optimal K<sub>P</sub> value is between 0.8 and 1, considering the wide input range.

**Figure 7: Typical Primary Current Waveform**

For CCM at a minimum input, the converter duty cycle can be determined with Equation (6):

$$D = \frac{(V_O + V_F) \times N}{(V_O + V_F) \times N + V_{DC(min)}}$$

(6)

Where  $V_F$  is the secondary diode's forward voltage, and N is the transformer turns ratio.

The MOSFET turn-on time can be calculated with Equation (7):

$$T_{ON} = \frac{D}{f_s} \tag{7}$$

Where f<sub>S</sub> is the operating frequency.

The input average current, ripple current, peak current, and valley current of the primary side are calculated using Equation (8), Equation (9), Equation (10), and Equation (11):

$$I_{AV} = \frac{P_{in}}{V_{DC(min)}} \tag{8}$$

$$I_{\text{ripple}} = K_{P} \times I_{\text{peak}} \tag{9}$$

$$I_{\text{peak}} = \frac{I_{\text{AV}}}{(1 - \frac{K_{\text{p}}}{2}) \times D}$$

(10)

$$I_{\text{vallev}} = (1 - K_{\text{P}}) \times I_{\text{peak}} \tag{11}$$

Estimate L<sub>m</sub> using Equation (12):

$$L_{m} = \frac{V_{DC(min)} \times T_{ON}}{I_{ripole}}$$

(12)

### **Current-Sense Resistor**

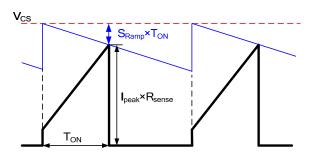

Figure 8 shows the peak current control waveform with slope compensation.

Figure 8: Peak Current Control Waveform with Slop Compensation

When the sum of the sense resistor voltage and the slope compensation voltage reaches the peak current limit ( $V_{CS}$ ), the HF920 turns off the internal MOSFET.  $V_{CS}$  equals the maximum current-set point ( $V_{CSL}$ ) under full load. Considering the margin, use 0.95 x  $V_{CSL}$  for designs. The voltage on the sense resistor can be calculated using Equation (13):

$$V_{\text{sense}} = 0.95 \times V_{\text{CSL}} - S_{\text{Ramp}} \times T_{\text{ON}}$$

(13)

Where  $S_{RAMP}$  is the slope compensation ramp in proportion to  $f_S$ . Typically,  $S_{RAMP}$  = 21mV/ $\mu$ s when  $R_{FSET}$  = 200k $\Omega$ .

The value of the sense resistor is calculated using Equation (14):

$$R_{\text{sense}} = \frac{V_{\text{sense}}}{I_{\text{neak}}} \tag{14}$$

The current-sense resistor should be chosen with an appropriate power rating. Its power loss can be calculated with Equation (15):

$$P_{\text{sense}} = \left[ \left( \frac{I_{\text{peak}} + I_{\text{valley}}}{2} \right)^2 + \frac{1}{12} \times \left( I_{\text{peak}} - I_{\text{valley}} \right)^2 \right] \times D \times R_{\text{sense}}$$

(15)

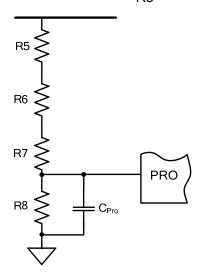

### Input Over-Voltage Protection on PRO

A typical input OVP circuitry of the HF920 is shown in Figure 9. The input OVP point can be calculated with Equation (16):

$$V_{INOVP} = V_{PRO} \times \frac{R5 + R6 + R7 + R8}{R8}$$

(16)

Figure 9: Input Over-Voltage Protection Set-Up

For resistors R5 to R7, 1206 packages should be used to meet the voltage rating requirement. The total value should be larger than  $10M\Omega$  for energy-saving purposes.

Switching noise may couple to these large resistors and disturb the PRO protection. It is recommended to connect a bypass ceramic capacitor to PRO. Place this capacitor as close to the IC as possible.

### **Thermal Performance Optimization**

The HF920 is dedicated to high input voltage applications. However, the high input voltage can cause a greater switching loss on the MOSFET, which can lead to poor thermal performance. Measures should be taken to reduce the switching loss when designing these applications.

First, try to use a lower switching frequency if possible. Then use a small transformer turns ratio to minimize the reflected voltage on the primary winding. Thus,  $V_{DS}$  is reduced. Finally, reduce the turn-on loss, since the turn-on loss composes a large part of the switching loss.

Turn-on loss is the product of the turn-on current spike and  $V_{\rm DS}$ . Reducing the turn-on loss can be achieved by reducing  $V_{\rm DS}$  or the turn-on current spike.

Reducing  $V_{DS}$  by using a small turns ratio is discussed above. Another way of reducing  $V_{DS}$  when the MOSFET turns on is to set the HF920 to work under deep DCM. In deep DCM, the  $V_{DS}$  oscillation is fully damped, so there is no chance of turning on at the high peak value.

The turn-on current spike is caused by a parasitic capacitor and output diode reverse recovery.

DCM operation helps prevent the output diode's reverse recovery. The transformer structure should be designed to achieve minimum parasitic capacitance of each winding and between the primary and secondary windings.

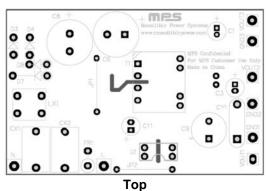

### **PCB Layout Guidelines**

Efficient PCB layout is critical for achieving reliable operation, good EMI performance, and good thermal performance. For best results, refer to Figure 10 and follow the guidelines below.

- 1. Minimize the power stage switching stage loop area. This includes the input loop (C8–C6-T1–U2–R21/R22–C8), the auxiliary winding loop (T1–D6–R16–C11–T1), the output loop (T1–D6–C9–T1, T1–D1–C1–T1, and T1–D2–C3–T1), and the RCD loop (T1–D5–R5/R7/C4–T1).

- Ensure that the power loop ground does not pass through the control circuit ground. If a heat sink is used, connect it to the primary GND plane to improve EMI and thermal dissipation.

- 3. Place the control circuit capacitors (for FB, PRO, and VCC) close to the IC to decouple the switching noise.

- 4. Enlarge the GND pad near the IC for good thermal dissipation.

- 5. Keep the EMI filter far away from the switching point.

- 6. Ensure enough clearance distance to meet the insulation requirement.

Figure 10: Recommended Layout

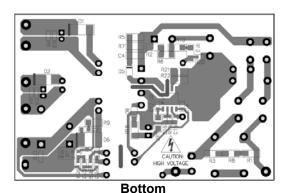

### Design Example

Table 2 is a design example using the application guidelines for the given specifications.

**Table 2: Design Example**

| V <sub>IN</sub>   | 85 to 420VAC |

|-------------------|--------------|

| V <sub>OUT1</sub> | 13.5V        |

| I <sub>OUT1</sub> | 0.3A         |

| V <sub>OUT2</sub> | 8V           |

| I <sub>OUT2</sub> | 0.05A        |

| V <sub>OUT3</sub> | 8V           |

| Іоит3             | 0.05A        |

| fs                | 50kHz        |

The detailed application schematic is shown in Figure 11. The typical performance and circuit waveforms are shown in the Typical Performance Characteristics section. For more device applications, please refer to the related evaluation board datasheets.

# TYPICAL APPLICATION CIRCUIT

Figure 11: Typical Application Schematic

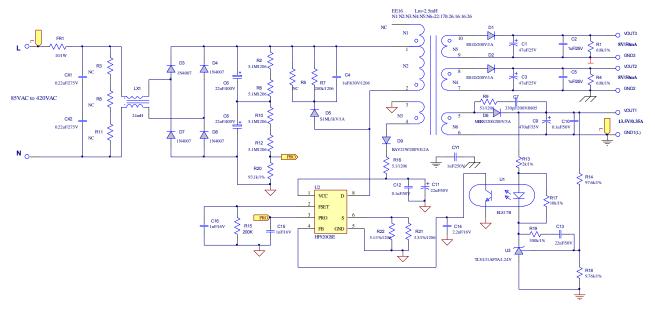

**Figure 12: Transformer Structure**

# **Table 3: Winding Order**

|          |         | _                       |               |           |

|----------|---------|-------------------------|---------------|-----------|

| Tape (T) | Winding | Terminal<br>Start → End | Wire Size (Φ) | Turns (T) |

| 1        | N1      | 1 → NC                  | 0.15mm*2      | 22        |

| 1        | N2      | 2 → 1                   | 0.15mm*1      | 170       |

| 1        | N3      | 4 → 3                   | 0.1mm*1       | 26        |

| 1        | N6      | 5 → 6                   | 0.3mm TIW *1  | 26        |

| 1        | N4      | 10 → 9                  | 0.16mm TIW *1 | 16        |

| 1        | N5      | $A \rightarrow B$       | 0.16mm TIW *1 | 16        |

|          |         |                         |               |           |

# **FLOW CHART**

# **EVOLUTION OF THE SIGNALS IN PRESENCE OF FAULTS**

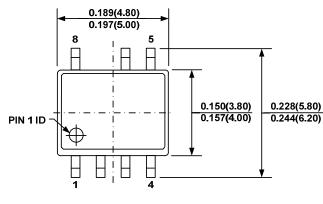

### PACKAGE INFORMATION

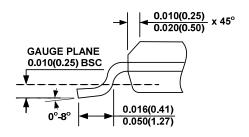

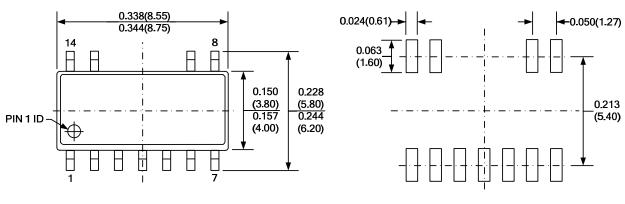

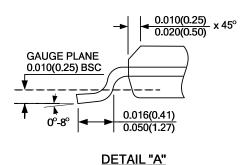

### SOIC8-7A

0.024(0.61) -0.050(1.27) 0.063(1.60) -0.213(5.40)

**TOP VIEW**

**RECOMMENDED LAND PATTERN**

**SIDE VIEW**

**FRONT VIEW**

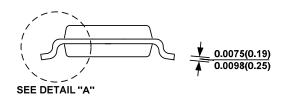

**DETAIL "A"**

### NOTE:

- 1) CONTROL DIMENSION IS IN INCHES. DIMENSION IN **BRACKET IS IN MILLIMETERS.**

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.004" INCHES MAX.

- 5) JEDEC REFERENCE IS MS-012.

- 6) DRAWING IS NOT TO SCALE.

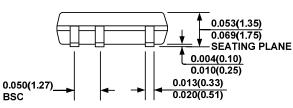

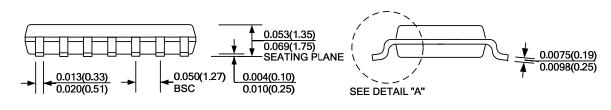

# PACKAGE INFORMATION (continued)

### SOIC14-11

**TOP VIEW**

**RECOMMENDED LAND PATTERN**

**FRONT VIEW**

**SIDE VIEW**

# NOTE:

- 1) CONTROL DIMENSION IS IN INCHES. DIMENSION IN BRACKET IS IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.004" INCHES MAX.

- 5) DRAWING CONFORMS TO JEDEC MS-012, VARIATION AB.

- 6) DRAWING IS NOT TO SCALE.

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Monolithic Power Systems (MPS):

HF920GSE-Z HF920GS-Z