# **MPQ8875A**

36V, 5A, Four-Switch, Synchronous Buck-Boost Converter with I<sup>2</sup>C Interface, AEC-Q100 Qualified

# DESCRIPTION

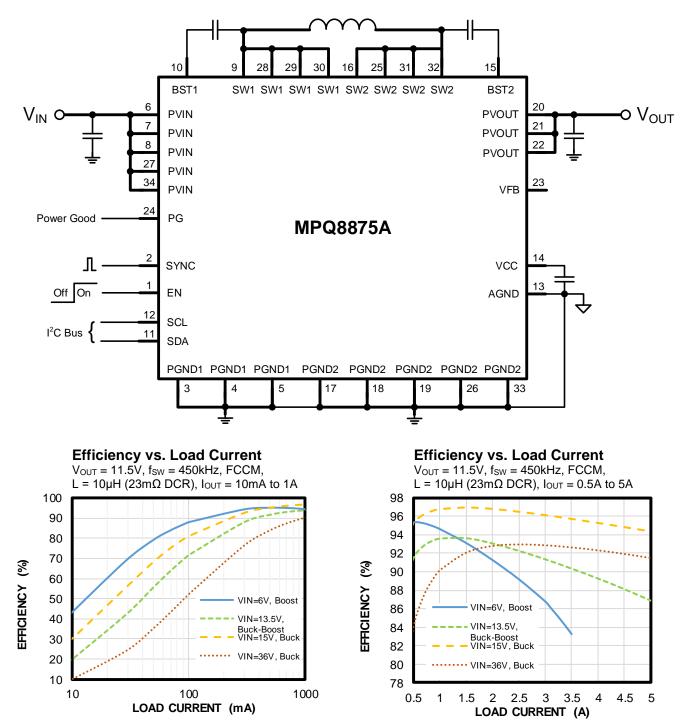

MPQ8875A is 36V, The а monolithic, synchronous buck-boost DC/DC converter. The wide 2.2V to 36V input voltage range makes this device well-suited for multi-purpose automotive and industrial applications. The proprietary constant-on-time (COT) control, as well as the fully integrated, four-switch configuration, allow the chip to flexibly change the converter topology between buck, boost, and buck-boost mode. This optimizes performance and efficiency with input voltages that are above, below, or equal to the output voltage. It also ensures seamless transitions between the adjacent operational regions.

The MPQ8875A is controlled separately via a standard I<sup>2</sup>C interface. The various parameters can be adjusted by writing the settings to the device without any hardware changes required.

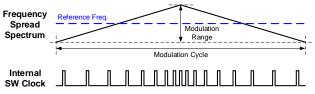

The switching frequency can be configured between 200kHz and 1MHz, or it can be synchronized between 250kHz and 1MHz via an external clock signal. In addition, the configurable frequency spread spectrum function can dither the switching frequency periodically for improved EMI performance.

Robust fault protections include input undervoltage lockout (UVLO), input over-voltage protection (OVP), cycle-by-cycle peak current limiting, output OVP, output short-circuit protection (SCP), and thermal shutdown. The built-in power good function can indicate whether the output voltage is regulated properly.

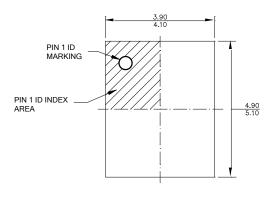

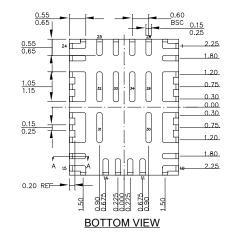

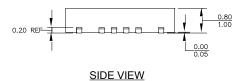

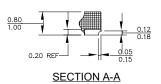

The MPQ8875A is available in a thermally enhanced QFN-34 (4mmx5mm) package.

# FEATURES

- 2.2V to 36V Wide Input Voltage Range

- Up to 5A Continuous Output Current

- <25µA Shutdown Current

- 180µA Quiescent Current when V<sub>IN</sub> = 12V

- Single-Channel, Four-Switch, Synchronous Buck-Boost Configuration:

- Internal 10mΩ Buck High-Side Power MOSFET

- Internal 25mΩ Buck Low-Side Synchronous Rectifier

- Internal 10mΩ Boost Low-Side Power MOSFET

- Internal 25mΩ Boost High-Side Synchronous Rectifier

- Proprietary Constant-On-Time (COT) Control for Seamless Transitions

- Internal Soft-Start

- Smart Power Good Output

- Easy-to-Optimize Efficiency and EMI Performance:

- Configurable 200kHz to 1MHz Switching Frequency

- Synchronizable Switching Frequency from 250kHz to 1MHz

- Switching Frequency Spread Spectrum

- Configurable Switching Speed

- Protection Features:

- o Cycle-by-Cycle Current Limiting

- Over-Current Protection (OCP)

- Configurable Input Under-Voltage Lockout (UVLO)

- Output Over-Voltage Protection (OVP)

- Input Over-Voltage Protection (OVP)

- Output Short-Circuit Protection (SCP)

- Over-Temperature Shutdown

MPQ8875A - 36V, 4-SWITCH SYNC BUCK-BOOST CONVERTER WITH I<sup>2</sup>C, AEC-Q100

#### FEATURES (continued)

- Standard, Configurable I<sup>2</sup>C Interface:

- Converter On/Off

- Input Range Selection

- Output Range from 0.5V to 30V for CCM, 5V to 30V for DCM

- Switching Frequency

- Synchronized Input/Output Selection

- o Switching Slew Rate

- Frequency Spread Spectrum Setting

- Compensation Network

- Ramp Compensation

- Soft-Start Time

- Dynamic Output Voltage Adjustment with Slew Rate Control

- o Converter Mode Transition Threshold

- Discontinuous Conduction Mode (DCM) or Forced Continuous Conduction Mode (FCCM)

- Constant-On-Time (COT) Control of the Boost Switch in Buck-Boost Mode

- Input Over-Voltage Protection (OVP)

- Output Over-Voltage Protection (OVP)

- o Cycle-by-Cycle Current Limit Threshold

- o Reverse Current Limit Threshold

- Over-Current Protection (OCP)

- Output Short-Circuit Protection (SCP)

- o Thermal Protection

- Power Good (PG) Threshold

- o Junction Temperature Reading

- One-Time Programmable (OTP) for Default Parameter Setting

- Available in QFN-34 (4mmx5mm) Package

- Available with Wettable Flanks

- Available in AEC-Q100 Grade 1

# **APPLICATIONS**

- Sensor Fusion Systems

- Camera Monitor Systems

- Infotainment Systems

- Automotive Applications

All MPS parts are lead-free, halogen free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are registered trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

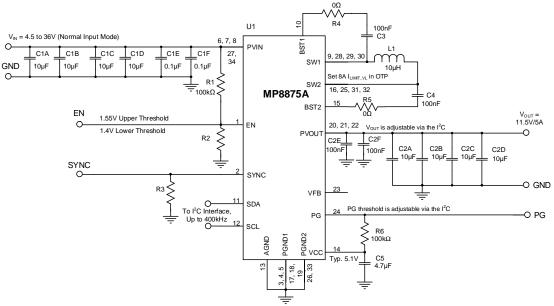

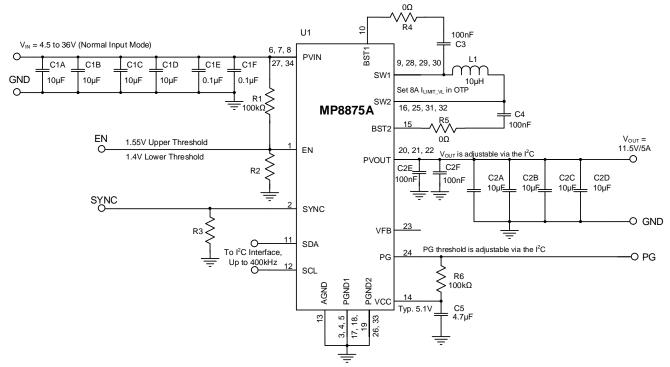

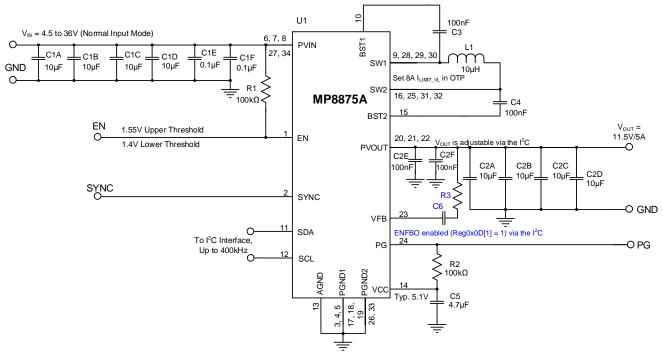

# TYPICAL APPLICATION

#### **ORDERING INFORMATION**

| Part Number*              | Package          | Top Marking | MSL Rating*** |

|---------------------------|------------------|-------------|---------------|

| MPQ8875AGVE-xxxx**, ****  | QFN-34 (4mmx5mm) | See Below   | 1             |

| MPQ8875AGVE-xxxx-AEC1**** | QFN-34 (4mmx5mm) | See Below   | I             |

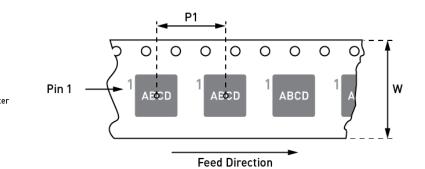

\* For Tape & Reel, add suffix -Z (e.g. MPQ8875AGVE-xxxx-Z).

\*\* "xxxx" is the configuration code identifier for the register settings stored in the OTP register. Each "x" can be a hexadecimal value between 0 and F. Contact an MPS FAE to create this unique number.

\*\*\* Moisture Sensitivity Level Rating

\*\*\*\* Wettable Flank

| TOP MARKING |

|-------------|

| MPSYWW      |

| M8875A      |

| LLLLLL      |

| E           |

MPS: MPS prefix Y: Year code WW: Week code M8875A: Part number LLLLLL: Lot number E: Wettable Flank

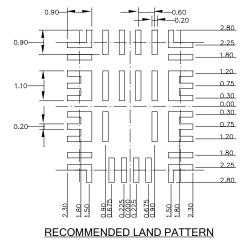

#### **PACKAGE REFERENCE**

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2021 MPS. All Rights Reserved.

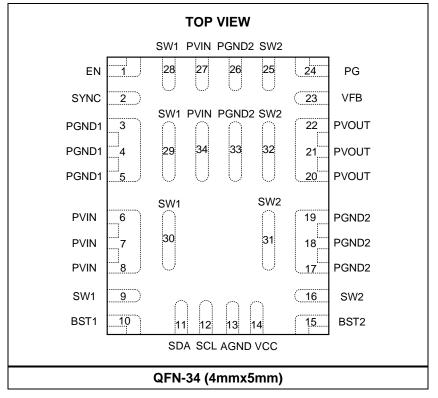

### **PIN FUNCTIONS**

| Pin #              | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

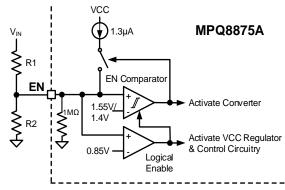

| 1                  | EN    | <b>On/off control input and custom input UVLO setting.</b> The EN pin can be driven by an external logic signal to enable or disable the chip. Pull EN below the specified threshold (about 1.4V) to shut down the chip. Pull EN above the specified threshold (about 1.55V) to enable the chip. Connect a resistor divider from the input voltage (PVIN pin) to the EN pin to set a customer-accurate under-voltage lockout (UVLO) threshold for the input voltage. A 1.3 $\mu$ A internal pull-up current source is enabled when the EN voltage is above its high threshold (about 1.55V). A 1M $\Omega$ internal resistor pulls the EN pin low when it is floating. This means that the part is off by default when there is no external pull-up voltage. |

| 2                  | SYNC  | <b>Synchronization input or output.</b> The SYNC pin can be configured through the I <sup>2</sup> C to synchronization input or output mode. In synchronization input mode, the chip synchronizes its switching with the external clock connected to this pin. The external clock frequency must be 20% greater than the configured frequency set in the OTP register. In synchronization output mode, the chip outputs its clock signal to synchronize the other chip's switching clock. Float the SYNC pin if it is not used.                                                                                                                                                                                                                              |

| 3, 4, 5            | PGND1 | <b>Power ground for the SW1 half-bridge.</b> The three PGND1 pins are connected inside the MPQ8875A. These pins should be electrically connected to the system power ground plane with the shortest and lowest-impedance connection possible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6, 7, 8,<br>27, 34 | PVIN  | <b>Power input for the converter.</b> Connect a large bulk input capacitor to PVIN for a stable power source, and connect bypass capacitors from PVIN to PGND1 to reduce noise. Inside the chip, three of the PVIN pins (pins 6, 7, and 8) are connected together. The two remaining PVIN pins (pins 27 and 34) are also connected together. Both sets of PVIN pins require a bypass capacitor. The bypass capacitors should be placed as close to the chip as possible. The input voltage (V <sub>IN</sub> ) is supplied by the PVIN pin.                                                                                                                                                                                                                   |

| 9, 28,<br>29, 30   | SW1   | <b>Power switch output 1.</b> The four SW1 pins (pins 9, 28, 29, and 30) are connected together inside the chip. These pins should be connected to one side of the external power inductor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 10                 | BST1  | <b>Bootstrap for SW1.</b> Place a capacitor between SW1 and BST1 to form a floating supply across the SW1 upper power switch driver. Generally, a 100nF ceramic capacitor is required to drive the SW1 upper power switch's gate above SW1's level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 11                 | SDA   | <b>I<sup>2</sup>C bus serial data input/output.</b> This pin is an open-drain port. An external pull-up resistor is required to connect this pin to the I <sup>2</sup> C bus supply rail. If SDA is not used, it is recommend to connect SDA to the VCC pin through a resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 12                 | SCL   | <b>I<sup>2</sup>C bus serial clock input.</b> This pin is an open-drain port. An external pull-up resistor is required to connect this pin to the I <sup>2</sup> C bus supply rail. If SCL is not used, it is recommend to connect SCL to the VCC pin through a resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 13                 | AGND  | Signal ground. Ground for the internal logic and signal control blocks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 14                 | VCC   | <b>5V internal regulator output.</b> VCC supplies power to the control blocks, I <sup>2</sup> C interface, and the power MOSFETs' gate driver. Bypass VCC to AGND with a $1\mu$ F to $10\mu$ F, external, low-ESR ceramic capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 15                 | BST2  | <b>Bootstrap for SW2.</b> Place a capacitor between SW2 and BST2 to form a floating supply across the SW2 upper power switch driver. A 100nF ceramic capacitor is typically required to drive the SW2 upper power switch's gate above SW2's level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 16, 25,<br>31, 32  | SW2   | <b>Power switch output 2.</b> The four SW2 pins (pins 16, 25, 31, and 32) are connected together inside the MPQ8875A. These pins should be connected to one side of the external power inductor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

# PIN FUNCTIONS (continued)

| Pin #                    | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17, 18,<br>19, 26,<br>33 | PGND2 | <b>Power ground for SW2 half-bridge.</b> Three of the PGND2 pins (pins 17, 18, and 19) are connected inside the MPQ8875A. The two remaining PGND2 pins (pins 26 and 33) are also connected together. These five pins should be electrically connected to the system power ground plane through the shortest and lowest-impedance connection possible.                                                                                                              |

| 20, 21,<br>22            | PVOUT | <b>Power output of the converter.</b> The three PVOUT pins (pins 20, 21, and 22) are connected together inside the MPQ8875A. The output capacitors should be placed as close to the chip as possible, with a short return path to the ground plane. In addition, connect a bypass capacitor from PVOUT to PGND2 to reduce noise. Place this capacitor as close to PVOUT as possible. The output voltage (V <sub>OUT</sub> ) is supplied by the PVOUT pin.          |

|                          |       | Feedback input. Two modes are available for the VFB pin via the I <sup>2</sup> C, described below:                                                                                                                                                                                                                                                                                                                                                                 |

| 23                       | VFB   | <ul> <li>No connection. Leave this pin floating.</li> <li>Tie this pin to the internal error amplifier's feedback input, which is also connected to the tap of the internal PVOUT resistor divider. To improve system stability, add an external RC compensation network from VOUT to this pin. The external compensation network should be placed as close to the chip as possible. If the external compensation is not used, leave this pin floating.</li> </ul> |

| 24                       | PG    | <b>Power good indicator</b> . This pin is an open-drain status pin that indicates if the output voltage is within its allowable window. Connect PG to VCC with a resistor (e.g. $100k\Omega$ ). After soft start ends, the PG pin asserts low when the output voltage is not within the allowable window. Float this pin if it is not used.                                                                                                                        |

#### ABSOLUTE MAXIMUM RATINGS (1)

| PVIN, PVOUT<br>V <sub>SW1</sub><br>V <sub>SW2</sub>                        | 0.3V to PVIN + 0.3V                                                          |

|----------------------------------------------------------------------------|------------------------------------------------------------------------------|

| V <sub>BST1</sub> (V <sub>SW1</sub><br>V <sub>BST2</sub> (V <sub>SW2</sub> | - 0.3V) to (V <sub>SW1</sub> + 5.5V)<br>- 0.3V) to (V <sub>SW2</sub> + 5.5V) |

| All other pins<br>Continuous power dissip<br>QFN-34 (4mmx5mm)              | ation (T <sub>A</sub> = 25°C) <sup>(2)</sup>                                 |

| Junction temperature                                                       | 150°C                                                                        |

| Storage temperature                                                        | 65°C to +150°C                                                               |

#### Electrostatic Discharge (ESD) Ratings

| Human body model (HBM)     | ±2000V |

|----------------------------|--------|

| Charged device model (CDM) | ±750V  |

#### **Recommended Operating Conditions**

Supply voltage (V<sub>IN</sub>):

| Normal input mode                         | 4.5V to 36V     |

|-------------------------------------------|-----------------|

| Low input mode                            | 2.2V to 36V     |

| Output voltage (VOUT) in CCM              | 0.5V to 30V     |

| Output voltage (VOUT) in DCM              | 5V to 30V       |

| Operating junction temp (T <sub>J</sub> ) | -40°C to +150°C |

#### Thermal Resistance θ<sub>JA</sub> θ<sub>JC</sub>

QFN-34 (4mmx5mm)

| JESD51-7 <sup>(3)</sup> | 38 | .8 | °C/W |

|-------------------------|----|----|------|

| EVQ8875A-VE-00A (4)     | 31 | .3 | °C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature,  $T_J$  (MAX), the junction-toambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) = ( $T_J$  (MAX) -  $T_A$ ) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation can cause excessive die temperature, and the regulator may go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) Measured on JEŠD51-7, 4-layer PCB. The value of θ<sub>JA</sub> given in this table is only valid for comparison with other packages, and cannot be used for design purposes. These values were calculated in accordance with JESD51-7, and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application.

- Measured on EVQ8875A-VE-00A, 4-layer, 9cmx9cm PCB, 2oz copper.

# **ELECTRICAL CHARACTERISTICS**

| Parameters                                    | Symbol              | Condition                                                                                                                                    |                               | Min  | Тур  | Max  | Units |

|-----------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------|------|------|-------|

| Input Supply Voltage                          |                     |                                                                                                                                              |                               |      |      |      |       |

| Input operating range                         | Max                 | Normal input mode                                                                                                                            |                               | 4.5  |      | 36   | V     |

| Input operating range                         | Vin                 | Low input mode, VCC ≥ 2.5                                                                                                                    | 5V                            | 2.2  |      | 36   | V     |

| Input under-voltage                           | Vin_uvlo            | Normal input mode,<br>V <sub>IN</sub> falling edge                                                                                           |                               | 3.2  | 3.6  | 4.2  | V     |

| lockout (UVLO) threshold                      | _                   | Low input mode, VIN falling                                                                                                                  | edge                          | 1.8  | 2.0  | 2.2  | V     |

|                                               |                     | Normal input mode                                                                                                                            |                               |      | 250  |      | mV    |

| Input UVLO hysteresis                         | VIN_UVLO_HYS        | Low input mode                                                                                                                               |                               |      | 225  |      | mv    |

| Minimum input start-up voltage <sup>(7)</sup> | Vin_startup         | Low input mode, $V_{IN}$ rising<br>VCC is powered from VIN,<br>$I_{CC} = 10mA$                                                               | edge,                         |      |      | 3    | V     |

| Input Supply Current                          |                     |                                                                                                                                              |                               |      |      |      |       |

|                                               | _                   | $V_{EN} = 0V, T_J = 25^{\circ}C$                                                                                                             |                               |      |      | 5    |       |

| Shutdown current                              | lin_sd              | $V_{EN} = 0V, T_J = -40^{\circ}C \text{ to } +150^{\circ}C$                                                                                  |                               |      |      | 25   | μA    |

|                                               |                     | $V_{IN} = 12V$ , no switching                                                                                                                | $V_{IN} = 12V$ , no switching |      | 180  | 500  | μA    |

| Quiescent current (normal)                    | IN_Q_NOR            | $V_{IN} = 24V$ , no switching                                                                                                                |                               |      | 180  | 500  | μA    |

| Quiescent current (fault)                     | $I_{IN_Q_FLT}$      | Fault latch condition                                                                                                                        |                               |      | 180  | 500  | μA    |

|                                               | 1                   | $V_{IN} = 12V, V_{OUT} = 11.5V,$<br>no load, buck-boost mode,                                                                                | ССМ                           |      | 33   |      | mA    |

| Active current (normal) <sup>(6)</sup>        |                     | SW1/SW2 switching                                                                                                                            | DCM                           |      | 0.31 |      | mA    |

| Active current (normal)                       | IQ_ACT_NOR          | no load, buck mode.                                                                                                                          | ССМ                           |      | 25   |      | mA    |

|                                               |                     |                                                                                                                                              | DCM                           |      | 0.4  |      | mA    |

| VCC Regulator                                 |                     | ·                                                                                                                                            |                               |      |      |      |       |

| Degulator output voltage                      | VCC                 | $V_{\text{IN}} = 12V,  V_{\text{OUT}} = 5V,  I_{\text{CC}} =$                                                                                | 1mA                           | 4.85 | 5.1  | 5.35 | V     |

| Regulator output voltage                      | VCC                 | $V_{IN} = 3V$ , $V_{OUT} = 5V$ , $I_{CC} = 1mA$                                                                                              |                               | 4.65 | 4.85 |      | V     |

| VCC line regulation                           |                     | $V_{IN} = 5.5V$ to 36V, Icc = 1m                                                                                                             | A                             | -0.5 |      | +0.5 | %     |

| VCC load regulation                           |                     | Icc = 1mA to 30mA                                                                                                                            |                               | -0.7 |      | +0.7 | %     |

| Dropout voltage                               | VCCdrv              | $\label{eq:VIN} \begin{array}{l} V_{\text{IN}} = 2.7 V,  V_{\text{OUT}} = 2.5 V, \\ I_{\text{CC}} = 5 m A \end{array}$                       |                               |      | 100  | 220  | mV    |

|                                               |                     | $\label{eq:Vout} \begin{array}{l} V_{\text{OUT}} = 2.7 \text{V}, \ V_{\text{IN}} = 2.5 \text{V}, \\ I_{\text{CC}} = 5 \text{mA} \end{array}$ |                               |      | 80   | 500  | mV    |

| Short circuit current limitation              | I <sub>CC_MAX</sub> | $V_{CC} = 0V$                                                                                                                                |                               | 40   | 60   | 100  | mA    |

| Parameters                                                       | Symbol                              | Condition                                               | Min  | Тур  | Max        | Units           |

|------------------------------------------------------------------|-------------------------------------|---------------------------------------------------------|------|------|------------|-----------------|

| VCC Regulator                                                    |                                     |                                                         |      |      |            |                 |

| VCC UVLO threshold                                               | VCCUVLO                             | Normal input mode,<br>VCC falling edge                  | 3.2  | 3.4  | 3.6        | V               |

|                                                                  | VCCUVLO                             | Low input mode,<br>VCC falling edge                     | 2.1  | 2.25 | 2.4        | V               |

| VCC UVLO hysteresis                                              | VCCUVLO_HYS                         |                                                         |      | 350  |            | mV              |

| Oscillator                                                       |                                     |                                                         |      |      |            |                 |

| Switching frequency range <sup>(5)</sup>                         | f <sub>SW</sub>                     |                                                         | 200  |      | 1000       | kHz             |

| Frequency PLL accuracy (6)                                       |                                     | fsw = default value in OTP<br>register 0x03h, bits[5:0] | -15  |      | +15        | %               |

| Minimum on time (7)                                              | ton_min                             |                                                         |      | 100  |            | ns              |

| Minimum off time (7)                                             | 4                                   | Buck mode                                               |      | 90   |            | ns              |

| Minimum on time ()                                               | toff_min                            | Boost mode                                              |      | 180  |            | ns              |

| Synchronization frequency range                                  | fsync                               | Sync clock input mode                                   | 250  |      | 1000       | kHz             |

| SYNC input logic high threshold                                  | Vsync_in_h                          | VSYNC rising edge                                       | 1.4  |      |            | V               |

| SYNC input logic low threshold                                   | V <sub>SYNC_IN_L</sub>              | V <sub>SYNC</sub> falling edge                          |      |      | 0.5        | V               |

| SYNC input minimum logic<br>high pulse width                     | tsync_in_pw_min                     |                                                         | 200  |      |            | ns              |

| SYNC output logic high (7)                                       | Vsync_out_h                         |                                                         |      | VCC  |            |                 |

| SYNC output logic low (7)                                        | Vsync_out_l                         |                                                         |      |      | 0.3        | V               |

| SYNC output duty cycle                                           | D <sub>SYNC_OUT</sub>               |                                                         |      | 50   |            | %               |

| <b>Frequency Spread Spectrum</b>                                 |                                     |                                                         |      |      |            |                 |

| Spread spectrum modulation frequency spread range <sup>(5)</sup> | f <sub>FSS</sub>                    |                                                         | ±3%  |      | ±30%       | f <sub>sw</sub> |

| Spread spectrum modulation frequency range <sup>(5)</sup>        | ffssm                               |                                                         | 0.25 |      | 8          | kHz             |

| Enable                                                           |                                     |                                                         |      |      |            |                 |

| Logic enable threshold                                           | $V_{\text{EN}_{\text{LOGIC}}}$      |                                                         | 0.5  | 0.85 | 1.15       | V               |

| System enable threshold                                          | Ven_on                              | V <sub>EN</sub> rising edge                             | 1.4  | 1.55 | 1.7        | V               |

| Pull-up hysteresis current                                       | IEN_HYS                             | After converter works                                   |      | 1.3  |            | μA              |

| Hysteresis voltage                                               | V <sub>EN_SYS</sub>                 |                                                         |      | 150  |            | mV              |

| Bootstrap                                                        |                                     |                                                         |      |      |            |                 |

|                                                                  | VBST1-VSW1                          | $-V_{CC} = 5V$                                          | 4.0  | 47   | <b>F</b> 4 | V               |

| Biased voltage for high-side                                     | V <sub>BST2</sub> -V <sub>SW2</sub> |                                                         | 4.3  | 4.7  | 5.1        |                 |

| driver (Q1/Q3)                                                   | V <sub>BST1</sub> -V <sub>SW1</sub> | Low input mode,<br>$V_{CC} = 2.55V$                     | 1.6  |      |            |                 |

|                                                                  | VBST2-VSW2                          |                                                         | 1.4  |      |            |                 |

| BST UVLO                                                         | VBST1/2_UVLO                        | VBST1/2 - VSW1/2 falling edge                           | 1.1  | 1.6  | 2.1        | V               |

| BST UVLO hysteretic                                              | V <sub>BST1/2_UVLO_HYS</sub>        |                                                         |      | 80   |            | mV              |

| Parameters                                         | Symbol          | Condition                                                              | Min  | Тур  | Max  | Units |

|----------------------------------------------------|-----------------|------------------------------------------------------------------------|------|------|------|-------|

| Power Switches                                     |                 |                                                                        |      |      |      |       |

|                                                    |                 | $V_{CC} = 5V, T_{J} = 25^{\circ}C$                                     |      | 10   | 20   |       |

| Main switch (Q1/Q3)<br>on resistance               |                 | $V_{CC} = 5V, T_J = -40^{\circ}C \text{ to } +150^{\circ}C$            |      | 10   | 25   | mΩ    |

|                                                    | Rds(on)_main    | Low-input mode, $V_{CC} = 2.55V$ ,<br>T <sub>J</sub> = 25°C            |      | 15   | 20   |       |

|                                                    |                 | Low-input mode, $V_{CC} = 2.55V$ ,<br>T <sub>J</sub> = -40°C to +150°C |      | 15   | 30   | mΩ    |

|                                                    |                 | $V_{CC} = 5V, T_J = 25^{\circ}C$                                       |      | 25   | 40   | mΩ    |

|                                                    |                 | $V_{CC} = 5V, T_{J} = -40^{\circ}C \text{ to } +150^{\circ}C$          |      | 25   | 50   | 11122 |

| Synchronous rectifier switch (Q2/Q4) on resistance | Rds(on)_sr      | Low-input mode, $V_{CC} = 2.55V$ ,<br>T <sub>J</sub> = 25°C            |      | 35   | 45   |       |

|                                                    |                 | Low-input mode, $V_{CC} = 2.55V$ ,<br>T <sub>J</sub> = -40°C to +150°C |      | 35   | 60   | mΩ    |

|                                                    | Isw_lkg         | $V_{SW1/SW2} = 36V, T_J = 25^{\circ}C$                                 |      |      | 1    | μA    |

| Switch leakage current                             |                 | Vsw <sub>1/sw2</sub> = 36V,<br>T <sub>J</sub> = -40°C to +150°C        |      |      | 20   |       |

| Peak current limit range (5)                       | Ilmt_pk         | I∟ rising edge                                                         | 2    |      | 9    | Α     |

| Peak current limit accuracy (6)                    |                 | I <sub>LIMT_PK</sub> = 9A                                              | 9    | 12   |      | Α     |

| Reverse current limit range (5)                    | ILIMT_RV        | FCCM, I∟ falling edge                                                  | -2.5 |      | -4.7 | Α     |

| Reverse current limit                              |                 | $I_{\text{LIMT}_{\text{RV}}} = -2.5 \text{A}$                          | -1.8 | -2.5 | -3.5 | A     |

| accuracy                                           |                 | $I_{\text{LIMT}_{\text{RV}}} = -4.7 \text{A}$                          | -3.8 | -4.7 | -6.5 | A     |

| Valley current limit range (5)                     | ILIMIT_VL       | OC fault triggers                                                      | 1    |      | 8    | А     |

| Valley current limit accuracy                      |                 | I <sub>LIMT_VL</sub> = +8A,<br>I <sub>LIMT_RV</sub> = -2.5A            | 6.64 | 8    | 9.36 | A     |

| (6)                                                |                 | I <sub>LIMT_VL</sub> = +8A,<br>I <sub>LIMT_RV</sub> = -4.7A            | 5.6  | 7    | 8.4  |       |

| Zero-current detection (ZCD) threshold             | Izcd            | DCM, I∟ falling edge                                                   |      | 100  |      | mA    |

| Switching slew rate range <sup>(5)</sup>           | SR <sub>R</sub> | Vsw1/2 rising edge                                                     | 1    |      | 2    | V/ns  |

| Switching siew rate range                          | SRF             | Vsw1/2 falling edge                                                    | 1    |      | 2    | V/ns  |

| Parameters                                                  | Symbol               | Condition                                                                                                                | Min  | Тур | Max    | Units |

|-------------------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------|------|-----|--------|-------|

| <b>Output Voltage Regulation</b>                            |                      | •                                                                                                                        | ·    |     | -      |       |

| Output voltage range                                        | Vout                 |                                                                                                                          | 0.5  |     | 30     | V     |

| PVOUT leakage current                                       | I <sub>OUT_LKG</sub> | $V_{IN} = V_{EN} = 0V, V_{OUT} = 12V$                                                                                    |      | 20  | 60     | μA    |

| Deference veltage renge (5)                                 | \/                   | Normal input mode                                                                                                        | 0.5  |     | 2.0    | V     |

| Reference voltage range <sup>(5)</sup>                      | $V_{REF}$            | Low-input mode                                                                                                           | 0.5  |     | 1.2    | V     |

| Reference voltage accuracy                                  |                      | $V_{REF} = 0.5V/1.2V/1.5V/2V,$<br>T <sub>J</sub> = 25°C                                                                  | -2   |     | +2     |       |

|                                                             |                      | $V_{\text{REF}} = 0.5 \text{V}/1.2 \text{V}/1.5 \text{V}/2 \text{V},$<br>T <sub>J</sub> = -40°C to +125°C <sup>(7)</sup> | -2.5 |     | +2.5   | %     |

|                                                             |                      | V <sub>REF</sub> = 0.5V/1.2V/1.5V/2V,<br>T <sub>J</sub> = -40°C to +150°C                                                | -3   |     | +3     |       |

| Output divider ratio range (5)                              | Vref/Vout            |                                                                                                                          | 1/30 |     | 1      |       |

| Dynamic adjustment step interval range <sup>(5)</sup>       | tdv_step             |                                                                                                                          | 20   |     | 166.67 | μs    |

| Dynamic adjustment step<br>interval accuracy <sup>(6)</sup> |                      | t <sub>DV_STEP</sub> = default value in OTP<br>register 0x01h, bits[4:3]                                                 | -15  |     | +15    | %     |

| VFB current                                                 | I <sub>FB</sub>      | V <sub>FB</sub> = 2V                                                                                                     | -100 |     | +100   | nA    |

| Parameters                                                          | Symbol               | Condition                                                     | Min   | Тур | Max   | Units            |

|---------------------------------------------------------------------|----------------------|---------------------------------------------------------------|-------|-----|-------|------------------|

| Buck-Boost Converter                                                |                      |                                                               |       |     |       |                  |

| Boost out of threshold range (5)                                    | VIN_BST_OUT          | V <sub>IN</sub> rising edge                                   | 0.7   |     | 0.9   | Vout             |

| Boost out of threshold accuracy                                     |                      | Vout = 12V                                                    | -0.04 |     | +0.04 | Vout             |

| Boost transition hysteresis range (5)                               | VIN_BST_HYS          |                                                               | 0.05  |     | 0.125 | Vout             |

| Boost transition hysteresis accuracy                                |                      | Vout = 12V                                                    | -0.03 |     | +0.03 | Vout             |

| Buck in threshold range (5)                                         | Vin_bk_in            | V <sub>IN</sub> rising edge                                   | 1.1   |     | 1.3   | Vout             |

| Buck in threshold accuracy                                          |                      | Vout = 12V                                                    | -0.04 |     | +0.04 | Vout             |

| Buck transition hysteresis range (5)                                | VIN_BK_HYS           |                                                               | 0.05  |     | 0.125 | V <sub>OUT</sub> |

| Buck transition hysteresis accuracy                                 |                      | V <sub>OUT</sub> = 12V                                        | -0.03 |     | +0.03 | V <sub>OUT</sub> |

| COT range of boost switch in buck-<br>boost mode <sup>(5) (7)</sup> | t <sub>BST_ON</sub>  |                                                               | 0.2   |     | 0.5   | t <sub>sw</sub>  |

| Input Over-Voltage Protection (OVF                                  | <b>)</b>             | •                                                             |       |     |       | •                |

| Input OVP threshold range (5)                                       | V <sub>IN_OVP</sub>  | V <sub>IN</sub> rising edge                                   | 11    |     | 33    | V                |

| Input OVP threshold accuracy                                        |                      |                                                               | -10   |     | +10   | %                |

| Input OVP hysteresis range (5)                                      | VIN_OVP_HYS          |                                                               | 0.03  |     | 0.05  | VIN              |

| Input OVP hysteresis accuracy                                       |                      |                                                               | -0.02 |     | +0.02 | VIN              |

| Output Over-Voltage Protection (O                                   | VP)                  |                                                               |       |     |       |                  |

| Output OVP threshold range <sup>(5)</sup>                           | V <sub>OUT_OVP</sub> | VOUT rising edge                                              | 1.1   |     | 1.3   | $V_{REF}$        |

| Output OVP threshold accuracy                                       |                      |                                                               | -0.05 |     | +0.05 | VREF             |

| Output OVP recovery threshold range <sup>(5)</sup>                  | VOUT_OVP_REC         | V <sub>OUT</sub> falling edge                                 | 1     |     | 1.05  | VREF             |

| Output OVP recovery threshold accuracy                              |                      |                                                               | -0.04 |     | +0.04 | Vref             |

| Over-Current Protection (OCP)                                       |                      |                                                               |       |     |       | •                |

| OC fault activation delay time range                                | tocp_delay           | Consecutive switching<br>count when COMP level<br>is too high | 32    |     | 256   | tsw              |

| Output Under-Voltage Protection (L                                  | JVP)                 |                                                               |       |     |       |                  |

| Output under-voltage (UV) threshold range <sup>(5)</sup>            | V <sub>OUT_UVP</sub> | V <sub>OUT</sub> falling edge                                 | 0.5   |     | 0.75  | $V_{REF}$        |

| Output UV threshold accuracy                                        |                      |                                                               | -0.04 |     | +0.04 | VREF             |

| Output UV fault activation delay time                               | tuvp_delay           | Consecutive switching<br>count when Vout <<br>Vout_uvp        | 2     |     | 16    | tsw              |

Typical values are at  $V_{IN}$  = 12V,  $V_{EN}$  = 2V,  $T_J$  = 25°C, all voltages with respect to ground, unless otherwise noted. Minimum and maximum values are at  $V_{IN} = 12V$ ,  $V_{EN} = 2V$ ,  $T_J = -40^{\circ}C$  to  $+150^{\circ}C$ , all voltages with respect to ground, guaranteed by characterization, unless otherwise noted.

| Parameters                                              | Symbol                                | Condition                                                                                            | Min   | Тур | Max   | Units     |

|---------------------------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------|-------|-----|-------|-----------|

| Thermal Shutdown                                        |                                       | · · · ·                                                                                              |       |     |       | •         |

| Thermal shutdown threshold range <sup>(5) (7)</sup>     | T <sub>SD</sub>                       | T <sub>J</sub> rising                                                                                | 150   |     | 170   | °C        |

| Thermal shutdown<br>hysteresis range <sup>(5) (7)</sup> | T <sub>HYS</sub>                      |                                                                                                      | 25    |     | 75    | °C        |

| Fault Recovery Timer                                    |                                       |                                                                                                      |       |     |       |           |

| Auto-recovery delay time range <sup>(5) (7)</sup>       | tflt_rec                              | Fault recovery mode is activated, except T <sub>SD</sub>                                             | 2     |     | 16    | ms        |

| Fault reset delay timer (7)                             | tflt_rst                              | After soft start ends during a recovery cycle, consecutive switching count when no fault is detected |       | 30  |       | μs        |

| Power Good Indicator (Oper                              | n Drain)                              |                                                                                                      |       |     |       |           |

| Power good (PG) high limit range <sup>(5)</sup>         | Vout_pg_h                             | Vout rising edge                                                                                     | 1.12  |     | 1.17  | Vref      |

| PG high limit accuracy                                  |                                       |                                                                                                      | -0.04 |     | +0.04 | VREF      |

| PG high limit hysteresis range <sup>(5)</sup>           | Vout_pg_h_hys                         |                                                                                                      | 0.04  |     | 0.06  | Vref      |

| PG high limit hysteresis accuracy                       |                                       |                                                                                                      | -0.02 |     | +0.02 | $V_{REF}$ |

| PG low limit range (5)                                  | $V_{\text{OUT}\_\text{PG}\_\text{L}}$ | Vout falling edge                                                                                    | 0.85  |     | 0.9   | Vref      |

| PG low limit accuracy (6)                               |                                       |                                                                                                      | 0.86  | 0.9 | 0.94  | Vref      |

| PG low limit hysteresis range                           | Vout_pg_l_hys                         |                                                                                                      | 0.04  |     | 0.06  | Vref      |

| PG low limit hysteresis accuracy                        |                                       |                                                                                                      | -0.02 |     | +0.02 | Vref      |

| PG output low voltage                                   | $V_{PG_L}$                            | I <sub>PG_SINK</sub> = 200μA                                                                         |       |     | 0.4   | V         |

| PG leakage current                                      | IPG_LKG                               | V <sub>PG</sub> = 5V                                                                                 |       |     | 1     | μA        |

| PG flip-flop delay timer                                | <b>t</b> PG_DELAY                     | After soft start ends, consecutive switching count when $V_{OUT}$ is in or not in regulation         |       | 30  |       | μs        |

Notes:

Configurable via the I<sup>2</sup>C interface. 5)

Not tested in the entire option range. Only guaranteed for the specified option, which is the default values pre-configured in the OTP 6) register.

Not tested in production. Guaranteed by design and characterization. 7)

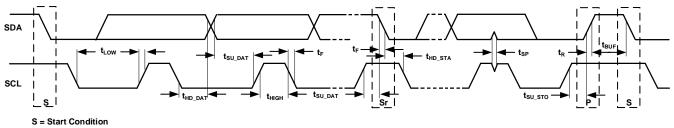

# I<sup>2</sup>C INTERFACE ELECTRICAL CHARACTERISTICS

Typical values are at  $V_{IN}$  = 12V,  $V_{EN}$  = 2V,  $T_J$  = 25°C. Minimum and maximum values are at  $V_{IN}$  = 12V,  $V_{EN}$  = 2V,  $T_J$  = -40°C to +150°C, guaranteed by characterization. All voltages with respect to ground, unless otherwise noted.

| Parameters                                         | Symbol              | Condition   | Min                          | Тур | Max  | Units |

|----------------------------------------------------|---------------------|-------------|------------------------------|-----|------|-------|

| SCL/SDA input logic low                            | VIL                 |             | 0                            |     | 0.8  | V     |

| SCL/SDA input logic high                           | VIH                 |             | 1.5                          |     |      | V     |

| SCL/SDA output logic low                           | Vol                 | ILOAD = 3mA |                              |     | 0.4  | V     |

| SCL clock frequency                                | fsc∟                |             |                              |     | 400  | kHz   |

| SCL high time                                      | tніgн               |             | 0.6                          |     |      | μs    |

| SCL low time                                       | t <sub>LOW</sub>    |             | 1.3                          |     | 1.67 | μs    |

| Data set-up time                                   | tsu_dat             |             | 100                          |     |      | ns    |

| Data hold time                                     | t <sub>HD_DAT</sub> |             | 0.25                         |     | 0.9  | μs    |

| Set-up time for repeated start                     | t <sub>su_sta</sub> |             | 0.6                          |     |      | μs    |

| Hold time for start                                | <b>t</b> hd_sta     |             | 0.6                          |     |      | μs    |

| Bus free time between a start and a stop condition | tbuf                |             | 1.3                          |     |      | μs    |

| Set-up time for stop condition                     | tsu_s⊤o             |             | 0.6                          |     |      | μs    |

| SCL/SDA rise time                                  | t <sub>R</sub>      |             | 20 + 0.1<br>х С <sub>в</sub> |     | 300  | ns    |

| SCL/SDA fall time                                  | t⊧                  |             | 20 + 0.1<br>х С <sub>в</sub> |     | 300  | ns    |

| Pulse width of suppressed spike                    | tsp                 |             | 0                            |     | 50   | ns    |

| Capacitance bus for each bus line                  | Св                  |             |                              |     | 400  | pF    |

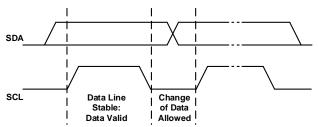

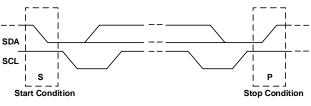

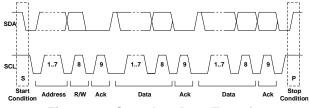

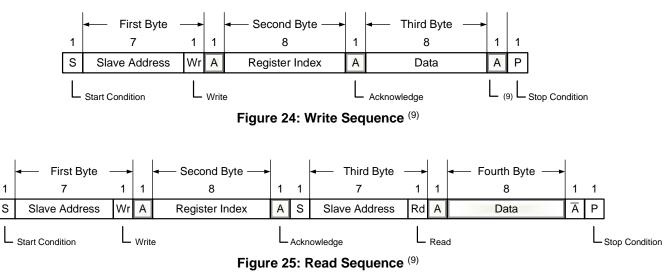

# I<sup>2</sup>C-COMPATIBLE INTERFACE TIMING DIAGRAM

Sr = Repeated Start Condition P = Stop Condition

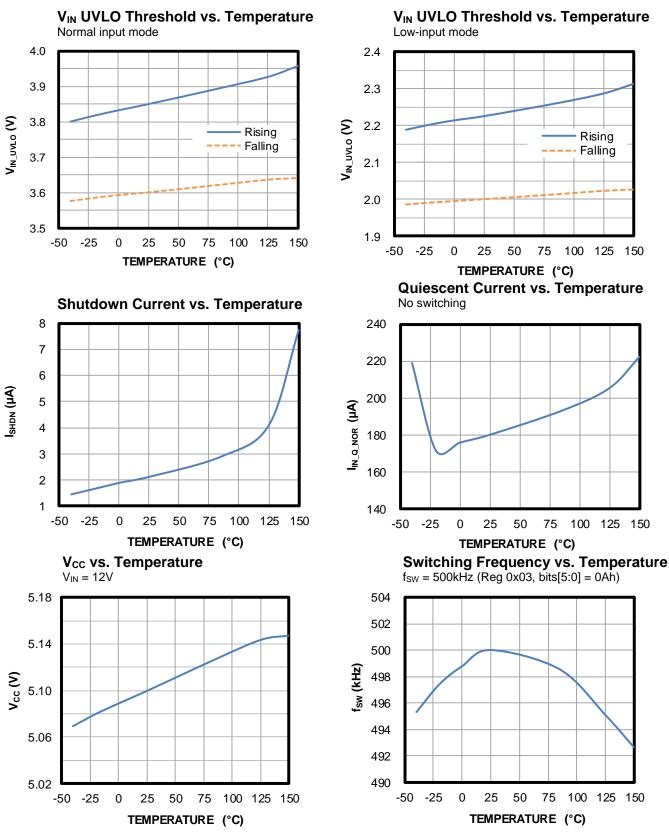

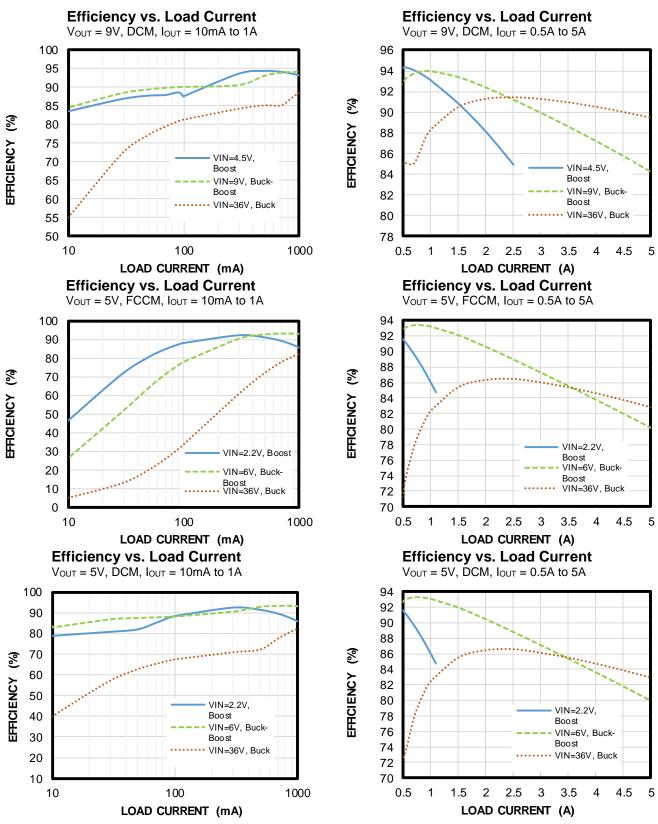

# TYPICAL CHARACTERISTICS

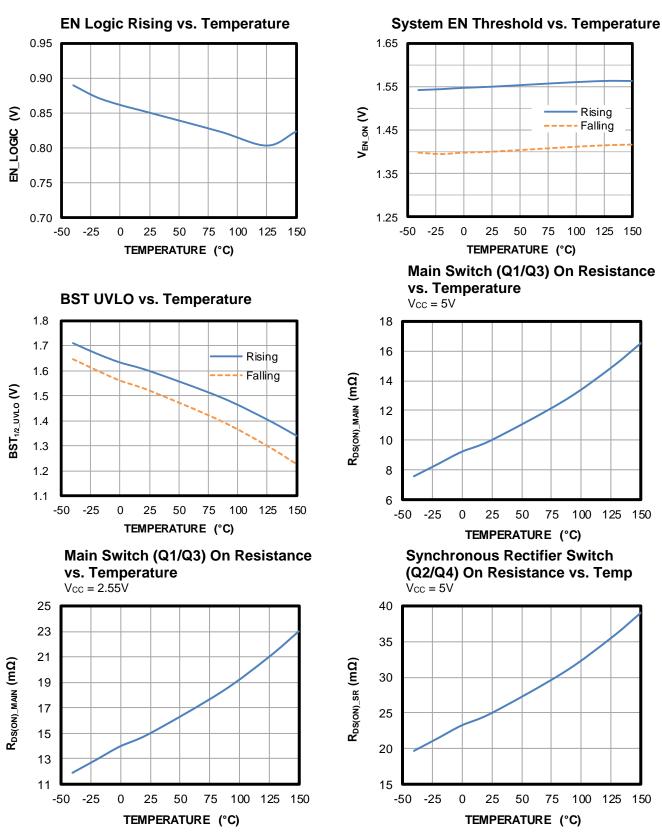

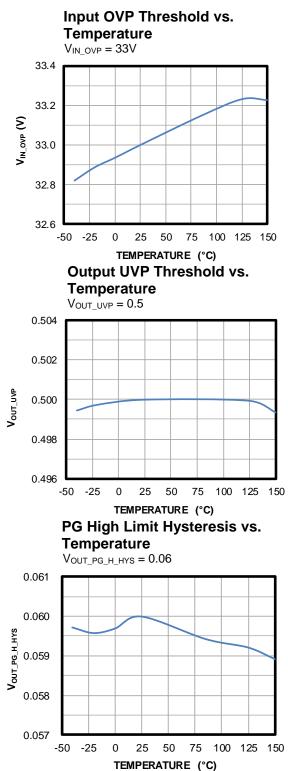

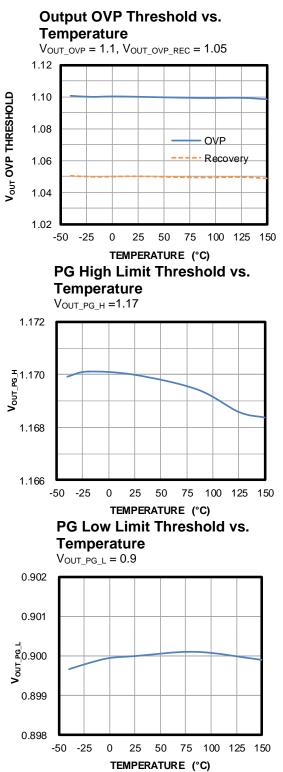

$V_{IN} = 12V$ ,  $T_J = -40^{\circ}C$  to +150°C, unless otherwise noted.

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2021 MPS. All Rights Reserved.

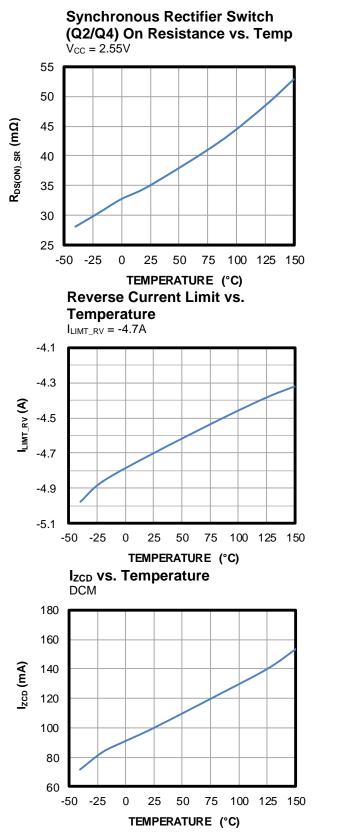

$V_{IN}$  = 12V,  $T_J$  = -40°C to +150°C, unless otherwise noted.

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2021 MPS. All Rights Reserved.

$V_{IN} = 12V$ ,  $T_J = -40^{\circ}C$  to  $+150^{\circ}C$ , unless otherwise noted.

Valley Current Limit vs. Temperature  $I_{LIMT\_VL} = 8A$

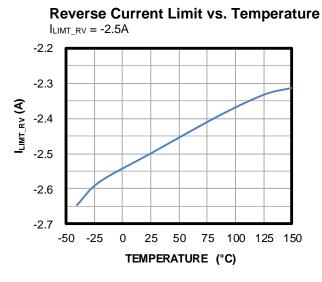

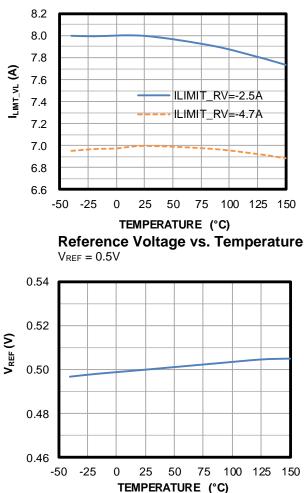

$V_{IN}$  = 12V,  $T_J$  = -40°C to +150°C, unless otherwise noted.

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2021 MPS. All Rights Reserved.

$V_{IN}$  = 12V,  $T_J$  = -40°C to +150°C, unless otherwise noted.

$V_{IN}$  = 12V,  $T_J$  = -40°C to +150°C, unless otherwise noted.

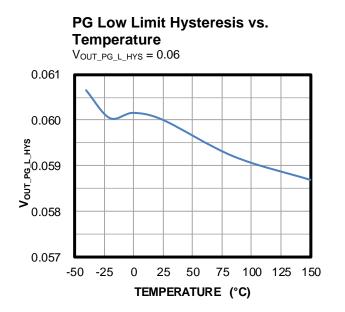

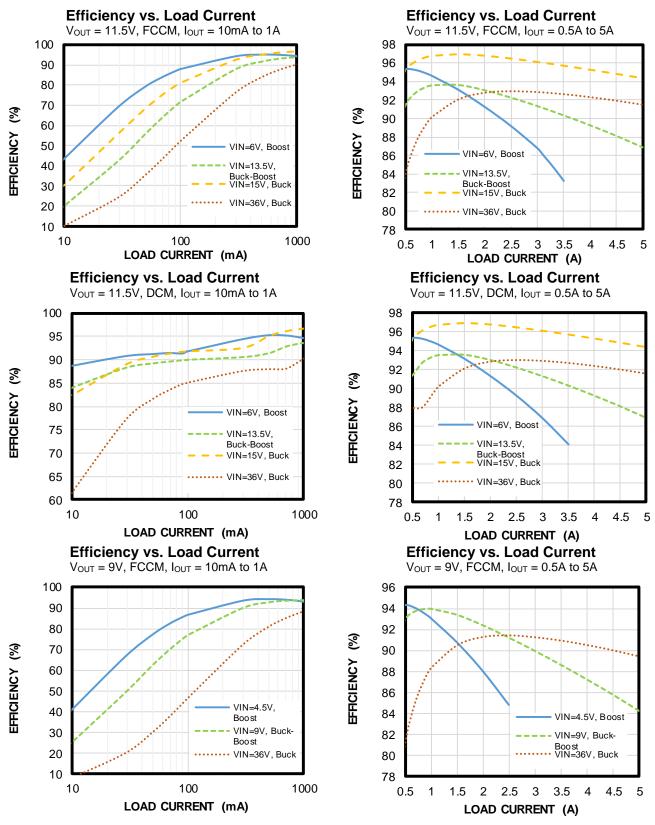

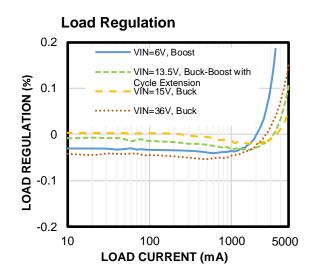

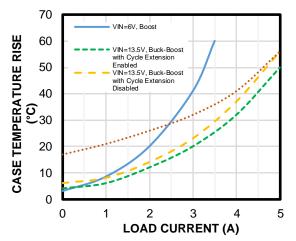

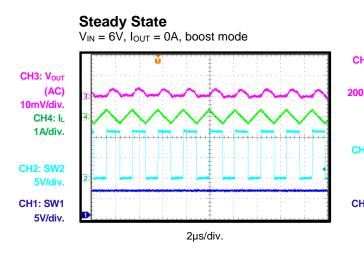

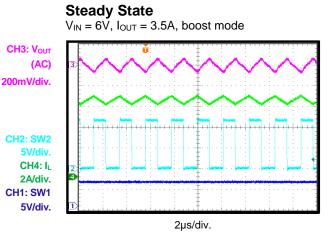

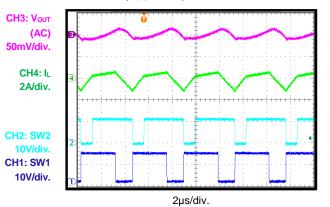

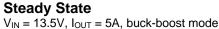

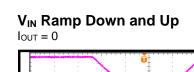

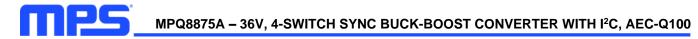

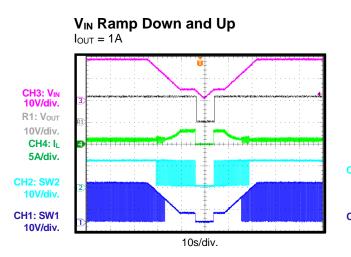

# **TYPICAL PERFORMANCE CHARACTERISTICS**

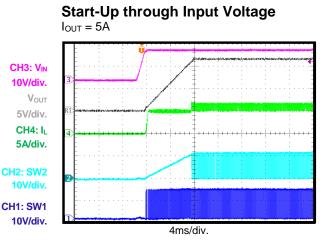

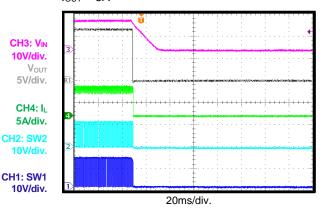

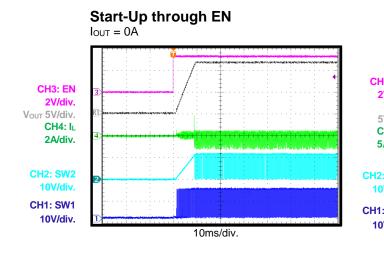

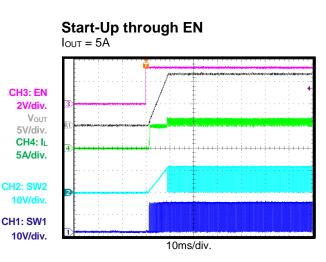

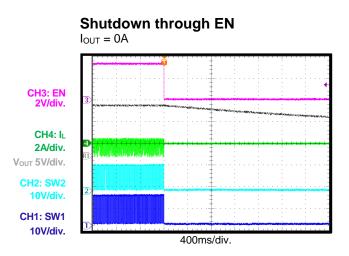

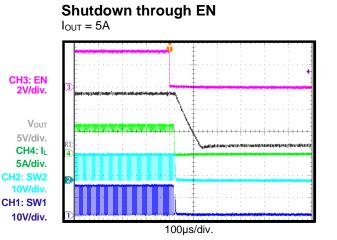

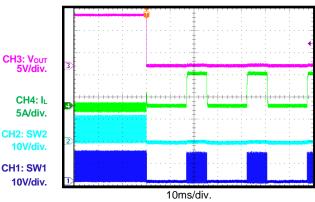

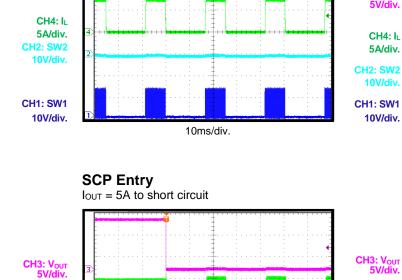

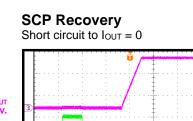

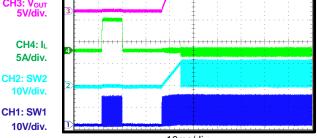

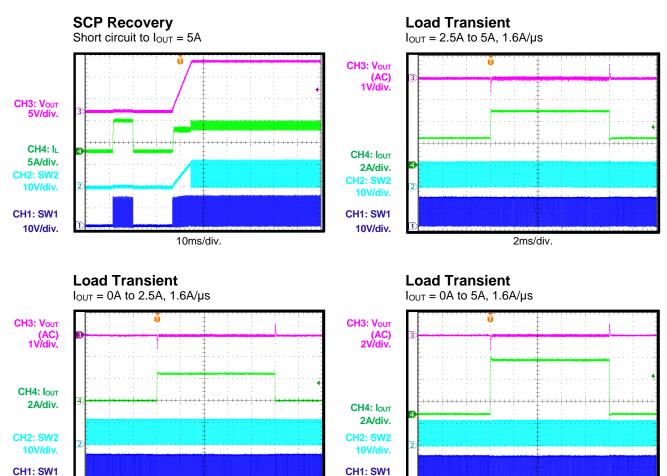

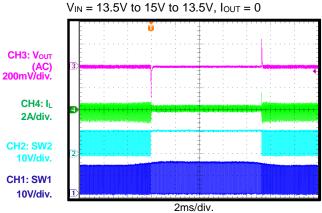

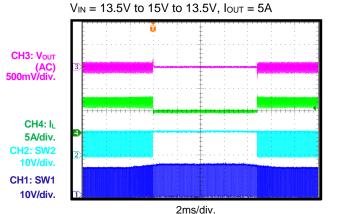

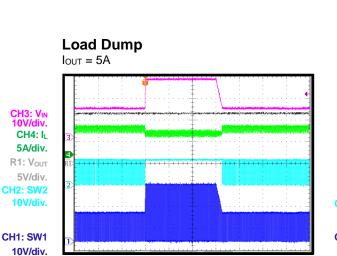

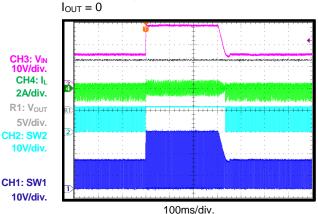

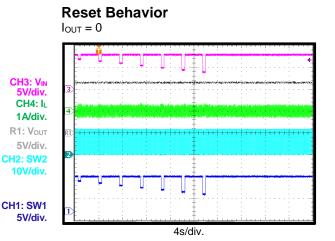

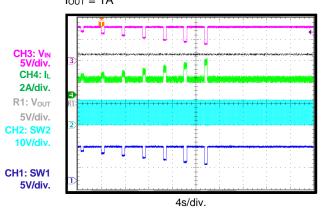

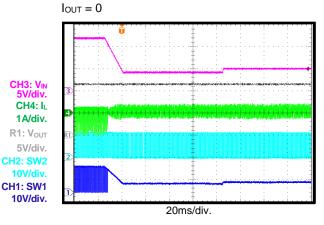

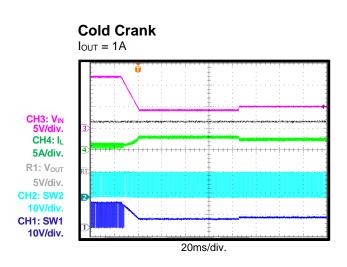

$V_{IN}$  = 13.5V,  $V_{OUT}$  = 11.5V, L = 10µH,  $C_{OUT}$  = 40µF,  $f_{SW}$  = 450kHz, FCCM,  $T_A$  = 25°C, unless otherwise noted.

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2021 MPS. All Rights Reserved.

$V_{IN}$  = 13.5V,  $V_{OUT}$  = 11.5V, L = 10µH,  $C_{OUT}$  = 40µF,  $f_{SW}$  = 450kHz, FCCM,  $T_A$  = 25°C, unless otherwise noted.

MPQ8875A Rev. 1.0 1/4/2021 MPS

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2021 MPS. All Rights Reserved.

$V_{IN}$  = 13.5V,  $V_{OUT}$  = 11.5V, L = 10µH,  $C_{OUT}$  = 40µF,  $f_{SW}$  = 450kHz, FCCM,  $T_A$  = 25°C, unless otherwise noted.

# Case Temperature Rise vs. Load Current

$V_{IN}$  = 13.5V,  $V_{OUT}$  = 11.5V, L = 10µH,  $C_{OUT}$  = 40µF,  $f_{SW}$  = 450kHz, FCCM,  $T_A$  = 25°C, unless otherwise noted.

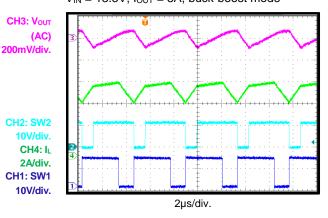

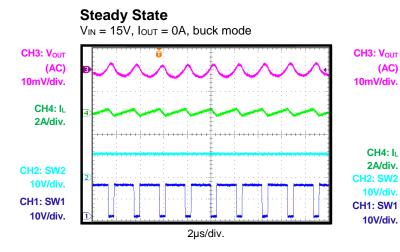

Steady State

$V_{IN} = 13.5V$ ,  $I_{OUT} = 0A$ , buck-boost mode

2µs/div.

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2021 MPS. All Rights Reserved.

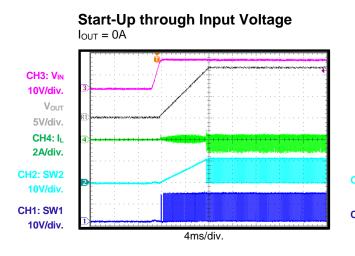

$V_{IN}$  = 13.5V,  $V_{OUT}$  = 11.5V, L = 10µH,  $C_{OUT}$  = 40µF,  $f_{SW}$  = 450kHz, FCCM,  $T_A$  = 25°C, unless otherwise noted.

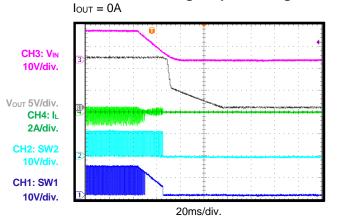

Shutdown through Input Voltage

#### Shutdown through Input Voltage Iout = 5A

$V_{IN} = 13.5V$ ,  $V_{OUT} = 11.5V$ ,  $L = 10\mu$ H,  $C_{OUT} = 40\mu$ F,  $f_{SW} = 450$ kHz, FCCM,  $T_A = 25^{\circ}$ C, unless otherwise noted.

**SCP Steady State**

CH3: V<sub>IN</sub> 10V/div.

CH4: IL

5A/div.

CH2: SW2

**CH1: SW1**

10V/div.

10V/div.

SCP Entry  $I_{OUT} = 0$  to short circuit

10ms/div.

10ms/div.

CH4: I∟

10V/div.

**CH1: SW1**

10V/div.

$V_{IN}$  = 13.5V,  $V_{OUT}$  = 11.5V, L = 10µH,  $C_{OUT}$  = 40µF,  $f_{SW}$  = 450kHz, FCCM,  $T_A$  = 25°C, unless otherwise noted.

10V/div.

2ms/div.

2ms/div.

10V/div.

$V_{IN} = 13.5V$ ,  $V_{OUT} = 11.5V$ ,  $L = 10\mu$ H,  $C_{OUT} = 40\mu$ F,  $f_{SW} = 450$ kHz, FCCM,  $T_A = 25^{\circ}$ C, unless otherwise noted.

#### CH4: I 2A/div. CH2: SW2 10V/div.

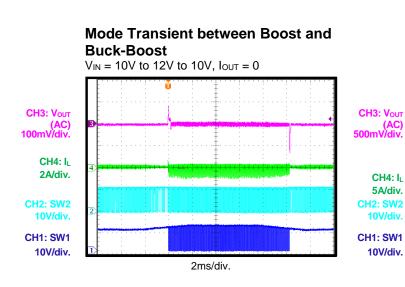

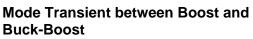

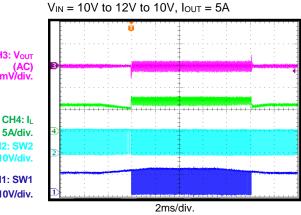

#### Mode Transient between Buck and **Buck-Boost**

#### Mode Transient between Buck and **Buck-Boost**

100ms/div.

#### Load Dump

MPQ8875A Rev. 1.0 1/4/2021

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2021 MPS. All Rights Reserved.

$V_{IN}$  = 13.5V,  $V_{OUT}$  = 11.5V, L = 10µH,  $C_{OUT}$  = 40µF,  $f_{SW}$  = 450kHz, FCCM,  $T_A$  = 25°C, unless otherwise noted.

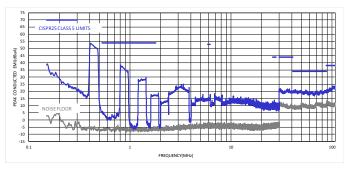

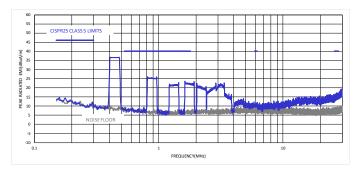

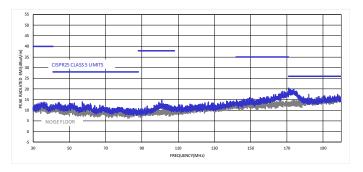

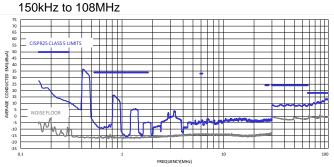

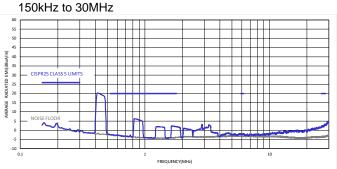

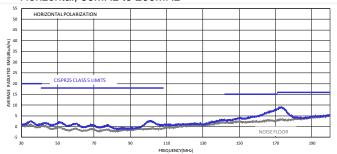

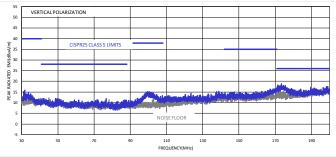

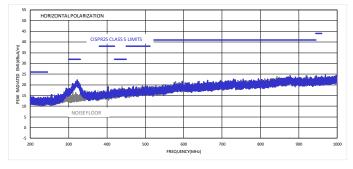

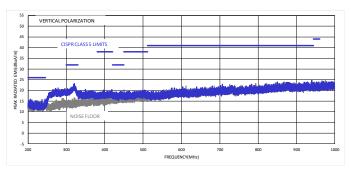

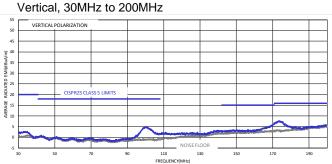

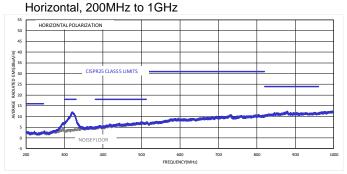

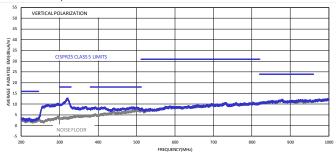

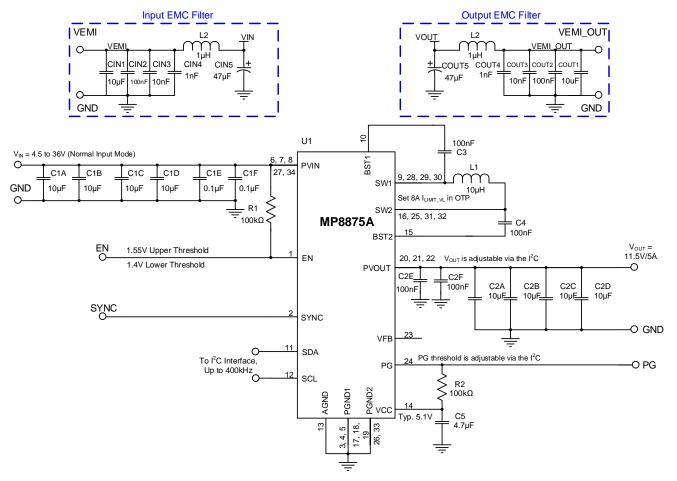

$V_{IN}$  = 12V,  $V_{OUT}$  = 11.5V,  $I_{OUT}$  = 5A, L = 10µH,  $f_{SW}$  = 450kHz, in buck-boost mode, with EMI filters and FSS enabled,  $T_A$  = 25°C, unless otherwise noted. <sup>(8)</sup>

CISPR25 Class 5 Peak Conducted Emissions 150kHz to 108MHz

# CISPR25 Class 5 Peak Radiated Emissions 150kHz to 30MHz

#### CISPR25 Class 5 Peak Radiated Emissions Horizontal, 30MHz to 200MHz

# CISPR25 Class 5 Average Conducted Emissions

#### CISPR25 Class 5 Average Radiated Emissions

#### CISPR25 Class 5 Average Radiated Emissions

Horizontal, 30MHz to 200MHz

$V_{IN} = 12V$ ,  $V_{OUT} = 11.5V$ ,  $I_{OUT} = 5A$ ,  $L = 10\mu$ H,  $f_{SW} = 450$ kHz, in buck-boost mode, with EMI filters and FSS enabled,  $T_A = 25^{\circ}C$ , unless otherwise noted. <sup>(8)</sup>

#### **CISPR25 Class 5 Peak Radiated Emissions**

Vertical, 30MHz to 200MHz

#### **CISPR25 Class 5 Peak Radiated Emissions** Horizontal, 200MHz to 1GHz

#### **CISPR25 Class 5 Peak Radiated Emissions** Vertical, 200MHz to 1GHz

#### **CISPR25 Class 5 Average Radiated** Emissions

#### CISPR25 Class 5 Average Radiated Emissions

#### **CISPR25 Class 5 Average Radiated** Emissions

Vertical, 200MHz to 1GHz

#### Notes:

8) All EMC test results are based on the application circuit with EMI filters (see Figure 34 on page 64).

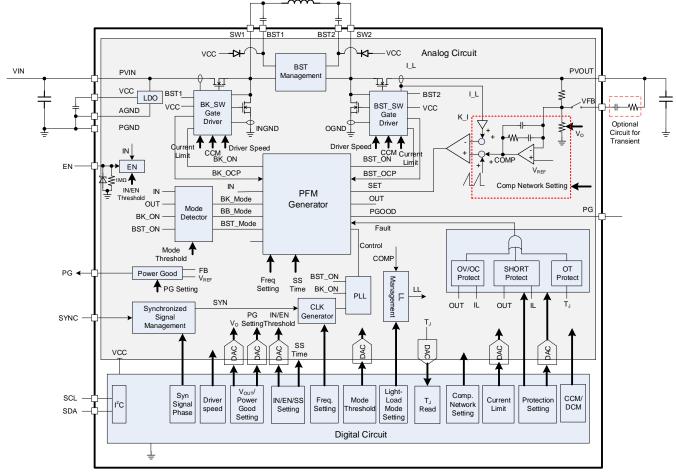

### FUNCTIONAL BLOCK DIAGRAM

Figure 1: Functional Block Diagram

## **OPERATION**

MPQ8875A is The 36V. а monolithic, synchronous buck-boost DC/DC converter with a 2.2V to 36V input voltage range. The wide input voltage (V<sub>IN</sub>) range makes this device well-suited for multi-purpose automotive and industrial applications.

integrated, low-resistance Four N-channel MOSFETs minimize the size of the external circuitry. These N-channel MOSFETs also allow the converter to regulate the output voltage  $(V_{OUT})$  when  $V_{IN}$  is above, below, or equal to V<sub>OUT</sub>. The flexible topology transitions reduce power losses to maximize efficiency.

In addition, the proprietary constant-on-time (COT) control algorithm ensures seamless transitions between the adjacent operational regions. The MPQ8875A can operate across a wide 200kHz to 1MHz switching frequency. This allows applications to be optimized for board size, efficiency, and electromagnetic compatibility (EMC). Most of the electrical characteristics can be configured by accessing the related internal registers via the device's I<sup>2</sup>C interface.

#### VCC Regulator

In normal operation, an internal low-dropout (LDO) regulator outputs a nominal 5V VCC supply from PVIN. This supplies power to both control blocks and the four MOSFETs' gate drivers. The VCC regulator has a 60mA current limit to prevent short circuiting the VCC rail. Add a 1µF to 10µF, low-ESR ceramic capacitor to act as the bypass capacitor from VCC to AGND.

The VCC supply cannot maintain a 5V output once PVIN drops below 5V. If PVOUT is sufficient for the VCC power supply (e.g. in boost mode), the reserved 4.55V regulator takes over the VCC supply from PVOUT.

VCC must exceed 2.25V for applications where the input voltage goes down to 2.2V.

#### Internal Under-Voltage Lockout (UVLO)

Under-voltage lockout (UVLO) is implemented to avoid the chip (or some blocks) from operating at an insufficient supply voltage. The MPQ8875A incorporates three internal, fixed UVLO comparators to monitor PVIN, VCC, and BST.

There are two PVIN input ranges that can be selected by the I<sup>2</sup>C interface: 4.5V to 36V for normal input mode, and 2.2V to 36V for lowinput mode. The PVIN/VCC UVLO levels are not identical when there are different voltage ranges.

The chip is disabled immediately if either PVIN or VCC falls below its respective UVLO threshold. The I<sup>2</sup>C interface cannot work if VCC is not valid.

If V<sub>IN</sub> falls below its UVLO threshold, all switching actions are disabled. Then the COMP voltage is pulled down until VIN exceeds the start-up voltage threshold.

Similarly, if VCC drops below its UVLO threshold, the chip stops switching. Then the COMP voltage is pulled down until VCC rises again.

Since VCC is the internal LDO output from PVIN (or PVOUT in some cases), the actual VCC voltage is determined by  $V_{IN}$  and the dropout voltage of the VCC regulator. The dropout voltage depends on the load current drawn from VCC. In scenarios with a higher switching frequency or larger FET driving capacity demand, the VCC regulator dropout voltage can rise. This means that the VCC can reach its UVLO threshold before the PVIN pin drops below its UVLO threshold.

BST UVLO indicates that there is inadequate driving capacity for the high-side MOSFET (HS-FET). Under this circumstance, the chip stops the HS-FETs from switching and pulls down COMP. The bootstrap charger conducts the low-side MOSFETs (LS-FETs) to charge the BST voltage. The converter restarts with soft start when the BST voltage exceeds its UVLO threshold.

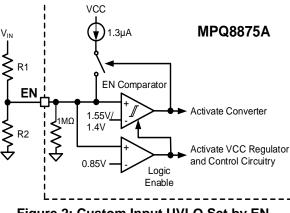

#### On/Off Control and Custom Input Under-Voltage Lockout (UVLO)

When EN is driven above its logic threshold (typically 0.85V), the VCC regulator is activated. Once VCC exceeds the VCC UVLO threshold, it starts to provide power to the internal control circuitry. Then the integrated EN comparator begins working.

If the EN voltage exceeds the comparator's upper threshold (typically 1.55V), the converter is enabled and soft start begins. If EN drops below the comparator's lower threshold, the converter stops switching. The VCC regulator and control circuitry continue working until the EN pin is pulled below its logic threshold (<0.5V). Then the MPQ8875A shuts down and consumes very little input current. The total supply current is reduced to <25µA.

In addition to serving as normal on/off logic control, the integrated EN comparator can set the EN pin to a custom input UVLO threshold by adding an external resistor divider from PVIN to GND (see Figure 2).

Figure 2: Custom Input UVLO Set by EN

The EN voltage is set via the resistor divider ratio from PVIN. When EN reaches 1.55V (the rising UVLO threshold of the integrated EN comparator), the converter starts switching, Meanwhile, an internal 1.3µA pull-up current source is enabled to source current from the EN pin.

To disable the converter when  $V_{IN}$  drops, the EN voltage must drop below the UVLO threshold of the EN comparator. This means VIN must fall enough to overcome the hysteresis from the 1.3µA pull-up current, as well as the inherent 150mV hysteresis of the EN comparator. As a result, the actual hysteresis can be set independently without changing the rising UVLO threshold.

In addition to EN logic, the converter can be turned on/off via the I<sup>2</sup>C interface. Set register 01h, bit[7] to 1 to turn the MPQ8875A on; set it to 0 to turn the MPQ8875A off.

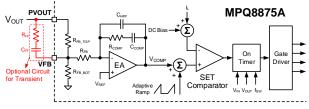

#### Constant-On-Time (COT) Control

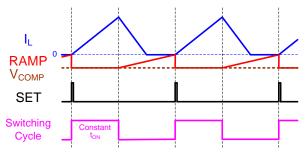

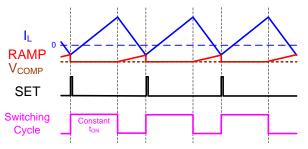

The MPQ8875A employs constant-on-time (COT) control to achieve fast load transient response. Figure 3 shows the COT control block diagram.

**Figure 3: COT Control**

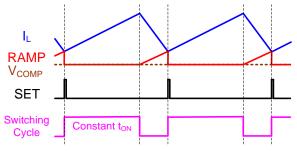

The operational error amplifier (EA) corrects any error voltage between VFB and VREF. With the help of the EA, the MPQ8875A can provide excellent load regulation across the whole load range, regardless of whether the device operates in forced continuous conduction mode (FCCM) or discontinuous conduction mode (DCM). It also features internal ramp compensation. The adaptive internal ramp is optimized so that the converter is stable across the entire operating voltage range, with proper design of the external components. Figure 4 shows how the switching cycle is generated.

**Figure 4: Switching Cycle Generation**

The EA corrects the error between  $V_{FB}$  and  $V_{REF}$ to output a fairly smooth DC voltage (V<sub>COMP</sub>). The internal ramp compensation is added onto V<sub>COMP</sub>. The combined V<sub>COMP</sub> is compared to the inductor current-sense signal  $(I_1)$ .

When  $I_L$  drops below the combined  $V_{COMP}$ , the set comparator outputs a SET signal to begin a new switching cycle. The converter's on time is fixed and determined by  $V_{IN}$ ,  $V_{OUT}$ , and the selected switching frequency. Once the on interval elapses, the main MOSFET turns off. Then the coupled synchronous rectifier (SR) switch turns on after a dead time to avoid shoot-through.

MPQ8875A - 36V, 4-SWITCH SYNC BUCK-BOOST CONVERTER WITH I<sup>2</sup>C, AEC-Q100

In FCCM, the SR switch remains on until the next SET signal comes or the reverse current limit is triggered. By repeating this operation, the MPQ8875A regulates  $V_{\text{OUT}}$ .

#### **Four-Switch Power Converter**

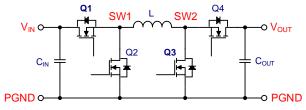

Figure 5 shows the topology of the four-switch power converter, which is comprised of four N-channel MOSFETs. Q1 and Q3 work as the main switches, while Q2 and Q4 act as the SR switches. The switches are properly controlled so that transitions between buck, buck-boost, and boost mode is continuous according to  $V_{\rm IN}$  and  $V_{\rm OUT}$ .

Figure 5: Four-Switch Power Converter

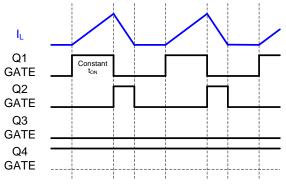

When stepping down from a higher  $V_{IN}$  to a lower  $V_{OUT}$ , the converter operates in buck mode (see Figure 6 and Figure 7). Q4 remains on and Q3 remains off for the entire switching cycle. Q1 and Q2 switch alternately, and behave like a typical synchronous buck converter. Q1's on time is fixed, and the off time can be adjusted via the control algorithm. Figure 6 shows buck mode in FCCM.

Figure 7 shows buck mode in DCM.

Figure 7: Buck Mode in DCM

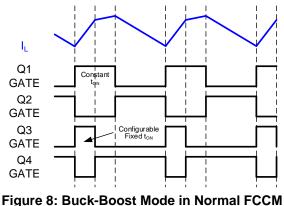

If  $V_{IN}$  is close to  $V_{OUT}$ , the converter enters buck-boost mode (see Figure 8 and Figure 9). Q1 and Q2 still operate independently like a synchronous buck regulator. Q1's on time is fixed, and its off time can be adjusted by the control algorithm. Q3 switches on synchronously with Q1, and remains on for a constant duty cycle, which can be configured based on the switching frequency. Then Q3 turns off, and Q4 switches on.

When Q1 and Q4 are on at the same time, the voltage across inductor is the voltage difference between  $V_{IN}$  and  $V_{OUT}$ . This value is so low that the inductor current is smooth during this period.

Figure 8 shows buck-boost mode in FCCM when  $V_{\text{IN}}$  exceeds  $V_{\text{OUT}}$ .

(VIN > VOUT)

Figure 9 shows buck-boost mode in DCM when  $V_{\text{IN}}$  exceeds  $V_{\text{OUT}}.$

Figure 9: Buck-Boost Mode in Normal DCM (V<sub>IN</sub> > Vout)

Figure 10 shows buck-boost mode in FCCM when  $V_{\text{OUT}}$  exceeds  $V_{\text{IN}}.$

Figure 10: Buck-Boost Mode in Normal FCCM (VIN < VOUT)

Figure 11 shows buck-boost mode in FCCM when  $V_{\text{OUT}}$  exceeds  $V_{\text{IN}}.$

Figure 11: Buck-Boost Mode in Normal DCM (V<sub>IN</sub> < V<sub>OUT</sub>)

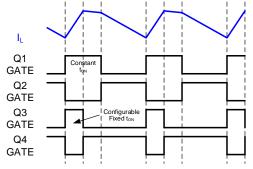

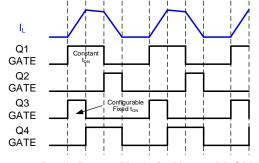

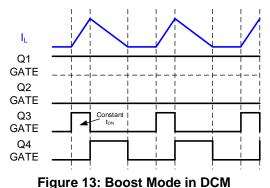

If  $V_{IN}$  is below  $V_{OUT}$ , the MPQ8875A operates in boost mode (see Figure 12 and Figure 13). Q1 remains on and Q2 remains off for the entire switching cycle. Q3 and Q4 are modulated to switch alternately, behaving like a typical synchronous boost regulator. Q3's on time is fixed, and its off time can be adjusted by the control algorithm.

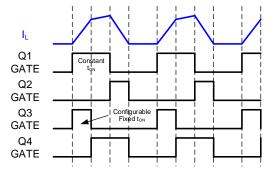

Figure 12 shows boost mode in FCCM.

Figure 12: Boost Mode in FCCM

Figure 13 shows boost mode in DCM.

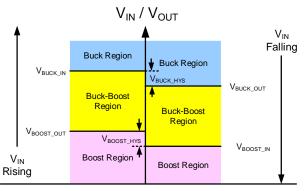

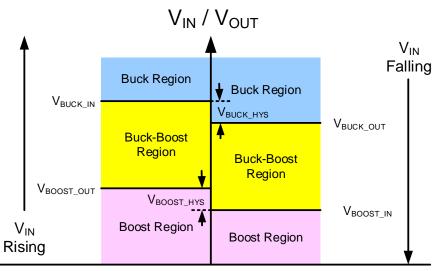

The mode-to-mode transition is automatic by comparing the sensed  $V_{IN}$  and sensed  $V_{OUT}$ . Figure 14 shows the power converter's regions of operation.

Figure 14: Regions of Operation

If  $V_{\rm IN}$  is significantly lower than the sensed  $V_{\rm OUT},$  the MPQ8875A works in boost mode. When  $V_{\rm IN}$  exceeds  $V_{\rm BOOST\_OUT},$  the device transitions into buck-boost mode. If  $V_{\rm IN}$  reaches  $V_{\rm BUCK\_IN},$  then buck mode is activated. Alternately, if  $V_{\rm IN}$  drops from a higher value to a lower one, the converter operates in buck mode, buck-boost mode, and boost mode successively.

avoid unexpected, To repetitive mode transitions when  $V_{IN}$  is close to the critical status between adjacent regions, there is a transition threshold hysteresis.

## **Bootstrap and Floating Driver**

The bootstrap circuitry drives the high-side Nchannel MOSFETs (Q1 and Q4). The external flying capacitors are charged up to maintain a sufficient driving voltage above SW via the internal bootstrap regulators.

At start-up, the bootstrap pre-charge process starts before the converter is ready for normal operation. Both LS-FETs (Q2 and Q3) turn on to force SW1 and SW2 low, allowing the bootstrap regulators to charge the flying capacitors from the VCC supply via the BST1 and BST2 pins, respectively. If the current limit is triggered, the LS-FETs turn off. The LS-FETs may switch several times before building up enough driving voltage across the flying capacitors. Then soft start begins.

If the converter is operating in buck-boost mode, the flying BST capacitor can be charged while the corresponding LS-FET is conducted.

However, in buck mode and boost mode, one HS-FET remains on, and its relevant LS-FET remains off for the entire switching cycle. Under this condition, the BST capacitors can charge each other through the internal charge regulator.

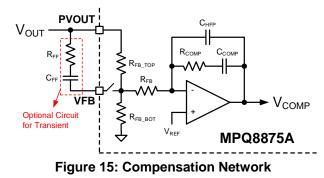

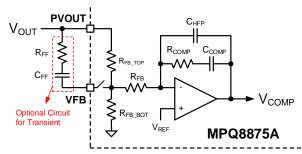

## Error Amplifier

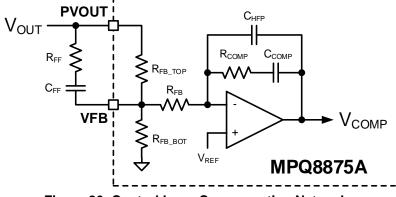

The MPQ8875A integrates a high-performance operational amplifier to implement control loop compensation for stable V<sub>OUT</sub> regulation (see Figure 15).

Figure 15 shows the typical Type Ш compensation network that is fully integrated into the MPQ8875A. Component values can be configured via the I<sup>2</sup>C interface. An external Vout sensing resistor divider, as well as

compensation network components, are not required.

To optimize the converter's transient response, a Type III compensation network is also available. The Type III compensation network is comprised of the internal, existing Type II compensation network, plus an external RC compensation network tied between the PVOUT and VFB pins (see Figure 15). If a Type III compensation network or an external output voltage sensing resistor divider is required, set 0Dh, bit[1] to 1.

### **Oscillator and Synchronization Input/Output**

MPQ8875A converter's The switching frequency can be configured to be between 200kHz and 1MHz via the I<sup>2</sup>C interface. The COT control algorithm determines the on time based on V<sub>IN</sub>, V<sub>OUT</sub>, and the operating switching frequency.

For EMI-sensitive applications, the switching clock can be synchronized to an external clock signal applied the SYNC pin to if synchronization input mode is enabled. The synchronization clock frequency ranges between 250kHz and 1MHz, and must be 20% greater than the configured frequency set in the one-time programmable (OTP) register. The square-wave amplitude should have a peak above 1.4V and a valley below 0.5V. The width of the synchronization pulse should be >200ns.

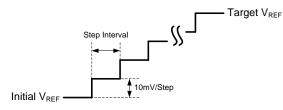

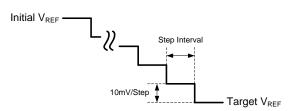

The MPQ8875A can operate in the designated switching frequency (via the I<sup>2</sup>C interface or external clock signal) in FCCM. Once the converter enters DCM, the switching frequency is self-adjusting based on the control algorithm.