#### The Future of Analog IC Technology

#### DESCRIPTION

The MPQ8039 is a general purpose, high frequency half bridge power driver capable of driving a 9A load. The device integrates both top and bottom N-Channel MOSFET power switches and is fully protected from both sourcing and sinking current by a preset cycle-by-cycle current limit. It has a wide input voltage range from 7.5V to 25V.

The MPQ8039 features a low-current shutdown mode, input under-voltage protection, thermal shutdown. It interfaces with standard logic signals and is available in a small SOIC8E package.

#### FEATURES

- Guaranteed Industrial/Automotive Temp.

Range Limits

- ±9A Peak Current Output

- ±4.25A Continuous Current Output

- Up to 1.2MHz Switching Frequency

- Protected Integrated Power 100mΩ Switches

- All Switches Current Limited

- Integrated Under-Voltage Protection

- Integrated Thermal Protection

- 2.5µA Standby Mode

- True 2-Quadrant Operation

- Sources and Sinks Current

- Available in AEC-Q100 Qualified Grade

#### **APPLICATIONS**

- Class D Audio Driver

25W/4Ω/10% Output Power Single Ended

70W/4Ω/10% Output Power Full Bridge

- Full or Half Bridge DC-DC Switching Regulator

- Motor Driver

All MPS parts are lead-free and adhere to the RoHS directive. For MPS green status, please visit MPS website under Products, Quality Assurance page. "MPS" and "The Future of Analog IC Technology" are Trademarks of Monolithic Power Systems, Inc.

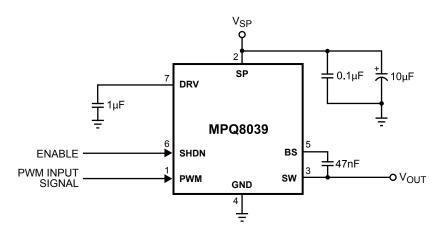

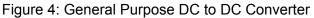

### TYPICAL APPLICATION

## ORDERING INFORMATION

| Part Number      | Package | Top Marking |  |  |

|------------------|---------|-------------|--|--|

| MPQ8039GN*       | SOIC8E  | MP8039      |  |  |

| MPQ8039GN-AEC1** | SOIC8E  | MP8039      |  |  |

\* For Tape & Reel, add suffix -Z (eg. MPQ8039GN-Z)

\*\* For Tape & Reel, add suffix –Z (eg. MPQ8039GN-AEC1–Z)

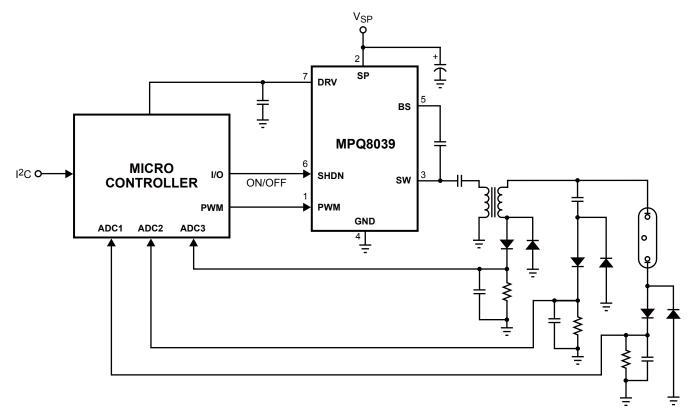

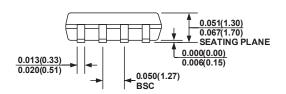

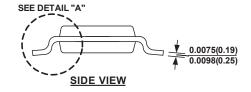

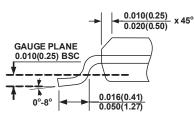

#### PACKAGE REFERENCE

#### ABSOLUTE MAXIMUM RATINGS (1)

| SP Supply Voltage (V <sub>SP</sub> ) | 0.3V to +28V <sup>(5</sup> ) |

|--------------------------------------|------------------------------|

| SW Pin Voltage                       | –0.3V to V <sub>SP</sub>     |

| SW to BS                             |                              |

| Voltage at All Other Pins            |                              |

| Continuous Power Dissipation         | $(T_A = +25^{\circ}C)^{(2)}$ |

|                                      | 2.5W                         |

| Storage Temperature                  | –55°C to +150°C              |

#### Recommended Operating Conditions <sup>(3)</sup>

| SP Supply Voltage (V <sub>SP</sub> )       | 7.5V to 24V     |

|--------------------------------------------|-----------------|

| Peak Output Current                        | 9A Maximum      |

| Operating Junction Temp. (T <sub>J</sub> ) | )40°C to +125°C |

## Thermal Resistance $^{(4)}$ $\theta_{JA}$

Notes:

Absolute maximum ratings are rated under room temperature unless otherwise noted. Exceeding these ratings may damage the device.

$\theta_{JC}$

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature TJ (MAX), the junction-to-ambient thermal resistance 0JA, and the ambient temperature TA. The maximum allowable continuous power dissipation at any ambient temperature is calculated by PD (MAX) = (TJ (MAX)-TA)/0JA. Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the device will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on approximately 1" square of 1 oz copper.

- 5) For room temperature only.

### **ELECTRICAL CHARACTERISTICS**

$V_{SP}$  = 12V,  $V_{SHDN}$  = 0V,  $T_{J}$  = -40°C to +125°C, Typical value are  $T_{J}$  = 25°C, unless otherwise noted.

| Parameter                                      | Symbol           | Condition                                                                    | Min | Тур  | Max  | Units |

|------------------------------------------------|------------------|------------------------------------------------------------------------------|-----|------|------|-------|

| SP Operating Current                           |                  |                                                                              |     | 1.5  | 2.5  | mA    |

| SP Shutdown Current                            |                  | V <sub>SHDN</sub> = 2V                                                       |     | 2.5  | 10   | μA    |

| SHDN, SP Threshold Low                         |                  |                                                                              |     |      | 1    | V     |

| SHDN, SP Threshold High                        |                  |                                                                              | 2   |      |      | V     |

| SHDN, SP Input Bias Current                    |                  |                                                                              |     | 1    |      | μA    |

| SW On Resistance                               |                  | $V_{SP}$ = 7.5V, High-Side and Low-Side                                      |     | 0.1  | 0.25 | Ω     |

| SW Current Limit (5)                           |                  | V <sub>PWM</sub> = 5, (Sinking)                                              |     | 9    |      | Α     |

|                                                |                  | V <sub>PWM</sub> = 0, (Sourcing)                                             |     | 9    |      | Α     |

| SW Switching Frequency                         |                  | V <sub>PWM</sub> = 0 to 2V, 50% Duty Cycle                                   |     |      | 1.2  | MHz   |

| SW Maximum Duty Cycle (6)                      |                  | $V_{SP}$ = 7.5V, $V_{PWM}$ = 2V, $C_{SW}$ 100nF,<br>f <sub>SW</sub> = 3.3kHz |     | 99.5 |      | %     |

| SW Rise/Fall Time                              |                  | V <sub>PWM</sub> = 0 to 5V                                                   |     | 20   |      | ns    |

| PWM Pulse Width                                |                  | $V_{PWM}$ = 0 to 2V, High or Low Pulse                                       | 200 |      |      | ns    |

| PWM to SW Delay Time Rising                    |                  | V <sub>PWM</sub> = 0 to 5V                                                   |     | 70   |      | ns    |

| PWM to SW Delay Time<br>Falling                |                  | V <sub>PWM</sub> = 5 to 0V                                                   |     | 70   |      | ns    |

| Thermal Shutdown<br>Temperature <sup>(5)</sup> |                  | T <sub>J</sub> Rising, Hysteresis = 20°C                                     |     | 160  |      | °C    |

| IN UVLO                                        |                  | Rising Edge                                                                  | 5.5 |      | 7.5  | V     |

| DRV Voltage                                    | V <sub>DRV</sub> | V <sub>SP</sub> =10V                                                         | 5.1 | 5.6  | 6.0  | V     |

| DW/M Threaded Violtage                         |                  | V <sub>PWM</sub> Rising                                                      |     |      | 2.4  | V     |

| PWM Threshold Voltage                          |                  | V <sub>PWM</sub> Falling                                                     | 1.3 |      |      | V     |

Notes:

6) Not production tested.

7) SW drives low for 1.5µs every 300µs to charge the BS to SW capacitor.

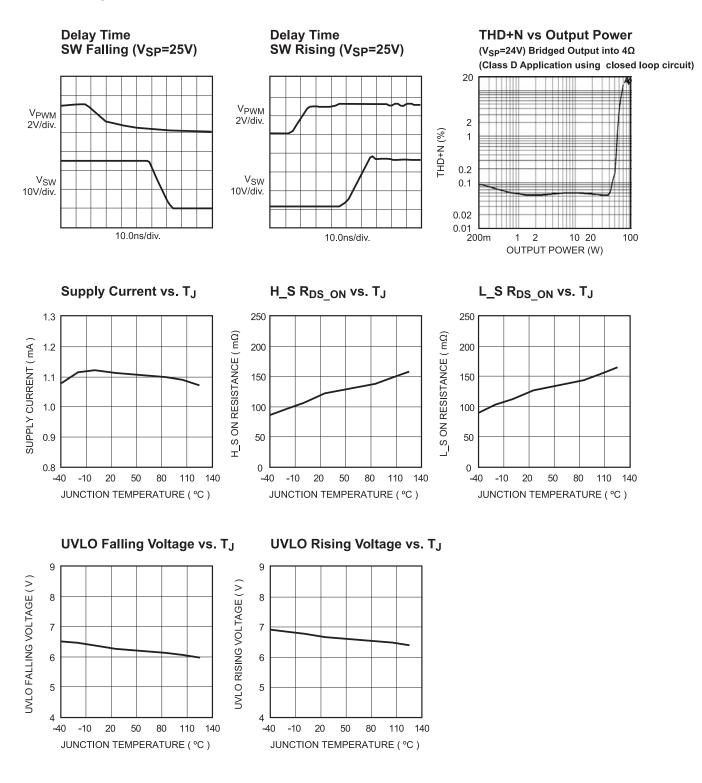

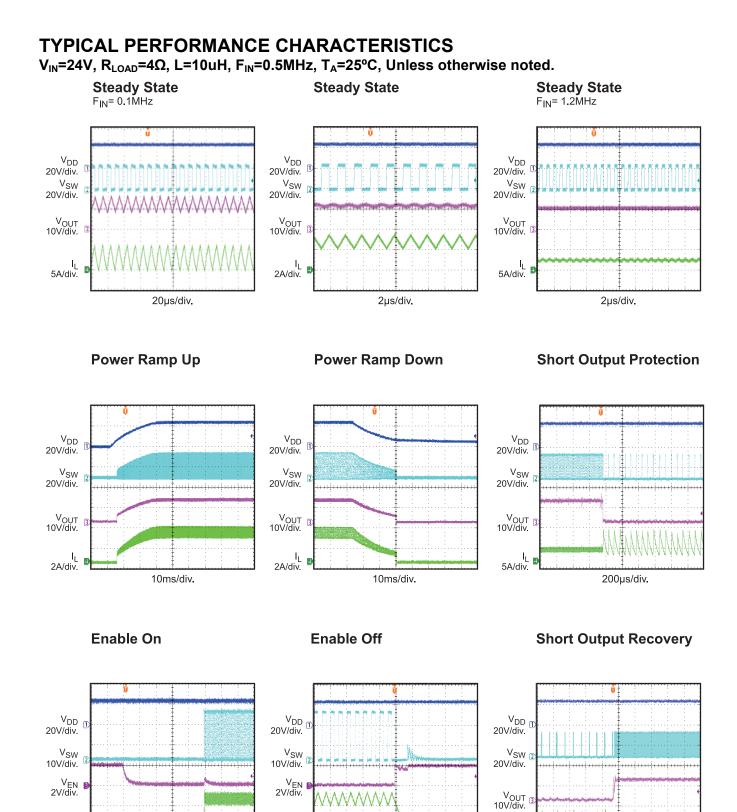

### **TYPICAL PERFORMANCE CHARACTERISTICS**

Circuit of Figure 4,  $T_A = +25^{\circ}C$ , unless otherwise noted.

100µs/div.

ا 2A/div.

> www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2016 MPS. All Rights Reserved.

2ms/div.

ا 5A/div

100µs/div.

Ι<sub>L</sub> 2A/div.

### **PIN FUNCTIONS**

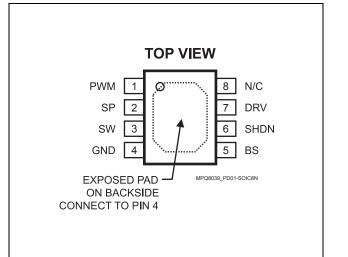

| Pin # | Name | Description                                                                                                                                                                                                                 |  |  |

|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1     | PWM  | Driver Logic Input. Drive PWM with the signal that controls the MPQ8039 output. Drive PWM high to turn on the high-side switch; drive PWM low to turn on the low-side switch.                                               |  |  |

| 2     | SP   | Power Supply Input. Connect SP to the positive side of the input power supply. Bypass SP to GND as close to the IC as possible.                                                                                             |  |  |

| 3     | SW   | Switched Output. SW is the power output of the MPQ8039. Connect the output LC filter to SW. SW is valid approximately 100µs after SP goes high.                                                                             |  |  |

| 4     | GND  | Ground. (Note: Connect the exposed pad on the bottom side to Pin 4).                                                                                                                                                        |  |  |

| 5     | BS   | Bootstrap Supply. BS powers the high-side gate of the MPQ8039. Connect a $0.1\mu F$ or greater capacitor between BS and SW.                                                                                                 |  |  |

| 6     | SHDN | Shutdown Input. SHDN enables/disables the MPQ8039. Drive SHDN low to turn on the MPQ8039, drive it high to turn it off. If not used, connect SHDN to GND.                                                                   |  |  |

| 7     | DRV  | Gate Drive Supply Bypass. The voltage at DRV is supplied from an internal regulator from SP. DRV powers the internal circuitry and internal MOSFET gate drives. Bypass DRV to GND with a $0.1\mu$ F to $10\mu$ F capacitor. |  |  |

| 8     | N/C  |                                                                                                                                                                                                                             |  |  |

#### **OPERATION**

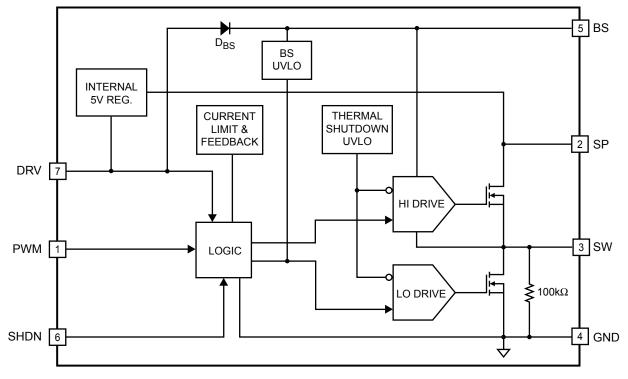

The MPQ8039 is a general purpose, power driver. It takes a logic input and drives a half bridge comprised of  $0.1\Omega$  high-side and low-side N-Channel MOSFET switches.

It operates at frequencies up to 1.2MHz, can accept a DC supply voltage as high as 25V, and produce peak output current as high as 9A.

Figure 1: Function Block Diagram

#### SW Output

The SW output drives the load. It is controlled by the logic input signal at PWM. When the signal at PWM is high (above 2V), the high-side switch is turned on. When the signal at PWM is low (less than 0.4V), the low-side switch is turned on.

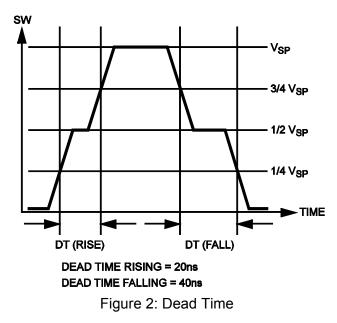

The MPQ8039 uses internal N-Channel MOSFETs for both the high-side and low-side switches. The high-side MOSFET gate drive is powered from the voltage between SW and BS, allowing BS to rise above the SP input voltage to power the high-side MOSFET. To do this a bootstrap capacitor is connected between SW and BS. When the low-side switch is on, the capacitor is internally charged from the voltage at DRV, which is also internally generated. There is a dead time region (typically 40ns) where both the upper and lower switches are off (see Figure 2).

Both the high-side and low-side switches have internal current limits to prevent failure due to excessive load current. Once the current limit is reached, both output switches are turned off and the fault output is asserted (driven low).

#### Shutdown

The MPQ8039 includes a  $2.5\mu$ A shutdown mode. When SHDN is high, both output switches are turned off and the input current drops to  $2.5\mu$ A. When the MPQ8039 is shutdown, the internally generated voltage at DRV drops to 0V. If the shutdown mode is not used, connect SHDN directly to GND.

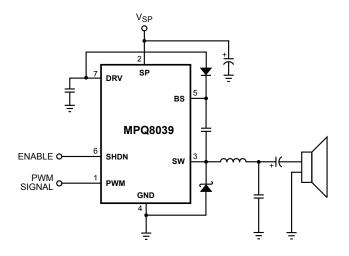

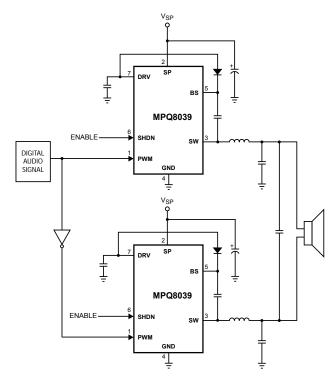

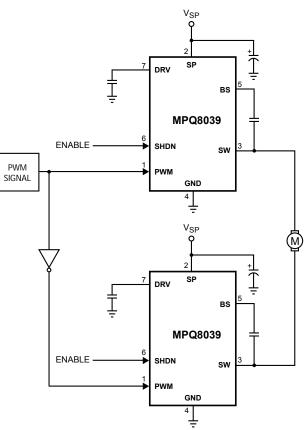

### **TYPICAL APPLICATION CIRCUITS**

#### Figure 3: Single Ended Audio Amplifier

Figure 5: 80W Full Bridge Audio Amplifier

Figure 6: Full Bridge Motor Driver

Figure 7: CCFL Driver Circuit

#### PACKAGE INFORMATION

0.089(2.26) 0.101(2.56)

BOTTOM VIEW

FRONT VIEW

RECOMMENDED LAND PATTERN

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Monolithic Power Systems (MPS):

MPQ8039GN-AEC1-Z MPQ8039GN-Z MPQ8039GN-P MPQ8039GN-AEC1-P