# **MPQ7795**

# 2.2MHz, Low-EMI, 24.5W, Mono BTL Class-D Audio Amplifier with Diagnostics, AEC-Q100 Qualified

#### DESCRIPTION

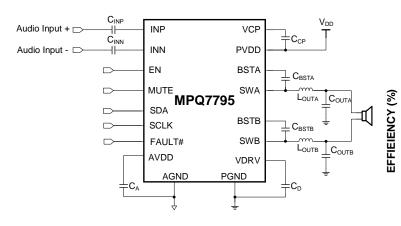

The MPQ7795 is an automotive-grade, low-EMI, differential analog input Class-D audio amplifier with I<sup>2</sup>C diagnostics. The device is a fully integrated audio amplifier that can drive a mono speaker in a bridge-tied load (BTL) configuration, and it significantly reduces the solution size.

The MPQ7795 utilizes a BTL structure capable of delivering 24.5W into  $4\Omega$  speakers with a 14.4V power supply (PV<sub>DD</sub>). MPS's Class-D audio amplifiers exhibit the high fidelity of Class-AB amplifiers, as well as high efficiency.

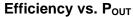

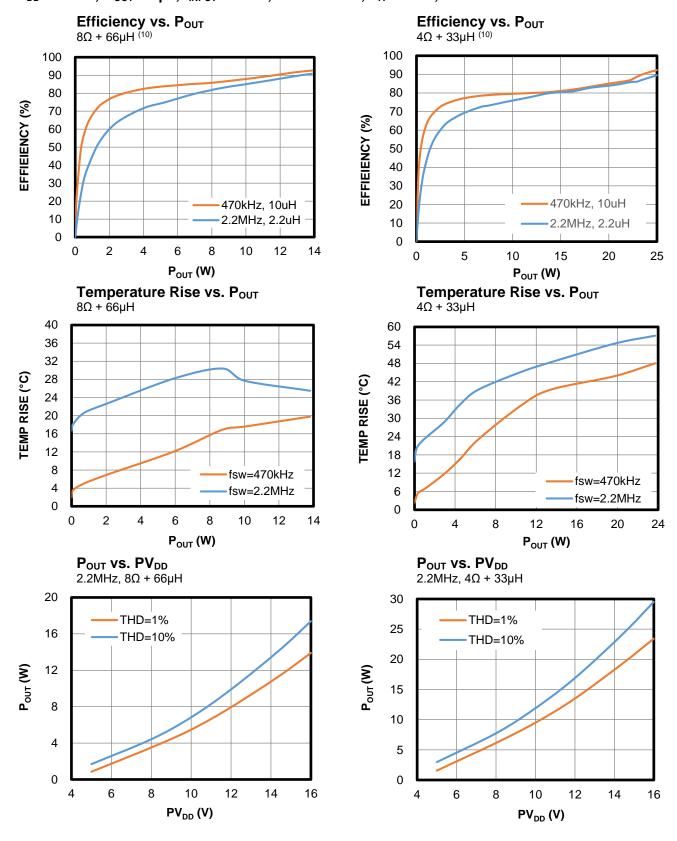

The switching frequency (f<sub>SW</sub>) can be set to 330kHz, 384kHz, 470kHz, or 2.2MHz. The MPQ7795's efficiency exceeds 90% during both 470kHz and 2.2MHz operation.

The MPQ7795 integrates a load diagnostic function that detects open load, short load, load-to-GND short, and load-to-PVDD short conditions. The diagnostics work when the device is enabled, which protects the load and the device.

In addition to over-current protection (OCP), under-voltage protection (UVP), and over-temperature protection (OTP), the MPQ7795 features an adjustable power limit ( $P_{\text{LIMIT}}$ ) function. The  $P_{\text{LIMIT}}$  circuit sets a limit on the output's peak-to-peak voltage ( $V_{\text{PK-PK}}$ ). This is accomplished by limiting the duty cycle to a fixed maximum value. This limit can be considered a virtual voltage rail, and it is below the supply connected to PVDD.

The device statuses can be reported to the microcontroller (MCU) via the I<sup>2</sup>C interface. The parameters can also be set via the I<sup>2</sup>C interface.

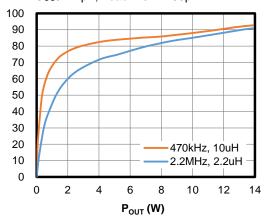

The MPQ7795 is available in a QFN-24 (4mmx4mm) package, and is AEC-Q100 qualified.

3/22/2023

### **FEATURES**

- Built to Handle Automotive Transients:

- Load Dump Up to 42V

- Cold Crank Down to 4.5V

- Cooler Thermals:

- Deliver 24.5W into 4Ω Loads with 14.4V  $PV_{DD}$

- High Power Efficiency

- Up to 92.6% for 8Ω Load

- Up to 90.4% for 4Ω Load

- Less than 20°C Junction Temperature (T<sub>J</sub>) Rise at 8Ω, 14W/470kHz

- Low-Ohmic BCD FET Technology

- Low EMI/EMC Noise:

- Meet CISPR 25 Class 5

- MeshConnect<sup>TM</sup> Flip-Chip Packaging

- Operates Outside of AM Radio Band

- Extends Vehicle Battery Life:

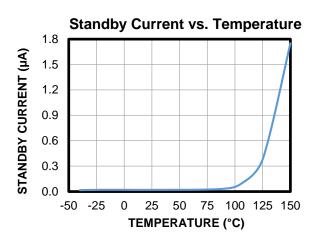

- 0.02µA Standby Current (I<sub>QSTBY</sub>)

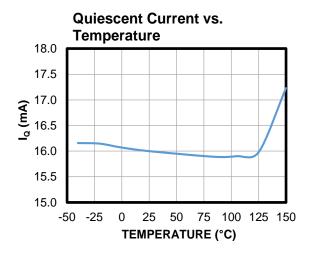

- 16mA Quiescent Current (I<sub>Q</sub>)

- Additional Features:

- Load Diagnostics:

- Open Load or Short Load

- Output Short to PVDD or Ground

- Status Report with I<sup>2</sup>C and Fault Pin

- Start-Up/Shutdown Pop Elimination

- 150mΩ Power MOSFETs

- 80dB PSRR at 100Hz

- Selectable Voltage Gain

- Adjustable Power Limiter

- Communicates with MCU via I<sup>2</sup>C Interface

- $\circ$  Supports 2Ω to 16Ω Speakers

- Available in a QFN-24 (4mmx4mm)

Package

- Available in a Wettable Flank Package

- Available in AEC-Q100 Grade 1

#### **APPLICATIONS**

- Automotive E-Call Systems

- Telematics Systems

- Infotainment Audio

- Cluster Systems

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

1

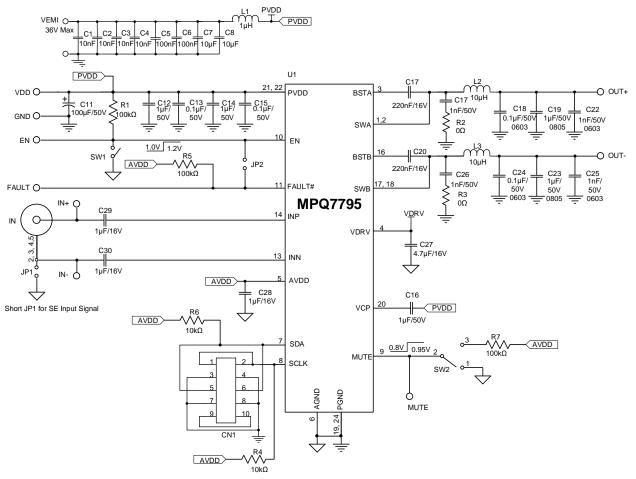

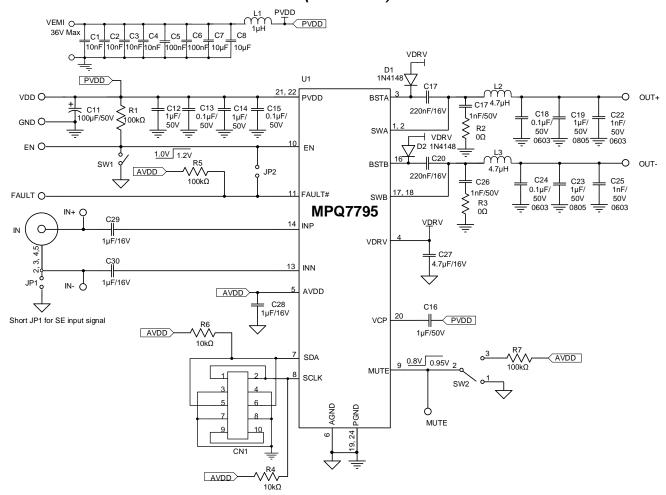

# **TYPICAL APPLICATION**

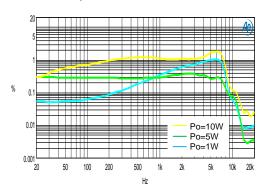

**Efficiency vs. Pout** PV<sub>DD</sub> = 14.4V, f<sub>INPUT</sub> = 1kHz, gain = 20dB,  $C_{OUT} = 1\mu F$ , Load =  $8\Omega + 66\mu H$

#### ORDERING INFORMATION

| Part Number*       | Package          | Top Marking | MSL Rating** |

|--------------------|------------------|-------------|--------------|

| MPQ7795GRE-AEC1*** | QFN-24 (4mmx4mm) | See Below   | 1            |

\* For Tape & Reel, add suffix -Z (e.g. MPQ7795GRE-AEC1-Z).

\*\* Moisture Sensitivity Level Rating

\*\*\* Wettable Flank

# **TOP MARKING (MPQ7795GRE-AEC1)**

MPSYWW MP7795 LLLLLL E

MPS: MPS prefix Y: Year code WW: Week code MP7795: Part number LLLLL: Lot number E: Wettable Flank

#### PACKAGE REFERENCE

# **PIN FUNCTIONS**

| Pin#          | Name   | Description                                                                                                                                                                                                                   |

|---------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2          | SWA    | Switched power output for amplifier A (the positive output).                                                                                                                                                                  |

| 3             | BSTA   | <b>High-side MOSFET bootstrap input for amplifier A.</b> A capacitor connected from BSTA to SWA supplies the gate drive current to the internal high-side MOSFET (HS-FET).                                                    |

| 4             | VDRV   | <b>Gate drive supply bypass.</b> The VDRV pin powers the internal circuitry, internal MOSFET gate drive, and the power limit ( $P_{\text{LIMIT}}$ ) function. Bypass VDRV to AGND with a 4.7 $\mu$ F to 10 $\mu$ F capacitor. |

| 5             | AVDD   | Internal analog reference. Connect a bypass capacitor from the AVDD pin to AGND.                                                                                                                                              |

| 6             | AGND   | Analog ground.                                                                                                                                                                                                                |

| 7             | SDA    | I <sup>2</sup> C data pin.                                                                                                                                                                                                    |

| 8             | SCLK   | I <sup>2</sup> C clock pin.                                                                                                                                                                                                   |

| 9             | MUTE   | <b>Mute control.</b> Drive the MUTE pin above 0.95V to disable output switching; drive MUTE below 0.8V to allow for switching.                                                                                                |

| 10            | EN     | <b>Enable input.</b> Drive EN above 1.2V to turn on the amplifiers; drive EN below 1V to turn them off.                                                                                                                       |

| 11            | FAULT# | <b>Fault output.</b> The FAULT# pin has a low output to indicate whether the IC has detected a fault. This output is an open drain.                                                                                           |

| 12, 15,<br>23 | NC     | No connection. Tie the NC pin to ground or leave it floating.                                                                                                                                                                 |

| 13            | INN    | Negative audio input. The INN pin is biased at 2V.                                                                                                                                                                            |

| 14            | INP    | Positive audio input. The INP pin is biased at 2V.                                                                                                                                                                            |

| 16            | BSTB   | <b>High-side MOSFET bootstrap input for amplifier B.</b> A capacitor connected from BSTB to SWB supplies the gate drive current to the internal HS-FET.                                                                       |

| 17, 18        | SWB    | Switched power output for amplifier B (the negative output).                                                                                                                                                                  |

| 19, 24        | PGND   | Power ground for amplifier.                                                                                                                                                                                                   |

| 20            | VCP    | Charge pump output for boost capacitor. Connect a capacitor from VCP to PVDD.                                                                                                                                                 |

| 21, 22        | PVDD   | <b>Power supply input.</b> Bypass the PVDD pin to PGND with a 1µF, X7R capacitor (in addition to the main bulk capacitor), placed close to the PVDD and PGND pins.                                                            |

#### **ABSOLUTE MAXIMUM RATINGS** (1)

| Supply voltage (PV <sub>DD</sub> )                  | 0.3V to +42V                   |

|-----------------------------------------------------|--------------------------------|

| V <sub>SWA</sub> , V <sub>SWB</sub>                 | 1V to PV <sub>DD</sub> + 1V    |

| V <sub>EN</sub> 0                                   | .3V to $PV_{DD} + 0.3V$        |

| V <sub>VDRV</sub>                                   | 0.3V to +5.5V                  |

| AVDD                                                |                                |

| BS voltage (V <sub>BSTA</sub> )V <sub>SWA</sub> - 0 | 0.3V to V <sub>SWA</sub> +5.5V |

| BS voltage (V <sub>BSTB</sub> )V <sub>SWB</sub> - 0 |                                |

| V <sub>VCP</sub> 0                                  | $.3V$ to $PV_{DD} + 5.5V$      |

| V <sub>VCP</sub> to V <sub>BSTX</sub>               |                                |

| V <sub>BSTX</sub> to V <sub>VDRV</sub>              | 0.3V to +40V                   |

| AGND to PGND                                        | 0.3V to +0.3V                  |

| All other pins                                      | 0.3V to +6V                    |

| Continuous power dissipation                        | $(T_A = 25^{\circ}C)^{(2)(6)}$ |

| QFN-24 (4mmx4mm)                                    | 5.2W                           |

| Junction temperature                                |                                |

| Lead temperature                                    |                                |

| Storage temperature                                 |                                |

|                                                     |                                |

#### ESD Ratings

| Human body model (HBM)     | Class 2 <sup>(3)</sup> |

|----------------------------|------------------------|

| Charged device model (CDM) |                        |

#### **Recommended Operating Conditions**

Supply voltage (PV<sub>DD</sub>)......4.5V to 36V Operating junction temp (T<sub>J</sub>)....-40°C to +150°C

| Thermal Resistance | $oldsymbol{	heta}_{JA}$ | <b>0</b> 30 |                     |

|--------------------|-------------------------|-------------|---------------------|

| QFN-24 (4mmx4mm)   |                         |             |                     |

| JESD51-7           | 42                      | 9           | °C/W (5)            |

| EVQ7795-R-00A      | 24                      | 6           | °C/W <sup>(6)</sup> |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature,  $T_J$  (MAX), the junction-to-ambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J$  (MAX)  $T_A$ ) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation can cause excessive die temperature, and the regulator may go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- B) Per AEC-Q100-002

- f) Per AEC-Q100-011

- 5) Measured on JESD51-7, 4-layer PCB. The values given in this table are only valid for comparison with other packages and cannot be used for design purposes. These values were calculated in accordance with JESD51-7, and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application, the value of  $\theta_{\rm JC}$  shows the thermal resistance from junction-to-case bottom.

- %) Measured on MPS MPQ7795 standard EVB, 7.62cmx6.35cm, 2oz. thick copper, 4-layer PCB. The value of  $\theta_{\text{JC}}$  shows the thermal resistance from junction-to-case top.

5

# **ELECTRICAL CHARACTERISTICS**

$PV_{DD}$  = 14.4V,  $V_{EN}$  = 5V,  $T_J$  = -40°C to +150°C, typical values are at  $T_J$  = 25°C, unless otherwise noted.

| Parameters                                                     | Symbol               | Condition                                                                                      | Min  | Тур  | Max  | Units |  |

|----------------------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------|------|------|------|-------|--|

| Operating Voltage and Current                                  |                      |                                                                                                |      |      |      |       |  |

| Standby current                                                | IQSTBY               | V <sub>EN</sub> = 0V, INN = INP = float                                                        |      | 0.02 | 3    | μA    |  |

| Quiescent current (7)                                          | lα                   | V <sub>EN</sub> = 5V, V <sub>MUTE</sub> = 0V,<br>INN = INP = float, no load, with<br>LC filter |      | 16   |      | mA    |  |

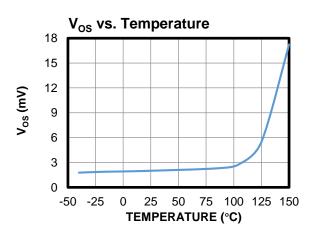

|                                                                |                      | Zero input, gain = 36dB, T <sub>J</sub> = 25°C                                                 | -20  | 2    | +20  | mV    |  |

| Output offset voltage                                          | Vos                  | Zero input, gain = 36dB,<br>T <sub>J</sub> = -40°C to +150°C                                   | -50  | 2    | +50  | mV    |  |

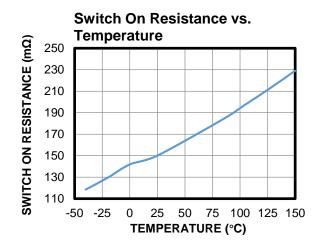

| MOSFETS                                                        |                      |                                                                                                |      |      |      |       |  |

|                                                                |                      | I <sub>ОUТ</sub> = 500mA, T <sub>J</sub> = 25°C                                                |      | 150  | 180  |       |  |

| SW on resistance                                               | R <sub>DS(ON)</sub>  | $I_{OUT} = 500$ mA,<br>$T_J = -40$ °C to +150°C                                                |      | 150  | 280  | mΩ    |  |

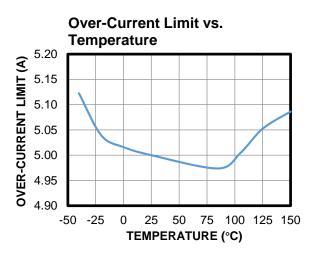

| Over-current limit                                             | ILIM                 | Sourcing and sinking                                                                           | 4    | 5    |      | Α     |  |

| Operating Parameters                                           |                      |                                                                                                |      |      |      |       |  |

|                                                                |                      | F1 = 0, F0 = 0                                                                                 | 290  | 330  | 370  | kHz   |  |

| Switching fraguency                                            | fsw                  | F1 = 0, F0 = 1                                                                                 | 338  | 384  | 430  | kHz   |  |

| Switching frequency                                            |                      | F1 = 1, F0 = 0                                                                                 | 413  | 470  | 527  | kHz   |  |

|                                                                |                      | F1 = 1, F0 = 1                                                                                 | 1825 | 2200 | 2375 | kHz   |  |

|                                                                | G                    | G1 = 0, G0 = 0, T <sub>J</sub> = 25°C                                                          | 19   | 20   | 21   |       |  |

| Coin of input signal                                           |                      | G1 = 0, G0 = 1, T <sub>J</sub> = 25°C                                                          | 25   | 26   | 27   | dB    |  |

| Gain of input signal                                           |                      | G1 = 1, G0 = 0, T <sub>J</sub> = 25°C                                                          | 31   | 32   | 33   |       |  |

|                                                                |                      | G1 = 1, G0 = 1, T <sub>J</sub> = 25°C                                                          | 35   | 36   | 37   |       |  |

| Input bias voltage                                             | V <sub>BIAS</sub>    | V <sub>EN</sub> = 5V                                                                           |      | 2.0  |      | V     |  |

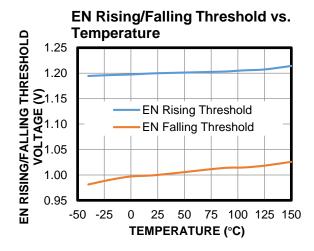

| ENI threehold voltage                                          | V <sub>EN_R</sub>    | V <sub>EN</sub> rising                                                                         |      | 1.2  | 1.5  | V     |  |

| EN threshold voltage                                           | V <sub>EN_F</sub>    | V <sub>EN</sub> falling                                                                        | 0.8  | 1.0  |      | V     |  |

| EN threshold hysteresis                                        | V <sub>EN_HYS</sub>  |                                                                                                |      | 0.2  |      | V     |  |

| EN enable input current                                        | I <sub>EN</sub>      | V <sub>EN</sub> = 5V                                                                           |      | 2.2  |      | μA    |  |

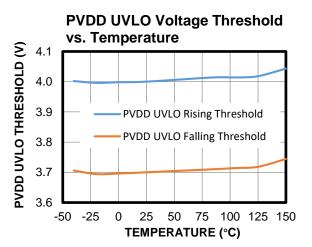

| PV <sub>DD</sub> under-voltage lockout (UVLO) rising threshold | V <sub>UVP_R</sub>   |                                                                                                | 3.6  | 4    | 4.4  | V     |  |

| PV <sub>DD</sub> UVLO falling threshold                        | V <sub>UVP_F</sub>   |                                                                                                | 3.3  | 3.7  | 4.1  | V     |  |

| PV <sub>DD</sub> UVLO threshold hysteresis                     | V <sub>UVP_HYS</sub> |                                                                                                |      | 0.3  |      | V     |  |

| MIITE thusehold                                                | V <sub>MUTE_R</sub>  | V <sub>MUTE</sub> rising                                                                       | 0.7  | 0.95 | 1.2  | V     |  |

| MUTE threshold voltage                                         | V <sub>MUTE_F</sub>  | V <sub>MUTE</sub> falling                                                                      | 0.6  | 0.8  | 1    | V     |  |

| Time                                                           |                      |                                                                                                |      |      |      |       |  |

| Turn-on time                                                   | ton                  |                                                                                                |      | 430  |      | ms    |  |

| Protection                                                     |                      |                                                                                                |      |      |      |       |  |

| Thermal shutdown trigger (7)                                   | T <sub>OTP_R</sub>   | T <sub>J</sub> rising                                                                          |      | 170  |      | °C    |  |

| Thermal shutdown hysteresis (7)                                | T <sub>OTP_HYS</sub> |                                                                                                |      | 20   |      | °C    |  |

| FAULT# low voltage                                             | V <sub>FT</sub>      | Isink = 2mA                                                                                    |      | 14   |      | mV    |  |

#### Note:

<sup>7)</sup> Derived from the bench characterization. Not tested in production.

# **ELECTRICAL CHARACTERISTICS** (continued)

$PV_{DD} = 14.4V$ ,  $V_{EN} = 5V$ ,  $T_{J} = -40$ °C to +150°C, typical values are at  $T_{J} = 25$ °C, unless otherwise noted.

| Parameters                                       | Symbol              | Condition               | Min | Тур | Max | Units |

|--------------------------------------------------|---------------------|-------------------------|-----|-----|-----|-------|

| Load Diagnostics                                 |                     |                         |     |     |     |       |

| Short to PVDD resistance                         | Rstb                |                         |     | 220 |     | Ω     |

| Short to ground resistance                       | Rstg                |                         |     | 250 |     | Ω     |

| Open load detection threshold                    | ROPEN               |                         |     | 95  |     | Ω     |

| Short load detection threshold                   | Rshort              |                         |     | 1.5 |     | Ω     |

| I <sup>2</sup> C Parameters                      |                     |                         |     |     |     |       |

| SCL/SDA input logic low                          | $V_{IL}$            |                         | 0   |     | 0.4 | V     |

| SCL/SDA input logic high                         | $V_{IH}$            |                         | 2.1 |     |     | V     |

| SCL/SDA output logic low                         | $V_{OL}$            | I <sub>LOAD</sub> = 3mA |     |     | 0.4 | V     |

| SCL clock frequency                              | fscL                |                         |     |     | 400 | kHz   |

| SCL high time                                    | thigh               |                         | 0.6 |     |     | μs    |

| SCL low time                                     | $t_{LOW}$           |                         | 1.3 |     |     | μs    |

| Data set-up time                                 | tsu_dat             |                         | 100 |     |     | ns    |

| Data hold time                                   | thd_dat             |                         | 0   |     | 0.9 | μs    |

| Set-up time for repeated start                   | <b>t</b> su_sta     |                         | 0.6 |     |     | μs    |

| Hold time for start                              | t <sub>HD_STA</sub> |                         | 0.6 |     |     | μs    |

| Bus free time between a start and a stop command | t <sub>BUF</sub>    |                         | 1.3 |     |     | μs    |

| Set-up time for stop command                     | ts∪_s⊤o             |                         | 0.6 |     |     | μs    |

| Rising time of SCL/SDA                           | t <sub>R</sub>      |                         |     |     | 120 | ns    |

| Falling time of SCL/SDA                          | t <sub>F</sub>      |                         |     |     | 120 | ns    |

| Pulse width of suppressed spike                  | tsp                 |                         | 0   |     | 50  | ns    |

| Capacitance bus for each bus line                | Св                  |                         |     |     | 400 | pF    |

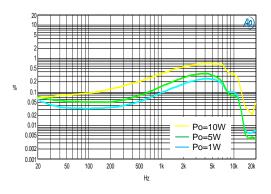

### **OPERATING CHARACTERISTICS (8)**

$PV_{DD} = 14.4V$ ,  $V_{EN} = 5V$ ,  $T_J = -40$  to +150°C, typical values are at  $T_J = 25$ °C, unless otherwise noted.

| Parameters                                                                | Symbol         | Condition                                                                           |         | Min  | Тур  | Max           | Units |

|---------------------------------------------------------------------------|----------------|-------------------------------------------------------------------------------------|---------|------|------|---------------|-------|

|                                                                           |                | $f_{SW} = 470kHz$ , $load = 8\Omega$                                                |         | 0.09 |      | %             |       |

| THD + noise                                                               | THD + N        | $f_{SW} = 470kHz$ , load = $4\Omega$                                                |         |      | 0.27 |               | %     |

| $(P_{OUT} = 1W, f_{INPUT})^{(9)} = 1kHz$                                  | א ד טווו       | $f_{SW} = 2.2MHz$ , $load = 8\Omega$                                                |         |      | 0.2  |               | %     |

|                                                                           |                | $f_{SW} = 2.2MHz$ , $load = 4\Omega$                                                |         |      | 0.38 |               | %     |

| -                                                                         |                | $f_{SW} = 470kHz$ , load = $8\Omega$                                                |         |      | 13.6 |               | W     |

| Output power (finput (9) = 1kHz,                                          | Роит           | $f_{SW} = 470kHz$ , load = $4\Omega$                                                |         |      | 24.4 |               | W     |

| THD + N = 10%                                                             | FOUT           | $f_{SW} = 2.2MHz$ , load = $8\Omega$                                                |         |      | 13.7 |               | W     |

|                                                                           |                | $f_{SW} = 2.2MHz$ , load = $4\Omega$                                                |         | 24.5 |      | W             |       |

|                                                                           |                | $f_{SW} = 470kHz$ , load = $8\Omega$                                                |         | 92.6 |      | %             |       |

| Efficiency                                                                | η              | $f_{SW} = 470kHz$ , $load = 4\Omega$                                                |         | 90.4 |      | %             |       |

| (THD + N = 10%)                                                           |                | $f_{SW} = 2.2MHz$ , load = $8\Omega$                                                |         | 90.8 |      | %             |       |

|                                                                           |                | $f_{SW} = 2.2MHz$ , load = $4\Omega$                                                |         |      | 86.8 |               | %     |

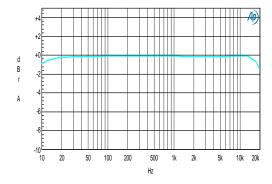

| Frequency response                                                        |                | Gain = 20dB, A-weighted, 22kHz                                                      | 20Hz to |      |      | 2             | dB    |

| Noise floor $(f_{SW} = 470 \text{kHz}, \text{ load} = 8\Omega)$           | V <sub>N</sub> | A-weighted, 20Hz to 22kH                                                            |         | 115  |      | $\mu V_{RMS}$ |       |

| Signal-to-noise ratio $(f_{SW} = 470 \text{kHz}, \text{ load} = 8\Omega)$ | SNR            | $f_{\text{INPUT}}$ <sup>(9)</sup> = 1kHz, THD + N A-weighted, $T_{\text{J}}$ = 25°C |         | 102  |      | dB            |       |

|                                                                           | -              | VRIPPLE = 1VPP, inputs                                                              | 100Hz   |      | 80   |               | dB    |

| Power supply rejection                                                    | PSRR           | AC-coupled to AGND,<br>$T_J = 25^{\circ}C$                                          | 1kHz    |      | 66   |               | dB    |

#### Note:

Operating specifications are for the typical application circuit (see Figure 12 on page 39). Not production tested.

f<sub>INPUT</sub> is an external parameter referring to the input signal frequency. The 470kHz performance is based on Figure 12 on page 39. The 2.2MHz performance is based on Figure 13 on page 40.

#### TYPICAL CHARACTERISTICS

$PV_{DD} = 14.4V$ ,  $T_J = 25$ °C, unless otherwise noted.

# TYPICAL CHARACTERISTICS (continued)

$PV_{DD} = 14.4V$ ,  $T_J = 25$ °C, unless otherwise noted.

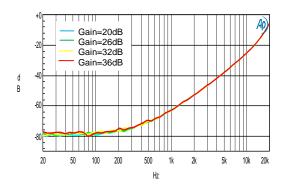

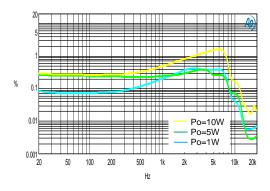

#### TYPICAL PERFORMANCE CHARACTERISTICS

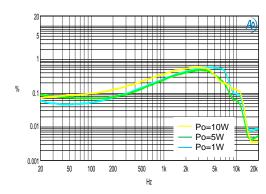

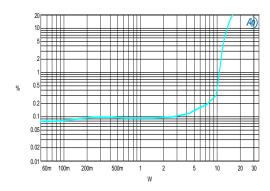

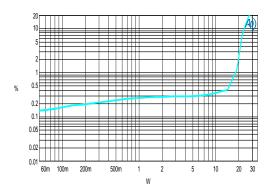

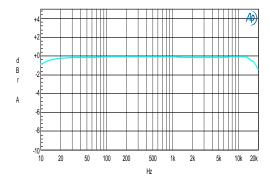

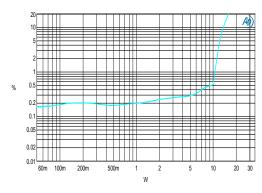

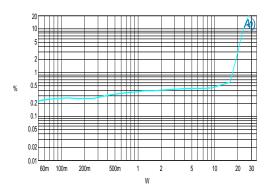

$PV_{DD} = 14.4V$ ,  $f_{SW} = 470kHz$ ,  $L_{OUT} = 10\mu H$ ,  $C_{OUT} = 1\mu F$ ,  $f_{INPUT} = 1kHz$ , Gain = 20dB,  $T_A = 25^{\circ}C$ , unless otherwise noted.

THD + N vs. Frequency  $8\Omega + 66 \mu H$

THD + N vs. Frequency

$4\Omega + 33 \mu H$

THD + N vs. Pout  $8\Omega + 66 \mu H$

THD + N vs. Pout  $4\Omega + 33 \mu H$

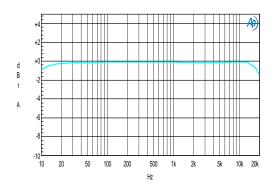

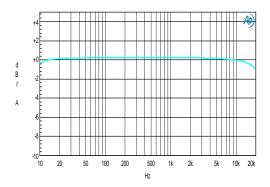

# **Frequency Response**

1W, 8Ω + 66μH

#### **Frequency Response**

1W, 4Ω + 33μH

$PV_{DD} = 14.4V$ ,  $f_{SW} = 470kHz$ ,  $L_{OUT} = 10\mu H$ ,  $C_{OUT} = 1\mu F$ ,  $f_{INPUT} = 1kHz$ , gain = 20dB,  $T_A = 25$ °C, unless otherwise noted.

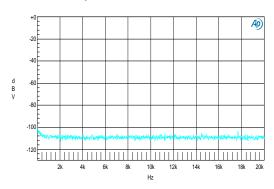

#### **PSRR**

$V_{AC}$  ripple =  $1V_{PP}$

#### **FFT Noise Floor Test**

$8\Omega + 66 \mu H$

$PV_{DD} = 14.4V$ ,  $f_{SW} = 2.2MHz$ ,  $L_{OUT} = 4.7\mu H$ ,  $C_{OUT} = 1\mu F$ ,  $f_{INPUT} = 1kHz$ , gain = 20dB,  $T_A = 25$ °C, unless otherwise noted.

THD + N vs. Frequency

THD + N vs. Frequency

$4\Omega + 33 \mu H$

THD + N vs. Pout

$8\Omega + 66 \mu H$

THD + N vs. Pout  $4\Omega + 33 \mu H$

#### **Frequency Response**

1W, 8Ω + 66μH

#### **Frequency Response**

1W, 4Ω + 33μH

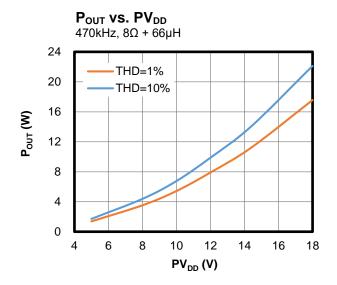

$PV_{DD} = 14.4V$ ,  $C_{OUT} = 1\mu F$ ,  $f_{INPUT} = 1kHz$ , Gain = 20dB,  $T_A = 25^{\circ}C$ , unless otherwise noted.

$PV_{DD} = 14.4V$ ,  $C_{OUT} = 1\mu F$ ,  $f_{INPUT} = 1kHz$ , Gain = 20dB,  $T_A = 25^{\circ}C$ , unless otherwise noted.

#### Note:

10) When  $f_{SW} = 470 \text{kHz}$ , inductor information: XAL6060-103MEB,  $10 \mu\text{H}$ , DCR =  $27 m\Omega$ . When  $f_{SW} = 2.2 \text{MHz}$ , inductor information: XAL4030-103MEB,  $10 \mu\text{H}$ , DCR =  $10 \mu\text{H}$ , DCR =  $10 \mu\text{H}$ , inductor information: XAL4030-103MEB,  $10 \mu\text{H}$ , DCR =  $10 \mu\text{H}$ , DCR =  $10 \mu\text{H}$ , inductor information: XAL4030-103MEB,  $10 \mu\text{H}$ , DCR =  $10 \mu\text{H}$ , DCR =  $10 \mu\text{H}$ , inductor information: XAL4030-103MEB,  $10 \mu\text{H}$ , DCR =  $10 \mu\text{H}$ , inductor information: XAL4030-103MEB,  $10 \mu\text{H}$ , DCR =  $10 \mu\text{H}$ , inductor information: XAL4030-103MEB,  $10 \mu\text{H}$ , DCR =  $10 \mu\text{H}$ , DCR =  $10 \mu\text{H}$ , inductor information: XAL4030-103MEB,  $10 \mu\text{H}$ , DCR =  $10 \mu\text{H}$ , DCR 222MEB, 2.2μH, DCR = 35.2mΩ.

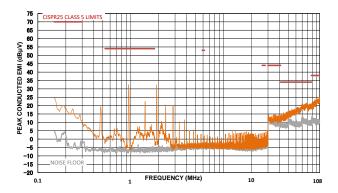

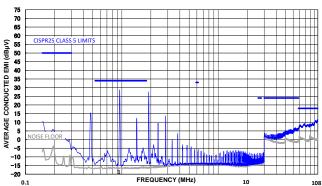

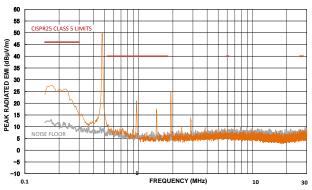

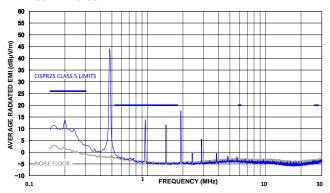

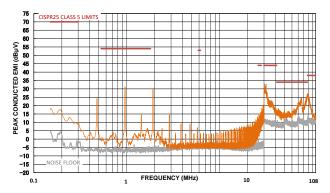

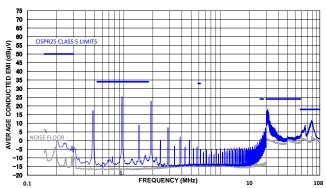

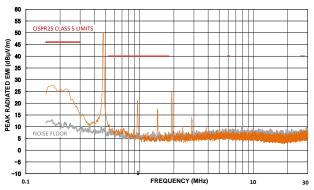

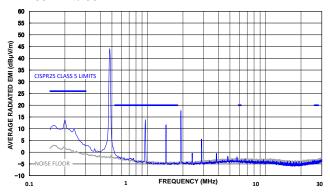

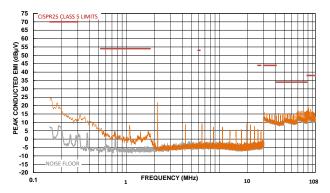

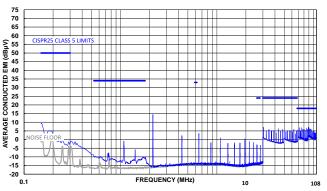

$PV_{DD} = 12V$ ,  $f_{SW} = 470$ kHz,  $L_{OUT} = 10\mu$ H (XEL5050-103MEC, 40.9m $\Omega$ , 3.6A),  $C_{OUT} = 1\mu$ F,  $f_{INPUT} = 1$ kHz, load =  $4\Omega$ , 1% THD + N, no output cable, gain = 20dB,  $T_A = 25$ °C, unless otherwise noted.

#### **CISPR25 Class 5 Peak Conducted Emissions**

150kHz to 108MHz

#### CISPR25 Class 5 Average Conducted **Emissions**

150kHz to 108MHz

#### CISPR25 Class 5 Peak Radiated **Emissions**

150kHz to 30MHz

#### CISPR25 Class 5 Average Radiated **Emissions**

150kHz to 30MHz

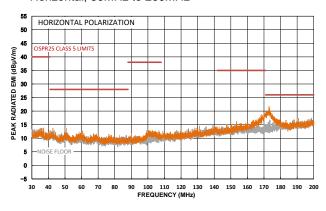

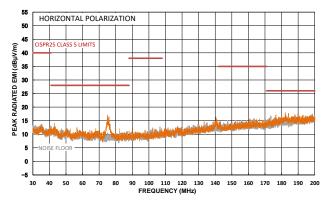

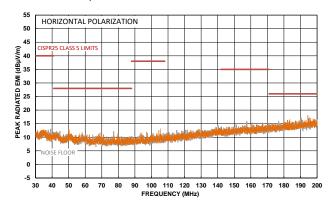

#### **CISPR25 Class 5 Peak Radiated Emissions**

Horizontal, 30MHz to 200MHz

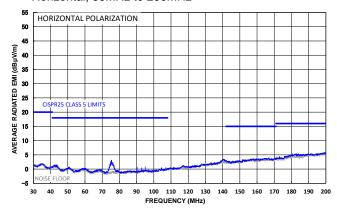

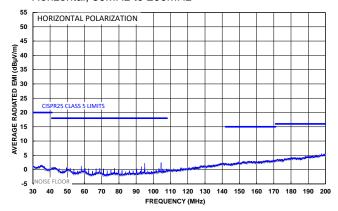

#### CISPR25 Class 5 Average Radiated **Emissions**

Horizontal, 30MHz to 200MHz

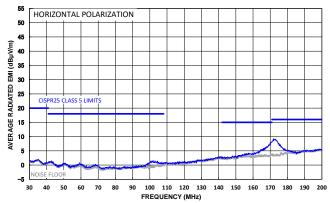

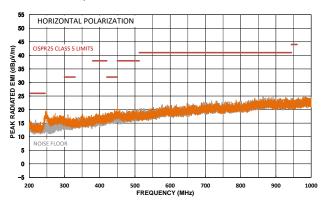

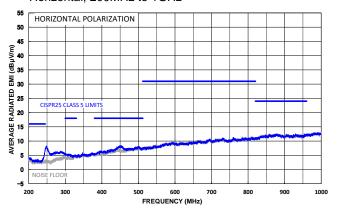

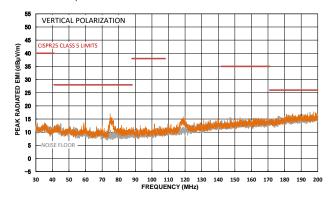

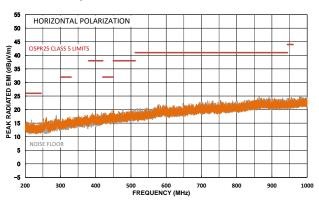

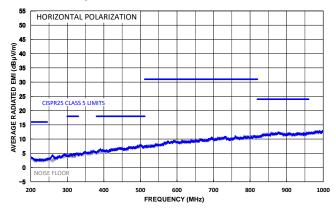

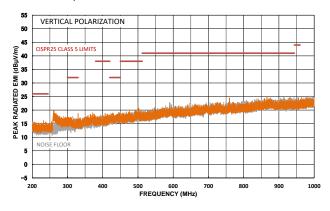

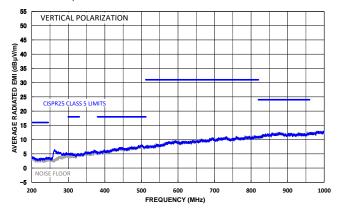

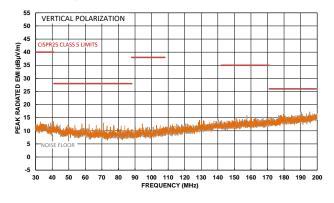

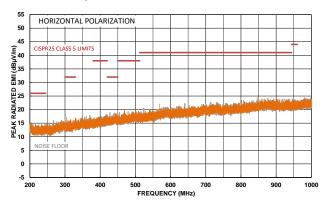

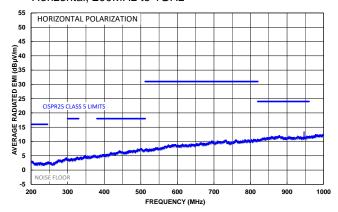

PV<sub>DD</sub>= 12V,  $f_{SW}$  = 470kHz,  $L_{OUT}$  = 10 $\mu$ H (XEL5050-103MEC, 40.9m $\Omega$ , 3.6A),  $C_{OUT}$  = 1 $\mu$ F,  $f_{INPUT}$  = 1kHz, load = 4 $\Omega$ , 1% THD + N, no output cable, gain = 20dB,  $T_A$  = 25°C, unless otherwise noted.

#### CISPR25 Class 5 Peak Radiated Emissions

Vertical, 30MHz to 200MHz

# CISPR25 Class 5 Average Radiated Emissions

Vertical, 30MHz to 200MHz

#### CISPR25 Class 5 Peak Radiated Emissions

Horizontal, 200MHz to 1GHz

# CISPR25 Class 5 Average Radiated Emissions

Horizontal, 200MHz to 1GHz

#### CISPR25 Class 5 Peak Radiated Emissions

Vertical, 200MHz to 1GHz

# CISPR25 Class 5 Average Radiated Emissions

Vertical, 200MHz to 1GHz

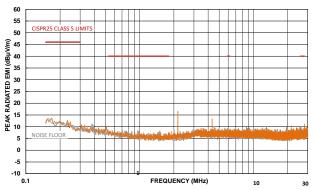

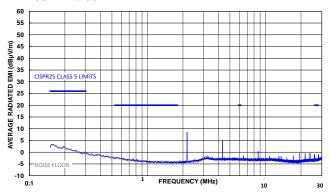

PV<sub>DD</sub>= 12V,  $f_{SW}$  = 470kHz,  $L_{OUT}$  = 10 $\mu$ H (XEL5050-103MEC, 40.9m $\Omega$ , 3.6A),  $C_{OUT}$  = 1 $\mu$ F,  $f_{INPUT}$  = 1kHz, load = 4 $\Omega$ , 1% THD + N, 2m output cable, gain = 20dB,  $T_A$  = 25°C, unless otherwise noted.

#### CISPR25 Class 5 Peak Conducted Emissions

150kHz to 108MHz

# **CISPR25 Class 5 Average Conducted Emissions**

150kHz to 108MHz

#### CISPR25 Class 5 Peak Radiated Emissions

150kHz to 30MHz

# CISPR25 Class 5 Average Radiated Emissions

150kHz to 30MHz

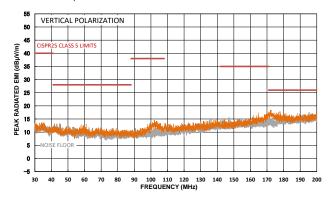

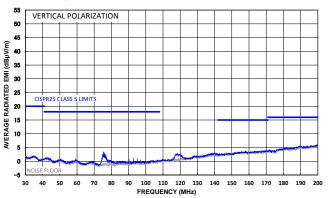

# CISPR25 Class 5 Peak Radiated Emissions

Horizontal, 30MHz to 200MHz

# CISPR25 Class 5 Average Radiated Emissions

Horizontal, 30MHz to 200MHz

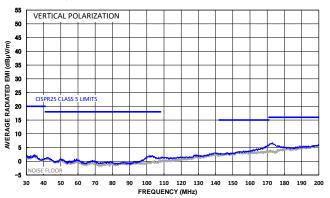

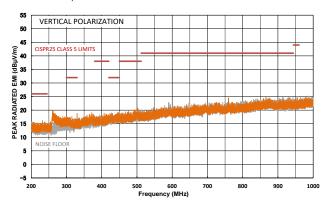

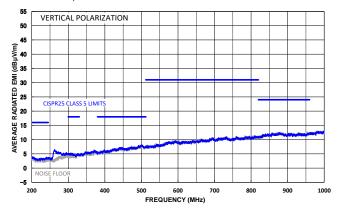

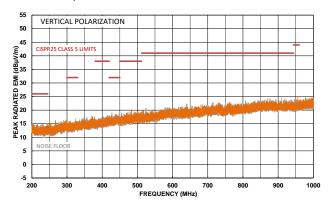

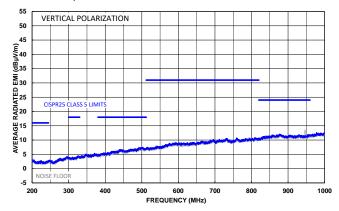

PV<sub>DD</sub>= 12V,  $f_{SW}$  = 470kHz,  $L_{OUT}$  = 10 $\mu$ H (XEL5050-103MEC, 40.9m $\Omega$ , 3.6A),  $C_{OUT}$  = 1 $\mu$ F,  $f_{INPUT}$  = 1kHz, load = 4 $\Omega$ , 1% THD + N, 2m output cable, gain = 20dB,  $T_A$  = 25°C, unless otherwise noted.

# CISPR25 Class 5 Peak Radiated Emissions

Vertical, 30MHz to 200MHz

# **CISPR25 Class 5 Average Radiated Emissions**

Vertical, 30MHz to 200MHz

#### CISPR25 Class 5 Peak Radiated Emissions

Horizontal, 200MHz to 1GHz

#### CISPR25 Class 5 Average Radiated Emissions

Horizontal, 200MHz to 1GHz

#### CISPR25 Class 5 Peak Radiated Emissions

Vertical, 200MHz to 1GHz

# CISPR25 Class 5 Average Radiated Emissions

Vertical, 200MHz to 1GHz

$PV_{DD}$ = 12V,  $f_{SW}$  = 2.2MHz,  $L_{OUT}$  = 4.7μH (XAL5030-472MEB, 36mΩ, 5.9A),  $C_{OUT}$  = 1μF,  $f_{INPUT}$  = 1kHz, load = 4Ω, 10.5W, no output cable, with shielding, gain = 20dB,  $T_A$  = 25°C, unless otherwise noted.

#### CISPR25 Class 5 Peak Conducted Emissions

150kHz to 108MHz

# **CISPR25 Class 5 Average Conducted Emissions**

150kHz to 108MHz

#### CISPR25 Class 5 Peak Radiated Emissions

150kHz to 30MHz

# CISPR25 Class 5 Average Radiated Emissions

150kHz to 30MHz

#### CISPR25 Class 5 Peak Radiated Emissions

Horizontal, 30MHz to 200MHz

# CISPR25 Class 5 Average Radiated Emissions

Horizontal, 30MHz to 200MHz

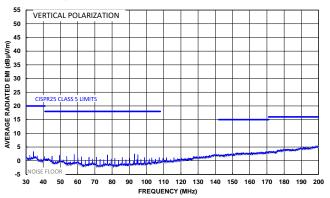

$PV_{DD}$  = 12V,  $f_{SW}$  = 2.2MHz,  $L_{OUT}$  = 4.7μH (XAL5030-472MEB, 36mΩ, 5.9A),  $C_{OUT}$  = 1μF,  $f_{INPUT}$  = 1kHz, load = 4Ω, 10.5W, no output cable, with shielding, gain = 20dB,  $T_A$  = 25°C, unless otherwise noted.

# CISPR25 Class 5 Peak Radiated Emissions

Vertical, 30MHz to 200MHz

# **CISPR25 Class 5 Average Radiated Emissions**

Vertical, 30MHz to 200MHz

#### CISPR25 Class 5 Peak Radiated Emissions

Horizontal, 200MHz to 1GHz

#### CISPR25 Class 5 Average Radiated Emissions

Horizontal, 200MHz to 1GHz

#### CISPR25 Class 5 Peak Radiated Emissions

Vertical, 200MHz to 1GHz

# CISPR25 Class 5 Average Radiated Emissions

Vertical, 200MHz to 1GHz

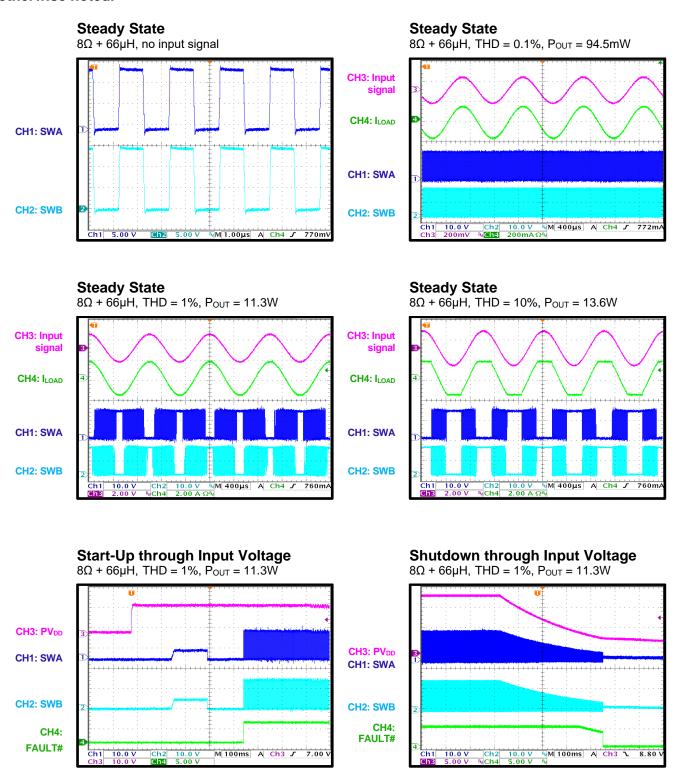

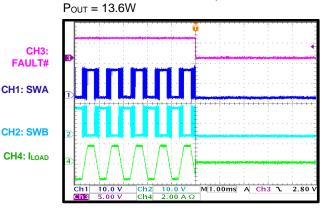

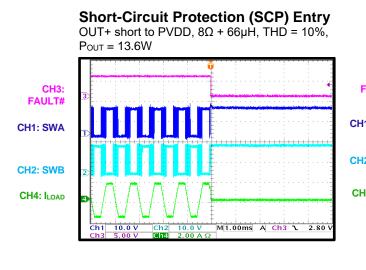

$PV_{DD} = 14.4V$ ,  $f_{SW} = 470kHz$ ,  $L_{OUT} = 10\mu H$ ,  $C_{OUT} = 1\mu F$ ,  $f_{INPUT} = 1kHz$ , gain = 20dB,  $T_A = 25$ °C, unless otherwise noted.

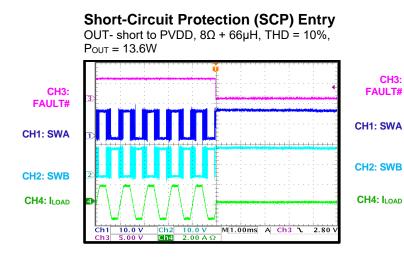

22

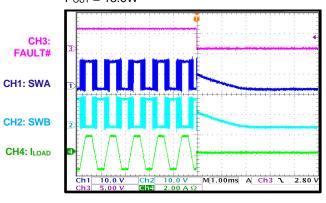

$PV_{DD}$  = 14.4V,  $f_{SW}$  = 470kHz,  $L_{OUT}$  = 10 $\mu$ H,  $C_{OUT}$  = 1 $\mu$ F,  $f_{INPUT}$  = 1kHz, gain = 20dB,  $T_A$  = 25°C, unless otherwise noted.

FAULT#

CH1: SWA

CH2: SWB

CH4: ILOAD

CH3: FAULT#

CH1: SWA

CH2: SWB

CH4: ILOAD

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

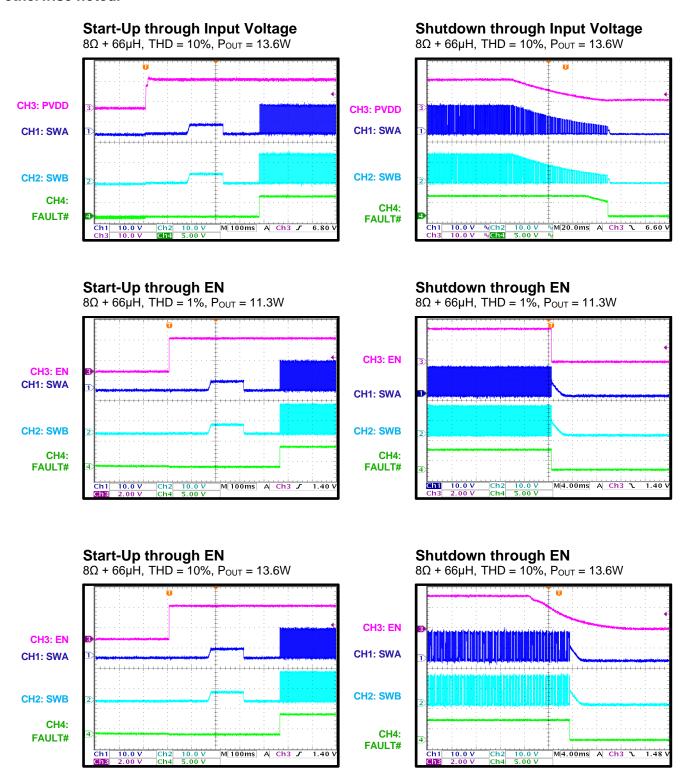

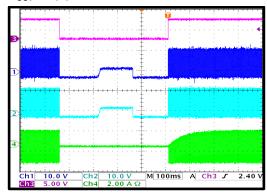

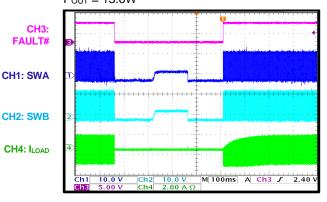

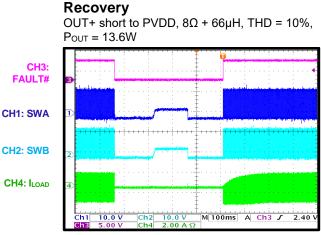

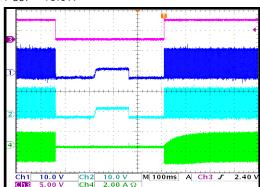

$PV_{DD}$  = 14.4V,  $f_{SW}$  = 470kHz,  $L_{OUT}$  = 10 $\mu$ H,  $C_{OUT}$  = 1 $\mu$ F,  $f_{INPUT}$  = 1kHz, gain = 20dB,  $T_A$  = 25°C, unless otherwise noted.

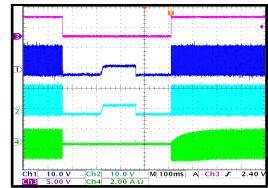

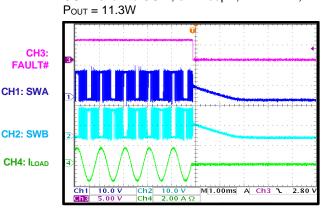

# **Short-Circuit Protection (SCP) Recovery**

OUT- short to GND,  $8\Omega$  +  $66\mu$ H, THD = 1%, Pout = 11.3W

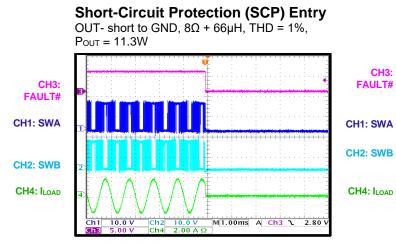

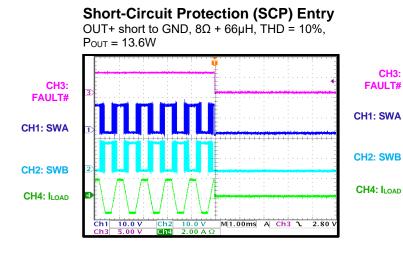

# Short-Circuit Protection (SCP) Entry

OUT- short to GND,  $8\Omega + 66\mu$ H, THD = 10%,

# Short-Circuit Protection (SCP) Recovery

OUT- short to GND,  $8\Omega$  +  $66\mu H$ , THD = 10%, Pout = 13.6W

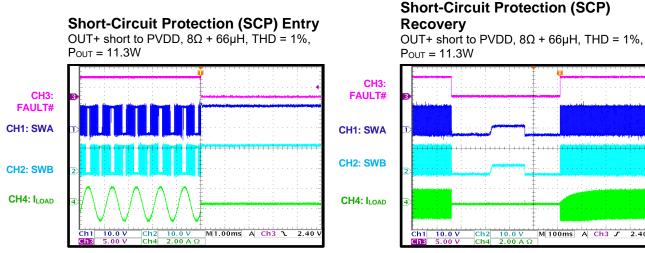

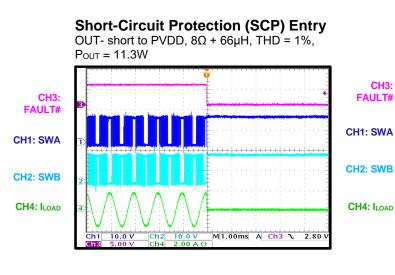

# Short-Circuit Protection (SCP) Entry

OUT+ short to GND,  $8\Omega$  +  $66\mu$ H, THD = 1%, Pout = 11.3W

# Short-Circuit Protection (SCP) Recovery

OUT+ short to GND,  $8\Omega$  +  $66\mu$ H, THD = 1%, Pout = 11.3W

**CH3**:

FAULT#

CH1: SWA

CH2: SWB

CH4: ILOAD

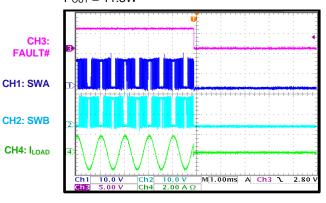

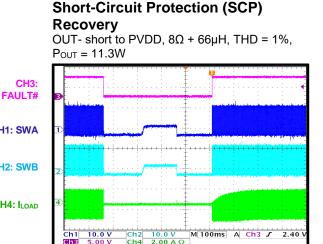

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$PV_{DD} = 14.4V$ ,  $f_{SW} = 470kHz$ ,  $L_{OUT} = 10\mu H$ ,  $C_{OUT} = 1\mu F$ ,  $f_{INPUT} = 1kHz$ , gain = 20dB,  $T_A = 25^{\circ}C$ , unless otherwise noted.

#### **Short-Circuit Protection (SCP)** Recovery

OUT+ short to GND,  $8\Omega + 66\mu H$ , THD = 10%, Pout =13.6W

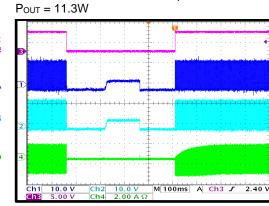

# **Short-Circuit Protection (SCP) Entry**

OUT+ short to OUT-,  $8\Omega + 66\mu H$ , THD = 1%,

#### **Short-Circuit Protection (SCP)** Recovery

OUT+ short to OUT-,  $8\Omega + 66\mu$ H, THD = 1%, Pout = 11.3W

# **Short-Circuit Protection (SCP) Entry**

OUT+ short to OUT-,  $8\Omega + 66\mu H$ , THD = 10%, Pout = 13.6W

#### **Short-Circuit Protection (SCP)** Recovery

OUT+ short to OUT-,  $8\Omega + 66\mu$ H, THD = 10%, Pout = 13.6W

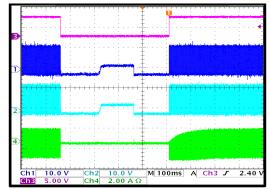

$PV_{DD} = 14.4V$ ,  $f_{SW} = 470kHz$ ,  $L_{OUT} = 10\mu H$ ,  $C_{OUT} = 1\mu F$ ,  $f_{INPUT} = 1kHz$ , gain = 20dB,  $T_A = 25^{\circ}C$ , unless otherwise noted.

**Short-Circuit Protection (SCP)**

**CH3**:

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$PV_{DD} = 14.4V$ ,  $f_{SW} = 470kHz$ ,  $L_{OUT} = 10\mu H$ ,  $C_{OUT} = 1\mu F$ ,  $f_{INPUT} = 1kHz$ , gain = 20dB,  $T_A = 25$ °C, unless otherwise noted.

#### **Short-Circuit Protection (SCP)** Recovery

OUT- short to PVDD,  $8\Omega + 66\mu H$ , THD = 10%, Pout = 13.6W

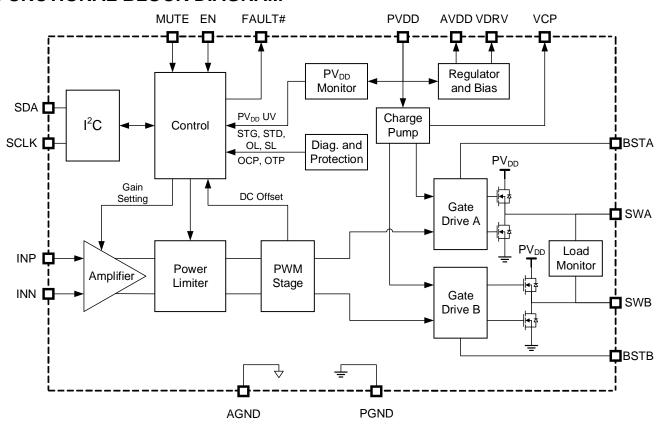

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 1: Functional Block Diagram

#### **OPERATION**

The MPQ7795 is a fully integrated Class-D mono BTL audio amplifier. Because of the switching Class-D output stage, power dissipation in the amplifier is drastically reduced when compared to Class-A, Class-B, or Class-A/B amplifiers, all while maintaining high fidelity and low distortion.

MPQ7795 includes four high-power MOSFETs. For each half-bridge channel, the output driver stage uses two N-channel MOSFETs to deliver the pulses to the LC output filter, which in turn drives the load. To fully enhance the high-side MOSFET (HS-FET), the bootstrap capacitor between the OUTx and BSTx pins drives the gate to a voltage that exceeds the source. While the output is driven low, the bootstrap capacitor is charged by the power supply through an internal circuit. The HS-FET's gate is driven high by the voltage at the bootstrap supply, forcing the MOSFET gate to a voltage that exceeds the power supply voltage and allows the MOSFET to fully turn on. This process reduces the amplifier's power loss.

The MPQ7795's gain is set by the following I<sup>2</sup>C bits: G0 and G1. The actual gain settings are controlled by the ratios of the internal input and feedback resistors.

#### **Enable (EN) and MUTE Function**

The MPQ7795's EN input is an active-high enable control. To enable the MPQ7795, drive EN with a minimum 1.5V voltage. To disable the amplifier, drive EN below 0.4V. While the MPQ7795 is disabled, the PVDD operating current is about 0.02µA, and the output driver MOSFETs turn off. AVDD and VDRV are also disabled. When the device is enabled, the load is automatically detected.

The MUTE pin is also an active-high input pin. To enter mute mode, drive MUTE with a 3.3V or 5V voltage. When the MPQ7795 is muted, the output driver MOSFETs turn off, and the load diagnostics are executed while AVDD and VDRV are still enabled. When the device exits mute mode, load detection is not performed.

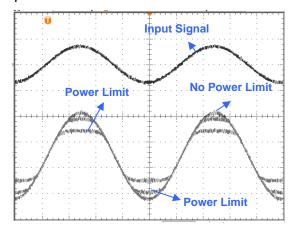

#### Adjustable Power Limit (PLIMIT)

The power limit ( $P_{LIMIT}$ ) circuit sets a limit on the output's peak-to-peak voltage ( $V_{PK-PK}$ ). The limit is set by limiting the duty cycle to a fixed maximum value (see Figure 2). This limit can be considered a virtual voltage rail that is below the supply connected to PVDD. This virtual voltage is set via the PL bits in the  $I^2C$ . This output voltage ( $V_{OUT}$ ) can be used to calculate the maximum output power ( $P_{OUT}$ ) for a given maximum input voltage ( $V_{IN}$ ) and speaker impedance.

Figure 2: PLIMIT Circuit Operation

The maximum output power ( $P_{OUT\_MAX}$ ) can be calculated with Equation (1):

$$P_{OUT\_MAX} = \frac{\left(\frac{R_L}{R_L + 2 \times R_S} V_P\right)^2}{2 \times R_L}$$

(1)

Where  $R_S$  is the total output series resistance (including  $R_{DS(ON)}$  and the DCR of the output inductors),  $R_L$  is the load resistance, and  $V_P$  is the output voltage amplitude.

In addition, the output power at 10% THD + N  $(P_{OUT@10\%THD+N})$  can be estimated with Equation (2):

$$P_{\text{OUT} @10\%\text{THD+N}} \approx 1.25 \times \text{unclamped } P_{\text{OUT}}$$

(2)

Table 1 on page 30 shows the  $P_{\text{LIMIT}}$  setting, and the typical max  $V_{\text{OUT}}$ , and  $P_{\text{OUT}}$  at 10% THD + N.

Table 1: Power Limit Typical Operation (11)

| Power Limit |      | Output<br>(V <sub>PK-PK</sub> ) |      | nt 10%<br>N (W) |

|-------------|------|---------------------------------|------|-----------------|

| Setting (V) | 4Ω   | 8Ω                              | 4Ω   | 8Ω              |

| 5           | 9.4  | 9.2                             | 1.5  | 0.8             |

| 5.9         | 11.2 | 11                              | 2.6  | 1.4             |

| 7           | 13.4 | 13                              | 4.1  | 2.2             |

| 8.4         | 15.2 | 15                              | 5.9  | 3.1             |

| 9.8         | 19.8 | 19.6                            | 11.8 | 6.2             |

| 11.8        | 22.8 | 22.8                            | 16.3 | 8.4             |

| 14          | 26.6 | 26.6                            | 23.3 | 11.8            |

| No limit    | 26.8 | 28.6                            | 24.5 | 13.8            |

#### Note

11) Test conditions:  $f_{SW}=470 kHz$ ,  $10 \mu H$  inductor (XAL6060-103MEB, DCR =  $27 m\Omega$ ),  $T_A=25 ^{\circ} C$ ,  $PV_{DD}=14.4 V$ , gain = 20 dB.

#### **Gain Setting**

The MPQ7795's gain is set by the following I<sup>2</sup>C bits: G0 and G1. The actual gain settings are controlled by the ratios of the internal input and feedback resistors.

Table 2 shows the typical gain and single-ended (SE) input impedance for each setting.

**Table 2: Gain Setting**

| G0 | G1 | Typ. GAIN<br>(dB) | Typ. SE Input Impedance (kΩ) |

|----|----|-------------------|------------------------------|

| 0  | 0  | 20                | 70                           |

| 1  | 0  | 26                | 50                           |

| 0  | 1  | 32                | 30                           |

| 1  | 1  | 36                | 20                           |

#### **Over-Temperature Shutdown**

Thermal monitoring is integrated into the MPQ7795. If the die temperature exceeds 170°C, all switches turn off. The temperature must fall below 150°C before normal operation resumes, with the same start-up sequence used to prevent popping noise.

#### Overload and Short-Circuit Protection (SCP)

The MPQ7795 has internal overload and short-circuit protection (SCP). The currents flowing through the both the HS-FETs and low-side MOSFETs (LS-FETs) are monitored. When a short circuit is detected, all the MOSFETs go to high impedance for a fixed duration. After this fixed duration, the MPQ7795 restarts with load diagnostics to prevent the pop noise from occurring.

Typically, if a short circuit occurs in play mode with an input signal, the MPQ7795 triggers an overload then restarts load diagnostics to check which fault occurred. If the fault is consistent, the load diagnostics repeat until the fault disappears.

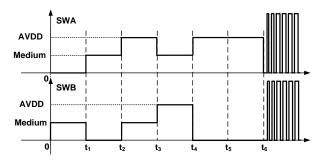

#### **Load Diagnostics**

When the device is enabled, the load diagnostics run before the part starts switching, or before entering a fault state. During diagnostics, the output is in a high-impedance state. The diagnostics typically take 480ms.

Step 1 (t<sub>0</sub> to t<sub>1</sub>): SWA pulls low to detect whether there is a short circuit between SWA and PVDD.

Step 2 ( $t_1$  to  $t_2$ ): SWB pulls to detect whether there is a short circuit between SWB and PVDD.

Step 3 ( $t_2$  to  $t_3$ ): SWA pulls high to detect whether there is a short circuit between SWA and GND.

Step 4 ( $t_3$  to  $t_4$ ): SWB pulls high to detect whether there is a short circuit between SWB and GND.

<u>Step 5 ( $t_4$  to  $t_5$ )</u>: SWB pulls low, and SWA is pulled high by an internal current source to detect whether there is a short circuit between SWA and SWB (short load detection).

<u>Step 6 ( $t_5$  to  $t_6$ )</u>: SWB pulls low, and SWA is pulled high by an internal current source to detect whether there is an open circuit between SWA and SWB (open load detection).

Each step takes 80ms. At the end of step 4, SWA and SWB are pulled to GND. After 100µs, SWA is pulled to AVDD (5V). From step 1 to step 4, the undetected output is in a high-impedance state.

Figure 3 shows the load diagnostics when there is no load.

FIGURE 3: LOAD DIAGNOSTICS (NO LOAD)

Load diagnostics can detect open load, short load, output short to PVDD, and output short to ground conditions. See the Electrical Characteristics section starting on page 6 for the relevant thresholds. If any status mentioned above is detected, the I<sup>2</sup>C reports the status.

If the load diagnostics find a fault, the MPQ7795 restarts at step 1 after the current step is finished. For example, if an SWB-to-PVDD short condition is detected, the load diagnostics restart after step 2 finishes, then the MPQ7795 repeats step 1 and step 2 until the short is removed.

#### **Fault Output**

The MPQ7795 includes an open-drain, active-low fault indicator output on the FAULT# pin. A fault is trigged if any of the following faults occur: over-current (OC), PVDD under-voltage (UV), over-temperature shutdown, DC offset, shorted load, output short to PVDD, and output short to ground.

The FAULT# pin pulls low if a fault is detected on any channel, then the output goes into a high-impedance state. When the fault condition is removed, the MPQ7795 resumes normal operation. FAULT# remains asserted until the fault register is cleared. The fault register can be cleared by writing 0xFF to register 0x01.

Note that open load conditions are not reported via the FAULT# pin, nor does the output go to a high-impedance state. This condition is only indicated by the I<sup>2</sup>C registers.

### I<sup>2</sup>C INTERFACE

#### I<sup>2</sup>C Serial Interface Description

The I<sup>2</sup>C bus is a 2-wire, bidirectional serial interface, consisting of a serial data line (SDA) and a serial clock line (SCL). The lines are externally pulled to a bus voltage when they are idle. Connecting to the line, a master device generates the SCL signal and device address, then arranges the communication sequence. The MPQ7795 works as a slave-only device, which supports up to 400kbps of bidirectional data transfer in fast mode, adding flexibility to the power supply solution. The output voltage, transition slew rate, and additional converter parameters can be instantaneously controlled by I<sup>2</sup>C interface.

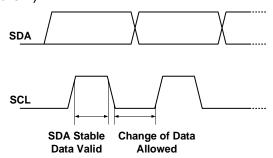

#### **Data Validity**

One clock pulse is generated for each data bit transferred. The data on the SDA line must be stable during the high period of the clock. The high or low state of the SDA line can only change when the clock signal on the SCL line is low (see Figure 4).

Figure 4: Bit Transfer on the I<sup>2</sup>C Bus

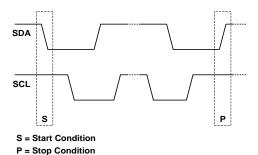

#### **Start and Stop Commands**

The start and stop commands are signaled by the master device, which signifies the beginning and the end of the I<sup>2</sup>C transfer. The start command is defined as the SDA signal transitioning from high to low while the SCL line is high. The stop command is defined as the SDA signal transitioning from low to high while the SCL is high (see Figure 5).

Figure 5: Start and Stop Commands

Start and stop commands are always generated by the master. The bus is considered busy after the start command. The bus is considered free again a certain time after the stop command. The bus stays busy if a repeated start command is generated instead of a stop command. The start and repeated start commands are functionally identical.

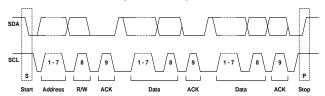

#### **Transfer Data**

Every byte puts on the SDA line must be 8 bits long. Each byte must be followed by an acknowledge (ACK) bit. The acknowledge-related clock pulse is generated by the master. The transmitter releases the SDA line (high) during the acknowledge clock pulse. The receiver must pull down the SDA line during the acknowledge clock pulse, so that it remains stable low during the high period of the clock pulse.

Figure 6 shows the data transfer format. After the start command, a slave address is sent. This address is 7 bits long followed by an eighth data direction bit (R/W). A "0" indicates a transmission (write), and a "1" indicates a request for data (read). A data transfer is always terminated by a stop command, which is generated by the master. However, if a master still wishes to communicate on the bus, it can generate a repeated start command and address another slave without first generating a stop command.

Figure 6: A Complete Data Transfer

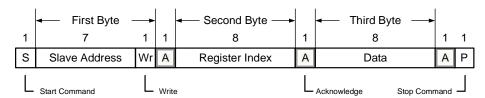

#### **Write Sequence**

The typical write sequence requires a master's start command, a valid slave address, a register index byte, and a corresponding data byte.

After receiving each byte, the MPQ7795 acknowledges what it has received by pulling the SDA line low during the high period of a single clock pulse. A valid I<sup>2</sup>C address selects the MPQ7795 (see Figure 7).

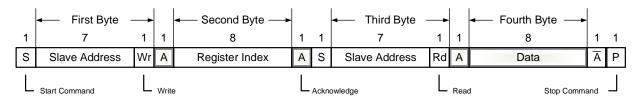

#### **Read Sequence**

The typical MPQ7795 read sequence requires a master's start command, then a valid slave address, followed by a register index byte. An additional start command comes with the re-

broadcast of the slave address, with bit[1] indicating a read cycle. The following fourth byte contains the data being returned by the MPQ7795. The byte value in the data byte reflects the value of the register index that was previously queried (see Figure 8).

#### **Chip Address**

The MPQ7795's 7-bit address is 0x6C.

When the master sends the address as an 8-bit value, the 7-bit address should be followed by bit 0 or 1 to indicate write or read operation, respectively. For write operations, the first byte should be 0xD8; for read operations, the first byte should be 0xD9.

Figure 7: Write Sequence

Figure 8: Read Sequence

### **REGISTER MAP**

The default slave address is 0x6C. The MPQ7795-AEC1's detailed register map is described in the tables below.

### FAULT\_STATUS\_DETECTION\_1 (0x01)

The FAULT\_STATUS\_DETECTION\_1 command indicates whether certain faults have occurred.

| Command  | Command FAULT_STATUS_DETECTION_1 |     |     |     |     |      |      |      |

|----------|----------------------------------|-----|-----|-----|-----|------|------|------|

| Format   | Unsigned binary                  |     |     |     |     |      |      |      |

| Bit      | 7                                | 6   | 5   | 4   | 3   | 2    | 1    | 0    |

| Access   | W1C                              | W1C | W1C | W1C | W1C | W1C  | W1C  | W1C  |

| Function | OT                               | DC  | UV  | ocs | LF  | BSTF | RESE | RVED |

| Bits | Bit Name | Default | Description                                                                          |

|------|----------|---------|--------------------------------------------------------------------------------------|

|      |          |         | Indicates whether over-temperature shutdown has occurred.                            |

| 7    | ОТ       | 0b      | No over-temperature shutdown has occurred     Over-temperature shutdown has occurred |

|      |          |         | Indicates whether DC offset detection has occurred.                                  |

| 6    | DC       | 0b      | 0: No DC offset fault has occurred 1: A DC offset fault has occurred                 |

|      |          |         | Indicates whether PV <sub>DD</sub> under-voltage lockout (UVLO) has occurred.        |

| 5    | UV       | 0b      | 0: No PV <sub>DD</sub> UVLO has occurred 1: PV <sub>DD</sub> UVLO has occurred       |

|      | ocs      | 0b      | Indicates whether over-current shutdown has occurred.                                |

| 4    |          |         | No over-current shutdown has occurred     Over-current shutdown has occurred         |

|      |          |         | Indicates whether a load fault has occurred.                                         |

| 3    | LF       | 0b      | 0: No load fault has occurred 1: A load fault has occurred                           |

|      |          |         | Indicates whether a boost capacitor fault has occurred.                              |

| 2    | BSTF     | 0b      | No boost capacitor fault has occurred     A boost capacitor fault has occurred       |

| 1:0  | RESERVED | -       | Reserved.                                                                            |

#### FAULT\_STATUS\_DETECTION\_2 (0x02)

The FAULT\_STATUS\_DETECTION\_2 command indicates certain device statuses.

| Command  | FAULT_STATUS_DETECTION_2 |                             |    |     |    |    |    |    |  |

|----------|--------------------------|-----------------------------|----|-----|----|----|----|----|--|

| Format   |                          | Unsigned binary             |    |     |    |    |    |    |  |

| Bit      | 7                        | 7 6 5 4 3 2 1 0             |    |     |    |    |    |    |  |

| Access   | W1C                      | W1C W1C W1C W1C W1C W1C W1C |    |     |    |    |    |    |  |

| Function | PLY                      | MU                          | LD | FLT | SL | OL | GS | PS |  |

| Bits | Bit Name | Default | Description                                      |  |  |

|------|----------|---------|--------------------------------------------------|--|--|

|      |          |         | Indicates whether the MPQ7795 is in play mode.   |  |  |

| 7    | PLY      | 0b      | 0: Not in play mode<br>1: Currently in play mode |  |  |

|     | MU  |    | Indicates whether the MPQ7795 is in mute mode.                                      |

|-----|-----|----|-------------------------------------------------------------------------------------|

| 6   |     | 0b | 0: Not in mute mode 1: Currently in mute mode                                       |

|     |     |    | Indicates whether the MPQ7795 is performing load diagnostics.                       |

| 5   | LD  | 0b | O: Not performing load diagnostics     Currently performing load diagnostics        |

|     |     |    | Indicates whether the MPQ7795 is in a fault state.                                  |

| 4   | FLT | 0b | 0: Not in a fault state 1: Currently in a fault state                               |

|     |     | 0b | Indicates whether a shorted load is present.                                        |

| 3   | SL  |    | No shorted load is present     A shorted load is present                            |

|     |     |    | Indicates whether an open load is present.                                          |

| 2   | OL  | 0b | 0: No open load is present 1: An open load is present                               |

|     | GS  | 0b | Indicates whether an output short to ground is present.                             |

| 1:0 |     |    | 0: No output short to ground is present     1: An output short to ground is present |

# PARAMETER\_CONTROL\_AND\_SETTING (0x03)

The PARAMETER\_CONTROL\_AND\_SETTING command sets certain device parameters.

| Command  | PARAMETER_CONTROL_AND_SETTING |                         |  |  |  |     |     |  |

|----------|-------------------------------|-------------------------|--|--|--|-----|-----|--|

| Format   | Unsigned binary               |                         |  |  |  |     |     |  |

| Bit      | 7                             | 7 6 5 4 3 2 1 0         |  |  |  |     |     |  |

| Access   | R/W                           | R/W R/W R/W R/W R/W R/W |  |  |  |     |     |  |

| Function | G[1:0] PL[2:0]                |                         |  |  |  | F[1 | :0] |  |

| Bits | Bit Name | Default | Description                                          |

|------|----------|---------|------------------------------------------------------|

|      |          |         | Sets the gain.                                       |

| 7:6  | G[1:0]   | 00b     | 0h: 20dB<br>1h: 26dB<br>2h: 32dB<br>3h: 36dB         |

|      |          |         | Sets the power limit.                                |

| 5:3  | PL[2:0]  | 111b    | 0h: 5V<br>1h: 5.9V<br>2h: 7V<br>3h: 8.4V             |

| 2    | RESERVED | -       | Reserved.                                            |

|      |          |         | Sets the switching frequency (fsw).                  |

| 1:0  | F[1:0]   | 10b     | 0h: 330kHz<br>1h: 384kHz<br>2h: 470kHz<br>3h: 2.2MHz |

#### APPLICATION INFORMATION

#### **Selecting the Input Coupling Capacitor**

The input coupling capacitor transmits the AC signal from the source to the MPQ7795 while blocking the DC voltage. Choose an input coupling capacitor such that the corner frequency ( $f_{\text{IN}}$ ) is below the passband frequency. The corner frequency can be calculated with Equation (3):

$$f_{IN} = \frac{1}{2 \times \pi \times R_{IN} \times C_{IN}}$$

(3)

The input resistor's impedance changes at different gain settings. At the same gain setting, the input impedance from part to part may shift by ±20% due to shifts in the actual resistance of the input resistors. Note that the gain variation between different parts is small.

For design purposes, the input network should be designed assuming an input impedance of  $16k\Omega$ , which is the MPQ7795's absolute minimum input impedance. At lower gains, the impedance can be as high as  $90k\Omega$ .

#### **Power Source**

The MPQ7795's power supply rejection is excellent, though power supply noise can pass to the output, so it is important to minimize power supply noise within the pass-band frequencies. Bypass the power supply with a large capacitor (typically aluminum electrolytic), along with two

smaller 1µF and 1nF ceramic capacitors placed at the PVDD supply pins.

#### **Output Short-to-Battery Protection**

If the output is shorted to a voltage bus that exceeds  $PV_{DD}$ , the MOSFET's body diode turns on, and the power loss can generate excessive heat. If possible, it is recommended to place a reverse blocking diode or MOSFET in series with PVDD.

#### **Input Signal**

Considering the internal 2V biased voltage, the amplitude of INN and INP should be limited to a 2V peak. A greater value can cause distortion and damage the chip. If the external input signals (INN and INP) have another DC bias, this effect can be eliminated with a series of output capacitors.

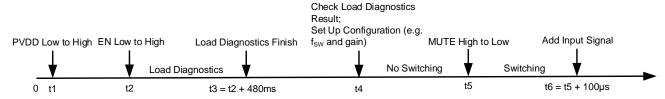

#### Start-Up Sequence

The MPQ7795 has a soft-start function to eliminate the popping noise when the system starts up. Figure 9 on page 37 shows the recommended start-up sequence. Soft start takes about  $100\mu s$  to set up  $V_{OUT}$ . Therefore, it is recommended to add an input signal  $100\mu s$  after turning MUTE from high to low. Soft start occurs as long as the power stage starts switching, including when MUTE goes from high to low, overload or short-load recovery, or overtemperature recovery.

Figure 9: Recommended Start-Up Sequence

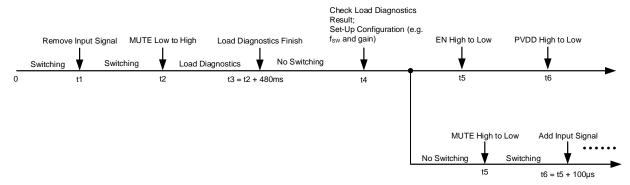

#### **Shutdown Sequence**

Generally, it is not required to wait between steps during the shutdown sequence. It is recommended to perform the load diagnostics before entering play mode again, as the open load and short load are not detected in play mode if the input signal is close to 0 (due to the synchronous switching of BTL channels). Figure 10 on page 37 shows the recommended shutdown sequence.

Figure 10: Recommended Shutdown Sequence

#### PCB Layout Guidelines (12)

An optimized PCB layout is very important for proper operation. A 4-layer layout is strongly recommended to improve thermal performance. For the best results, refer to Figure 11 on page 38 and follow the guidelines below:

- Cut the top layer copper around IN to optimize EMI/EMC performance.

- 2. Place the high-current paths (GND, IN, and SW) very close to the device with short, direct, and wide traces.

- Use large copper areas to minimize conduction loss and thermal stress.

- Place the ceramic input capacitors as close to the IN and GND pins as possible to minimize high-frequency noise.

- Route SW and BST away from sensitive analog areas.

- 6. Use multiple vias to connect the power planes to the inner layer.

#### Note:

12) The recommended PCB layout is based on the circuit in Figure 13 on page 41.

#### PCB Layout and EMI Considerations

The circuit layout is critical for optimal performance, low output distortion, and reduced noise. Duplicate the EVB layout for the best results. For additional layout changes, follow these guidelines below.

- 1. Place the following components as close to the MPQ7795 as possible:

- a. <u>Bootstrap Capacitors (C<sub>BS</sub>)</u>: C<sub>BS</sub> supplies the gate drive's current to the internal HS-FET. Place C<sub>BS</sub> as close to BST pin and SW pins as possible.

- b. Power Supply Bypass Capacitors (C<sub>BYP</sub>): C<sub>BYP</sub> carries the transient current for the switching power stage. To avoid overstressing the MPQ7795 and creating excessive output noise, place C<sub>BYP</sub> as close to the PVDD pins as possible.

- Output Inductor (L<sub>OUT</sub>): Place the output inductors close to MPQ7795 to minimize the size of the switching nodes SWA and SWB.

- 2. Minimize the size of high-current loops that carry rapidly changing currents.

- 3. Place the PVDD bypass capacitors are as close to the MPQ7795 as possible.

- 4. Route any traces carrying the switch node (SW) voltages far from any input signal traces. If the trace must run near the SW trace near the input, shield the input with a ground plane between the traces.

- Minimize nodes that carry rapidly changing voltage, such as SW. If sensitive traces run near a trace connected to SW, place a ground shield between the traces.

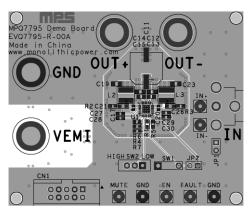

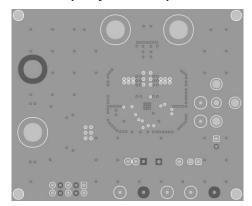

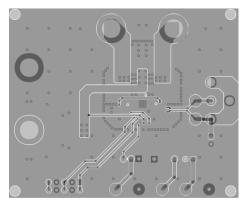

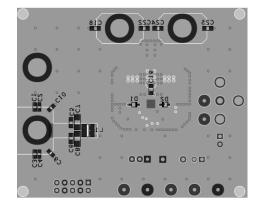

Top Layer and Top Silk

**Inner Layer 1**

**Inner Layer 2**

Bottom Layer and Bottom Silk Figure 11: Recommended PCB Layout

### TYPICAL APPLICATION CIRCUITS

Figure 12: Typical Application Circuit with EMI Filters (470kHz Frequency)

# **TYPICAL APPLICATION CIRCUITS (continued)**

Figure 13: Typical Application Circuit with EMI Filters (2.2MHz Frequency)

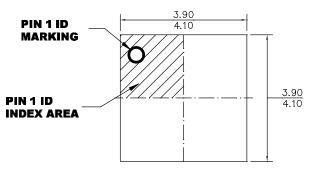

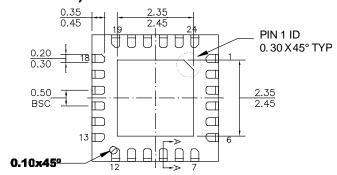

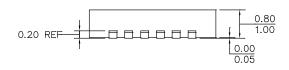

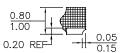

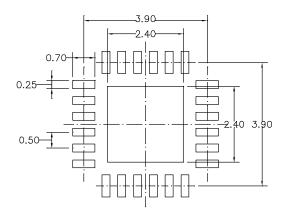

### **PACKAGE INFORMATION**

# QFN-24 (4mmx4mm)

**TOP VIEW**

**BOTTOM VIEW**

**SIDE VIEW**

**SECTION A-A**

#### **NOTE:**

- 1) THE LEAD SIDE IS WETTABLE.

- 2) ALL DIMENSIONS ARE IN MILLIMETERS.

- 3) LEAD COPLANARITY SHALL BE 0.08 MILLIMETERS MAX.

- 4) JEDEC REFERENCE IS MO-220.

- 5) DRAWING IS NOT TO SCALE.

**RECOMMENDED LAND PATTERN**

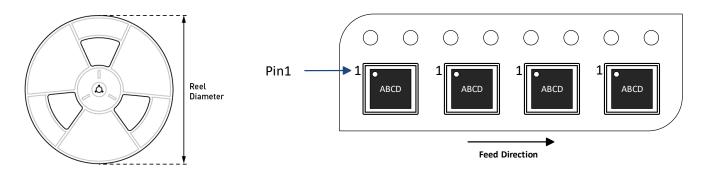

# **CARRIER INFORMATION**

| Part Number           | Package<br>Description | Quantity/<br>Reel | Quantity/<br>Tube | Quantity/<br>Tray | Reel<br>Diameter | Carrier<br>Tape<br>Width | Carrier<br>Tape<br>Pitch |

|-----------------------|------------------------|-------------------|-------------------|-------------------|------------------|--------------------------|--------------------------|

| MPQ7795GRE-<br>AEC1-Z | QFN-24<br>(4mmx4mm)    | 5000              | N/A               | N/A               | 13in             | 12mm                     | 8mm                      |

© 2023 MPS. All Rights Reserved.

### **REVISION HISTORY**

| Revision # | Revision Date | Description     | Pages Updated |

|------------|---------------|-----------------|---------------|

| 1.0        | 3/22/2023     | Initial Release | -             |

Notice: The information in this document is subject to change without notice. Users should warrant and guarantee that thirdparty Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Monolithic Power Systems (MPS):

MPQ7795GRE-AEC1-Z MPQ7795GRE-AEC1-P