MPQ4210

40V, 100W Synchronous Buck-Boost Controller with I<sup>2</sup>C and Current Monitor, AEC-Q100 Qualified

## DESCRIPTION

The MPQ4210 is a synchronous, four-switch, buck-boost controller capable of regulating different output voltages with a wide input voltage range and high efficiency. It provides an I<sup>2</sup>C interface, which supports  $V_{OUT}$  voltage programmability,  $V_{OUT}$  slew-rate control, and output constant current limit programmability, making the MPQ4210 suitable for USB power delivery (PD) design in USB Type-C power supplies.

The MPQ4210 uses valley current control in buck mode and peak current control in boost mode, providing fast load transient response and smooth buck-boost mode transient. The MPQ4210 provides forced continuous conduction mode (FCCM) and a programmable average current limit, which supports flexible designs for different applications.

It also features programmable over-current protection (OCP) mode, programmable over-voltage protection (OVP) mode, and programmable  $V_{\rm IN}$  UVLO hysteresis.

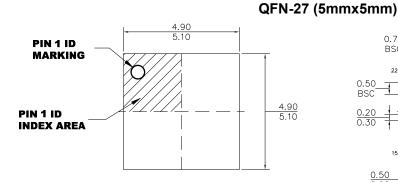

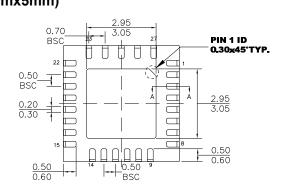

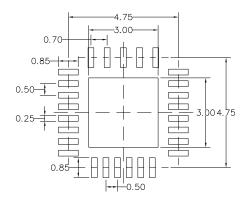

The MPQ4210 is available in a QFN-27 (5mmx5mm) package.

## **FEATURES**

- 6V to 40V Start-Up Input Voltage Range

- 5V to 40V Operation Input Voltage Range

- Flexible I<sup>2</sup>C Interface Control for:

- 0.5V to 28V Output Voltage Range

- 0.3V to 2.047V Reference Voltage Range with 1mV Step

- $\circ$  Selectable V\_{OUT} Slew Rate

- Programmable Constant Current Limit

- Output Current Monitor Function (IMON)

- Programmable Soft-Start Time

- Switching Frequency Spread Spectrum for EMI Optimization

- Integrated VOUT Discharge Function

- Selectable 200kHz, 300kHz, 400kHz, and 600kHz Switching Frequency

- Forced CCM Operation Mode

- Programmable V<sub>IN</sub> UVLO Hysteresis

- OCP, SCP, and OVP

- Interrupt Indicator for OCP, OVP, and PNG

- Available in a QFN-27 (5mmx5mm) Package with Wettable Flank

- AEC-Q100 Qualified

## **APPLICATIONS**

- USB Power Delivery

- Industrial PC Power Supplies

- Super-Capacitor Charging

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are registered trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

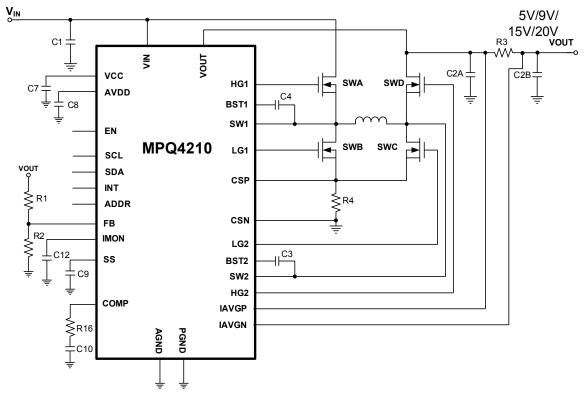

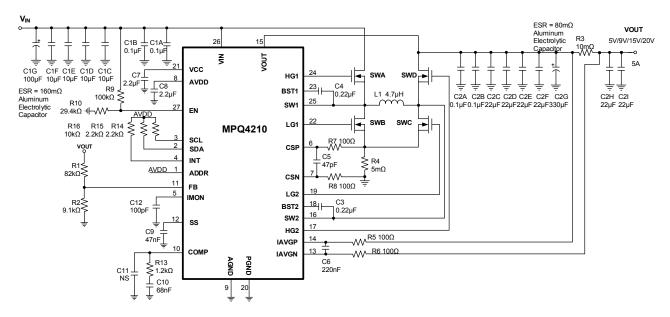

# **TYPICAL APPLICATION**

## **ORDERING INFORMATION**

| Part Number     | Package          | Top Marking |

|-----------------|------------------|-------------|

| MPQ4210GU-AEC1* | QFN-27 (5mmx5mm) | See Below   |

\* For Tape & Reel, add suffix –Z (e.g. MPQ4210GU–AEC1-Z).

## **TOP MARKING**

## MPSYYWW

MP4210

LLLLLLL

MPS: MPS prefix YY: Year code WW: Week code MP4210: Part number LLLLLLL: Lot number

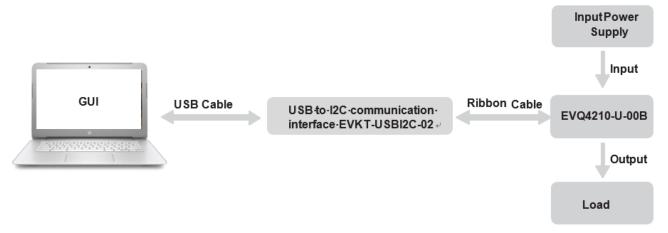

## **EVALUATION KIT EVKT-MPQ4210**

EVKT-MPQ4210 Kit contents: (Items below can be ordered separately).

| # | Part Number            | Item                                                                            | Quantity |

|---|------------------------|---------------------------------------------------------------------------------|----------|

| 1 | EVQ4210-U-00B          | MPQ4210GU Evaluation Board                                                      | 1        |

| 2 | EVKT-USBI2C-02-<br>BAG | Includes USB to I2C Communication interface device, USB Cable, and Ribbon Cable | 1        |

### Order direct from MonolithicPower.com or our distributors.

### Figure A-1: EVKT-MPQ4210 Evaluation Kit Set-Up

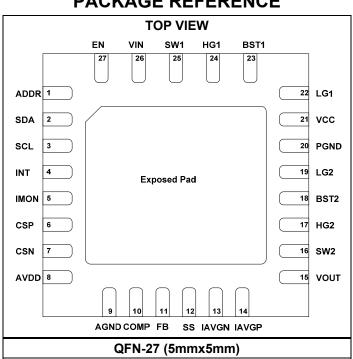

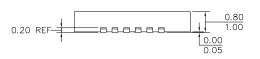

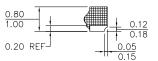

### PACKAGE REFERENCE

## **PIN FUNCTIONS**

| Pin # | Name  | Description                                                                                                                                                                                                                                                                                             |

|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | ADDR  | I <sup>2</sup> C slave address set pin.                                                                                                                                                                                                                                                                 |

| 2     | SDA   | I <sup>2</sup> C data signal.                                                                                                                                                                                                                                                                           |

| 3     | SCL   | I <sup>2</sup> C clock signal.                                                                                                                                                                                                                                                                          |

| 4     | INT   | <b>Interrupt for PNG, OCP, OTP and OVP events.</b> In default set-up, INT is masked off for response to a PNG event. It is an open-drain output, and is pulled low when an interrupt event occurs, recovering to open drain when the fault is cleared. INT is an open drain when the IC is not enabled. |

| 5     | IMON  | Current monitor output. Represents the signal between IAVGP and IAVGN.                                                                                                                                                                                                                                  |

| 6     | CSP   | <b>Positive input of the switching current-sense signal.</b> Connect to the high side of the current-sense resistor.                                                                                                                                                                                    |

| 7     | CSN   | <b>Negative input of the switching current-sense signal.</b> Connect to the low side of the current-sense resistor.                                                                                                                                                                                     |

| 8     | AVDD  | <b>5V internal control circuit bias supply.</b> Decouple with a ≥2.2µF capacitor.                                                                                                                                                                                                                       |

| 9     | AGND  | Analog ground.                                                                                                                                                                                                                                                                                          |

| 10    | COMP  | <b>Internal error amplifier output pin.</b> Connect a capacitor and resistor in series to AGND for loop compensation.                                                                                                                                                                                   |

| 11    | FB    | VOUT voltage feedback pin. Connect a resistor divider from VOUT to FB.                                                                                                                                                                                                                                  |

| 12    | SS    | <b>Soft-start set pin.</b> Sets the hiccup off-time period. Connect an external capacitor to SS.                                                                                                                                                                                                        |

| 13    | IAVGN | <b>Negative terminal of average current limit sense input.</b> The IAVGN and IAVGP pins can only be used for the output current limit setting by connecting to the positive terminal of the output rail.                                                                                                |

# PIN FUNCTIONS (continued)

| Pin # | Name        | Description                                                                                                                                                                                              |

|-------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14    | IAVGP       | <b>Positive terminal of average current limit sense input.</b> The IAVGN and IAVGP pins can only be used for the output current limit setting by connecting to the positive terminal of the output rail. |

| 15    | VOUT        | <b>Voltage sense input.</b> Supplies power to VCC based on VCC power logic. Connect to the output capacitor.                                                                                             |

| 16    | SW2         | <b>Boost switch node of the converter.</b> Connect to the source of SWD and the drain of SWC.                                                                                                            |

| 17    | HG2         | Boost high-side MOSFET gate driver pin. Connect directly to the gate of SWD.                                                                                                                             |

| 18    | BST2        | <b>Bootstrap power pin for boost high-side MOSFET gate driver.</b> Connect one capacitor between BST2 and SW2. BST2 is supplied by VCC or BST1.                                                          |

| 19    | LG2         | Boost high-side MOSFET gate driver pin. Connect directly to the gate of SWC.                                                                                                                             |

| 20    | PGND        | Power ground. Gate-driving current return pin.                                                                                                                                                           |

| 21    | VCC         | <b>Driver circuit and internal bias supply</b> . Powered by VIN or VOUT. Decouple with a $\geq 2.2 \mu$ F ceramic capacitor as close to this pin as possible.                                            |

| 22    | LG1         | Buck low-side MOSFET gate driver pin. Connect directly to the gate of the SWB.                                                                                                                           |

| 23    | BST1        | <b>Bootstrap power pin for buck high-side MOSFET gate driver.</b> Supplied by VCC or BST2. Connect one capacitor between BST1 and SW1.                                                                   |

| 24    | HG1         | Buck high-side MOSFET gate driver pin. Connect directly to the gate of SWA.                                                                                                                              |

| 25    | SW1         | <b>Buck switch node of the converter.</b> Connect to the source of SWA and the drain of SWB.                                                                                                             |

| 26    | VIN         | VIN power supply and voltage sense input.                                                                                                                                                                |

| 27    | EN          | <b>Chip enable control pin.</b> If not used, connect EN to the input source for automatic start-<br>up. EN can also program VIN UVLO. Do not float this pin.                                             |

|       | Exposed Pad | Connect to ground.                                                                                                                                                                                       |

## ABSOLUTE MAXIMUM RATINGS (1)

| VIN, EN0.3V to +45V<br>VOUT, IAVGP, IAVGN0.3V to +30V |

|-------------------------------------------------------|

| VCC0.3V to +8.5V                                      |

| SW1, SW2                                              |

| LG1, LG2                                              |

| 0.3V to +10V (-2V to +11V for <20ns)                  |

| BST1, HG10.3V to V <sub>SW1</sub> + 8.5V              |

| BST2, HG20.3V to V <sub>SW2</sub> + 8.5V              |

| All other pins0.3V to +6.5V                           |

| Continuous power dissipation <sup>(2) (5)</sup>       |

| Junction temperature                                  |

| Lead temperature                                      |

| Storage temperature65°C to +150°C                     |

### **Recommended Operating Conditions** <sup>(3)</sup>

| Start-up voltage (V <sub>ST</sub> )                 | 6V to 40V  |

|-----------------------------------------------------|------------|

| Operation voltage (V <sub>IN</sub> ) <sup>(4)</sup> | 5V to 40V  |

| Output voltage (V <sub>OUT</sub> ) 0                | .5V to 28V |

| Operating junction temp (T <sub>J</sub> )40°C       | to +125°C  |

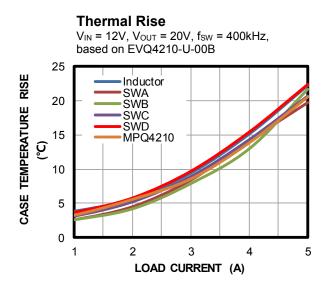

| Thermal Resistance      | θյΑ | θյς |      |

|-------------------------|-----|-----|------|

| EVQ4210-U-00B (5)       | 25  | 6   | °C/W |

| JESD51-7 <sup>(6)</sup> |     | 6   | °C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-to-ambient thermal resistance θ<sub>JA</sub>, and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX) T<sub>A</sub>) / θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- Operation voltage after V<sub>OUT</sub> is regulated to 5V or higher voltage, and the VCC load is smaller than 10mA.

- 5) Measured on EVQ4210-U-00B, 6-layer PCB, 2oz-1oz-1oz-1oz-1oz-2oz.

- 6) The value of 0<sub>JA</sub> given in this table is only valid for comparison with other packages, and cannot be used for design purposes. These values were calculated in accordance with JESD51-7, and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application.

# **ELECTRICAL CHARACTERISTICS**

# $V_{IN}$ = 12V, $V_{OUT}$ = 12V, $V_{EN}$ = 2V, $T_J$ = -40°C to 125°C, typical values are tested at $T_J$ = 25°C, unless otherwise noted.

| Parameter                                 | Condition             | Min                                                                                    | Тур  | Max   | Units |      |

|-------------------------------------------|-----------------------|----------------------------------------------------------------------------------------|------|-------|-------|------|

| Power Supply                              |                       |                                                                                        |      |       |       |      |

| Operating VCC voltage                     | Vcc                   | $V_{IN} = 6V$ or $V_{OUT} = 6V$ ,<br>0mA to 20mA on VCC                                | 5.1  | 5.95  | 6     | V    |

|                                           | VCC                   | $V_{IN}$ = 12V or $V_{OUT}$ = 12V,<br>0mA to 60mA on VCC                               | 6.7  | 7.2   | 7.7   | V    |

| VIN UVLO (7)                              | <b>VIN</b> UVLO-R     | VIN rising                                                                             | 5    | 5.5   | 5.9   | V    |

| VCC UVLO (7)                              | VCC <sub>UVLO-R</sub> |                                                                                        | 3.8  | 4.3   | 4.8   | V    |

| VCC power source change                   | VIN <sub>TH_VCC</sub> | $V_{OUT}$ = 12V, ramp $V_{IN}$<br>from 5V to 10V                                       | 8.1  | 8.8   | 9.5   | V    |

| threshold                                 | VOUT <sub>TH_VC</sub> | from 5V to 10V                                                                         | 8.1  | 8.8   | 9.5   | V    |

| AVDD voltage                              | VAVDD                 | $V_{IN}$ = 12V, 0mA to 5mA                                                             | 4.7  | 5.2   | 5.6   | V    |

|                                           |                       | V <sub>EN</sub> = 0V, measured on<br>VIN and VOUT pins                                 |      |       | 2     | μA   |

| Shutdown current                          | Isd                   | ENPWR bit = 0,<br>$V_{IN}$ = 12V, $V_O$ = 0V,<br>measured on VIN pin,<br>$V_{EN}$ = 2V | 300  | 450   | 600   | μΑ   |

| Enable Control (EN Pin)                   |                       |                                                                                        |      |       |       |      |

| EN turn-on threshold voltage              | V <sub>EN-ON</sub>    | VEN rising (switching)                                                                 | 1.25 | 1.35  | 1.45  | V    |

| EN high threshold voltage                 | V <sub>EN-H</sub>     | V <sub>EN</sub> rising (micro-power)                                                   |      |       | 1.1   | V    |

| EN low threshold voltage                  | V <sub>EN-L</sub>     | VEN falling (micro-power)                                                              | 0.4  |       |       | V    |

| EN turn-on hysteresis current             | I <sub>EN-HYS</sub>   | EN > V <sub>EN-ON</sub> , EN source<br>current                                         | 3.2  | 4.7   | 6.2   | μA   |

| EN input current                          | I <sub>EN</sub>       | V <sub>EN</sub> = 0V, 3.3V                                                             |      | 0.01  |       | μA   |

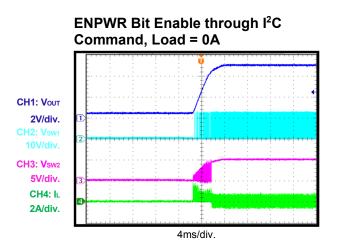

| ENPWR turn-on delay <sup>(8)</sup>        | TENPWR_Delay          | From ENPWR =<br>1 to switching,<br>Css = 47nF                                          |      | 1     |       | ms   |

| Feedback Control                          |                       |                                                                                        |      |       |       |      |

|                                           |                       | VREF bits = 7FFH,<br>TJ = 25°C                                                         | -1%  | 2.047 | 1%    | V    |

| Reference voltage                         | V <sub>REF</sub>      | VREF bits = 7FFH,<br>T <sub>J</sub> = -40°C to 125°C                                   | -2%  | 2.047 | 2%    | V    |

|                                           | V ILLI                | VREF bits = 1F4H,<br>$T_J = 25^{\circ}C$                                               | -2%  | 0.5   | 2%    | V    |

|                                           |                       | VREF bits = 1F4H,<br>$T_J = -40^{\circ}$ C to 125°C                                    | -3%  | 0.5   | 3%    | V    |

| FB input current                          | I <sub>FB</sub>       | V <sub>FB</sub> = 0.52V                                                                |      |       | 200   | nA   |

| Error amp transconductance                | GEA                   | $V_{FB} = V_{REF} + 10mV,$<br>$V_{COMP} = 2.5V$                                        |      | 1220  |       | µA/V |

| Comp to current sense gain <sup>(8)</sup> | Gcs                   | $\Delta V_{CS} / \Delta V_{COMP}$                                                      |      | 200   |       | mV/V |

| SS charge current                         | I <sub>CHG_SS</sub>   | During soft start and<br>overload recovery                                             | 2    | 6     | 10    | μA   |

| SS discharge current                      | Idsg_ss               | After hiccup protection is triggered                                                   |      | 1     |       | μA   |

# ELECTRICAL CHARACTERISTICS (continued)

# $V_{IN}$ = 12V, $V_{OUT}$ = 12V, $V_{EN}$ = 2V, $T_J$ = -40°C to 125°C, typical values are tested at $T_J$ = 25°C, unless otherwise noted.

| Parameter                                                                       | Symbol              | Condition                                                 | Min                           | Тур      | Max  | Units |

|---------------------------------------------------------------------------------|---------------------|-----------------------------------------------------------|-------------------------------|----------|------|-------|

| VREF change slew-rate                                                           | T <sub>REF</sub>    | SR = 00                                                   | 25                            | 38       | 51   | mV/ms |

| 5                                                                               | IREF                | SR = 11                                                   | 130                           | 150      | 170  | mV/ms |

| Current Limit                                                                   | 1                   | T                                                         | 1                             |          | 1    | 1     |

| Buck valley current limit                                                       | ILIMIT_BUCK         |                                                           | 113                           | 133      | 153  | mV    |

| Boost peak current limit                                                        | ILIMIT_BOOST        |                                                           | 130                           | 150      | 170  | mV    |

| OCP hiccup threshold <sup>(8)</sup>                                             | VTH_OCP             |                                                           |                               | 60%      |      | VREF  |

| Average constant current limit                                                  | Iav_limit           | ILIM bits = 011,<br>IAVGN = 12V, ramp<br>IAVGP voltage up | 39                            | 45       | 51   | mV    |

| J                                                                               | _                   | ILIM bits = 111,<br>IAVGN = 12V, ramp<br>IAVGP voltage up | 60                            | 68       | 76   | mV    |

| CSP and CSN bias current                                                        | Ics_bias            | $V_{CSP} = V_{CSN} = 0V$                                  |                               | 70       |      | μA    |

| IAVGP and IAVGN bias current                                                    | Iav_bias            | IAVGN = 5V<br>IAVGN = 20V<br>IAVGP - IAVGN =<br>40mV      |                               | 55       |      | μA    |

| Switching Frequency                                                             |                     |                                                           |                               |          | T    |       |

|                                                                                 |                     | fsw bits = 10, Vout = 5V                                  | 300                           | 400      | 500  | kHz   |

| Switching frequency                                                             | fsw                 | fsw bits = 00<br>V <sub>OUT</sub> = 5V                    | 140                           | 200      | 260  | kHz   |

| Frequency spread span <sup>(8)</sup>                                            | fss                 | Dither bit = 1                                            |                               | ±6%      |      | fsw   |

| Frequency spread spectrum<br>modulation frequency <sup>(8)</sup><br>Gate Driver | <b>f</b> modulation | Dither bit = 1                                            |                               | 2        |      | kHz   |

| Gate source current capability                                                  | I <sub>HG_SO</sub>  |                                                           |                               | 0.7      |      | Α     |

| (8)                                                                             | ILG_SO              | $V_{CC} = 7.2V, 4.7nF$ load                               |                               | 0.85     |      | A     |

| Gate sink current capability (8)                                                | ILG_SI              | V <sub>CC</sub> = 7.2V, 4.7nF load                        |                               | 1.6<br>2 |      | A     |

| Low-side gate output high voltage                                               | -<br>Vls_high       |                                                           | V <sub>CC</sub> -<br>0.05     |          |      | V     |

| Low-side gate output low voltage                                                | VLS_LOW             |                                                           |                               |          | 0.05 | V     |

| High-side gate output high voltage                                              | Vhs_high            |                                                           | V <sub>BST-SW</sub> -<br>0.05 |          |      | V     |

| High-side gate output low voltage                                               | VHS_LOW             |                                                           |                               |          | 0.05 | V     |

| Dead-time between high-side gate and low-side gate <sup>(8)</sup>               | T <sub>DEAD</sub>   |                                                           |                               | 30       |      | ns    |

| OVP Protection                                                                  | 1                   | T                                                         | ,                             |          | 1    |       |

| FB feedback OVP trigger threshold                                               | VOVP_RISING         |                                                           | 119%                          | 127%     | 135% | VREF  |

| FB feedback OVP recover threshold                                               | VOVP_FALLING        |                                                           | 104%                          | 111%     | 118% | Vref  |

| Thermal Protection                                                              | I                   | 1                                                         | ,                             |          | T    |       |

| Thermal shutdown <sup>(8)</sup>                                                 | T <sub>SD</sub>     |                                                           |                               | 150      |      | °C    |

| Thermal shutdown hysteresis <sup>(8)</sup>                                      | T <sub>SD-HYS</sub> |                                                           |                               | 25       |      | °C    |

# ELECTRICAL CHARACTERISTICS (continued)

$V_{IN}$  = 12V,  $V_{OUT}$  = 12V,  $V_{EN}$  = 2V,  $T_J$  = -40°C to 125°C, typical values are tested at  $T_J$  = 25°C, unless otherwise noted.

| Parameter                           | Symbol                 | Condition                                      | Min   | Тур    | Max   | Units |

|-------------------------------------|------------------------|------------------------------------------------|-------|--------|-------|-------|

| Power Good (INT Pin)                |                        |                                                |       |        |       |       |

| Power good upper trip threshold     | PGh_fallin<br>g        | INT pin pulls low                              | 110%  | 117%   | 124%  | VREF  |

|                                     | PG <sub>H_RISING</sub> | INT pin naca to nigh                           | 101%  | 106.5% | 112%  | VREF  |

| Power good lower trip threshold     | PGL_FALLIN<br>G        | INT pin pulls low                              | 80%   | 85.5%  | 91%   | VREF  |

|                                     | $PG_{L_{RISING}}$      | PNG bit resets to 0, and INT pin rises to high | 85%   | 91%    | 97%   | VREF  |

| Power good delay (INT response      |                        | Low to high                                    |       | 10     |       | μs    |

| to PNG event)                       | PGdelay                | VOUT UV, high to low                           |       | 2      |       | μs    |

|                                     |                        | VOUT OV, high to low                           |       | 6.5    |       | μs    |

| INT sink current capability         | Isink_int              | Sink 4mA                                       |       | 0.1    | 0.4   | V     |

| INT leakage current                 | ILKG_INT               | $V_{INT} = 5V$                                 |       |        | 1     | μA    |

| I <sup>2</sup> C Interface (400kHz) |                        |                                                |       |        |       |       |

| Input logic low voltage             | VLI                    | SCL, SDA                                       |       |        | 0.8   | V     |

| Input logic high voltage            | V <sub>HI</sub>        | SCL, SDA                                       | 2     |        |       | V     |

| Logic input current                 | Iscl_sda_lk<br>g       | SCL/SDA = 5V                                   | -1    |        | 1     | μA    |

| Output logic low voltage            | VLO                    | SDA, sink 4mA                                  |       |        | 0.4   | V     |

| ADDR Pin Setting Threshold          |                        |                                                |       |        |       |       |

| Voltage threshold 1                 | ADDR1                  | Set I <sup>2</sup> C address 64H               | 0.51  |        | 0.68  | AVDD  |

| Voltage threshold 2                 | ADDR2                  | Set I <sup>2</sup> C address 66H               | 0.74  |        |       | AVDD  |

| Pin to GND pull-down resistor       | RADDR                  | ADDR pin                                       |       | 2      |       | MΩ    |

| Current Monitor Function            |                        |                                                |       |        |       |       |

| IMON output voltage gain            |                        | +5mV IAVG sense voltage                        |       | 18.8   |       | V/V   |

| IMON output voltage gain            | GAINIMON               | +55mV IAVG sense voltage                       | 16.92 | 18.8   | 20.68 | V/V   |

Notes:

7) The MPQ4210 has a minimum start-up voltage of 6V, and VIN UVLO falling is lower than VCC UVLO falling.

8) Guaranteed by characterization.

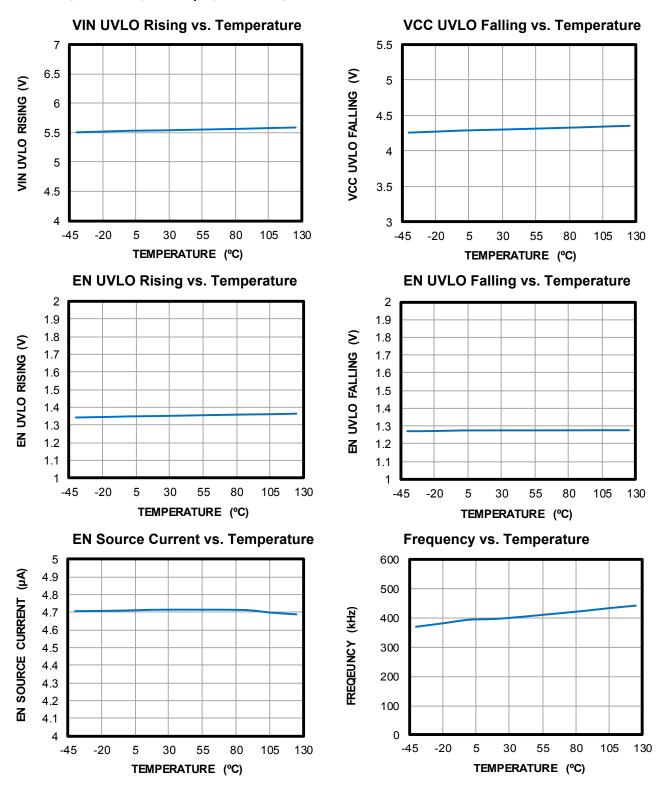

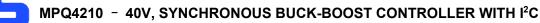

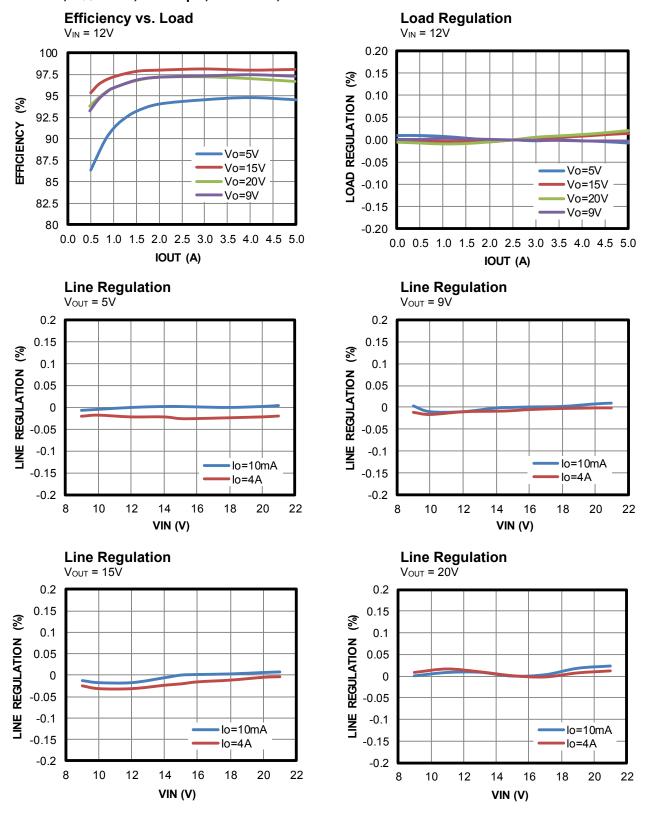

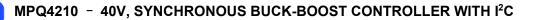

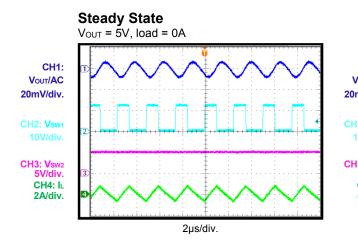

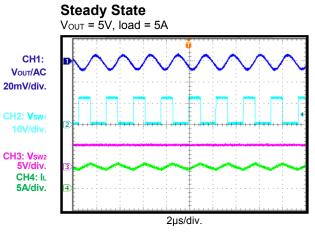

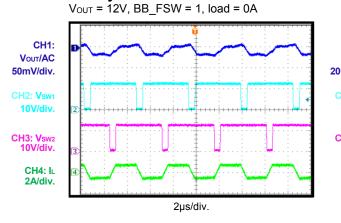

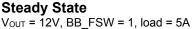

# **TYPICAL PERFORMANCE CHARACTERISTICS**

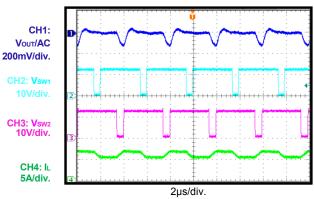

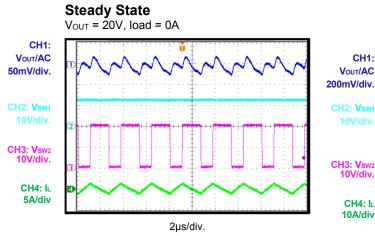

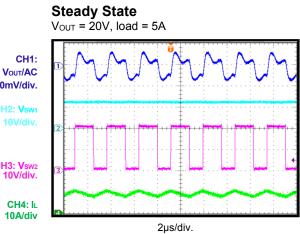

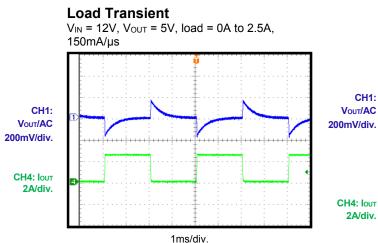

$V_{IN}$  = 12V,  $V_{OUT}$  = 5V, L = 4.7µH,  $T_A$  = 25°C, unless otherwise noted.

$V_{IN}$  = 12V,  $V_{OUT}$  = 5V, L = 4.7µH,  $T_A$  = 25°C, unless otherwise noted.

MPQ4210 Rev. 1.1 www.MonolithicPower.com 7/12/2019 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2019 MPS. All Rights Reserved.

MPQ4210 Rev. 1.1 7/12/2019 www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2019 MPS. All Rights Reserved.

$V_{IN}$  = 12V,  $V_{OUT}$  = 5V, L = 4.7µH, T<sub>A</sub> = 25°C, unless otherwise noted.

$V_{IN}$  = 12V,  $V_{OUT}$  = 5V, L = 4.7µH,  $T_A$  = 25°C, unless otherwise noted.

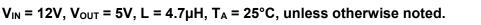

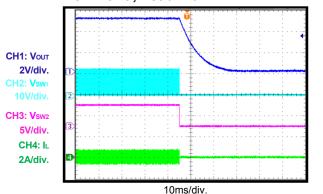

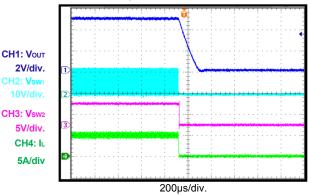

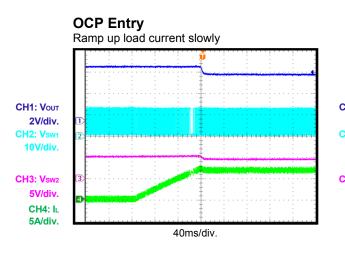

CH1: Vour 2V/div. CH2: Vsw1 10V/div. CH3: Vsw2 5V/div. CH4: IL 5A/div.

# ENPWR Bit Disable through I<sup>2</sup>C Command, Load = 0A

EN Pin Disable, Load = 10mA

ENPWR Bit Disable through I<sup>2</sup>C Command, Load = 5A

### EN Pin Disable, Load = 5A

MPQ4210 Rev. 1.1 7/12/2019

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2019 MPS. All Rights Reserved.

$V_{IN}$  = 12V,  $V_{OUT}$  = 5V, L = 4.7µH, T<sub>A</sub> = 25°C, unless otherwise noted.

Steady State

MPQ4210 Rev. 1.1 7/12/2019

Load Transient

150mA/µs

CH1:

V<sub>IN</sub> = 12V, V<sub>OUT</sub> = 5V, load = 2.5A to 5A,

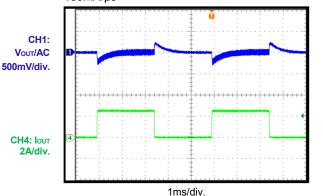

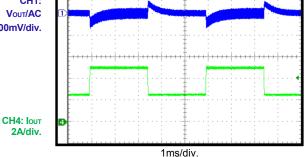

## **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

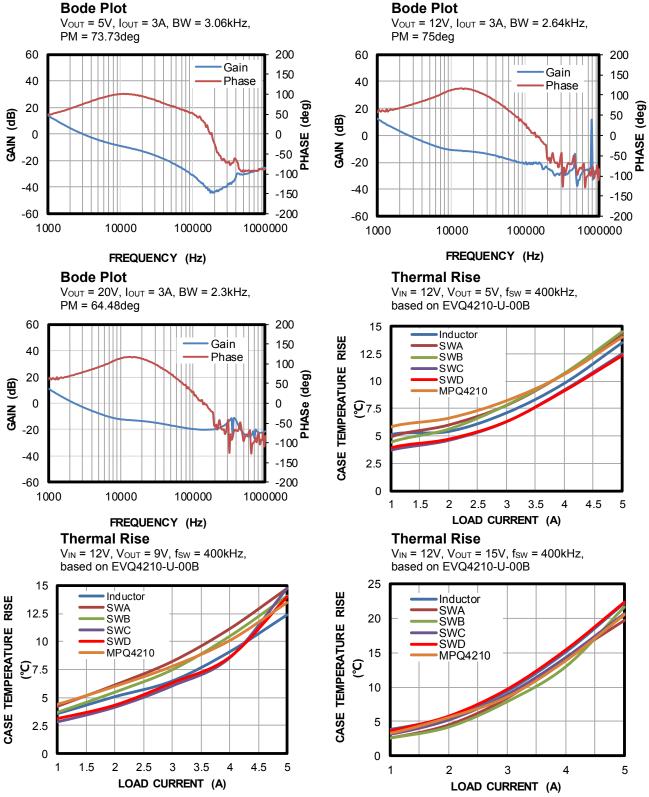

$V_{IN}$  = 12V,  $V_{OUT}$  = 5V, L = 4.7µH, T<sub>A</sub> = 25°C, unless otherwise noted.

Load Transient

$V_{IN}$  = 12V,  $V_{OUT}$  = 20V, load = 0A to 2.5A, 150mA/µs

CH4: IOUT 2A/div. 1ms/div. Load Transient V<sub>IN</sub> = 12V, V<sub>OUT</sub> = 20V, load = 2.5A to 5A, 150mA/µs CH1: Vout/AC 500mV/div.

MPQ4210 Rev. 1.1 7/12/2019

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2019 MPS. All Rights Reserved.

5V/div.

CH2: Vswi

10V/div.

CH4: I∟

10A/div

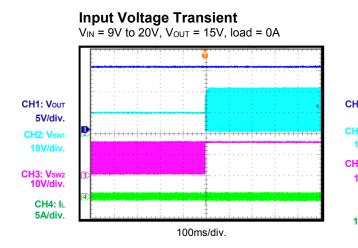

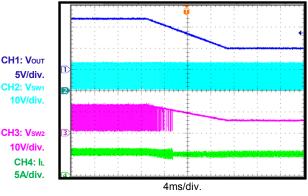

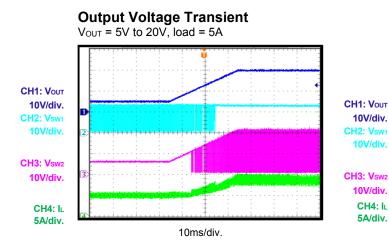

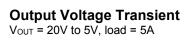

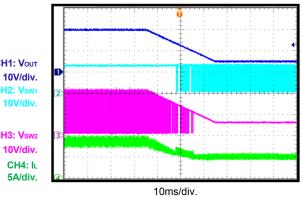

# **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

$V_{IN}$  = 12V,  $V_{OUT}$  = 5V, L = 4.7µH, T<sub>A</sub> = 25°C, unless otherwise noted.

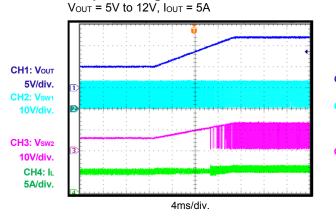

**Output Voltage Transient**

**Output Voltage Transient**

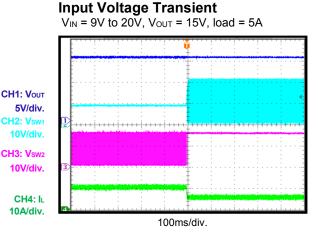

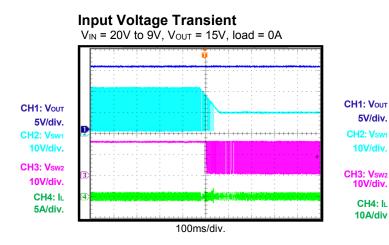

Input Voltage Transient

VIN = 20V to 9V, VOUT = 15V, load = 5A

100ms/div.

MPQ4210 Rev. 1.1 7/12/2019

$V_{IN}$  = 12V,  $V_{OUT}$  = 5V, L = 4.7µH, T<sub>A</sub> = 25°C, unless otherwise noted.

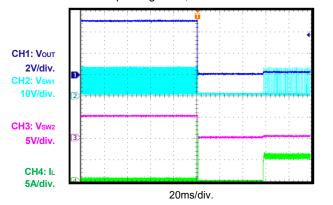

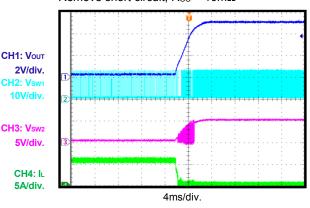

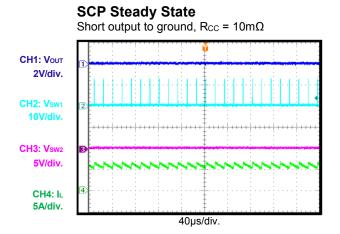

CH1: Vour 2V/div. CH2: Vsw1 10V/div. CH3: Vsw2 5V/div. CH4: lL 5A/div.

Short output to ground,  $R_{CC} = 10m\Omega$

SCP Recovery Remove short circuit,  $R_{CC} = 10m\Omega$

MPQ4210 Rev. 1.1 7/12/2019

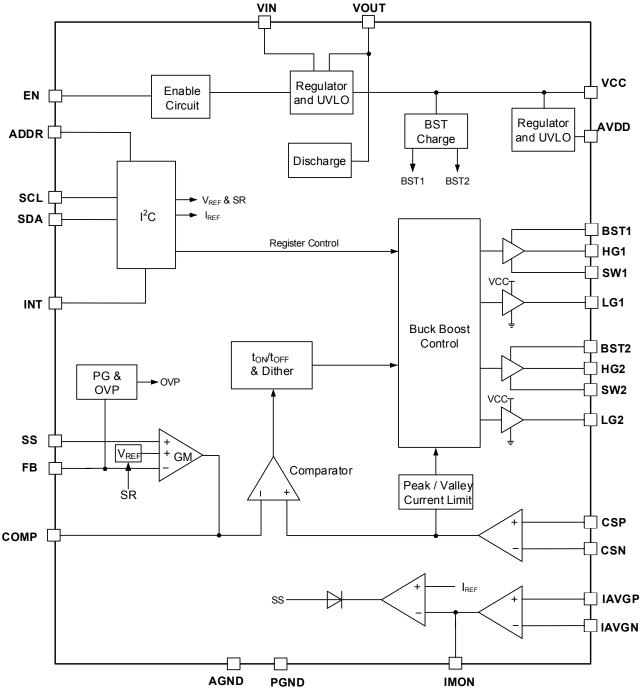

# FUNCTIONAL BLOCK DIAGRAM

Figure 1: Functional Block Diagram

## **OPERATION**

The MPQ4210 is a four-switch buck-boost controller. It works with fixed frequency in buck, boost, and buck-boost modes. One special buck-boost control strategy provides high efficiency over the device's full input range and smooth transient between different modes. Figure 1 shows the internal block diagram, and the following sections describe the MPQ4210's functions.

### **Buck-Boost Operation**

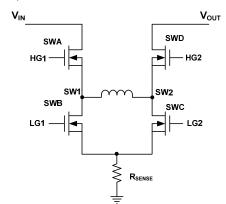

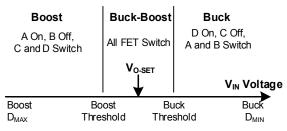

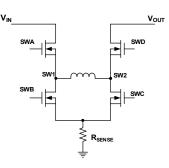

The MPQ4210 can regulate output above, equal to, or below the input voltage. Based on the one-inductor, four-switch power structure (see Figure 2), it operates in buck mode, boost mode, or buck-boost mode with different  $V_{IN}$  inputs (see Figure 3).

Figure 2: Buck-Boost Topology

Figure 3: Buck-Boost Operation Range

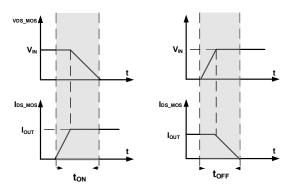

## Buck Mode (V<sub>IN</sub> > V<sub>OUT</sub>)

When  $V_{IN}$  is significantly higher than  $V_{OUT}$ , the MPQ4210 works in buck mode. SWA and SWB switch during buck regulation; while SWC is off, SWD remains on to conduct the inductor current.

In each cycle of buck mode, SWA turns on when the FB voltage ( $V_{FB}$ ) drops below the reference voltage ( $V_{REF}$ ). After SWA turns off, SWB turns on to conduct the inductor current until it triggers

the COMP control signal. By repeating operation in this way, the converter regulates the output voltage.

### Boost Mode (VIN < VOUT)

When  $V_{IN}$  is significantly lower than  $V_{OUT}$ , the MPQ4210 works in boost mode. In boost mode, SWC and SWD switch for the boost regulation. While SWB is off, SWA remains on to conduct the inductor current.

In each cycle of boost mode, SWC turns on to conduct the inductor current. When the inductor current rises and triggers the control signal on COMP, SWC turns off and SWD turns on for the current freewheel. Then SWC turns on and off repeatedly to regulate the output voltage in boost mode.

## Buck-Boost Mode (V\_IN $\approx$ V\_OUT)

When  $V_{IN}$  is close to  $V_{OUT}$ , the converter cannot provide enough energy to load in buck mode due to SWA's minimum off time, or the converter supplies too much power to load in boost mode due to SWC's minimum on time. In these conditions, the MPQ4210 adopts buck-boost control to regulate the output.

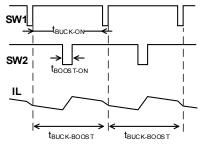

Figure 4: Buck-Boost Waveform

If  $V_{IN}$  is close to  $V_{OUT}$ , buck-boost mode engages, and one boost switching is inserted into each buck switching period. The MOSFET turn-on sequence is: SWA&SWD  $\rightarrow$  SWA&SWC  $\rightarrow$ SWA&SWD  $\rightarrow$  SWB&SWD. Then the inductor current can meet the COMP voltage requirement, and supply enough current to output.

### **Power Supply**

The MPQ4210's internal circuit is powered by 5.2V AVDD, while the gate drivers are powered by 7.2V VCC. VCC is regulated from  $V_{IN}$  and  $V_{OUT}$ , while AVDD is powered by VCC.

When  $V_{IN}$  power is supplied and EN is high, the MPQ4210 tries to regulate VCC at 7.2V, and at the same time AVDD is regulated to 5.2V. When AVDD rises above the UVLO voltage, the part starts switching if ENPWR is high, and regulates  $V_{OUT}$  by soft-start control. If  $V_{IN}$  and  $V_{OUT}$  are both above 8.8V, the MPQ4210 powers VCC from whichever is the lower voltage source to reduce power-loss. Otherwise, it powers VCC from the higher voltage power source of  $V_{IN}$  and  $V_{OUT}$  to get enough VCC voltage. VCC and BST have separate UVLO, which keeps the gate signal off. VCC and BST should have enough voltage to enable MPQ4210 switching, except for AVDD UVLO.

The MPQ4210 operates within a 6V to 40V input voltage range. When VCC is powered from VOUT after start-up, the part works until  $V_{\rm IN}$  drops below 5V.

When the MPQ4210 is powered off by AVDD\_UVLO or the EN signal, the I<sup>2</sup>C interface cannot respond to the host, and COMP is immediately pulled low. The VCC, AVDD, and BST voltages drop slowly with leakage, but all logic is off.

### Start-Up

When the MPQ4210 is enabled, it starts switching with soft-start (SS) control. The SS circuit charges current to the SS pin and ramps the SS voltage up from 0V. It then feeds to the error amplifier to control output voltage. After the SS signal rises to the programmed reference voltage (set by VREF bits), soft start completes and closed-loop regulation starts. The SS voltage rises and clamps at 0.6V higher than  $V_{REF}$  in steady state, unless a protection is triggered.

Normally the MPQ4210 starts with buck switching after start-up because  $V_{OUT}$  is much lower than  $V_{IN}$ . If there is some bias voltage on  $V_{OUT}$ , the part will not switch until the SS signal rises above  $V_{FB}$ , which is proportional to the  $V_{OUT}$  bias voltage. During SS, the IC works in auto

PFM mode. OVP and hiccup-OCP do not work during the SS period.

### Enable (EN) and Programmable UVLO

The EN pin enables and disables the MPQ4210. When applying a voltage higher than the EN high threshold (>1.1V), the part starts up some of the internal circuits (micro-power mode). If the EN voltage exceeds the turn-on threshold (1.35V), the MPQ4210 enables all functions and starts switching operation. Switching operation is disabled when the EN voltage falls below its lower threshold (<1.28V).

If  $V_{EN} < 0.4V$ , the MPQ4210 completely shuts down. After shutdown, the part sinks a small amount of current from the input power (typically <1µA). EN is compatible with voltage up to 40V. For automatic start-up, connect EN directly to VIN. During EN shutdown, the I<sup>2</sup>C resets to its default value after a 200ms discharge time.

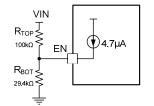

The MPQ4210 features a programmable UVLO hysteresis. When powering up, EN sources a 4.7 $\mu$ A current out of the EN pin (see Figure 5) once the EN voltage is higher than 1.35V. V<sub>IN</sub> must decrease to overcome the current source and stop switching after the IC starts. The VIN start-and-stop switching threshold is determined with Equation (1) and Equation (2):

$$V_{IN_{ON}}(V) = V_{EN_{ON}}(V) \times (1 + \frac{R_{TOP}}{R_{BOT}}) = 5.95V$$

(1)

$$V_{\text{IN_OFF}}(V) = V_{\text{EN_OFF}}(V) \times (1 + \frac{R_{\text{TOP}}}{R_{\text{BOT}}}) - 4.7 \mu A \times R_{\text{TOP}}(k\Omega) \div 1000 = 5.16V$$

(2)

Where  $V_{\text{EN}\_\text{ON}}$  is about 1.35V (typical),  $V_{\text{EN}\_\text{OFF}}$  is about 1.28V.

Figure 5: VIN UVLO Program

### Forced CCM Mode

The MPQ4210 works in forced continuous conduction mode (FCCM). Buck on time and boost off time are determined by an internal circuit to get fixed frequency, based on the  $V_{IN}/V_{OUT}$  ratio. When the load decreases, the average input current drops and the inductor current may go to negative from  $V_{OUT}$  to  $V_{IN}$  during the SWD on-period. This forces the inductor current to work in continuous mode with fixed frequency, producing a low  $V_{OUT}$  ripple.

### **Switching Current Limit**

The MPQ4210 senses the low-side MOSFET current with the CSP and CSN pins. It provides the valley current limit in buck mode and peak current limit in boost mode for each cycle-by-cycle switch. In buck mode, the next period will not start before  $I_L$  drops to the valley current limit, so it may foldback the frequency when the valley current limit is triggered. The switching current limit can be programmed with an external sense resistor. The SWB and SWC current signal is blanked internally for about 180ns to enhance noise rejection.

When the cycle-by-cycle current limit is triggered, the interrupt OCP bit is set to 1; and if the OCP bit is not masked off, the INT is pulled low.

During over-current condition, the MPQ4210 runs in cycle-by-cycle current limit. It may also trigger hiccup protection or latch-off protection, depending on the OCP\_MODE bit's setting. In hiccup mode, the IC turns off once FB drops below 60% of  $V_{REF}$  and triggers the switching current limit after SS period. It will attempt recovery after a fixed off time, programmed by SS capacitor discharge period. In latch-off mode, the IC turns off if FB falls below 60% of  $V_{REF}$ . Once the latch off protect is triggered, the chip doesn't recover until a new Vin power cycle, EN toggle or ENPWR bit toggle. If the hiccup and latch-off protections are disabled, the IC continues switching with a cycle-by-cycle current limit. The hiccup and latch-off protections are masked during the SS period.

Based on the cycle-by-cycle switching current limit, the MPQ4210 maximum input current can be calculated with Equation (3) in buck mode and Equation (4) in boost mode:

$$\begin{split} I_{INmax}(A) &= \frac{Vo}{VIN} \times \eta \times \\ (\frac{Buckvalleycurrent limit(mV)}{R_{sense}(m\Omega)} + \frac{VIN - Vo}{2 \times L(\mu H) \times f(kHz)} \times \end{split} \tag{3}$$

$$\frac{Vo}{VIN} \times 10^{3}) \\ I_{INmax}(A) &= \frac{Boostpeakcurrent limit(mV)}{R_{sense}(m\Omega)} - \frac{VIN}{2 \times L(\mu H) \times f(kHz)} \times \end{aligned} \tag{4}$$

$$\frac{Vo - VIN}{Vo} \times 10^{3})$$

Where  $\eta$  is the efficiency, the buck valley current limit typical value is 133mV, the boost peak current limit typical value is 150mV, and R<sub>SENSE</sub> is the cycle-by-cycle switching current limit sense resistor.

### Average Current Limit

The IAVGP and IAVGN pins sense the output current in the MPQ4210. A sense resistor can be connected to the VOUT line for average output current limit control. Once the sensed signal is higher than the current limit reference voltage, one internal EA pulls down  $V_{SS}$ . Eventually,  $V_{SS}$  replaces  $V_{REF}$  to control COMP, and the inductor current is limited by COMP to transfer less energy to output. SS regulates output low until the average load current drops.

If the switching current is regulated by the average current limit, and it does not trigger cycle-by-cycle current limit, the MPQ4210 will not trigger hiccup or latch-off protection even if the average current limit is reached. This feature makes constant current charge possible in the MPQ4210. If only the average current limit is triggered, the interrupt OCP bit does not set to 1, and INT will not pull low.

It is recommended to add a  $100\Omega/220$ nF current sense filter (see Figure 13).

### **Overload and Short-Circuit Protection**

When overload occurs, the MPQ4210 limits the output current by average current limit loop regulation. If average current limit loop is disabled, the cycle-by-cycle switching current limit works. In cycle-by-cycle current limit condition, if the IC works in boost mode and the SWC peak current is limited. If the IC works in buck mode, SWB remains on until I<sub>L</sub> drops to the buck valley current limit level, and then the next

MPQ4210 - 40V, SYNCHRONOUS BUCK-BOOST CONTROLLER WITH I<sup>2</sup>C

cycle can kick in. Therefore, the inductor current can be controlled in all work modes.

### **Output Voltage Regulation**

The MPQ4210 regulates  $V_{OUT}$  through FB pin feedback.  $V_{FB}$  is compared to the internal reference, which is between 300mV and 2.047V depending on the VREF register bit's setting. The EA output on COMP controls the inductor current to supply output voltage.

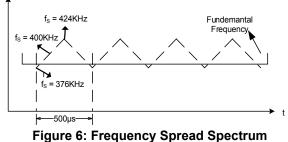

# Switching Frequency and Frequency Spread Spectrum Function

The MPQ4210 programs switching frequency with a 2-bit FSW register. The frequency is selectable at 200kHz, 300kHz, 400kHz, and 600kHz. Typically, a 400kHz switching frequency is recommended.

The MPQ4210 has a frequency spread spectrum function. Set the Dither bit = 1 (0x02, D[4]) to enable this function. Set the Dither bit = 0 to disable the function. The purpose of the spread spectrum is to minimize the peak emissions at certain frequencies.

The MPQ4210 uses a 2kHz triangle wave to modulate the internal oscillator. The frequency span of the spread spectrum operation is  $\pm 6\%$ .

MDO 4240 frequency opread Spectrum

The MPQ4210 frequency spread frequency can be enabled for a 200kHz, 300kHz, 400kHz, or 600kHz switching frequency.

### Gate Driver and BST Power

The MPQ4210 provides four N-channel MOSFET gate drivers for the H-bridge MOSFETs (see Figure 2). Each driver is capable of sourcing and sinking current. In buck operation, LG1 and HG1 switch while HG2 remains on. In boost operation, LG2 and HG2 switch while HG1 remains on. LG1 and LG2 are powered by VCC power, while HG1 and HG2 are powered by BST1 and BST2 power.

Capacitors between BST1 to SW1 and BST2 to SW2 are necessary to supply the power, which can be from an internal diode from VCC or from charging each other.

### **Over-Voltage Protection**

The MPQ4210 monitors FB. If V<sub>FB</sub> exceeds 127% of V<sub>REF</sub> and the OVP\_MODE bits are 01, the IC discharges the V<sub>OUT</sub> capacitor through one internal discharge resistor. It stops discharging when V<sub>FB</sub> drops to 111% of the regulation voltage. If the OVP\_MODE bits are 00, there is no logic to stop switching even if V<sub>FB</sub> is higher than the OVP threshold. If the OVP\_MODE bits are 10, the IC latches off when V<sub>OUT</sub> rises to 127% of V<sub>REF</sub>.

### Interrupt (INT Pin)

The MPQ4210 has one interrupt pin for the following fault events: OCP, OVP, OTP, and PNG ( $V_{OUT}$  power not good) reporting.

When the switching peak cycle-by-cycle current limit (OCP), output over-voltage (FB OVP), or over-temperature protection (OTP) is triggered, the corresponding register bit sets to 1. At the same time, INT pulls low to indicate an interrupt signal, depending on the related Mask register setting.

INT is an open-drain output. When the MPQ4210 is disabled, INT is an open drain.

### Slew-Rate Control and Output Discharge

The MPQ4210 sets the output voltage change slew-rate through internal SR bits. Four kinds of  $V_{REF}$  change (rising and falling) slew rate can be selected in different application requirement: 38mV/ms, 50mV/ms, 75mV/ms and 150mV/ms.

During voltage transient, the discharge function works when GO-BIT sets to 1. The discharge function is disabled automatically after GO\_BIT resets to 0 (which means  $V_{REF}$  change completes). If  $V_{OUT}$  has not been discharged to the goal voltage when  $V_{REF}$  change completes due to too large of an output capacitor, the OVP discharge function or DISCHG bit can be used to continue discharging  $C_{OUT}$ .

The output discharge function is enabled in the following conditions:

- 1. GO\_BIT set to 1. Discharge works until 20ms delay passes after GO\_BIT resets to 0.

- 2. DISCHG bit set to 1.

- 3. OVP\_MODE bits set to 01, and FB is 127% of  $V_{\text{REF}}.$

- 4. ENPWR bit power off. Discharge works until 200ms delay passes.

- 5. EN pin off. Discharge works until 200ms delay passes.

- If VIN\_UVLO is triggered, but AVDD has residual voltage, the MPQ4210 discharges for 200ms. This discharge function may halt if the AVDD voltage drops.

### **Current Monitor Output**

The MPQ4210 senses the average load current through one sense resistor, and outputs one voltage signal on the IMON pin. The signal is amplified from the IAVGP - IAVGN voltage difference. One small capacitor from IMON to AGND is recommended. The IMON output voltage can be calculated with Equation (5):

$$V_{IMON}(mV) = GAIN \times I_{OUT}(A) \times R_{sens}(m\Omega)$$

(5)

Typically, the IMON GAIN is 18.  $R_{sens}$  is the output current sense resistor.

### Soft-Start Time Programmable (SS)

The MPQ4210 has a soft-start pin to program the soft-start time. The SS charge current is typically about  $6\mu$ A. The soft-start time can be estimated with Equation (6):

$$T_{SS}(ms) = C_{SS}(nF) \times V_{REF}(V) \div Iss(\mu A)$$

(6)

Typically, the I<sub>SS</sub> charge current is about  $6\mu$ A, C<sub>SS</sub> = 47nF, and V<sub>REF</sub> = 0.5V. The soft-start time is about 3.9ms.

### **Thermal Protection**

The MPQ4210 integrates one temperature monitor circuit. If the junction temperature is higher than 150°C, the MPQ4210 shuts down. After the temperature drops below 125°C, the IC resumes operation. When OTP is triggered, INT is pulled low if it is not masked.

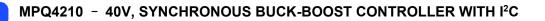

### I<sup>2</sup>C Interface

The MPQ4210 integrates one  $I^2C$  interface. The device address is defined as 1100xxxb, and the final one bit is R/W bit, which is 0 for a write

command and 1 for a read command. It works as a slave and supports standard mode (100kbps) and fast mode (400kbps) communication. Table 1 shows I<sup>2</sup>C slave address selection.

Table 1: I<sup>2</sup>C Slave Address

Figure 7: ADDR Set-Up

See the Register Description section on page 32 for details on  $I^2C$  and register control functions.

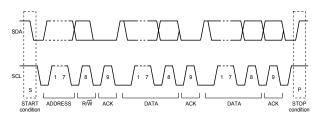

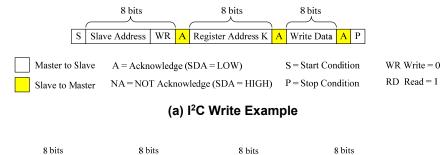

#### I<sup>2</sup>C Transfer Data

Every byte put on the SDA line must be 8 bits long. Each byte must be followed by an acknowledge bit. The acknowledge-related clock pulse is generated by the master. The transmitter releases the SDA line (HIGH) during the acknowledge clock pulse. The receiver must pull down the SDA line during the acknowledge clock pulse so that it remains stable (LOW) during the HIGH period of this clock pulse.

Figure 8 shows the format for data transfers. After the START condition (S), a slave address is sent. This address is 7 bits long, followed by an eighth data direction bit (R/W). A 0 indicates a transmission (WRITE), and a 1 indicates a request for data (READ). A data transfer is always terminated by a STOP condition (P) generated by the master. However, if a master still wishes to communicate on the bus, it can generate a repeated START condition (Sr) and address another slave without first generating a STOP condition.

Figure 8: Complete Data Transfer

The MPQ4210 includes a full  $I^2C$  slave controller. The  $I^2C$  slave fully complies with the  $I^2C$  specification requirements. It requires a start condition, a valid I<sup>2</sup>C address, a register address byte, and a data byte for a single data update.

After receiving each byte, the MPQ4210 acknowledges by pulling the SDA line low during the HIGH period of a single clock pulse. A valid I<sup>2</sup>C address selects the MPQ4210. The MPQ4210 then performs an update on the falling edge of the LSB byte.

Figure 9 shows an example of the  $I^2C$  read and write command.

(b) I<sup>2</sup>C Read Example

Figure 9: I<sup>2</sup>C Read and Write

## **APPLICATION INFORMATION**

### **Output Voltage Setting**

The default output voltage is set using a resistor divider to FB. The default reference voltage ( $V_{REF}$ ) is 0.5V. The bottom resistor in the resistor divider is typically in the 1k $\Omega$  to 50k $\Omega$  range.

The top resistor in the feedback resistor divider is selected using Equation (7):

$$R1 = \frac{V_{OUT} - V_{REF}}{V_{REF}} \times R2 \qquad (7)$$

It is possible to use the I<sup>2</sup>C interface to select the FB  $V_{REF}$  and get another output voltage.

### **Inductor Selection**

The inductor selection is based on the work mode. The inductance for the buck mode is calculated with Equation (8):

$$L_{\text{Buck}} = \frac{V_{\text{OUT}}}{F_{\text{SW}} \times \Delta I_{\text{L}}} \times (1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}})$$

(8)

Where  $\Delta I_{L}$  is the peak-to-peak inductor ripple current, and it is about 30% to 50% of the maximum load current.

In boost mode, the inductor selection is based on limiting  $\Delta I_{L}$  to about 30% to 50% of the maximum input current. The target inductance for boost mode is calculated with Equation (9) and Equation (10):

$$L_{Boost} = \frac{V_{IN} \times (V_{OUT} - V_{IN})}{V_{OUT} \times F_{SW} \times \Delta I_{L}}$$

(9)

$$I_{\text{IN}(\text{max})} = \frac{V_{\text{OUT}} \times I_{\text{LOAD}(\text{max})})}{V_{\text{IN}} \times \eta}$$

(10)

Where  $I_{LOAD(max)}$  is the maximum load current,  $\Delta I_L$  is the peak-to-peak ripple current (about 30% to 50% of the maximum input current), and  $\eta$  is the efficiency.

Choosing a larger inductance reduces the ripple current but also increases the size of the inductor and reduces the achievable bandwidth of the converter by moving the right half-plane zero to lower frequencies. The appropriate balance should be chosen based on the application requirements.

### Input Capacitor Selection

buck mode, the MPQ4210 In has а discontinuous input current (boost mode is continuous), and requires a capacitor to supply the AC current during buck mode while maintaining the DC input voltage. Ceramic capacitors recommended are for best performance, and should be placed as close to VIN as possible. Capacitors with X5R or X7R ceramic dielectrics are recommended because of their stable temperature characteristics. The capacitors must also have a ripple current rating greater than the maximum input ripple current of the converter. The buck mode input ripple current can be estimated with Equation (11):

$$I_{CIN_{RMS}} = I_{OUT} \times \sqrt{\frac{V_{OUT}}{V_{IN}} \times (1 - \frac{V_{OUT}}{V_{IN}})} \quad (11)$$

The worst-case condition in buck mode occurs at  $V_{IN}$  =  $2V_{OUT}$ , calculated with Equation (12):

$$I_{CIN_{RMS}} = \frac{I_{OUT}}{2}$$

(12)

For simplification, choose an input capacitor with an RMS current rating greater than half of the maximum load current.

The input capacitance value determines the input voltage ripple of the converter. If there is an input voltage ripple requirement in the system, choose an input capacitor that meets the specification.

In buck mode, the input voltage ripple can be estimated with Equation (13):

$$\Delta V_{IN} = \frac{I_{OUT}}{F_{SW} \times C_{IN}} \times \frac{V_{OUT}}{V_{IN}} \times (1 - \frac{V_{OUT}}{V_{IN}})$$

(13)

The worst-case condition occurs at  $V_{IN} = 2V_{OUT}$ , calculated with Equation (14):

$$\Delta V_{\rm IN} = \frac{1}{4} \frac{I_{\rm OUT}}{F_{\rm SW} \times C_{\rm IN}}$$

(14)

### **Output Capacitor Selection**

In boost mode, the output current is discontinuous, so  $C_{OUT}$  must be capable of reducing the output voltage ripple.

A higher capacitance value may be required to lower the output ripple and the transient response. Low-ESR capacitors, such as X5R or X7R ceramic capacitors, are recommended. If using ceramic capacitors, the capacitance dominates the impedance at the switching frequency, so the output voltage ripple is independent of the ESR. The output voltage ripple is estimated with Equation (15):

$$\Delta V_{OUT} = \frac{(1 - \frac{V_{IN}}{V_{OUT}}) \times I_{LOAD}}{C_{OUT} \times F_{SW}}$$

(15)

Where  $V_{\text{RIPPLE}}$  is the output ripple voltage, and  $C_{\text{OUT}}$  is the capacitance of the output capacitor.

If using hybrid, polymer, or low-ESR electrolytic capacitors, the ESR dominates the impedance at the switching frequency, so the output ripple is estimated using Equation (16):

$$\Delta V_{\text{OUT}} = \frac{(1 - \frac{V_{\text{IN}}}{V_{\text{OUT}}}) \times I_{\text{LOAD}}}{C_{\text{OUT}} \times F_{\text{SW}}} + \frac{I_{\text{LOAD}} \times R_{\text{ESR}} \times V_{\text{OUT}}}{V_{\text{IN}}}$$

(16)

Where  $R_{\text{ESR}}$  is the equivalent series resistance of the output capacitors.

For a 100W USB PD application, one  $330\mu$ F electrolytic capacitor and four  $10\mu$ F ceramic capacitors are recommended.

Choose output capacitors to satisfy the output ripple and load transient requirements of the design. Capacitance derating should be taken into consideration when designing high output voltage applications.

### **External MOSFET Selection**

The MPQ4210 requires four external N-channel power MOSFETs. Figure 10 shows two for the top switches (switches A and D) and two for the bottom switches (switches B and C). In buck mode, SWA and SWB switch while SWD remains on. In boost mode, SWC and SWD switch while SWA remains on.

#### Figure 10: Buck-Boost Topology

The critical parameters of selecting a MOSFET are:

1. Maximum drain-to-source voltage, V<sub>DS(MAX)</sub>

The SWA and SWB need to withstand the maximum input voltage and the transient spikes at SW1 during switching. Therefore, it is recommended to select  $V_{\text{DS(MAX)}}$  for SWA and SWB at 1.5 times the input voltage.

The SWC and SWD see output voltage and transient spikes at SW2 during switching. Therefore, it is recommended to select SWC and SWD at  $\geq$ 1.5 times the output voltage.

- 2. Maximum current, I<sub>D(MAX)</sub>

- V<sub>TH</sub>: The driver voltages of the MPQ4210 are supplied by VCC. The gate plateau voltages of the MOSFETs should be smaller than the minimum VCC voltage of the converter, otherwise the MOSFETs may not fully enhance during start-up or overload conditions.

- 4. On resistance, R<sub>DS(ON)</sub>

- 5. Total gate charge,  $Q_G$

For the MPQ4210, all switches  $Q_G$  should be smaller than 50nC (at 7.2V GATE condition). If there are two MOSFETs in parallel, each MOSFET  $Q_G$  need be smaller than 25nC.

#### **MOSFET SWA**

When the MPQ4210 works in boost mode, SWA is on consistently. Its conduction power loss can be calculated with Equation (17):

$$P_{C_Loss(SWA)} = (I_o \times \frac{V_{OUT}}{V_{IN}})^2 \times R_{DSON(SWA)}$$

(17)

Assume that the MOSFET junction-to-ambient thermal resistance is 50°C/W (this is determined by the board power dissipation), and that the maximum acceptant temperature rise is 50°C, thus, the maximum power loss is 1W, shown with Equation (18):

$$P_{C\_Loss(SWA)} < 1W$$

(18)

Based on this equation, we can select the MOSFET  $\ensuremath{\mathsf{R}_{\text{ON}}}\xspace$

When the MPQ4210 works in buck mode, the conduction and switching loss of SWA can be calculated with Equation (19) and Equation (20), respectively:

$$P_{C\_Loss(SWA)} = \frac{V_{OUT}}{V_{IN}} \times I_o^2 \times R_{DSON(SWA)}$$

(19)

$$P_{\text{SW}_{\text{Loss}(\text{SWA})}} = \frac{1}{2} V_{\text{IN}} \times I_{\text{OUT}} \times (t_{\text{on}} + t_{\text{off}}) \times F_{\text{sw}}$$

(20)

The switch on time  $(t_{on})$  and the switch off time  $(t_{off})$  are based on the MOSFET datasheet information (see Figure 11).

Figure 11: Switch On Time and Switch Off Time

### **MOSFET SWB**

When MPQ4210 work in buck mode, its conduction loss can be calculated with Equation (21):

$$P_{C_{Loss(SWB)}} = (1 - \frac{V_{OUT}}{V_{IN}}) \times I_o^2 \times R_{DSON(SWB)}$$

(21)

### **MOSFET SWC**

When the MPQ4210 works in boost mode, SWB is always off. Its conduction loss in boost mode can be calculated with Equation (22):

$$P_{C_{Loss(SWC)}} = (1 - \frac{V_{IN}}{V_{OUT}}) \times (I_o \times \frac{V_{OUT}}{V_{IN}})^2 \times R_{DSON(SWC)}$$

(22)

When the MPQ4210 works in boost mode, the SWC switching loss can be calculated with Equation (23):

$$P_{SW\_Loss(SWC)} = \frac{1}{2} \times V_{OUT} \times (I_{OUT} \times \frac{V_{OUT}}{V_{IN}}) \times (t_{on} + t_{off}) \times F_{sw}$$

(23)

### MOSFET SWD

When the MPQ4210 works in buck mode, SWD is on consistently. Its power loss can be calculated with Equation (24):

$$P_{C\_Loss(SWD)} = I_o^2 \times R_{DSON(SWD)}$$

(24)

When the MPQ4210 works in boost mode, the SWD conduction loss can be calculated with Equation (25):

$$P_{C_Loss(SWD)} = (\frac{V_{IN}}{V_{OUT}}) \times (I_o \times \frac{V_{OUT}}{V_{IN}})^2 \times R_{DSON(SWD)}$$

(25)

Dead time and the low-side MOSFET switching loss can be ignored.

### **Compensation Components**

The COMP pin controls system stability and transient response. COMP is the output of the internal error amplifier. A series capacitor-resistor combination sets a pole-zero combination to control the control system's characteristics.

### Figure 12: COMP External Compensation

The COMP external compensation sets one pole  $F_{P1}$  and one zero  $F_{Z1}$  (see Figure 12). These are determined by Equation (26) and Equation (27):

$$F_{P1} = \frac{1}{2\pi \times C11 \times R13}$$

(26)

$$F_{z_1} = \frac{1}{2\pi \times C10 \times R13}$$

(27)

When the MPQ4210 works in buck mode, the DC gain of the voltage feedback loop is calculated with Equation (28):

$$A_{VDC} = R_{LOAD} \times \frac{G_{CS}}{R_{SENSE}} \times A_{V-EA} \times \frac{V_{FB}}{V_{OUT}}$$

(28)

Where  $A_{V-EA}$  is the error-amplifier voltage gain (300V/V),  $G_{CS}$  is the COMP to current sense gain,  $R_{SENSE}$  is the current sense resistor, and  $R_{LOAD}$  is the load resistor value.

The system has two important poles: one is from the compensation capacitor (C10) and the output resistor of the error amplifier, and the other one is from the output capacitor and the load resistor. These poles can be calculated with Equation (29) and Equation (30), respectively:

$$F_{P_2} = \frac{G_{EA}}{2\pi \times C10 \times A_{V-EA}}$$

(29)

$$F_{P3} = \frac{1}{2\pi \times C_{OUT} \times R_{LOAD}}$$

(30)

Where  $G_{\text{EA}}$  is the error-amplifier transconductance (1220 $\mu\text{A/V}),$  and  $C_{\text{OUT}}$  is the output capacitor.

The system may have another significant zero if the output capacitor has a large capacitance or a high ESR value. This zero can be located with Equation (31):

$$F_{ESR} = \frac{1}{2\pi \times C_{OUT} \times R_{ESR}}$$

(31)

When the MPQ4210 works in boost mode, the DC gain of the voltage feedback loop is calculated with Equation (32):

$$A_{VDC} = \frac{V_{IN} \times A_{V-EA} \times R_{LOAD} \times V_{FB} \times G_{CS} \times R13}{2 \times V_{OUT}^2 \times R_{SENSE}}$$

(32)

There is also a right-half-plane zero ( $F_{RHPZ}$ ) that exists in boost mode. The frequency of the right half-plane zero is determined with Equation (33):

$$F_{RHPZ} = \frac{R_{LOAD}}{2 \times \pi \times L} \times (\frac{V_{IN}}{V_{OUT}})^2$$

(33)

The right half-plane zero increases the gain and reduces the phase simultaneously, which results in a smaller phase and gain margin. The worstcase condition occurs when the input voltage is at its minimum and the output power is at its maximum.

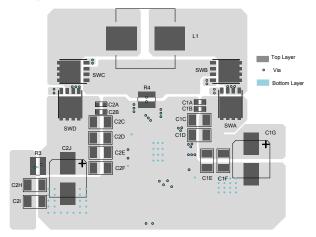

### **PCB Layout Guidelines**

Efficient layout is a critical step in designing a buck-boost controller. Improper layout may result in reduced performance, EMI problems, resistive loss, and even system instability. For best results, refer to Figure 13 and follow the steps below:

- 1. In buck mode, place the input power loop including the input filter capacitor ( $C_{IN}$ ), the power MOSFETs (SWA and SWB), and the cycle-by-cycle current sense resistor (R4) as close as possible.

- 3. Use wide copper traces and power loop vias to help thermal dissipation.

- 4. Connect the exposed pad to GND, and place vias on the exposed pad for IC thermal dissipation.

- 5. Place small decoupling capacitors close to VIN, VOUT, and AGND.

- 6. Lay out the gate drive traces and return paths as directly as possible. Lay out the forward and return traces close together, either running side by side or on top of each other on adjacent layers, to minimize the inductance of the gate drive path.

- Use Kelvin connections to R3 (for the average current sense) and R4 (for the cycleby-cycle current), and run lines in parallel from the R3/R4 terminals to the IC pins. Avoid crossing noisy areas such as SW1 and SW2 or gate drive traces.

- 8. Place the filter capacitor for the current sense signal as close to the IC pins as possible.

- 9. Place the VCC and AVDD capacitors as close as possible to the VCC and AVDD pins.

- 10. Place the BST1 bootstrap capacitor close to the IC, and connect directly to the BST1 and SW1 pins.

- 11. Place the BST2 bootstrap capacitor close to the IC, and connect directly to the BST2 and SW2 pins.

- 12. The feedback loop should be far away from any noise source. Place the FB dividers (R1 and R2) as close as possible to the FB and AGND pins.

- 13. Separate the power and signal paths so that no power or switching current flows through the AGND connections. Connect the PGND and AGND traces near the PGND pin, near the VCC capacitor PGND connection, or near the PGND connection of the cycle by cycle current sense resistor (R4).

**Top Layer**

Bottom Layer Figure 13: Recommended PCB Layout

# **TYPICAL APPLICATION CIRCUITS**

Figure 14: VIN = 12V, VOUT = 5V/9V/15V/20V for 100W USB PD

# **REGISER DESCRIPTION**

### **Register Map**

| Address | Register            | Туре | D7  | D6     | D5     | D4     | D3        | D2            | D1     | D0           | Reset<br>State |

|---------|---------------------|------|-----|--------|--------|--------|-----------|---------------|--------|--------------|----------------|

| 0x00    | REF_LS<br>B         | R/W  | -   | -      | -      | -      | -         | ,             | VREF_L |              | 0000<br>0100   |

| 0x01    | REF_MS<br>B         | R/W  |     | VREF_H |        |        |           |               |        | 0011<br>1110 |                |

| 0x02    | Control 1           | R/W  | SR  |        | DISCHG | Dither | PNG_Latch | Reserved (9)  | GO_BIT | ENPWR        | 0100<br>0000   |

| 0x03    | Control 2           | R/W  | FSV | V      | -      | BB_FSW | OCP_      | MODE OVP_MODE |        | 1000<br>0101 |                |

| 0x04    | ILIM                | R/W  | -   | -      | -      | -      | Reserved  | ILIM          |        | 0000<br>1001 |                |

| 0x05    | Interrupt<br>status | R/W  | -   | -      | -      | OTP    | -         | OVP           | OCP    | PNG          | 0000<br>0000   |

| 0x06    | Interrupt<br>mask   | R/W  | -   | -      | -      | M_OTP  | -         | M_OVP         | M_OCP  | M_PNG        | 0000<br>0001   |

Note:

9) This bit must be written to 1 before start-up.

### Register Name: REF\_LSB, 0x00, Read/Write

| Name   | Bits   | Default<br>Value | Description                                      |  |

|--------|--------|------------------|--------------------------------------------------|--|

| VREF_L | D[2:0] | 100              | Feedback V <sub>REF</sub> low 3 bits. LSB = 1mV. |  |

### Register Name: REF\_MSB, 0x01, Read/Write

| Name   | Bits   | Default<br>Value | Description                                       |

|--------|--------|------------------|---------------------------------------------------|

| VREF_H | D[7:0] | 0011<br>1110     | Feedback V <sub>REF</sub> high 8 bits. LSB = 8mV. |

See below for FB reference data format.

| Name                                   |    | VREF |    |     |               |               |     |     |     |     |              |     |               |     |   |   |

|----------------------------------------|----|------|----|-----|---------------|---------------|-----|-----|-----|-----|--------------|-----|---------------|-----|---|---|

| Format Direct, unsigned binary integer |    |      |    |     |               |               |     |     |     |     |              |     |               |     |   |   |

| Register Name                          |    | N/A  |    |     |               | VREF_H D[7:0] |     |     |     |     |              |     | VREF_L D[2:0] |     |   |   |

| Bit                                    | 15 | 14   | 13 | 12  | 11            | 10            | 9   | 8   | 7   | 6   | 5            | 4   | 3             | 2   | 1 | 0 |

| Access                                 |    | N/A  |    | r/w | r/w           | r/w           | r/w | r/w | r/w | r/w | r/w          | r/w | r/w           | r/w |   |   |

| Function                               |    | N/A  |    |     | Data bit high |               |     |     |     |     | Data bit low |     |               |     |   |   |

| Default Value<br>(0.5V)                |    | N/A  |    |     |               | 500 integer   |     |     |     |     |              |     |               |     |   |   |

Total 11 bits to set reference voltage. If V is an 11-bit, unsigned binary integer of VREF [10:0], then:  $V_{FB}$  (V) = V/1000.

| Name      | Bits   | Default<br>Value | Description                                                                                                                                                                                                                                                                         | Description                                                                                                                                                            |  |  |  |  |

|-----------|--------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|           |        |                  |                                                                                                                                                                                                                                                                                     | g slew rate. This SR control only works after S period, the $V_{\text{OUT}}$ slew rate is controlled by                                                                |  |  |  |  |

|           |        |                  | $V_{OUT}$ slew rate = $V_{REF}$ slew rate × feedback ratio of (R1 + R2) / R2.                                                                                                                                                                                                       |                                                                                                                                                                        |  |  |  |  |

|           |        |                  | SR Bits Value                                                                                                                                                                                                                                                                       | V <sub>REF</sub> Slew Rate                                                                                                                                             |  |  |  |  |

| SR        | D[7:6] | 01               | 00                                                                                                                                                                                                                                                                                  | 38mV/ms                                                                                                                                                                |  |  |  |  |

|           |        |                  | 01                                                                                                                                                                                                                                                                                  | 50mV/ms                                                                                                                                                                |  |  |  |  |

|           |        |                  | 10                                                                                                                                                                                                                                                                                  | 75mV/ms                                                                                                                                                                |  |  |  |  |

|           |        |                  | 11                                                                                                                                                                                                                                                                                  | 150mV/ms                                                                                                                                                               |  |  |  |  |

|           |        |                  | bit 1 to always turn on the<br>0 to turn off output dischar<br>ENPWR bit is low.                                                                                                                                                                                                    |                                                                                                                                                                        |  |  |  |  |

| DISCHG    | D[5]   | 0                | <ul> <li>4) Output OVP (When OVP_MODE enables discharge)</li> <li>5) VIN UVLO</li> <li>When GO_BIT is set to 1, V<sub>OUT</sub> discharges will automatically turn on.<br/>After GO_BIT resets to 0 with 20ms extra delay, the V<sub>OUT</sub> discharge path turns off.</li> </ul> |                                                                                                                                                                        |  |  |  |  |

|           |        |                  | VREF change with this inte                                                                                                                                                                                                                                                          | to set the slew rate low so $V_{OUT}$ can follow the rnal discharge current. If $V_{OUT}$ cannot follow the discharge due to a large $C_{OUT}$ capacitor, s discharge. |  |  |  |  |

| Dither    | D[4]   | 0                | Frequency spread sprectru                                                                                                                                                                                                                                                           |                                                                                                                                                                        |  |  |  |  |

|           |        |                  |                                                                                                                                                                                                                                                                                     | s bit is 1, and disabled when this bit is 0.                                                                                                                           |  |  |  |  |

|           |        | 0                | PNG status bit reset control bit. Refer to PNG bit description on page 36.                                                                                                                                                                                                          |                                                                                                                                                                        |  |  |  |  |