**MP7200**

# 42V, 1.2A Buck-Boost or 3A Buck Synchronous LED Driver

## DESCRIPTION

The MP7200 is a high-frequency, constantcurrent, buck-boost LED driver with integrated power MOSFETs. It offers a very compact solution to achieve up to 1.2A of continuous output current, with excellent load and line regulation across a wide input supply range. The MP7200 can also be configured to buck mode to provide up to 3A of constant load current.

Constant frequency hysteretic control mode provides extremely fast transient response without loop compensation. The switching frequency goes up to a fixed 2.3MHz in buck mode to reduce the current ripple and improve EMI, and down to 1.15MHz in buck-boost mode to optimize efficiency and thermal performance.

Full protection features include over-current protection (OCP), output over-voltage (OV) and under-voltage (UV), thermal derating (TD), and thermal shutdown (TSD). The fault indicator outputs an active logic low signal if a fault condition occurs.

The MP7200 requires a minimal number of readily available, standard external components, and is available in a space-saving QFN-19 (3mmx4mm) package.

## **FEATURES**

- Wide 6V to 42V Operating Input Range

- $44m\Omega/40m\Omega$  Low  $R_{DS(ON)}$  Internal Power MOSFETs

- High-Efficiency Synchronous Mode

Operation

- Configurable 1.2A Buck-Boost or 3A Buck Mode

- Configurable LED Current without Current-Sense Resistor

- Default 2.3MHz Switching Frequency for Buck Mode and 1.15MHz Switching Frequency for Buck-Boost Mode with Spread Spectrum

- PWM Dimming (Dimming Frequency from 100Hz to 2kHz)

- Internal 500Hz Two-Step Dimming with Configurable Duty Cycle

- Fault Indication for LED Short (to GND and Battery) and Open, Output Over-Voltage, and Thermal Shutdown

- Over-Current Protection (OCP) with Latch-Off Mode

- Configurable Thermal Derating via NTC Remote Temperature Sense

- EMI Reduction Technique

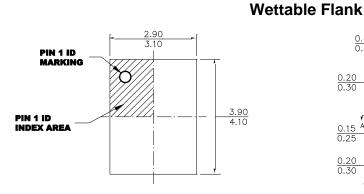

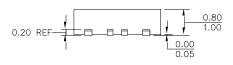

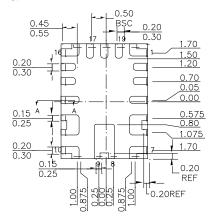

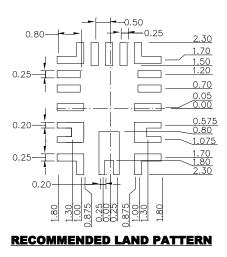

- Available in a QFN-19 (3mmx4mm) Package with Wettable Flanks

## APPLICATIONS

- Turn Indicator Lights

- Daytime Running Lights (DRLs)

- Fog Lights

- Rear Lights

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

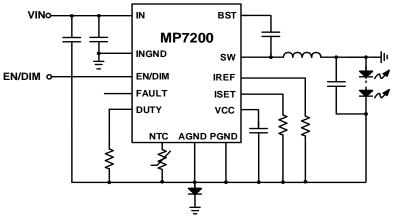

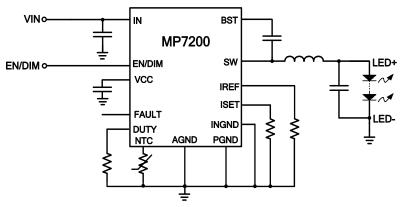

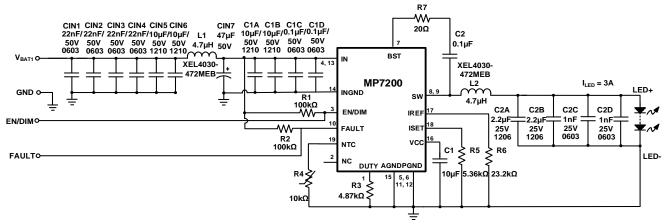

# **TYPICAL APPLICATIONS**

Figure 1: Buck-Boost Topology (≤9.09kΩ RIREF)

Figure 2: Buck Topology (≥14.7kΩ RIREF)

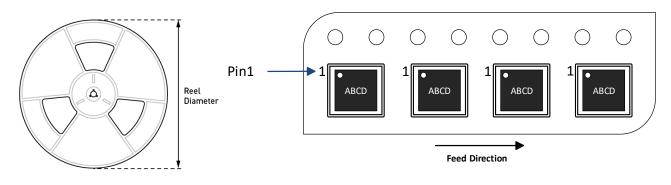

## **ORDERING INFORMATION**

| Part Number* | Package          | Top Marking | MSL Rating** |

|--------------|------------------|-------------|--------------|

| MP7200GLE*** | QFN-19 (3mmx4mm) | See Below   | 1            |

\* For Tape & Reel, add suffix -Z (e.g. MP7200GLE-Z).

\*\* Moisture Sensitivity Level Rating.

\*\*\* Wettable Flank.

## **TOP MARKING**

## MPYW 7200 LLL E

MP: MPS prefix Y: Year code W: Week code 7200: First four digits of the part number LLL: Lot number E: Wettable flank

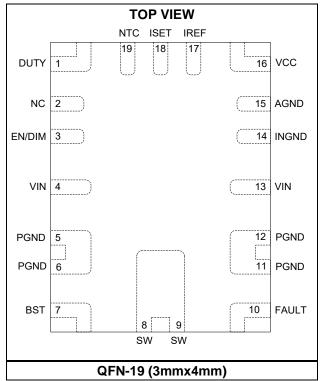

## PACKAGE REFERENCE

MP7200 Rev. 1.0 1/21/2021

## **PIN FUNCTIONS**

| Pin #           | Name   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1               | DUTY   | <b>Two-step dimming duty setting.</b> Connect a resistor ( $R_{DUTY}$ ) between DUTY and AGND to disable two-step dimming or set the two-step dimming duty cycle. The two-step dimming duty cycle can be set between 5% and 15%, with 1% a step. For more details on the relationship between duty cycle and $R_{DUTY}$ , see the Two-Step Dimming section on page 43. If the DUTY pin is shorted to ground or an open fault is detected before start-up, the part latches off and FAULT is asserted.                                                        |

| 2               | NC     | Not connection. Leave this pin floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3               | EN/DIM | <b>Enable/dimming control.</b> Pull EN high to enable the chip. The part starts to sense the pin's configuration at the first positive edge. Once the configuration is completed, apply a 100Hz to 2kHz external clock to the EN/DIM pin for PWM dimming ( $R_{DUTY} = 4.87 K\Omega$ ). EN/DIM can be connected to VIN through a maximum 100k $\Omega$ resistor. In two-step dimming mode, EN is off and the PWM dimming function is deactivated. Pull this pin high for 100% dimming duty, and pull this pin low to set the dimming duty via $R_{DUTY}$ .   |

| 4, 13           | VIN    | <b>Supply voltage.</b> The MP7200 operates from a 6V to 42V input rail. VIN requires an input capacitor ( $C_{IN}$ ) to decouple the input rail. Connect VIN to the input rail using a wide PCB trace.                                                                                                                                                                                                                                                                                                                                                       |

| 5, 6, 11,<br>12 | PGND   | <b>Power ground.</b> PGND is the power device reference ground, including the configuration pins (e.g. NTC), so it requires additional considerations while designing the PCB layout. PGND is also used to dissipate the thermal heat.                                                                                                                                                                                                                                                                                                                       |

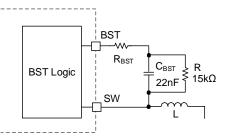

| 7               | BST    | <b>Bootstrap.</b> Place a capacitor between the SW and BST pins to form a floating supply across the high-side MOSFET driver. Place an optional resistor between the SW and BST capacitors to reduce SW voltage spikes and improve EMI performance.                                                                                                                                                                                                                                                                                                          |

| 8,9             | SW     | <b>Switch output.</b> SW is the middle point between the high-side and low-side MOSFETs. When designing the PCB layout, it is recommended to make the SW node as small as possible with a wide trace. This reduces noise coupling and improves EMI.                                                                                                                                                                                                                                                                                                          |

| 10              | FAULT  | <b>Fault indicator.</b> FAULT is an open-drain output with an internal $300k\Omega$ pull-up resistor connected to VIN, and a $4M\Omega$ pull-down resistor connected to INGND. FAULT is pulled low if any of the following occurs: LED short or open, over-temperature protection (OTP), false mode detection, or over-current protection (OCP). FAULT can be continuously connected to VIN with a pull-up resistor.                                                                                                                                         |

| 14              | INGND  | VIN, EN/DIM, and FAULT ground for buck-boost topology. For a buck topology, connect INGND to PGND and AGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 15              | AGND   | <b>Analog ground.</b> Reference ground of the logic circuit. Connect AGND to PGND using an external trace.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 16              | VCC    | <b>Internal bias supply.</b> VCC supplies power to the internal control circuit and gate drivers.<br>Connect a $\geq 3\mu$ F decoupling capacitor to VCC and ground. A 10 $\mu$ F/10V or 16V, X7R capacitor is strongly recommend due to capacitance derating.                                                                                                                                                                                                                                                                                               |

| 17              | IREF   | <b>Mode selection and NTC reference current setting.</b> Connect a $\leq 9.09k\Omega$ resistor at IREF to select buck-boost mode, or a $\geq 14.7k\Omega$ resistor to select buck mode. The voltage of IREF is 0.57V. Connect a resistor (R <sub>IREF</sub> ) from IREF to GND to get a reference current (0.57V / R <sub>IREF</sub> ). If the IREF pin is shorted to ground or an open fault is detected, the part is latched off and asserts FAULT. The NTC pin current is 50 (buck mode) or 5 (buck-boost mode) times that of the IREF reference current. |

| 18              | ISET   | <b>LED current setting.</b> Connect an external resistor from ISET to ground to set the LED average current. If the ISET pin is shorted to ground or an open fault is detected, the part is latched off and asserts FAULT.                                                                                                                                                                                                                                                                                                                                   |

| 19              | NTC    | <b>Remote temperature sense.</b> Connect NTC to a resistor network to configure the temperature derating starting point. There are protections if NTC is shorted to PGND, AGND, INGND, or the battery.                                                                                                                                                                                                                                                                                                                                                       |

## ABSOLUTE MAXIMUM RATINGS (1)

| $ \begin{array}{l} V_{IN} - V_{PGND/AGND} & -0.3V \ to \ +50V \\ V_{IN} - V_{INGND} & -0.3V \ to \ +50V \\ V_{INGND} - V_{PGND/AGND} & -0.3V \ to \ +50V \\ V_{FAULT} - V_{INGND} & -0.3V \ to \ +50V \\ V_{EN/DIM} - V_{INGND} & -0.3V \ to \ +5.5V \\ V_{SW} - V_{PGND/AGND} \ -0.3V \ to \ V_{IN} - V_{PGND/AGND} \ + 0.3V \\ V_{BST} & V_{SW} \ + \ 5.5V \\ V_{NTC} - V_{PGND/AGND} & -0.3V \ to \ +5.5V \\ All \ other \ pins \ - V_{PGND/AGND} & -0.3V \ to \ +5.5V \\ Continuous \ power \ dissipation \ (T_A = 25^{\circ}C) \ ^{(2)} \ ^{(4)} \\ QFN-19 \ (3mmx4mm) \ \ 3.9W \\ \end{array} $ |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

## ESD Ratings

| Human body model (HBM)     | ±2kV  |

|----------------------------|-------|

| Charged device model (CDM) | ±750V |

## **Recommended Operating Conditions**

| Supply voltage (V <sub>IN</sub> - V <sub>PGND</sub> ) |             |

|-------------------------------------------------------|-------------|

| LED current (I <sub>LED</sub> ) in buck-boost mode    | e           |

|                                                       | .Up to 1.2A |

| LED current (I <sub>LED</sub> ) in buck mode          |             |

| Operating junction temp (T <sub>J</sub> )40°C         | to +125°C   |

### **Thermal Resistance** $\theta_{JA}$ $\theta_{JC}$

QFN-19 (3mmx4mm)

| JESD51-7 <sup>(3)</sup> | <br>11 | °C/W |

|-------------------------|--------|------|

| EVQ7200-L-00A (4).      | <br>6  | °C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature, T<sub>J</sub> (MAX), the junction-toambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature, T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX) - T<sub>A</sub>) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation can cause excessive die temperature, and the regulator may go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) Measured on JESD51-7, 4-layer PCB. The value of  $\theta_{JA}$  given in this table is only valid for comparison with other packages and cannot be used for design purposes. These values were calculated in accordance with JESD51-7 and simulated on a specified JEDEC board. They do not represent the performance obtained in an actual application.

- 4) Measured on MPS standard EVB of MP7200, 2oz, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 13.5V,  $V_{EN}$  = 2V,  $T_J$  = -40°C to +125°C  $^{(5)}$ , typical values are at  $T_J$  = 25°C, buck mode, unless otherwise noted.

| Parameter                                         | Symbol                | Condition                                                                                             | Min   | Тур           | Max   | Units    |

|---------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------|-------|---------------|-------|----------|

| Shutdown supply current                           | lin                   | $V_{EN} = 0V$                                                                                         |       | 30            | 80    | μA       |

| Quiescent supply current                          | lq                    | $V_{EN} = 2V$ , no switching, I <sub>REF</sub> floating<br>(exclude I <sub>REF</sub> and NTC current) |       | 1.2           | 2     | mA       |

|                                                   |                       | FAULT latch                                                                                           |       |               | 2     | mA       |

| HS-FET on resistance                              | HS <sub>RDS(ON)</sub> | $V_{BST-SW} = 5V, R_{ISET} = 13.3k\Omega$                                                             |       | 44            | 75    | mΩ       |

| HO-FET ON TESISIANCE                              | HORDS(ON)             | $V_{BST-SW} = 5V, R_{ISET} = 40.2k\Omega$                                                             |       | 85            | 150   | mΩ       |

| LS-FET on resistance                              | 18                    | $V_{CC}$ = 5.2V, $R_{ISET}$ = 13.3k $\Omega$                                                          |       | 40            | 70    | mΩ       |

| LO-FET ON TESISTATICE                             | LS <sub>RDS(ON)</sub> | $V_{CC} = 5.2V, R_{ISET} = 40.2k\Omega$                                                               |       | 80            | 140   | mΩ       |

| Quitab lookogo                                    | 014/                  | $V_{EN} = 0V, V_{SW} = 13.5V, T_J = 25^{\circ}C$                                                      |       |               | 1     | μA       |

| Switch leakage                                    | SWlkg                 | $V_{EN} = 0V, V_{SW} = 13.5V$                                                                         |       |               | 5     | μA       |

| Peak current limit (6)                            | L                     | $R_{ISET} = 40.2k\Omega$                                                                              | 2.65  | 3.15          | 3.65  | Α        |

|                                                   | ILIMIT_PEAK           | R <sub>ISET</sub> = 13.3kΩ                                                                            | 5.3   | 6.3           | 7.3   | А        |

| Zero-current detection (6)                        |                       |                                                                                                       |       | 50            |       | mA       |

| Oscillator frequency                              | f <sub>SW</sub>       |                                                                                                       | 2000  | 2300          | 2600  | kHz      |

| Minimum on time (6)                               | ton_min               |                                                                                                       |       | 55            | 80    | ns       |

| Minimum off time (6)                              | toff_min              |                                                                                                       |       | 75            | 100   | ns       |

| Maximum duty cycle (6)                            | DMAX                  | Low dropout                                                                                           | 95    | 98            |       | %        |

| Frequency spread spectrum <sup>(6)</sup>          |                       |                                                                                                       |       | 15            |       | kHz      |

| Frequency spread<br>spectrum range <sup>(6)</sup> |                       |                                                                                                       |       | ±10%<br>x fsw |       | kHz      |

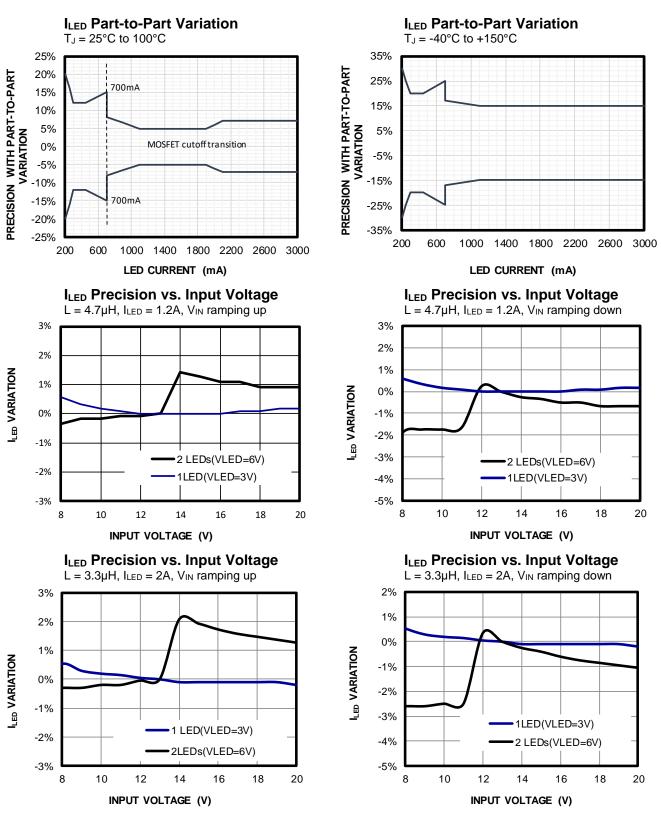

|                                                   |                       | R <sub>ISET</sub> = 13.3kΩ, T <sub>J</sub> = 25°C to 100°C                                            | -5%   | 1.2           | +5%   | <b>_</b> |

| LED current                                       | ILED                  | R <sub>ISET</sub> = 13.3kΩ                                                                            | -15%  |               | +15%  | A        |

| LED current threshold for<br>MOSFET cutoff        | I <sub>LED_CUT</sub>  |                                                                                                       |       | 600           | 700   | mA       |

| ISET voltage                                      | VISET                 | Іізет = 45µА                                                                                          | 0.578 | 0.592         | 0.606 | V        |

| ISET current threshold for                        |                       | ILED < ILED_CUT                                                                                       | 80    | 120           | 160   | μA       |

| pin short                                         |                       | ILED > ILED_CUT                                                                                       | 180   | 220           | 260   | μA       |

| ISET current threshold for pin open               |                       |                                                                                                       | 0.5   | 1.4           | 5     | μA       |

| EN rising threshold                               | VEN_RISING            | Ven - Vingnd                                                                                          | 1.2   | 1.67          | 2.5   | V        |

| EN falling threshold                              | VEN_FALLING           | Ven - Vingnd                                                                                          | 1     | 1.58          | 2.2   | V        |

| EN threshold hysteresis                           | V <sub>EN_HYS</sub>   | Ven - Vingnd                                                                                          |       | 100           |       | mV       |

|                                                   |                       | Ven - Vingnd = 2V                                                                                     |       | 2             | 8     | μA       |

| EN input current                                  | IEN                   | Ven - Vingnd = 0V                                                                                     |       | 0             | 0.2   | μA       |

$V_{IN}$  = 13.5V,  $V_{EN}$  = 2V,  $T_J$  = -40°C to +125°C  $^{\rm (5)}$ , typical values are at  $T_J$  = 25°C, buck mode, unless otherwise noted.

| Parameter                                                   | Symbol                                | Condition                               | Min   | Тур   | Max   | Units |

|-------------------------------------------------------------|---------------------------------------|-----------------------------------------|-------|-------|-------|-------|

| EN turn-off delay                                           | ten-td-off                            |                                         | 10    | 25    | 45    | ms    |

| VIN under-voltage lockout<br>(UVLO) rising threshold        | $\text{INUV}_{\text{VTH}_{\text{R}}}$ | Vin - Vingnd                            | 5.75  | 6     | 6.25  | V     |

| VIN UVLO falling threshold                                  | $\text{INUV}_{\text{VTH}_{\text{F}}}$ | Vin - Vingnd                            | 4.5   | 4.9   | 5.2   | V     |

| VIN UVLO threshold<br>hysteresis                            | INUVHYS                               | Vin - Vingnd                            |       | 1.1   |       | V     |

| VCC UVLO rising threshold                                   | Vcc_vth                               | Vcc - Vagnd                             | 4.4   | 4.7   | 5     | V     |

| VCC UVLO falling threshold                                  |                                       | V <sub>CC</sub> - V <sub>AGND</sub>     | 3.4   | 4.05  | 4.7   | V     |

| VCC UVLO threshold<br>hysteresis                            | V <sub>CC_HYS</sub>                   | V <sub>CC</sub> - V <sub>AGND</sub>     |       | 650   |       | mV    |

| VCC regulator                                               | Vcc                                   | Icc = 0mA                               | 4.9   | 5.1   | 5.3   | V     |

| VCC load regulation                                         |                                       | Icc = 20mA                              | 4.7   |       |       | V     |

| VCC maximum current ability                                 |                                       | Vcc = Vcc_uvLo + 100mV,<br>no switching | 50    | 80    | 120   | mA    |

| VCC source current ability <sup>(6)</sup>                   |                                       | Vcc = Vcc_uvlo + 100mV, switching       |       | 25    |       | mA    |

|                                                             |                                       | IDUTY1                                  | 40    | 45    | 50    | μA    |

| DUTY source current                                         | Iduty                                 | IDUTY2                                  | 550   | 600   | 650   | μA    |

| VDUTY threshold maximum                                     |                                       | IDUTY1 and IDUTY2                       | 3.287 | 3.355 | 3.422 | V     |

| VDUTY threshold minimum (6)                                 |                                       | IDUTY1 and IDUTY2                       | 0.28  | 0.302 | 0.33  | V     |

| Two-step dimming frequency                                  |                                       |                                         |       | 500   |       | Hz    |

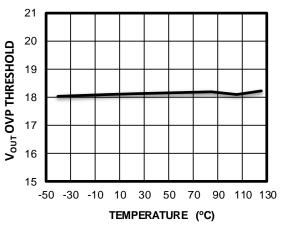

| Output over-voltage (OV) threshold                          | OVvth                                 |                                         | 16.5  | 18    | 19    | V     |

| Output under-voltage (UV) threshold                         | UV <sub>VTH</sub>                     |                                         | 0.6   | 1.1   | 1.7   | V     |

| LED low-current threshold                                   |                                       | ILED_SETTING < ILED_CUT                 | 45    | 60    | 75    | mA    |

|                                                             |                                       | ILED_SETTING > ILED_CUT                 | 100   | 120   | 150   | mA    |

| FAULT assertion delay time during start-up                  | t <sub>ft-d_start</sub>               |                                         | 25    | 35    | 40    | ms    |

| FAULT assertion deglitch time after start-up <sup>(6)</sup> | tft-d                                 |                                         |       | 20    |       | μs    |

| FAULT assertion low sink                                    |                                       | Vfault = 12V                            | 10    | 30    | 50    | mA    |

| current ability                                             | FAULT_SINK                            | VFAULT = 0.2V                           | 5     | 12    |       | mA    |

| FAULT pull-up resistor                                      |                                       |                                         | 100   | 300   | 500   | kΩ    |

| FAULT pull-down resistor                                    |                                       |                                         | 2000  | 4000  | 6000  | kΩ    |

| IREF current for mode detection                             |                                       |                                         | 200   | 240   | 280   | μA    |

$V_{IN}$  = 13.5V,  $V_{EN}$  = 2V,  $T_J$  = -40°C to +125°C  $^{(5)}$ , typical values are at  $T_J$  = 25°C, buck mode, unless otherwise noted.

| Parameter                                                | Symbol | Condition                               | Min   | Тур  | Max   | Units |

|----------------------------------------------------------|--------|-----------------------------------------|-------|------|-------|-------|

| VIREF threshold for mode detection                       |        |                                         | 2.6   | 2.7  | 2.8   | V     |

| IREF voltage                                             | VIREF  | I <sub>REF</sub> = 20µA                 | 0.50  | 0.57 | 0.63  | V     |

| IREF current threshold for pin<br>short detection        |        |                                         | 60    | 90   | 120   | μA    |

| IREF current threshold for pin open detection            |        |                                         |       | 3    | 6     | μA    |

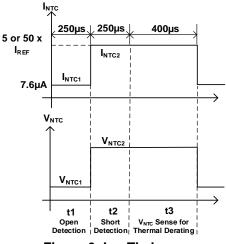

| NTC source current                                       | INTC1  |                                         | 4.5   | 7.6  | 10    | μA    |

|                                                          | INTC2  | $V_{NTC} = 1.25V$ , $I_{REF} = 20\mu A$ | 980   | 1020 | 1060  | μA    |

| NTC voltage for current                                  |        | ILED = 98% of the nominal voltage       | -2.5% | 1.25 | +2,5% | V     |

| derating                                                 |        | ILED = 58% of the nominal voltage       | -2.5% | 0.65 | +2.5% | V     |

| VNTC OV threshold                                        |        | VNTC1                                   | 1.8   | 2    | 2.2   | V     |

| VNTC threshold for over-<br>temperature protection (OTP) |        | V <sub>NTC2</sub>                       | 0.2   | 0.38 | 0.48  | V     |

| VNTC deglitch time for OTP                               |        | $V_{NTC} = 0.3V$                        | 180   | 256  | 320   | μs    |

| VNTC UV threshold                                        |        | V <sub>NTC2</sub>                       | 0.14  | 0.18 | 0.22  | V     |

| Thermal shutdown (6)                                     |        |                                         | 155   | 170  | 185   | °C    |

$V_{IN}$  = 13.5V,  $V_{EN}$  = 2V,  $T_J$  = -40°C to +125°C  $^{\rm (5)}$ , typical values are at  $T_J$  = 25°C, buck-boost mode, unless otherwise noted.

| Parameter                                      | Symbol                 | Condition                                                                                                | Min   | Тур           | Max   | Units |

|------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------|-------|---------------|-------|-------|

| Shutdown supply current                        | lin                    | $V_{EN} = 0V$                                                                                            |       | 30            | 80    | μA    |

| Quiescent supply current                       | lα                     | V <sub>EN</sub> = 2V, no switching, I <sub>REF</sub> float<br>(exclude I <sub>REF</sub> and NTC current) |       | 1.2           | 2     | mA    |

|                                                |                        | FAULT latch                                                                                              |       |               | 2     | mA    |

| HS-FET on resistance                           | HS <sub>RDS(ON)</sub>  | $V_{BST-SW} = 5V, R_{ISET} = 13.3k\Omega$                                                                |       | 44            | 75    | mΩ    |

| LS-FET on resistance                           | LSRDS(ON)              | $V_{CC} = 5.2V, R_{ISET} = 13.3k\Omega$                                                                  |       | 40            | 70    | mΩ    |

| Switch lookage                                 | SWLKG                  | $V_{EN} = 0V, V_{SW} = 13.5V, T_J = 25^{\circ}C$                                                         |       |               | 1     | μA    |

| Switch leakage                                 | SVVLKG                 | V <sub>EN</sub> = 0V, V <sub>SW</sub> = 13.5V                                                            |       |               | 5     | μA    |

| Peak current limit (6)                         | ILIMIT_PEAK            |                                                                                                          | 5.3   | 6.3           | 7.3   | А     |

| Zero-current detection (ZCD) <sup>(5)</sup>    |                        |                                                                                                          |       | 50            |       | mA    |

| Oscillator frequency                           | f <sub>SW</sub>        |                                                                                                          | 920   | 1150          | 1380  | kHz   |

| Minimum on time (6)                            | t <sub>ON_MIN</sub>    |                                                                                                          |       | 55            | 80    | ns    |

| Minimum off time (6)                           | toff_min               |                                                                                                          |       | 75            | 100   | ns    |

| Maximum duty cycle (6)                         | D <sub>MAX</sub>       | Low dropout                                                                                              | 95    | 98            |       | %     |

| Frequency spread spectrum <sup>(6)</sup>       |                        |                                                                                                          |       | 15            |       | kHz   |

| Frequency spread spectrum range <sup>(6)</sup> |                        |                                                                                                          |       | ±10%<br>x fsw |       | kHz   |

|                                                |                        | $R_{ISET} = 21.5 k\Omega$ , $T_J = 25^{\circ}C$ to $100^{\circ}C$                                        | -7%   | 0.75          | +7%   | ^     |

| LED ourrent                                    |                        | $R_{ISET} = 21.5 k\Omega$                                                                                | -15%  |               | +15%  | A     |

| LED current                                    | LED                    | $R_{ISET} = 13.3 k\Omega$ , $T_J = 25^{\circ}C$ to $100^{\circ}C$                                        | -5%   | 1.2           | +5%   | А     |

|                                                |                        | $R_{ISET} = 13.3 k\Omega$                                                                                | -15%  |               | +15%  |       |

| ISET voltage                                   | VISET                  | I <sub>ISET</sub> = 45μA                                                                                 | 0.578 | 0.592         | 0.606 | V     |

|                                                |                        | $V_{IN} = 6.6V$ , $V_{ISET}$ with respect to the nominal voltage                                         | 91.5  | 95            | 98.5  | %     |

| Power derating ratio                           |                        | $V_{IN} = 5.3V$ , $V_{ISET}$ with respect to the nominal voltage                                         | 72.5  | 76            | 79.5  | %     |

| ISET current threshold for<br>pin short        |                        |                                                                                                          | 90    | 110           | 130   | μA    |

| ISET current threshold for<br>pin open         |                        |                                                                                                          | 0.5   | 1.4           | 5     | μA    |

| EN rising threshold                            | V <sub>EN_RISING</sub> | Ven - Vingnd                                                                                             | 1.2   | 1.67          | 2.5   | V     |

| EN falling threshold                           | VEN_FALLING            | Ven - Vingnd                                                                                             | 1.0   | 1.58          | 2.2   | V     |

| EN threshold hysteresis                        | Ven_hys                | Ven - Vingnd                                                                                             |       | 100           |       | mV    |

$V_{IN}$  = 13.5V,  $V_{EN}$  = 2V,  $T_J$  = -40°C to +125°C  $^{\rm (5)}$ , typical values are at  $T_J$  = 25°C, buck-boost mode, unless otherwise noted.

| Parameter                                       | Symbol                  | Condition                                             | Min   | Тур   | Max   | Units |

|-------------------------------------------------|-------------------------|-------------------------------------------------------|-------|-------|-------|-------|

| EN input ourropt                                | IEN                     | $V_{EN} = 2V$                                         |       | 2     | 8     | μA    |

| EN input current                                |                         | $V_{EN} = 0V$                                         |       | 0     | 0.2   | μA    |

| EN turn-off delay                               | t <sub>EN-TD-OFF</sub>  |                                                       | 10    | 25    | 45    | ms    |

| VIN UVLO rising threshold                       | $INUV_{\text{VTH}_R}$   | Vin - Vingnd                                          | 5.75  | 6     | 6.25  | V     |

| VIN UVLO falling threshold                      | $INUV_{\text{VTH}_F}$   | Vin - Vingnd                                          | 4.5   | 4.9   | 5.2   | V     |

| VIN UVLO threshold<br>hysteresis                | INUV <sub>HYS</sub>     | Vin - Vingnd                                          |       | 1.1   |       | V     |

| VCC UVLO rising threshold                       | $V_{CC_VTH}$            | V <sub>CC</sub> - V <sub>AGND</sub>                   | 4.4   | 4.7   | 5     | V     |

| VCC UVLO falling threshold                      |                         | V <sub>CC</sub> - V <sub>AGND</sub>                   | 3.4   | 4.05  | 4.7   | V     |

| VCC UVLO threshold<br>hysteresis                | V <sub>CC_HYS</sub>     | V <sub>CC</sub> - V <sub>AGND</sub>                   |       | 650   |       | mV    |

| VCC regulator                                   | Vcc                     | I <sub>CC</sub> = 0mA                                 | 4.9   | 5.1   | 5.3   | V     |

| VCC load regulation                             |                         | $I_{CC} = 20 \text{mA}$                               | 4.7   |       |       | V     |

| VCC maximum current ability                     |                         | $V_{CC} = V_{CC_UVLO} + 100 \text{mV}$ , no switching | 50    | 80    | 120   | mA    |

| VCC source current ability (6)                  |                         | $V_{CC} = V_{CC_UVLO} + 100mV$ , switching            |       | 25    |       | mA    |

| DUTY source current                             | IDUTY                   | Iduty1                                                | 40    | 45    | 50    | μA    |

|                                                 | IDOTT                   | IDUTY2                                                | 550   | 600   | 650   | μA    |

| VDUTY threshold maximum                         |                         | IDUTY1 and IDUTY2                                     | 3.287 | 3.355 | 3.422 | V     |

| VDUTY threshold minimum                         |                         | IDUTY1 and IDUTY2                                     | 0.28  | 0.302 | 0.33  | V     |

| Two-step dimming frequency                      |                         |                                                       |       | 500   |       | Hz    |

| Output OV threshold                             | OVVTH                   | Vingnd - Vagnd                                        | 17    | 18    | 19    | V     |

| Output UV threshold                             | UVVTH                   | Vingnd - Vagnd                                        | 1     | 1.35  | 1.7   | V     |

| VIN load dump protection threshold              |                         |                                                       | 38    | 40    | 42    | V     |

| VIN load dump protection<br>falling threshold   |                         |                                                       | 37    | 39    | 41    | V     |

| VIN load dump protection<br>hysteresis          |                         |                                                       |       | 1     |       | V     |

| Output discharge current for                    |                         | V <sub>INGND</sub> - V <sub>PGND</sub> > 5V           | 40    | 100   | 180   | mA    |

| load dump protection                            |                         | V <sub>INGND</sub> - V <sub>PGND</sub> = 1V           | 20    | 45    | 90    | mA    |

| FAULT assertion delay time when during start-up | t <sub>ft-d_start</sub> |                                                       | 25    | 35    | 40    | ms    |

| FAULT assertion deglitch time after start-up    | t <sub>FT-D</sub>       |                                                       |       | 20    |       | μs    |

$V_{IN}$  = 13.5V,  $V_{EN}$  = 2V,  $T_J$  = -40°C to +125°C  $^{\rm (5)}$ , typical values are at  $T_J$  = 25°C, buck-boost mode, unless otherwise noted.

| Parameter                                         | Symbol      | Condition                               | Min   | Тур  | Max   | Units |

|---------------------------------------------------|-------------|-----------------------------------------|-------|------|-------|-------|

| FAULT assertion low sink                          | IFAULT_SINK | V <sub>FAULT</sub> = 12V                | 10    | 30   | 50    | mA    |

| current ability                                   |             | $V_{FAULT} = 0.2V$                      | 5     | 12   |       | mA    |

| FAULT pull-up resistor                            |             |                                         | 100   | 300  | 500   | kΩ    |

| FAULT pull-down resistor                          |             |                                         | 2000  | 4000 | 6000  | kΩ    |

| IREF current for mode detection                   |             |                                         | 200   | 240  | 280   | μA    |

| VIREF threshold for mode detection                |             |                                         | 2.6   | 2.7  | 2.8   | V     |

| IREF voltage                                      | VIREF       | I <sub>REF</sub> = 20µA                 | 0.50  | 0.57 | 0.63  | V     |

| IREF current threshold for<br>pin short detection |             |                                         | 600   | 900  | 1200  | μA    |

| IREF current threshold for<br>pin open detection  |             |                                         |       | 40   | 70    | μA    |

| NTC source current                                | INTC1       |                                         | 4.5   | 7.6  | 10    | μA    |

| NTC Source current                                | INTC2       | $V_{NTC} = 1.25V, I_{REF} = 200\mu A$   | 980   | 1020 | 1060  | μA    |

| NTC voltage for current                           |             | ILED = 98% of the nominal voltage       | -2.5% | 1.25 | +2.5% | V     |

| derating                                          |             | $I_{LED} = 58\%$ of the nominal voltage | -2.5% | 0.65 | +2.5% | V     |

| VNTC OV threshold                                 |             | VNTC1                                   | 1.8   | 2    | 2.2   | V     |

| VNTC threshold for OTP                            |             | VNTC2                                   | 0.2   | 0.38 | 0.48  | V     |

| VNTC deglitch time for OTP                        |             | V <sub>NTC</sub> = 0.3V                 | 180   | 256  | 320   | μs    |

| V <sub>NTC</sub> UV threshold                     |             | V <sub>NTC2</sub>                       | 0.14  | 0.18 | 0.22  | V     |

| Thermal shutdown (6)                              |             |                                         | 155   | 170  | 185   | °C    |

#### Notes:

5) Not tested in production. Guaranteed by over-temperature correlation.

6) Not tested in production. Guaranteed by design and characterization.

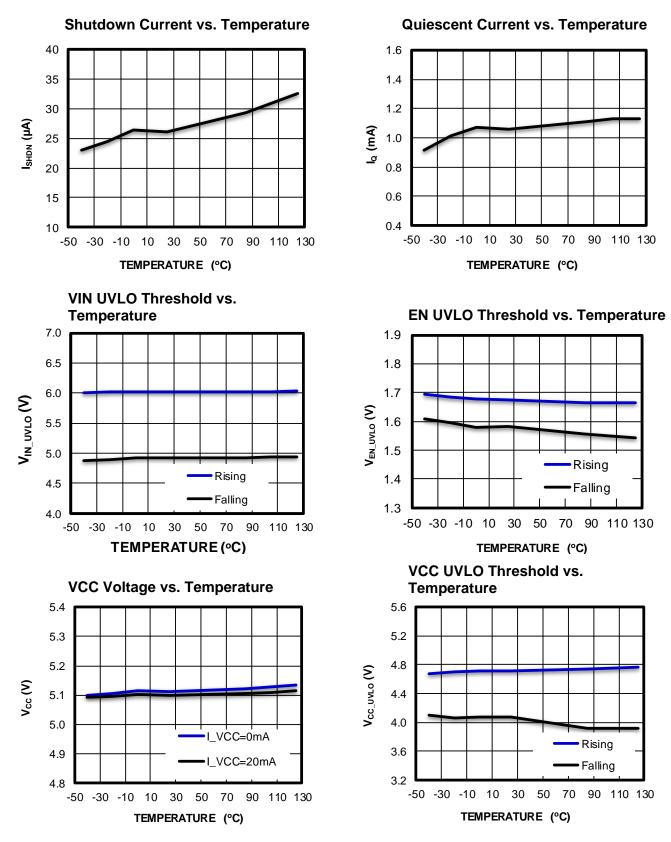

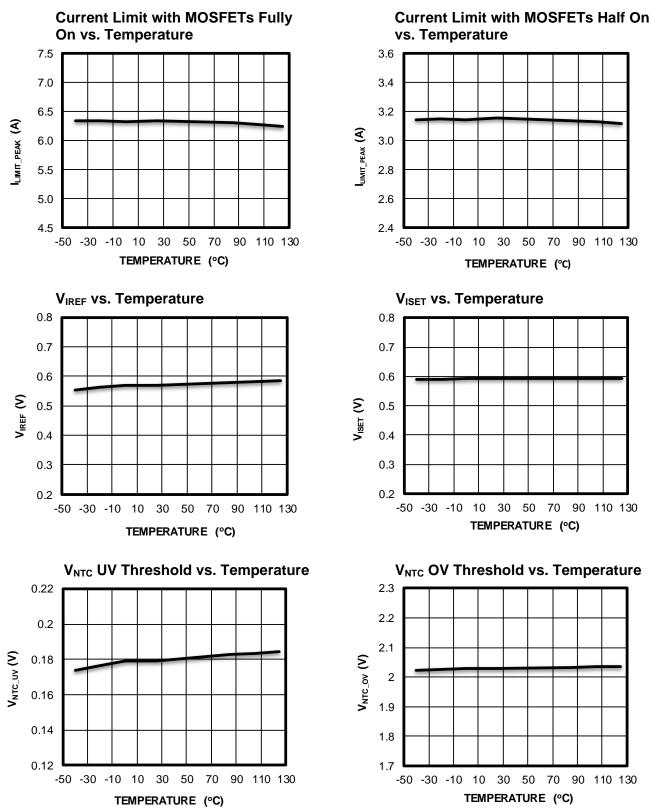

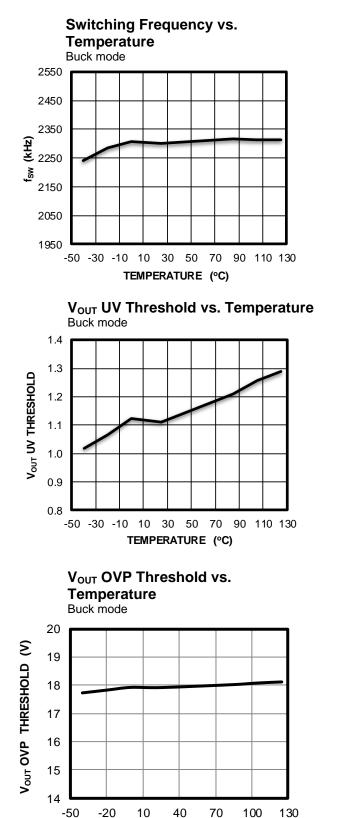

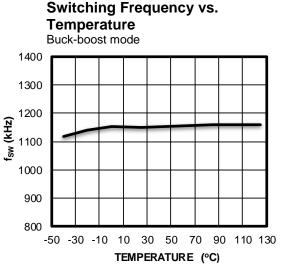

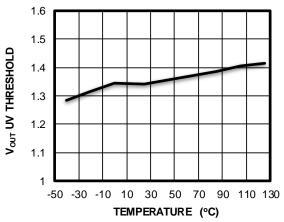

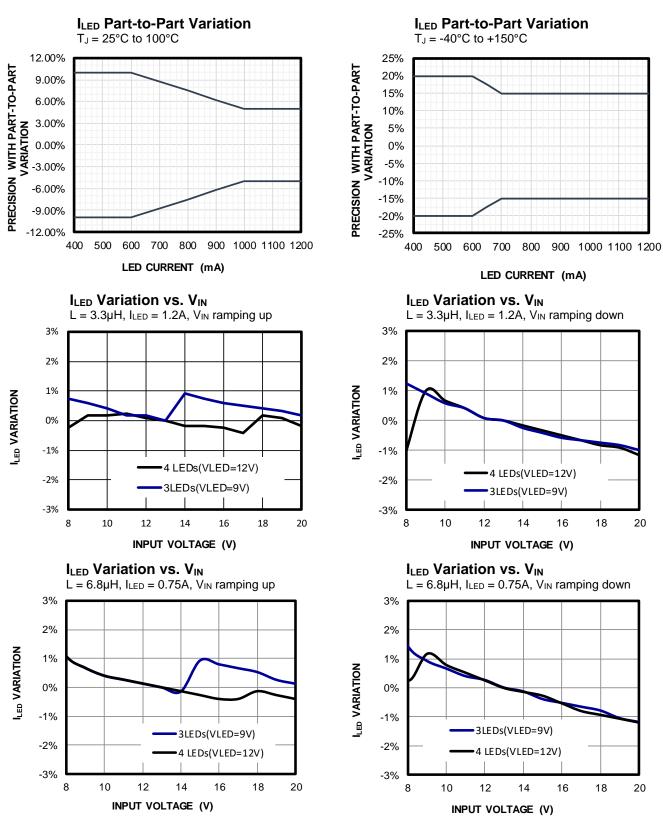

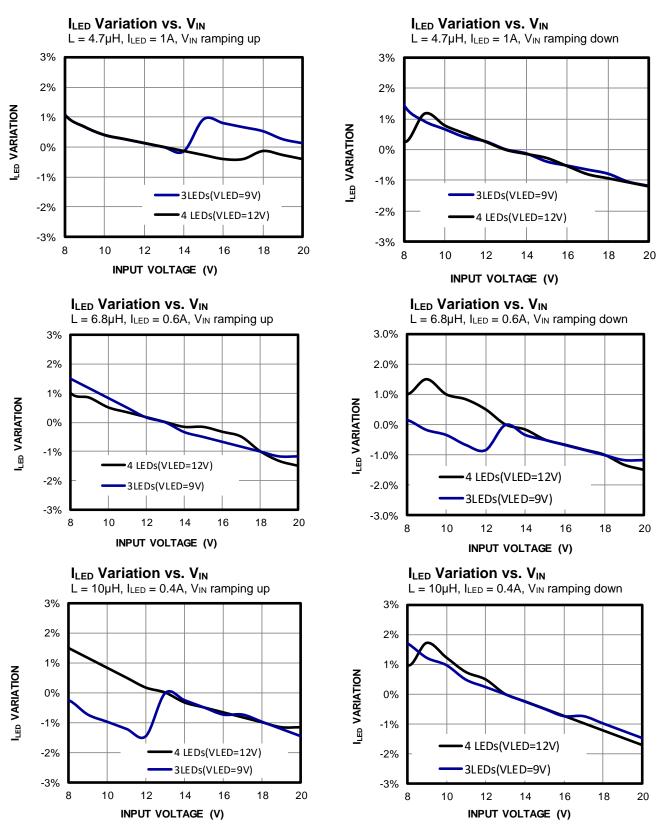

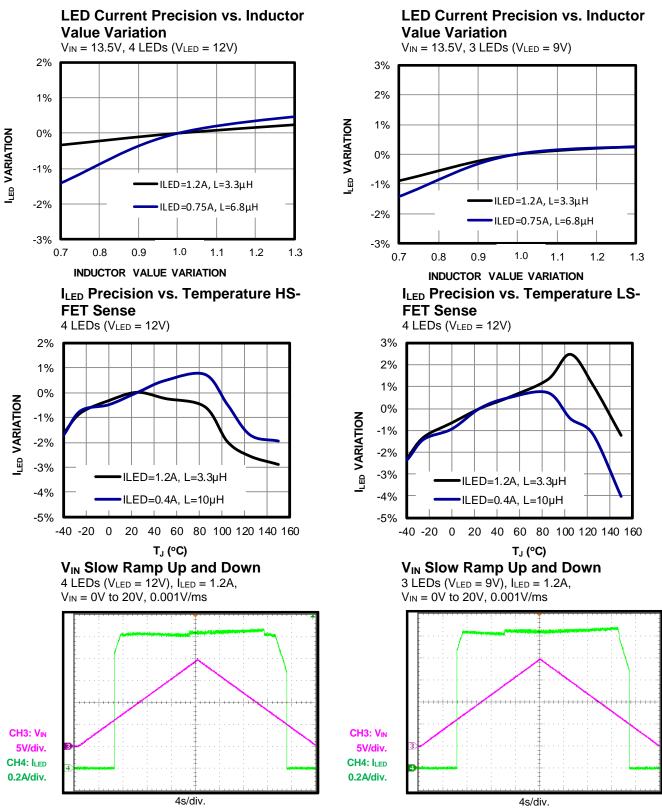

## **TYPICAL CHARACTERISTICS**

$V_{IN} = 12V$ ,  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted.

$V_{IN} = 12V$ ,  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted.

$V_{IN} = 12V$ ,  $T_{J} = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted.

**VOUT UV Threshold vs. Temperature** Buck-boost mode

**V**<sub>OUT</sub> OVP Threshold vs. Temperature Buck-boost mode

-50

-20

10

40

**TEMPERATURE (°C)**

100

130

## **TYPICAL PERFORMANCE CHARACTERISTICS**

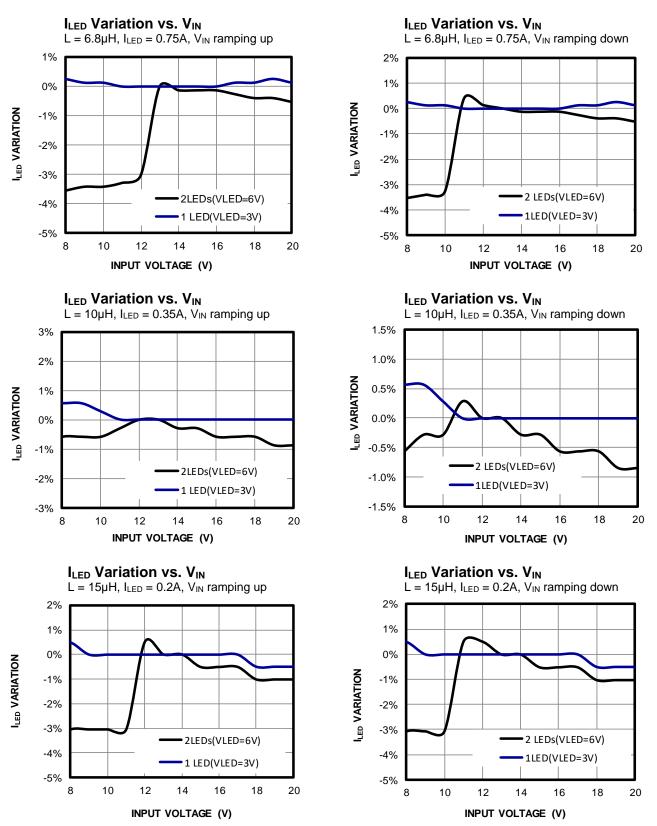

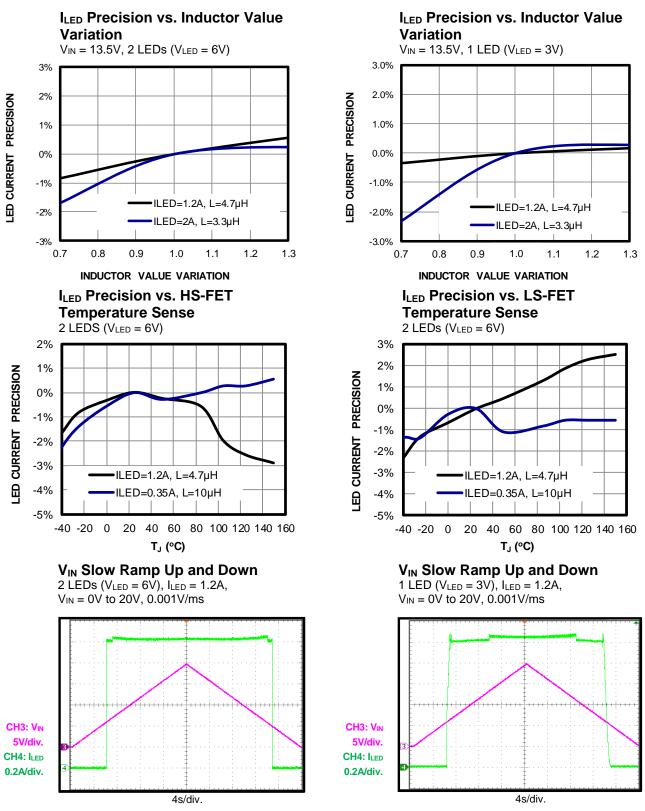

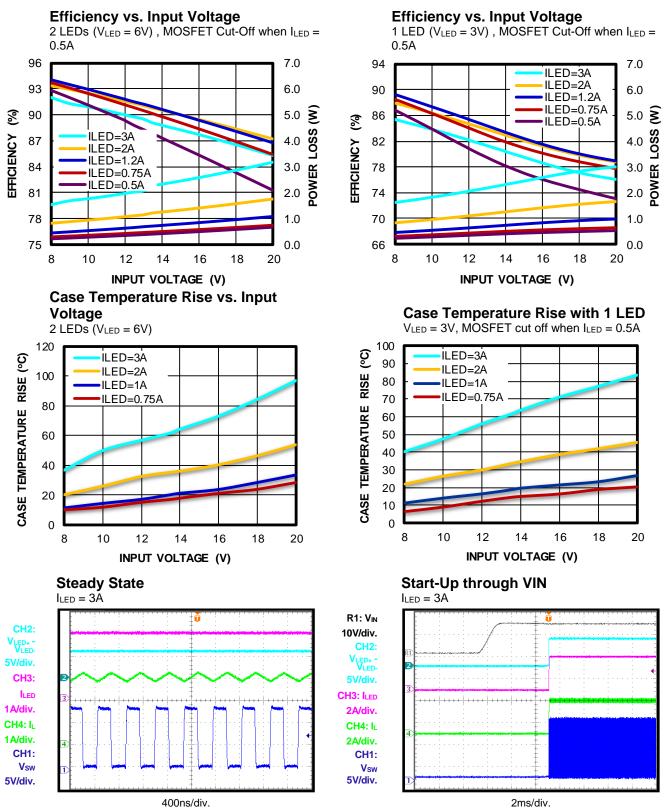

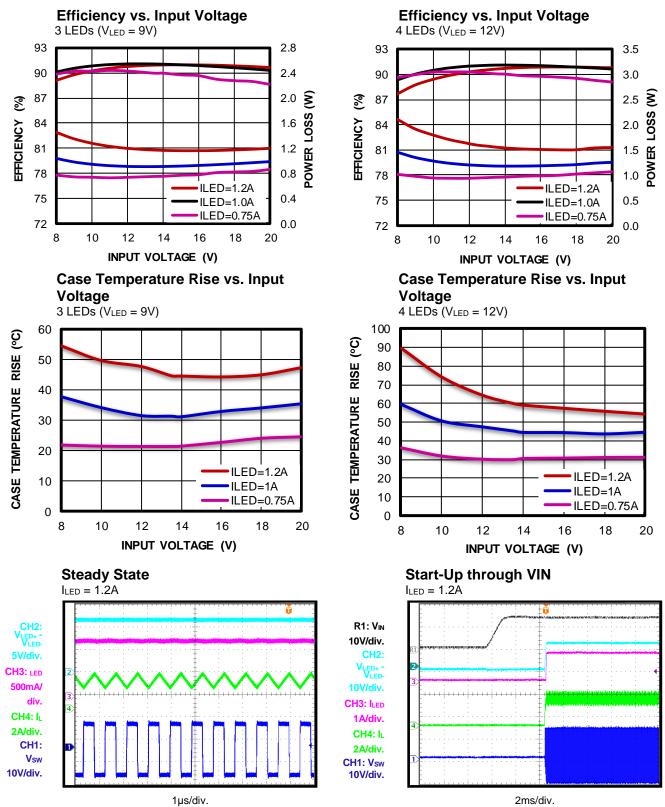

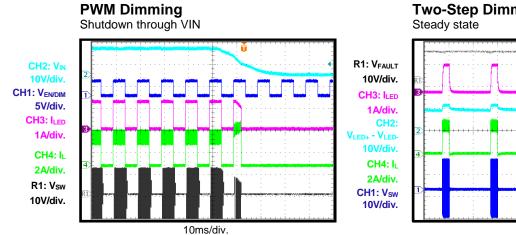

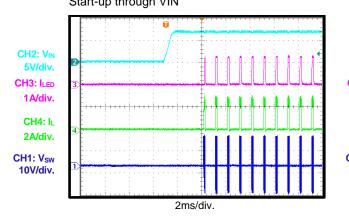

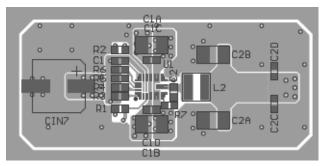

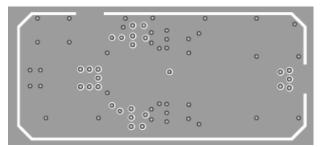

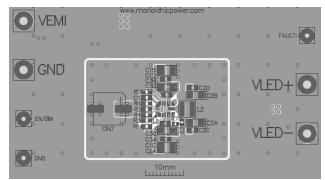

Buck mode, 2 LEDs (V<sub>LED</sub> = 6V), V<sub>IN</sub> = 13.5V,  $f_{SW}$  = 2.3MHz, L = 4.7µH, T<sub>A</sub> = 25°C, unless otherwise noted.

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2021 MPS. All Rights Reserved.

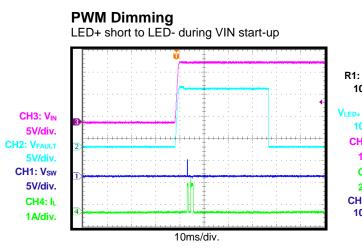

Buck mode, 2 LEDs (V<sub>LED</sub> = 6V), V<sub>IN</sub> = 13.5V,  $f_{SW}$  = 2.3MHz, L = 4.7µH, T<sub>A</sub> = 25°C, unless otherwise noted.

MP7200 Rev. 1.0 1/21/2021 www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2021 MPS. All Rights Reserved.

Buck mode, 2 LEDs (V<sub>LED</sub> = 6V), V<sub>IN</sub> = 13.5V,  $f_{SW}$  = 2.3MHz, L = 4.7µH, T<sub>A</sub> = 25°C, unless otherwise noted.

MP7200 Rev. 1.0 1/21/2021

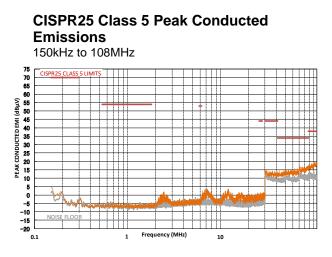

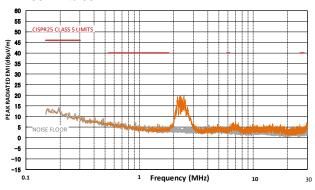

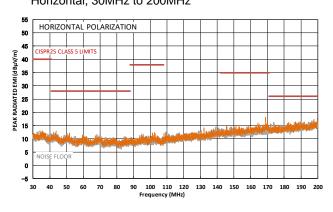

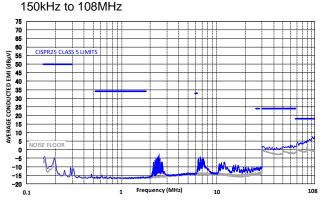

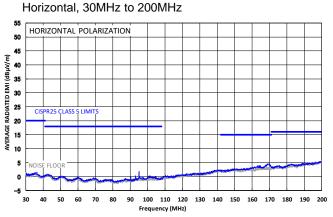

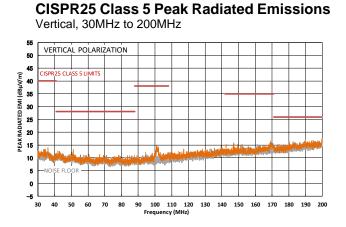

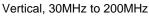

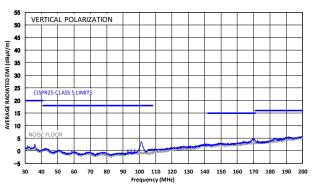

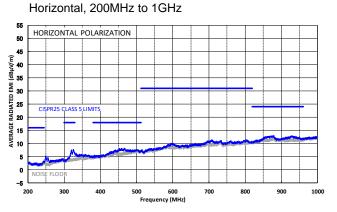

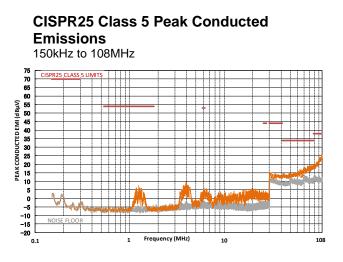

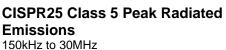

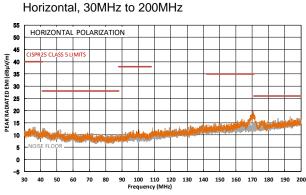

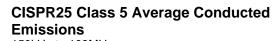

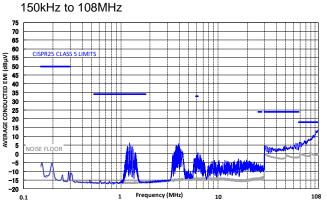

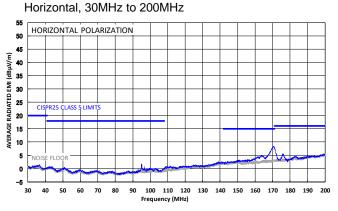

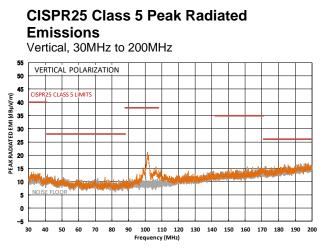

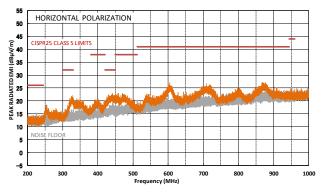

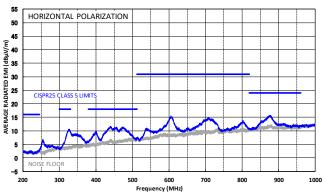

Buck mode,  $V_{IN}$  = 12V, 2 LEDs in series ( $V_{LED}$  = 6V) when  $I_{LED}$  = 3A, L = 4.7µH,  $f_{SW}$  = 2.3MHz, with EMI filters,  $T_A$  = 25°C, unless otherwise noted.<sup>(7)</sup>

CISPR25 Class 5 Peak Radiated Emissions 150kHz to 30MHz

#### CISPR25 Class 5 Peak Radiated Emissions Horizontal, 30MHz to 200MHz

CISPR25 Class 5 Average Conducted Emissions

## CISPR25 Class 5 Average Radiated Emissions

150kHz to 30MHz

## CISPR25 Class 5 Average Radiated Emissions

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2021 MPS. All Rights Reserved.

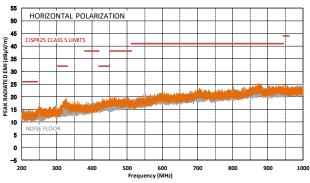

Buck mode,  $V_{IN}$  = 12V, 2 LEDs in series ( $V_{LED}$  = 6V) when  $I_{LED}$  = 3A, L = 4.7µH,  $f_{SW}$  = 2.3MHz, with EMI filters,  $T_A$  = 25°C, unless otherwise noted. <sup>(7)</sup>

#### CISPR25 Class 5 Peak Radiated Emissions Horizontal, 200MHz to 1GHz

Vertical, 200MHz to 1GHz 55 VERTICAL POLARIZATION 50 45 (m/v40 (m/v40) 35 CISP S 5 LIMITS RADIATED EMI 30 52 50 ¥ 15 10 0 -5 200 300 400 700 800 900 1000 500 600 Frequency (MHz)

#### **CISPR25 Class 5 Average Radiated**

## CISPR25 Class 5 Average Radiated Emissions

#### CISPR25 Class 5 Average Radiated Emissions

#### Note:

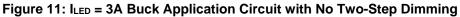

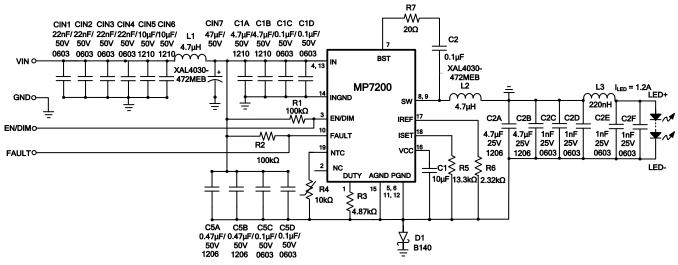

7) Buck mode EMC test results are based on the application circuit with EMI filters (see Figure 11 on page 54).

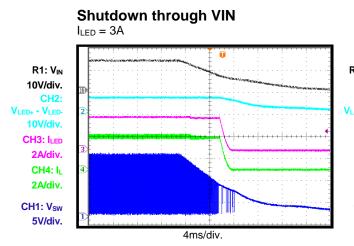

Buck mode, 2 LEDs in series ( $V_{LED} = 6V$ ),  $V_{IN} = 13.5V$ ,  $f_{SW} = 2.3MHz$ ,  $L = 4.7\mu$ H,  $T_A = 25^{\circ}$ C, unless otherwise noted.

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2021 MPS. All Rights Reserved.

Buck mode, 2 LEDs (V<sub>LED</sub> = 6V), V<sub>IN</sub> = 13.5V,  $f_{SW}$  = 2.3MHz, L = 4.7µH, T<sub>A</sub> = 25°C, unless otherwise noted.

# Start-Up through EN/DIM ILED = 3A R1: VENDIM 2V/div. CH2: /LED - VLED 5V/div. CH3: ILED 2A/div. CH4: IL 2A/div. CH1: Vsw 5V/div.

1ms/div.

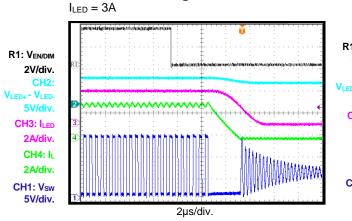

Shutdown through EN/DIM

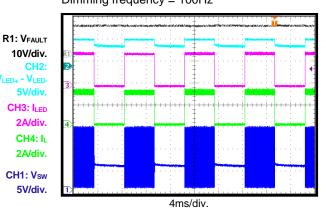

#### **PWM Dimming Steady State** Dimming frequency = 100Hz

**PWM Dimming Steady State**

10ms/div.

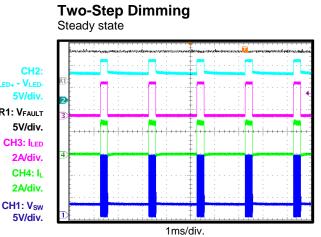

Buck mode, 2 LEDs (V<sub>LED</sub> = 6V), V<sub>IN</sub> = 13.5V,  $f_{SW}$  = 2.3MHz, L = 4.7µH, T<sub>A</sub> = 25°C, unless otherwise noted.

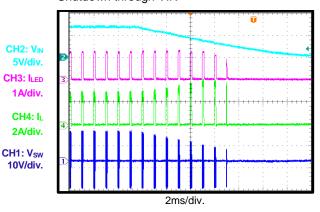

Two-Step Dimming Shutdown through VIN

Buck mode, 2 LEDs (V<sub>LED</sub> = 6V), V<sub>IN</sub> = 13.5V,  $f_{SW}$  = 2.3MHz, L = 4.7µH, T<sub>A</sub> = 25°C, unless otherwise noted.

#### Two-Step Dimming LED open entry

Buck mode, 2 LEDs (V<sub>LED</sub> = 6V), V<sub>IN</sub> = 13.5V,  $f_{SW}$  = 2.3MHz, L = 4.7µH, T<sub>A</sub> = 25°C, unless otherwise noted.

www.MonolithicPower.com

CH1: Vsw

10V/div.

CH1: Vsw

MP7200 Rev. 1.0

1/21/2021

10V/div.

10ms/div.

10ms/div.

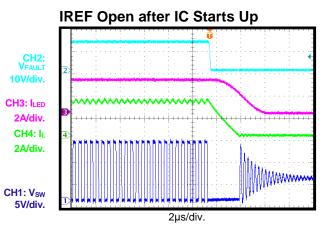

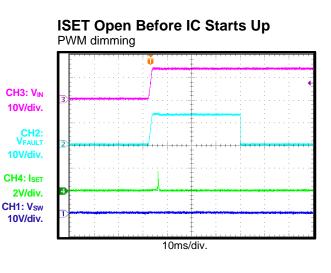

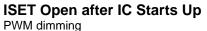

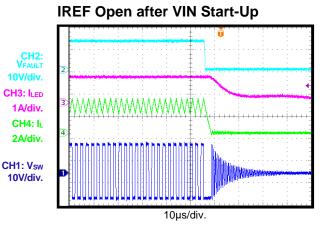

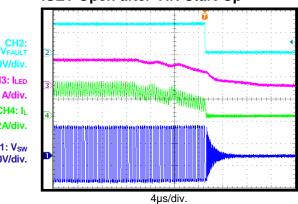

Buck mode, 2 LEDs (V<sub>LED</sub> = 6V), V<sub>IN</sub> = 13.5V,  $f_{SW}$  = 2.3MHz, L = 4.7µH, T<sub>A</sub> = 25°C, unless otherwise noted.

IREF Open after IC Starts Up PWM dimming

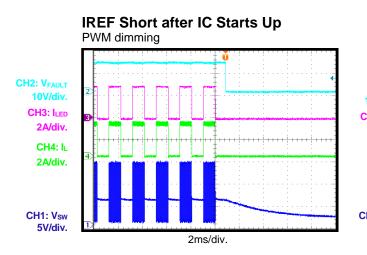

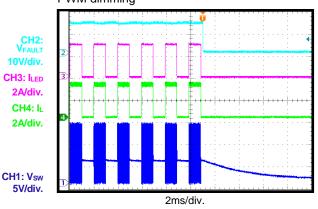

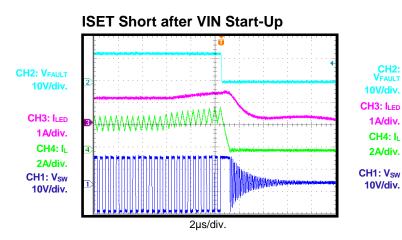

Buck mode, 2 LEDs (V<sub>LED</sub> = 6V), V<sub>IN</sub> = 13.5V,  $f_{SW}$  = 2.3MHz, L = 4.7µH, T<sub>A</sub> = 25°C, unless otherwise noted.

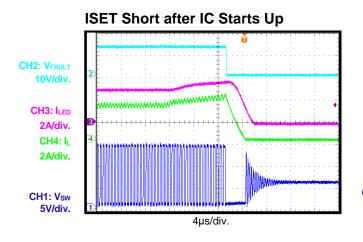

ISET Short after IC Starts Up

Buck mode, 2 LEDs (V<sub>LED</sub> = 6V), V<sub>IN</sub> = 13.5V,  $f_{SW}$  = 2.3MHz, L = 4.7µH, T<sub>A</sub> = 25°C, unless otherwise noted.

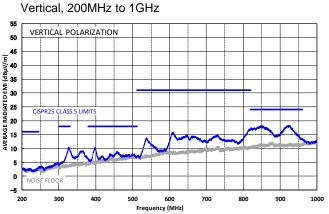

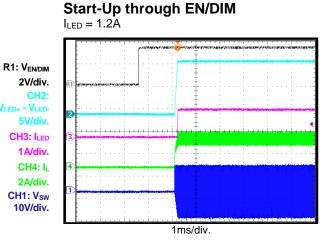

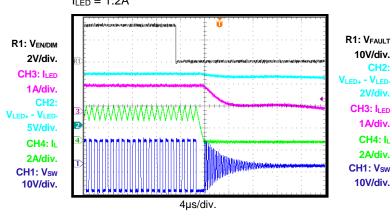

Buck-boost mode, 4 LEDs (V<sub>LED</sub> = 12V), V<sub>IN</sub> = 13.5V,  $f_{SW}$  = 1.15MHz, L = 4.7µH, T<sub>A</sub> = 25°C, unless otherwise noted.

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2021 MPS. All Rights Reserved.

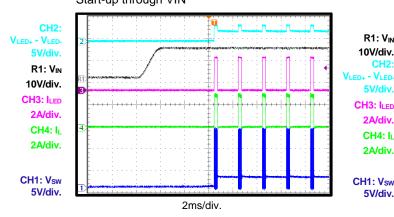

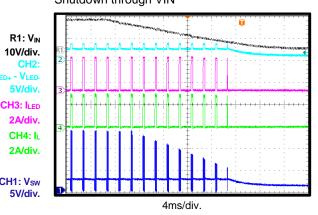

Buck-boost mode, 4 LEDs (V<sub>LED</sub> = 12V), V<sub>IN</sub> = 13.5V,  $f_{SW}$  = 1.15MHz, L = 4.7µH, T<sub>A</sub> = 25°C, unless otherwise noted.

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2021 MPS. All Rights Reserved.

Buck-boost mode, 4 LEDs (V<sub>LED</sub> = 12V), V<sub>IN</sub> = 13.5V,  $f_{SW}$  = 1.15MHz, L = 4.7µH, T<sub>A</sub> = 25°C, unless otherwise noted.

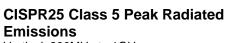

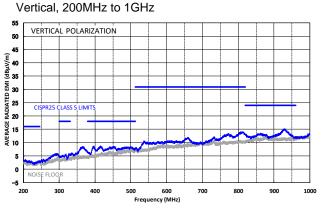

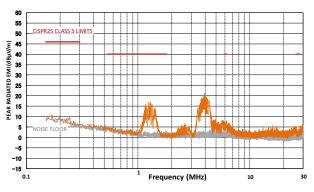

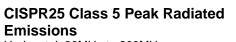

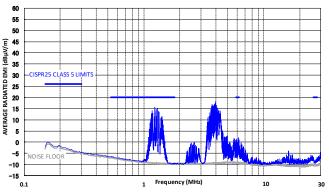

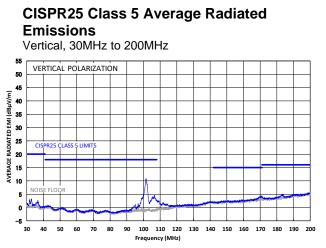

Buck-boost mode,  $V_{IN}$  = 12V, 4 LEDs in series ( $V_{LED}$  = 12V) when  $I_{LED}$  = 1.2A, L = 4.7µH,  $f_{SW}$  = 1.15MHz, with EMI filters,  $T_A$  = 25°C, unless otherwise noted. <sup>(8)</sup>

## CISPR25 Class 5 Average Radiated Emissions

150kHz to 30MHz

## CISPR25 Class 5 Average Radiated Emissions

Buck-boost mode,  $V_{IN}$  = 12V, 4 LEDs in series ( $V_{LED}$  = 12V) when  $I_{LED}$  = 1.2A, L = 4.7µH,  $f_{SW}$  = 1.15MHz, with EMI filters,  $T_A$  = 25°C, unless otherwise noted. <sup>(8)</sup>

## CISPR25 Class 5 Peak Radiated Emissions

Horizontal, 200MHz to 1GHz

## CISPR25 Class 5 Peak Radiated Emissions

Vertical, 200MHz to 1GHz 55 VERTICAL POLARIZATION 50 45 42 40 (m//ηdBh/m) IM3 0 CISPR25 C 20 STADIATED E 100 ¥ 15 10 5 0 -5 300 400 700 800 900 200 1000 500 600 Frequency (MHz)

## CISPR25 Class 5 Average Radiated Emissions

Horizontal, 200MHz to 1GHz

## CISPR25 Class 5 Average Radiated Emissions

#### Note:

The MP7200 buck-boost mode EMC test results are based on the application circuit with EMI filters (see Figure 12 on page 54).

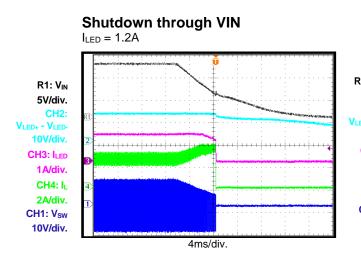

Buck-boost mode, 4 LEDs (V<sub>LED</sub> = 12V), V<sub>IN</sub> = 13.5V,  $f_{SW}$  = 1.15MHz, L = 4.7µH, T<sub>A</sub> = 25°C, unless otherwise noted.

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2021 MPS. All Rights Reserved.

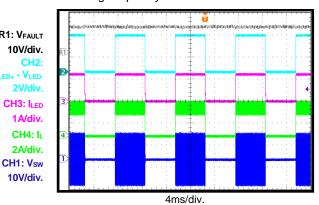

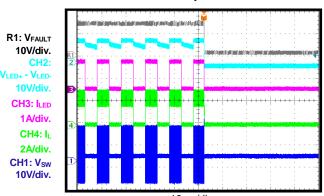

Buck-boost mode, 4 LEDs (V<sub>LED</sub> = 12V), V<sub>IN</sub> = 13.5V,  $f_{SW}$  = 1.15MHz, L = 4.7µH, T<sub>A</sub> = 25°C, unless otherwise noted.

Shutdown through EN/DIM ILED = 1.2A

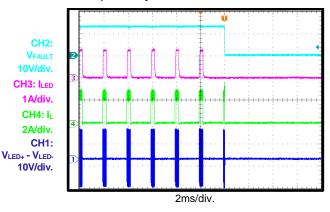

**PWM Dimming Steady State** Dimming frequency = 100Hz

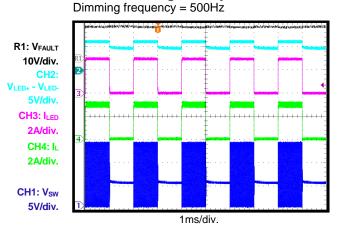

PWM Dimming Steady State Dimming frequency = 500Hz CH2: VENDM SV/div. R1: VFAULT 10V/div. CH3: ILED 1A/div. CH1: Vsw 10V/div. CH1: Vsw

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2021 MPS. All Rights Reserved.

R1: Vsw

10V/div.

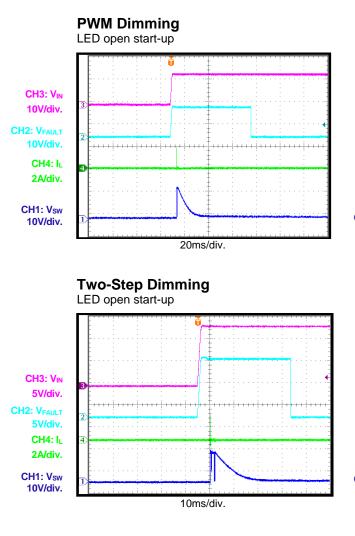

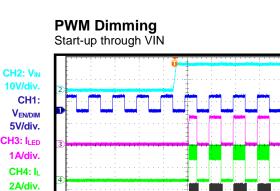

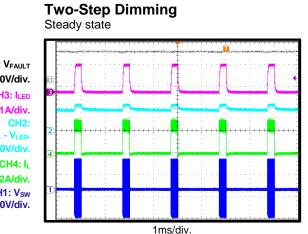

Buck-boost mode, 4 LEDs (V<sub>LED</sub> = 12V), V<sub>IN</sub> = 13.5V,  $f_{SW}$  = 1.15MHz, L = 4.7µH, T<sub>A</sub> = 25°C, unless otherwise noted.

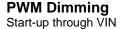

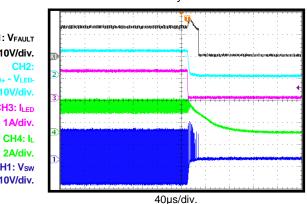

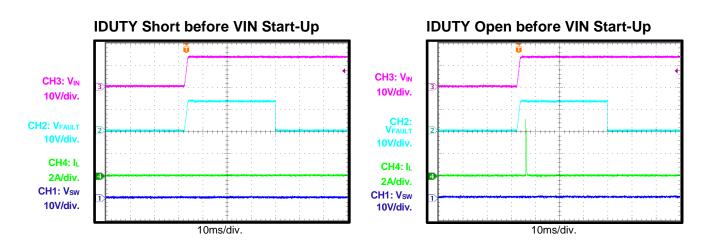

Two-Step Dimming Start-up through VIN

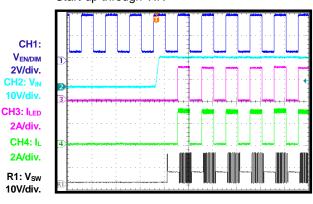

Two-Step Dimming Shutdown through VIN

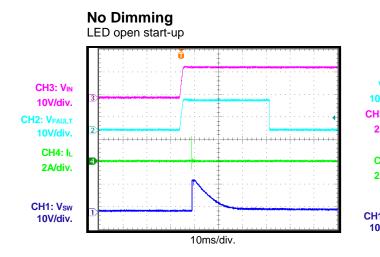

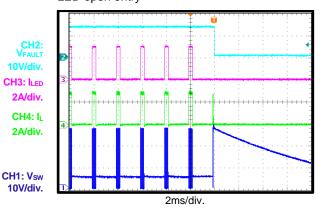

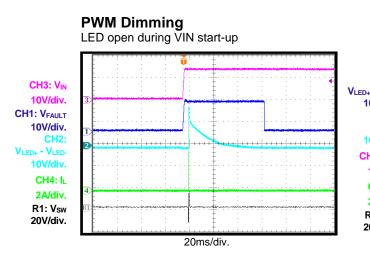

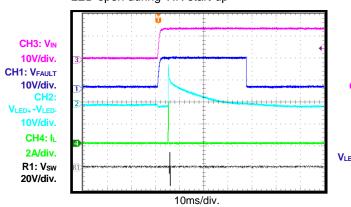

Buck-boost mode, 4 LEDs (V<sub>LED</sub> = 12V), V<sub>IN</sub> = 13.5V,  $f_{SW}$  = 1.15MHz, L = 4.7µH, T<sub>A</sub> = 25°C, unless otherwise noted.

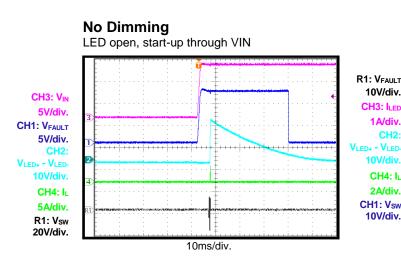

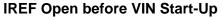

#### **Two-Step Dimming** LED open during VIN start-up

#### Two-Step Dimming LED open entry

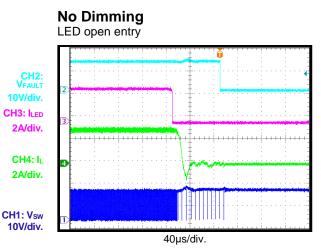

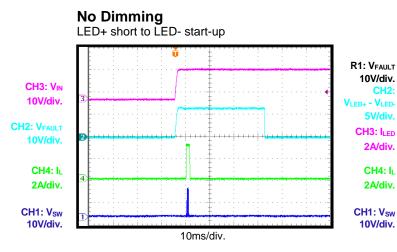

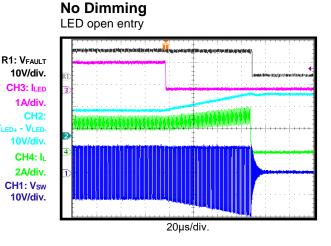

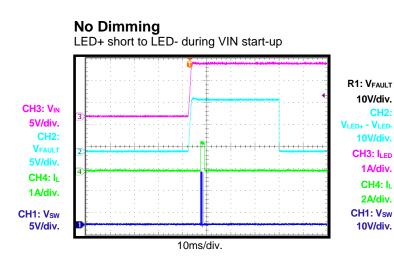

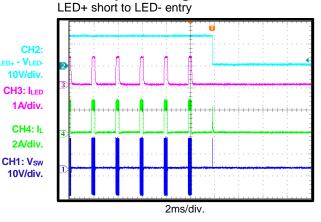

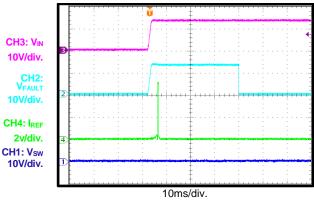

#### **No Dimming** LED+ short to LED- entry

## **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

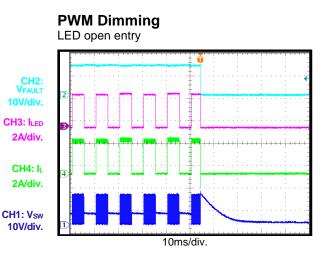

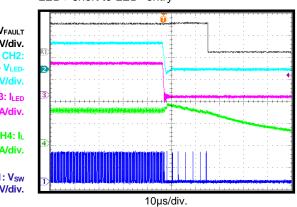

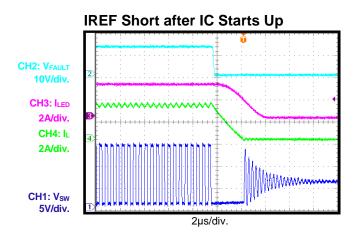

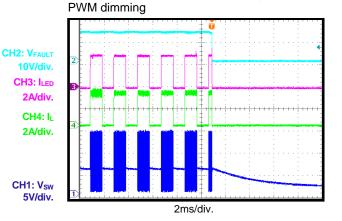

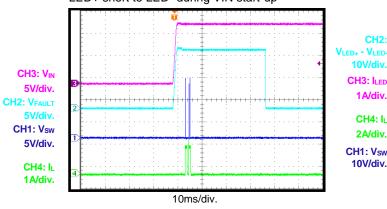

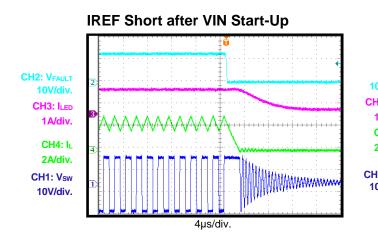

Buck-boost mode, 4 LEDs (V<sub>LED</sub> = 12V), V<sub>IN</sub> = 13.5V,  $f_{SW}$  = 1.15MHz, L = 4.7µH, T<sub>A</sub> = 25°C, unless otherwise noted.

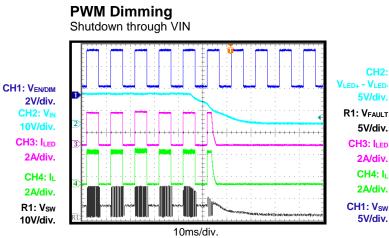

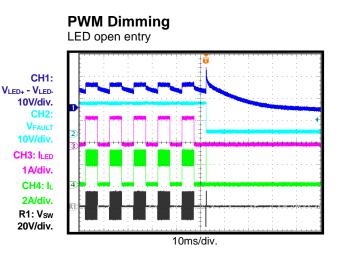

**PWM Dimming** LED+ short to LED- entry

10ms/div.

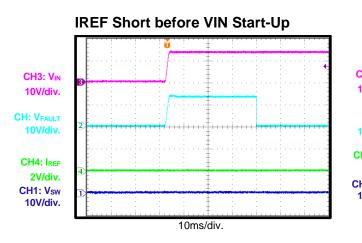

Two-Step Dimming LED+ short to LED- during VIN start-up

**Two-Step Dimming**

#### MP7200 Rev. 1.0 1/21/2021

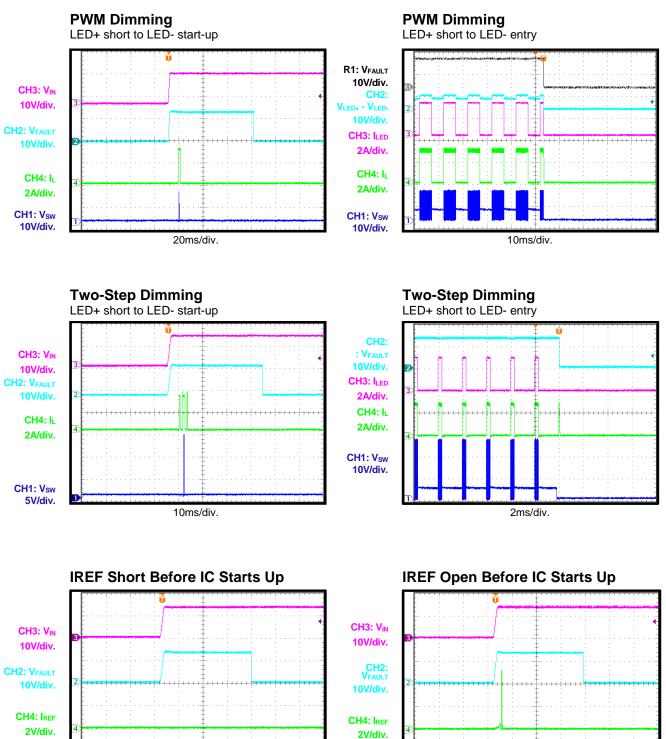

## **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

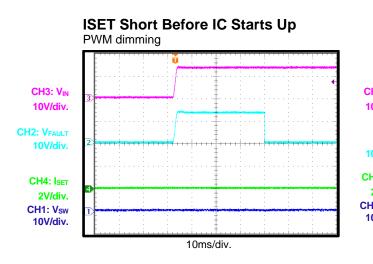

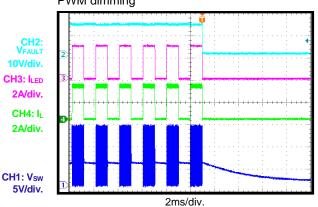

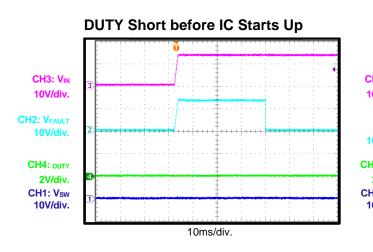

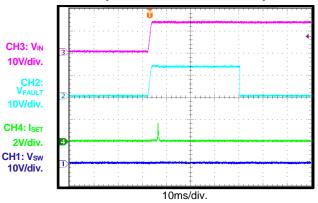

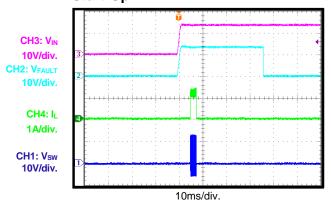

Buck-boost mode, 4 LEDs (V<sub>LED</sub> = 12V), V<sub>IN</sub> = 13.5V,  $f_{SW}$  = 1.15MHz, L = 4.7µH, T<sub>A</sub> = 25°C, unless otherwise noted.

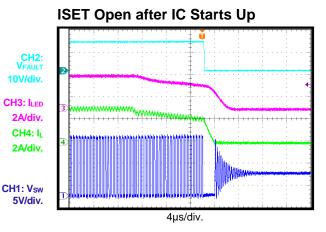

## CH3: VIN 10V/div. CH2: VFAULT 10V/div. CH4: ISET 2V/div. CH1: VSW 10V/div. H1: VSW 10V/div.

#### ISET Open after VIN Start-Up

MP7200 Rev. 1.0 1/21/2021

## **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

Buck-boost mode, 4 LEDs (V<sub>LED</sub> = 12V), V<sub>IN</sub> = 13.5V,  $f_{SW}$  = 1.15MHz, L = 4.7µH, T<sub>A</sub> = 25°C, unless otherwise noted.

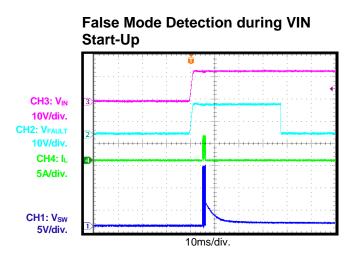

## False Mode Detection during VIN Start-Up

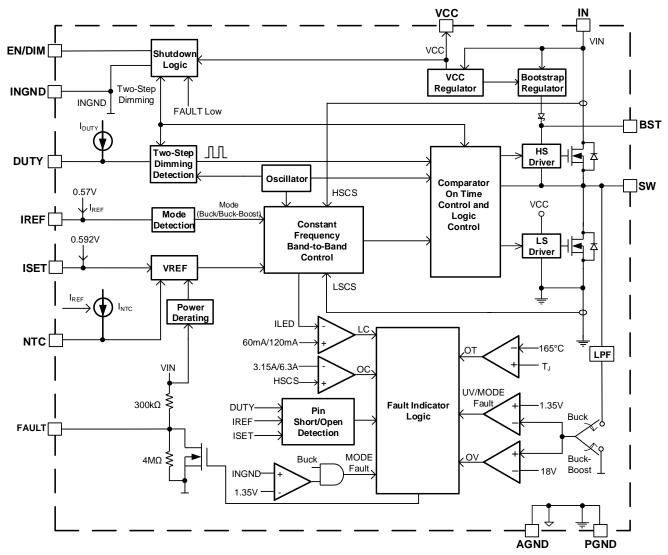

## FUNCTIONAL BLOCK DIAGRAM

Figure 3: Functional Block Diagram

## OPERATION

The MP7200 is a high-frequency, synchronous, rectified, buck-boost or buck switch-mode LED driver with built-in power MOSFETs. It offers a very compact solution to achieve up to 1.2A of continuous output current in a buck-boost topology (or 3A in a buck topology), with excellent load and line regulation across a 6V to 42V input supply range.

#### Fixed-Frequency Band-to-Band Control

The MP7200 uses fixed-frequency band-to-band control, plus spread spectrum, to reduce electromagnetic interference (EMI) noise. Compared to fixed-frequency PWM control, band-to-band control offers a simpler control loop and faster transient response. The loop is stable without an output capacitor. Band-to-band control compares the inductor current to the internal thresholds (IBANDPEAK and IBANDVALLEY).

When the inductor current (I<sub>L</sub>) exceeds I<sub>BANDPEAK</sub>, the high-side MOSFET (HS-FET) turns off. When I<sub>L</sub> drops below I<sub>BANDVALLEY</sub>, the HS-FET turns on. (I<sub>BANDPEAK</sub> + I<sub>BANDVALLEY</sub>) / 2 is controlled by a PID loop to regulate the LED current. I<sub>BANDPEAK</sub> - I<sub>BANDVALLEY</sub> is controlled by a PLL loop to regulate the switching frequency to be 2.3MHz in buck mode, and 1.15MHz in buck-boost mode. If the minimum on time (t<sub>ON\_MIN</sub>) or minimum off time (t<sub>OFF\_MIN</sub>) is triggered, the switching frequency is extended. The real switching frequency is (D / t<sub>ON\_MIN</sub>) or (1 - D) / t<sub>OFF\_MIN</sub>, where D is the required duty cycle, and t<sub>ON\_MIN</sub> and t<sub>OFF\_MIN</sub> are both 80ns maximum.

The spread spectrum function uses a 15kHz modulation frequency with a triangular profile to spread the internal oscillator frequency across a  $\pm 10\%$  nominal switching frequency window (1.15MHz in buck mode, and 2.3MHz in buckboost mode).

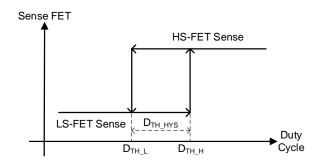

### **Middle-Point Inductor Current Sense**

The MP7200 senses the LED current by sensing the inductor current middle point ( $I_{LMID}$ ).  $I_{LMID}$  is sensed through the sensing FET.  $I_{LMID}$  is sensed through the HS-FET when the duty cycle exceeds  $D_{TH_{L}H}$  (55% in buck mode or 60% in buck-boost mode), and is sensed through the LS-FET when the duty cycle is below  $D_{TH_{L}}$  (45% in buck mode or 40% in buck-boost mode).

A duty cycle hysteresis ( $D_{TH_HYS}$ ) (10% in buck mode and 20% in buck-boost mode) is used to prevent frequent current-sense switches between the HS-FET and LS-FET at the critical duty cycle (see Figure 4).

Figure 4: Current-Sense MOSFET vs. Duty Cycle

In buck mode, the LED current is equal to  $I_{LMID}$ . In buck-boost mode, it is equal to  $I_{LMID} \times V_{IN} / (V_{IN} + V_{OUT})$ .

#### Buck and Buck-Boost Mode Selection

The MP7200 can be configured to buck or buckboost mode by connecting a different resistor ( $R_{IREF}$ ) at the IREF pin.

Mode detection starts when VCC reaches its under-voltage lockout (UVLO) threshold of about 4.7V. There is a 240µA current source ( $I_{REF_DET}$ ) flowing out of the IREF pin to detect the resistor voltage value at the pin during start-up. If the voltage generated by  $I_{REF_DET} \times R_{IREF}$  is below 2.6V, buck-boost mode is selected. If  $I_{REF_DET} \times$  $R_{IREF}$  exceeds 2.8V, buck mode is selected. The corresponding  $R_{IREF}$  is ≤9.09k $\Omega$  for buck-boost mode, and ≥14.7k $\Omega$  for buck mode.

Certain resistors are recommended to avoid an IREF short fault in buck-boost mode, and an IREF open fault in buck mode. In buck mode, R<sub>IREF</sub> should be set between 1.05k $\Omega$  and 9.09k $\Omega$ . In buck-boost mode, R<sub>IREF</sub> should be set between 14.7k $\Omega$  and 80.6k $\Omega$ . Once the resistor has been detected, the mode is latched and I<sub>REF</sub> becomes 0.57V / R<sub>IREF</sub>, which is the reference for the NTC pin current. The latched mode signal is reset by VCC UVLO; it cannot be reset by pulling EN/DIM low.

An internal 1MHz filter works with a 250 $\mu$ s deglitch time to protect the part from false mode detection caused by noise coupling at the pin. To ensure that the detected mode is consistent with the real topology connection, V<sub>INGND</sub> - V<sub>PGND</sub> is

monitored. If buck mode is detected when  $(V_{INGND} - V_{PGND}) > 1.35V$ , or buck-boost mode is detected when  $(V_{INGND} - V_{PGND}) < 1.35V$  (detected as output under-voltage [UV] condition), the part latches off and asserts FAULT low.

#### **Internal Regulator**

The 5.1V internal regulator (VCC) powers most of the internal circuitries. VCC rises once V<sub>IN</sub> reaches its rising UVLO threshold, regardless of whether EN is high or low. VCC is a reference to PGND and AGND, but not INGND. This means that in buck-boost mode, VCC cannot have the same ground level as INGND. In buck-boost mode, the regulator uses either V<sub>IN</sub> or V<sub>INGND</sub> as the input: When (V<sub>INGND</sub> - V<sub>PGND</sub>) < 5.1V, VCC is powered from VIN. When (V<sub>INGND</sub> - V<sub>PGND</sub>) > 5.1V, the VCC regulator input switches to V<sub>INGND</sub> to reduce power loss. Once this switch occurs, VIN does not power VCC until V<sub>INGND</sub> - V<sub>PGND</sub> drops below 4.8V.

A smaller-value VCC capacitor can cause VCC voltage ringing and can makes the switch unstable. A  $\geq$ 3µF decoupling ceramic capacitor is needed at the VCC pin. When selecting a VCC capacitor, consider the capacitance derating to ensure that the real capacitance  $\geq$ 3µF. A 10µF, X7R capacitor with a  $\geq$ 10V DC rated voltage is recommended. VCC has its own UVLO with a 4.7V rising threshold and a 4.05V falling threshold. In addition to powering internal circuitries, VCC also powers external circuitries in the system, with a current capability of 25mA.

#### CCM Operation and DCM Operation

The MP7200 uses continuous conduction mode (CCM) to ensure that the part works with fixed frequency across the full load range. The advantage of CCM is the controllable frequency and lower output ripple at light loads. When = 0A, the MP7200 enters BANDVALLEY discontinuous conduction mode (DCM), in which the LS-FET acts as an ideal diode. Use an inductor that can ensure that the part does not enter DCM, even during a power or thermal derating. Otherwise, LED current precision cannot be guaranteed.

## Enable Control (EN)

When the two-step dimming function is not active (see the Two-Step Dimming section on page 43), EN/DIM is a control pin that turns the LED driver on and off. Drive  $V_{EN/DIM} - V_{INGND}$  above 1.67V to turn the part on. Drive  $V_{EN/DIM} - V_{INGND}$  below 1.58V for longer than 25ms to turn the part off and reset FAULT. When two-step dimming is active, the part automatically turns on while VIN and VCC exceed their UVLO thresholds, and EN is configured to be the two-step dimming control pin. Drive EN/DIM high to select a 100% dimming duty. Drive EN/DIM low to select the dimming duty via the DUTY pin. EN cannot reset FAULT in two-step dimming mode.

Connect EN/DIM to VIN through a resistor in both buck and buck-boost mode (it can also be connected to VCC in buck mode) if the EN/DIM pin is not used to control whether the part is on or off. In this scenario, the part always delivers the full configured current (no dimming). If twostep dimming is deactivated, connect an internal  $1M\Omega$  resistor from EN/DIM to INGND to float EN/DIM and shut down the chip. Place an integrated Zener diode in parallel with the EN/DIM pin to clamp V<sub>EN/DIM</sub> - V<sub>INGND</sub> to about 7V. This internal Zener diode can handle a 1mA current for a load dump voltage up to 100V when a 100k $\Omega$  resistor is connected between VIN and EN/DIM.

#### ISET

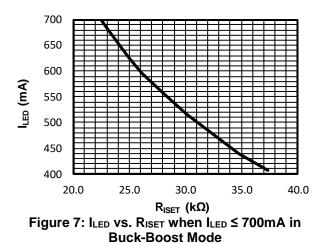

The LED average current can be configured by connecting a resistor ( $R_{ISET}$ ) at the ISET pin. The LED current can be calculated with Equation (1):

$$I_{\text{LED}}(A) = 16 / R_{\text{ISET}}(k\Omega)$$

(1)

The ISET pin nominal voltage ( $V_{ISET}$ ) is 0.592V.  $V_{ISET}$  can be set below 0.592V to decrease the LED current in the event of power derating or thermal derating.

During the mode detection period during start-up while the device is in buck mode, the ISET current is monitored to detect if the LED current is set above or below 600mA. If  $I_{ISET} > 22.2\mu A$  during this period, then the LED current setting is detected as >600mA and the MOSFETs turn fully on.

If the LED current setting is detected to be <600mA, half of the HS-FETs and LS-FETs are cut off to improve current-sense accuracy. After

this cutoff, the current limit drops from 6.3A to 3.15A. The signal to indicate whether the LED current is above or below 600mA is latched once detection finishes, and only can be reset by VCC UVLO. After LED current detection, the MOSFET's  $R_{DS(ON)}$  does not change, even if the current setting exceeds or falls below 600mA.

During normal operation, the ISET pin is continuously monitored to detect the occurrence of an open or short to GND condition. If the ISET current is above its specific value, the device detects a pin short to ground. In buck-boost mode, the MOSFET is always on, regardless of the current.

If the LED current ( $I_{LED}$ ) is set below 600mA, the ISET current threshold for short detection is 120µA (with the 4.9k $\Omega$  resistor, or 3.24A  $I_{LED}$ ). If  $I_{LED}$  is set above 600mA, the threshold is 220µA (with a 2.7k $\Omega$  resistor, or 5.9A  $I_{LED}$ ). When the ISET current is below 1.4µA (with a 428k $\Omega$  resistor, or 37.3mA  $I_{LED}$ ), a pin open fault is detected.

The part latches off if the ISET pin detects a short or open fault, regardless of whether FAULT is asserted. If there is an ISET pin short or open fault after start-up, FAULT is pulled low immediately. There is a 25ms to 40ms delay for FAULT assertion if a short or open fault is detected during start-up.

#### IREF

The IREF pin configures the device to buck or buck-boost mode. Afterward, it sets the current in the external NTC. After mode detection finishes, the IREF pin voltage (V<sub>IREF</sub>) is set to 0.57V with a 10.5% tolerance. Connect a resistor (R<sub>IREF</sub>) between IREF and AGND to get a current (I<sub>REF</sub>) equal to 0.57V / R<sub>IREF</sub>. This current is used as a reference current for the NTC's current source. The NTC current is 50 times that of I<sub>REF</sub> in buck mode, and 5 times that of I<sub>REF</sub> in buckboost mode. The IREF current is continuously monitored to detect if the IREF pin open and short to GND conditions occur.

If the IREF current exceeds  $90\mu$ A in buck mode (with a  $6.3k\Omega$  resistor) or  $900\mu$ A in buck-boost mode (with a  $0.63k\Omega$  resistor), a short-to-GND fault is detected. If the IREF current drops below  $3\mu$ A in buck mode (with a  $190k\Omega$  resistor) or below  $40\mu A$  in buck-boost mode (with a  $14.3k\Omega$  resistor), an open fault is detected.

The part latches off if a short or open fault is detected on IREF, regardless of whether FAULT asserts. If there is an IREF pin short or open fault after start-up, FAULT is pulled low immediately. There is a 25ms to 40ms delay for FAULT assertion if a short or open fault is detected during start-up.

#### **PWM** Dimming

When two-step dimming is inactive ( $R_{DUTY} = 4.87 k\Omega$ ), an external 100Hz to 2kHz PWM waveform can be applied to the EN/DIM pin. In external PWM dimming mode, the part stops switching when EN/DIM drops below 1.58V and  $I_{LED}$  is 0A. The part resumes normal operation with the nominal LED current, and when EN/DIM exceeds 1.67V. The average LED current is proportional to the PWM duty, and its accuracy can be up to ±15% when  $V_{IN} = 13.5V \pm 0.5V$  and  $T_J$  is between 25°C and 100°C.

Note that the EN/DIM high-voltage period should always be longer than 100µs. Otherwise, the part can stop switching, and an LED open fault may not be detected. To prevent the part from shutting down, the EN/DIM low-voltage period should not be longer than 10ms (EN turn-off delay).

### Two-Step Dimming

When VCC reaches its UVLO rising threshold (4.7V), two-step dimming detection is activated on the DUTY pin. A 45 $\mu$ A current source (I<sub>DUTY1</sub>) with a ±11% tolerance flows through the resistor between the DUTY pin and GND.

If the generated voltage ( $V_{DUTY}$ ) exceeds 3.347V, an open fault is detected, the part latches off, and FAULT asserts. If 0.302V <  $V_{DUTY}$  < 3.347V, the two-step dimming function is activated and the two-step dimming duty cycle is selected using Table 1. If  $V_{DUTY}$  is below 0.302V, the DUTY current source rises to 600µA ( $I_{DUTY2}$ ) with a ±8.75% tolerance to detect  $V_{DUTY}$  again.

If  $V_{DUTY} > 2.235V$  at this point, two-step dimming is disabled. Then the part can be turned on/off through EN/DIM, or can work in normal PWM dimming by applying a dimming signal at EN/DIM. If  $V_{DUTY} < 0.302V$ , a short fault is detected, the part latches off, and FAULT asserts. If  $0.302V < V_{DUTY} < 2.235V$ , two-step dimming is reactivated and the two-step dimming duty cycle is determined by  $V_{DUTY}$ . After this detection, the duty is not affected by changing  $V_{DUTY}$ , even if the DUTY pin is opened or shorted to GND.

Once two-step dimming is activated, PWM dimming is deactivated. The EN/DIM pin is used as the input pin to select no dimming or low dimming. When the EN/DIM pin is high, a 100% dimming duty cycle is selected. When EN/DIM is low, the dimming duty cycle is determined by  $I_{DUTY}$  and  $V_{DUTY}$ . The part can switch between dimming values in less than 20ms.

Configurable dimming is implemented as PWM dimming, but not analog dimming. When twostep dimming is activated at  $I_{DUTY1}$ , the dimming duty can be set between 15% and 10% with a 1% step. The corresponding typical  $V_{DUTY}$  is between 3.347V and 0.302V, with a 33% decrement for each step. When two-step dimming is activated at  $I_{DUTY2}$ , the dimming duty can be set between 9% and 5% with a 1% step. The corresponding  $V_{DUTY}$  is between 2.235V and 0.302V, with a 33% decrement for each step. Table 1 shows the relationship between the two-step dimming duty and  $V_{DUTY}$  window when considering different  $V_{DUTY}$  threshold tolerances.

| Two Stop Dim          | mina Dutu |         |       |       |         |       |       |

|-----------------------|-----------|---------|-------|-------|---------|-------|-------|

| Two-Step Dimming Duty |           | VDUTY_H |       |       | VDUTY_L |       |       |

| IDUTY1                | IDUTY2    | Min     | Тур   | Max   | Min     | Тур   | Max   |

| Latch                 | No two-   | 4.018   | 4.100 | 4.182 | 3.280   | 3.347 | 3.414 |

| 15%                   | step dim. | 3.280   | 3.347 | 3.414 | 2.190   | 2.235 | 2.279 |

| 14%                   | 9%        | 2.190   | 2.235 | 2.279 | 1.460   | 1.489 | 1.519 |

| 13%                   | 8%        | 1.460   | 1.489 | 1.519 | 0.969   | 0.989 | 1.009 |

| 12%                   | 7%        | 0.969   | 0.989 | 1.009 | 0.634   | 0.653 | 0.673 |

| 11%                   | 6%        | 0.634   | 0.653 | 0.673 | 0.407   | 0.428 | 0.449 |

| 10%                   | 5%        | 0.407   | 0.428 | 0.449 | 0.28    | 0.302 | 0.33  |

| To IDUTY2             | Latch     | 0.28    | 0.302 | 0.33  | -       |       |       |

Table 1: Two-Step Dimming Duty vs. VDUTY Window

To prevent errors while selecting the two-step dimming duty, ensure that the  $V_{DUTY}$  window is between the minimum  $V_{DUTY_H}$  and maximum  $V_{DUTY_L}$  values when selecting  $R_{DUTY}$ . An E96 series resistor is recommend to select precise dimming values. Table 2 shows the proposed  $R_{DUTY}$  in E96 series for different two-step dimming duties, while considering the  $I_{DUTY}$ tolerance and a ±3% resistor tolerance

If  $V_{CC}$  drops below 4.05V before two-step dimming detection finishes, two-step dimming detection stops and does not restart until  $V_{CC}$  returns to 4.7V. The two-step dimming signal, together with the two-step dimming duty, is latched once detection finishes. It only can be reset by VCC UVLO, and not an EN shutdown.

The two-step dimming frequency is typically 500Hz, within  $\pm 50$ Hz.

#### Table 2: Two-Step Dimming Duty vs. RDUTY

| Two-Step Dimming Duty                         | <b>R</b> duty <b>(Ω)</b> |

|-----------------------------------------------|--------------------------|

| 15%                                           | 61900                    |

| 14%                                           | 41200                    |

| 13%                                           | 27400                    |

| 12%                                           | 18200                    |

| 11%                                           | 12100                    |

| 10%                                           | 7870                     |

| PWM dimming (two-step<br>dimming inactivated) | 4870                     |

| 9%                                            | 3090                     |

| 8%                                            | 2050                     |

| 7%                                            | 1370                     |

| 6%                                            | 887                      |

| 5%                                            | 576                      |

#### Under-Voltage Lockout (UVLO)

Under-voltage lockout (UVLO) protects the chip from operating at an insufficient supply voltage. Both ( $V_{IN} - V_{INGND}$ ) and  $V_{CC}$  have UVLO thresholds. The  $V_{IN} - V_{INGND}$  UVLO rising threshold is 6V, with a 1.1V hysteresis. The  $V_{CC}$ UVLO rising threshold is 4.7V, with a 0.65V hysteresis. Neither of these UVLOs triggers a fault.

#### Fault Detection and Indication

The MP7200 has fault indication. The FAULT pin is the open drain of a MOSFET. FAULT is internally pulled up to VIN through a  $300k\Omega$ resistor, and pulled down with a  $4M\Omega$  resistor connected to INGND. The FAULT pin is pulled high during normal operation. It pulls low to indicate a fault status if any of the following events occur:

- An LED short or open fault

- Thermal shutdown

- False mode detection

- Over-current protection (OCP)

An ISET or IREF pin short/open fault during (or after) start-up can assert FAULT. An IDUTY pin short/open fault can only assert FAULT if it is detected before start-up. The MP7200 senses the output by monitoring the average SW voltage in buck mode, or the INGND voltage in buckboost mode. If LED+ shorts to LED- or PGND, V<sub>OUT</sub> drops below its under-voltage (UV) threshold, a short-circuit is detected, and FAULT asserts. If an LED open or output over-voltage (OV) fault is detected in buck-boost mode, or the high-side MOSFET current is detected in buck mode, then FAULT asserts. The low-current threshold is 60mA when the LED current is set below 600mA, or 120mA when the LED current is set above 600mA.

To prevent the part from latching due to cold crank conditions while in buck mode, low-current detection is disabled when  $V_{IN}$  drops below 7.5V. If LED+ (INGND) shorts to the battery,  $V_{IN}$  -  $V_{INGND}$  falls below its UV threshold in buck-boost mode, and FAULT cannot assert. If LED- (PGND) shorts to INGND,  $V_{INGND}$  drops below its UV threshold and FAULT asserts. If an LED open fault occurs,  $V_{INGND}$  exceeds its OV threshold and FAULT asserts.

At high temperatures, the part operates with a reduced current level. The device only stops if the internal temperature reaches the 170°C over-temperature (OTP) threshold and FAULT asserts. If any fault occurs, the part stops switching, the FAULT output asserts in 20 $\mu$ s, and then the part latches. While latched, V<sub>CC</sub> is still present, and the part's consumption current is <2mA. FAULT can be reset by V<sub>CC</sub> UVLO. EN shutdown (EN going low longer than 25ms) can also reset FAULT if two-step dimming is not selected.

At start-up, the FAULT pin is not activated, and remains inactive for at least 25ms. FAULT is active within 40ms. In PWM dimming mode, the FAULT counter works only when the dimming signal is high, which makes the inactive time 30ms/PWM dimming duty. This avoids any false functions from the system when multiple parts have connected FAULT pins and share the same EN signal. Individual parts are self-protected and latch off immediately if a fault condition is detected, regardless of whether FAULT asserts.

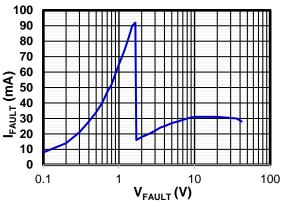

The FAULT pin can withstand a 30mA current and protects itself if the pin shorts to a high voltage (e.g.  $V_{BATT}$ ). If FAULT is low (<1.6V), the FAULT sink current increases to enhance the pull-down capability. Figure 5 shows the detailed FAULT sink current when the FAULT pin is pulled low at different voltages.

Figure 5: FAULT Sink Current vs. FAULT Voltage

In PWM dimming and two-step dimming, fault conditions may not be detected when the dimming on time is below 100µs. Ensure that the dimming on time exceeds 100µs for normal fault detection operation. Table 3 shows the fault detection options.

| Detection                  |                                                                                                                                                      |                                                                         |  |  |  |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|--|

| Fault Conditions           | Buck Mode                                                                                                                                            | Buck-Boost Mode                                                         |  |  |  |

| LED+ short to LED-         | V <sub>OUT</sub> UV (V <sub>OUT</sub> < 1.1V)                                                                                                        | INGND UV ( $V_{INGND}$ - $V_{PGND}$ < 1.35V) <sup>(10)</sup>            |  |  |  |

| LED+ short to PGND         | Vout UV (Vout < 1.1V)                                                                                                                                | INGND UV (VINGND - VPGND < 1.35V)                                       |  |  |  |

| LED+ short to INGND        | V <sub>OUT</sub> UV (V <sub>OUT</sub> < 1.1V)                                                                                                        | Normal condition                                                        |  |  |  |

| LED+ short to battery      | Low LED current<br>(IHS < 60mA when ILED_SETTING < 600mA)<br>(IHS < 120mA when ILED_SETTING > 600mA)                                                 | Cannot assert FAULT due to<br>VIN - VINGND UVLO                         |  |  |  |