# Ideal Diode for Solar Panel Bypass and **General OR-ing Circuits**

#### DESCRIPTION

The MP6914 is an ideal diode that integrates a 30V,  $5.3m\Omega$  power MOSFET to replace bypass diodes in photovoltaic panel. The power loss can be significantly reduced with the MP6914 due to its low voltage drop and reverse leakage current. The part is available with SOIC8-EP package.

#### **FEATURES**

- Integrated 5.3mΩ 30V Power Switch

- Very low reverse leakage current

- Rugged design for long lifetime

- Available in SOIC8-EP package

#### **APPLICATIONS**

- Bypass diode in photovoltaic panels

- **OR-ing circuit**

All MPS parts are lead-free, halogen free, and adhere to the RoHS directive. For MPS green status, please visit MPS website under Quality Assurance.

"MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

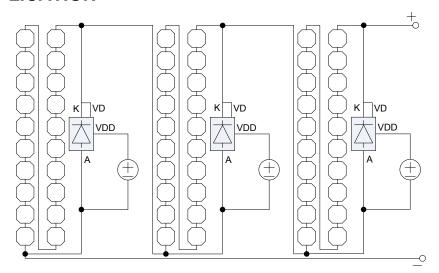

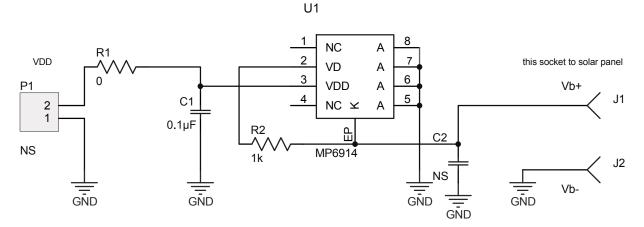

#### TYPICAL APPLICATION

#### ORDERING INFORMATION

| Part Number* | Package | Top Marking |

|--------------|---------|-------------|

| MP6914DN     | SOIC8E  | MP6914      |

\* For Tape & Reel, add suffix –Z (e.g. MP6914DN–Z);

For RoHS, compliant packaging, add suffix -LF (e.g. MP6914DN-LF-Z).

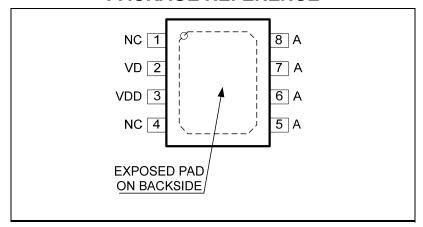

### **PACKAGE REFERENCE**

# **ABSOLUTE MAXIMUM RATINGS (1)**

| Cathode to Anode             |                              |

|------------------------------|------------------------------|

| Continuous Power Dissipation | $(T_A = +25^{\circ}C)^{(2)}$ |

|                              |                              |

| Junction Temperature         | 150°C                        |

| Lead Temperature (Solder)    | 260°C                        |

| Storage Temperature          | -55°C to +150°C              |

# Recommended Operation Conditions (3)

| Thermal Resistance (4) | $oldsymbol{	heta}_{JA}$ | $	heta_{JC}$ |       |

|------------------------|-------------------------|--------------|-------|

| SOIC8E                 | 50                      | 10           | .°C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub>(MAX), the junction-toambient thermal resistance  $\theta_{\text{JA}},$  and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at ambient temperature calculated is  $D(MAX)=(T_J(MAX)-T_A)/\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

$T_A$ = +25°C, unless otherwise noted.

| Parameter                                        | Symbol              | Conditions                                                          | Min | Тур  | Max | Units |

|--------------------------------------------------|---------------------|---------------------------------------------------------------------|-----|------|-----|-------|

| VDD Voltage Range                                | $V_{DD}$            |                                                                     | 6   |      | 24  | V     |

| VDD UVLO Rising                                  | V <sub>DD</sub> _rs |                                                                     | 3.4 | 3.8  | 4.2 | V     |

| VDD UVLO Hysteresis                              | V <sub>DD</sub> _hs |                                                                     | 0   | 0.6  | 1   | V     |

| Operating Current                                | $I_{op}$            | $V_{DD}$ =12V, $V_{AK}$ =0.5V                                       |     | 1    | 2   | mA    |

| Quiescent Current                                | $I_{q}$             | $V_{DD}$ =12V, $V_{AK}$ =0V                                         | 60  | 90   | 120 | μΑ    |

| A-K Forward Voltage                              | $V_{fwd}$           | I <sub>AK</sub> =1A                                                 | 20  | 30   | 40  | mV    |

| A-K Forward Voltage                              | $V_{fwd}$           | I <sub>AK</sub> =10A, T <sub>j</sub> =25°C                          |     | 53   |     | mV    |

| A-KT of ward voltage                             | <b>v</b> fwd        | I <sub>AK</sub> =10A, T <sub>j</sub> =75°C                          |     | 61   |     | mV    |

| Turn-off Total Delay                             | $T_{Doff}$          |                                                                     | 2   | 4    | 6   | μs    |

| POWER SWITCH SECTION                             |                     |                                                                     |     |      |     |       |

| Drain-Source Breakdown<br>Voltage <sup>(5)</sup> | $V_{(BR)DSS}$       | V <sub>GS</sub> =0V, I <sub>KA</sub> =250μA                         | 30  | 32   |     | V     |

| Gate-Threshold Voltage                           | $V_{GS\_th}$        | $V_{DS}=V_{GS}$ , $I_{kA}=250\mu A$                                 |     | 1.9  |     | V     |

| AK Turn-on Threshold                             | $V_{AK\_ON}$        | V <sub>DD</sub> =12V                                                |     | 125  | 250 | mV    |

| Gate-Body Leakage                                | $I_{GSS}$           | V <sub>DS</sub> =0V, V <sub>GS</sub> =±12V                          |     | ±100 |     | nA    |

| Leakage Current                                  | I <sub>LK</sub>     | From K to A, V <sub>DD</sub> =0V                                    |     |      | 1   | μΑ    |

| Drain-Source On-State                            | В                   | V <sub>GS</sub> =10V,, I <sub>D</sub> =10A,<br>T <sub>j</sub> =25°C |     | 5.3  |     | mΩ    |

| Resistance                                       | $R_{DS(ON)}$        | V <sub>GS</sub> =10V,, I <sub>D</sub> =10A,<br>T <sub>j</sub> =75°C |     | 6.1  |     | mΩ    |

| Input Capacitance                                | C <sub>iss</sub>    |                                                                     |     | 2800 |     | pF    |

| Output Capacitance                               | C <sub>oss</sub>    | V <sub>DS</sub> =30V, f=1MHz                                        |     | 450  |     | pF    |

| Reverse Transfer Capacitance                     | C <sub>rss</sub>    |                                                                     |     | 300  |     | pF    |

| <b>Body Diode Characteristics</b>                |                     |                                                                     |     |      |     |       |

| Diode Forward Voltage                            | $V_{AK}$            | V <sub>DD</sub> =2.5V, I <sub>AK</sub> =1A                          |     | 0.7  | 0.8 | V     |

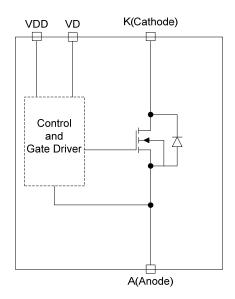

<sup>5)</sup> D is K, S is A, refer to "BLOCK DIAGRAM"

# **PIN FUNCTIONS**

| Pin# | Name | Description                                 |

|------|------|---------------------------------------------|

| 1,4  | NC   | No Connection                               |

| 2    | VD   | Drain voltage sense, need to connect K pin. |

| 3    | VDD  | Supply Voltage, reference to anode.         |

| 5-8  | Α    | FET Source, also used as diode anode        |

| EP   | K    | FET Drain, also used as diode cathode       |

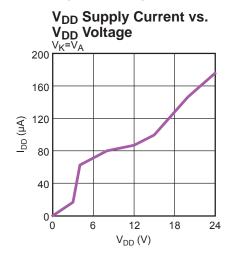

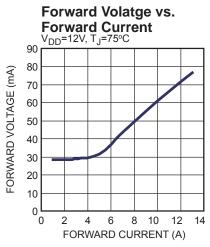

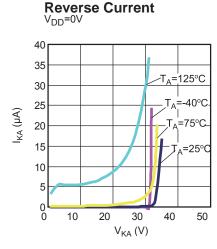

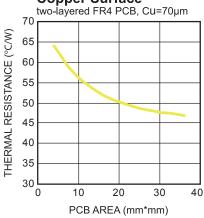

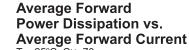

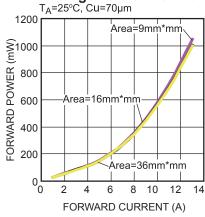

### TYPICAL PERFORMANCE CHARACTERISTICS

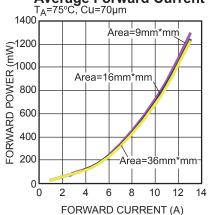

VDD=12V, T<sub>A</sub>=+25°C, tested on two-layered FR4 PCB with 70um Cu, otherwise noted

Thermal Resistance Junction-to-Ambient vs. Copper Surface

Average Forward

Power Dissipation vs.

Average Forward Current

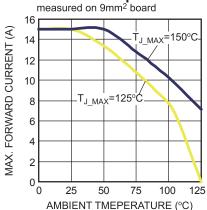

# Maximum Forward Current vs. Ambient Temperature

# **BLOCK DIAGRAM**

Figure 1—Function Block Diagram

#### **OPERATION**

Photovoltaic cells can not generate power in some conditions, such as clouds or fog. Due to the mismatch currents betweens the series connected cells, the shaded cells will work like a load while the good cells still produce power. They dissipate power instead of generating power and cause hot spot. To protect the PV from the damage due to hot spot, bypass diodes in PV junction box are commonly used to allow the current pass around the shaded PV cells. MP6914 is comprised of an internal power MOSFET and control circuits. It need an external power for VDD and behaves like a diode. Compared with a bypass diode, MP6914 has significantly low forward voltage drop and a very low reverse leakage current.

#### **Turn-on Phase**

When current goes through the internal body diode, the body diode voltage drop from A to K (>500mV) is much larger than the turn-on threshold (125mV) of internal control circuitry, which leads to the turn on of the internal MOSFET. The control circuitry will regulate the  $V_{AK}$  at about 30mV by controlling the gate driver voltage of the internal MOSFET.

#### **Turn-off Phase**

When the shaded PV cells start to generate power (this means the voltage which drops across A-K is smaller than 30mV), the control circuitry stops working and the internal MOSFET is turned off.

#### **APPLICATION INFORMATION**

#### **Loss Calculation**

The MP6914 provide solutions for photovoltaic applications, designed to increase system efficiency by implementing a bypass function through a  $5.3 \text{m}\Omega$ power MOSFET transistor instead of a conventional Schottky diode.

MP6914 should be connected in parallel to the cell string which is intended to be protected. In normal work this string produce enery with a voltage  $V_{\text{KA}}$ . In normal work MP6914 comsumes a power determined by:

$$P_{LOSS}(W) = V_{KA}(V) * I_{KA}(\mu A) * 10^{-6}$$

Where  $I_{KA}$  Is the reverse current (see Figure 3), typically  $<3\mu A$ , so  $P_{LOSS}$  is very small.

When this cell string is shaded to act as a load of other cells, MP6914 will turn on the internal MOSFET to prevent hot-spot issue. Now  $I_{KA}$  is the negative forward current  $I_F$  (typically 0~10A), equal to current in the real load of PV cells.  $V_{KA}$  is the negative forward voltage  $V_F$  .if  $I_F$  is below 5A,  $V_F$  is clamped to about 30mV, otherwise can be found in Figure "Forward Voltage vs. Forward Current". Then substituting  $V_F$  and  $I_F$  into previous equation can calculate out the loss in this case.

$P_{LOSS}$  (W),  $\theta_{JA}$  (45-65°C/W), ambient temperature  $T_a$  (°C) and maximum allowed junction temperature (150°C) decide the maximum  $I_F$  (A). In common case, this relation can be expressed:

$$I_F = (150 - T_a)/(\theta_{JA} * V_F * 0.001)$$

Where  $V_F$  in mV, and can be found in the anterior Figure "Forward Voltage vs. Forward Current", and the maximum  $I_F$  is sketched in Figure "Maximum Forward Current vs. Ambient Temperature".

#### **Component Selection**

A small capacitor is needed to keep a clean voltage for  $V_{DD}$  pin,  $0.1\mu F$  is enough. A resistor of  $1k\Omega$  is needed between  $V_D$  and K pins in order to prevent noise from PV cells line. This resistor doesn't consume power.

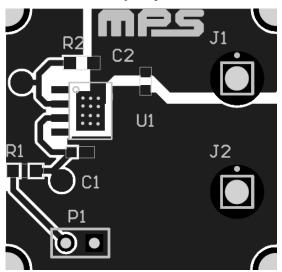

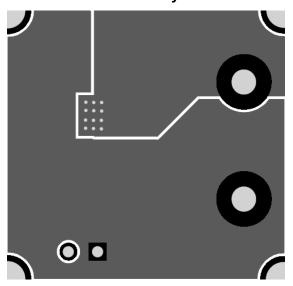

### **PCB Layout Guide**

As usually the current flowing into A pin through K pin Is big, the copper plane connected to these pins is recommended as big as possible, as shown in the figures below:

Top Layer

**Bottom Layer**

© 2015 MPS. All Rights Reserved.

The  $V_{DD}$  decoupling capacitor should be closed to  $V_{DD}$  and A pins (C1 in the upper figure). The  $V_D$  resistor (R2 in the upper figure) connects a joint close to K pin and keeps the  $V_D$  trace short. MP6914DN-00A is a good example.

And many vias from top layer through bottom layer needed for current conducting and thermal radiating.

#### **Design Example**

Below is a design example following the application guidelines for the specifications:

**Table 1: Design Example**

| V <sub>DD</sub> (V)                  | 6-24    |

|--------------------------------------|---------|

| V <sub>b</sub> (V)                   | -0.8-30 |

| I <sub>b</sub> (I <sub>AK</sub> : A) | 0-10    |

The detailed application schematic is shown in figure 2. The typical performance and circuit waveforms have been shown in the Typical Performance Characteristics section. For more device applications, please refer to the related Evaluation Board Datasheets.

### TYPICAL APPLICATION CIRCUITS

Figure 2—24V/10A Application Circuit

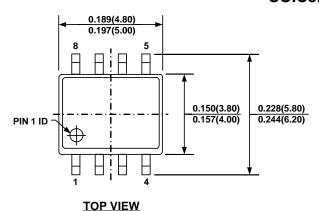

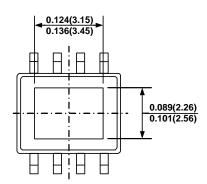

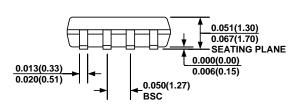

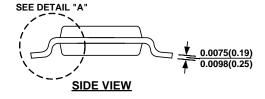

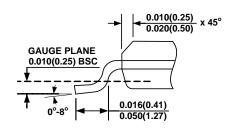

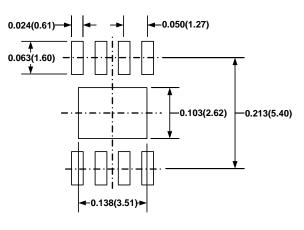

#### PACKAGE INFORMATION

#### SOIC8E

**BOTTOM VIEW**

#### **FRONT VIEW**

RECOMMENDED LAND PATTERN

**DETAIL "A"**

#### NOTE:

- 1) CONTROL DIMENSION IS IN INCHES. DIMENSION IN BRACKET IS IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.004" INCHES MAX.

- 5) DRAWING CONFORMS TO JEDEC MS-012, VARIATION BA.

- 6) DRAWING IS NOT TO SCALE.

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Monolithic Power Systems (MPS):

MP6914DN-LF MP6914DN-LF-Z MP6914DN-LF-P