Peak Current Mode Boost PWM Controller with Programmable Frequency, External Soft Start Light Load Operation, and SOIC8 Package

The Future of Analog IC Technology

## DESCRIPTION

The MP3910A is a Peak Current Mode PWM controller that can drive an external MOSFET capable of handling more than 10A current. It has a typical operational current of 400µA and can accommodate flyback, boost for non-isolated and isolated applications.

Current mode control provides inherently simple loop compensation and cycle-by-cycle current limit. Under-voltage lockout, soft-start and slope compensation are all provided to minimize the external component count.

While designed for Flyback applications, the MP3910A can also be used for other topologies including Boost, Forward and Sepic. The 1A gate driver minimizes the power loss of the external MOSFET while allowing the use of a wide variety of standard threshold devices. Additionally, MP3910A has pulse skipping mode function that improves the efficiency with light load or no load. It also provides hiccup protection for OLP, OVP and SCP condition.

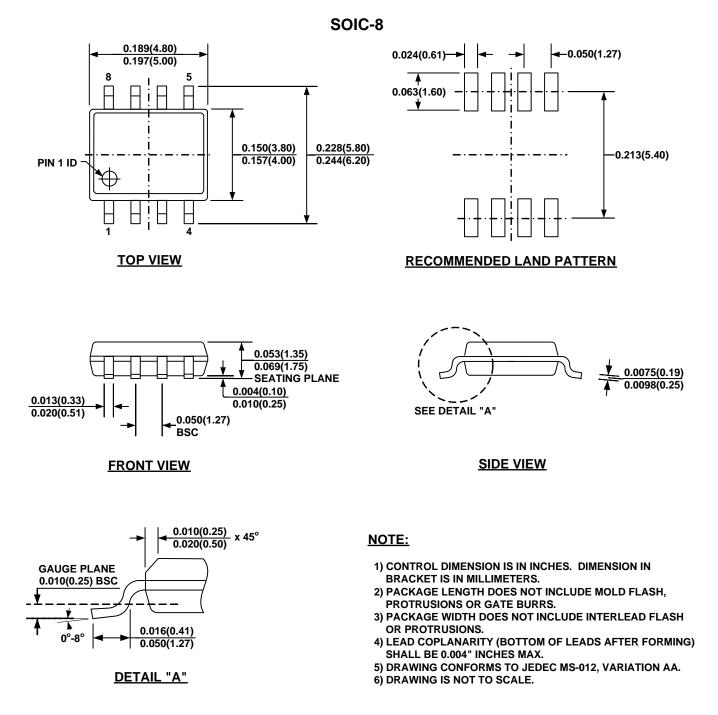

The MP3910A is available in SOIC8 package.

## FEATURES

- 9V to 14V Supply Voltage Range

- 1A MOSFET Gate Driver

- External Soft-Start

- Pulse Skipping Operation with Light Load

- Programmable Switching Frequency (30kHz-to-400kHz)

- Cycle-by-Cycle Current Limit

- Over Voltage Protection

- Short Circuit Protection

- Over Temperature Protection

- Available in SOIC8 Package

## APPLICATIONS

- Telecom Isolated Power Supplies

- Brick Modules

- Off-line Controller

- General Step Up Applications

- PoE Powered Devices

All MPS parts are lead-free, halogen free, and adhere to the RoHS directive. For MPS green status, please visit MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

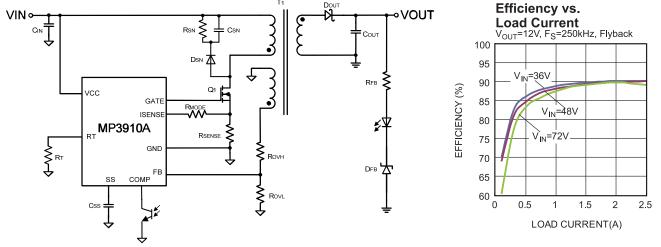

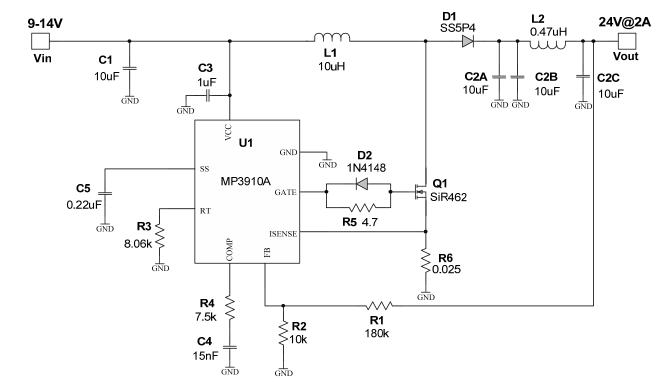

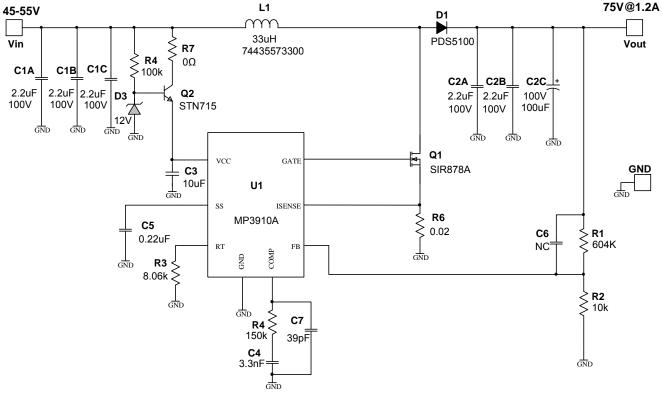

# TYPICAL APPLICATION

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2017 MPS. All Rights Reserved.

### **ORDERING INFORMATION**

| Part Number* | Package | Top Marking |

|--------------|---------|-------------|

| MP3910AGS    | SOIC-8  | See Below   |

\* For Tape & Reel, add suffix –Z (e.g. MP3910AGS–Z);

## **TOP MARKING**

## MP3910A LLLLLLLL MPSYWW

MP3910A: product code of MP3910AGS; LLLLLLL: lot number; MPS: MPS prefix; Y: year code; WW: week code:

## **PACKAGE REFERENCE**

## ABSOLUTE MAXIMUM RATINGS (1)

| VCC, GATE to GND0.3V to 16<br>All Other Pins0.3V to 6<br>Continuous Power Dissipation $(T_A = +25^{\circ}C)^{(2)}$ |   |

|--------------------------------------------------------------------------------------------------------------------|---|

| 1.38W                                                                                                              | ٧ |

| Maximum Operating Frequency 500kHz                                                                                 |   |

| Storage Temperature55°C to +150°C                                                                                  | С |

| Junction Temperature150°C                                                                                          | 2 |

| Lead Temperature                                                                                                   | 2 |

| $\square$                                                                                                          |   |

### Recommended Operating Conditions (\*)

| Supply Voltage V <sub>CC</sub>             | 9V to 14V      |

|--------------------------------------------|----------------|

| Operating Junction Temp. (T <sub>J</sub> ) | 40°C to +125°C |

####

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-to-ambient thermal resistance θ<sub>JA</sub>, and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX)-T<sub>A</sub>)/θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

## **ELECTRICAL CHARACTERISTICS**

$V_{CC}$  = 12V,  $T_J$  = -40°C to125°C (typical values are tested at 25°C), unless otherwise noted.

| Parameters                                                 | Symbol                | Condition                                                                            | Min | Тур  | Max  | Units |

|------------------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------|-----|------|------|-------|

| Input Supply Management                                    | 2                     |                                                                                      |     |      |      |       |

| VCC UVLO Threshold                                         | V <sub>UVLO</sub>     | Rising edge                                                                          | 7.4 | 8    | 8.7  | V     |

| VCC UVLO Hysteresis                                        | V <sub>UVLO HYS</sub> |                                                                                      |     | 650  |      | mV    |

| Quiescent Current                                          | l <sub>Q</sub>        | V <sub>FB</sub> =1.35V                                                               |     | 400  | 520  | μA    |

| Driving Signal                                             |                       |                                                                                      |     |      |      |       |

| Gate Driver Impedance<br>(Sourcing)                        |                       | I <sub>GATE</sub> =-20mA                                                             |     | 4.1  |      | Ω     |

| Gate Driver Impedance<br>(Sinking)                         |                       | I <sub>GATE</sub> =20mA                                                              |     | 2    |      | Ω     |

| Error Amplifier                                            |                       |                                                                                      |     |      |      |       |

| Error Amplifier<br>Transconductance                        | G <sub>EA</sub>       | $V_{FB}$ is +-50mV from FB Reference, $V_{COMP}$ =1.5V                               |     | 0.56 |      | mA/V  |

| Maximum Amplifier Output<br>Current                        |                       | Sourcing or Sinking                                                                  |     | 75   |      | μA    |

| COMP High Voltage                                          |                       | I <sub>SENSE</sub> =0V, V <sub>FB</sub> =1V<br>I <sub>SENSE</sub> =1V, Floating COMP |     | 2.4  |      | V     |

| Current Sense                                              | 1                     |                                                                                      |     |      |      |       |

| Current Comparator<br>Leading Edge Blanking <sup>(7)</sup> | T <sub>LEB</sub>      |                                                                                      |     | 214  | 398  | ns    |

| ISENSE Limit                                               | Vlimit                | T <sub>J</sub> =25°C                                                                 | 163 | 185  | 206  | mV    |

| SCP Limit <sup>(5)</sup>                                   | V <sub>SCP</sub>      |                                                                                      |     | 350  |      | mV    |

| Current Sense Amplifier<br>Gain                            | G <sub>SENSE</sub>    | $\Delta V_{COMP} / \Delta V_{ISENSE}$                                                |     | 2.7  |      | V/V   |

| ISENSE Bias Current                                        | I <sub>SENSE</sub>    | TJ=25°C                                                                              |     | 0.01 | 0.15 | μA    |

| PWM                                                        | 02.102                |                                                                                      |     |      |      |       |

| $V_{COMP}$ (Skipping Mode) <sup>(5)</sup>                  |                       | Pulse skipping mode operation threshold, V(comp)                                     |     | 0.95 |      | V     |

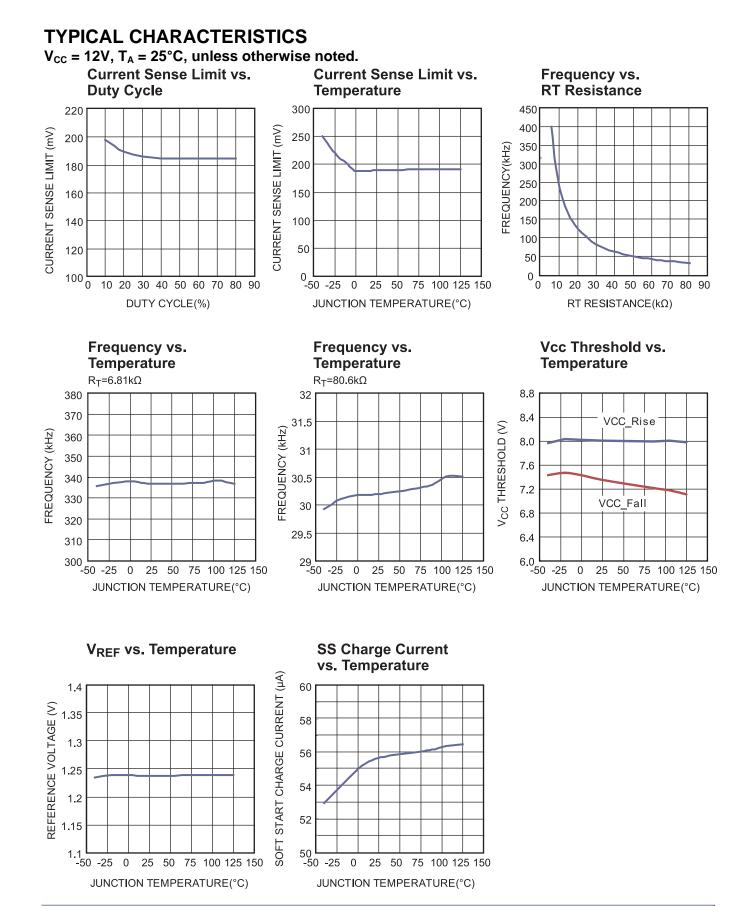

| 0 11 1 5                                                   | _                     | $R_{T}=6.81k\Omega$                                                                  | 308 | 337  | 363  | kHz   |

| Switching Frequency                                        | F <sub>sw</sub>       | R <sub>T</sub> =80.6kΩ                                                               | 25  | 30   | 35   | kHz   |

| Minimum ON Time                                            | T <sub>ON-MIN</sub>   |                                                                                      |     | 214  | 398  | ns    |

| Maximum Duty Cycle                                         | D <sub>MAX</sub>      | R <sub>T</sub> =6.81kΩ                                                               | 93  | 95   |      | %     |

| Soft-start <sup>(6)</sup>                                  |                       |                                                                                      |     |      |      |       |

| Charge Current                                             | I <sub>SS</sub>       |                                                                                      |     | 54   |      | μA    |

| Over Load Detection<br>Discharge Current                   |                       |                                                                                      |     | 17.8 |      | μA    |

| Discharge Current During<br>Protection                     |                       |                                                                                      |     | 1.66 |      | μA    |

| Charged Threshold Voltage                                  |                       |                                                                                      |     | 3.65 |      | V     |

| Over Load Shutdown<br>Threshold Voltage                    |                       |                                                                                      |     | 2.9  |      | V     |

| Protection Reset Threshold Voltage                         |                       |                                                                                      |     | 0.2  |      | V     |

## **ELECTRICAL CHARACTERISTICS** (continued)

$V_{cc} = 12V$ ,  $T_{J} = -40^{\circ}C$  to  $125^{\circ}C$  (typical at a temperature range of  $25^{\circ}C$ ), unless otherwise noted.

| Parameters                            | Symbol                      | Condition                                      | Min   | Тур   | Max   | Units |

|---------------------------------------|-----------------------------|------------------------------------------------|-------|-------|-------|-------|

| Voltage Feedback Managen              | Voltage Feedback Management |                                                |       |       |       |       |

| Mode Detection Voltage <sup>(5)</sup> |                             |                                                |       | 185   |       | mV    |

| Mode Detection Current <sup>(5)</sup> |                             |                                                |       | 55    |       | μA    |

| Mode Detection Time <sup>(5)</sup>    |                             |                                                |       | 180   |       | μs    |

|                                       | V <sub>FB</sub>             | T <sub>J</sub> =25°C                           | 1.222 | 1.237 | 1.252 | V     |

| FB Reference Voltage                  |                             | T <sub>J</sub> =-40°C to 125°C                 | 1.211 | 1.237 | 1.258 | V     |

| FB Bias Current                       | I <sub>FB</sub>             | V <sub>FB</sub> =1.237V, T <sub>J</sub> = 25°C |       | 0.01  | 0.15  | μA    |

| OVP Reference Level                   | V <sub>OVP</sub>            |                                                | 1.391 | 1.438 | 1.479 | V     |

| COMP Pull up Resistor                 |                             |                                                |       | 14.4  |       | kΩ    |

| COMP Pull up Voltage <sup>(5)</sup>   |                             |                                                |       | 3.6   |       | V     |

| Thermal Protection                    |                             |                                                |       |       |       |       |

| Thermal Shutdown <sup>(5)</sup>       | T <sub>SD</sub>             |                                                |       | 160   |       | °C    |

| Thermal Hysteresis <sup>(5)</sup>     |                             |                                                |       | 20    |       | °C    |

Notes:

Guaranteed by engineering sample characterization.

Refer to "soft-start section" for detail function of discharge current and threshold voltage.

7) It is same as Minimum on Time.

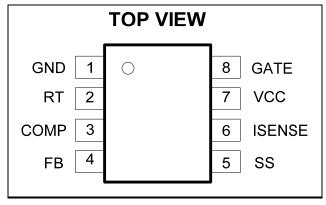

## **PIN FUNCTIONS**

| Pin # | Name   | Description                                                                                                                                                                                                                                                                                                                                                             |

|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | GND    | Power ground pin which is gate driver return.                                                                                                                                                                                                                                                                                                                           |

| 2     | RT     | Switching frequency set pin. Connect a resistor from this pin to GND to set the switching frequency (30kHz~400kHz).                                                                                                                                                                                                                                                     |

| 3     | COMP   | Feedback pin for isolated solution. Error amplifier output pin for un-isolated solution.                                                                                                                                                                                                                                                                                |

| 4     | FB     | Feedback and OVP monitor pin with respective internal reference voltage for un-<br>isolated solution. OVP monitor pin for isolated solution. Connected to GND if not used<br>in isolated solution.                                                                                                                                                                      |

| 5     | SS     | Soft-start pin. Connect one capacitor between this pin and GND to control the duration of COMP voltage rising. It determines both the soft-start current, and hiccup protection delay.                                                                                                                                                                                  |

| 6     | ISENSE | Current Sense and application mode (isolated/un-isolated) setting pin. At start-up, this pin will output one current signal and sense the voltage for mode setting detection. During normal operation, this pin will sense the voltage across sense resistor for current mode control, as well as cycle-by-cycle current limit, over load and short circuit protection. |

| 7     | VCC    | IC Input supply. Connect a bypass capacitor from this pin to GND. VCC voltage should be lower than 14V in application.                                                                                                                                                                                                                                                  |

| 8     | GATE   | This pin drives the external N-channel power MOSFET device.                                                                                                                                                                                                                                                                                                             |

#### MP3910A Rev. 1.11

2/14/2017

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2017 MPS. All Rights Reserved.

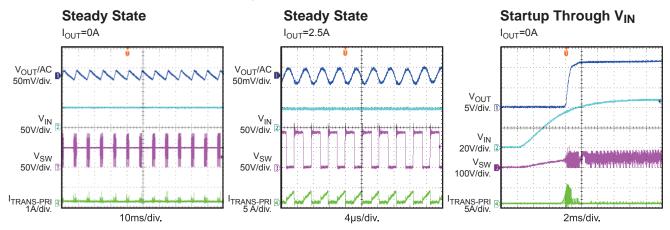

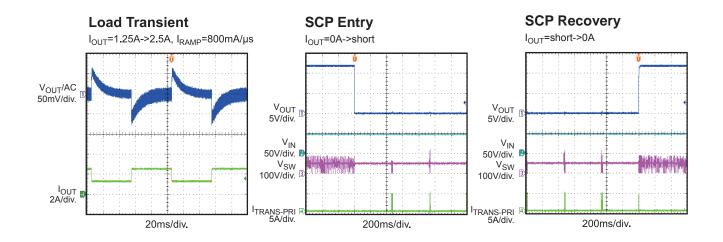

## **TYPICAL PERFORMANCE CHARACTERISTICS**

VOUT

VIN

V<sub>SW</sub>

5V/div.

20V/div.

100V/div.

I<sub>TRANS-PRI</sub> 5A/div.

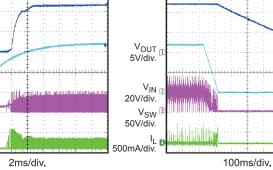

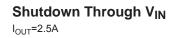

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

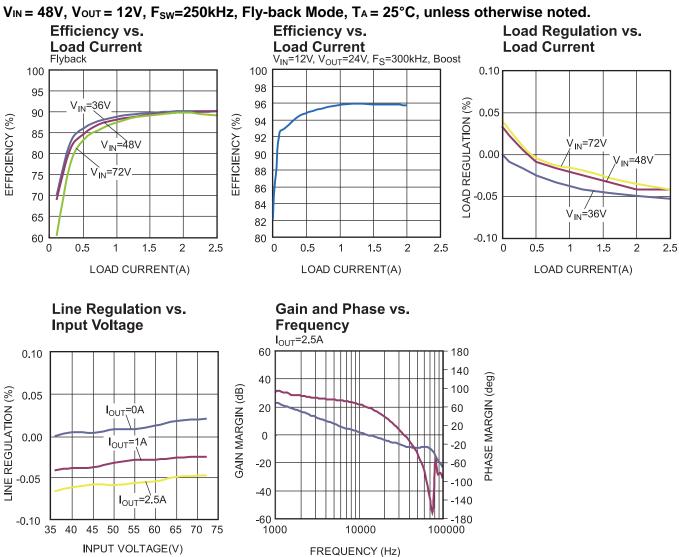

$V_{IN} = 48V$ ,  $V_{OUT} = 12V$ ,  $F_{sw} = 250$ kHz, Fly-back Mode,  $T_A = 25^{\circ}$ C, unless otherwise noted.

Shutdown Through VIN

I<sub>OUT</sub>=0.01A

Startup Through V<sub>IN</sub> I<sub>OUT</sub>=2.5A

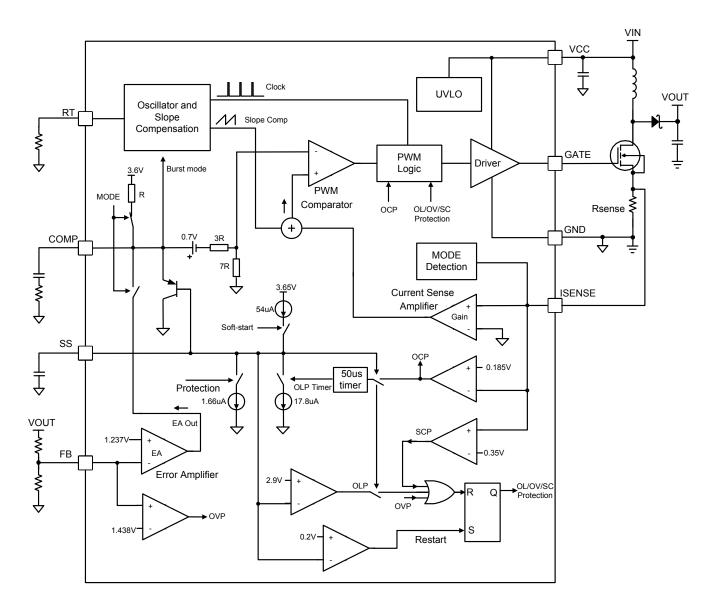

## FUNCTION BLOCK DIAGRAM

Figure 1: Functional Block Diagram

## **OPERATION**

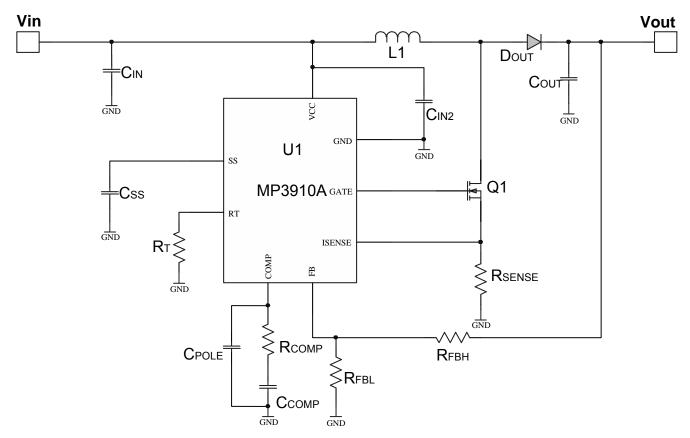

The MP3910A uses a programmable frequency, peak current mode architecture to regulate the feedback voltage. The operation of the MP3910A can be understood with the block diagram of Figure 1.

#### **PWM Operation**

At the beginning of each cycle the external Nchannel MOSFET is turned on, forcing the current in the inductor to increase. The current through the FET can be sensed and when the sum voltage of amplified ISENSE signal and slope signal rises above the voltage set by the COMP pin, the external FET is turned off. The inductor current then flows to the output capacitor through the schottky diode. The inductor current is controlled by the COMP voltage, which itself is controlled by the output voltage. Thus the output voltage controls the inductor current to satisfy the load. This current mode architecture improves transient response and control loop stability over voltage mode architecture.

#### **Pulse Skipping Mode**

At light load condition, the MP3910A goes into pulse skipping mode to improve light load efficiency. Pulse skipping decision is based on its internal COMP voltage. If COMP is lower than the internal sleep threshold with typical 0.95V, a PAUSE command is generated to block the turn-on clock pulse so the power MOSFET is turned off immediately, saving gate driving and switching losses. This PAUSE command also puts the whole chip into sleep mode, consuming very low guiescent current to further improve the light load efficiency. The gate driver output remains low until COMP voltage is higher than the sleep threshold, then PAUSE signal is reset so the chip is back into normal PWM operation.

#### **VCC Power Supply**

MP3910A operates with supply voltage from 9V to 14V on VCC pin. VCC UVLO's rising threshold is 8V with a hysteresis of 650mV. When the voltage at VCC pin crosses the VCC UVLO, the controller is enabled and all the internal circuitry is powered by VCC source. VCC voltage should be lower than 14V. For high input voltage application, one external

voltage clamp circuit is needed to regulate VCC voltage in appropriate range.

#### Feedback Loop Setting

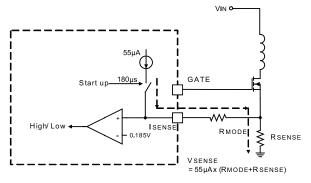

To be coincident for different design in isolated and un-isolated application, MP3910A can feedback the output signal through either of FB pin or COMP pin by different setting on ISENSE pin.

For un-isolated application such as boost mode, MP3910A integrates one error amplifier which can amplify the output error signal from FB pin, COMP pin needs one RC network for compensation. For isolated application such as fly-back mode, the feedback signal from optocoupler has been amplified by secondary circuitry, directly connect the signal to COMP pin will make loop compensation much easier by eliminating the primary side amplifier.

The different feedback loop can be set by different ISENSE pin connection. At the beginning of part enabled, ISENSE pin will output 180us current pulse with typical value of 55uA. as showed in Figure 2, if the reflected voltage on ISENSE pin is higher than 185mV, MP3910A will disable the internal error amplifier between FB and COMP pins and pull up COMP pin to 3.6V source with  $14.4k\Omega$  resistor, the feedback signal can be connected to COMP pin directly. If the detected voltage is lower than 185mV, MP3910A will enable the internal error amplifier but turn off the pull up resistor. Then COMP pin is just one output pin of error amplifier and the feedback signal should be connected to FB pin.

Figure 2: Feedback Mode Setting

MP3910A Rev. 1.11 2/14/2017

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2017 MPS. All Rights Reserved.

Generally, it is recommended to place one resistor with 5Kohm~10Kohm between ISENSE pin and current sense resistor for the feedback mode through COMP pin, and connect ISENSE pin to current sense resistor directly for feedback mode through FB pin.

#### Soft-Start

MP3910A uses one external capacitor on SS pin to control COMP voltage rising for soft-start. When the chip starts, the capacitor on SS pin is charged by one 54uA current source at a slow pace set by the capacitance. When the SS voltage is lower than the external COMP voltage, SS overrides the COMP signal so the PWM comparator uses SS instead of COMP as the PWM turn off reference. When SS is higher than COMP voltage, COMP gains the control back and the soft start finishes. The soft-start can reduce voltage stresses and surge currents during start up, also prevent the converter output voltage from overshooting during startup. Soft start occurs during the start up time and protection recovery time after OLP, SCP and OVP. During normal condition, the SS voltage is clamped at 3.65V.

#### Programmable Oscillator

The MP3910A oscillating frequency is set by an external resistor from the RT pin to ground. The value of  $R_T$  can be estimated from:

$$R_{\tau} = \frac{2.35 \times 10^3}{f_{SW}}$$

$R_T$  is in k $\Omega$  and  $f_{SW}$  is in kHz.

The frequency setting resistor value shouldn't be too large for noise immunity consideration. It is recommended to set the frequency within 30kHz to 400kHz.

#### Current Sense and Over Current Protection

The MP3910A is peak current mode controller. The current through the external FET can be sensed through a sensing resistor used in series with the source terminal of FET. The sensed voltage on ISENSE pin is then amplified and fed to the high speed current comparator for the current mode control purpose. The current comparator takes this sensed voltage (plus slope compensation) as one of its inputs, then compares the power switch current with the COMP voltage. When the amplified current signal is higher than the COMP voltage, the comparator output is low, turning off the power MOSFET.

If the voltage on the ISENSE pin exceeds the current-limit threshold voltage with typical value of 185mV, MP3910A will turn off the GATE output for that cycle, until the internal oscillator starts the next cycle, and sense current again. MP3910A limits the current of MOSFET cycle-by-cycle.

#### **Over Load Protection (OLP)**

The peak current is limited cycle-by-cycle, if the load continues increasing after triggering OCP protection, the output voltage will decrease and the peak current will trigger OCP every cycle. MP3910A set the over load detection by continue monitoring the ISENSE pin voltage.

Once the SS voltage is charged to 3.65V after start up, the OLP protection is enabled. If an OCP signal is detected, the soft-start charging current is disabled and one over current discharge source is enabled, the SS voltage drops with the rate of 17.8uA current. At the same time, one 50us one-shot timer is activated and it remains active for 50µs after the OCP condition stops. The 17.8uA discharge source cannot be turn off until the one-shot timer becomes inactive. If the OCP disappears before at least 50us prior than the SS capacitor discharging to 2.9V, MP3910A will run back to normal work condition and the SS capacitor will be re-charged to 3.65V with 54uA rate. If the SS capacitor is discharged to 2.9V, MP3910A will register it as over load condition and turn off the gate output until next re-start cycle. At the same time. 17.8uA discharge current is disabled and the 1.66uA over load discharge source is enabled. After the SS voltage is discharged to 0.2V, MP3910A will re-start up with new soft-start cycle. This is hiccup mode protection.

The OLP detection function is disabled after the SS voltage is discharged to be lower than 2.9V and it will be re-enabled after SS voltage is re-charged to 3.65V. So the OLP only occurs after the soft-start is completed.

© 2017 MPS. All Rights Reserved.

12

#### Short Circuit Protection

When the output is shorted to the ground, the part works in OCP mode and current is limited cycle-by-cycle, the part may run into OLP protection.

But if the peak current cannot be limited by 185mV ISENSE voltage in every cycle due to leading edge blanking (LEB) time, the current may run out of control and transformer may run into saturation. If the monitored ISENSE voltage reaches 0.35V, the part will turn off the GATE out and run into hiccup mode by discharge SS capacitor with 1.66uA current. It will also restart up if SS voltage is discharged to 0.2V.

In case the short circuit is removed, the output voltage will recover only after the next new restart cycle.

For boost converter, it has no method to limit current from the input to the output in the condition of output short circuit. If protection from this type condition is desired, it is necessary to add some secondary protection circuit.

#### **Over Voltage Protection**

For isolated-flyback application, the positive plateau of auxiliary winding voltage is proportional to the output voltage, MP3910A features the over voltage protection by using the auxiliary winding voltage instead of directly monitoring the output voltage. The auxiliary voltage can be monitored by FB pin through resistor divider, once the voltage is higher than OVP reference voltage, MP3910A turns off the GATE output and discharge SS voltage with 1.66uA current until SS voltage is lower than 0.2V, then the part will initial one new re-start cycle.

To avoid the mis-trigger due to the oscillation of the leakage inductance and the parasitic capacitance, the OVP sampling has a  $T_{OVPS}$  blanking with 500ns typical value. For some oscillation condition, one external filter is necessary to work together with the 500ns LEB time.

For un-isolated solution, the DC output voltage is applied to FB pin and it can easily detect the OVP condition.

#### Thermal Shutdown

Thermal shutdown is implemented to prevent the chip from thermally running away. When the silicon die temperature is higher than its upper threshold, it shuts down the whole chip. When the temperature is lower than its low threshold, thermal shutdown is gone so the chip is enabled again with a new start-cycle.

### **APPLICATION INFORMATION**

#### **COMPONENT SELECTION**

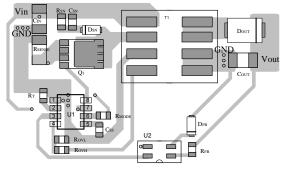

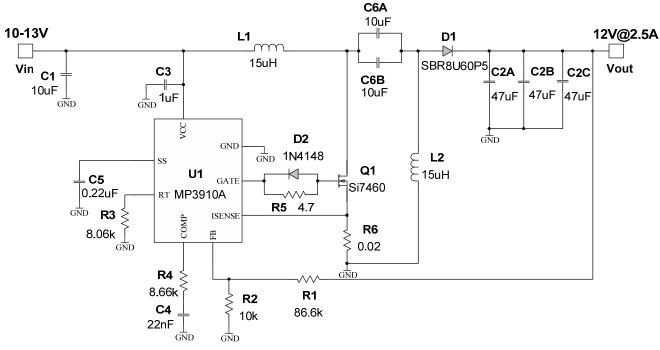

MP3910A can be used for topologies including Flyback, Boost and Sepic. Refer to figure 5 and below introduction for typical external component selection of boost converter.

#### Setting the Output Voltage

Set the output voltage by selecting the resistive voltage divider ratio. If we use  $10k\Omega$  for the low-side resistor (R<sub>FBL</sub>) of the voltage divider, we can determine the high-side resistor (R<sub>FBH</sub>) by the equation:

$$\mathsf{R}_{\mathsf{FBH}} = \frac{\mathsf{R}_{\mathsf{FBL}} \times (\mathsf{V}_{\mathsf{OUT}} - \mathsf{V}_{\mathsf{REF}})}{\mathsf{V}_{\mathsf{REF}}}$$

Where  $V_{OUT}$  is the output voltage

For  $R_{FBL}$ =10k $\Omega$ ,  $V_{OUT}$ =24V and  $V_{REF}$ =1.237V, then  $R_{FBH}$ =182k $\Omega$ .

#### Selecting the Soft-start Capacitor

MP3910A ramps external capacitor voltage on SS pin to control COMP voltage, which determines inductor peak current. The SS pin voltage can be estimated from below equation:

$$Vss = \frac{54\mu A}{C_{ss}} \times T_{ss}$$

When OLP, SCP, OVP occurs, the SS acts as a timer. Once the protection occurs, the 1.66uA current discharges SS cap for hiccup protection.

#### **Selecting the Input Capacitor**

An input capacitor is required to supply the AC ripple current to the inductor, while limiting noise at the input source. A low ESR capacitor is required to keep the noise to the IC at a minimum. Ceramic capacitors are preferred, but tantalum or low-ESR electrolytic capacitors may also suffice. When using tantalum or electrolytic capacitors, a small high quality ceramic capacitor, i.e. 1uF, should be place close to IC. The capacitance for boost input can be calculated as:

$$C_{\rm IN} \approx \frac{\Delta I}{8 \times \Delta V_{\rm IN} \times F_{\rm SW}}$$

Where  $\Delta I$  is the peak-to-peak inductor ripple current and  $\Delta V_{IN}$  is the input voltage ripple.

#### Selecting the Output Capacitor

The output capacitor maintains the DC output voltage. For best results, use low-ESR capacitors to minimize the output voltage ripple.

The output capacitor's characteristics also affect system stability. For best results, use ceramic, tantalum, or low-ESR electrolytic capacitors. For ceramic capacitors, the capacitance dominates the impedance at the switching frequency, and so the output voltage ripple is mostly independent of the ESR. The output voltage ripple is estimated as:

$$\Delta V_{\text{out}} \approx I_{\text{load}} \times \frac{1 - \frac{V_{\text{IN}}}{V_{\text{out}}}}{C_{\text{out}} \times F_{\text{sw}}}$$

Where  $\Delta V_{OUT}$  is the output ripple voltage, VIN and VOUT are the DC input and output voltage, respectively, ILOAD is the load current, FSW is the switching frequency, and COUT is the value of the output capacitor.

For tantalum or low-ESR electrolytic capacitors, the ESR dominates the impedance at the switching frequency, so the output ripple is estimated as:

$$\Delta V_{\text{OUT}} \approx I_{\text{LOAD}} \times \frac{1 - \frac{V_{\text{IN}}}{V_{\text{OUT}}}}{C_{\text{OUT}} \times F_{\text{SW}}} + \frac{I_{\text{LOAD}} \times R_{\text{ESR}} \times V_{\text{OUT}}}{V_{\text{IN}}}$$

Where RESR is the equivalent series resistance of the output capacitors. Choose an output capacitor that satisfies the output ripple and load transient requirements of the design.

## Selecting the Inductor and Current Sensing Resistor

The inductor is required to transfer the energy between the input source and the output capacitors. A larger value inductor results in less ripple current that results in lower peak inductor current, and therefore reduces the stress on the power MOSFET. However, the larger value inductor has a larger physical size, higher series resistance, and lower saturation current.

A good rule of thumb is to allow the peak-topeak ripple current to be approximately 30-50% of the maximum input current. Make sure that the peak inductor current is below 80% of the IC's maximum current limit at the operating duty cycle to prevent loss of regulation. Make sure that the inductor does not saturate under the worst-case load transient and startup conditions. The required inductance value can be calculated by:

$$L \approx \frac{V_{IN} \times (V_{OUT} - V_{IN})}{V_{OUT} \times F_{SW} \times \Delta I}$$

$$I_{IN} = \frac{V_{OUT} \times I_{LOAD}}{V_{IN} \times \eta}$$

$$\Delta I = (30\% - 50\%) \times I_{A},$$

Where  $I_{LOAD}$  is the load current,  $\Delta I$  is the peakto-peak inductor ripple current and  $\eta$  is the efficiency. For a typical design, boost converter efficiency can reach 85%~95%.

The switch current is usually used for the peak current mode control. In order to avoid hitting the current limit, the voltage across the sensing resistor R<sub>SENSE</sub> should be less than 80% of the worst case current limit voltage, 185mV.

$$\mathsf{R}_{\mathsf{SENSE}} = \frac{0.8 \times 0.185}{\mathsf{I}_{\mathsf{L}(\mathsf{PEAK})}}$$

Where  $I_{\text{L}(\text{PEAK})}$  is the peak value of the inductor current.

#### Selecting the Power MOSFET

The MP3910A is capable of driving a wide variety of N-Channel power MOSFETS. The critical parameters of selecting a MOSFET are:

- 1. Maximum drain to source voltage, VDS(MAX)

- 2. Maximum current, ID(MAX)

- 3. On-resistance, RDS(ON)

- 4. Gate source charge Q<sub>GS</sub> and gate drain charge Q<sub>GD</sub>

- 5. Total gate charge, QG

Ideally, the off-state voltage across the MOSFET is equal to boost output voltage. Considering the voltage spike when it turns off, V<sub>DS(MAX)</sub> should be greater than 1.5 times of the output voltage.

The maximum current through the power MOSFET happens when the input voltage is minimum and the output power is maximum. The maximum RMS current through the MOSFET is given by:

$$\mathbf{I}_{\text{RMS}} = \mathbf{I}_{\text{IN}} \times \sqrt{\frac{\mathbf{V}_{\text{OUT}} - \mathbf{V}_{\text{IN}}}{\mathbf{V}_{\text{OUT}}}}$$

The current rating of the MOSFET should be greater than 1.5 times IRMS,

The on resistance of the MOSFET determines the conduction loss, which is given by:

$$\mathsf{P}_{\text{LOSS}} = \mathsf{I}_{\text{RMS}}^2 \times \mathsf{R}_{\text{DS(ON)}} \times \mathsf{K}$$

Where K is the on-resistance temperature coefficient of the MOSFET. So it is smaller, it is better.

The switching loss is related to Q<sub>GD</sub> and Q<sub>GS1</sub> which determine the commutation time. Q<sub>GS1</sub> is the charge between the threshold voltage and the plateau voltage when a driver charges the gate, which can be read in the chart of V<sub>GS</sub> vs. Q<sub>G</sub> of the MOSFET datasheet. Q<sub>GD</sub> is the charge during the plateau voltage. These two parameters are needed to estimate the turn on and turn off loss.

$$P_{\text{SW}} = \frac{Q_{\text{GS1}} \times R_{\text{G}}}{V_{\text{DR}} - V_{\text{TH}}} \times V_{\text{DS}} \times I_{\text{IN}} \times F_{\text{SW}} + \frac{Q_{\text{GD}} \times R_{\text{G}}}{V_{\text{DR}} - V_{\text{PLT}}} \times V_{\text{DS}} \times I_{\text{IN}} \times F_{\text{SW}}$$

Where  $V_{TH}$  is the threshold voltage,  $V_{PLT}$  is the plateau voltage,  $R_G$  is the gate resistance,  $V_{DS}$  is the drain-source voltage. Please note that the switching loss is the most difficult part in the loss estimation. The formula above provides a simple physical expression.

On the other hand, small  $Q_G$  will cause fast turn on/off speed which determines the spike and kick.

#### Selecting the Diode

The boost output rectifier diode supplies current to the inductor when the MOSFET is off. Use a Schottky diode to reduce losses due to the diode forward voltage and recovery time. The diode should be rated for a reverse voltage greater than the expected output voltage. The average current rating must exceed the maximum expected load current, and the peak current rating must exceed the peak inductor current.

#### **Boost Converter Compensation Design**

The output of the transconductance error amplifier (COMP) is used to compensate the regulation control system. The system uses two poles and one zero to stabilize the control loop. The poles are  $F_{P1}$ , which is set by the output capacitor ( $C_{OUT}$ ) and load resistance, and  $F_{P2}$  which starts from origin. The zero ( $F_{Z1}$ ) is set by the compensation capacitor ( $C_{COMP}$ ) and the compensation resistor ( $R_{COMP}$ ). These parameters are determined by the equations:

www.MonolithicPower.com

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2017 MPS. All Rights Reserved.

$$F_{P_1} = \frac{1}{2 \times \pi \times C_{OUT} \times R_{LOAD}}$$

$$F_{Z1} = \frac{1}{2 \times \pi \times C_{COMP} \times R_{COMP}}$$

Where RLOAD is the load resistance.

The DC mid-band loop gain is:

$$A_{\text{VDC}} = \frac{0.5 \times G_{\text{EA}} \times V_{\text{IN}} \times R_{\text{LOAD}} \times V_{\text{REF}} \times R_{\text{COMP}}}{V_{\text{OUT}}^2 \times R_{\text{SENSE}} \times G_{\text{SENSE}}}$$

Where  $V_{\text{REF}}$  is the voltage reference, 1.237V. G<sub>SENSE</sub> is the current sense amplifier gain and G<sub>EA</sub> is the error amplifier transconductance.

The ESR zero in this example locates at very high frequency. Therefore, it is not taken into design consideration.

There is also a right-half-plane zero ( $F_{RHPZ}$ ) that exists in continuous conduction mode (inductor current does not drop to zero on each cycle) step-up converters. The frequency of the right half plane zero is:

$$\mathsf{F}_{\mathsf{RHPZ}} = \frac{\mathsf{V}_{\mathsf{IN}}^2 \times \mathsf{R}_{\mathsf{LOAD}}}{2 \times \pi \times \mathsf{L} \times \mathsf{V}_{\mathsf{OUT}}^2}$$

The right-half-plane zero increases the gain and reduces the phase simultaneously, which results in smaller phase margin and gain margin. The worst case happens at the condition of minimum input voltage and maximum output power.

In order to achieve system stability,  $F_{z1}$  is placed close to  $F_{P1}$  to cancel the pole.  $R_{COMP}$  is adjusted to change the voltage gain. Make sure the bandwidth  $F_C$  is about 1/10 of the lower one of the ESR zero and the right-half-plane zero.

$$\frac{1}{2 \times \pi \times C_{\text{OUT}} \times R_{\text{LOAD}}} = \frac{1}{2 \times \pi \times C_{\text{COMP}} \times R_{\text{COMP}}}$$

$$R_{\text{COMP}} = \frac{V_{\text{OUT}}^2 \times 2 \times \pi \times C_{\text{OUT}} \times F_c \times R_{\text{SENSE}} \times G_{\text{SENSE}}}{G_{\text{EA}} \times V_{\text{REF}} \times V_{\text{IN}}}$$

Based on these equations,  $\mathsf{R}_{\mathsf{COMP}}$  and  $\mathsf{C}_{\mathsf{COMP}}$  can be solved.

In cases where the ESR zero is in a relatively low frequency region and results in insufficient gain margin, an optional capacitor ( $C_{POLE}$ ) should be added between COMP pin and GND. Then a pole, formed by  $C_{POLE}$  and  $R_{COMP}$ , should be placed at the ESR zero to cancel the adverse effect.

$$C_{\text{POLE}} = \frac{1}{2 \times \pi \times R_{\text{COMP}} \times F_{\text{ESRZ}}}$$

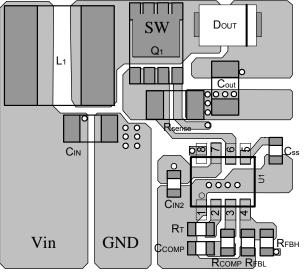

#### PCB Layout Guide

High frequency switching regulators require very careful layout for stable operation and low noise. For boost topology layout:

- 1. Keep the high current path as short as possible between the MOSFET drain, output diode, output capacitor and current sense resistor for minimal noise and ringing.

- 2. The VCC capacitor must be placed close to the VCC pin for best decoupling.

- 3. All feedback components must be kept close to the FB pin to prevent noise injection on the FB pin trace.

- 4. The ground return of the input and output capacitors should be tied to the GND pin with single point connection.

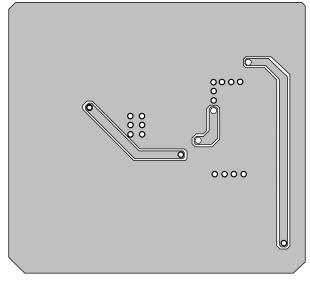

Refer to Figure 3 for boost layout, which is referenced to schematic in Figure 5

Top Layer

Bottom Layer Figure 3: Boost PCB Layout

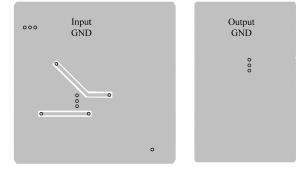

For flyback topology PCB layout:

- 1. Keep the input loop as short as possible between input cap, transformer, MOSFET, current sense resistor and GND plane for minimal noise and ringing.

- 2. Keep the output loop between rectifier diode, output cap and transformer as short as possible.

- 3. The clamp loop circuit between  $D_{\text{SN}},\ C_{\text{SN}}$  and transformer should be as small as possible

- 4. The VCC capacitor must be placed close to the VCC pin for best decoupling.

- 5. The feedback trace should be far away from noise source such as drain of power FET.

- 6. Use single point connection between power GND and signal GND.

Refer to Figure 4 for flyback layout, which is referenced to schematic on page 1 (excluding the snubber). For more detail information, refer to flyback EVB datasheet.

Top Layer

**Bottom Layer**

Figure 4: Fly-back PCB Layout

#### Design Example

Below is a design example following the application guidelines for the specifications:

| able 1: Boost Design Example |        |  |  |  |

|------------------------------|--------|--|--|--|

| V <sub>IN</sub>              | 9-14V  |  |  |  |

| V <sub>OUT</sub>             | 24V    |  |  |  |

| f <sub>sw</sub>              | 300kHz |  |  |  |

The detailed application schematic is shown in Figure 6. And there is another design example for fly-back application in Figure 7.

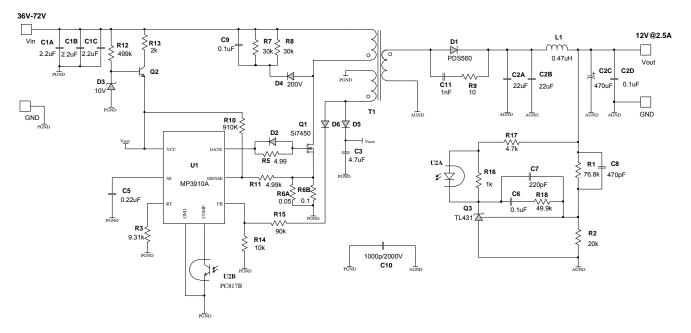

#### Table 2: Fly-back Design Example

|                  | <u> </u> |  |

|------------------|----------|--|

| V <sub>IN</sub>  | 36-72V   |  |

| V <sub>OUT</sub> | 12V      |  |

| f <sub>sw</sub>  | 250kHz   |  |

The typical performance and circuit waveforms of flyback have been shown in the Typical Performance Characteristics section.

Figure 5: Boost Design Reference Schematic

## **TYPICAL APPLICATION CIRCUITS**

Figure 7: Typical Fly-back Converter Application Schematic

## **PACKAGE INFORMATION**

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.

## **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Monolithic Power Systems (MPS):

MP3910AGS