# 900V Offline Switching Regulator

## **DESCRIPTION**

The MP110 is a flyback regulator with an integrated 900V MOSFET. Requiring a minimum number of external components, the MP110 provides excellent power regulation in AC-DC applications that require high reliability. These applications include smart meters, large appliances, industrial controls and products powered by unstable AC grids.

The regulator uses peak current mode control to provide excellent transient response and easy loop compensation. When the output power falls below a given level, the regulator enters burst mode to lower the stand-by power consumption.

The MPS proprietary 900V monolithic process enables an over temperature protection (OTP) that is on the same silicon of the 900V power FET, offering the most precise thermal protection. It also offers a full suite of protection features such as  $V_{\rm CC}$  under-voltage lockout, over-load protection, over-voltage protection, and short-circuit protection.

MP110 The is designed to minimize interference electromagnetic for wireless communication in home and building automation operating frequency applications. The externally programmed with a single resistor so that the power supply's radiated energy can be designed to avoid the interference to wireless communication.

In addition to the programmable frequency, the MP110 employs a frequency jittering function that not only greatly reduces the noise level, but also reduces the cost of EMI filter.

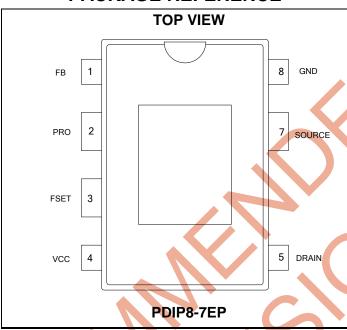

The MP110 is available in the PDIP8-7EP package.

## **FEATURES**

- Internal Integrated 900V MOSFET

- Programmable switching frequency up to 300kHz

- Frequency jittering

- Current-mode operation

- Internal high voltage current source

- Low standby power consumption via active burst mode

- Internal leading-edge blanking

- Built-in soft-start function

- Internal slope compensation

- Built-in PRO pin pull-up auto restart function

- Over-Temperature Protection (OTP)

- V<sub>CC</sub> under-voltage lockout with hysteresis

- Over-Voltage Protection on V<sub>CC</sub>

- Time-based overload protection

- Short-Circuit Protection (SCP)

# **APPLICATIONS**

- Smart Power Meters

- Large Appliances

- Industrial Controls

- All AC-DC supplies sold where power grid may be unstable

All MPS parts are lead-free and adhere to the RoHS directive. For MPS green status, please visit MPS website under Products, Quality Assurance page. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

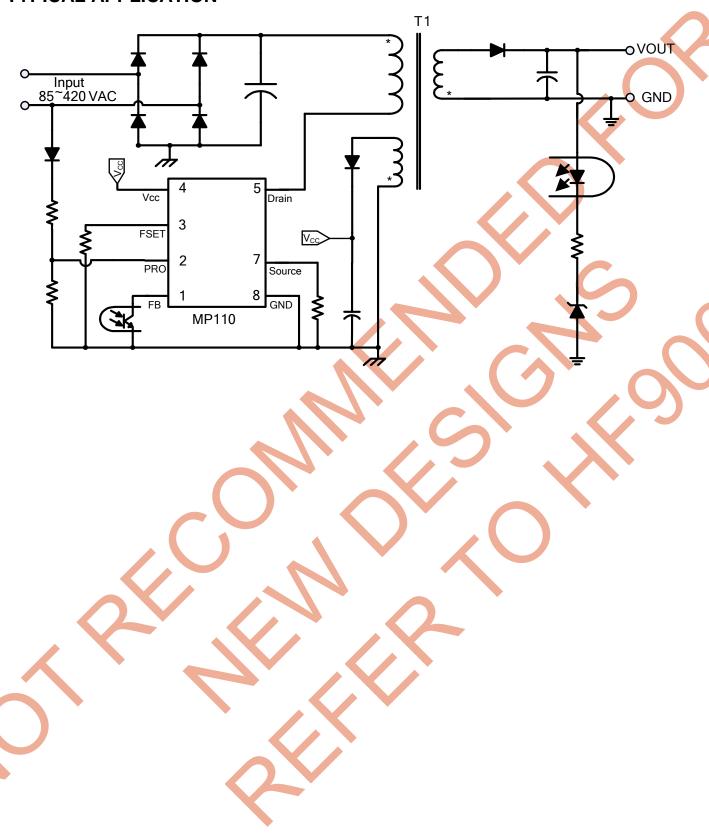

# **TYPICAL APPLICATION**

# ORDERING INFORMATION

| Part Number* | Package   | Top Marking |  |

|--------------|-----------|-------------|--|

| MP110GPR     | PDIP8-7EP | MP110       |  |

\* For Tape & Reel, add suffix -Z (e.g. MP110GPR-Z);

## PACKAGE REFERENCE

# ABSOLUTE MAXIMUM RATINGS (1)

| ADOULD IL MAMMON                          | ITATINGO                              |

|-------------------------------------------|---------------------------------------|

| Drain                                     | 0.3V to 900V                          |

| Vcc                                       | –0.3V to 30 V                         |

| All Other Pins                            |                                       |

| Continuous Power Dissipation (            | T <sub>A</sub> =+25°C) <sup>(2)</sup> |

| PDIP8-7EP                                 |                                       |

| Junction Temperature                      |                                       |

| Lead Temperature                          | 260°C                                 |

| Storage Temperature                       | -60°C to +150°C                       |

| Thermal Shut Down                         | 150°C                                 |

| Thermal Shut Down Hysteresis.             | 30°C                                  |

| ESD Capability Human Body Mo              |                                       |

| ESD Capability Machine Model.             | 200V                                  |

| Operating Temperature                     |                                       |

| Recommended Operation C                   | Conditions (3)                        |

| V <sub>CC</sub> to GND                    |                                       |

| Operating Junction Temp (T <sub>J</sub> ) | -40°C to +125°C                       |

|                                           |                                       |

| Thermal Resistance (4) | $\theta_{JA}$ | $\theta_{JC}$ |

|------------------------|---------------|---------------|

| PDIP8-7EP              | 68            | 7°C/W         |

#### Notes

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-to-ambient thermal resistance θ<sub>JA</sub>, and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX)-T<sub>A</sub>)/θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

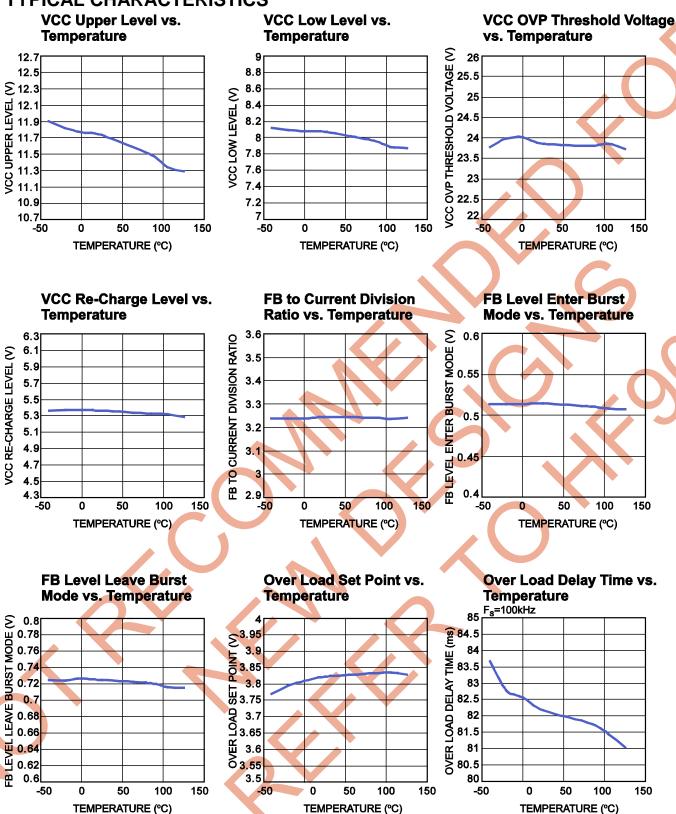

$V_{CC}$  =12V,  $T_J$ =-40°C~125°C, Min & Max are guaranteed by characterization, typical is tested under 25°C, unless otherwise noted

| Parameter                                                      | Symbol                 | Conditions                                          |                                               | Min  | Тур  | Max      | Unit |

|----------------------------------------------------------------|------------------------|-----------------------------------------------------|-----------------------------------------------|------|------|----------|------|

| Start-up Current Source (Pin Drain)                            |                        |                                                     |                                               |      |      |          |      |

| Supply Current from Drain                                      | I <sub>Charge</sub>    | V <sub>CC</sub> =6V;<br>V <sub>Drain</sub> =400V    |                                               | 1.5  | 2    | 2.9      | mA   |

| Leakage Current from Drain                                     | I <sub>Leak</sub>      | $V_{CC} = 13V;$<br>$V_{Drain} = 400V$               |                                               |      | 15   | 30       | μA   |

| Break-Down Voltage                                             | $V_{(BR)DSS}$          | I <sub>leakage</sub> =100μA                         |                                               | 900  |      |          | V    |

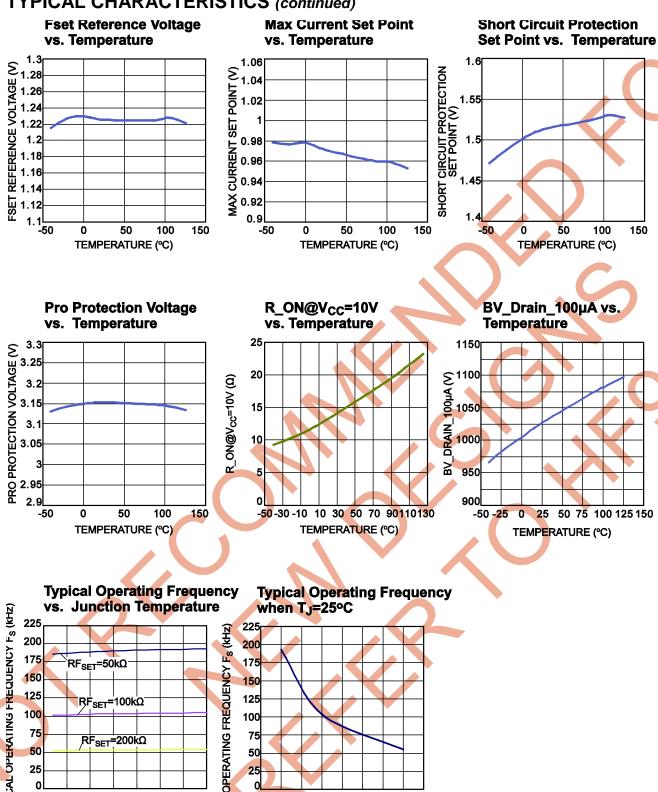

| On-State Resistance                                            | R <sub>DS(ON)</sub>    | V <sub>CC</sub> =10V;<br>I <sub>Drain</sub> =100mA; | T <sub>J</sub> =25°C<br>T <sub>J</sub> =125°C |      | 13   | 17<br>26 | Ω    |

| Supply Voltage Management                                      | (Pin V <sub>cc</sub> ) | Brain ,                                             | 1, 1200                                       |      |      |          |      |

| V <sub>CC</sub> Upper Level at which the IC Switch On          | V <sub>CCH</sub>       |                                                     |                                               | 10.6 | 11.7 | 13.2     | V    |

| V <sub>CC</sub> Lower Level at which the IC Switch Off         | V <sub>CCL</sub>       |                                                     |                                               | 7    | 8    | 9        | V    |

| V <sub>CC</sub> Hysteresis                                     | V <sub>CC_HYS</sub>    |                                                     |                                               | 3    | 3.8  | 4.6      | V    |

| V <sub>CC</sub> OVP Level                                      | V <sub>OVP</sub>       |                                                     |                                               | 22.5 | 24   | 25.3     | V    |

| V <sub>CC</sub> Re-Charge Level at which the Protection Occurs | $V_{CCR}$              |                                                     |                                               | 4.5  | 5.3  | 6        | V    |

| Quiescent Current at<br>Protection Phase                       | I <sub>Pro</sub>       | V <sub>CC</sub> =6V; V <sub>pro</sub> =4V           |                                               |      |      | 600      | μA   |

| Quiescent Current                                              | ΙQ                     | V <sub>CC</sub> =13V                                |                                               |      | 700  | 900      | uA   |

| Operation Current                                              | I <sub>cc</sub>        | V <sub>CC</sub> =13V; f <sub>S</sub> =100kHz        |                                               |      | 1.7  | 2        | mA   |

| Feedback Management (Pin                                       | FB)                    |                                                     |                                               |      |      |          |      |

| Internal Pull-Up Resistor                                      | R <sub>FB</sub>        |                                                     |                                               |      | 10   |          | kΩ   |

| Internal Pull-Up Voltage                                       | V <sub>UP</sub>        |                                                     |                                               | 3.8  | 4.1  | 4.4      | V    |

| FB to Current-Set-Point Division Ratio                         | I <sub>div</sub>       |                                                     |                                               |      | 3.3  | 3.5      |      |

| Internal Soft-Start Time                                       | T <sub>SS</sub>        |                                                     |                                               |      | 3    |          | ms   |

| FB Decreasing Level at which the Regulator Enters Burst Mode   | V <sub>BURL</sub>      |                                                     | 0.4                                           | 0.5  | 0.6  | V        |      |

| FB Increasing Level at which the Regulator Leaves Burst Mode   | V <sub>BURH</sub>      |                                                     | 0.58                                          | 0.7  | 0.86 | V        |      |

| Over-Load Set Point                                            | V <sub>OLP</sub>       |                                                     | 3.6                                           | 3.8  | 4    | V        |      |

| Over-Load Delay Time                                           | T <sub>Delay</sub>     | f <sub>S</sub> =100kHz                              |                                               |      | 82   |          | ms   |

# **ELECTRICAL CHARACTERISTICS**

V<sub>CC</sub> =12V, T<sub>J</sub>=-40°C~125°C, Min & Max are guaranteed by characterization, typical is tested under 25°C, unless otherwise noted

| Parameter                                               | Symbol                          | Conditions                                               | Min  | Тур  | Max  | Unit     |  |

|---------------------------------------------------------|---------------------------------|----------------------------------------------------------|------|------|------|----------|--|

| Timing Resistor(Pin FSET)                               |                                 |                                                          |      |      |      |          |  |

| FSET Reference Voltage                                  | $V_{FSET}$                      |                                                          | 1.16 | 1.23 | 1.29 | <b>V</b> |  |

| Frequency Spectrum Jittering Range, in Percentage of Fs | R <sub>Jittering</sub>          | Example: f <sub>S</sub> =100kHz, then jittering is ±4kHz |      | ±4   |      | %        |  |

| Typical Operating Frequency                             | f <sub>S</sub>                  | T <sub>J</sub> =25                                       | 90   | 104  | 118  | kHz      |  |

| Current Sampling Manageme                               | ent (Pin So                     | urce)                                                    |      |      |      |          |  |

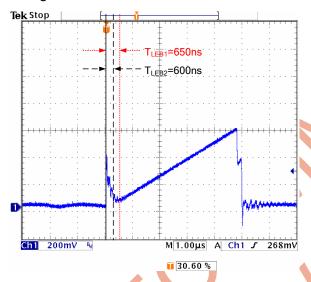

| Leading-Edge Blanking for<br>Current Sensor             | T <sub>LEB1</sub>               |                                                          |      | 650  |      | ns       |  |

| Leading-Edge Blanking for SCP                           | T <sub>LEB2</sub>               |                                                          |      | 600  |      | ns       |  |

| Maximum Current Set Point                               | V <sub>CS</sub>                 |                                                          | 0.90 | 0.96 | 1.02 | <b>V</b> |  |

| Short-Circuit Protection Set Point                      | $V_{SC}$                        |                                                          | 1.32 | 1.42 | 1.62 | V        |  |

| Slope Compensation Ramp                                 | $S_Ramp$                        | f <sub>S</sub> =100kHz                                   |      | 40   |      | mV/μs    |  |

| Protection Management (Pin                              | Protection Management (Pin PRO) |                                                          |      |      |      |          |  |

| Protection Voltage                                      | $V_{PRO}$                       |                                                          | 2.95 | 3.1  | 3.3  | V        |  |

| Protection Hysteresis                                   | $V_{HY}$                        |                                                          |      | 0.2  |      | V        |  |

| Thermal Shutdown                                        |                                 |                                                          |      |      |      |          |  |

| Thermal Shutdown Threshold                              |                                 | N' /                                                     |      | 150  | X    | °C       |  |

| Thermal Shutdown Recovery Hysteresis                    |                                 |                                                          |      | 30   |      | °C       |  |

# **PIN FUNCTIONS**

| Pin# | Name            | Description                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | FB              | Feedback. The output voltage from the external compensation circuit is fed into this pin. This pin and the current sense signal from Source determines the PWM duty cycle. A feedback voltage of $V_{\text{OLP}}$ triggers over-load protection, while $V_{\text{BURL}}$ triggers burst-mode operation. The regulator exits burst-mode operation and enters normal operation when the FB voltage reaches $V_{\text{BURH}}$ . |

| 2    | PRO             | Protection. Pull-up PRO to shut down the IC with hysteresis.                                                                                                                                                                                                                                                                                                                                                                 |

| 3    | FSET            | Switching converter frequency set. Connect a resistor to GND to set the switching frequency up to 300kHz.                                                                                                                                                                                                                                                                                                                    |

| 4    | V <sub>cc</sub> | Supply voltage. Connect a 22 $\mu$ F bulk capacitor and a 0.1 $\mu$ F ceramic capacitor for most applications. When $V_{CC}$ rises to $V_{CCH}$ , the IC starts switching; when it falls below $V_{CCL}$ , the IC stops switching.                                                                                                                                                                                           |

| 5    | Drain           | Drain of the internal MOSFET. Input for the start-up high voltage current source.                                                                                                                                                                                                                                                                                                                                            |

| 7    | Source          | Source of the internal MOSFET. Input of the primary current sense signal.                                                                                                                                                                                                                                                                                                                                                    |

| 8    | GND             | The IC Ground.                                                                                                                                                                                                                                                                                                                                                                                                               |

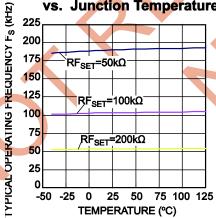

# TYPICAL CHARACTERISTICS

TEMPERATURE (°C)

TEMPERATURE (°C)

# TYPICAL CHARACTERISTICS (continued)

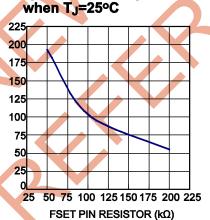

# TYPICAL PERFORMANCE CHARACTERISTICS

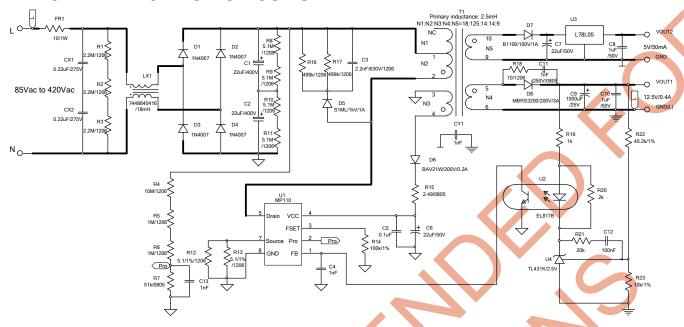

Performance waveforms are tested on the evaluation board of the Design Example section.  $V_{IN} = 230V$ ,  $V_{OUT1} = 12.5V$ ,  $V_{OUT2} = 5V$ , Primary Inductance=2.5mH,  $N_P:N_{AUX}:N_{S1}:N_{S2} = 125:14:14:9$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

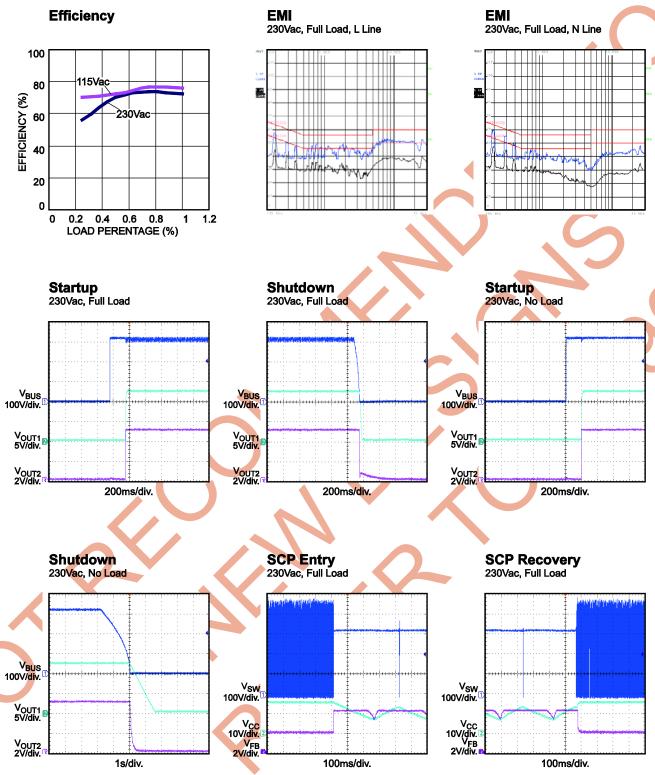

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

Performance waveforms are tested on the evaluation board of the Design Example section.  $V_{IN} = 230V$ ,  $V_{OUT1} = 12.5V$ ,  $V_{OUT2} = 5V$ , Primary Inductance=2.5mH,  $N_P:N_{AUX}:N_{S1}:N_{S2} = 125:14:14:9$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

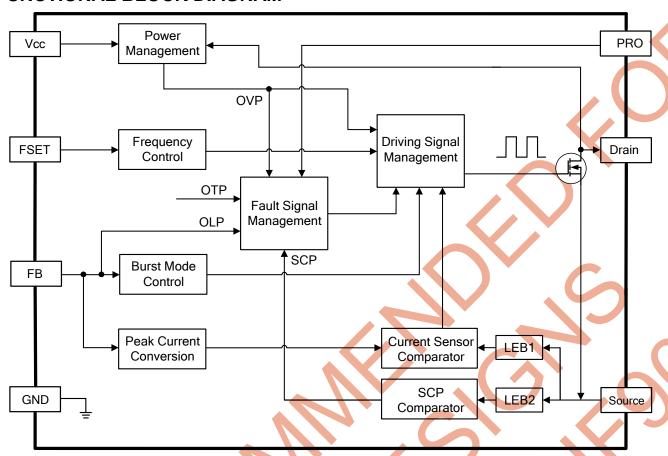

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 1: Internal Function Block Diagram

#### **OPERATION**

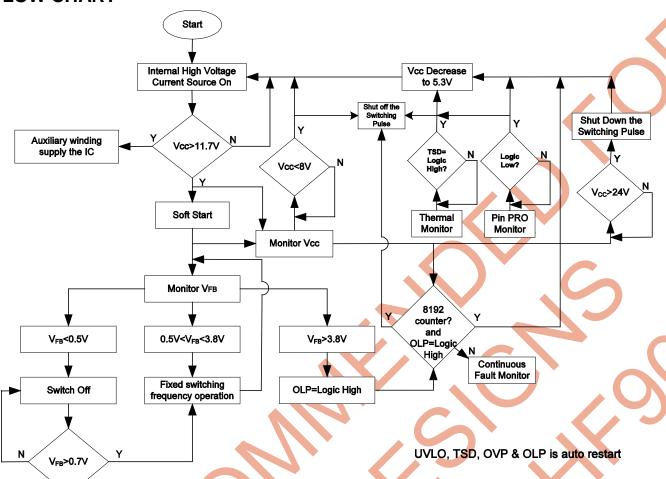

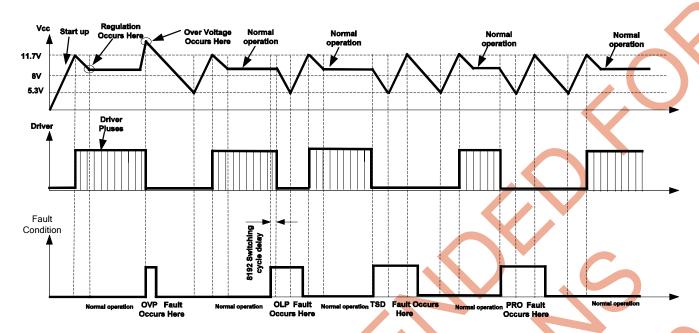

The MP110 incorporates all the necessary features required by a reliable switch mode power supply. The proprietary 900V monolithic integration enables a highly integrated power supply solution. It has burst mode operation to minimize the stand-by power consumption at light load. Protection features such as auto-recovery for over-load protection (OLP), short-circuit protection (SCP), over-voltage protection (OVP), and thermal shutdown for over-temperature protection (OTP) - contribute to a safer converter design with minimal external components.

## **PWM Operation**

The MP110 employs peak current mode control. On the secondary side, the output voltage is divided down by a voltage divider network. This voltage is fed back to the primary side as voltage on the FB pin using an opto-coupler and a shunt regulator. The voltage at the FB pin is compared to the  $V_{\text{Sense}}$  voltage which measures MOSFET switching current. The integrated MOSFET turns on at the beginning of each clock cycle. The current in the transformer magnetizing inductance increases until it reaches the value set by the FB voltage, and then the integrated MOSFET turns off.

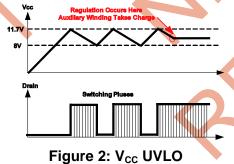

## Start-up and V<sub>cc</sub> UVLO

Initially, the IC is driven by the internal current source which is drawn from the high-voltage Drain pin. The IC starts switching and the internal high-voltage current source turns off as soon as the voltage on pin  $V_{\rm CC}$  reaches 11.7V ( $V_{\rm CCH}$ , typical value). At this point, the supply of the IC is taken over by the auxiliary winding of the transformer. When  $V_{\rm CC}$  falls below 8V ( $V_{\rm CCL}$ , typical value), the regulator stops switching and the internal high-voltage current source turns on again.

The lower threshold of VCC UVLO decreases from 8V ( $V_{CCL}$ , typical value) to 5.3V ( $V_{CCR}$ , typical value) when fault conditions happen, such as SCP, OLP, OVP, and OTP.

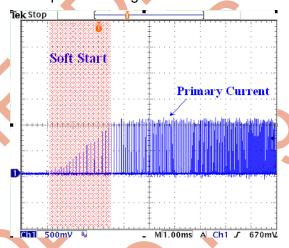

#### **Soft-Start**

The MP110 implements an internal soft-start circuit in order to reduce stress on the primary side MOSFET, secondary diode and smoothly establish the output voltage during start-up. The internal soft-start circuit gradually increases the primary current sense threshold which determines the MOSFET peak current during start-up. The pulse width of the power switching device is progressively increased to establish correct operating conditions until the feedback control loop takes charge.

Figure 3: Soft Start

#### Switching Frequency

The switching frequency of MP110 can be set by FSET pin. The frequency can be set by a resistor between FSET pin and GND pin. The oscillator frequency can be attained below:

$$f_s = \frac{1}{200 \times 10^{-9} + 112.5 \times 10^{-12} \times \frac{R_{FSET}}{V_{FSET}}}$$

Hz

V<sub>FST</sub> (1.23V) is the FSET pin reference voltage. **Over Voltage Protection (OVP)**

Monitoring the  $V_{\text{CC}}$  pin voltage via a 20us time constant filter allows the MP110 to enter OVP during an over-voltage condition, typically when  $V_{\text{CC}}$  goes above 24V. The regulator will resume operation after the fault disappears.

## **Over Load Protection (OLP)**

MP110 shuts when the power supply undergoes an overload. OLP is achieved by continuously monitoring the FB voltage. A fault signal is triggered when FB pulls up to 3.8V ( $V_{\text{OLP}}$ , typical value) and after 82ms delay (8192 switching cycle,  $f_{\text{S}}$ =100kHz), if the fault signal is still present, MP110 shuts down. When the fault disappears, the power supply resumes operation. The OLP delay time can be attained below.

$$T_{Delay} = \frac{82ms \times 100kHz}{f_s}$$

# **Short Circuit Protection (SCP)**

By monitoring the CS Pin, MP110 shuts down when the voltage rises higher than 1.42V (V<sub>SC</sub>, typical value) to indicate a short circuit. The MP110 enters a safe low-power mode that prevents any thermal damage or stress damage. As soon as the fault disappears, the power supply resumes operation.

## Thermal shutdown (OTP)

When the junction temperature of the IC exceeds  $150^{\circ}\text{C}$ , the over temperature protection is activated and stops output driver switching to prevent MP110 from any thermal damage. As soon as the junction temperature drops below  $120^{\circ}\text{C}$ , the regulator resumes operation. During the protection period, the regulator enters autorecovery mode. The VCC voltage is discharged to  $V_{\text{CCR}}$  and is re-charged to  $V_{\text{CCH}}$  by the internal high voltage current source.

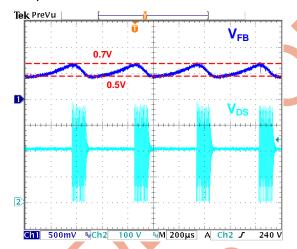

#### **Burst Operation**

To minimize stand-by power consumption, the MP110 implement burst mode at no load and light load. As the load decreases, the FB voltage decreases. The IC stops switching when the FB voltage drops below 0.5V (V<sub>BRUL</sub>, typical value). As the load power increases, the output voltage drops at a rate dependent on the load. This causes the FB voltage to rise again due to the negative feedback control loop. Once the FB voltage exceeds 0.7V (V<sub>BRUH</sub>, typical value), the switching pulse resumes. The FB voltage then decreases and the whole process repeats. Burst-mode operation alternately enables and disables the switching pulse of the MOSFET. Hence switching loss at no load and light load conditions

is greatly reduced. Figure 4 shows the burst mode operation of MP110.

Figure 4: Burst Mode Operation

#### **PRO Pin**

The PRO pin provides extra protection against abnormal conditions. Use the PRO pin for input OVP or other protections (input UVP, overtemperature protection for key component and so on). If the PRO pin voltage exceeds 3.1V (V<sub>PRO</sub>, typical value), the IC shuts down to enter autorecovery mode. As soon as the fault disappears, the power supply resumes operation.

## **Peak Current Limit**

In normal operation, the primary peak current is sensed by a sensing resistor between the Source pin and Ground. The turn-off threshold of the MOSFET is set by FB voltage,  $V_{Sense}=V_{FB}/I_{div}$ . When the sensing resistor voltage reaches the  $V_{Sense}$ , the MOSFET turns off. The  $I_{div}$  is the FB to current-set-point division ratio.

During over-load condition, the primary peak current threshold is internally limited to the maximum value 0.96V ( $V_{CS}$ , typical value) even if  $V_{FB}$  voltage exceeds 3.2V to avoid excessive output power and lower the switch voltage rating.

During start-up period, the primary peak current threshold internally increases to the maximum current set point V<sub>CS</sub> gradually.

#### **Leading Edge Blanking**

In order to avoid turning off the MOSFET from mis-trigger spikes shortly after the switch turns

on, the IC implements leading-edge blanking. During the blanking time, any trigger signal on source pin is blocked. An internal leading-edge blanking(LEB) unit containing two LEB times is employed between the Source pin and the current comparator input to avoid premature switching pulse termination due to the parasitic capacitances. During the blanking time, the current comparator is disabled and can not turn off the MOSFET.

Current sensor leading edge blanking inhibits the current limitation comparator during 650ns ( $T_{LEB1}$ , typical value) and SCP leading edge blanking inhibits the SCP current comparator during 600ns ( $T_{LEB2}$ , typical value). Figure 5 shows the primary current sense waveform and the leading edge blanking.

Figure 5: Leading Edge Blanking

# **APPLICATION INFORMATION**

## **Input Capacitor Choose**

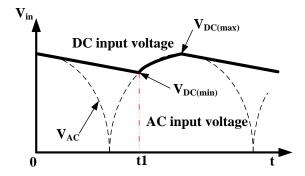

The bulk capacitors after the rectifier bridge filter the rectified AC input which supply the DC input voltage for the converter. Figure 6 shows the typical DC bus voltage waveform of full bridge rectifier.

Figure 6: Input voltage waveform

When the full-bridge rectifier is used, the input capacitor is usually set as  $2\mu F/W$  for the universal input condition (85~265V<sub>AC</sub>). Halve the capacitor values for high voltage input (>185VAC) application. The input power  $P_{in}$  can be estimated as follow.

$$P_{in} = \frac{V_O \times I_O}{n}$$

Where  $V_0$  is the output voltage,  $I_0$  is the rated output current,  $\eta$  is the estimated efficiency. Generally,  $\eta$  is between 0.75 and 0.85 depending on the input range and output application.

From the waveform above, the AC input voltage  $V_{AC}$  and DC input voltage  $V_{DC}$  can be got as follow.

$$V_{DC}(V_{AC},t) = \sqrt{2 \times V_{AC}^2 - \frac{2 \times P_{in}}{C_{in}} \times t}$$

By setting V<sub>AC</sub>=V<sub>DC</sub>, t1 where DC bus voltage reaches to its minimum value can be calculated. So the minimum DC voltage is as follow.

$$V_{DC(min)} = V_{DC}(V_{AC(min)}, t1)$$

Very low DC input voltage could cause thermal problem in full load. It's recommend the minimum

DC voltage is higher than 70V, or the input capacitor value should be increased.

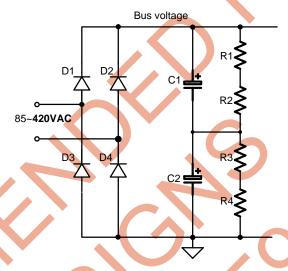

As a 900V offline regulator, MP110 is very suitable for very high voltage input application. But the general input capacitors with 400V voltage rating can not satisfy the safety requirement. Thus the stack capacitors could be used in very high input voltage application such as 420VAC input which refers to the Figure7.

Figure 7: Input Stack Capacitor Circuit

The C1 and C2 endure the half of input DC voltage rating respectively. The R1~R4 should be use the same value resistor to equalize the C1, C2 voltage stress. And the R1~R4 is recommended to use the 1206 package to satisfy safety requirement. Also, the R1~R4 value should be large enough for energy saving. For example, the total value of R1~R4 is  $20M\Omega$  which consumes about 18mW in 600VDC bus voltage.

#### Primary-Side Inductor Design (L<sub>m</sub>)

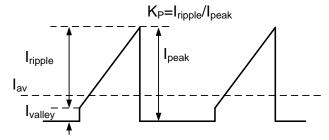

Normally, the converter is designed to operate in CCM under low input voltage. CCM is needed to satisfy the output energy requirement in universal input condition. With built-in slope compensation function, MP110 can support CCM when duty cycle exceeds 50%. Set the ratio  $(K_P)$  of the primary inductor ripple current amplitude vs. the peak current value to  $0 < K_P \le 1$ , where  $K_P = 1$  for DCM. Figure 8 shows the relevant waveforms. A larger inductor leads to a smaller  $K_P$ , which can

reduce RMS current but increase transformer size. For 5W application, an optimal  $K_P$  value is usually between 0.8 and 1 for the universal input range and 1 for a 230VAC input range.

Figure 8: Typical Primary-Current Waveform For CCM at minimum input, the converter duty cycle is:

$$D = \frac{(V_O + V_F) \times N}{(V_O + V_F) \times N + V_{DC(min)}}$$

Where:

$V_{\text{F}}$  is the secondary diode's forward voltage,

N is the transformer turns ratio.

The MOSFET turn-on time is

$$T_{ON} = \frac{D}{f_s}$$

f<sub>S</sub> is operating frequency.

The input average current, ripple current, peak current and valley current of the primary side are described as follows:

$$\begin{split} I_{\text{AV}} &= \frac{P_{\text{in}}}{V_{\text{DC(min)}}} \\ I_{\text{ripple}} &= K_{\text{P}} \times I_{\text{peak}} \\ I_{\text{peak}} &= \frac{I_{\text{AV}}}{(1 - \frac{K_{\text{P}}}{2}) \times D} \\ I_{\text{valley}} &= (1 - K_{\text{P}}) \times I_{\text{peak}} \end{split}$$

The following equation estimates L<sub>m</sub> as

$$L_{m} = \frac{V_{DC(min)} \times T_{ON}}{I_{ripple}}$$

#### **Current-Sense Resistor**

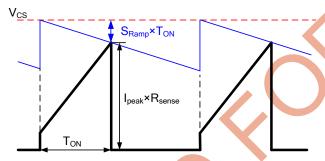

Figure 9: Slope Compensation waveform

Figure 9 shows the slope compensation waveform. When the sum of the sense resistor voltage and the slope compensation voltage reaches the peak current limit  $V_{CS}$ , MP110 turns off the internal MOSFET. The maximum peak current limit is 0.96V ( $V_{CS}$ , typical value) and the slope compensation slew rate is 40mV/us. Considering the margin, use  $0.95\times V_{CS}$  as the peak current limit at full load. The voltage on sense resistor is given by the following equation:

$$V_{\text{sense}} = 0.95 \times V_{\text{CS}} - S_{\text{Ramp}} \times T_{\text{ON}}$$

So the value of the sense resistor is

$$R_{\text{sense}} = \frac{V_{\text{sense}}}{I_{\text{peak}}}$$

Select the current sense resistor with appropriate power rating based on the power loss:

$$P_{\text{sense}} = \left[ \left( \frac{I_{\text{peak}} + I_{\text{valley}}}{2} \right)^2 + \frac{1}{12} \times \left( I_{\text{peak}} - I_{\text{valley}} \right)^2 \right] \times D \times R_{\text{sense}}$$

# **PRO pin**

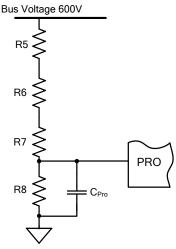

Extra protection can be enable thru the MP110 PRO pin. A typical input over-voltage protection circuitry is shown in figure 10.

Figure 10: Input Over Voltage Protection Setup

The input over voltage protection point can be calculated by the following function:

$$V_{INOVP} = V_{PRO} \times \frac{R5 + R6 + R7 + R8}{R8}$$

1206 packages should be used for resistors R5~R8 for safety consideration and the total value should be larger than  $10M\Omega$  for energy saving purpose.

The switching voltage noise could be introduced by large R5~R8 value which disturbs the PRO pin protection action. One ceramic cap with around 1nF should be paralleled with PRO pin and GND pin. It should be located near the IC to decouple the switching voltage noise.

## **Frequency Jittering**

MP110 provides the frequency jittering function which simplifies the input EMI filter design and also decreases the system cost. MP110 has the optimized frequency jittering with ±4% frequency deviation range and 256T<sub>S</sub> carrier cycle which can effectively improve EMI by spreading the energy dissipation over the frequency range.

## Thermal

MP110 is popular for high input voltage application with 900V integrated MOSFET. The thermal is the key factor to influence the output power especially the high input voltage and high operating frequency. The turn-on loss is dominant in high input voltage caused by the parasitic cap of secondary side diode and

transformer, which bring about the IC very high junction temperature.

In order to deliver maximum power, a proper heatsink for MP110 should be designed for optimum thermal performance. In addition, it's recommended to set the operating frequency less than 150kHz in order to achieve better thermal performance and better EMI in application.

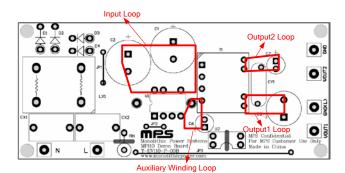

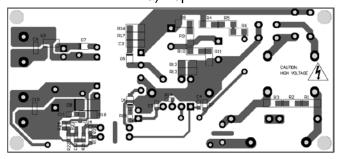

## **PCB Layout Guide**

PCB layout is important to achieve reliable operation, good EMI performance, and good thermal performance. Follow these guidelines to optimize performance.

- 1) Minimize the power stage switching stage loop area. This includes the input loop (C2–C1-T1–U1–R12/R13–C2), the auxiliary winding loop (T1–D6–C6–T1), the output loop (T1–D8–C9–T1 and T1–D7–C7–T1) and the RCD loop (T1–D5–R16/R17/C3–T1)

- The input loop GND and control circuit should be separate and only connect at C2.

- Connecting the heatsink to the primary GND plane improves EMI and thermal dissipation.

- 4) Place the control circuit capacitors (such as those for FB, PRO and VCC pins) close to IC to decouple switching voltage noise.

- 5) Enlarge the GND pad near the IC for good thermal dissipation.

- 6) Keep the EMI filter far away from the switching point.

- 7) The two outputs clearance distance should satisfy the insulation requirement.

a) Top

b) Bottom

Figure 11: PCB Layout

# **Design Example**

The following is a design example using the application guidelines for the given specifications:

| $V_{IN}$          | 85 to 420VAC |  |

|-------------------|--------------|--|

| $V_{OUT1}$        | 12.5V        |  |

| I <sub>OUT1</sub> | 0.4A         |  |

| $V_{OUT2}$        | 5V           |  |

| I <sub>OUT2</sub> | 0.05A        |  |

| f <sub>S</sub>    | 100kHz       |  |

The detailed application schematic is shown in Figure 12. The typical performance and circuit waveforms have been shown in the typical performance characteristics section. For more device applications, please refer to the related evaluation board datasheets.

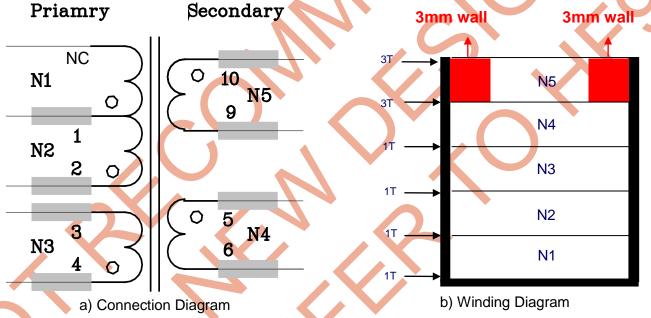

# **TYPICAL APPLICATION CIRCUITS**

Figure 12: Typical Application Schematic

Figure 13: Transformer Structure

# Table 2—Winding Order

| Tape (T) | Winding | Margin Wall<br>PRI side | Terminal<br>Start—>End | Margin Wall<br>SEC side | Wire Size (φ) | Turns (T) |  |

|----------|---------|-------------------------|------------------------|-------------------------|---------------|-----------|--|

| 1        |         |                         |                        |                         |               |           |  |

|          | N1      | 0mm                     | 1—>NC                  | 0mm                     | 0.18mm*2      | 18        |  |

| 1        | N2      | 0mm                     | 2—>1                   | 0mm                     | 0.18mm*1      | 125       |  |

| 1        | N3      | 0mm                     | 4—>3                   | 0mm                     | 0.15mm*1      | 14        |  |

| 1        | N4      | 0mm                     | 5—>6                   | 0mm                     | 0.4mm*1       | 14        |  |

| 3        | 144     | OHIIII                  | 0 /0                   | Onlin                   | 0.4111111     | 17        |  |

| 3        | N5      | 3mm                     | 10—>9                  | 3mm                     | 0.2mm*1       | 9         |  |

## **FLOW CHART**

# **EVOLUTION OF THE SIGNALS IN PRESENCE OF FAULTS**

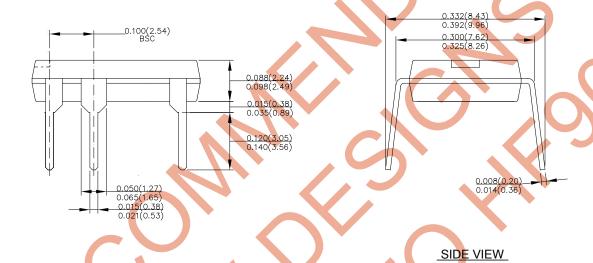

# **PACKAGE INFORMATION**

# PDIP8-7EP 0.367(9.32) 8 0.387(9.83) 5 0.160(4.10) 0.169(4.30) 0.120(3.10) 0.130(3.31) 0.240(6.10) 0.260(6.60)

#### **TOP VIEW**

4

# NOTE:

- 1) CONTROL DIMENSION IS IN INCHES. DIMENSION IN BRACKET IS IN MILLIMETERS.

- 2) PACKAGE LENGTH AND WIDTH DO NOT INCLUDE MOLD FLASH, OR PROTRUSIONS.

- 3) JEDEC REFERENCE IS MS-001, VARIATION BA.

- 4) DRAWING IS NOT TO SCALE.

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

$\frac{\text{Monolithic Power Systems (MPS)}}{\text{MP110GPR-Z MP110GPR}}:$