### **APPLICATIONS**

- IEEE 802.15.4 systems

- ZigBee® systems

- Industrial monitoring and control

- Home and building automation

- Automatic Meter Reading

- Low-power wireless sensor networks

- Set-top boxes and remote controls

- Consumer electronics

### **KEY FEATURES**

- State-of-the-art selectivity/co-existence Adjacent channel rejection: 49 dB Alternate channel rejection: 54 dB

- Excellent link budget (103dB) 400 m Line-of-sight range

- Extended temp range (-40 to +125°C)

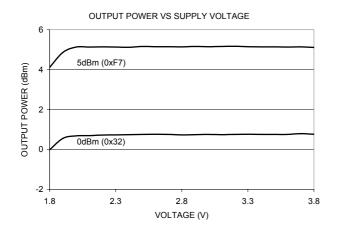

- Wide supply range: 1.8 V − 3.8 V

- Extensive IEEE 802.15.4 MAC hardware support to offload the microcontroller

- AES-128 security module

- CC2420 interface compatibility mode

### **Low Power**

- RX (receiving frame, -50 dBm) 18.5 mA

- TX 33.6 mA @ +5 dBm

- TX 25.8 mA @ 0 dBm

- <1μA in power down</li>

### General

- Clock output for single crystal systems

- RoHS compliant 5 x 5 mm QFN28 (RHD) package

#### Radio

- IEEE 802.15.4 compliant DSSS baseband modem with 250 kbps data rate

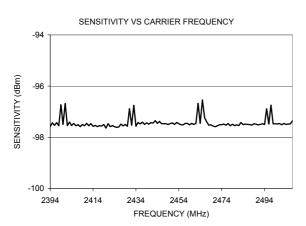

- Excellent receiver sensitivity (-98 dBm)

- Programmable output power up to +5 dBm

- RF frequency range 2394-2507 MHz

- Suitable for systems targeting compliance with worldwide radio frequency regulations: ETSI EN 300 328 and EN 300 440 class 2 (Europe), FCC CFR47 Part 15 (US) and ARIB STD-T66 (Japan)

### Microcontroller Support

- Digital RSSI/LQI support

- Automatic clear channel assessment for CSMA/CA

- Automatic CRC

- 768 bytes RAM for flexible buffering and security processing

- Fully supported MAC security

- 4 wire SPI

- 6 configurable IO pins

- Interrupt generator

- Frame filtering and processing engine

- Random number generator

### **Development Tools**

- Reference design

- IEEE 802.15.4 MAC software

- ZigBee® stack software

- Fully equipped development kit

- Packet sniffer support in hardware

### **DESCRIPTION**

The CC2520 is TI's second generation ZigBee® / IEEE 802.15.4 RF transceiver for the 2.4 GHz unlicensed ISM band. This chip enables industrial grade applications by offering state-of-the-art selectivity/co-existence, excellent link budget, operation up to 125°C and low voltage operation.

In addition, the CC2520 provides extensive hardware support for frame handling, data buffering, burst transmissions, data encryption, data authentication, clear channel assessment, link quality indication and frame timing information. These features reduce the load on the host controller.

In a typical system, the CC2520 will be used together with a microcontroller and a few additional passive components.

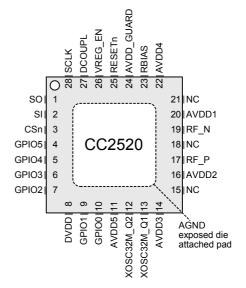

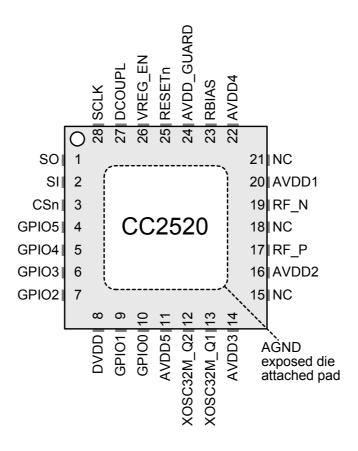

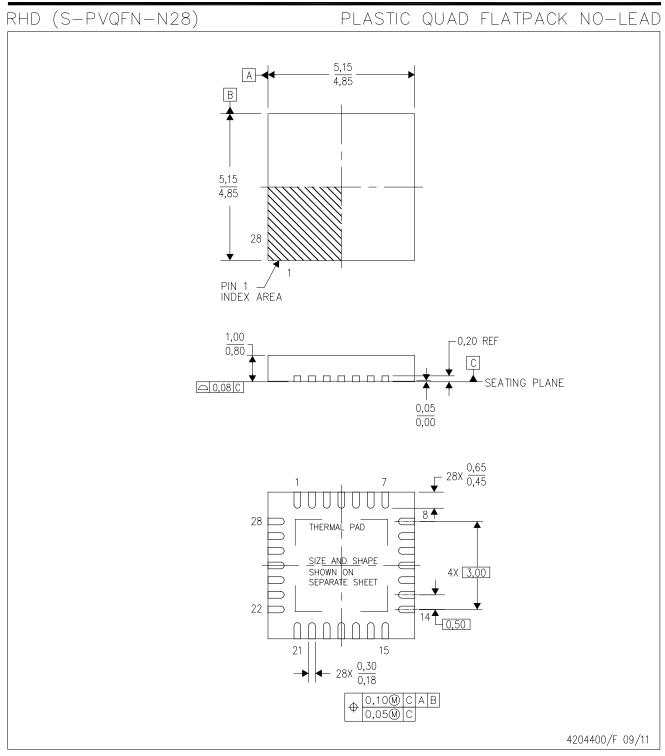

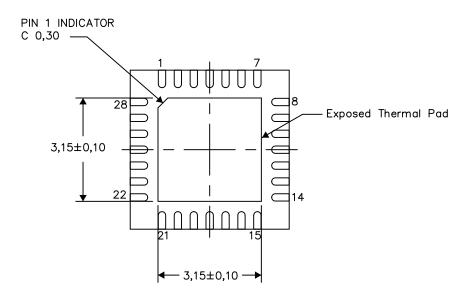

# QFN28 (RHD) PACKAGE TOP VIEW

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers threto appear at the end of this datasheet.

ZigBee® is a registered trademark owned by ZigBee Alliance, Inc.

# CC2520 DATASHEET 2.4 GHZ IEEE 802.15.4/ZIGBEE® RF TRANSCEIVER SWRS068 – DECEMBER 2007

| TΑ | BLE OF C | CONTENTS                                                          |    |

|----|----------|-------------------------------------------------------------------|----|

| 1  | Abbrev   | viations                                                          | 5  |

| 2  | Refere   | nces                                                              | 7  |

| 3  | Featur   | es                                                                | 8  |

| 4  | Absolu   | te Maximum Ratings                                                | 10 |

| 5  | Electric | cal Characteristics                                               | 11 |

|    | 5.1      | Recommended Operating Conditions                                  | 11 |

|    | 5.2      | DC Characteristics                                                | 11 |

|    | 5.3      | Wake-Up and Timing                                                | 11 |

|    | 5.4      | Current Consumptions                                              | 11 |

|    | 5.5      | Receive Parameters                                                |    |

|    | 5.6      | Frequency Synthesizer Parameters                                  |    |

|    | 5.6.1    | Transmit Parameters                                               | 12 |

|    | 5.7      | RSSI/CCA Parameters                                               |    |

|    | 5.8      | FREQEST Parameters                                                | 13 |

|    | 5.9      | Typical Performance Curves                                        |    |

|    | 5.10     | Low-Current Mode RX                                               | 19 |

|    | 5.10.1   | Low-Current RX Mode Parameters                                    | 19 |

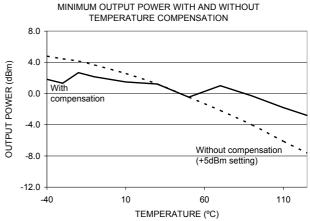

|    | 5.11     | Optional Temperature Compensation of TX                           |    |

|    | 5.11.1   | Using the Temperature Sensor                                      |    |

| 6  | Crysta   | Specific Parameters                                               |    |

|    | 6.1      | Crystal Requirements                                              |    |

|    | 6.2      | On-chip Crystal Frequency Tuning                                  |    |

| 7  |          |                                                                   |    |

| 8  |          | onal Introduction                                                 |    |

|    | 8.1      | Integrated 2.4 GHz IEEE 802.15.4 Compliant Radio                  |    |

|    | 8.2      | Comparison to CC2420                                              |    |

|    | 8.3      | Block Diagram                                                     |    |

| 9  |          | ation Circuit                                                     |    |

|    | 9.1      | Input / Output Matching                                           |    |

|    | 9.2      | Bias Resistor                                                     |    |

|    | 9.3      | Crystal                                                           |    |

|    | 9.4      | Digital Voltage Regulator                                         |    |

|    | 9.5      | Power Supply Decoupling and Filtering                             |    |

|    | 9.6      | Board Layout Guidelines                                           |    |

|    | 9.7      | Antenna Considerations                                            |    |

|    | 9.8      | Choosing the Most Suitable Interconnection with a Microcontroller |    |

|    | 9.9      | Interfacing CC2520 and MSP430F2618                                |    |

|    |          | Peripheral Interface (SPI)                                        |    |

|    | 10.1     | CSn                                                               |    |

|    | 10.2     | SCLK                                                              |    |

|    | 10.3     | SI                                                                |    |

|    | 10.4     | 80                                                                |    |

|    | 10.5     | SPI Timing Requirements                                           |    |

|    | GPIO.    |                                                                   | 35 |

|    | 11.1     | Reset Configuration of GPIO Pins                                  |    |

|    | 11.2     | GPIO as Input                                                     |    |

|    | 11.3     | GPIO as Output                                                    |    |

|    | 11.4     | Switching Direction on GPIO                                       |    |

|    | 11.5     | GPIO Configuration                                                |    |

|    |          | Modes                                                             |    |

|    | 12.1     | Switching Between Power Modes                                     |    |

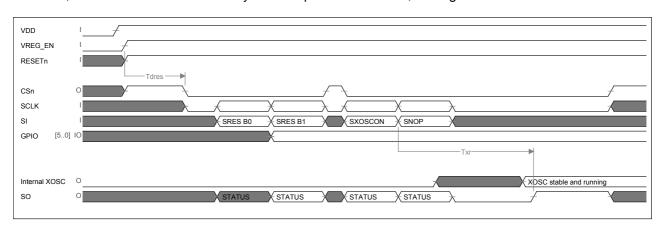

|    | 12.2     | Power Up Sequence Using RESETn (recommended)                      | 41 |

| 12.3             | Power Up With SRES                                   | 41 |

|------------------|------------------------------------------------------|----|

| 13 Instruc       | tion Set                                             | 43 |

| 13.1             | Definitions                                          | 43 |

| 13.2             | Instruction Descriptions                             | 43 |

| 13.3             | Instruction Set Summary                              | 51 |

| 13.4             | Status Byte                                          |    |

| 13.5             | Command Strobes                                      | 53 |

| 13.6             | Command Strobe Buffer                                | 53 |

| 14 Except        | ions                                                 |    |

| 14.1             | Exceptions on GPIO Pins                              | 56 |

| 14.2             | Predefined Exception Channels                        |    |

| 14.3             | Binding Exceptions to Instructions (command strobes) | 57 |

| 15 Memor         | у Мар                                                | 59 |

| 15.1             | FREG                                                 | 60 |

| 15.2             | SREG                                                 | 60 |

| 15.3             | TX FIFO                                              | 60 |

| 15.4             | RX FIFO                                              | 60 |

| 15.5             | MEM                                                  |    |

| 15.6             | Frame Filtering and Source Matching Memory Map       |    |

|                  | ncy and Channel Programming                          |    |

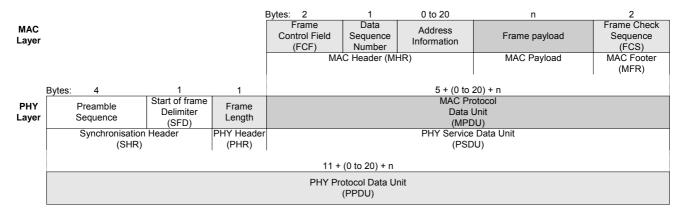

|                  | 02.15.4-2006 Modulation Format                       |    |

|                  | 02.15.4-2006 Frame Format                            |    |

| 18.1             | PHY Layer                                            |    |

| 18.2             | MAC Layer                                            |    |

|                  | nit Mode                                             |    |

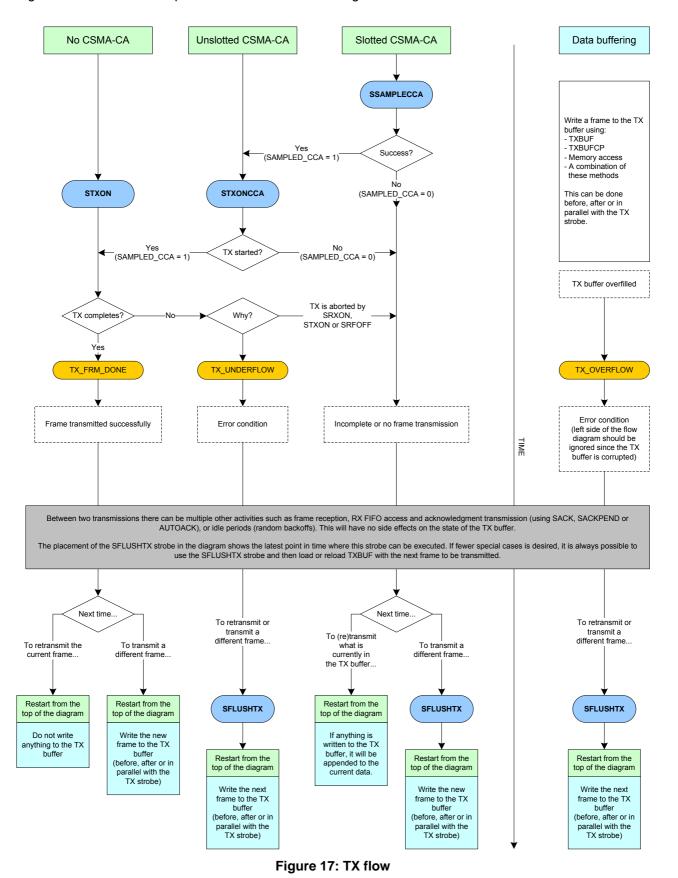

| 19.1             | TX Control                                           |    |

| 19.2             | TX State Timing                                      |    |

| 19.3             | TX FIFO Access                                       |    |

| 19.3.1           | Retransmission                                       |    |

| 19.3.2           | Error Conditions                                     |    |

| 19.4             | TX Flow Diagram                                      |    |

| 19.5             | Frame Processing                                     |    |

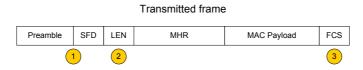

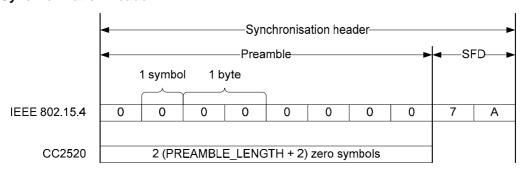

| 19.5.1           | Synchronization Header                               |    |

| 19.5.2           | Frame Length Field                                   |    |

| 19.5.3           | Frame Check Sequence                                 |    |

|                  | Exceptions                                           |    |

| 19.7             | Clear Channel Assessment                             |    |

| 19.8             | Output Power Programming                             |    |

| 19.9             | Tips And Tricks                                      |    |

| 20 Receiv        | e Mode                                               |    |

| -                | RX Control                                           |    |

| 20.2             | RX State Timing                                      |    |

| 20.3             | Frame Processing                                     |    |

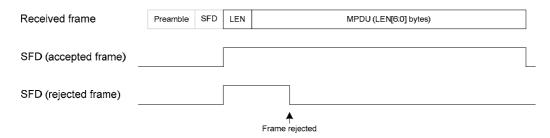

| 20.3.1<br>20.3.2 | Synchronization Header And Frame Length Fields       |    |

| 20.3.2           | Frame Filtering Source Address Matching              |    |

| 20.3.3           |                                                      |    |

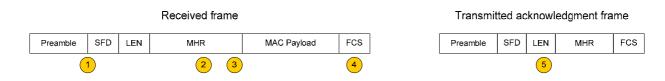

| 20.3.4           | Frame Check SequenceAcknowledgement Transmission     |    |

| 20.3.5           | RX FIFO Access                                       |    |

| 20.4             | Using the FIFO and FIFOP Signals                     |    |

| 20.4.1           | Error Conditions                                     |    |

| 20.4.2           | RSSI                                                 |    |

|                  |                                                      | 84 |

# CC2520 DATASHEET 2.4 GHZ IEEE 802.15.4/ZIGBEE® RF TRANSCEIVER SWRS068 – DECEMBER 2007

| 21 | Radio  | Control State Machine                   | 85  |

|----|--------|-----------------------------------------|-----|

| 22 |        | l Oscillator                            |     |

| 23 | Extern | al Clock Output                         | 88  |

| 24 |        | om Number Generation                    |     |

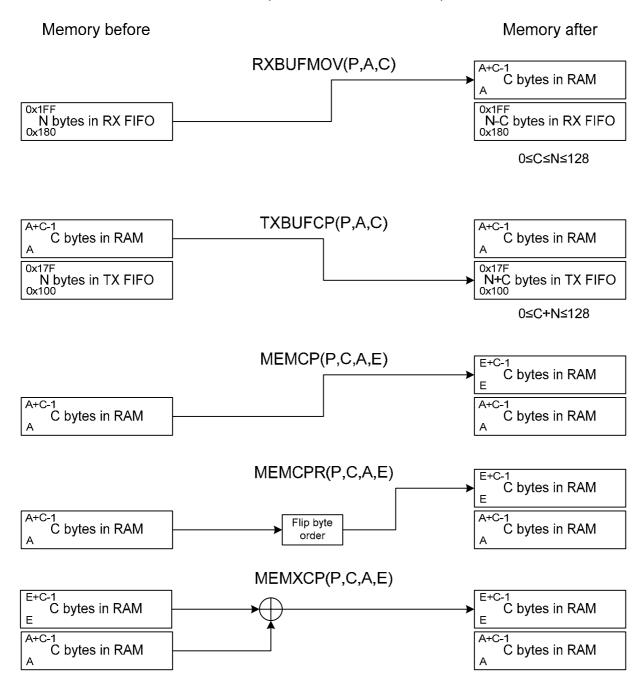

| 25 | Memo   | ry Management Instructions              | 91  |

| 2  | 5.1    | RXBUFMOV                                | 92  |

| 2  | 5.2    | TXBUFCP                                 | 92  |

| 2  | 5.3    | MEMCP                                   | 92  |

| 2  | 5.4    | MEMCPR                                  | 92  |

| 2  | 5.5    | MEMXCP                                  | 92  |

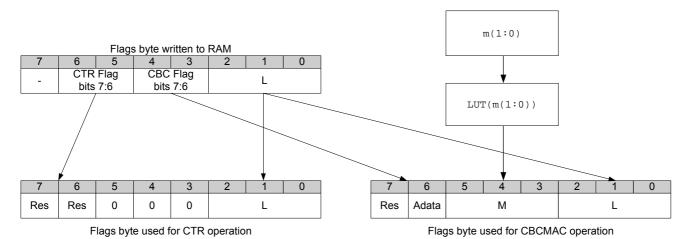

| 26 | Securi | ty Instructions                         | 93  |

| 2  | 6.1    | Decoding of the Flags Field in CC2520   | 93  |

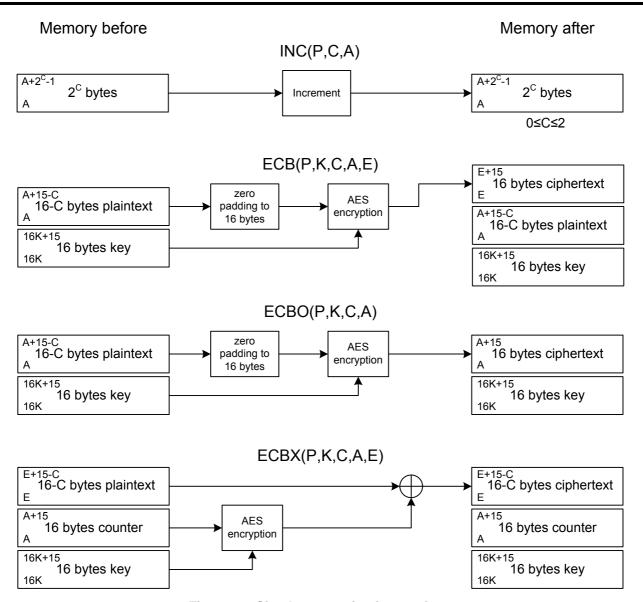

| 2  | 6.2    | INC                                     |     |

| 2  | 6.3    | ECB                                     | 94  |

| 2  | 6.4    | ECBO                                    | 95  |

| 2  | 6.5    | ECBX                                    | 95  |

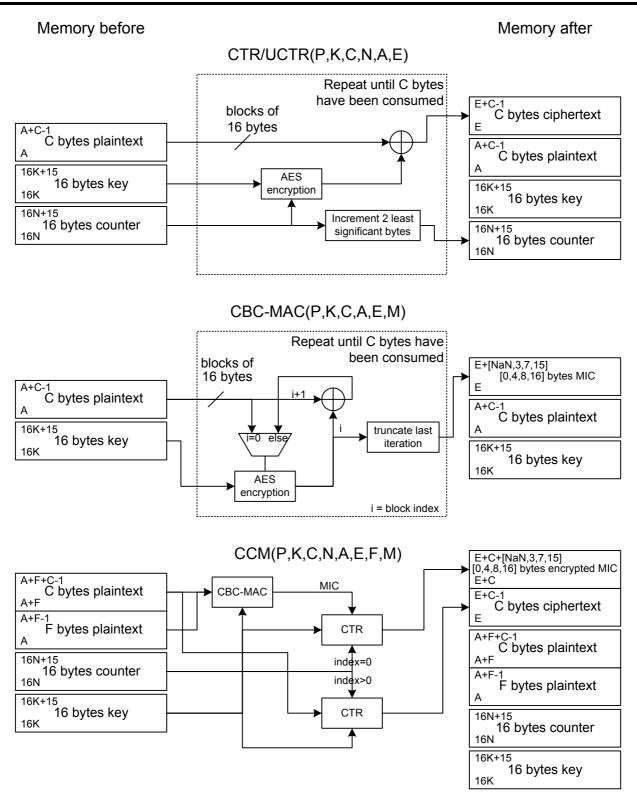

| 2  | 6.6    | CTR / UCTR                              | 96  |

| 2  | 6.7    | CBC-MAC                                 | 97  |

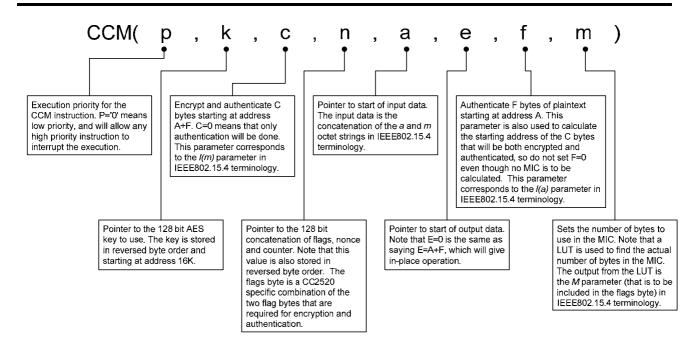

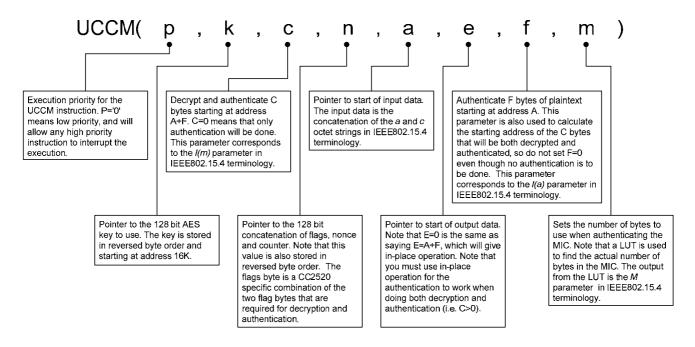

| 2  | 6.8    | CCM / UCCM                              | 97  |

|    | 26.8.1 | Inputs to the CCM and UCCM Instructions | 97  |

| 2  | 6.9    | Examples from IEEE802.15.4-2006         |     |

|    | 26.9.1 | Authentication Only Using CCM*          | 99  |

|    | 26.9.2 |                                         |     |

|    | 26.9.3 |                                         |     |

| 27 | Packe  | t Sniffing                              |     |

| 28 | Regist | ers                                     | 102 |

| 2  | 8.1    | Register Settings Update                |     |

| 2  | 8.2    | Register Access Modes                   |     |

| 2  | 8.3    | Register Descriptions                   |     |

| 29 | Datasl | neet Revision History                   |     |

| 30 |        | ging Information                        |     |

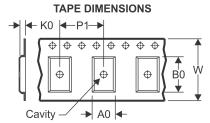

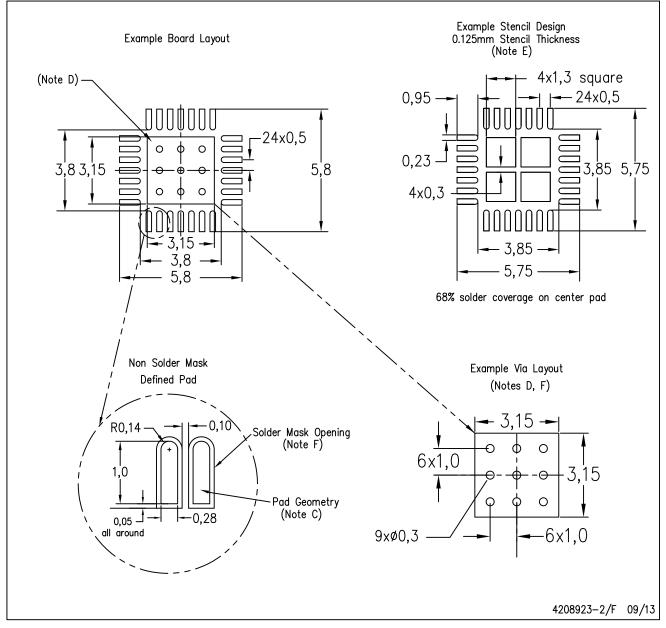

| 3  | 0.1    | Mechanical Data                         |     |

### **Abbreviations**

**AAF** Anti Aliasing Filter Acknowledge **ACK**

Analog to Digital Converter **ADC** ADI Analog-Digital Interface **AES** Advanced Encryption Standard

Automatic Gain Control **AGC**

Active Mode AM

Association of Radio Industries and Businesses **ARIB**

**BER** Bit Error Rate **BIST Built In Self Test**

**CBC-MAC** Cipher Block Chaining Message Authentication Code

Clear Channel Assessment CCA Counter mode + CBC-MAC CCM CDM Charged Device Model Code of Federal Regulations CFR

CHP Charge Pump

**CMOS** Complementary Metal Oxide Semiconductor

**CRC** Cyclic Redundancy Check

CSMA-CA Carrier Sense Multiple Access with Collision Avoidance

CTR Counter mode (encryption)

CW **Continuous Wave**

DAC Digital to Analog Converter

**Direct Current** DC DPU Data Processing Unit

**DSSS** Direct Sequence Spread Spectrum

Electronic Code Book (mode of AES operation) **ECB**

Electro Static Discharge ESD Equivalent Series Resistance **ESR**

European Telecommunications Standards Institute **ETSI**

EU **European Union EVM** Error Vector Magnitude

**FCC Federal Communications Commission**

**FCF** Frame Control Field **FCS** Frame Check Sequence **FFCTRL** FIFO and Frame Control

First In First Out **FIFO** Frequency Synthesizer FS Finite State Machine **FSM**

General Purpose Input/Output **GPIO**

Human Body Model **HBM HSSD** High Speed Serial Debug

I/O Input / Output

In-phase / Quadrature-phase I/O

**IEEE** Institute of Electrical and Electronics Engineers

IF Intermediate Frequency

Industrial. Scientific and Medical ISM

ITU-T International Telecommunication Union -

Telecommunication Standardization Sector

kilo bits per second kbps

Loop Back LB LF Loop Filter

Low-Noise Amplifier LNA Local Oscillator LO Low Pass Filter **LPF LPM** Low-Power Mode

5

LQI Link Quality Indication LSB Least Significant Bit / Byte

LUT Look-Up Table

MAC Medium Access Control MCU Micro Controller Unit

MFR MAC Footer MHR MAC Header

MIC Message Integrity Code

MISO Master In Slave Out

MM Machine Model

MOSI Master Out Slave In

MPDU MAC Protocol Data Unit

MSB Most significant Bit / Byte

MSDU MAC Service Data Unit

NA Not Available NC Not Connected

O-QPSK Offset - Quadrature Phase Shift Keying

PA Power Amplifier

PAN Personal Area Network

PCB Printed Circuit Board

PD Power Down, Phase Detector

PER Packet Error Rate

PHR PHY Header

PHY Physical Layer

PLL Phase Locked Loop

PQFP Plastic Quad FlatPack

PSDU PHY Service Data Unit

PUE Pull-Up Enable

QLP Quad Leadless Package

RAM Random Access Memory

RBW Resolution BandWidth

RF Radio Frequency

RHD Not actually an acronym. This is the package name used in TI.

RISC Reduced Instruction Set Computer

RoHS Restriction of Hazardous Substances Directive

ROM Read Only Memory

RSSI Received Signal Strength Indicator

RX Receive

SFD Start of Frame Delimiter SHR Synchronization Header

SI Serial In SO Serial Out

SPI Serial Peripheral Interface

S-PQFP Plastic Quad Flat Pack

T/R Transmit / Receive

TBD To Be Decided / To Be Defined

TX Transmit User Interface

VCO Voltage Controlled Oscillator VGA Variable Gain Amplifier

XOSC Crystal Oscillator

LR Low Rate

NaN Not any Number

# 2 References

- [1] IEEE std. 802.15.4 2003: Wireless Medium Access Control (MAC) and Physical Layer (PHY) specifications for Low Rate Wireless Personal Area Networks (LR-WPANs) http://standards.ieee.org/getieee802/download/802.15.4-2003.pdf

- [2] IEEE std. 802.15.4 2006: Wireless Medium Access Control (MAC) and Physical Layer (PHY) specifications for Low Rate Wireless Personal Area Networks (LR-WPANs) http://standards.ieee.org/getieee802/download/802.15.4-2006.pdf

- [3] CC2420 datasheet http://www.ti.com/lit/pdf/swrs041

- [4] NIST FIPS Pub 197: Advanced Encryption Standard (AES), Federal Information Processing Standards Publication 197, US Department of Commerce/N.I.S.T., November 26, 2001. <a href="http://csrc.nist.gov/publications/fips/fips197/fips-197.pdf">http://csrc.nist.gov/publications/fips/fips197/fips-197.pdf</a>

- [5] CC2520 reference designs http://focus.ti.com/docs/prod/folders/print/cc2520.html#applicationnotes

- [6] CC2520 Errata note http://www.ti.com/lit/pdf/swrz024

- [7] CC2520 Product folder http://focus.ti.com/docs/prod/folders/print/cc2520.html

- [8] NIST software package for randomness testing: http://csrc.nist.gov/rng/

- [9] The diehard software package for randomness testing: <a href="http://stat.fsu.edu/~geo/diehard.html">http://stat.fsu.edu/~geo/diehard.html</a>

- [10] MSP430F2618 Product folder http://focus.ti.com/docs/prod/folders/print/msp430f2618.html

- [11] 2.4 GHz Inverted F Antenna http://www.ti.com/lit/pdf/swru120

- [12] Antenna selection guide http://www.ti.com/lit/pdf/swra161

### 3 Features

### 2394-2507MHz transceiver

- DSSS transceiver

- 250kbps data rate, 2 MChip/s chip rate

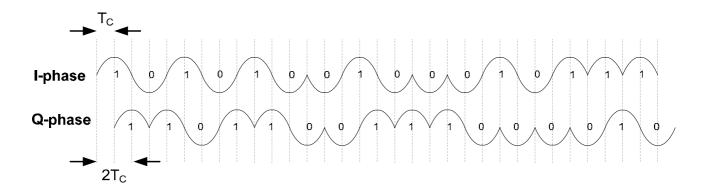

- O-QPSK with half sine pulse shaping modulation

- Very low current consumption

- RX (receiving frame, -50 dBm): 18.5 mA

- RX (waiting for frame): 22.3 mA

- TX (+5 dBm output power): 33.6 mA

- TX (0 dBm output power): 25.8 mA

- Three flexible power modes for reduced power consumption

- Low power fully static CMOS design

- Very good sensitivity (-98dBm)

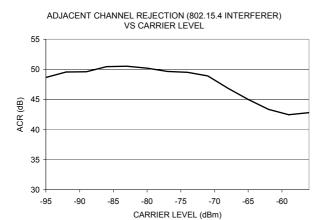

- High adjacent channel rejection (49 dB)

- High alternate channel rejection (54 dB)

- On chip VCO, LNA, PA and filters.

- Low supply voltage (1.8 3.8 V)

- Programmable output power up to +5 dBm

- I/Q direct conversion transceiver

### **Small Size**

- QFN 28 (RHD) package, 5 x 5 mm

- Very few external components

- o minimized number of passives

- Only reference crystal needed

- Clock output for other ICs to limit the number of crystals needed in a system

- · No external filters needed.

### Easy and Flexible User Interface

- 4-wire SPI

- Serial clock up to 8 MHz

- · 6 GPIO pins with full flexibility

- · Interrupt generator

- Full control of automatic responses to different events

- Embedded packet sniffer mode

- CC2420 compatibility mode

# **Data Processing Unit For Advanced Data Handling**

- Spacious (768 byte) on-chip RAM allows powerful on-chip frame processing

- 128 byte transmit data FIFO

- 128 byte receive data FIFO

- Full read and write access to RAM

- 128 bit AES

# IEEE 802.15.4 MAC Hardware Support

- Automatic preamble generator

- · Synchronization word insertion and detection

- CRC-16 computation and verification over the MAC payload

- · Frame filtering

- · Automatic ACK and setting of the pending-bit

- Clear Channel Assessment (CCA)

- · Energy detection / RSSI

- Link Quality Indication (LQI)

- Fully automatic MAC security (CTR, CBC-MAC, CCM)

# **Development Tools**

• See product folder [7]

# Suited For Use in Systems That Target Compliance to the Following Standards

- IEEE 802.15.4 PHY

- ETSI EN 300 328

- ETSI EN 300 440 class 2

- FCC CFR47 part 15

- ARIB STD-T66

# 4 Absolute Maximum Ratings

over operating free-air temperature range unless otherwise noted (1)

| PARAMETER                    | LIMITS                      | UNIT |

|------------------------------|-----------------------------|------|

| Supply voltage (2)           | -0.3 to 3.9                 | V    |

| Voltage on any digital pin   | -0.3 to VDD + 0.3 (Max 3.9) | V    |

| Voltage on 1.8 V pins        | -0.3 to 2.0                 | V    |

| Input RF level               | +10                         | dBm  |

| Storage temperature range    | -50 to 150                  | °C   |

| Reflow soldering temperature | 260                         | °C   |

| ESD HBM                      | 800                         | V    |

| ESD CDM                      | 500                         | V    |

| ESD MM                       | 100                         | V    |

Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress

ratings only, and functional operation of the device at these or any other conditions beyond those indicated under

"recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may

affect device reliability.

<sup>2)</sup> All voltage values are with respect to network ground terminal.

This device has limited built-in gate protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# 5 Electrical Characteristics

Note that these characteristics are only valid when using the recommended register settings presented in section 28.1.

# 5.1 Recommended Operating Conditions

| PARAMETER                | MIN | NOM | MAX | UNIT |

|--------------------------|-----|-----|-----|------|

| Operating supply voltage | 1.8 |     | 3.8 | V    |

| Ambient temperature      | -40 |     | 125 | °C   |

### 5.2 DC Characteristics

$T_A$  =25°C, VDD=3.0 V,  $f_c$ =2440 MHz if nothing else stated. All parameters measured on Texas Instruments' CC2520 EM 2.1 reference design with 50  $\Omega$  load.

| PARAMETER               | CONDITIONS                                           | MIN | TYP | MAX | UNIT   |

|-------------------------|------------------------------------------------------|-----|-----|-----|--------|

| Logic "1" input voltage | Valid for all pads (both GPIOs and fixed-input pads) |     |     | 80% | of VDD |

| Logic "0" input voltage | Valid for all pads (both GPIOs and fixed-input pads) | 30% |     |     | of VDD |

| Input pad hysteresis    | Only for fixed-input pads like RESET_N, CSn etc      |     | 0.5 |     | V      |

| Logic "0" input current | Input equals 0V                                      | -25 |     | 25  | nA     |

| Logic "1" input current | Input equals VDD                                     | -25 |     | 25  | nA     |

# 5.3 Wake-Up and Timing

T<sub>A</sub> =25°C, VDD=3.0 V, f<sub>c</sub> =2440 MHz if nothing else stated. All parameters measured on Texas Instruments' CC2520 EM 2.1 reference design with 50 Ω load.

| PARAMETER             | COMMENTS                                            | MIN | TYP | MAX | UNIT    |

|-----------------------|-----------------------------------------------------|-----|-----|-----|---------|

| LPM2 → AM time        | Internal regulator startup time + XOSC startup time |     | 0.3 |     | ms      |

| LPM1 → AM time        | XOSC startup time                                   |     | 0.2 |     | ms      |

| AM → RX time          |                                                     |     |     | 192 | μS      |

| AM → TX time          |                                                     |     |     | 192 | μS      |

| RX/TX turnaround time |                                                     |     |     | 192 | μS      |

| TX/RX turnaround time |                                                     |     |     | 192 | μS      |

| Radio bit rate        |                                                     |     | 250 |     | kbps    |

| Radio chip rate       |                                                     |     | 2.0 |     | MChip/s |

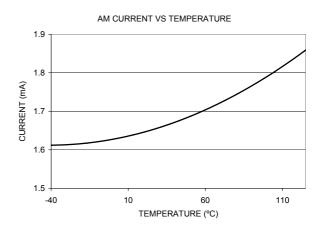

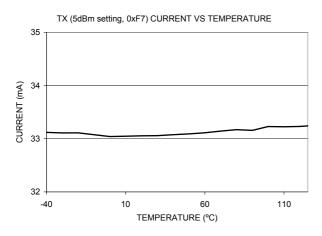

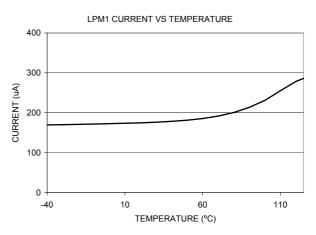

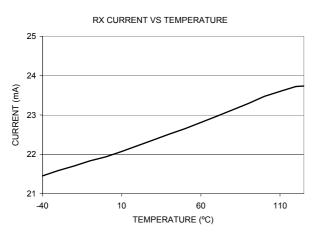

### 5.4 Current Consumptions

$T_A$  =25°C, VDD=3.0 V,  $f_c$  =2440 MHz if nothing else stated. All parameters measured on Texas Instruments' CC2520 EM 2.1 reference design with 50  $\Omega$  load.

| PARAMETER           | CONDITIONS                                                     | MIN | TYP  | MAX  | UNIT |

|---------------------|----------------------------------------------------------------|-----|------|------|------|

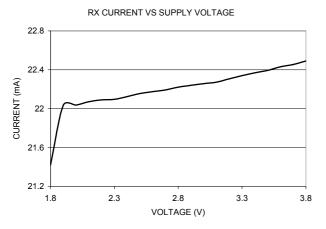

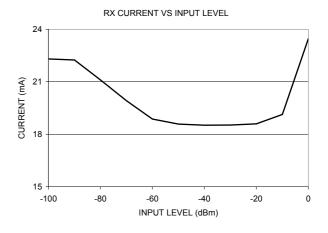

|                     | Wait for sync                                                  |     | 22.3 | 24.8 | mA   |

| Receive current     | $T_A$ =-40 to 125°C, VDD=1.8 to 3.8 V, $f_c$ =2394 to 2507 MHz |     |      | 26.3 | mA   |

| Receive current     | Wait for sync, Low-current RX setting                          |     | 18.8 |      | mA   |

|                     | Receving frame, -50 dBm input level                            |     | 18.5 |      | mA   |

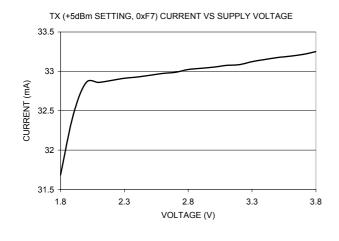

|                     | 0 dBm setting                                                  |     | 25.8 | 28.8 | mA   |

| Transmit current    | +5 dBm setting                                                 |     | 33.6 | 37.2 | mA   |

|                     | $T_A$ =-40 to 125°C, VDD=1.8 to 3.8 V, $f_c$ =2394 to 2507 MHz |     |      | 37.5 | mA   |

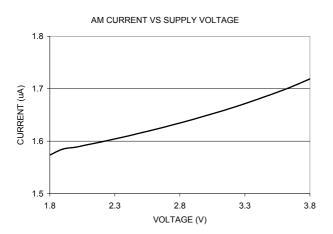

| Active Mode current | XOSC on, digital regulator on.                                 |     | 1.6  | 1.9  | mA   |

| Active wode current | $T_A$ =-40 to 125°C, VDD=1.8 to 3.8 V, $f_c$ =2394 to 2507 MHz |     |      | 2.6  | mA   |

| PARAMETER      | CONDITIONS                                                     | MIN | TYP | MAX  | UNIT |

|----------------|----------------------------------------------------------------|-----|-----|------|------|

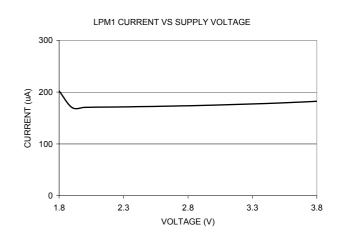

| LPM1 current   | XOSC off, digital regulator on. State retention.               |     | 175 | 250  | μА   |

| LPIVIT Current | $T_A$ =-40 to 125°C, VDD=1.8 to 3.8 V, $f_c$ =2394 to 2507 MHz |     |     | 1000 | μА   |

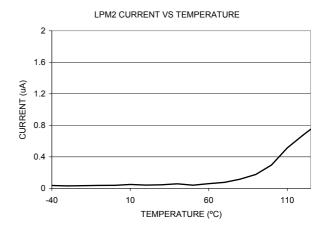

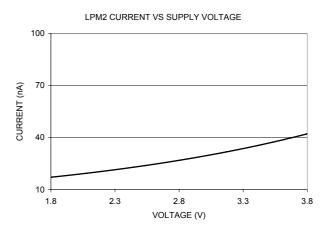

| LDM2 ourrent   | XOSC off, digital regulator off. No state retention.           |     | 30  | 120  | nA   |

| LPM2 current   | $T_A$ =-40 to 125°C, VDD=1.8 to 3.8 V, $f_c$ =2394 to 2507 MHz |     |     | 4.5  | μА   |

### 5.5 Receive Parameters

T<sub>A</sub> =25°C, VDD=3.0 V, f<sub>c</sub> =2440 MHz if nothing else stated. All parameters measured on Texas Instruments' CC2520 EM 2.1 reference design with 50 Ω load.

| PARAMETER                                                                                                                                           | 40 MHz if nothing else stated. All parameters measured on Texas Instruments' CC CONDITIONS          | MIN | TYP    | MAX | UNIT |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----|--------|-----|------|

| Desciver consitivity                                                                                                                                | [2] requires -85 dBm                                                                                | -99 | -98    | -95 | dBm  |

| Receiver sensitivity                                                                                                                                | $T_A$ =-40 to 125°C, VDD=1.8 to 3.8V, $f_c$ =2394 to 2507 MHz                                       |     |        | -88 | dBm  |

| Saturation                                                                                                                                          | [2] requires -20 dBm                                                                                |     | 6      |     | dBm  |

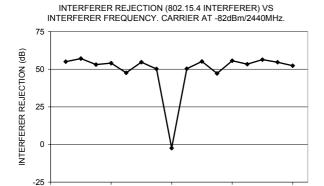

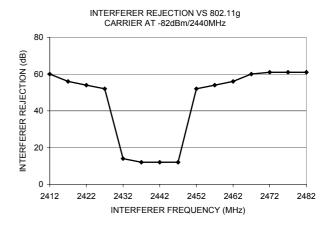

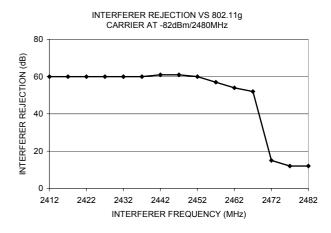

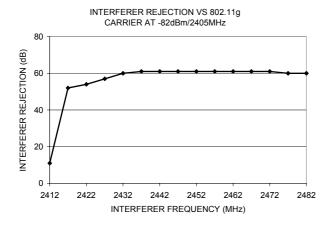

|                                                                                                                                                     | Wanted signal 3 dB above the sensitivity level, 802.15.4 modulated interferer at 802.15.4 channels: |     |        |     |      |

| Interferer Rejection                                                                                                                                | ±5 MHz from wanted signal. [2] requires 0 dB                                                        |     | 49     |     | dB   |

| interierer rejection                                                                                                                                | ±10 MHz from wanted signal. [2] requires 30 dB                                                      |     | 54     |     | dB   |

|                                                                                                                                                     | ±20MHz or above. Wanted signal at -82dBm.                                                           |     | 55     |     | dB   |

| Maximum Spurious<br>Emission                                                                                                                        | 30 – 1000 MHz                                                                                       |     | < -80  |     | dBm  |

| Conducted measurement in<br>a 50Ω single ended load.<br>Complies with EN 300 328,<br>EN 300 440 class 2, FCC<br>CFR47, Part 15 and ARIB<br>STD-T-66 | 1 – 12.75 GHz                                                                                       |     | -56    |     | dBm  |

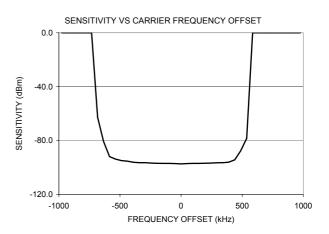

| Frequency error tolerance                                                                                                                           | Input level is 3 dB above sensitivity level.                                                        |     | +/-400 |     | kHz  |

| IIP3                                                                                                                                                |                                                                                                     |     | -24    |     | dBm  |

# 5.6 Frequency Synthesizer Parameters

$T_A$  =25°C, VDD=3.0 V,  $f_c$  =2440 MHz if nothing else stated. All parameters measured on Texas Instruments' CC2520 EM 2.1 reference design with 50  $\Omega$  load.

| PARAMETER                        | CONDITIONS                                                            | MIN  | TYP  | MAX  | UNIT   |

|----------------------------------|-----------------------------------------------------------------------|------|------|------|--------|

|                                  | At ±1 MHz offset from carrier                                         |      | -111 |      | dBc/Hz |

| Phase noise. Unmodulated carrier | At ±2 MHz offset from carrier                                         |      | -118 |      | dBc/Hz |

|                                  | At ±5 MHz offset from carrier                                         |      | -128 |      | dBc/Hz |

| RF Frequency range               | Programmable in 1 MHz steps. Use 5 MHz steps for compliance with [2]. | 2394 |      | 2507 | MHz    |

### 5.6.1 Transmit Parameters

$T_{A}$  =25°C, VDD=3.0 V,  $f_{c}$  =2440 MHz if nothing else stated. All parameters measured on Texas Instruments' CC2520 EM 2.1 reference design with 50  $\Omega$  load.

| PARAMETER                                                | CONDITIONS                                                                                  | MIN | TYP | MAX | UNIT |

|----------------------------------------------------------|---------------------------------------------------------------------------------------------|-----|-----|-----|------|

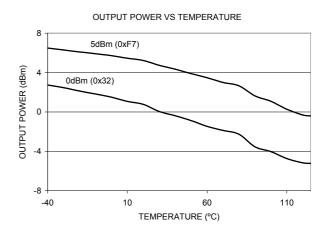

| Output power                                             | 0 dBm setting                                                                               | -3  | 1   | 5   | dBm  |

| Note: to reduce the output power variation over          | +5 dBm setting                                                                              | 2   | 5   | 7   | dBm  |

| temperature, it is suggested that different settings are | $T_A\text{=-}40$ to 85°C, VDD=2.0 to 3.8 V, $f_c$ =2394 to 2507 MHz                         | -3  |     | 8   | dBm  |

| used at different temperatures. The on-chip              | $T_A\text{=-}40 \text{ to } 85^{\circ}\text{C}$ , VDD=1.8 to 3.8 V, $f_c$ =2394 to 2507 MHz | -4  |     | 8   | dBm  |

| temperature sensor can be used for this purpose.         | $T_A\text{=-}40$ to 125°C, VDD=2.0 to 3.8 V, $f_c$ =2394 to 2507 MHz                        | -6  |     | 8   | dBm  |

| Please see section 5.11 for more information.            | $T_A\text{=-}40$ to 125°C, VDD=1.8 to 3.8 V, $f_c$ =2394 to 2507 MHz                        | -9  |     | 8   | dBm  |

| PARAMETER                                                                                                                                          | CONDITIONS                                                    | MIN | TYP | MAX | UNIT |

|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----|-----|-----|------|

| Largest spurious emission at maximum output power.                                                                                                 | 25 MHz – 1 GHz (outside restricted bands)                     |     | -40 |     | dBm  |

| Texas Instruments CC2520<br>EM reference design<br>complies with EN 300 328,                                                                       | 25 MHz – 1 GHz (within FCC restricted bands)                  |     | -53 |     | dBm  |

| EN 300 440, FCC CFR47 Part 15 and ARIB STDT-66.                                                                                                    | 47-74, 87.5-118, 174-230, 470-862 MHz (ETSI restricted bands) |     | -42 |     | dBm  |

| Transmit on 2480 MHz<br>under FCC at +5 dBm is<br>supported by duty-cycling,<br>or by reducing output                                              | 1800 MHz-1900 MHz (ETSI restricted band)                      |     | -56 |     | dBm  |

| power.                                                                                                                                             | 5150 MHz-5300 MHz (ETSI restricted band)                      |     | -54 |     | dBm  |

| The peak conducted spurious emission might violate ETSI and FCC                                                                                    | At 2483.5 MHz and above (FCC restricted band)                 |     |     |     |      |

| restricted band limits at                                                                                                                          | f <sub>c</sub> =2480 MHz, +5 dBm                              |     | -37 |     | dBm  |

| frequencies below 1GHz. All radiated spurious emissions are within the limits of ETSI/FCC/ARIB. Applications that must pass conducted requirements | f <sub>c</sub> =2480 MHz, 0 dBm                               |     | -41 |     | dBm  |

| are suggested to use a simple 50 Ω high pass filter between matching network and RF connector.                                                     | At 2·RF and 3·RF (FCC restricted band)                        |     | -54 |     | dBm  |

|                                                                                                                                                    | [2] requires max. 35%. Measured as defined by [2].            |     | ·   |     |      |

| Error Vector Magnitude (EVM)                                                                                                                       | +5 dBm setting. f <sub>c</sub> =IEEE 802.15.4 channels        |     | 6   |     | %    |

| (=)                                                                                                                                                | 0 dBm setting. $f_c$ =IEEE 802.15.4 channels                  |     | 2   |     | %    |

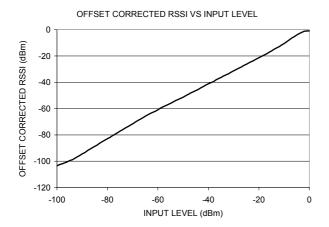

# 5.7 RSSI/CCA Parameters

$T_{A}$  =25°C, VDD=3.0 V,  $f_{c}$  =2440 MHz if nothing else stated. All parameters measured on Texas Instruments' CC2520 EM 2.1 reference design with 50  $\Omega$  load.

| PARAMETER         | COMMENTS                            | MIN | TYP  | MAX | UNIT |

|-------------------|-------------------------------------|-----|------|-----|------|

| RSSI range        |                                     |     | 100  |     | dB   |

| RSSI/CCA accuracy |                                     |     | +/-4 |     | dB   |

| RSSI/CCA offset   | Real RSSI = Register value - offset |     | 76   |     | dB   |

| LSB value         |                                     |     | 1    |     | dB   |

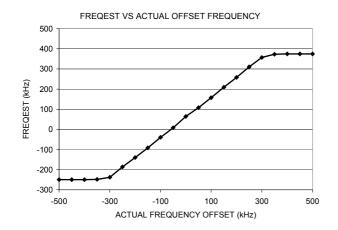

# 5.8 FREQEST Parameters

$T_{A}$  =25°C, VDD=3.0 V,  $f_{c}$  =2440 MHz if nothing else stated. All parameters measured on Texas Instruments' CC2520 EM 2.1 reference design with 50  $\Omega$  load.

| PARAMETER        | COMMENTS                                       | MIN | TYP    | MAX | UNIT |

|------------------|------------------------------------------------|-----|--------|-----|------|

| FREQEST range    |                                                |     | +/-300 |     | kHz  |

| FREQEST accuracy |                                                |     | +/-10  |     | kHz  |

| FREQEST offset   | Real frequency offset = FREQEST value - offset |     | 64     |     | kHz  |

| LSB value        |                                                |     | 7.8    |     | kHz  |

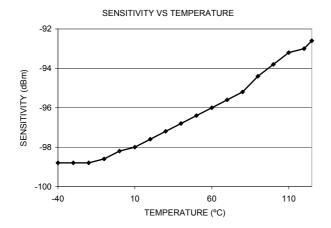

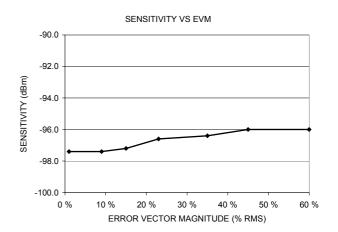

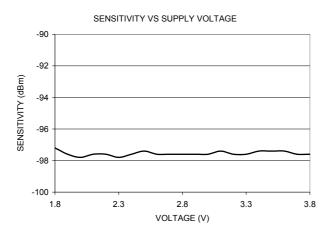

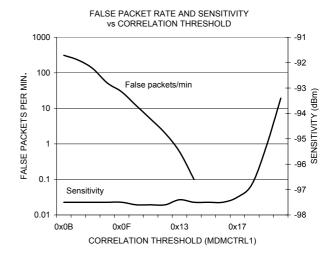

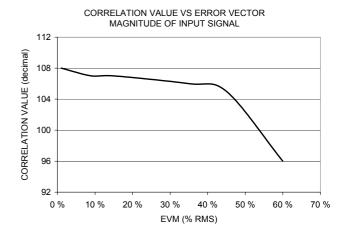

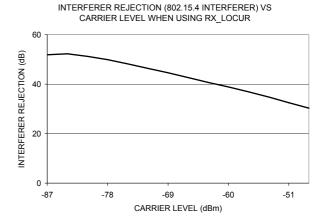

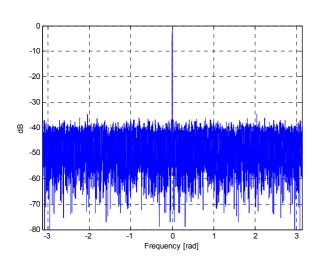

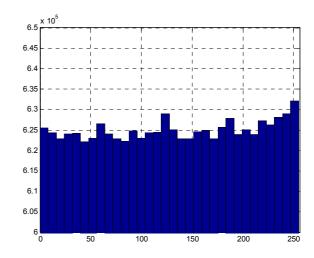

# 5.9 Typical Performance Curves

T<sub>A</sub> =25°C, VDD=3.0 V, f<sub>c</sub> =2440 MHz if nothing else stated. All parameters measured on Texas Instruments' CC2520 EM 2.1 reference design with 50 Ω load.

2440

INTERFERER FREQUENCY (MHz)

2460

2480

2400

2420

### 5.10 Low-Current Mode RX

Applications that spend more time waiting for an input signal than actually receiving it, might benefit from using the special low-current RX mode. This mode draws less current at the expense of sensitivity.

Note that when using this mode, neither RSSI nor CCA is valid. This means that these settings can not be used in conjunction with STXONCCA, for instance. Also note that the interferer rejection will drop at stronger input signal levels compared to when using the regular recommended settings.

Important: The low-current RX mode is only valid from -40 to 85°C!

### 5.10.1 Low-Current RX Mode Parameters

$T_A$  =25°C, VDD=3.0 V,  $f_c$ =2440 MHz if nothing else stated. All parameters measured on Texas Instruments' CC2520 EM 2.1 reference design with 50  $\Omega$  load.

| PARAMETER            | CONDITIONS                                                                                          | MIN   | TYP  | MAX | UNIT |  |  |

|----------------------|-----------------------------------------------------------------------------------------------------|-------|------|-----|------|--|--|

| RX current           | Wait for sync                                                                                       |       | 18.8 |     |      |  |  |

| Sensitivity          | [2] requires -85 dBm                                                                                | -90 d |      |     |      |  |  |

|                      | Wanted signal 3 dB above the sensitivity level, 802.15.4 modulated interferer at 802.15.4 channels: |       |      |     |      |  |  |

| Interferen Deientien | ±5 MHz from wanted signal. [2] requires 0 dB                                                        |       | 52   |     | dB   |  |  |

| Interferer Rejection | ±10 MHz from wanted signal. [2] requires 30 dB                                                      | 54    |      |     | dB   |  |  |

|                      | ±20MHz or above.                                                                                    |       | 55   |     | dB   |  |  |

Table 1: Low-current RX mode. Use in addition to regular recommended settings.

| Register | Setting (hex) | Comment                                                 |

|----------|---------------|---------------------------------------------------------|

| RXCTRL   | 33            | Reduces sensitivity and current consumption             |

| FSCTRL   | 12            | Reduces current consumption and valid temperature range |

| AGCCTRL2 | EB            | Reduces sensitivity and current consumption             |

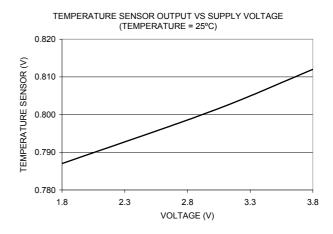

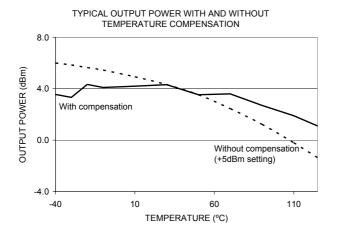

# 5.11 Optional Temperature Compensation of TX

Using the on-chip temperature sensor (or any other sensor), it is possible to adapt the settings to the actual temperature. This will reduce the variation in output power over temperature, which in the range -40°C to 125°C can be significant.

For this purpose, a TX setting only suited for high-temperature operation has been found (F7125deg). This setting should only be used above 70 degrees, but will significantly reduce the drop in output power at high temperatures.

Table 2: F7125deg setting, only suited for high temperature operation (only changes from recommended settings shown)

| Register | Setting (hex) Comment |                                              |  |  |

|----------|-----------------------|----------------------------------------------|--|--|

| TXCTRL   | 94                    | Increased output power at high temperatures. |  |  |

| FSCTRL   | 7B                    | Increased output power at high temperatures. |  |  |

Table 3: Suggested TXPOWER register settings for different temperatures

| Temperature             | -40 | -30 | -20 | -10 | 10  | 30  | 50  | 70       | 90       | 110      | 125      | °C  |

|-------------------------|-----|-----|-----|-----|-----|-----|-----|----------|----------|----------|----------|-----|

| Recommended<br>Setting  | 13  | 13  | AB  | AB  | F2  | F7  | F7  | F7125deg | F7125deg | F7125deg | F7125deg | -   |

| Typical Output<br>Power | 3.6 | 3.3 | 4.3 | 4.1 | 4.2 | 4.3 | 3.5 | 3.6      | 2.7      | 1.9      | 1.1      | dBm |

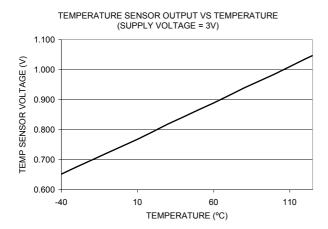

### 5.11.1 Using the Temperature Sensor

The on-chip temperature sensor can be accessed via the GPIO0 and GPIO1 pins by following this procedure:

- Configure GPIO0 and GPIO1 as inputs by writing 0x80 to the GPIOCTRL0 and GPIOCTRL1 registers.

- Enable analog output functionality for these two pins by setting GPIOCTRL.GPIO ACTRL='1'.

- Select temperature sensor output by writing 0x01 to the ATEST register. This will make GPIO1 output GND and GPIO0 will output a voltage proportional to the temperature.

- Use an ADC in the microcontroller to measure the output voltage on GPIO0 and then calculate the temperature.

The output from the temperature sensor is shown in graph form in section 5.9, but as a basis for calculating the temperature, the following numbers can be used:

Tc=-40 - 125°C, VDD=1.8 - 3.8 V

| Parameter                                                        | Min | Тур   | Max | Unit    |

|------------------------------------------------------------------|-----|-------|-----|---------|

| Temp sensor voltage at 25°C                                      |     | 0.8   |     | V       |

| Temp. sens. output vs temperature                                |     | 25    |     | mV/10°C |

| Temp. sens. output vs supply voltage                             |     | 6     |     | mV/V    |

| Temp. sens accuracy no calibration (at fixed voltage)            |     | +/-12 |     | °C      |

| Temp, sens. accuracy with 1-point calibration (at fixed voltage) |     | +/-1  |     | °C      |

# 6 Crystal Specific Parameters

# 6.1 Crystal Requirements

| PARAMETER                              | CONDITIONS                                                                                                                                   | MIN  | TYP | MAX | UNIT |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| Crystal frequency                      |                                                                                                                                              |      | 32  |     | MHz  |

| Crystal frequency accuracy requirement | Including initial tolerance, aging and temperature dependency, as specified by [2]. Can be relaxed using on-chip crystal tuning (see below). | - 40 |     | 40  | ppm  |

| ESR                                    |                                                                                                                                              |      |     | 60  | Ohm  |

| C <sub>0</sub>                         |                                                                                                                                              |      |     | 7   | pF   |

| CL                                     |                                                                                                                                              |      |     | 16  | pF   |

# 6.2 On-chip Crystal Frequency Tuning

| PARAMETER                                 | CONDITIONS                                  | MIN TYP                             | MAX | UNIT |

|-------------------------------------------|---------------------------------------------|-------------------------------------|-----|------|

| Crystal tuning range (C <sub>tune</sub> ) | Only adding capacitance is possible         | 7                                   |     | pF   |

| Crystal tuning step size                  |                                             | 0.4                                 |     | pF   |

| Crystal tuning drift                      | In % of applied tuning                      | +/-10                               |     | %    |

| CRYSTAL TUNIN                             | NG USING CC2520 EM 2.1 REFERENCE DESIGI     | N (NX3225DA, C <sub>L</sub> = 16 pF | ):  |      |

| Start-up time                             |                                             | 0.2                                 |     | ms   |

| Crystal tuning step size                  | NDK crystal NX3225DA, C <sub>L</sub> =16 pF | 3                                   |     | ppm  |

| Crystal tuning range                      |                                             | -45                                 |     | ppm  |

| CRYSTAL T                                 | UNING USING OTHER CRYSTALS, ALL NUMBE       | RS ARE ESTIMATES :                  |     | •    |

| Start-up time                             | NDV - LINVIGOEDA O 40 E                     | 0.2                                 |     | ms   |

| Crystal tuning step size                  | NDK crystal NX4025DA, C <sub>L</sub> =13 pF | 8                                   |     | ppm  |

| Crystal tuning range                      |                                             | -120                                |     | ppm  |

| Start-up time                             |                                             | 0.1                                 |     | ms   |

| Crystal tuning step size                  | NDK crystal NX5032SA, C <sub>L</sub> =10 pF | 10                                  |     | ppm  |

| Crystal tuning range                      |                                             | -160                                |     | ppm  |

See section 22 for further details on using the crystal oscillator.

# 7 Pinout

Figure 1: Pinout of CC2520 (top view)

Table 4: CC2520 Pinout

| Signal  | Pin#                        | Туре | Description                                     |  |  |  |  |  |

|---------|-----------------------------|------|-------------------------------------------------|--|--|--|--|--|

| SPI     |                             |      |                                                 |  |  |  |  |  |

| SCLK    | 28                          | 1    | SPI interface: Serial Clock. Maximum 8 MHz      |  |  |  |  |  |

| SO      | 1                           | 0    | SPI interface: Serial Out                       |  |  |  |  |  |

| SI      | 2                           | 1    | SPI interface: Serial In                        |  |  |  |  |  |

| CSn     | 3                           | 1    | SPI interface: Chip Select, active low          |  |  |  |  |  |

|         | General Purpose digital I/O |      |                                                 |  |  |  |  |  |

| GPIO0   | 10                          | Ю    | General purpose digital I/O                     |  |  |  |  |  |

| GPIO1   | 9                           | Ю    | General purpose digital I/O                     |  |  |  |  |  |

| GPIO2   | 7                           | Ю    | General purpose digital I/O                     |  |  |  |  |  |

| GPIO3   | 6                           | Ю    | General purpose digital I/O                     |  |  |  |  |  |

| GPIO4   | 5                           | Ю    | General purpose digital I/O                     |  |  |  |  |  |

| GPIO5   | 4                           | Ю    | General purpose digital I/O                     |  |  |  |  |  |

|         |                             |      | Misc                                            |  |  |  |  |  |

| RESETn  | 25                          | 1    | External reset pin, active low                  |  |  |  |  |  |

| VREG_EN | 26                          | 1    | When high, digital voltage regulator is active. |  |  |  |  |  |

| NC      | 15,<br>18, 21               |      | Not Connected.                                  |  |  |  |  |  |

| Signal       | Pin #                       | Туре                    | Description                                                                                                                |  |  |  |  |  |

|--------------|-----------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Analog       |                             |                         |                                                                                                                            |  |  |  |  |  |

| RBIAS        | 23                          | Analog IO               | External precision bias resistor for reference current. 56 k $\Omega$ , $\pm 1\%$                                          |  |  |  |  |  |

| RF_N         | 19                          | RF IO                   | Negative RF input signal to LNA in receive mode Negative RF output signal from PA in transmit mode                         |  |  |  |  |  |

| RF_P         | 17                          | RF IO                   | Positive RF input signal to LNA in receive mode Positive RF output signal from PA in transmit mode                         |  |  |  |  |  |

| XOSC32M_Q1   | 13                          | Analog IO               | Crystal oscillator pin 1                                                                                                   |  |  |  |  |  |

| XOSC32M_Q2   | 12                          | Analog IO               | Crystal oscillator pin 2                                                                                                   |  |  |  |  |  |

| Power/ground |                             |                         |                                                                                                                            |  |  |  |  |  |

| AVDD         | 11,<br>14,<br>16,<br>20, 22 | Power<br>(Analog)       | 1.8 V to 3.8 V analog power supply connections                                                                             |  |  |  |  |  |

| AVDD_GUARD   | 24                          | Power<br>(Analog)       | Power supply connection for digital noise isolation and digital voltage regulator.                                         |  |  |  |  |  |

| DCOUPL       | 27                          | Power<br>(Digital)<br>O | 1.6 V to 2.0 V digital power supply output for decoupling.  Note: this pin can not be used to supply any external devices. |  |  |  |  |  |

| DVDD         | 8                           | Power<br>(Digital)      | 1.8 V to 3.8 V digital power supply for digital pads.                                                                      |  |  |  |  |  |

| AGND         | Die                         | Ground                  |                                                                                                                            |  |  |  |  |  |

|              | pad                         | (Analog)                |                                                                                                                            |  |  |  |  |  |

# 8 Functional Introduction

# 8.1 Integrated 2.4 GHz IEEE 802.15.4 Compliant Radio

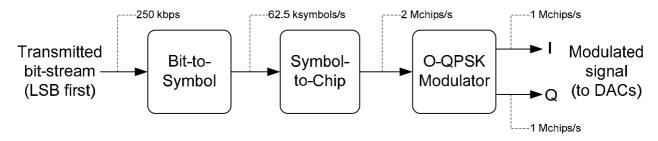

CC2520 features a Direct Conversion Transceiver operating in the 2.4 GHz band with excellent receiver sensitivity and robustness to interferers. The CC2520 radio complies with the IEEE 802.15.4 PHY specification. The radio has 250 kbps data rate, 2 Mchip/s chip rate, and is suitable for systems targeting compliance with worldwide radio frequency regulations covered by ETSI EN 300 328 and EN 300 440 class 2 (Europe), FCC CFR47 Part 15 (US) and ARIB STD-T66 (Japan).

# 8.2 Comparison to CC2420

CC2520 represents significant improvement over the CC2420 features and performance. A comparison is given in the table below.

Table 5: Comparison of CC2420 and CC2520

| Feature                       | CC2420                                                                              | CC2520                                                                                                                                                                                                          |  |  |

|-------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Standard                      | IEEE 802.15.4-2003                                                                  | IEEE 802.15.4-2006                                                                                                                                                                                              |  |  |

| Maximum output power          | 0 dB                                                                                | +5 dB                                                                                                                                                                                                           |  |  |

| Typical sensitivity           | -95 dBm                                                                             | -98 dBm                                                                                                                                                                                                         |  |  |

| General clock output          | No                                                                                  | Yes, configurable frequency 1-16MHz                                                                                                                                                                             |  |  |

| User interface                | Command strobes and configuration registers. All user control goes through the SPI. | Instruction set (which includes the command strobes as a subset) and configuration registers. Command strobes may be triggered by GPIO pins, which gives excellent timing control. Improved status information. |  |  |

| Register access               | Possible without crystal oscillator running.                                        | Only possible when crystal oscillator is running.                                                                                                                                                               |  |  |

| Digital inputs                | No Schmitt triggers                                                                 | Schmitt triggers on all digital inputs.                                                                                                                                                                         |  |  |

| Digital outputs               | Fixed configuration                                                                 | Highly flexible and configurable                                                                                                                                                                                |  |  |

| Start up                      | Manual start of XOSC                                                                | XOSC starts automatically after reset (by reset_n pin). Manual start of XOSC after SRES instruction.                                                                                                            |  |  |

| Crystal frequency             | 16 MHz                                                                              | 32 MHz                                                                                                                                                                                                          |  |  |

| Packet sniffing               | No hardware support                                                                 | Hardware support for non-intrusive sniffing of both transmitted and received frames.                                                                                                                            |  |  |

| Maximum SPI clock speed       | 10 MHz                                                                              | 8 MHz                                                                                                                                                                                                           |  |  |

| RAM size                      | 364 byte                                                                            | 768 byte                                                                                                                                                                                                        |  |  |

| Operating voltage             | 2.1 – 3.6 V                                                                         | 1.8 – 3.8 V                                                                                                                                                                                                     |  |  |

| Maximum operating temperature | 85°C                                                                                | 125°C                                                                                                                                                                                                           |  |  |

| Security                      | Limited flexibility                                                                 | Highly flexible security instructions. More RAM available allows more flexible processing.                                                                                                                      |  |  |

| Package                       | QLP-48, 7x7 mm                                                                      | QFN 28 (RHD), 5x5 mm                                                                                                                                                                                            |  |  |

| RF frequency range            | 2400-2483.5 MHz                                                                     | 2394-2507 MHz                                                                                                                                                                                                   |  |  |

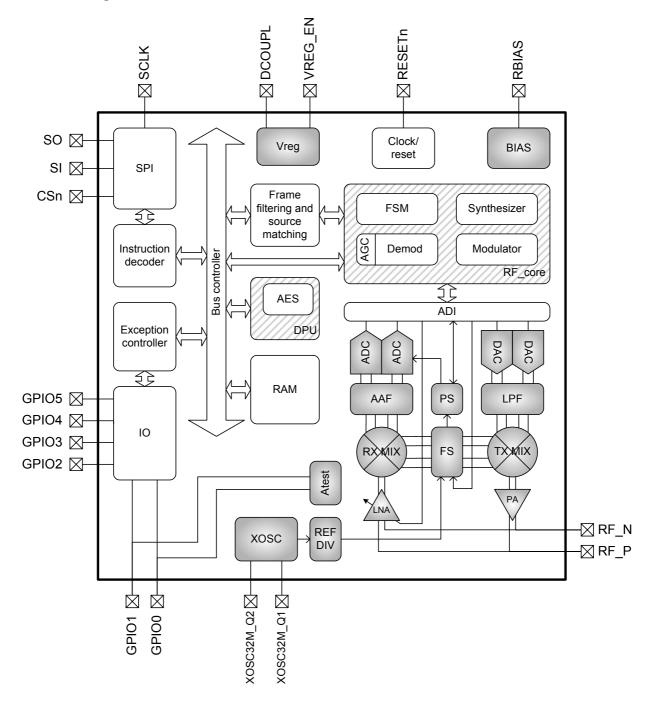

# 8.3 Block Diagram

Figure 2: CC2520 block diagram

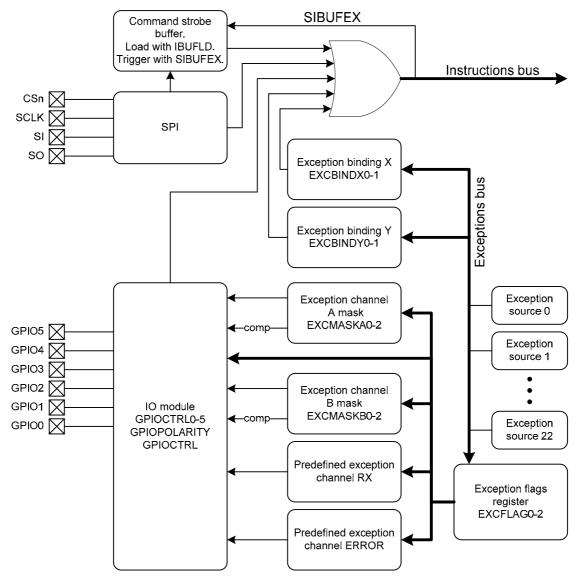

CC2520 is typically controlled by a microcontroller connected to the **SPI** and some GPIOs. The microcontroller will send instructions to CC2520 and it is the responsibility of the **instruction decoder** to execute the instructions or pass them on to other modules.

The execution of an instruction or external events (e.g. reception of a frame) may result in one or more exceptions. The exceptions provide a very flexible mechanism for automating tasks. They can for instance be used to trigger execution of other instructions or they can be routed out to GPIO pins and used as interrupt signals to the microcontroller. The **exception controller** is responsible for handling of the exceptions.

The microcontroller will typically be connected to one or more of the GPIO pins. The function of each pin is independently controlled by the **IO** module based on register settings. It is possible to observe a large number of internal signals on the GPIO pins. The GPIO pins can also be configured as inputs and used to trigger the execution of certain instructions. This would typically be used when the microcontroller needs to precisely control the timing of an instruction.

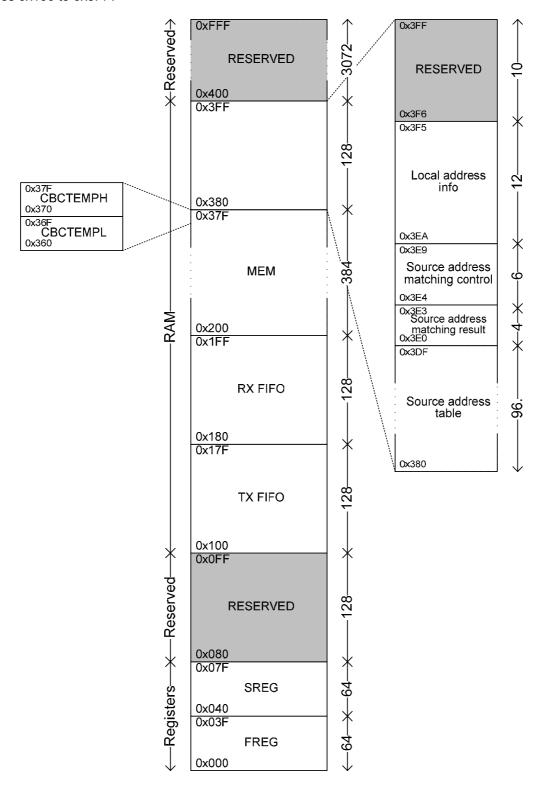

The **RAM** module contains memory which is used for receive and transmit FIFOs (in fixed address ranges) and temporary storage for other data. There are separate instructions for general memory access and FIFO access.

The **data processing unit (DPU)** is responsible for execution of the more advanced instructions. The DPU includes an AES core, which is used while executing the security instructions. Memory management (copying, incrementing etc.) is also performed by the DPU.

The Clock/Reset module generates the internal clocks and reset signals.

The **RF core** contains several submodules that support and control the analog radio modules.

The **FSM** submodule controls the RF transceiver state, the transmitter and receiver FIFOs and most of the dynamically controlled analog signals such as power up / down of analog modules. The FSM is used to provide the correct sequencing of events (such as performing an FS calibration before enabling the receiver). Also, it provides step by step processing of incoming frames from the demodulator: reading the frame length, counting the number of bytes received, checks the FCS, and finally, optionally handles automatic transmission of ACK frames after successful frame reception. It performs similar tasks in TX including performing an optional CCA before transmission and automatically going to RX after the end of transmission to receive an ACK frame. Finally, the FSM controls the transfer of data between modulator/demodulator and the TXFIFO/RXFIFO in RAM.

The **modulator** transforms raw data into I/Q signals to the transmitter DAC. This is done in compliance with the IEEE 802.15.4 standard.

The **demodulator** is responsible for retrieving the sent data from the received signal.

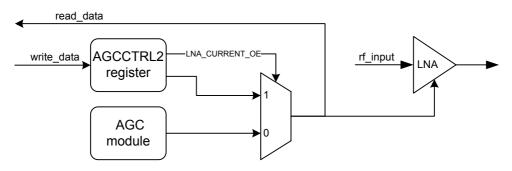

The amplitude information from the demodulator is used by the **automatic gain control (AGC)**. The AGC adjusts the gain of the analog LNA so that the signal level within the receiver is approximately constant..

The **frame filtering and source matching** supports the FSM in RF\_core by performing all operations needed in order to do frame filtering and source address matching, as defined by IEEE 802.15.4.

The **xosc** module interfaces the crystal which is connected to the XOSC32M\_Q1 and XOSC32M\_Q2 pins. The xosc module generates a clock for the digital part and RF system, and implements the programmable crystal frequency tuning.

The **BIAS** module generates voltage and current references. It relies on a high precision (1%)  $56k\Omega$  external resistor which is shown in the application circuit in Figure 3.

The **TX DACs** convert the digital baseband signal to analog signals.

After LPF the signal is fed to the **TXMIX** module, which is an up-converting complex mixer.

The **PA** amplifies the RF signal up to a maximum of ~5dBm during TX.

The **LNA** amplifies the received RF signal. The gain is controlled by the digital AGC module so that optimum sensitivity and interferer rejection is achieved.

The RXMIX module is a complex down-mixer that converts the RF signal to a baseband signal.

A passive anti-aliasing filter (AAF) low pass filters the signal after down mixing.

The low pass filtered I and Q signals and digitized by the ADC.

# CC2520 DATASHEET 2.4 GHZ IEEE 802.15.4/ZIGBEE® RF TRANSCEIVER SWRS068 – DECEMBER 2007

The frequency synthesizer (FS) generates the carrier wave for the RF signal.

The **voltage regulator (Vreg)** provides a 1.8V supply voltage to the digital core. It contains a current limiter, which is enabled for currents above  $\sim$ 32mA.

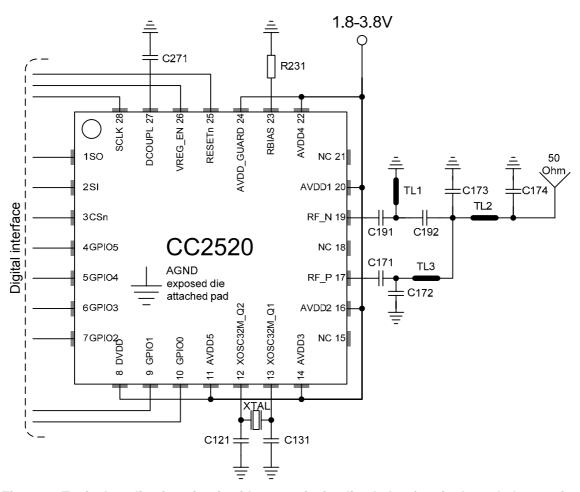

# 9 Application Circuit

Very few external components are required for the operation of CC2520. A typical application circuit is shown in Figure 4. Note that it does not show how the board layout should be done. The board layout will greatly influence the RF performance of CC2520.

This section is meant as an introduction only. For further details, see the reference design, which includes complete board layouts and bill of materials with manufacturer and part numbers. The reference design can be downloaded from the CC2520 product folder [7].

Note that decoupling capacitors are not shown in the figure below. See the reference design for complete bill of materials.

Figure 3: Typical application circuit with transmission line balun for single-ended operation

See the antenna selection guide [12] for further details on other compact and low-cost alternatives.

# 9.1 Input / Output Matching

The RF input/output is high impedance and differential.

When using an unbalanced antenna such as a monopole, a balun should be used in order to optimize performance. The balun can be implemented using low-cost discrete inductors and capacitors only or in combination with transmission lines replacing the discrete inductors.

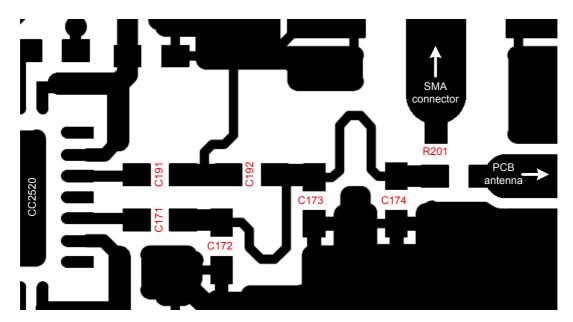

Figure 4 shows the balun implemented in a two-layer reference design. It consists of three transmission lines (L1, L2 and L3) and the discrete components C191, C171, C192, C173 and C174. The circuit will present the optimum RF termination to CC2520 with a  $50\Omega$  load on the antenna connection.

Figure 4: Actual board layout of the RF section of the reference design (rev 2.1).

### 9.2 Bias Resistor

The bias resistor R231 is used to set an accurate bias current. A high precision ( $\pm 1\%$ ) 56k $\Omega$  resistor should be used.

### 9.3 Crystal

An external 32MHz crystal with two loading capacitors (C121 and C131) is used for the crystal oscillator.

It is possible to feed a single-ended signal to the XOSC32M\_Q1 pin and thus not use a crystal.

# 9.4 Digital Voltage Regulator

The on chip voltage regulator supplies 1.8 V to the digital part of CC2520. C271 is a decoupling capacitor for the voltage regulator. Note that this should not be used to provide power to other IC's.

# 9.5 Power Supply Decoupling and Filtering

Proper power supply decoupling must be used for optimum performance. This is shown as a lumped capacitor C1 in Figure 4. The placement and size of the decoupling capacitors and the power supply filtering are very important to achieve the best performance in an application. TI provides a compact reference design that should be followed very closely.

# 9.6 Board Layout Guidelines

It is highly recommended to copy the board layout from the reference design [5].

- It is recommended to use star topology for the power supplies to CC2520.

- The power supply decoupling capacitor C1 is a lumped component. On the actual board layout there should be separate decoupling capacitors as close to each of the power pins as possible.

- The balun is highly layout sensitive. The inductors in Figure 4 are actually transmission lines embedded in the PCB and their values must be adapted according to the board layout. The values of the capacitors C192, C172, C173 and C174 must also be adapted to the actual board layout.

- The GPIO pins can be configured to use internal pull-up resistors. They are not enabled after a

reset or in LPM2. Remember to take the default GPIO configuration into consideration when

connecting these signals, because there will be some time before the MCU is able to change the

configuration. In LPM2 GPIO5 (which is configured as an input) should be connected to either

- ground or VDD. The other GPIO pins should be grounded or high impedance. Failing to do this, will result in significantly higher current consumption than necessary.

- The SO pin is configured as an input when CSn is high or the device is in reset or LPM2. This makes it possible to connect multiple SPI slaves to one SPI master. This pin should not be left floating when in LPM2, as this will draw more current than necessary. If the voltage level can not be controlled in any other way, use a 1MOhm pull-down resistor.

- The crystal input lines should be routed as far away from each other as practically possible.

- The NC pins can be left floating.

- Glitches on the digital inputs may create serious issues in a system design. The digital input pads have Schmitt-triggers to help make them less sensitive to glitches, but the board layout should still avoid routing the digital input lines close to other noisy signals.

### 9.7 Antenna Considerations

The reference design contains two antenna options. As default, the SMA connector is connected to the balun through a  $0\Omega$  resistor. This resistor can be soldered off and rotated  $90^{\circ}$  clockwise in order to connect to the PCB antenna, which is a planar inverted F antenna (PIFA).

Note that all testing and characterization has been done using the SMA connector. The PCB antenna has only been functionally tested by establishing a link between two EMs. In our experiment, the PCB antenna gave approximately the same range as when using an antenna connected to the SMA connector.

Please refer to the antenna selection guide [12] and the Inverted F antenna app note [11] for further details.

### 9.8 Choosing the Most Suitable Interconnection with a Microcontroller

- Connect the 4 SPI signals; CSn, SCLK, SI and SO to the microcontroller.

These signals are required in order to configure CC2520 and exchange data with it.

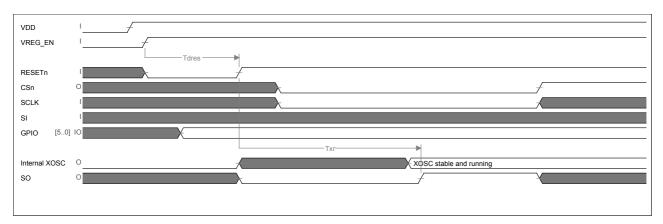

- Connect RESETn to the microcontroller. Using the RESETn signal is the recommended way to reset CC2520 for instance after powering up. If saving a pin is critical, the RESETn pin can be connected to VDD. The CC2520 can still be reset with the SRES command strobe. This will also require a manual start of the crystal oscillator by issuing a SXOSCON command strobe.

- Connecting VREG\_EN to the microcontroller will make it possible to put CC2520 into LPM2 to save power. VREG\_EN may be connected to VDD and thus always leave the regulator on. If power saving is not important in the target application, this may be an acceptable way of saving a pin.

- Connecting one or more of the GPIOs to the microcontroller is optional.

The number of GPIOs to connect depends on the application. Connecting more GPIOs to the microcontroller generally gives more flexibility and less SPI traffic because it reduces the need to keep reconfiguring the GPIOs for different uses.

- If CC2520 will be providing clock to the microcontroller, GPIO0 should be connected to the clock input of the microcontroller. After reset, GPIO0 will output a 1MHz clock signal with 50/50 duty cycle.

The digital IO of CC2520 is described in more detail from section 12.

### 9.9 Interfacing CC2520 and MSP430F2618

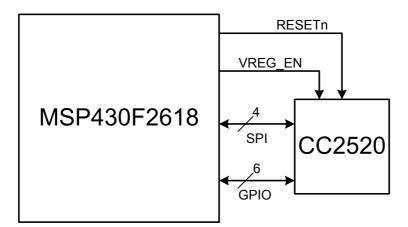

The MSP430F2618 is well suited for use with the CC2520. The suggested interfacing of these two chips is given in Table 5. The interconnections shown in Table 6 are exactly the same as is used in the CC2520 development kit [5].

31

Table 6: Interconnection of MSP430F2618 and CC2520

| CC2520  | MSP430F2618            |  |  |

|---------|------------------------|--|--|

| VREG_EN | P01.0/TACLK/CAOUT      |  |  |

| RESETn  | P05.7/TBOUTH/SVSOUT    |  |  |

| SCLK    | P05.3/UCB1CLK/UCA1STE  |  |  |

| SO      | P05.2/UCB1SOMI/UCB1SCL |  |  |

| SI      | P05.1/UCB1SIMO/UCB1SDA |  |  |

| CSn     | P05.0/UCB1STE/UCA1CLK  |  |  |

| GPIO0   | P01.3/TA2              |  |  |

| GPIO1   | P01.5/TA0              |  |  |

| GPIO2   | P01.6/TA1              |  |  |

| GPIO3   | P01.1/TA0/BSLTX        |  |  |

| GPIO4   | P01.2/TA1              |  |  |

| GPIO5   | P01.7/TA2              |  |  |

A simplified drawing of the interconnection of MSP430F2618 and CC2520 is shown in Figure 8. For further details on the MSP430F2618, please refer to [10].

Figure 5: Interconnection of MSP430F2618 and CC2520

# 10 Serial Peripheral Interface (SPI)

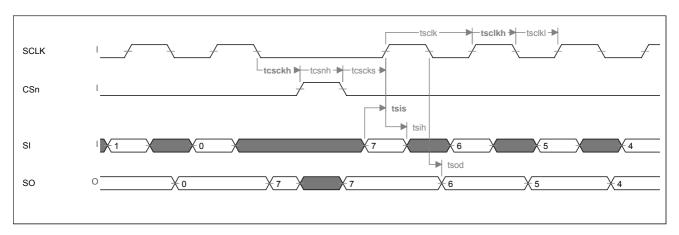

The SPI provides an interface for giving instructions to the CC2520 and transferring data between CC2520 and a microcontroller. The CC2520 4-wire slave interface consists of three input signals (CSn, SCLK and SI) and one output signal (SO).

In section 15 all instructions available via the SPI interface are listed and described. The instructions are byte oriented and required bytes sent over the interface to CC2520 vary from 1 and up. To transfer one byte CSn must be pulled low and SCLK must complete 8 periods starting with a positive edge. There are no requirements to maximum period for SCLK or that it needs to be continuous. As long as CSn is held low, SCLK can be halted at any time and started again when desired.

### 10.1 CSn

CSn is an input enable signal for the SPI and is controlled by the external MCU. The CSn signal is used as an asynchronous active high reset to the SPI module.

CSn must be held low during all SPI operations and must also be held low for more than two periods of XOSC before the first positive edge of SCLK and more than two periods of XOSC after the last negative edge of SCLK.

When CSn is high it must be held high for at least 2 periods of XOSC.

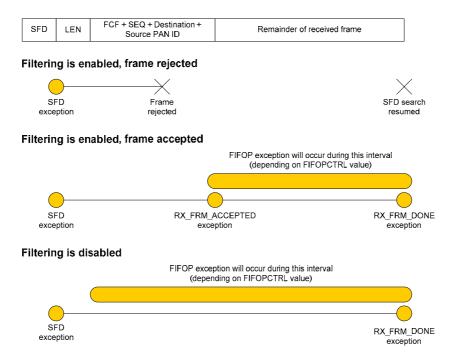

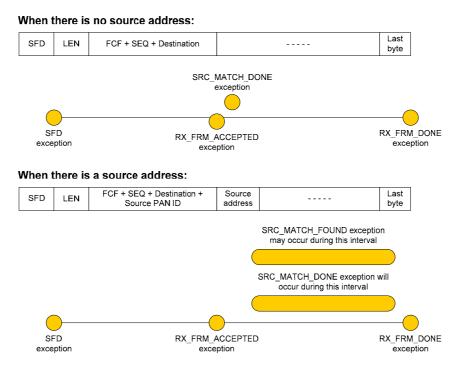

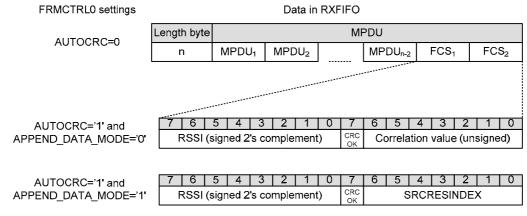

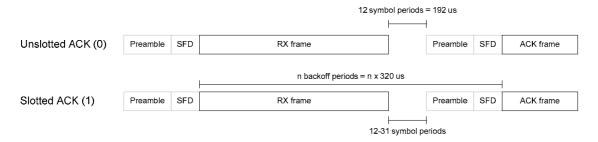

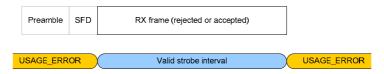

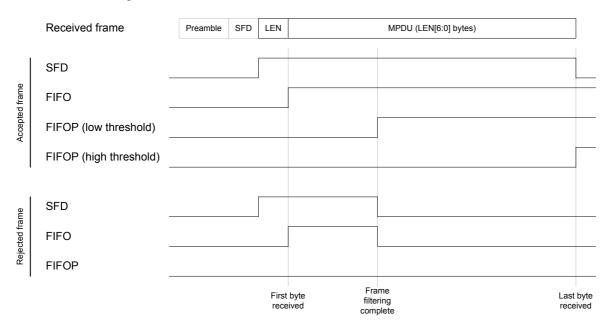

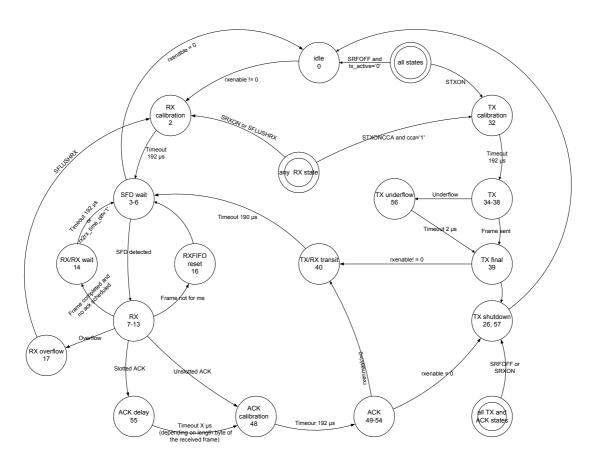

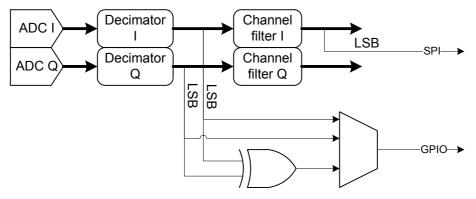

CSn can be held low between SPI operations in the case where the last instruction completed has a constant number of bytes, but this will result in unnecessary power consumption since parts of the instruction controller will then be running.