## SY898530U

# 500MHz 1:16 3.3V-to-2.5/3.3V LVPECL Fanout Buffer

### **General Description**

The SY898530U is a 1:16 Fanout buffer which can accept most standard differential logic levels and outputs the signal as a differential 2.5V or 3.3V LVPECL signal. The part can amplify input signals as small as 150mVpp to the full LVPECL output swing. The SY898530U is well suited for clock distribution applications which demand versatility and low-skew performance. It is pin-to-pin compatible with IDT's ICS8530 fanout buffer.

The SY898530U operates from a 3.3V  $\pm 5\%$  core power supply and a 2.5V  $\pm 5\%$  or a 3.3V  $\pm 5\%$  output supply. The SY898530U is guaranteed over the full commercial temperature range (0°C to  $\pm 70$ °C). It is available in a 48-pin TQFP lead-free package.

Data sheets and support documentation can be found on Micrel's web site at <a href="https://www.micrel.com">www.micrel.com</a>.

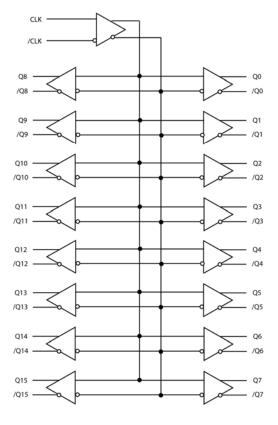

### **Functional Block Diagram**

#### **Features**

- 16 Differential 2.5V/3.3V LVPECL outputs

- Differential CLK inputs. Accepts LVDS, LVPECL, LVHSTL, SSTL, HCSL logic levels

- Translates any single-ended input signal to 2.5/3.3V LVPECL levels with a resistor bias on /CLK input

- 500MHz maximum output frequency

- <50ps output skew

- <250ps part-to-part skew</li>

- <2ns propagation delay

- 3.3V Core, 2.5/3.3V output operating supply

- 0°C to +70°C operating temperature

- Available in 48-pin TQFP package

- Pin-to-pin compatible with ICS8530

### **Applications**

- Data distribution

- High-performance PCs

- Communications

- Parallel processor-based systems

Precision Edge is a registered trademark of Micrel, Inc.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

## Ordering Information(1)

| Part Number                     | Package Type | Operating Range | Package Marking                             | Lead Finish |

|---------------------------------|--------------|-----------------|---------------------------------------------|-------------|

| SY898530UTZ                     | TQFP-48      | Commercial      | SY898530UTZ with Pb-Free bar-line indicator | Matte-Sn    |

| SY898530UTZTR <sup>(2)</sup>    | TQFP-48      | Commercial      | SY898530UTZ with Pb-Free bar-line indicator | Matte-Sn    |

| SY898530UTZTX <sup>(2, 3)</sup> | TQFP-48      | Commercial      | SY898530UTZ with Pb-Free bar-line indicator | Matte-Sn    |

#### Notes:

- 1. Contact factory for die availability. Dice are guaranteed at  $T_A$  = 25°C, DC Electricals only.

- Tape and Reel.

- 3. EIA specification orientation.

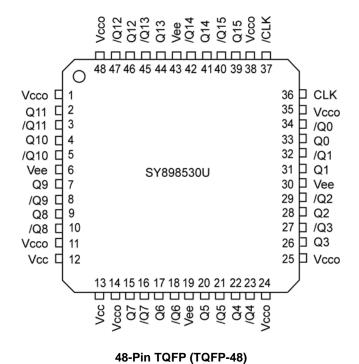

## **Pin Configuration**

## **Pin Description**

| Pin Number     | Pin Name  | Pin Function                                                                                                                                                                                                                             |

|----------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 36, 37         | CLK, /CLK | Differential Clock Inputs. Accepts LVDS, LVPECL, LVHSTL, SSTL, HCSL logic levels. CLK is internally connected to a pull-down resistor, /CLK is internally connected to a pull-up resistor. See "Pin Characteristics" for typical values. |

| 33, 34         | Q0, /Q0   |                                                                                                                                                                                                                                          |

| 31, 32         | Q1, /Q1   |                                                                                                                                                                                                                                          |

| 28, 29         | Q2, /Q2   |                                                                                                                                                                                                                                          |

| 26, 27         | Q3, /Q3   |                                                                                                                                                                                                                                          |

| 22, 23         | Q4, /Q4   |                                                                                                                                                                                                                                          |

| 20, 21         | Q5, /Q5   |                                                                                                                                                                                                                                          |

| 17, 18         | Q6, /Q6   |                                                                                                                                                                                                                                          |

| 15, 16         | Q7, /Q7   | LVPECL Differential Output Pairs. Differential buffered copies of the input signal. The                                                                                                                                                  |

| 9, 10          | Q8, /Q8   | output swing is typically 740mV. See Interface Applications for termination information.                                                                                                                                                 |

| 7, 8           | Q9, /Q9   |                                                                                                                                                                                                                                          |

| 4, 5           | Q10, /Q10 |                                                                                                                                                                                                                                          |

| 2, 3           | Q11, /Q11 |                                                                                                                                                                                                                                          |

| 46, 47         | Q12, /Q12 |                                                                                                                                                                                                                                          |

| 44, 45         | Q13, /Q13 |                                                                                                                                                                                                                                          |

| 41, 42         | Q14, /Q14 |                                                                                                                                                                                                                                          |

| 39, 40         | Q15, /Q15 |                                                                                                                                                                                                                                          |

| 1, 11, 14, 24, | VCCO      | Output Power Supply: Bypass with 0.1µF//0.01µF low ESR capacitors as close to the                                                                                                                                                        |

| 25, 35, 38, 48 | VCCO      | V <sub>CCO</sub> pins as possible. Supplies the output buffers.                                                                                                                                                                          |

| 12, 13         | VCC       | Core Power Supply: Bypass with $0.1\mu F//0.01\mu F$ low ESR capacitors as close to the $V_{CC}$ pins as possible. Supplies input and core circuitry.                                                                                    |

| 6, 19, 30, 43  | VEE       | Ground                                                                                                                                                                                                                                   |

## **Pin Characteristics**

| Symbol                | Description              | Min. | Тур. | Max. | Units |

|-----------------------|--------------------------|------|------|------|-------|

| C <sub>IN</sub>       | Input Capacitance        |      | 4    |      | pF    |

| R <sub>PULLUP</sub>   | Input Pull Up Resistor   |      | 50   |      | ΚΩ    |

| R <sub>PULLDOWN</sub> | Input Pull Down Resistor |      | 30   |      | ΚΩ    |

## **Clock Input Function Table**

| Inj                   | outs                  | Out  | puts | Innut to Output Made         | Polarity      |  |

|-----------------------|-----------------------|------|------|------------------------------|---------------|--|

| CLK                   | /CLK                  | Qx   | /Qx  | Input to Output Mode         | Polarity      |  |

| 0                     | 1                     | Low  | High | Differential to Differential | Non-Inverting |  |

| 1                     | 0                     | High | Low  | Differential to Differential | Non-Inverting |  |

| 0                     | Biased <sup>(1)</sup> | Low  | High | Single-Ended to Differential | Non-Inverting |  |

| 1                     | Biased <sup>(1)</sup> | High | Low  | Single-Ended to Differential | Non-Inverting |  |

| Biased <sup>(1)</sup> | 0                     | High | Low  | Single-Ended to Differential | Inverting     |  |

| Biased <sup>(1)</sup> | 1                     | Low  | High | Single-Ended to Differential | Inverting     |  |

#### Note:

<sup>1.</sup> Refer to Interface Applications for Single-Ended Interfaces.

## Absolute Maximum Ratings<sup>(1)</sup>

| Supply Voltage (V <sub>CC</sub> )         | 4.6V                           |

|-------------------------------------------|--------------------------------|

| Input Voltage (V <sub>IN</sub> )          | 0.5V to V <sub>CC</sub> + 0.5V |

| LVPECL Output Current (I <sub>OUT</sub> ) |                                |

| Continuous                                | 50mA                           |

| Surge                                     | 100mA                          |

| Lead Temperature (soldering,              |                                |

| Storage Temperature (T <sub>s</sub> )     |                                |

## Operating Ratings<sup>(2)</sup>

| Supply Voltage (V <sub>CC</sub> )         | 3.135V to 3.465V |

|-------------------------------------------|------------------|

| Output Supply Voltage (V <sub>CCO</sub> ) | 2.375V to 3.465V |

| Ambient Temperature (T <sub>A</sub> )     | 0°C to +70°C     |

| Package Thermal Resistance <sup>(3)</sup> |                  |

| TQFP                                      |                  |

| Still-air $(\theta_{JA})$                 | 48°C/W           |

| Junction-to-Case (θ <sub>JC</sub> )       | 13°C/W           |

### DC Electrical Characteristics<sup>(6)</sup>

$V_{CC} = 3.135V$  to 3.465V,  $V_{CCO} = 2.375V$  to 3.465V,  $T_A = 0^{\circ}C$  to +70°C, unless otherwise stated.

| Symbol           | Parameter                  |               | Condition                               | Min.  | Тур. | Max.                   | Units |

|------------------|----------------------------|---------------|-----------------------------------------|-------|------|------------------------|-------|

| V <sub>CC</sub>  | Power Supply Voltage Range |               |                                         | 3.135 | 3.3  | 3.465                  | V     |

| V <sub>cco</sub> | Output Power Supply        |               |                                         | 2.375 |      | 3.465                  | V     |

| I <sub>EE</sub>  | Power Supply Current       |               | Max. V <sub>CC</sub> , V <sub>CCO</sub> |       |      | 125                    | mA    |

|                  | In next LUCI I Commont     | CLK           | \\ -\\ - 2.405\\                        |       |      | 150                    | uA    |

| I <sub>IH</sub>  | Input HIGH Current         | /CLK          | $V_{CC} = V_{IN} = 3.465V$              |       |      | 5                      | uA    |

|                  | 1 0 0 0 0 0 0 0            | CLK V 2.405VA | \ -2.465\\\\ -0.5\\                     | -5    |      |                        | uA    |

| I <sub>IL</sub>  | Input LOW Current          | /CLK          | $V_{CC} = 3.465 V, V_{IN} = 0.5 V$      | -150  |      |                        | uA    |

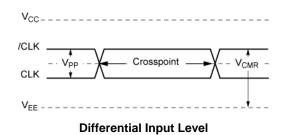

| $V_{PP}$         | Peak-to-Peak Input S       | wing          |                                         | 0.15  |      | 1.3                    | V     |

| $V_{\text{CMR}}$ | Common Mode Input          | Voltage       | Note 4, 5                               | 0.5   |      | V <sub>cc</sub> - 0.85 | V     |

## PECL Outputs DC Electrical Characteristics<sup>(6)</sup>

$V_{CC}$  = 3.135V to 3.465V,  $V_{CCO}$  = 2.375V to 3.465V,  $T_A$  = 0°C to +70°C, Outputs terminated with 50 $\Omega$  to  $V_{CCO}$ -2V unless otherwise stated.

| Symbol           | Parameter            | Condition | Min.                   | Тур. | Max.                   | Units |

|------------------|----------------------|-----------|------------------------|------|------------------------|-------|

| V <sub>OH</sub>  | Output HIGH Voltage  |           | V <sub>CCO</sub> – 1.1 |      | V <sub>CCO</sub> - 0.7 | V     |

| V <sub>OL</sub>  | Output LOW Voltage   |           | V <sub>CCO</sub> - 2.0 |      | V <sub>CCO</sub> – 1.4 | V     |

| V <sub>OUT</sub> | Output Voltage Swing |           | 0.55                   |      | 0.93                   | V     |

#### Notes:

- 1. Permanent device damage may occur if absolute maximum ratings are exceeded. This is a stress rating only and functional operation is not implied at conditions other than those detailed in the operational sections of this data sheet. Exposure to absolute maximum ratings conditions for extended periods may affect device reliability.

- 2. The data sheet limits are not guaranteed if the device is operated beyond the operating ratings.

- 3.  $\theta_{JA}$  and  $\theta_{JC}$  values are determined for a 4-layer board in still-air.

- 4. For single-ended applications, the maximum input voltage for CLK, /CLK is  $V_{CC}$ +0.3V.

- 5. Common mode voltage is defined as V<sub>IH</sub>.

- 6. The circuit is designed to meet the DC specifications shown in the above table after thermal equilibrium has been established.

#### **AC Electrical Characteristics**

$V_{CC}$  = 3.135V to 3.465V,  $V_{CCO}$  = 2.375V to 3.465V,  $T_A$  = 0°C to +70°C, unless otherwise stated.

| Symbol                          | Parameter                              | Condition             | Min. | Тур. | Max. | Units             |

|---------------------------------|----------------------------------------|-----------------------|------|------|------|-------------------|

| f <sub>MAX</sub>                | Maximum Frequency                      |                       | 500  |      |      | MHz               |

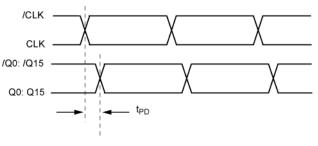

| t <sub>PD</sub>                 | Propagation Delay                      | Note 7                | 1    |      | 2    | ns                |

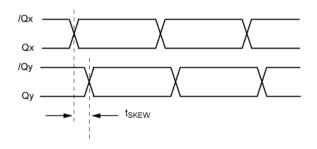

| 4                               | Output-to-Output skew                  | Note 8, 10            |      | 26   | 50   | ps                |

| t <sub>Skew</sub>               | Part-to-Part Skew                      | Notes 9, 10           |      |      | 250  | ps                |

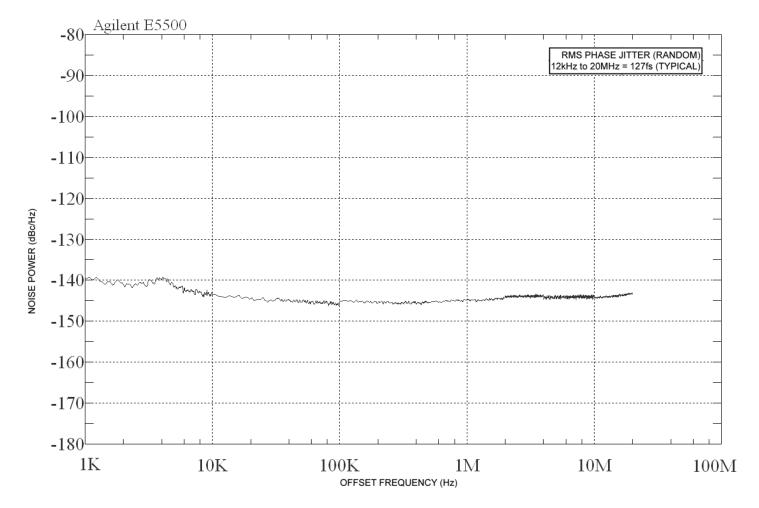

| t <sub>JITTER</sub>             | Integration Range = 12kHz – 20MHz      | Output = 500MHz       |      | 127  |      | fs <sub>rms</sub> |

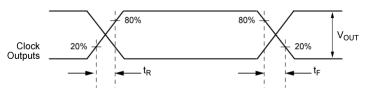

| t <sub>R</sub> , t <sub>F</sub> | Output Rise/Fall Times<br>(20% to 80%) | At full output swing. | 300  |      | 700  | ps                |

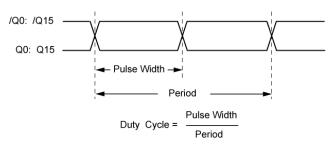

|                                 | Duty Cycle                             |                       | 47   | 50   | 53   | %                 |

#### Notes:

- 7. Measured from the differential input crossing point to the differential output crossing point.

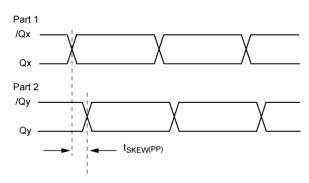

- 8. Output-to-Output skew is the difference in time between outputs, receiving data from the same input, for the same temperature, voltage and transition.

- 9. Part-to-part skew is defined for two parts with identical power supply voltages at the same temperature and no skew at the edges at the respective inputs.

- 10. This parameter is defined in accordance with JEDEC Standard 65.

## **Phase Noise Graph**

Phase Noise Plot: 500MHz @ 3.3V

## **Test Circuit**

**Output Duty Cycle**

**Propagation Delay**

**Output Rise/Fall Times**

Output-to-Output Skew

Part-to-Part Skew

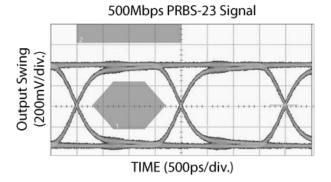

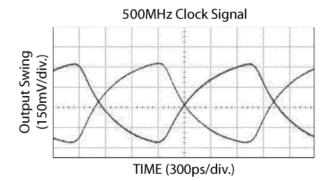

## **Typical Characteristics**

$V_{CC}$  = 3.3V,  $V_{CCO}$  = 2.5V or 3.3V,  $T_A$  = 25°C, Input Signal = 800mV

## **Junction Temperature**

The maximum recommended junction temperature is  $T_J$  =125°C. The outputs are terminated with 50 ohms to Vcco - 2V. Below is a calculation of the worst case scenario with zero airflow:

```

T<sub>.</sub>|= Junction Temperature

T<sub>A</sub> = Ambient Temperature

\Theta_{JA} = Junction-to-Ambient Thermal Resistance

P<sub>d</sub> = Power Dissipation

P_d = P_{d \text{ core}} + P_{d \text{ outputs}}

P_{d\_core} = V_{cc\_max} * I_{ee\_max}

P_{d core} = 3.465V * 125mA = 433mW

P<sub>d output</sub> = Pd_h + Pd_I

P_{d_h} = [(V_{oh} - (V_{cco} - 2V))/R_L] * (V_{cco} - V_{oh_max})

P_{dh} = [(2V - 0.7V)/50\Omega] * 0.7V

P_{dh} = 18.2 \text{mW}

P_{d \mid l} = [(V_{ol} - (V_{cco} - 2V))/R_L] * (V_{cco} - V_{ol \mid max})

P_{d_{\perp}} = [(2V - 1.4V)/50\Omega] * 1.4V

P_{d | I} = 16.8 \text{mW}

P_{d \text{ output}} = 35 \text{mW}

P<sub>d outputs</sub> = 16 * 35mW

P<sub>d outputs</sub> = 560mW

P_d = 433 \text{mW} + 560 \text{mW}

P_d = 0.993 W

T_J = T_A + \Theta_{JA} * P_d

T_{J\_worst\_case} = 70^{\circ}C + 0.993W * 48^{\circ}C/W

```

The worst case junction temperature is below 125 C.

$T_{J \text{ worst case}}$  = 118 °C in still air.

## **Output Interface Applications**

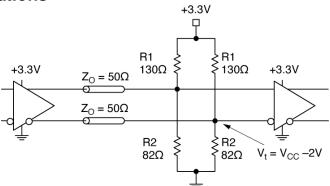

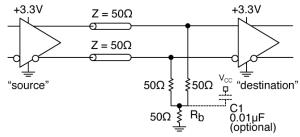

Figure 1. Parallel Termination-Thevenin Equivalent

#### Notes:

1. For +2.5V systems: R1 =  $250\Omega$ , R2 =  $82.5\Omega$ .

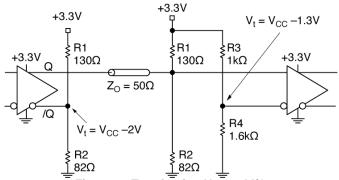

Figure 2. Three-Resistor "Y-Termination"

#### Notes:

- 1. Power-saving alternatives to Thevenin termination.

- 2. Place termination resistors as close to destination inputs as possible.

- 3. For +2.5V systems,  $R_b$  = 19 $\Omega$ .  $R_b$  resistor sets the DC bias voltage, equal to  $V_t$ .

Figure 3. Terminating Unused I/O

#### Notes:

- 1. Unused output (/Q) must be terminated to balance the output.

- 2. For 2.5V systems: R1 = 250 $\Omega$ , R2 = 62.5 $\Omega$ , R3 = 1.25k $\Omega$ , R4 = 1.2k $\Omega$ .

## **Input Interface Applications**

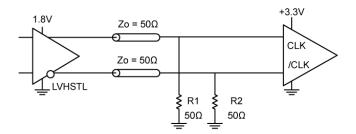

Figure 4. CLK and /CLK Input Driven By 1.8V LVHSTL

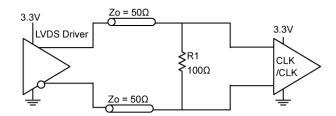

Figure 5. CLK and /CLK Input Driven By 3.3V LVDS Driver

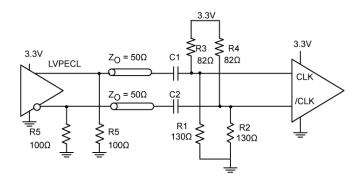

Figure 6. CLK and /CLK Input Driven By 3.3V LVPECL Driver with AC Couple

#### Notes:

1. For +2.5V systems: R5 = 50  $\Omega$ . R1 & R2 = 220 $\Omega$ , R3 & R4 = 68 $\Omega$ .

SY898530U Micrel, Inc.

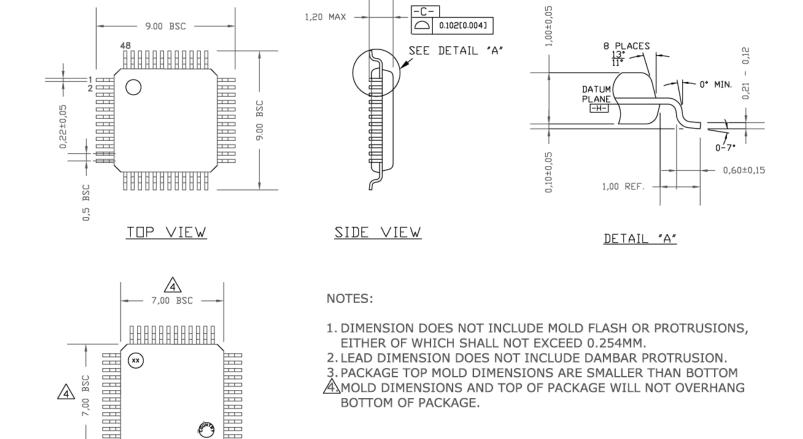

### **Package Information**

BOTTOM VIEW

7,00 BSC

48-Pin TQFP (TQFP-48)

BOTTOM OF PACKAGE.

3. PACKAGE TOP MOLD DIMENSIONS ARE SMALLER THAN BOTTOM

AMOLD DIMENSIONS AND TOP OF PACKAGE WILL NOT OVERHANG

### MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB http://www.micrel.com

Micrel makes no representations or warranties with respect to the accuracy or completeness of the information furnished in this data sheet. This information is not intended as a warranty and Micrel does not assume responsibility for its use. Micrel reserves the right to change circuitry, specifications and descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Micrel's terms and conditions of sale for such products, Micrel assumes no liability whatsoever, and Micrel disclaims any express or implied warranty relating to the sale and/or use of Micrel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2011 Micrel, Incorporated.

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

## Microchip:

SY898530UTZ SY898530UTZ TR SY898530UTZ-TR